Labonnah Farzana Rahman, Mamun Bin Ibne Reaz, Mohd Alauddin Mohd Ali, Mohd Marufuzzaman

# Design and Implementation of a Low Supply Voltage Voltage Type Sense Amplifier with Low Current Consumption for RFID Transponder

DOI 10.7305/automatika.54-2.119 UDK 621.375.4.027.2 IFAC 4.4

Original scientific paper

Current or voltage-type sense amplifier (SA) is the key element for sensing process of RFID transponder EEP-ROM. The performance of the EEPROM is influenced by the SA features like memory access time, power dissipation and the reliability. However, larger current or power dissipation put limitations on using current type SA with respect to voltage type SA. A low voltage SA with lower current consumption is presented in this research work, which is compatible with the low power applications like RFID transponder EEPROM. In this research,  $0.18\mu$ m process is employed to design the low voltage SA with lower power consumption. The simulated results of the output showed that voltage type SA is able to operate under a low power supply voltage (VDD). In addition, only 32  $\mu$ A current is dissipated by the modified voltage type SA during read period. Moreover, the proposed voltage type SA provides better reliability than the circuits presented in other research papers.

Key words: Transponder, EEPROM, RFID, Sense amplifier

Dizajn i implementacija naponskog mjernog pojačala za RFID transponder s niskim naponom napajanja i malom potrošnjom struje. Strujno ili naponsko mjerno pojačalo (MP) je ključni element očitanja RFID transpondera s EEPROM-om. Na učinak EEPROM-a utječu svojstva pojačala kao što su vrijeme pristupa memoriji, energetski gubici i pouzdanost. Veliki gubici struje i energije ograničavaju mogućnost korištenja strujnog mjernog pojačala u odnosu na naponsko. U ovom radu prikazano je niskonaponsko mjerno pojačalo s malom potrošnjom energije koje je prikladno za korištenje kod RFID transpondera s EEPROM-om. Koristi se proces od  $0.18\mu$ m za dizajniranje niskonaponskog pojačala male potrošnje. Simulacije izlaznog napona su pokazale da naponsko mjerno pojačalo može raditi s niskim naponom napajanja. Tijekom vremena očitanja na modificiranom naponskom pojačalu troši se samo  $32\mu$ A struje. Predloženo naponsko mjerno pojačalo ima bolju pouzdanost od onih prikazanih u drugim člancima.

Ključne riječi: transponder, EEPROM, RFID, mjerno pojačalo

## **1 INTRODUCTION**

In low voltage applications like RFID transponder, EEPROM is used as a storage device. RFID is the technology for automated identification of products, objects or human. RFID system requires EEPROM memory for highspeed read/write operation. At present, a key design aspect for RFID tag IC is the low power dissipation and low cost [1-3]. Therefore, in RFID transponders embedded nonvolatile memories (NVM) like EEPROM play a vital role. In fact, EEPROM has become very significant alternative for any application requiring NVM over the last few years [4].

Reading/writing process is the most significant factor for low-power RFID transponders EEPROM [5-6]. The power of the EEPROM SA must be low to increase RFID reading speed [7]. In EEPROM, the read access time is a key factor to determine the read path, which is strongly affected by the SA. One of the main challenges for new generation NVM is to develop a robust and high-speed read circuit with a low VDD. As the power supply becomes lower, the design of a high-speed low-power SA becomes very critical [8-9]. Moreover, the reliability of the SA has to be improved to make consistent operations of RFID transponders.

Generally, the current sensing method is widely employed to design a conventional SA in EPROM read operation. Due to the advanced speed and reliability features, current type SA has been used more frequently than voltage type SA [9]. However, conventional current sensing method has the drawbacks of higher power dissipation and larger time for sensing. Moreover, current type SA requires extra control logic to prevent incorrect read out current. As a result, current type SA is unacceptable to low power applications like RFID transponders. Consequently, lower current and power consumption made voltage type SA superior to current type SA, which is compatible in RFID tag EEPROM [9-10].

To attain reduced sensing current, numerous voltagetype SA circuits have been designed for NVM. However, at lower VDD the reading consistency issues and higher reading current is experienced by the researchers [11]. In 2009, Liu et al. proposed voltage type SA with low cost, low power and reliability. The circuit is implemented using SMIC  $0.35\mu$ m CMOS process [12]. In VDD = 3.3 V the charging time is 35 ns for the voltage type SA. In addition, the highest average current consumption during the sense period is  $40\mu$ A. However, the lowest VDD required for the design was 1.4 V. However, the voltage claimed by Liu et al. is not as low as VDD for RFID transponder.

In this research, a low voltage SA for EEPROM memories in RFID tag is designed to attain the lower reading current/power. This design overcomes the limitations of the conventional current SA. Low voltage sensing method has been used in this design to achieve better circuit performance, and decreasing sensing time. To reduce the reading current/power an additional capacitor is used in this design. The proposed low voltage-type SA is designed in CEDEC  $0.18 - \mu m$  CMOS process. Simulations results show that the modified low voltage-type SA performs better than the SA designed by Liu et al. [12].

# 2 CONVENTIONAL SA

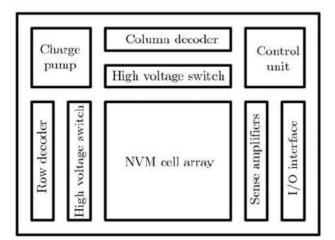

Though the floating-gate devices have many limitations, low power design on circuit level is still the best solution for RFID applications [13]. NVM type EEPROM circuits block diagram is shown in Figure 1, where the NVM cell array is used to store data.

The control unit, row and column decoders and high-voltage switches are used inside EEPROM to control logic operations. On the other hand, the charge pump is used to generate a high voltage for writing operations. The SAs are useful for sensing the '0' and '1' bit. Whereas, the in-put/output (I/O < 7 : 0 >) interface is used for transferring output data.

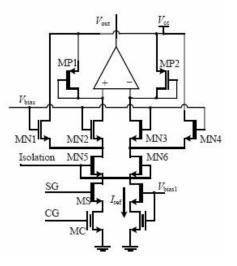

Several researchers treat the design of conventional SAs using current sensing method [7, 9, 14]. Figure 2 shows the circuit diagram of the conventional SA.

In the conventional SA circuit, the measurement of  $0^{\circ}$  and  $1^{\circ}$  is classified by using a differential circuit for reliability between the read out current and a reference current. However, the circuit has some drawbacks:

Fig. 1. Block diagram of an EEPROM [10]

Fig. 2. The circuit diagram of conventional SA [7, 9, 14]

- High power consumption is pointed as the most common problem of the conventional SA. A large reference current I<sub>ref</sub> is required by the conventional SA circuit to differentiate between '0' and '1' data, which is typically the average of the read out currents. Tens of μA reference current is needed for reliability [10]. Thus, a large amount of read out current: I<sub>ref</sub>ε(nI<sub>ref</sub>, 3nI<sub>ref</sub>) is required for the conventional SA for reading parallel data. Where, n is the number of bits read out in parallel [12].

- 2. Floating gate transistor changes the '0' and '1' current levels by attribute degeneration. Thus, for '0' and '1' the perfect selection of  $I_{ref}$  is differed from the initial average of the read out currents. Therefore, a minor variation between the read out current and the refer-

ence current for one level to other is produced. This distinction of the current necessitates more time for sensing [15].

3. The conventional SA circuit is constructed with many floating gate transistor which store charge. Hence, it is important to use an extra control logic circuit to prevent incorrect read out current and correctly manage the charge stored on key nodes.

However, to reduce the sensing time and to make the power consumption lower, a low voltage SA is essential for non-volatile memories like EEPROM in RFID tag. Moreover, to avoid incorrect read out current, the low voltage SA will not require an extra control logic circuit.

## 3 PROPOSED SA

The compact model (CM) of the floating gate (FG) [16] devices has been used in conventional SA for circuit simulations. However, this compact model experienced two main limitations. First, thin gate oxide transistors with lightly or medium-doped drain (LDD/MDD) diffusions are the main aim of MOS compact model. More than 7nm thickness is used as the oxide of the FG devices while the source and drain junction is usually abrupt. As a result, the existing transistor models might become essential to adapt with this same type of devices. Second, between the control gate node and the source, drain and body nodes, few coupling capacitance exist. Moreover, two neighbor cells may be affected by the coupling capacitance as memory cells are getting closer and smaller one to each other. Based on these limitations, a voltage-mode SA is designed with only one capacitor between the control gate node and the source, drain and body nodes. This method reduces the effect of coupling capacitance between the transistors. Moreover, this method is useful to achieve the lower sensing power/current and higher reading fidelity without speed deprivation compared to the conventional SA.

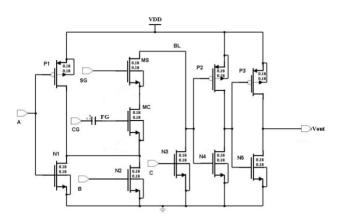

Figure 3 shows the improved designed SA circuit composed of charge controlling and voltage sensing circuits. The memory cell consist of a FG transistor MC and a select transistor MS. To reduce the coupling capacitance between two adjacent memory cells only one capacitor has been used between the control gate and the FG node (which is the gate of the MOS transistor MC).

In the modified SA, the selected sensing path is controlled by the control gate (CG) and transistor MC and a selecting gate (SG) with the transistor MS. The task of the decoders is to control this selecting gate and the terminal CG is determined by a voltage between the two thresholds of memory cells.

For the improved voltage-type SA, the EEPROM memory cell implemented in  $27^{\circ}$ C operating conditions of the

Fig. 3. Schematic diagram of the proposed low voltagetype SA

CEDEC  $0.18 - \mu m$  CMOS process. The threshold voltage of transistor MC is set to 1.5V to store a '0' signal; and the threshold voltage is set to -1V to store a '1' signal. Fig. 3 shows that the operation states of this SA are controlled by the three control terminals: A, B and C.

This modified voltage SA has two states: working state and out-of-work state. In the out-of-work state, to ensure the drain and source of the memory cell are at low level, all the three inputs A, B and C are set to '1'. On the other hand, for the working state, voltage on CG is  $V_{CG} = (P+Q)/2$ and voltage on SG is  $V_{SG} = V_{dd}$  where, P is the threshold voltage of the MC when storing a '0' signal, and Q when storing a '1' signal.

At the beginning to turn off N2 and N3 transistor, inputs C and B are set to '0'. After that, A is set to '0'. At this time,  $V_{out} = 0$  when the stored signal of MC is '0'. Additionally, when the stored signal is '0', the BL (bit line) is charged to  $V_{BL} = min(V_{dd} - V_{tms}, 1.5 - V_{tmc})$ , where,  $V_{tms}$  is the threshold voltage for MS transistor, and  $V_{tmc}$  is the threshold voltage for transistor MC. The stored signal '1' will be generated correctly at  $V_{out}$  as long as,  $V_{BL} > \frac{V_{dd}}{2}$ .

In Figure 3, for sensing the stored voltage '0' or '1' at transistor MC, the drain and source of MOS transistors employ bidirectional conduction [11]. This voltage mode SA enables costs to be reduced; since it has no bias circuit. The parasitic capacitance is utilized as the charging load at the drain of N3 transistor. To decrease the charged voltage, the threshold voltage of the two inverter composed of NMOS transistors N4, N5 and PMOS transistors P2, P3 have been added. This will result in a shorter charging time of BL and makes the lower read power dissipation. Additionally, the modified voltage type SA is capable of resisting the degeneration features of the floating gate transistor by using a voltage sensing method rather than a current sensing method. The transient current and charges for charging in

one read process are described respectively, by the following equations:

$$\frac{\partial (V_{BLT}C_{N3})}{\partial t} = \beta (V_{CG} - V_{tmc} - V_{BLT})^2 \qquad (1)$$

$$\int_{0}^{T} \beta (V_{CG} - V_{tmc} - V_{BLT})^2 dt = C_{N3} (V_{CG} - V_{tmc})$$

(2)

where,  $V_{BLT}$  is the transient voltage of the BL,  $C_{N3}$  is the parasitic capacitance at the drain of N3 , and T is the charging time  $\beta = \mu_n C_{ox} W/(2L)$ .

Using equation (1) and (2), the average charging time and current can be obtained during one read period.

# 4 RESULTS AND DISCUSSION

The 27°C operating condition has been set for the modified voltage-type SA and the conventional SAs.They are designed and simulated in CEDEC  $0.18\mu$ m CMOS process. Simulations are done to evaluate the circuit performance of the modified SA with the previously reported voltage type SA [12]. The transistors involved in the sensing circuitry were of equal size  $W/L = 0.18\mu/0.18\mu$ . The significant design factors are listed in Table 1.

Table 1. Main design parameters

| VDD       | C1    | W/L               | SG | CG   |

|-----------|-------|-------------------|----|------|

| (Min/Max) |       |                   |    |      |

| 1V/3V     | 0.1pF | $0.18\mu/0.18\mu$ | 3V | 1.5V |

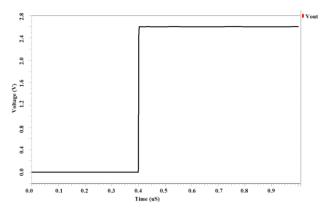

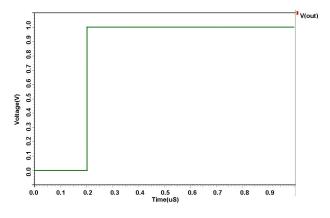

By using, the critical design parameters listed in the above table the output data V(out) for the modified SA is shown in Figure 4 under 2.6 V as VDD. As shown in Fig. 4 the modified voltage type SA reads '0' data at the beginning. At  $0.4\mu$ s the SA reads '1'. The circuit is also able to work for the supply voltage longer than 2.6 V, but above this operating voltage, the circuit experiences noise.

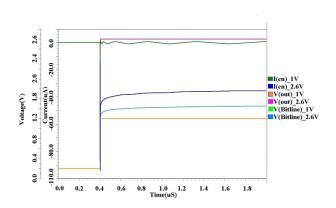

Furthermore, depending on the principle of the memory cell, VCG in equation (1) is the best value for voltage sensing and a lower voltage can be set for VCG. By equation (2) and regulating the threshold voltage of the inverter in Figure 3, the modified voltage mode SA is capable of operating at voltages as low as 1 V. The  $V_{out}$  data for a 1 V as VDD are shown in Figure 5.

The simulation results in Figure 5 show that the voltage required by the voltage-type SA can be significantly reduced from 2.6 V to 1 V, where the voltage was controlled by CG. In order to show the correct behavior of the voltage-type SA, the VDD is set to 1 V and the capacitive load to 0.1 pF.

Fig. 4. Simulation waveforms of V(out) under VDD = 2.6V

Fig. 5. Simulated waveforms of V(out) when Vdd = 1V

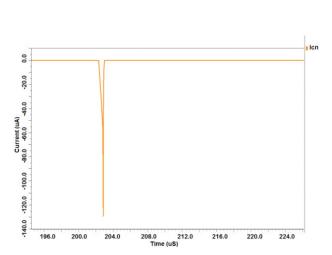

The corresponding current consumption for the modified voltage type SA is shown in Figure 6. Here the average current consumption during the read period is only  $32\mu$ A for the maximum clock speed of 20 MHz. This feature is useful for some electronic systems focused on low voltage and low power such as RFID transponder.

Figure 7 presents a comparison results among the  $V_{out}$  data, the average current consumption during the read period, and the corresponding bit line voltage under 1 V as VDD. The figure further proves that the SA is capable of operating at a voltage as low as 1 V. The circuit is also able to work for the supply voltage longer than 1 V, but in this operating voltage, the circuit experiences noise.

Generally, the required working temperature range of the RFID tag is from  $-25^{\circ}$ C to  $85^{\circ}$ C. As, the modified voltage-type SA circuit is able to work within the temperature range from  $-25^{\circ}$ C to  $125^{\circ}$ C. Therefore, this modified circuit has no power differentiation in working temperature of RFID tag.

A performance evaluation study of voltage type SA between this work and Liu et al. on the low voltage function-

Fig. 6. Simulation waveforms of the current consumption  $I_{cn}$  for voltage type SA

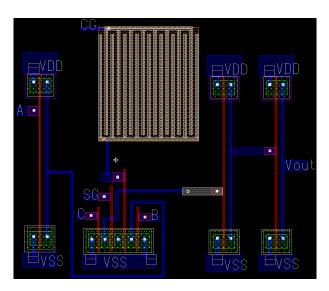

Fig. 8. A layout design of the low voltage-type SA

ality with current consumption is shown in 2.

Fig. 7. Simulated waveforms of  $I_{cn}$ , V(out) and V(BL)under VDD = 1V

Table 2. Performance evaluation of the voltage-type SA between Liu et al. and this work.

| Research       | et al. and th<br>CMOS<br>Technol-<br>ogy | Vdd<br>(Min) | Vdd<br>(Max) | Average<br>current<br>consumption |

|----------------|------------------------------------------|--------------|--------------|-----------------------------------|

| Liu et.<br>al. | $0.35 \mu m$                             | 1.4 V        | 3.3 V        | 40µA                              |

| This<br>Work   | $0.18 \mu m$                             | 1 V          | 2.6 V        | 32µA                              |

From the study, it is shown that the circuit is able to work within 1 V to 2.6 V as VDD, which is lower than the Liu et al. Moreover, the modified circuit required lower current 32  $\mu$ A during read period, whereas, Liu et al. SA consumed 40  $\mu$ A. Hence, the comparison study proves that the proposed voltage type SA performs better than Liu et al.

The modified low voltage-type SA circuit layout is designed in CEDEC 0.18- $\mu$ m CMOS process. In Figure 8, the completed chip layout of the modified low voltage SA is presented. In this layout, the capacitor connected with the control gate transistor is about 0.1pF. This small capacitor only takes a small area of the circuit to reduce the cost of the whole chip. In this research,  $W/L = 0.18\mu/0.18\mu$ is the size for each cell of the MOS transistors, which also proves that the modified SA circuit size is lower than the circuit size designed by Liu et al.

# **5** CONCLUSION

An improved design and a comparative study of low voltage SA circuit using a voltage sensing method is presented in this research. The modified circuit has been designed by using the CEDEC 0.18- $\mu$ m CMOS embedded EEPROM process. In this research, the bidirectional conduction between the drain and source of MOS transistors is used to sense the stored voltage (0'/1') at the floating gate transistors. According to the performance evaluation results, it has been proven that, the circuit is capable of working under a low voltage range from 1 V to 2.6 V. Moreover, the required current dissipation during read period for the proposed design is lower than the design of Liu et al. Furthermore, the measured results confirm that this low voltage SA is free from the power delineation caused by the temperature change. Additionally, the circuit size reduced significantly by using small transistors and capacitors.

# ACKNOWLEDGMENT

This work was supported by the researh grant Arus Perdana (UKM-AP-ICT-20-2010) and Brain Gain Malayisa (MOSTI/BGM/R&D/20) from Universiti Kebangsaan Malaysia and the Ministry of Science, Technology and Innovation (MOSTI) respectively.

#### REFERENCES

- R. Barnett, J. Liu, "An EEPROM Programming Controller for Passive UHF RFID Transponders with Gated Clock Regulation Loop and Current Surge Control", *IEEE Journal* of Solid-State Circuits, vol.43, no.8, pp. 1808-1815, Aug. 2008.

- [2] F. M. Yasin, M.K. Khaw, M. B. I. Reaz, "Radio Frequency Identification: Evolution of Transponder Circuit Design", *Microwave Journal*, vol. 49, no.6, pp. 56-70, 2006.

- [3] T. Dake, E. Ozalevli, "A Precision High-Voltage Current Sensing Circuit", *IEEE Transactions on* Circuits and Systems I: Regular Papers, vol.55, no.5, pp. 1197 – 1202, Jun. 2008.

- [4] L. F. Rahman, M.B.I Reaz, M. A. M. Ali., M. Kamada, "Design of an EEPROM in RFID tag: Employing mapped EPC and IPv6 address", in *Proceedings book of the IEEE* Asia Pacific Conference on *Circuits and Systems(APCCAS),(* Kuala Lumpur, Malaysia), pp. 168-171, 6-9 Dec. 2010.

- [5] R. Glidden, C. Bockorick, S. Cooper, "Design of ultralow-cost UHF RFID tags for supply chain applications", *IEEE Communications Magazine*, vol.42, no.8, pp. 140-151, Aug. 2004.

- [6] D. S. Liu, X. C. Zou, F. Zhang, "Embedded EEPROM Memory Achieving Lower Power - New design of EEP-ROM memory for RFID tag IC", *IEEE Circuits and Devices Magazine*, vol.22, no.6, pp. 53-59, Nov-Dec. 2006.

- [7] J. M. Daga, C. Papaix, M. Merandat, S. Rechard, G. Medulla, J. Guichaoua and D. Auvergne, "Design techniques for EEPROMs embedded in portable systems on chips", *IEEE Design & Test of Computers*, vol.20, no.1, pp. 68-75.5, Jan-Feb, 2003.

- [8] L. Jiang, W. Xueqiang, W. Qin, W. Dong, Z. Zhigang, P. Liyang L. Ming, "A low-voltage sense amplifier for high-performance embedded flash memory", *Journal of Semiconductors*, vol.31, no.10, pp.1-5(5pages), Oct. 2010.

- [9] R. Micheloni, L. Crippa, M. Sangalli, "The flash memory read path: building blocks and critical aspects", *Proceedings of the IEEE*, vol.91, no.4, pp. 537-553, Apr. 2003.

- [10] N. Otsuka, M. A. Horowitz, "Circuit techniques for 1.5 V power supply flash memory", *IEEE Journal of Solid- State Circuits*, vol. 32, no.8, pp. 1217–1230, Aug. 1997.

- [11] L. Ming, K. J. Feng, W. Y. Yuan, "A novel voltage-type sense amplifier for low-power nonvolatile memories", *Science China Information Sciences*, vol.53, no.8, pp. 1676-1681, Aug. 2010.

- [12] D. S. Liu, X. Zou, Q. Yu, F. Zhang, "New design of sense amplifier for EEPROM memory", *Journal of Zhejiang Uni*versity Science A, vol.2, pp. 179-183, Jan. 2009.

- [13] R. Huang, F. L. Zhou, Y. M. Cai, "Novel vertical channel double gate structures for high density and low power flash memory applications", *Science China Series F: Information Sciences*, vol.51, pp. 799–806, 2008.

- [14] F. Xu, X.Q. He, L. Zhang, "Key design techniques of a 40 ns 16 K bits embedded EEPROM memory", in *Proceedings book of the International Conference on Communications, Circuits and Systems (ICCCAS)*, vol. 2, pp. 1516–1520, 27-29 Jun. 2004.

- [15] P. Canet, F. Lalande, J. Razafindramora, "Integrated Reliability in EEPROM Nonvolatile Memory Cell Design", in *Proceedings books of the IEEE Non-volatile Memory Technology Symposium*, (Marseille, France), pp.66-69, 15-17 Nov. 2004.

- [16] P. Pavan, L. Larcher, A. Marmiroli, "Floating Gate Devices: Operation and Compact Modeling", *Journal of Nano Science and Technology Institute (NSTI)*, vol. 2, pp. 120-123, 2004.

Labonnah Farzana Rahman was born in Bangladesh in September 1983. She received her B.Sc. (Eng.) in Computer Science and Engineering from Shah Jalal University of Science and Technology, Sylhet, Bangladesh in 2006. Since 2007 to 2009 she worked for GlaxoSmithKline Bangladesh Limited as an IT Systems Executive. Currently she is doing her Ph.D. in the area of designing readerless RFID transponder systems under the Dept. of Electrical, Electronic and Systems Engineering in UKM. Her research interests

are in the following fields: VLSI, IP Networking, Wireless Networking, Data Communication, Microchip design and fabrication.

#### Design and Implementation of a Low Supply Voltage Voltage Type Sense Amplifier L. F. Rahman, M. B. I. Reaz, M. A. M. Ali, M. Marufuzzaman

Mamun Bin Ibne Reaz was born in Bangladesh, in December 1963. He received his B.Sc. and M.Sc. degree in Applied Physics and Electronics, both from University of Rajhashi, Bangladesh, in 1985 and 1986, respectively. He received his D.Eng. degree in 2007 from Ibaraki University, Japan. He is currently a Professor in the Universiti Kebangsaan Malaysia, Malaysia involving in teaching, research and industrial consultation. He is a regular associate of the Abdus Salam International Center for Theoretical Physics since 2008.

He has vast research experiences in Norway, Ireland and Malaysia. He has published extensively in the area of IC Design and Biomedical application IC. He is author and co-author of more than 100 research articles in design automation and IC design for biomedical applications.

**Mohd. Marufuzzama** was born in Bangladesh in June 1983. He received the B.Sc. (Engg.) in Computer Science and Engineering from Shah Jalal University of Science and Technology, Sylhet, Bangladesh in 2006. He completed his Masters from Universiti Kebangsaan Malaysia in 2012. Currently he is doing his PhD in the Dept. of Electrical, Electronic and Systems Engineering in University Kebangsaan Malaysia. His research interests are in the following fields: Hardware Implementation, Smart home, IP Network-

ing, Wireless Networking, Data Communication, Microchip design and fabrication.

## **AUTHORS' ADDRESSES**

Labonnah Farzana Rahma, B.Sc. Prof. Mamun Bin Ibne Reaz, Ph.D. Prof. Mohd Alauddin Mohd Ali, Ph.D. Mohd. Marufuzzam, B.Sc. Department of Electrical, Electronic and Systems Engineering, University Kebangsaan Malaysia, 43600 UKM Bangi, Selangor Darul Ehsan, Malaysia

email: labonnahf@gmail.com, mamun.reaz@gmail.com, mama@eng.ukm.my, mohd.marufuzzaman@gmail.com

Received: 2011-10-08 Accepted: 2012-06-30

Mohd Alauddin Mohd Ali received his B.Eng. (Electrical), B.Sc. (Mathematics) and M.Sc. in Electrical Engineering from University of Tasmania, Australia in 1978, 1979 and 1984 respectively. He is also received his Dip. Peng. Islam from Universiti Kebangsaan Malaysia in 1987 and Ph.D. (Electrical) from University of Nottingham in 1994. Currently he is working as a Director of Institute of Space Science, ANGKASA, Research Fellow of Institute of Microengineering and Nanoelectronics (IMEN). He is also working

as a Professor in the Department of Electrical, Electronic and Systems Engineering, Universiti Kebangsaan Malaysia.