## University of Arkansas, Fayetteville

# ScholarWorks@UARK

**Graduate Theses and Dissertations**

7-2021

# Design and Validation of A High-Power, High Density All Silicon Carbide Three-Level Inverter

Zhongjing Wang University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Electrical and Electronics Commons, Electronic Devices and Semiconductor Manufacturing Commons, Power and Energy Commons, and the Transportation Engineering Commons

#### Citation

Wang, Z. (2021). Design and Validation of A High-Power, High Density All Silicon Carbide Three-Level Inverter. *Graduate Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/etd/4197

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu.

Design and Validation of A High-Power, High Density All Silicon Carbide Three-Level Inverter

## A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering with a concentration in Electrical Engineering

by

Zhongjing Wang

Central South University

Bachelor of Engineering, 2015

The Ohio State University

Master of Science in Electrical and Computer Engineering, 2017

July 2021 University of Arkansas

| This dissertation is approved for rec | commendation to the Graduate Council. |  |

|---------------------------------------|---------------------------------------|--|

| Yue Zhao, Ph.D. Dissertation Director |                                       |  |

| Juan C. Balda, Ph.D. Committee Member | Roy McCann, Ph.D. Committee Member    |  |

| David Huitink, Ph.D. Committee Member |                                       |  |

#### **ABSTRACT**

Transportation electrification is clearly the road toward the future. Compared to internal combustion engine, the electrified vehicle has less carbon-dioxide emission, less maintenance costs and less operation costs. It also offers higher efficiency and safety margin. More importantly, it relieves human's dependence on conventional fossil energy. In the electrification progress, the revolution of electric traction drive systems is one of the most important milestone. The traction system should keep high efficiency to avoid performance reduction. Moreover, the motor drive should be designed within limited space without sacrificing output power rating. Based on the road map from US Drive Electrical and Electronics Technical Team, US Department of Energy, a gap is still there between roadmap target and the state-of-art. To fill the gap, this dissertation performs a systematic research in motor drive system for traction inverters. This paper starts from optimal theoretical design of power converters by using loss model and real-time simulation system. Based on optimal paper design, hardware design is implemented. The component design for converter, such as the laminated busbar, are the focus in this dissertation. The optimized busbar structure can effectively reduce stray inductance in the current-commutation loop, reducing switching overshoots of power modules and increasing semiconductor reliability. The systemlevel design and trade-off is also analyzed and illustrated by using a 250kW three-level T-type neutral-point clamped converter. The design has reached high efficiency and high-power density. The converter system is also evaluated through comprehensive tests, such as double-pulse tests and continuous tests. The test setup, test condition and test result analysis are discussed in the dissertation. In the end, the dissertation also proposed an improved impedance characterization method for components parasitic inductance measurement in traction drive systems, such as

laminated busbar, power module and capacitors. The characterization shares better accuracy and can be customized for device under test with any geometry.

© 2021 Zhongjing Wang All Rights Reserved

#### ACKNOWLEDGMENTS

First and foremost, I would like to express my great appreciation to my advisor, Prof. Yue Zhao, whose cheerful personality, pursuit of innovative ideas, diligent work attitude and patience for each student have influenced me with latent power. Under his guidance, our lab has maintained a free, equal, and cooperative research environment. I will always remember Prof. Zhao's meticulous revision of my papers and the great support for me to start my career. I really enjoyed my four years of Ph. D. study with Prof. Zhao's guidance and mentorship.

I am very grateful to my other committee members, Profs. Juan C. Balda, Profs. David Huitink, and Profs. Roy McCann. As my committee members, they provided valuable suggestions through multiple discussions both for my projects and dissertation works. My appreciation also goes to Profs. Fang Luo, Margot Purdy from College of Engineering, Audra Johnston from International Students and Scholars, and Dr. Chris Farnell from NCREPT.

I would like to take this opportunity to express my gratitude to my colleagues whom I have worked together with on multiple meaningful and challenging projects: Mohammad Hazzaz Mahmud, Yuheng Wu, Bakhtiyar Nafis, and Fei Diao. I also want to thank my other colleagues and friends: Dr. Shuang Zhao, Zhe Zhao, Dr. Waleed Alhosaini, Zhuxuan Ma, Nan Lin, Xinyuan Du, Tyler Adamson, Dr. Cai Chen, Dr. Balaji Narayanasamy, Hongwu Peng, Dr. Amol Deshpande, Sudharsan Chinnaiyan, Si Huang, Rana Alizadeh, Xingchen Zhao. I'd also like to thank Dr. Yuzhi Zhang for his help and guidance during my internship at ABB USCRC at Raleigh, NC, and Dr. He Li, Dr. Chengcheng Yao, Yingzhuo Chen for their support during my internship at Tesla at Palo Alto, CA.

Last but not at least, I would like to say that I am very lucky to spend four years in this quiet town. There are wonderful and responsible teachers, kind administrative staff, and supportive learning and research environment. I will keep this four-year memory deeply in my heart, and this journey will encourage and accompany me into new stages in my life. I will put everything I learned here in my future work and share my future gains with people who have helped me here.

# **DEDICATION**

This dissertation is dedicated to my dearest fiancé, Zhao Yuan, and my beloved parents, Xueming Wang and Xia Wang.

# TABLE OF CONTENTS

| CHAPT | ER 1 INTRODUCTION                                                                       | 1   |

|-------|-----------------------------------------------------------------------------------------|-----|

| 1.1   | Motivation and challenges                                                               | 1   |

| 1.2   | Research objectives                                                                     | 4   |

| 1.3   | Dissertation outline                                                                    | 5   |

| 1.4   | Reference                                                                               | 9   |

| CHAPT | ER 2                                                                                    | 12  |

| -     | act 250 kW Silicon Carbide MOSFET based Three-Level Traction Inverter fent Applications | •   |

| 2.1   | Abstract                                                                                | 12  |

| 2.2   | Introduction                                                                            | 13  |

| 2.3   | Instantaneous fundamental-cycle average loss calculation                                | 16  |

| 2.3   | 3.1 MOSFETs                                                                             | 17  |

| 2.3   | 3.2 Diodes                                                                              | 18  |

| 2.3   | 3.3 A case study of DC bus voltage                                                      | 21  |

| 2.3   | 3.4 A case study of switching frequency                                                 | 22  |

| 2.4   | DC-link capacitor selection                                                             | 22  |

| 2.5   | Thermal management and bussing structure                                                | 24  |

| 2.6   | Preliminary real-time simulation results                                                | 26  |

| 2.7   | Conclusion                                                                              | 26  |

| 2.8   | Reference                                                                               | 28  |

| CHAPT | ER 3                                                                                    | 29  |

| _     | and Validation of A 250 kW All Silicon Carbide High-Density Three-Leve                  | • • |

| 3.1   | Abstract                                                                                | 29  |

| 3.2   | Introduction                                                                            | 30  |

| 3.3   | Operating modes analysis and loss evaluation of a T-type phase leg                      | 33  |

| 3.3   | 3.1 The operating modes of a T-type phase leg                                           | 33  |

| 3.3   | 3.2 Semiconductor loss evaluation                                                       | 39  |

| 3.4   | Switching characterization of SiC modules in a T-type configuration                     | 42  |

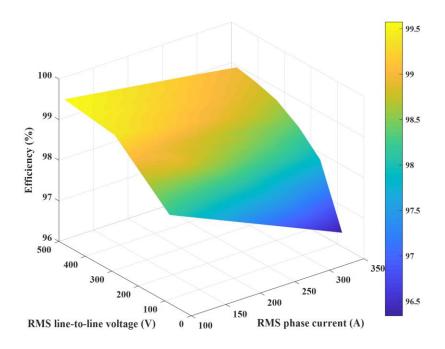

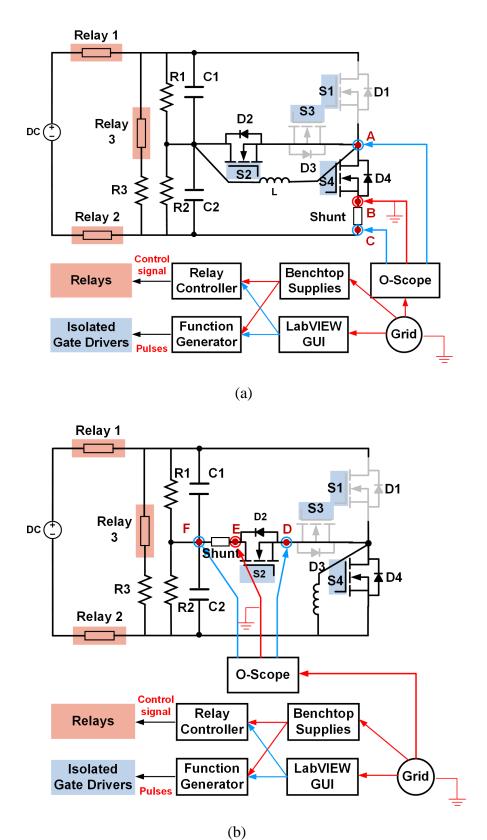

| 3.4   | .1 Clamped inductive load (CIL) test                                                    | 42  |

| 3.4   | .2 Switching waveform and switching energy analysis                                     | 47  |

| 3.5   | Full power prototype                                                                    | 51  |

| 3.5   | 5.1 SiC modules and gate drivers                                                        | 51  |

| 3.5.2      | DC-link capacitor                                                                                    | 52         |

|------------|------------------------------------------------------------------------------------------------------|------------|

| 3.5.3      | Laminated busbar                                                                                     | 53         |

| 3.6        | Experimental studies                                                                                 | 56         |

| 3.7        | Conclusion                                                                                           | 59         |

| 3.8        | Reference                                                                                            | 61         |

| СНАРТЕ     | R 4                                                                                                  | 64         |

|            | sign and Optimization for Voltage Overshoot Mitigation of A Silicon Carb<br>ee-Phase T-Type Inverter |            |

| 4.1        | Abstract                                                                                             | 64         |

| 4.2        | Introduction                                                                                         | 65         |

| 4.3        | Modeling and analysis of current commutation loops in a T-type inverter.                             | 68         |

| 4.3.1      |                                                                                                      |            |

| 4.3.2      | A practical circuit model for a T-type phase leg                                                     | 71         |

| 4.3.3      | Modeling and analysis of CCLs in a T-type phase leg                                                  | 71         |

| 4.4        | Multi-layer laminated busbar design process                                                          | 74         |

| 4.4.1      | The busbar design principles                                                                         | 74         |

| 4.4.2      | Busbar design process for a three-phase T-type inverter                                              | 76         |

| 4.4.3      | An enhanced bus bar design – a 3D design concept                                                     | 81         |

| 4.5        | Busbar parasitic inductance extraction                                                               | 83         |

| 4.5.1      | Simulation studies using finite element analysis                                                     | 83         |

| 4.5.2      | Stay inductance measurement using impedance analyzer                                                 | 86         |

| 4.6        | A hybrid bus bar structure with PCB snubber circuit using high-frequency 88                          | capacitors |

| 4.7        | Experimental studies                                                                                 | 89         |

| 4.8        | Conclusion                                                                                           | 95         |

| 4.9        | Reference                                                                                            |            |

| СНАРТЕ     | R 5                                                                                                  | 99         |

| Fixtures D | esign Considerations for Impedance Measurement                                                       | 99         |

| 5.1        | Abstract                                                                                             | 99         |

| 5.2        | Introduction                                                                                         | 99         |

| 5.3        | Measurement by using the commercial fixture adapter                                                  | 101        |

| 5.4        | Design approach for the custom fixture adapter boards                                                | 102        |

| 5.5        | Experimental validations                                                                             | 107        |

| 5.6        | Conclusion                                                                                           | 110        |

| 5.7        | Reference                                                                                            | 111        |

| CHAPTI   | ER 6                                            | 113 |

|----------|-------------------------------------------------|-----|

| Fixtures | Design Considerations for Impedance Measurement | 113 |

| 6.1      | Conclusion                                      | 113 |

| 6.2      | Future work                                     | 116 |

# LIST OF FIGURES

| Figure 2-1 Schematic of proposed traction inverter system                                                                                                                                                                                                                                 | 14               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Figure 2-2 Wolfspeed's all SiC high-performance half-bridge power module                                                                                                                                                                                                                  | 15               |

| Figure 2-3 The overall flow chart of loss model                                                                                                                                                                                                                                           | 17               |

| Figure 2-4 Simulation result of power losses when $Vdc = 700 \text{ V}$ , $pf = 0.8$ , $fs = 20 \text{ kHz}$ for (a in main switch bridge (b) Sa,4 in the middle switch bridge.                                                                                                           |                  |

| Figure 2-5 HIL simulation result when $Vdc = 700 \text{ V}$ , $pf = 0.8$ , $fs = 20 \text{ kHz}$ (a) line-to-line v (b) phase current.                                                                                                                                                    | _                |

| Figure 3-1 A schematic of the proposed T-type traction inverter                                                                                                                                                                                                                           | 32               |

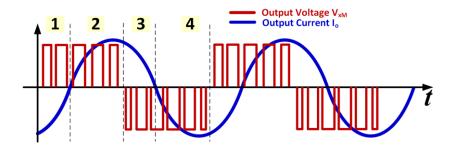

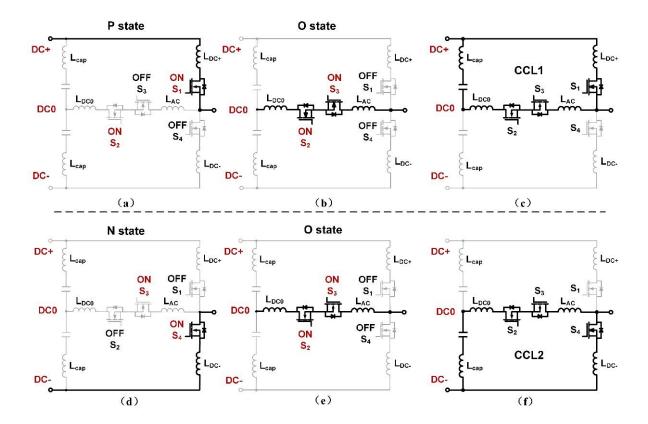

| Figure 3-2 An illustration of four operating intervals in a T-type phase leg                                                                                                                                                                                                              | 33               |

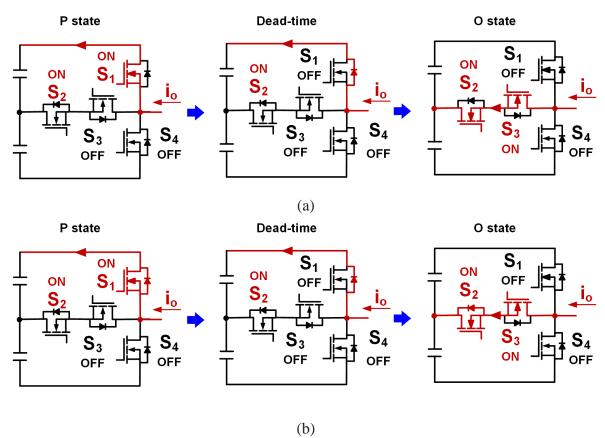

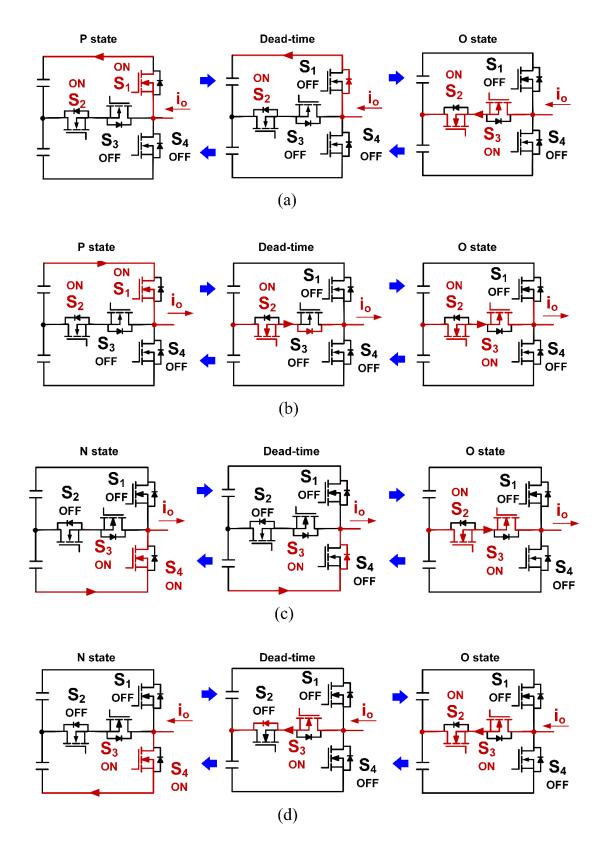

| Figure 3-3 The operating mode when $VxM > 0$ and $Io < 0$ with (a) low load current and (b load current. (S1 to S4 are the four switch positions in a T-type phase leg. The ON of associated with each switch position stands for the gate signal in that particular operating materials. | r OFF<br>node.). |

| Figure 3-4 An illustration for the switching transitions when (a) $VxM > 0$ and $Io < 0$ ; (b) $Volume{0}$ and $Io > 0$ ; (c) $VxM < 0$ and $Io > 0$ ; and (d) $VxM < 0$ and $Io < 0$                                                                                                     | /xM >            |

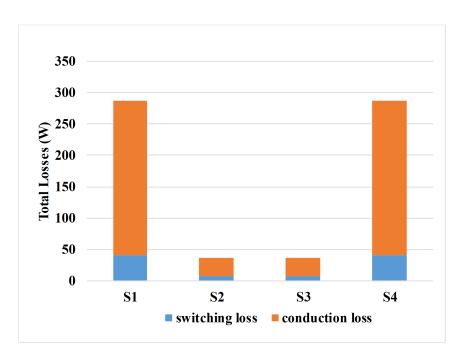

| Figure 3-5 The distribution of the average power losses with a 0.8 power factor load                                                                                                                                                                                                      | 41               |

| Figure 3-6. The efficiency map obtained using simulation-based loss model                                                                                                                                                                                                                 | 41               |

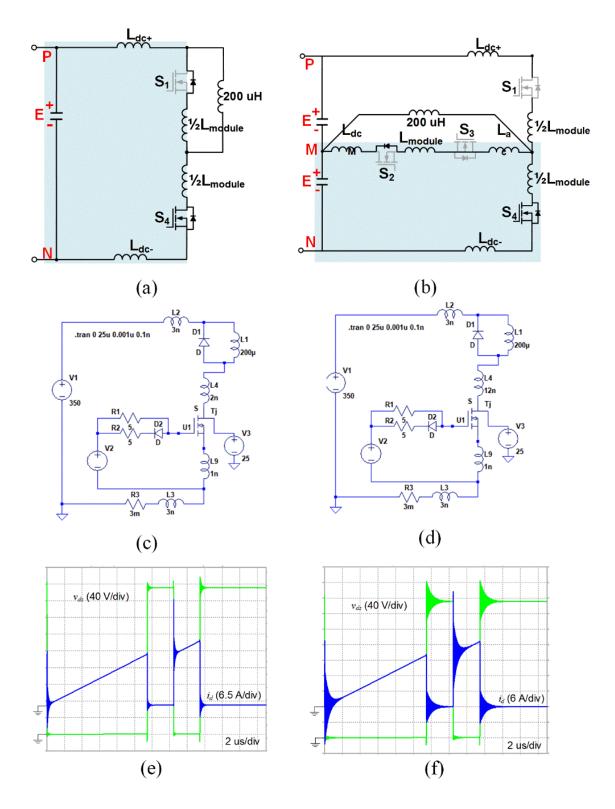

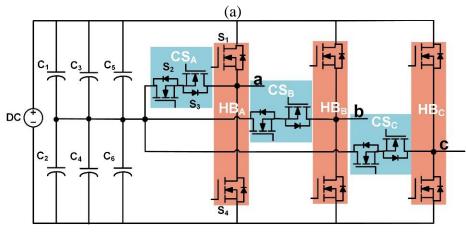

| Figure 3-7 Schematic of CIL test for (a) HB module and (b) CS module                                                                                                                                                                                                                      | 44               |

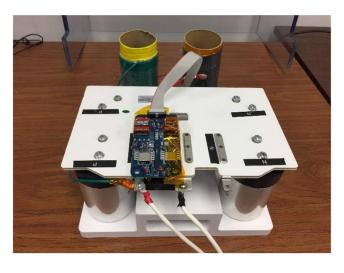

| Figure 3-8 The CIL test setup for a T-type phase leg                                                                                                                                                                                                                                      | 45               |

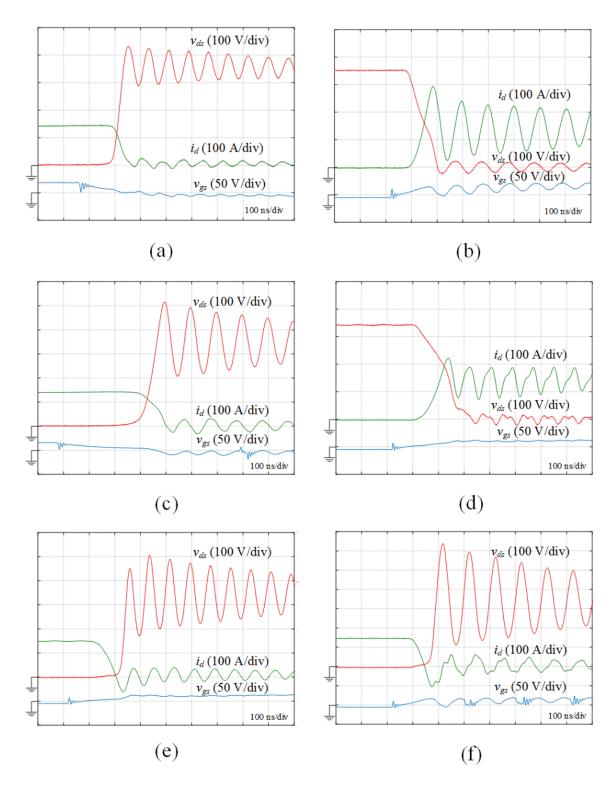

| Figure 3-9 Switching waveforms of the T-type modules at $Vdc = 700 \text{ V}$ , $Ids = 150 \text{ A}$ with R 5 $\Omega$ and $Rgoff = 2.5 \Omega$ : (a) turn-off of S4, (b) turn-on of S4, (c) turn-off of S2, (d) turn-on (e) turn-off of D4, and (f) turn-off of D2.                     | of S2,           |

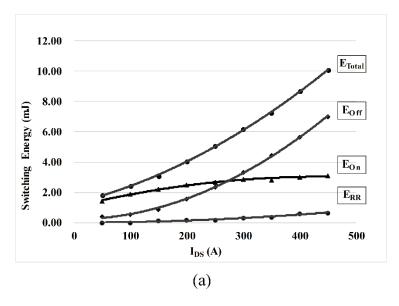

| Figure 3-10 Measured switching energy of T-type module at $Vdc = 700 \text{ V}$ , with Rgon = 5 Rgoff = 2.5 $\Omega$ : (a) S4, (b) S2                                                                                                                                                     |                  |

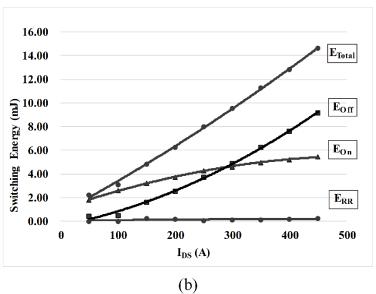

| Figure 3-11 Equivalent circuit of DPT for (a) an HB module and (b) a T-type phase leg, (d) are the corresponding simulation circuit, (e) and (f) are corresponding switching wave respectively.                                                                                           | forms,           |

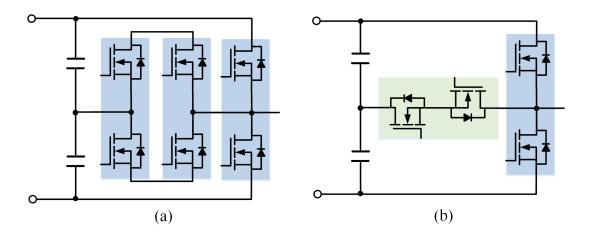

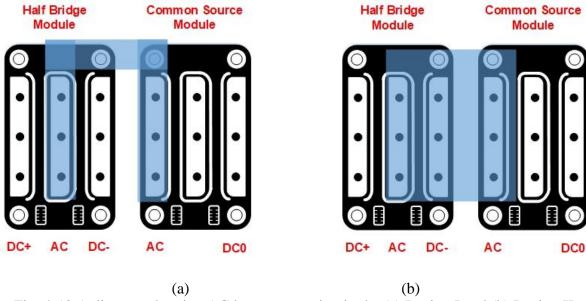

| Figure 3-12 T-type configuration built by (a) three HB modules (b) one HB module and o module.                                                                                                                                                                                            |                  |

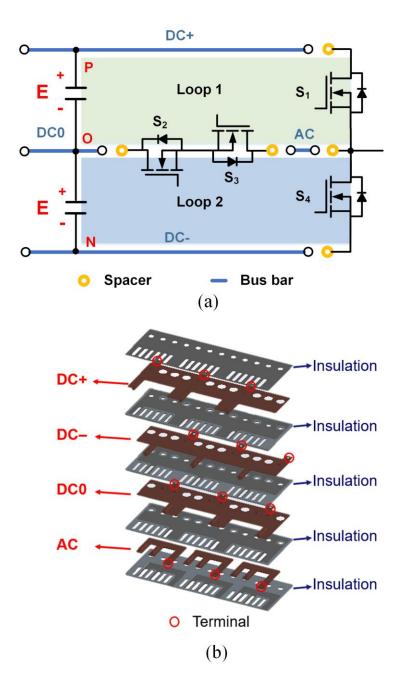

| Figure 3-13 T-type phase leg (a) circuit with busbar (b) exploded view                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3-14 A picture of the traction inverter prototype                                                                                                                                    |

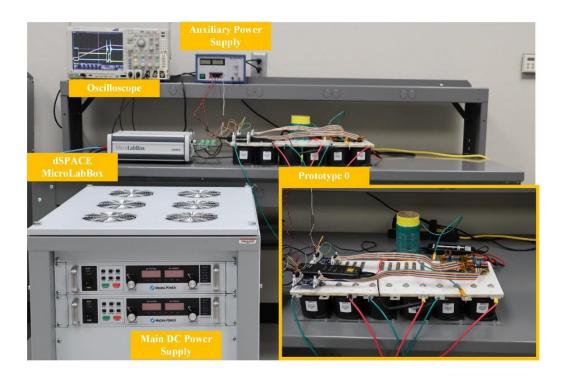

| Figure 3-15 The CIL test setup for actual prototype                                                                                                                                         |

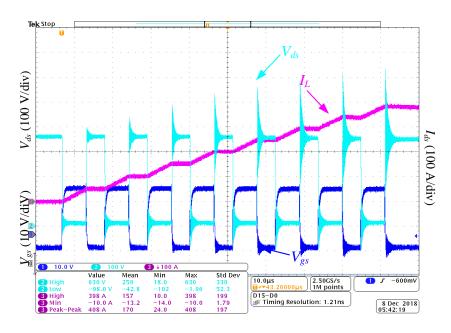

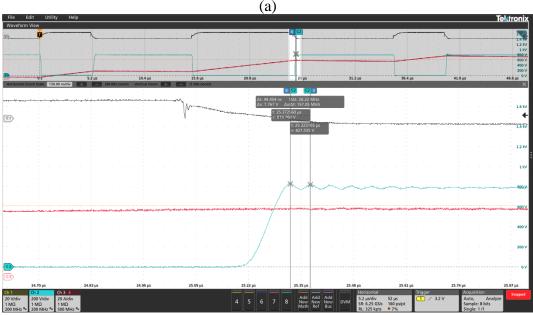

| Figure 3-16 A typical prototype-based CIL test result                                                                                                                                       |

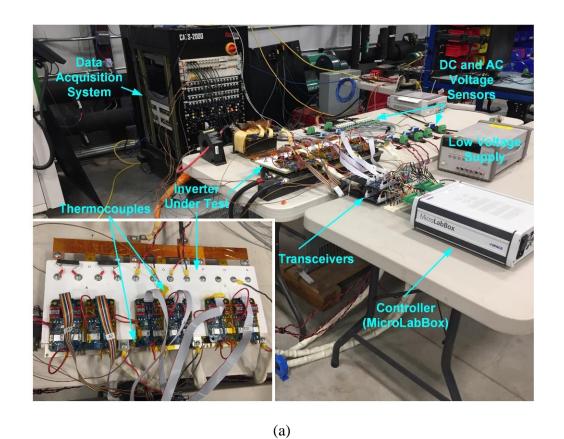

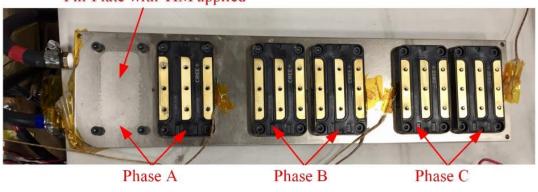

| Figure 3-17 (a) The test setup for high power testing and (b) a picture of the cold plate with one module removed                                                                           |

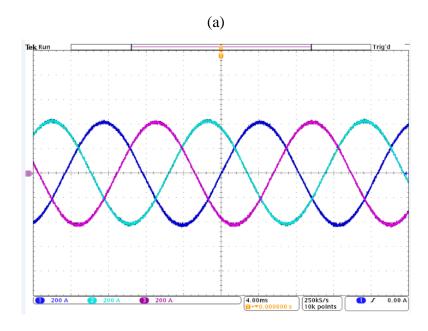

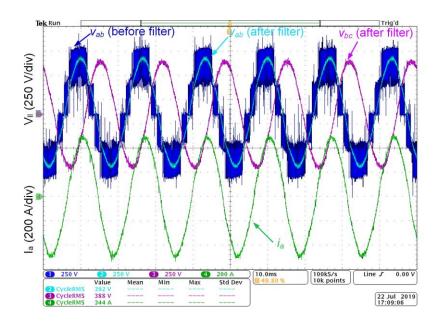

| Figure 3-18 Three-phase continuous test result.                                                                                                                                             |

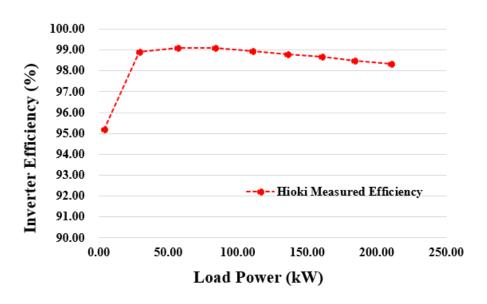

| Figure 3-19 Measured efficiency curve                                                                                                                                                       |

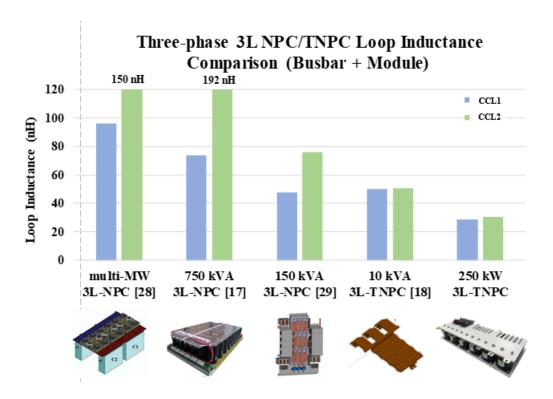

| Figure 4-1 Comparison of loop inductance for three-phase 3L inverters                                                                                                                       |

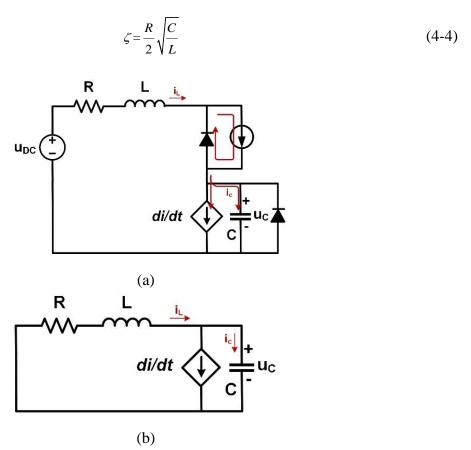

| Figure 4-2 Dynamic model of a single device turn-off transient: (a) an equivalent circuit and (b) a small signal simplified second-order RLC circuit.                                       |

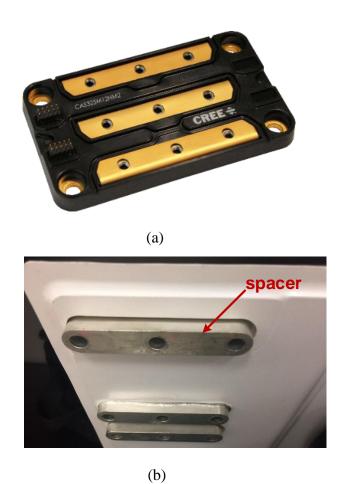

| Figure 4-3 Pictures of (a) the Wolfspeed SiC module [25] used in this work and (b) a laminated busbar with embedded spacers                                                                 |

| Figure 4-4 A detailed equivalent circuit model of a T-type phase leg                                                                                                                        |

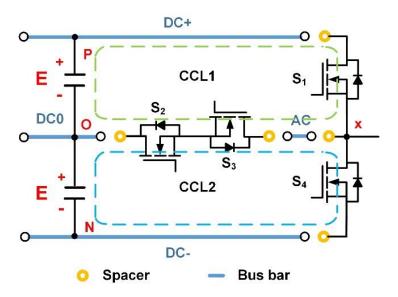

| Figure 4-5 CCLs in a T-type inverter. Note, black solid portion represents conduction paths in (a), (b), (d) and (e), and represents the CCLs in (c) and (f)                                |

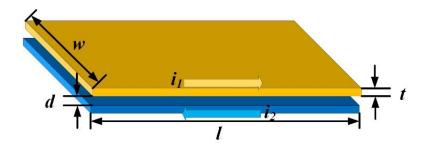

| Figure 4-6 Model of a generic two-layer laminated busbar                                                                                                                                    |

| Figure 4-7 (a) A possible placement of the major components in a T-type inverter and (b) it's corresponding schematic                                                                       |

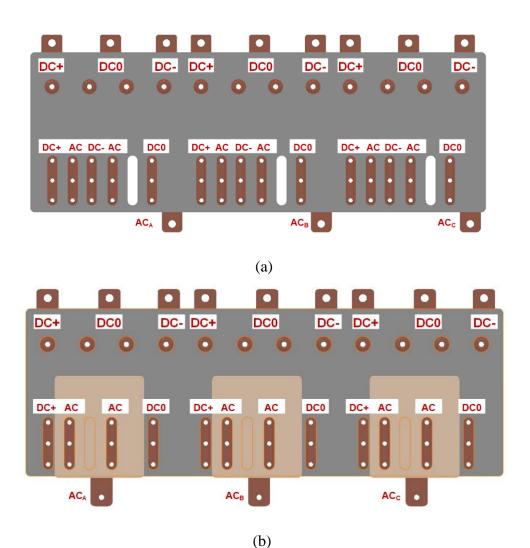

| Figure 4-8 The planar layout of the laminated busbar for a three-phase T-type inverter: (a) Design I and (b) Design II                                                                      |

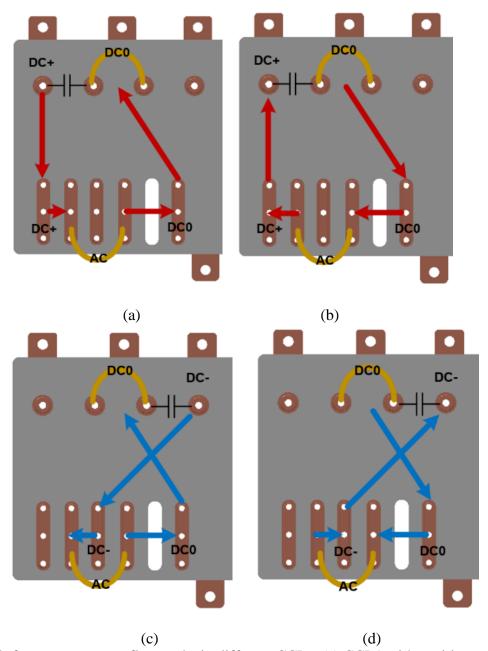

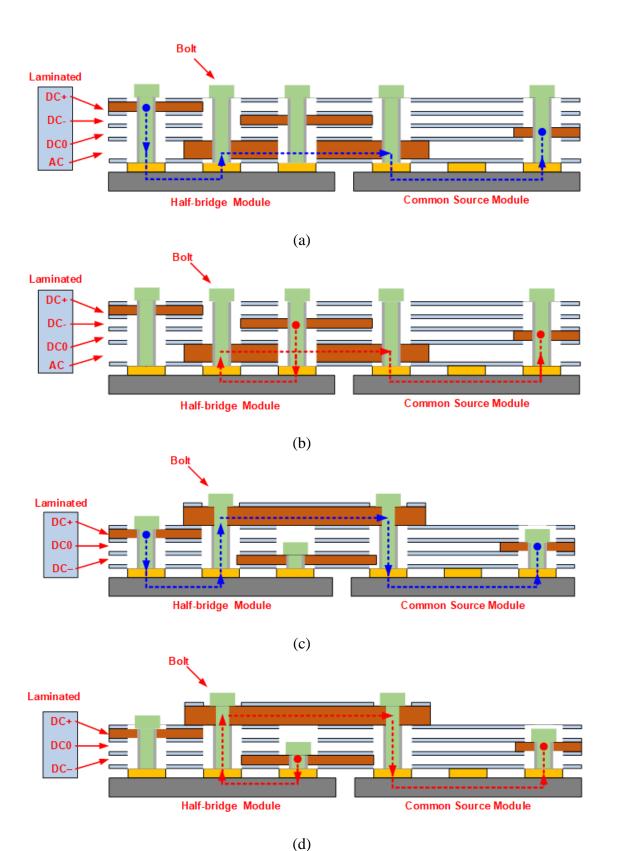

| Figure 4-9 High-frequency current flow paths in different CCLs: (a) CCL1 with positive current (b) CCL1 with negative current (c) CCL2 with negative current (d) CCL2 with positive current |

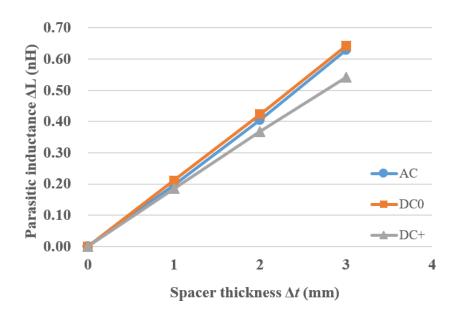

| Figure 4-10 Relationship between spacer thickness $\Delta t$ and the parasitic inductance $\Delta L$ 80                                                                                     |

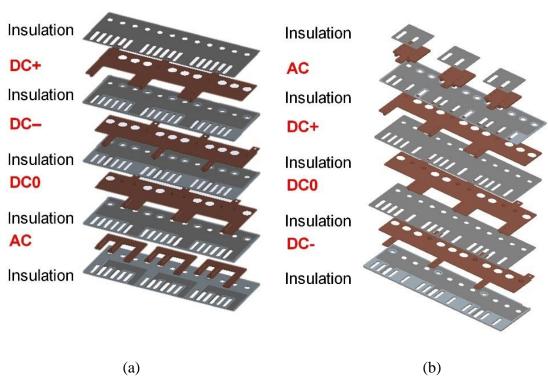

| Figure 4-11 Exploded view of two bus bar designs (a) Design I and (b) Design II                                                                                                             |

| Figure 4-12 A diagram showing AC layer connection in the (a) Design I and (b) Design II 82                                                                                                  |

| Figure 4-13 Cross section views of bus bars for (a) Design I CCL1, (b) Design I CCL2, (b) Design II CCL1 and (d) Design II CCL2.                                                            |

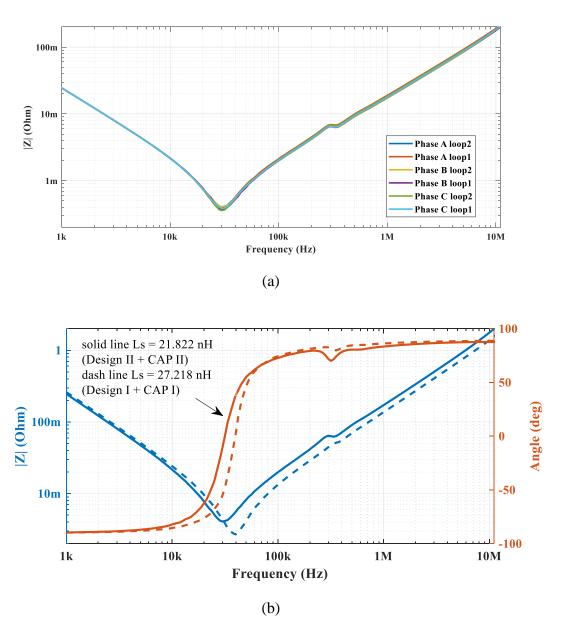

| Figure 4-14 Impedance analyzer extraction setup                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4-15 (a) measured loop impedance of busbar Design I with CAP I and (b) a loop impedance comparison between the busbar Design I with CAP I and busbar Design II with CAP II |

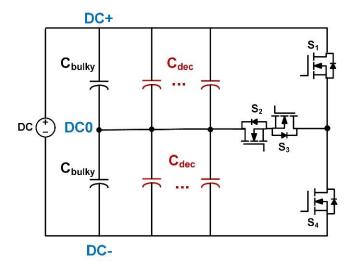

| Figure 4-16 Schematic of T-type topology with decoupling capacitors                                                                                                               |

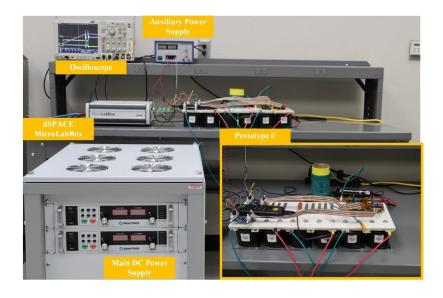

| Figure 4-17 A picture of the T-type inverter prototype                                                                                                                            |

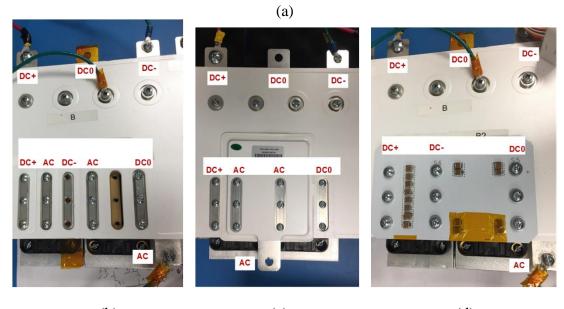

| Figure 4-18 (a) The CIL test setup and details of (b) busbar Design I, (c) busbar Design II and (d) busbar Design I with snubbers                                                 |

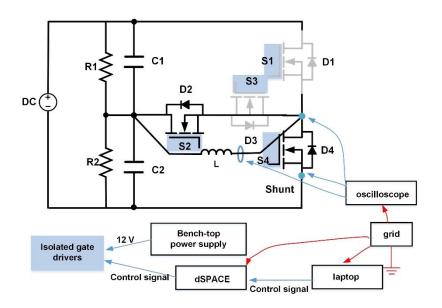

| Figure 4-19 Schematic of CIL test for HB module                                                                                                                                   |

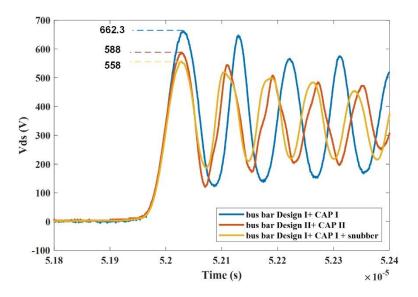

| Figure 4-20 Comparisons of drain to source voltage with 700V dc bus and 450A load current 93                                                                                      |

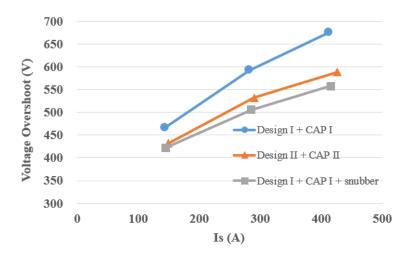

| Figure 4-21 Comparison of voltage overshoot with various load currents                                                                                                            |

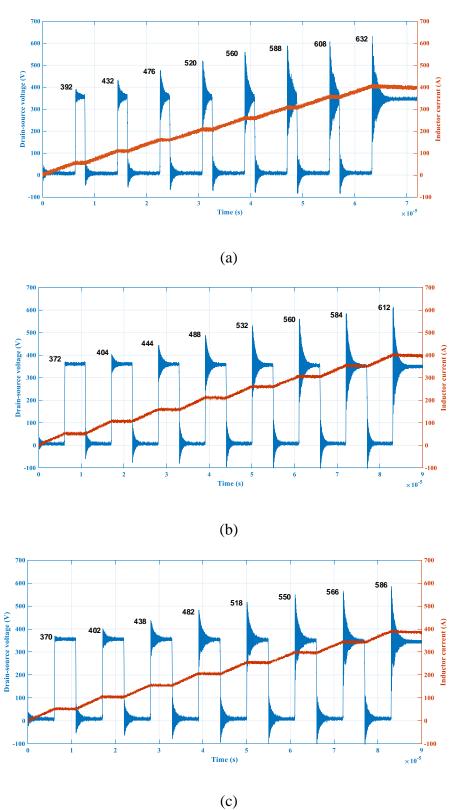

| Figure 4-22 The drain to source voltage and load current waveforms during the MPTs for (a) busbar Design I + CAP I (b) busbar Design II + CAP II (c) busbar Design II + CAP II    |

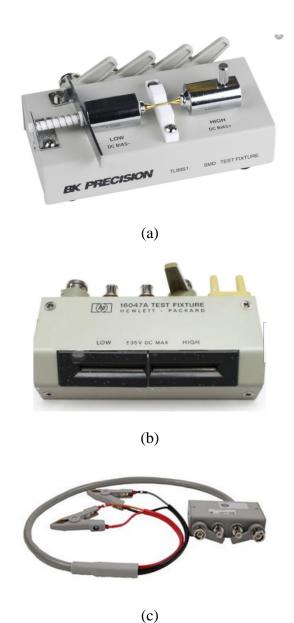

| Figure 5-1 Commercial fixture adapter of impedance analyzer (a) for SMD (b) for leaded passive device (c) with clip lead                                                          |

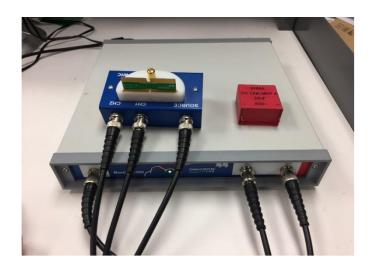

| Figure 5-2 Setup for commercial fixture adapters with impedance analyzers (a) B-WIC with Bode 100 (b) 16047E with E4990A                                                          |

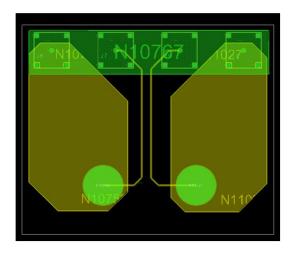

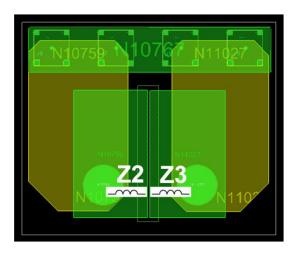

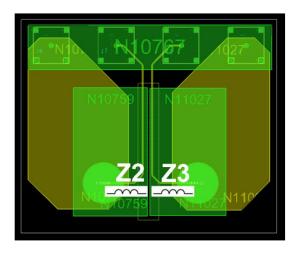

| Figure 5-3 PCB layout for three customized fixture designs (a) Method 1 (b) Method 2 (c) Method 3                                                                                 |

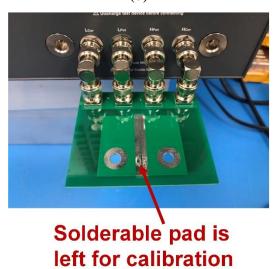

| Figure 5-4 Test setups for (a) Method 1with an external copper bar connected for the short calibration, (b) Method 2 or 3 and (c) zoomed-in view for Method 3                     |

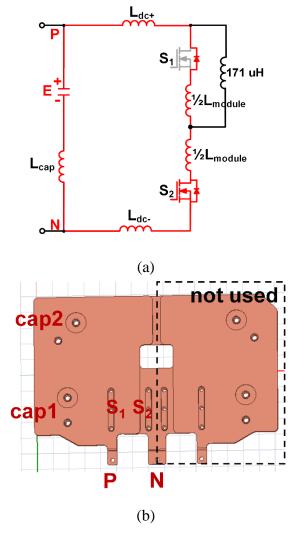

| Figure 5-5 HB inverter (a) schematic of its DPT (b) its bus bar layout (c) setup for its impedance measurement (bus bar + dc-link capacitors)                                     |

| Figure 5-6 Half-bridge inverter DPT (a) setup (b) turn-off waveforms                                                                                                              |

# LIST OF TABLES

| Table 1-1 Comparison of numbers of different voltage rating SiC devices on a 13.8 kV ca<br>H-bridge inverter [1.15]. |     |

|----------------------------------------------------------------------------------------------------------------------|-----|

| Table 2-1 Power loss simulation result on 700, 800, 900 V dc bus when $fs = 20 \text{ kHz.}$                         | 19  |

| Table 2-2 Power loss simulation result on 700, 800, 900 V dc bus when $fs = 40 \text{ kHz.} \dots$                   | 21  |

| Table 3-1 Switching states.                                                                                          | 34  |

| Table 3-2 Device conduction intervals.                                                                               | 34  |

| Table 3-3 Device power loss distributions                                                                            | 38  |

| Table 3-4 Device switching loss distributions.                                                                       | 38  |

| Table 3-5 Stray inductance of the bus bar extracted using Q3D.                                                       | 55  |

| Table 4-1 Switching states.                                                                                          | 71  |

| Table 4-2 FEA simulation results for bus bar Design I.                                                               | 84  |

| Table 4-3 FEA simulation results for bus bar Design II                                                               | 84  |

| Table 4-4 Measured total inductance of busbar Design I with CAP I.                                                   | 84  |

| Table 4-5 Inverter system specifications                                                                             | 89  |

| Table 5-1 Measurement result by different methods                                                                    | 102 |

#### LIST OF PUBLICATIONS

1. Z. Wang et al., "A Compact 250 kW Silicon Carbide MOSFET based Three-Level Traction Inverter for Heavy Equipment Applications," 2018 IEEE Transportation Electrification Conference and Expo (ITEC), Long Beach, CA, 2018, pp. 1129-1134.

Chapter 2 is made up of this paper

2. Z. Wang, Y. Wu, M. H. Mahmud, Z. Zhao, Y. Zhao and H. A. Mantooth, "Design and Validation of A 250-kW All-Silicon Carbide High-Density Three-Level T-Type Inverter," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 8, no. 1, pp. 578-588, March 2020.

Chapter 3 is made up of this paper

- 3. Z. Wang, Y. Wu, M. Mahmud, Z. Yuan, Y. Zhao and H. A. Mantooth, "Busbar Design and Optimization for Voltage Overshoot Mitigation of A Silicon Carbide High-Power Three-Phase T-Type Inverter," in IEEE Transactions on Power Electronics. *Chapter 4 is made up of this paper*

- 4. Z. Wang et al., "Fixtures Design Considerations for Impedance Measurement." 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), Phenix, AZ, 2021. *Chapter 5 is made up of this paper*

#### **CHAPTER 1**

#### INTRODUCTION

## 1.1 Motivation and challenges

Transportation electrification has been a trend for many years. The electrified vehicle offers great benefits compared to the conventional internal combustion engine (ICE) including less carbon-dioxide emission, less dependents on fossil energies, less operation costs, less maintenance, higher safety rating and better efficiency. The recent breakthrough battery technologies further making the high-performance and heavy-duty electrified vehicles possible.

Nevertheless, the electric traction drive systems (ETDS) could be a bottleneck. With the limited vehicle space, the power electronics motor drive should have high power density to deliver sufficient energy at limited time. Besides, ETDS are required to maintain high efficiency in various operation conditions to keep long mileage.

Accordingly, the office of efficiency and renewable energy, department of energy (DOE) has proposed US Drive Electrical and Electronics Technical Team (EETT) Roadmap [1], which proposed design targets of ETDS in 2025, as seen table 1-1. A power density over 33kW/L and 88% volume reduction is required.

It is seen a huge gap between the state-of-art and the 2025 target. To fill the gap, tremendous works have been made in several aspects. For example, the topology innovation and selection are one of the keys to improve motor drive performance. It is seen that the conventional three-phase two-level topology enjoys simple structure, high reliability, and low conduction loss [2]. However, its insufficient output-THD performance [3], high EMI noise introduced by high dv/dt [4], and extraneous switching loss [5] could limit its performance for high power motor drive.

Table 1-1 DOE EETT Roadmap for Power Electronics Converters in Year of 2020 and 2025 [1]

| Technical Targets of Power-electronics Equipment in Electrified Vehicles |                |            |           |  |  |  |

|--------------------------------------------------------------------------|----------------|------------|-----------|--|--|--|

|                                                                          | Years<br>Items | 2025       |           |  |  |  |

| ETDS                                                                     | Cost           | 4.7 \$/kW  | 3.3 \$/kW |  |  |  |

| 2105                                                                     | Power Density  | 5.7 kW/L   | 50 kW/L   |  |  |  |

|                                                                          | Cost           | 50 \$/kW   | 35\$/kW   |  |  |  |

| On-board Charger                                                         | Specific Power | 3 kW/kg    | 4 kW/kg   |  |  |  |

| On-board Charger                                                         | Power Density  | 3.5 kW/L   | 4.6 kW/L  |  |  |  |

|                                                                          | Efficiency     | 97.0%      | 98.0%     |  |  |  |

| D 1                                                                      | Cost           | <50 \$/kW  | 30 \$/kW  |  |  |  |

| Buck DC/DC Converter                                                     | Specific Power | >1.2 kW/kg | 4 kW/kg   |  |  |  |

| (325V to 14V)                                                            | Power Density  | >3.0 kW/L  | 4.6 kW/L  |  |  |  |

|                                                                          | Efficiency     | > 94.0%    | 98.0%     |  |  |  |

Recently, the three-level neutral-point clamped converter (3L-NPC) and three-level active neutral-point clamped converter (3L-ANPC) gains more and more attentions. The University of Tennessee and General Electric have demonstrated its efficiency of 99.0% through designing a 1-MW 3L-ANPC motor-drive prototypes [6,7]. Such a topology can greatly reduce switching loss, dv/dt noise and limit THD. Because each device only needs to withstand half DC-link voltage, higher DC-link voltage can be utilized for given device ratings. Or the lower voltage-rating semiconductors can be used for the given DC-link voltages. However, 3L-NPC and 3L-ANPC

increase the counts of power semiconductor per phase, causing higher conductional loss and more complicated hardware design and optimization.

Three-level T-type neutral-point clamped topology (3L-TNPC) also has great potential in motor drive applications [8]. Compared to the two-level converter, 3L-TNPC has advantages of common three-level topologies, such as low dv/dt, low switching loss and lower output THD [9]. When compared it to 3L-NPC and 3L-ANPC, the 3L-TNPC has less switch counts and conduction loss [10]. However, the 3L-TNPC's external-leg has higher voltage stress compared to the 3L-NPC and 3L-ANPC. And the conduction loss of 3L-TNPC is lower than 3L-NPC but it is higher than two level converters [11]. Working with Advanced Research Projects Agency–Energy (Apar-E), and the Center for Power Optimization of Electro-thermal Systems (POETS), the University of Arkansas has built three prototypes of 3L-TNPC with power density over 25kW/L, and peak efficiency greater than 99.0% [12,13].

Besides the two-level converter and three-level converter, researchers also found a place for nine-level converters in high-performance motor drive. The recent research in Dr. Pilawa's group from the University of California Berkeley and the University of Illinois at Urbana-Champaign Urban demonstrates that nine-level switch-cap converters deliver power up to 200kVA with high efficiency high power density [14].

Great efforts are made in applying advanced semiconductors in motor drive. The wide-bandgap (WBG) based devices, such as Silicon-carbide (SiC) Metal—oxide—semiconductor Field-effect Transistor (MOSFET) [15], SiC junction-gate field-effect transistor (JFET) [16], SiC diode [17], Gallium Nitride (GaN) High-electron-mobility Transistors (HEMT) [18] and GaN field-effect transistor (FET) [19].

Compared to the conventional Si material, the WBG materials have higher break-down E-field, higher drift velocity, better thermal conductivity, and can handle higher carrier concentration. As a result, the WBG-based power semiconductors offer better figure-of-merit. For example, at the given bare-die dimension, the SiC-MOSFET and GaN HEMT offers lower on-state resistance and lower switching loss compared to the Si-IGBT and Si-MOSFET [20].

As a result, applying such devices into motor drive can bring benefits. For example, the [21] replaces four Si-Diodes by SiC-diodes in a 3L-NPC converter, reducing total loss by about 13%. Additionally, [22] combines SiC-MOSFET and Si-IGBT as a hybrid switch unit. It allows Si-IGBT carries majority conduction loss and SiC-MOSFET offers lower switching loss. The 3L-TNPC converter based on hybrid-switch concept can offer efficiency over 99.0% at switching frequency of 20kHz. Moreover, [23] utilizes full-SiC-MOSFET module in a 450-kVA converter. The full-SiC-MOSFET enables over tripled switching frequency and can keep peak efficiency over 99.47%.

## 1.2 Research objectives

Though tremendous efforts are made in improving motor drive performance, it is still seen a huge gap between the state-of-art and the 2025 target. To fill the gap, research should be made in the following aspects.

- 1. High-accuracy modeling system to guide motor drive design, such as semiconductor loss modeling and estimation, DC-link ripple modeling, and hardware parasitic modeling.

- 2. Understanding the system-level trade-off of motor drive systems, including

- The trade-off between different motor-drive topologies,

- The trade-off between switching loss, conduction loss and output THD,

- 3. Multi-dimensional integration of power electronics system to achieve

- Optimized parasitic control,

- Optimized thermal dissipation,

- Compact converter-level packaging with high power density.

- 4. Fully utilize the advantages of wide bandgap devices, such as Silicon-carbide metal—oxide—semiconductor field-effect transistor (MOSFET), including

- Optimized SiC-MOSFET configuration with optimized conduction loss and switching loss,

- Minimized stray inductance of SiC-MOSFET's commutation loop for overshoot mitigation,

- Proper switching speed with sufficient switching loss reduction,

- Well-controlled junction temperature

#### 1.3 Dissertation outline

Chapter 2 is at the inverter's paper-design stage. After determining the topology and fully understanding its advantages, this chapter discusses the decision of specifications. First of all, a real-time simulation model is built, which can use the look- up table to recall the information from the datasheet, and by judging the operation mode of the switch device, we can see the conduction and switching loss distribution in real time. At the same time, the dc-bus voltage and switching frequency are easy to be adjusted, so through case studies, the best dc-bus and switching frequency

for our topology application scenarios are determined. At the same time, the hardware selection of dc-link capacitor is also preliminarily determined considering the requirements of capacitance and RMS current. Finally, through HIL simulation, the inverter's modulation is verified. This chapter paved the way for subsequent hardware design and experiments in the following chapters.

Chapter 3 is a summary of the inverter hardware design and high-power test results. The beginning is an in-depth analysis of the operation mode of the SiC MOSFET based T-type inverter. There is also a summary of power loss under various voltage and current directions. The next step is to use the real-time simulation mentioned in Chapter 2 to analyze the loss distribution, and find the module with higher power loss. This is very helpful for the subsequent cold plate design. At the same time, by breaking down the loss, we can find the main source of total loss is the conduction loss. These simulation results can help to initially determine whether the efficiency target can be achieved theoretically. Next, the clamped inductor test (CIL) is introduced. Through the switching loss results obtained from the CIL, we can optimize the accuracy of the loss model. This chapter also explains the phenomenon that the oscillation of T-type inverter is larger than that of two-level inverter. The following of this chapter explains the selection of module, gate driver, and dc-link cap, and also briefly introduces the design of the laminated bus bar. Finally, this chapter shows the results of the full-power test. Through the analysis of the power analyzer measurement, the target efficiency of 98.5% is achieved.

Chapter 4 focuses on the design of the laminated bus bar of this inverter. First, it theoretically explains why the laminated bus bar with low stray inductance has benefit to the whole inverter system, and then introduces the composition of the specific T-type inverter bus bar. Then the design difficulty considering the specific module layout is pointed out. Then this chapter summarizes and analyzes all the current communication loops (CCLs) of the inverter and obtained

the guidance of optimizing bus bar design. Next, the busbar design principles in the traditional method are elaborated, and self-inductance and mutual inductance are introduced at the same time. The final bus bar design of this inverter is introduced in detail. In the design process, we found that reducing self-inductance and increasing mutual inductance are two effective ways for reducing the total stray inductance. Based on this analysis, this chapter proposes a new bus bar 3-dimentional (3D) design concept. The bus bar layer buried under others at certain potentials can reduce self-inductance and increase mutual inductance. This chapter proves that the new bus bar design concept can effectively reduce total stray inductance through Q3D simulation and direct measurement with impedance analyzer. In addition, the article also proposed a hybrid bus bar structure with PCB snubber circuit using high-frequency capacitors. Finally, it is proved through experiments that the new 3D concept bus bar with low ESL dc-link capacitor can effectively reduce the Vds overshoot. Additionally, the hybrid bus bar structure with PCB snubber circuit can also suppress Vds overshoot.

Chapter 5 introduces the issue of how the fixture should be designed when the impedance analyzer is used to measure non-standard components. Through the previous chapters, we have learned that the stray inductance in the entire CCL has an impact on the Vds overshoot of the switch device. So, in the components' design and selection stages, it is particularly important to accurately know the internal inductance of each component. At present, when measuring with an impedance analyzer, high-precision fixtures are mainly designed for SMD and lead terminal components. In the design of high-power converters, we need to know some non-standard components' inductance, such as bulk dc-link capacitors and customized bus bar, which requires us to design a fixture to connect these devices with the impedance analyzer. This chapter discusses the design of this fixture to improve the accuracy of the measurement. First of all, as a comparison,

a leaded film capacitor is selected as the standard reference, and it is measured by two commercial fixtures and impedance analyzers. Then three PCB customized fixtures were designed, and the standard film capacitor is measured again. Through comparative experiments, we found one of the customized designs is closest to the commercial fixture measurement results, then the design guidance is summarized. In the end, experiments are conducted to verify this optimal design. The CCL inductance of a 2-L inverter is measured through an impedance analyzer and fixture. The results proved that the inductance derived from the Q3D simulation results and double-pulse-test (DPT) Vds waveform oscillation frequency are highly consistent with our fixture measurement results, thus proving the accuracy of the customized fixture measurement.

#### 1.4 Reference

- [1] Drive, U. S. "Electrical and electronics technical team roadmap." Partnership Plan, Roadmaps, and Other Documents (2013).

- [2] Y. Chen, et al., "A Model-Based Multi-Objective Optimization for High Efficiency and High Power Density Motor Drive Inverters for Aircraft Applications," *NAECON 2018 IEEE National Aerospace and Electronics Conference*, 2018, pp. 36-42, doi: 10.1109/NAECON.2018.8556757.

- [3] A. Choudhury, P. Pillay and S. S. Williamson, "Comparative Analysis Between Two-Level and Three-Level DC/AC Electric Vehicle Traction Inverters Using a Novel DC-Link Voltage Balancing Algorithm," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 2, no. 3, pp. 529-540, Sept. 2014, doi: 10.1109/JESTPE.2014.2310140.

- [4] W. Perdikakis, M. J. Scott, K. J. Yost, C. Kitzmiller, B. Hall and K. A. Sheets, "Comparison of Si and SiC EMI and Efficiency in a Two-Level Aerospace Motor Drive Application," in *IEEE Transactions on Transportation Electrification*, vol. 6, no. 4, pp. 1401-1411, Dec. 2020, doi: 10.1109/TTE.2020.3010499.

- [5] Y. Yan, et al., "An Analytical SiC MOSFET Switching Behavior Model Considering Parasitic Inductance and Temperature Effect," 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), 2020, pp. 2829-2833, doi: 10.1109/APEC39645.2020.9124548.

- [6] D. Zhang, J. He and D. Pan, "A Megawatt-Scale Medium-Voltage High-Efficiency High Power Density "SiC+Si" Hybrid Three-Level ANPC Inverter for Aircraft Hybrid-Electric Propulsion Systems," in *IEEE Transactions on Industry Applications*, vol. 55, no. 6, pp. 5971-5980, Nov.-Dec. 2019, doi: 10.1109/TIA.2019.2933513.

- [7] H. Gui et al., "Design of Low Inductance Busbar for 500 kVA Three-Level ANPC Converter," 2019 IEEE Energy Conversion Congress and Exposition (ECCE), 2019, pp. 7130-7137, doi: 10.1109/ECCE.2019.8912605.

- [8] Z. Yuan et al., "Design and Evaluation of A 150 kVA SiC MOSFET Based Three Level TNPC Phase-leg PEBB for Aircraft Motor Driving Application," 2019 IEEE Energy Conversion Congress and Exposition (ECCE), 2019, pp. 6569-6574, doi: 10.1109/ECCE.2019.8913071.

- [9] H. Peng et al., "Improved space vector modulation for neutral-point balancing control in hybrid-switch-based T-type neutral-point-clamped inverters with loss and common-mode voltage reduction," in *CPSS Transactions on Power Electronics and Applications*, vol. 4, no. 4, pp. 328-338, Dec. 2019, doi: 10.24295/CPSSTPEA.2019.00031.

- [10] Mustafeez-ul-Hassan, et al., "Model Based Optimization of Propulsion Inverter for More-Electric Aircraft Applications Using Double Fourier Integral Analysis," 2020 AIAA/IEEE Electric Aircraft Technologies Symposium (EATS), 2020, pp. 1-7.

- [11] Z. Yuan et al., "Design and Evaluation of Laminated Busbar for Three-Level T-Type NPC Power Electronics Building Block With Enhanced Dynamic Current Sharing," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 8, no. 1, pp. 395-406, March 2020, doi: 10.1109/JESTPE.2019.2947488.

- [12] Z. Wang, Y. Wu, M. H. Mahmud, Z. Yuan, Y. Zhao and H. A. Mantooth, "Busbar Design and Optimization for Voltage Overshoot Mitigation of a Silicon Carbide High-Power Three-Phase T-Type Inverter," in *IEEE Transactions on Power Electronics*, vol. 36, no. 1, pp. 204-214, Jan. 2021, doi: 10.1109/TPEL.2020.2998465.

- [13] A. Deshpande, et al., "Design of a High-Efficiency, High Specific-Power Three-Level T-Type Power Electronics Building Block for Aircraft Electric-Propulsion Drives," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 8, no. 1, pp. 407-416, March 2020, doi: 10.1109/JESTPE.2019.2952367.

- T. Modeer, C. B. Barth, N. Pallo, W. H. Chung, T. Foulkes and R. C. N. Pilawa-Podgurski, "Design of a GaN-based, 9-level flying capacitor multilevel inverter with low inductance layout," *2017 IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2017, pp. 2582-2589, doi: 10.1109/APEC.2017.7931062.

- [15] M. Imaizumi and N. Miura, "Characteristics of 600, 1200, and 3300 V Planar SiC-MOSFETs for Energy Conversion Applications," in *IEEE Transactions on Electron Devices*, vol. 62, no. 2, pp. 390-395, Feb. 2015, doi: 10.1109/TED.2014.2358581.

- [16] T. Friedli, S. D. Round, D. Hassler and J. W. Kolar, "Design and Performance of a 200-kHz All-SiC JFET Current DC-Link Back-to-Back Converter," in *IEEE Transactions on Industry Applications*, vol. 45, no. 5, pp. 1868-1878, Sept.-oct. 2009, doi: 10.1109/TIA.2009.2027538.

- [17] R. Singh, J. A. Cooper, M. R. Melloch, T. P. Chow and J. W. Palmour, "SiC power Schottky and PiN diodes," in *IEEE Transactions on Electron Devices*, vol. 49, no. 4, pp. 665-672, April 2002, doi: 10.1109/16.992877.

- [18] U. K. Mishra, P. Parikh and Yi-Feng Wu, "AlGaN/GaN HEMTs-an overview of device operation and applications," in *Proceedings of the IEEE*, vol. 90, no. 6, pp. 1022-1031, June 2002, doi: 10.1109/JPROC.2002.1021567.

- [19] N. Ikeda et al., "GaN Power Transistors on Si Substrates for Switching Applications," in *Proceedings of the IEEE*, vol. 98, no. 7, pp. 1151-1161, July 2010, doi: 10.1109/JPROC.2009.2034397.

- [20] S. Hazra et al., "High Switching Performance of 1700-V, 50-A SiC Power MOSFET Over Si IGBT/BiMOSFET for Advanced Power Conversion Applications," in *IEEE Transactions on Power Electronics*, vol. 31, no. 7, pp. 4742-4754, July 2016, doi: 10.1109/TPEL.2015.2432012.

- [21] Schweizer, M., T. Friedli, and J. W. Kolar. "Comparative evaluation of advanced 3-level inverter/converter topologies against 2-level systems." Swiss Federal Institute of

- Technology, Zurich, Power Electronic Systems Laboratory, European Center for Power Electronics, Nuremberg, DE (2010).

- [22] H. Peng, et al., "Comprehensive Analysis of Three-phase Three-level T-type Neutral-Point-Clamped Inverter with Hybrid Switch Combination," 2019 IEEE 10th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), 2019, pp. 816-821, doi: 10.1109/PEDG.2019.8807618.

- [23] Z.Yuan, et al., " A Three-phase 450 kVA SiC-MOSFET Based Inverter With High Efficiency and High Power Density By Using 3L-TNPC," 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), 2021

#### **CHAPTER 2**

# A COMPACT 250 KW SILICON CARBIDE MOSFET BASED THREE-LEVEL TRACTION INVERTER FOR HEAVY EQUIPMENT APPLICATIONS

© 2018 IEEE. Reprinted, with permission, from Z. Wang et al., "A Compact 250 kW Silicon Carbide MOSFET based Three-Level Traction Inverter for Heavy Equipment Applications," 2018 IEEE Transportation Electrification Conference and Expo (ITEC), Long Beach, CA, 2018, pp. 1129-1134.

### 2.1 Abstract

A sustained effort is required to realize the aggressive targets of electrification of heavy equipment, e.g., the heavy-duty off-road vehicles, due to numerous emerging challenges, which are different from those in the automotive industry. Heavy equipment manufacturers are increasingly investing in new generation of power electronics technology to fulfill the high performance and reliability targets under harsh environments while reducing fuel consumption and staying cost competitive. In this work, a holistic power electronic circuits design is proposed to achieve 4× power density at 98% peak efficiency for a compact 250 kW three-phase three-level (3-L) T-type traction inverter. The proposed T-type inverter is designed using the best-in-class silicon carbide (SiC) power modules. Most importantly a multi-objective optimization approach to trade the volumetric power density (kW/l) against SiC device type (650, 900 and 1200 V), dc bus voltage, switching frequency, the size of the passive components. T-type inverter system design guidance is given in this work, including loss calculation, dc-link capacitor selection, thermal management solution, and bussing structure. In addition, the hardware-in-the-loop

simulation study is performed to validate the performance of the control system designed for the traction inverter.

#### 2.2 Introduction

The electrified drivetrain of the heavy equipment demands outstanding efficiency at low costs. Recently, significant amount of research effort has gone into the development of highly efficient and compact traction inverters [1], [2], since the improved efficiency and power density coupled with lower losses in the motor and lighter weight all combine to produce more powerful, more energy efficient heavy equipment that is expected to reduce more than 25% operating costs [3]. To reduce the size and cost of passive components, the switching frequency often needs to be increased to medium range, e.g., 10-25 kHz. With higher switching frequency, conventional 2level silicon (Si) based power converters will have significantly increased losses that require bulky cooling systems. Potential loss reduction can be achieved through either topology innovation or the adoption of wide bandgap (WBG) power semiconductor devices. It has been proven that multilevel topologies, e.g., the 3-level (3-L) neutral point clamped converter and T-type converter, have better efficiency if the switching frequency is higher than 10 kHz [4]. The rapid development of a new generation WBG technologies opens up the possibility of high efficiency and highperformance operation at higher switching frequencies. In this work, a system-level multiobjective optimization is proposed to realize a compact 250 kW T-type that will fully exploit the benefits of both the SiC devices and the 3-level topology.

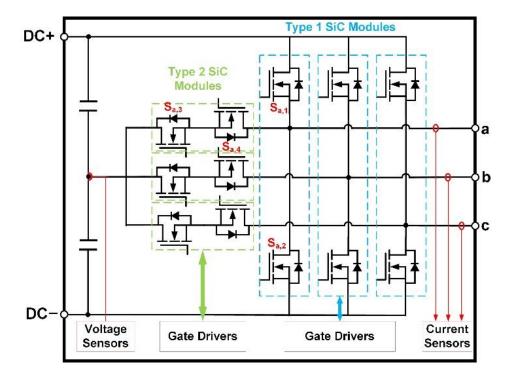

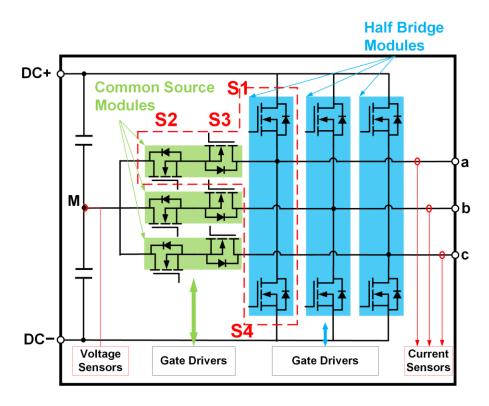

The main circuit topology is built upon the T-type inverter [5], which combines the positive aspects of two-level converters, such as low conduction losses and simple operation principles with the advantages of a three-level converter such as low switching losses and superior output voltage quality. The schematic of the proposed traction inverter system is shown in Fig. 2.1, which

includes the dc-link capacitors, gate drivers, various voltage and current sensors, and the main T-type inverter realized by two sets of SiC MOSFET half-bridge modules at different voltage ratings.

Figure 2-1 Schematic of proposed traction inverter system.

In this work, the multi-objective optimization approach is proposed to trade power density (kW/l) against SiC device type (650, 900, 1200V), switching frequency, dc bus voltage, the dc-link capacitor, and thermal management solutions.

Silicon Carbide (SiC) devices have the ability to operate at higher voltage. At a given power rating, the higher dc bus voltage of the inverter enables cable size reduction, resulting in significant copper savings and an overall weight reduction of the electric drivetrain [3]. In addition, a higher dc bus voltage will extend the constant torque-speed range of the motors. Therefore, in this work, the dc bus voltage is intended to increase from 700 V normally used for heavy-duty vehicles to an optimal value for most efficient design, which is higher than 850 V.

The selected voltage rating of the SiC devices is determined by the topology and the dc bus voltage. As shown in Fig. 1,  $S_{a,1}$  and  $S_{a,2}$  need to block full dc bus voltage, while  $S_{a,3}$  and  $S_{a,4}$  only need to block half of the dc bus voltage. All SiC devices are packaged into Wolfspeed's HT-3000 platform as shown in Fig. 2.2 [6], but the configuration of the devices in the module may be different. For instance,  $S_{a,1}$  and  $S_{a,2}$  are packaged as a standard half-bridge module, while  $S_{a,3}$  and  $S_{a,4}$  are packaged in a module using a common-source configuration.

Figure 2-2 Wolfspeed's all SiC high-performance half-bridge power module.

In this work, space vector pulse-width modulation (SVPWM) is used for its higher dc bus voltage utilization. An inverter system level loss model in real-time is firstly designed to estimate the system semiconductor losses based on the possible operation states. The comparison of simulation results on different dc voltages as well as the switching frequency is done to help system design from loss aspect. Then dc-link capacitor selection procedure is introduced considering both minimum capacitance calculation and capacitor root-mean-square (RMS) current calculation. In addition, thermal management solutions and bussing structure are also mentioned in this work briefly. Finally, the hardware-in-the-loop (HIL) simulation study is performed to validate the performance of designed T-type traction inverter system.

## 2.3 Instantaneous fundamental-cycle average loss calculation

Semiconductor power loss analysis plays a critical role in inverter system design, which not only gives guidance in the thermal design but also indicates the major contributors to the losses, which in turn helps to improve system efficiency. Two major parts, conduction loss and switching loss are included in semiconductor power loss analysis in this work. Due to the physical structure difference among various power devices, e.g., IGBTs, MOSFETs, and etc., the device loss models are slightly different, especially when the current and voltage are in the opposite direction. The following loss analysis presented in this work focuses on SiC MOSFETs, and the real-time loss model can be applied to various topologies. Most of the existing loss calculation methods are based on mathematical models, and they usually assume some ideal conditions, for instance, neglecting harmonics [7]. On the other hand, mathematical models are often case by case when gate control part varies. As a result, building a flexible generic real-time loss model benefits a lot in inverter design.

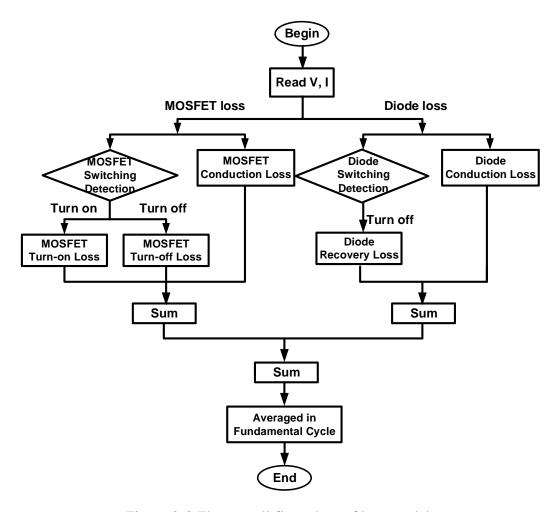

In this work, six CAS325M12HM2 1.2 kV SiC MOSFET modules are used in the design, in which main switches,  $S_{a,1}$  and  $S_{a,2}$ , are configured in the standard half bridge structure, while middle switches,  $S_{a,3}$  and  $S_{a,4}$ , are using common-source configuration. It is assumed that electrical characteristics of single MOSFET chip in both these two kinds of modules are the same. According to [8], the loss model is built in Matlab Simulink. The overall flow chart of real-time loss calculation is shown in Fig. 2.3. Both instantaneous power loss and average loss over a fundamental cycle can be generated by the model. The sampling period, which is set as 0.5  $\mu$ s, should be set small enough to ensure the accuracy. The instantaneous voltage and current information are read directly from MOSFET block measurement ports.

Figure 2-3 The overall flow chart of loss model.

## **2.3.1 MOSFETs**

To determine the switching loss, the switching state should be detected firstly. Assume over two consecutive sampling periods, i.e., the kth and k-1th,

$$Ik > 0 \& Ik-1 = 0 \rightarrow turn on$$

$$Ik = 0 \& Ik-1 > 0 \rightarrow turn off$$

Once the switching state is detected, the turn-on and turn-off energy look-up table is used to determine the switching energy. Switching energy vs.  $I_{DS}$  is usually tested at 25 °C and presented in the datasheet. Temperature conversion should be done using the figure of switching energy vs.

the junction temperature, Tj. Till now, the value of switching energy has been corrected by temperature and current, but not the voltage, e.g.,  $V_{DS-test}$  is 800 V. It can be assumed that Eon and Eoff are proportional with VDS, then equation (2-1), (2-2) can be used to calculate the final loss energy.

$$E_{on} = \frac{E_{on,I_k} \cdot V_{DS-test}}{V_{k-1}} \tag{2-1}$$

$$E_{off} = \frac{E_{off,I_{k-1}} \cdot V_{DS-test}}{V_k} \tag{2-2}$$

For conduction loss, due to the physical structure of MOSFETs, it can be regarded when current and voltage are in the opposite direction, current will go through MOSFET itself in steady state, not the antiparallel diode. So both drain-source/source-drain voltage vs. current in 1st and 3rd quadrant need to be considered. Look-up tables are built using the data when Vgs = 20 V, then conduction power loss can be calculated by equation (2-3).

$$P_{\text{con.}} = V_{DS} \cdot I_D \cdot S \tag{2-3}$$

where S represents switching state, either 0 or 1.

### 2.3.2 Diodes

For switching loss, diode turn-on loss is usually neglected since it is very small. Reverse recovery energy Err or reverse recovery charge Qrr is usually given in the datasheet. Based on these information, the switching state detection and switching energy correction can be done by previous the MOSFET loss calculation procedure. In this work, since SiC Schottky diodes have

already been anti-paralleled in the module used in this work, the diode reverse recovery loss is neglected.

For conduction loss, the antiparallel diode characteristic in the datasheet is needed when Vgs = -5 V and at the actual operating temperature. Then conduction power loss can be calculated by

$$P_{\text{con.}} = V_{DS} \cdot I_D \cdot \overline{S} \tag{2-4}$$

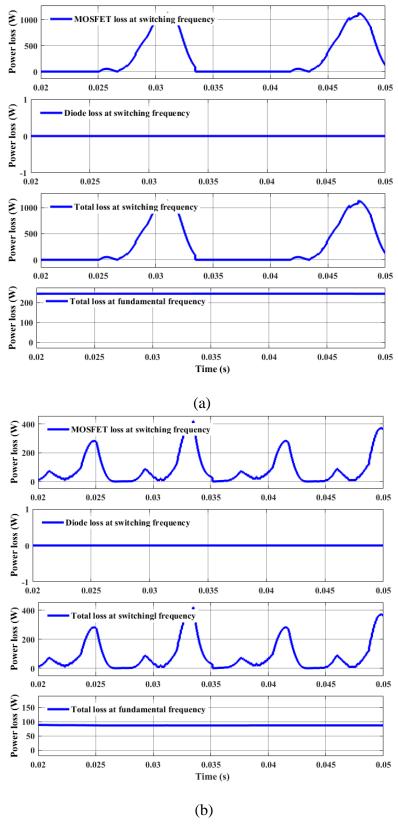

Real-time simulation results of power loss are shown in Fig. 2-4, in which both MOSFET and diode instantaneous losses are captured. Meanwhile, average power loss over the fundamental frequency is also given, which is very useful in thermal design. Due to the symmetry of modulation waveform, the loss on  $S_{a,1}$  and  $S_{a,2}$  are equal, similar for  $S_{a,3}$  and  $S_{a,4}$ .

Table 2-1 Power loss simulation result on 700, 800, 900 V dc bus when  $f_s = 20 \text{ kHz}$

| Vdc<br>(V) | m     | Power | Power loss on S1 (W) |       | Power loss on S3 (W) |      | 3-phase<br>total (W) | Percentage on system power (%) |       |

|------------|-------|-------|----------------------|-------|----------------------|------|----------------------|--------------------------------|-------|

|            |       | Sw.   | Con.                 | Total | Sw.                  | Con. | Total                |                                |       |

| 700        | 0.97  | 47    | 198                  | 245   | 6                    | 79   | 85                   | 1980                           | 0.792 |

| 800        | 0.849 | 56    | 173                  | 229   | 7                    | 119  | 126                  | 2130                           | 0.852 |

| 900        | 0.754 | 61    | 153                  | 214   | 8                    | 149  | 157                  | 2226                           | 0.890 |

Figure 2-4 Simulation result of power losses when Vdc = 700 V, pf = 0.8, fs = 20 kHz for (a)  $S_{a,2}$  in main switch bridge (b)  $S_{a,4}$  in the middle switch bridge.

Table 2-2 Power loss simulation result on 700, 800, 900 V dc bus when  $f_s = 40 \text{ kHz}$

| Vdc<br>(V) | m     | Power loss on S1 (W) |      | Power loss on S3 (W) |     | 3-phase<br>total (W) | Percentage<br>on system<br>power (%) |      |       |

|------------|-------|----------------------|------|----------------------|-----|----------------------|--------------------------------------|------|-------|

|            |       | Sw.                  | Con. | Total                | Sw. | Con.                 | Total                                |      |       |

| 700        | 0.97  | 93                   | 194  | 287                  | 13  | 76                   | 89                                   | 2256 | 0.902 |

| 800        | 0.849 | 108                  | 167  | 275                  | 14  | 116                  | 130                                  | 2430 | 0.972 |

| 900        | 0.754 | 122                  | 149  | 271                  | 16  | 146                  | 162                                  | 2598 | 1.039 |

# 2.3.3 A case study of DC bus voltage

In this work, the design target is a 250 kW traction drive inverter with T-type topology with rated 480 Vrms line-to-line voltage and 300 Arms phase current. The modulation index needs to be tuned to coordinate the dc bus voltage. 700 V, 800 V, 900 V are selected to be compared in this work. The loss result is listed in Table 2-1. Switching frequency is set to be 20 kHz here, and power factor is 0.8. Due to the T-type operation characteristics, the conduction power loss on the diode is 0 with RL load. In addition to the aforementioned zero reverse recovery energy in SiC Schottky diodes. The total diode loss is assumed as 0. Therefore, only MOSFET loss data is given in Table 2-1.

From Table 2-1, it can be seen that 700 V DC results in the smallest total power losses, which is around 0.79% of the total inverter power, which means the 98% peak efficiency is achievable even considering other type losses. In addition, the modulation index has a critical impact on conduction loss. The conduction loss on S<sub>a,1</sub> is proportional to modulation index, but reversed for S<sub>a,3</sub>. Here assumed middle bridge also use 1.2 kV module, but actually only half of the dc voltage rating is enough for middle bridge module. If 650 V device is used in middle bridge, the R<sub>ds-on</sub> will

be reduced significantly, and therefore the loss will also reduce. The tradeoff between power loss and loss distribution should also be noticed. Although the 900 V dc bus case has 12.42% more power loss than 700 V case, the loss distribution is more even on the two modules per phase. Finally, switching loss in middle bridges  $S_{a,3}$  is almost negligible, conduction loss accounts for the major loss. This is mainly because when current and voltage is in the same direction, the MOSFET is "soft" switching. Here the small switching loss comes from the 0.8 power factor. The larger the power factor, the smaller the middle bridge switching loss.

# 2.3.4 A case study of switching frequency

Since CAS325M12HM2 can work at a switching frequency much higher than 20 kHz, the power loss at 40 kHz switching frequency is also compared in Table 2-2. As can be seen from the table, when switching frequency increases to 40 kHz, conduction loss decreases slightly, while switching loss increases dramatically. As a result, although higher switching frequency can give better output voltage quality, the tradeoff between output quality and power loss needs to be considered.

# 2.4 DC-link capacitor selection

Because the dc bus has stray inductance and resistance and the dc side current is pulsating, the dc-link capacitor is needed to solve potential EMI issues. Also, dc-link capacitor takes large portion of the overall inverter volume, the dc link capacitor selection will obviously affect the system power density. The dc-link capacitance depends on the energy of current ripple need to be absorbed and the rating of RMS current. DC-link current ripple includes not only load current at the fundamental frequency, but also current at PWM switching frequency and their harmonic contents.

According to [9], theoretical minimum dc-link capacitance in a three-phase 3-L converter is derived as equation (2-5). This calculation method is based on two main considerations: the maximum input power and the maximum allowable voltage fluctuation.

$$C_{d,\min} \ge \frac{\Delta P_{Max} \cdot T_d}{2V_{dc} \cdot \Delta V_{dc}} \tag{2-5}$$

where  $\Delta P_{Max}$  is maximum power variation of inverter;  $T_d$  is response time of voltage control loop (5 to 10 times of switching period); and  $\Delta V_{dc}$  is maximum allowable voltage fluctuation.

In this work,  $\Delta P_{Max}$  is set to 30% of the full power, and  $\Delta V_{dc}$  is set to 15% of the dc bus voltage. Then the minimum dc-link capacitance is

$$C_{d,\min} \ge \frac{\Delta P_{Max}(30\% \times 250k) \cdot T_d(10/20k)}{2V_{dc}(700) \cdot \Delta V_{dc}(15\% \times 700)} = 255\mu F$$

(2-6)

From equation (2-7), it can be seen that to keep the capacitor working at allowable temperature; the RMS current needs to be predicted when selecting the capacitor [10].

$$T_{c} = T_{a} + I_{CAPRMS}^{2} R_{ESR} R_{th,c-a}$$

(2-7)

where  $T_c$  is the capacitor temperature,  $T_a$  is the ambient temperature,  $R_{ESR}$  is the equivalent series resistance of the capacitor,  $R_{th,c-a}$  is the thermal resistance between capacitor and ambient.

The DC-link capacitor RMS current is related to PWM modulation index and power factor.

According to [10], for the 3-L inverter, it can be derived as following

$$I_{AVG} = \frac{3}{4} I_N M \cos(\phi) \tag{2-8}$$

$$I_{RMS} = \sqrt{\frac{3I_N^2 M (\sqrt{3} + \frac{2}{\sqrt{3}}\cos(2\phi))}{4\pi}}$$

(2-9)

$$I_{CAPRMS} = \sqrt{I_{RMS}^2 - I_{AVG}^2}$$

(2-10)

where I<sub>N</sub> is the phase peak current.

Also, the capacitance, ESR, ESL are all changing with temperature and switching frequency, these need to be noticed during the capacitor selection. Due to safety concerns, it is better to select components' parameters larger than the calculated value. Since the temperature has a significant impact on the dc-link capacitor, proper thermal management approach needs to be considered, such as natural or forced air cooling or liquid cooling. In addition, attaching the capacitors directly to bus bar will be beneficial for cooling.

In this work, the calculated RMS current is 173 A, and 225  $\mu$ F capacitance is needed. To give sufficient safety margin, six film capacitors FFVE6K0227K are selected, they are  $3\times220~\mu$ F in series.

# 2.5 Thermal management and bussing structure

The loss calculation can guide the selection of proper thermal management approach, using proper heatsink or cold plate. Datasheet indicates that the limitation of power dissipation is related to module case temperature. After the average power loss over the fundamental period is known, it is obvious that main switch bridge has more heat dissipation than middle switch bridge. In this work, the maximum calculated power loss is  $245 \times 2 = 490$ W per module. This information can be translated to the maximum allowable case temperature. Based on the performance and cost, proper heatsink and cold plate can be determined.

For high power inverter, bus bar design is a significant part. Bus bar can withstand higher current than traditional cables, and also has much lower impedance, such that the reliability is enhanced. For dc bus bar, 400 circular mils/A is the traditional basis for the design of single conductor, and 5% more cross-sectional area of a conductor needs to be added for each additional conductor laminated into the bus structure [11]. Capacitance between different conductor levels is

preferred to be large, and inductance need to be small so that the overall impedance will be much smaller. This will benefit the noise attenuation. As a result, within the tolerance of voltage rating, the thickness of insulation layer should be as thin as possible. Skin effect needs to be considered for AC bus bar design.

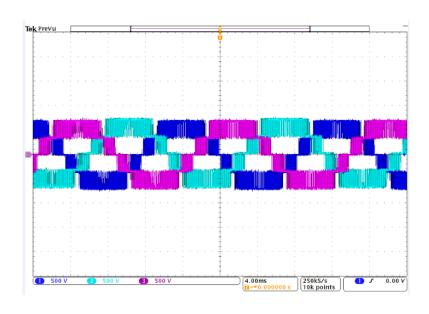

(b) Fig. 2-5 HIL simulation result when  $V_{dc}=700~V,~pf=0.8,~fs=20~kHz$  (a) line-to-line voltage (b) phase current.

# 2.6 Preliminary real-time simulation results

To evaluate the performance of the proposed T-type traction inverter, hardware-in-the-loop (HIL) simulation is performed. The HIL simulation is mainly used to validate the effectiveness of controller design. In this work, the control algorithms are implemented in the control platform designed using TI's TMS320F28379D dual-core microcontroller. As shown in Fig. 2-5, HIL studies have been performed to validate the capability of the controller to synthesize a 480 Vrms three-phase output voltage. The switching frequency is set 20 kHz, DC bus is 700 V, and power factor is simulated at 0.8. Both three-phase line-to-line voltage and phase current waveforms are given.

#### 2.7 Conclusion

In this work, to design a compact 250 kW three-level T-type traction inverter, a holistic PE design approach is proposed trade the power density (kW/l) against SiC device type, the dc bus voltage, the switching frequency, and the heat dissipation method. The real-time loss calculation model is given in this work, which can be applied to other circuit topology. The dc-link capacitor selection approach is also briefly introduced. Thermal management and bus bar design are also important for the integrated high-power density inverter system design. Finally, preliminary HIL simulation study is performed to validate the performance of the designed control for the traction inverter system.

## Acknowledgment

This work was supported in part by the National Science Foundation (NSF) Engineering Research Center (ERC) for Power Optimization of Electro-Thermal Systems (POETS) with cooperative agreement EEC-1449548. The information, data, or work presented herein was also

funded in part by the Advanced Research Projects Agency-Energy (ARPA-E), U.S. Department of Energy, under Award Number DE-AR0000895. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

#### 2.8 Reference

- [1] A. H. Wijenayake et al., "Design of a 250 kW, 1200 V SiC MOSFET-based three-phase inverter by considering a subsystem level design optimization approach," 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, 2017, pp. 939-946.

- [2] K. Olejniczak et al., "A 200 kVA electric vehicle traction drive inverter having enhanced performance over its entire operating region," 2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Albuquerque, NM, USA, 2017, pp. 335-341.

- [3] B. Singh, "Novel and Ruggedized Power Electronics for Off-Highway Vehicles," in *IEEE Electrification Magazine*, vol. 2, no. 2, pp. 31-41, June 2014.

- [4] M. Schweizer, T. Friedli, and J. W. Kolar, "Comparison and implementation of a 3-level NPC voltage link back-to-back converter with SiC and Si diodes," *Proc. IEEE 25th Annual Appl. Power Electron. Conf. Expo.*, pp., 1527–1533.

- [5] M. Schweizer and J. W. Kolar, "Design and Implementation of a Highly Efficient Three-Level T-Type Converter for Low-Voltage Applications," in *IEEE Transactions on Power Electronics*, vol. 28, no. 2, pp. 899-907, Feb. 2013.

- [6] Wolfspeed, CAS325M12HM2, 1200V, 325A, Silicon Carbide High-Performance 62 mm Half-Bridge Module. [Online]. Available:

- http://www.wolfspeed.com/cas325m12hm2

- [7] X. Yuan, "Analytical averaged loss model of a three-level T-type converter," in *Proc. International Conference on Power Electronics, Machines and Drives (PEMD 2014)*, Manchester, 2014, pp. 1-6.

- [8] "Loss Calculation in a Three-Phase 3-Level Inverter- MATLAB & Simulink", Mathworks.com, 2018. [Online]. Available: https://www.mathworks.com/help/physmod/sps/examples/loss-calculation-in-a-three-phase-3-level-inverter.html?searchHighlight=LOSS%20MODEL%20INVERTER&s\_tid=doc\_srchtitle. [Accessed: 20- Apr- 2018].

- [9] P. Alemi, Y. C. Jeung and D. C. Lee, "DC-Link Capacitance Minimization in T-Type Three-Level AC/DC/AC PWM Converters," in *IEEE Transactions on Industrial Electronics*, vol. 62, no. 3, pp. 1382-1391, March 2015.

- [10] K. Gopalakrishnan, S. Das and G. Narayanan, "Analysis Expression for RMS DC Link Capacitor Current in a Three Level Inverter," *Centenary conference*, 2011

- [11] "Design Guide Formulas | Engineering Tool Box |", Busbar.com, 2018. [Online]. Available: http://www.busbar.com/resources/formulas/. [Accessed: 20- Apr- 2018].

#### **CHAPTER 3**

# DESIGN AND VALIDATION OF A 250 KW ALL SILICON CARBIDE HIGH-DENSITY THREE-LEVEL T-TYPE INVERTER

© 2020 IEEE. Reprinted, with permission, from Z. Wang, Y. Wu, M. H. Mahmud, Z. Zhao, Y. Zhao and H. A. Mantooth, "Design and Validation of A 250-kW All-Silicon Carbide High-Density Three-Level T-Type Inverter," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 8, no. 1, pp. 578-588, March 2020.

#### 3.1 Abstract

This paper presents a comprehensive design and validation of a compact all silicon carbide (SiC) 250 kW T-type traction inverter with a power density of 25 kW/l and 98.5% peak efficiency. All the operation modes and switching transitions in a T-type phase leg are analyzed to model the semiconductor power losses over a fundamental cycle. Special attention has been paid to investigate the behavior and losses due to the reverse conduction of the SiC MOSFETs. Then a loss model is built based upon this analysis to calculate the device loss distribution and system efficiency, which is further used to determine the optimal switching frequency. In addition, detailed inverter system design and prototyping procedure, including the selection of SiC modules and dc-link capacitors, and the optimization of a 4-layer laminated busbar, are presented. In this work, the T-type phase leg is formed by a normal half bridge module and a common source module. The switching performance and losses in this configuration are different from two-level topology that only uses one SiC module. Therefore, the switching performance and the associated switching energy in each switch position are characterized using a custom clamped inductive load (CIL) test

setup designed for a T-type phase leg. The performance of the full power traction inverter prototype has been verified experimentally using pulse testing and continuous power testing.

#### 3.2 Introduction