University of Arkansas, Fayetteville ScholarWorks@UARK

Graduate Theses and Dissertations

7-2021

## Distributed Modeling Approach for Electrical and Thermal Analysis of High-Frequency Transistors

Amirreza Ghadimi Avval University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Electrical and Electronics Commons, Electromagnetics and Photonics Commons, Electronic Devices and Semiconductor Manufacturing Commons, Semiconductor and Optical Materials Commons, and the Thermodynamics Commons

#### Citation

Ghadimi Avval, A. (2021). Distributed Modeling Approach for Electrical and Thermal Analysis of High-Frequency Transistors. *Graduate Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/ etd/4135

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu.

#### Distributed Modeling Approach for Electrical and Thermal Analysis of High-Frequency Transistors

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering with a concentration in Electrical Engineering

by

Amirreza Ghadimi Avval University of Tabriz Bachelor of Science in Electrical Engineering, 2014 Shahid Beheshti University Master of Science in Electrical Engineering, 2016

#### July 2021 University of Arkansas

This dissertation is approved for recommendation to the Graduate Council.

Samir M. El-Ghazaly, Ph.D. Dissertation Director

Shui-Qing Yu, Ph.D. Committee Member Morgan E. Ware, Ph.D. Committee Member

Gregory J. Salamo, Ph.D. Committee Member

#### Abstract

The research conducted in this dissertation is focused on developing modeling approaches for analyzing high-frequency transistors and present solutions for optimizing the device output power and gain. First, a literature review of different transistor types utilized in high-frequency regions is conducted and gallium nitride high electron mobility transistor is identified as the promising device for these bands. Different structural configurations and operating modes of these transistors are explained, and their applications are discussed. Equivalent circuit models and physics-based models are also introduced and their limitations for analyzing the small-signal and large-signal behavior of these devices are explained. Next, a model is developed to investigate the thermal properties of different semiconductor substrates. Heat dissipation issues associated with some substrate materials, such as sapphire, silicon, and silicon carbide are identified, and thinning the substrates is proposed as a preliminary solution for addressing them. This leads to a comprehensive and universal approach to increase the heat dissipation capabilities of any substrate material and 2X-3X improvement is achieved according to this novel technique.

Moreover, for analyzing the electrical behavior of these devices, a small-signal model is developed to examine the operation of transistors in the linear regions. This model is obtained based on an equivalent circuit which includes the distributed effects of the device at higher frequency bands. In other words, the wave propagation effects and phase velocity mismatches are considered when developing the model. The obtained results from the developed simulation tool are then compared with the measurements and excellent agreement is achieved between the two cases, which serves as the proof for validation. Additionally, this model is extended to predict and analyze the nonlinear behavior of these transistors and the developed tool is validated according to the obtained large-signal analysis results from measurement. Based on the developed modeling approach, a novel fabrication technique is also proposed which ensures the high-frequency operability of current devices with the available fabrication technologies, without forfeiting the gain and output power. The technical details regarding this approach and a sample configuration of the electrode model for the transistor based on the proposed design are also provided.

#### Acknowledgement

I would like to express my deepest appreciation and gratitude to my Ph.D. supervisor, Dr. Samir El-Ghazaly, for his patience and assistance throughout this entire journey. He was not only a knowledgeable advisor whose technical support was indispensable to my sanity, but also a caring mentor who gave me guidance and motivation and helped me in setting my goals towards the coming steps in my professional life. His timely advice and meticulous scrutiny aided me to accomplish this task.

Also, I would like to acknowledge my dissertation committee members, Dr. Gregory Salamo, Dr. Shui-Qing Yu, and Dr. Morgan Ware for their support and motivation and assisting me in achieving all my objectives in this path. They have always made me feel very welcomed when I was in need.

I am also very much grateful that I had the chance to work with Dr. Cynthia sides during the "Emerging technologies in industry" course I took with her. It was indeed an invaluable experience that gave insights to more practical aspects of my studies.

Also, I would like to thank Dr. James Rankin, our former Vice Provost for Research and Economic Development, who was simply there when no one else was.

I would also like to express my special thanks to the Technology Ventures and Licensing Office at the university. They were always supportive and encouraging us to keep up the inventive spirit.

The work in this research was supported in part by the National Science Foundation (NSF) under Grant 1745143, and in part by the U.S. Army Research Office under Award W911NF-20-2-0120. Any opinions, findings, and conclusions or recommendations expressed in this research are those of the author and do not necessarily reflect those of the National Science Foundation and the U.S. Army Research Office.

### Dedication

To the loving memory of the victims of Flight PS752

And to the memory of Howard C. Baskerville,

who could not be indifferent to the sufferings of people fighting for their rights

## Epigraph

"Let the future tell the truth and evaluate each one according to his work and accomplishments.

The present is theirs; the future, for which I have really worked, is mine"

— Nikola Tesla

## **Table of Contents**

## **Chapter 1: Introduction**

| 1.1 Introduction                                                                             | 1  |

|----------------------------------------------------------------------------------------------|----|

| 1.2 Thermal management and heat dissipation issues                                           | 3  |

| 1.3 Device analysis and distributed modeling approach                                        | 5  |

| 1.4 Optimized electrode design                                                               | 14 |

| 1.5 Dissertation objectives and motivation                                                   | 17 |

| 1.6 Dissertation organization                                                                | 18 |

| 1.7 References                                                                               | 18 |

| Chapter 2: Heterojunction field effect transistors                                           |    |

| 2.1 Introduction                                                                             | 20 |

| 2.2 Passive and active characteristics of HEMTs                                              | 22 |

| 2.3 New design of AlGaN/GaN HEMT                                                             | 31 |

| 2.4 HEMT modeling                                                                            | 33 |

| 2.5 HEMT applications                                                                        | 40 |

| 2.6 Conclusion                                                                               | 42 |

| 2.7 References                                                                               | 42 |

| Chapter 3: Apparatus and method to reduce the thermal resistance of semiconductor substrates |    |

| 3.1 Introduction                                                                             | 45 |

| 3.2 Substrate modeling                                                                       | 47 |

| 3.3 Description of the proposed solution                                                     | 51 |

| 3.4 Heat distribution results                                                                | 53 |

| 3.5 Conclusion                                                                               | 60 |

| 3.6 | References |

|-----|------------|

|     |            |

# Chapter 4: Distributed-model-based approach for electrical and thermal analysis of high-frequency GaN HEMTs

| 4.1 Introduction                                                    | 64  |

|---------------------------------------------------------------------|-----|

| 4.2 Device configuration and modeling procedure                     | 67  |

| 4.3 Distributed modeling approach and finite difference analysis    | 73  |

| 4.4 Simulation and model validation                                 | 76  |

| 4.5 Heat distribution effects                                       | 79  |

| 4.6 Conclusion                                                      | 84  |

| 4.7 References                                                      | 84  |

| Chapter 5: Increasing transistor gain using metamaterial electrodes |     |

| 5.1 Introduction                                                    | 89  |

| 5.2 Device structure and equivalent circuit model                   | 92  |

| 5.3 Small-signal analysis                                           | 95  |

| 5.4 Large-signal analysis                                           | 96  |

| 5.5 Operability limitations in mm-wave devices                      | 97  |

| 5.6 Solution for high-frequency operability                         | 100 |

| 5.7 Conclusion                                                      | 102 |

| 5.8 References                                                      | 103 |

| Chapter 6: Conclusion and future work                               |     |

| 6.1 Conclusion                                                      | 105 |

| 6.2 Future work                                                     | 108 |

#### List of published papers

**Chapter 2:** A. G. Avval, E. Larique, and S. M. El-Ghazaly, "Heterojunction field effect transistors" *Reference Module in Materials Science and Materials Engineering*, Amsterdam, The Netherlands: Elsevier, 2018.

**Chapter 3:** A. G. Avval, S. Yu, G. J. Salamo, and S. M. El-Ghazaly, "Apparatus and method to reduce the thermal resistance of semiconductor substrates," U.S. Patent Application US20200194333A1, Jun. 2020.

**Chapter 4:** A. G. Avval and S. M. El-Ghazaly, "Distributed-Model-Based Approach for Electrical and Thermal Analysis of High-Frequency GaN HEMTs," *IEEE Access*, vol. 8, pp. 152333-152341, 2020.

**Chapter 5:** A. G. Avval and S. M. El-Ghazaly, "Increasing transistor gain using metamaterial electrodes," U.S. Patent Application, Serial No. 62/986,906, filed on 03/09/2020.

#### Chapter 1

#### Introduction

#### **1.1 Introduction**

Systems and devices with high output powers, operating at high-frequency bands have penetrated almost every aspect of the applications in the areas of wireless communications, remote sensing, and aerospace, to name only a few. These two features are the most critical properties of the devices that embody the future of many systems in achieving higher data rates. One of the main categories of these systems is the active microwave devices that, as the name indicates, is expected to operate at the microwave (MW) and millimeter-wave (mm-wave) frequency bands in order to meet the broad bandwidths and reconfigurability requirements. In general, many technologies operating at this frequency range owe their emergence and advancements to the material properties of gallium nitride (GaN) utilized in high electron mobility transistor (HEMT) devices. High saturation velocity, high electron mobility, high sheet carrier density, and high breakdown voltage are some of the characteristics associated with GaN that make it a material that meets the requirements of building high-power amplifiers (HPAs) capable of working at high operating frequencies.

These high-frequency transistors are incorporated in many of the complicated contemporary systems in order to drive a multitude of compact passive and active circuit components and elements that are accompanied by numerous discontinuity levels and transmission line sections. Charge transport, thermal properties, and electromagnetic-wave propagations are some of the topics that must be addressed in such high-performance mm-wave systems, and this must be conducted on more than an individual basis. The reason is mainly due to their diverse physical dimensions in the structure and various frequency scales and power levels while operating. Understanding these subject matters has offered technical cognizance to

enhance the device performance of mm-wave transistors for various applications in terms of increasing their efficiency, gain, bandwidth, and output power.

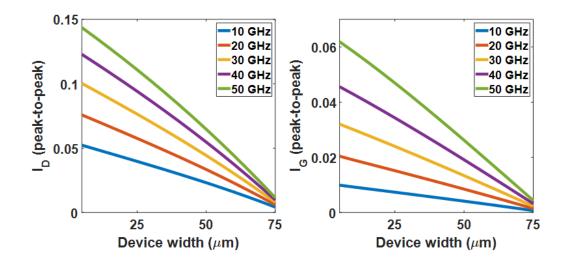

The gain and RF output power for mm-wave transistors are directly related to the device width, which signifies the direction along the device electrodes perpendicular to the flow of charges. At mm-wave bands, the device electrodes may act as transmission lines due to their large size relative to the wavelength of the guided wave inside the device. In typical transistor configurations, the input impedance (gate to source) and output impedance (drain to source) are significantly different. Consequently, the phase velocities of the propagating waves on the input line, gate electrode, and output line, drain electrode, will be different. This phase velocity mismatch, when exists, causes significant degradations in the device performance, such as reducing the available gain and output power and limiting the maximum operating frequency. To avoid the phase-cancellation effects, the fabricated device width is normally limited to at least less than one-twentieth of the propagating wavelength, which makes the effects of the velocity mismatch ignorable. Consequently, a sufficient number of transistor fingers needs to be incorporated in order to obtain the desired output power. Therefore, numerous interconnects are introduced to the device design which adds more parasitic elements to the system. Hence, in addition to optimizing the semiconductor structure, rearranging the electrode layouts to reduce the phase-velocity mismatch, increase the efficiency, and minimize the effects of discontinuities and signal losses, are of great importance in designing mm-wave transistors.

In this research, three main issues associated with the operation of high-frequency transistors are identified and appropriate solutions are provided. The first issue is related to the thermal management, where the devices are not capable of sufficiently dissipating the internally generated heat. The second problem relates to the limitations with the developed circuit models for analyzing these devices, where the required reliability and comprehensiveness are not offered by the modeling approaches. The last issue is about the presence of a phase velocity mismatch with the devices operating at mm-wave frequency bands which notably reduces the gain of the device and imposes fabrication limitation. These issues will be briefly explained in the following sections and the extended discussions will be provided in the next chapters.

#### 1.2 Thermal management and heat dissipation issues

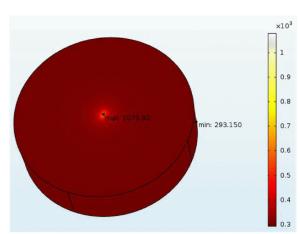

Transistor operations are mainly associated with different gain values and output power densities provided at specific frequency bands along with other figures of merit. One of the important factors that has a huge effect on these operating modes and needs to be studied and analyzed when characterizing a semiconductor device, is the operation over different temperature gradients. In GaN HEMTs, due to being a high-power device, a great amount of internal heat is generated, and it affects the electrical behavior of the transistor [1]. Hence, information about the maximum temperature that the device channel can handle is very vital. The generated heat in the channel layer is normally dissipated through the substrate layer and deciding on the optimized material type and structure for this layer is a very critical stage of device design and development [2].

For all types of transistors that are operating at high voltage levels, the created current in the output is very large which translates into the generation of high temperature gradients. These local hot spots that are generally in the vicinity of the gate electrode, if not cooled efficiently, hinder the proper operation of the device or even damage the structure of the transistor. Therefore, the heat handling and dissipation capabilities of the device is very important for a reliable transistor operation at high frequency ranges and high output power levels. The solution provided in this research is associated with the thermal conductance of the substrate platform on which the device is grown, which leads to improvements in power handling capabilities of the transistor.

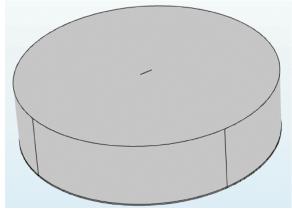

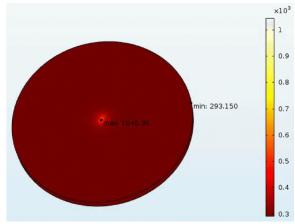

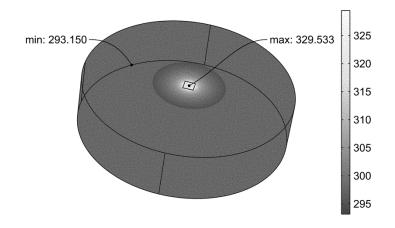

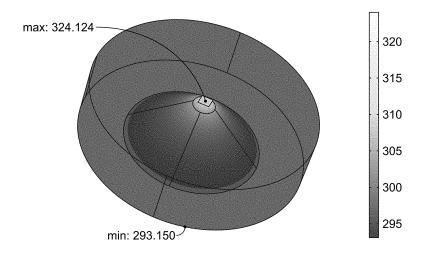

For this purpose, different substrate materials and structures are modeled, and rigorous simulation are conducted to identify the thermal issues and present solutions. The initial material to be tested is sapphire which possesses specific characteristics suitable for high-frequency and high-power operations. However, sapphire has a low heat conductivity which gives rise to numerous heat dissipation issues and results in being substituted with other semiconductor substrates, such as silicon carbide, in many applications. This imposes some cost limitations as sapphire is a much cheaper option. In this research, all the simulations are conducted in COSMOL Multiphysics where the dimensions for the structures and the boundary conditions are defined according to practical experiments. The initial step for proposing a holistic fabrication approach for solving the heat dissipation issues with substrates is to consider utilizing thinner platforms in device structures. The simulation results associated with this design is promising and an analytical approach is also employed to further validate the obtained results. From practical viewpoints, the thinner substrates are achieved either prior or after the fabrication process.

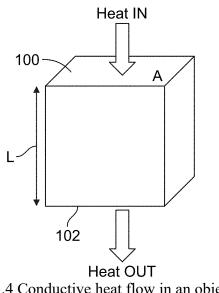

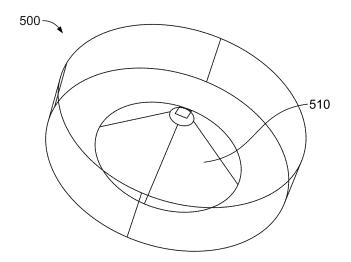

The heat transfer model utilized in this study is the conduction heat transfer that mainly relates to temperature gradients in a solid structure. For increasing the heat conduction coefficient, which results in a decrement in thermal resistance of the material, a selective etching process is utilized which is applied on the substrate from backside. The resulting configuration is a substrate which is comprised of materials such as silicon, sapphire, and silicon carbide and includes a plurality of spaced-apart heat sinks that are filled with one or more materials with high

heat conductivity such as copper. The etched section is generally in the shape of a truncated cone for facilitating the process. Practically, the filling process for the hollow etched section is performed through sputtering [3]. For the optimized design, the improvement for the silicon, silicon carbide, and sapphire substrates is 78%, 101%, and 288%, respectively. All the details related to the thermal modeling and optimization of the device structure will be provided in Chapter 3.

#### 1.3 Device analysis and distributed modeling approach

In the recent years, there has been an increasing demand for developing high-power and high-frequency devices for many applications in wireless communication systems, where the circuit models have played a major role in optimizing the design process for advanced state-of-the-art monolithic microwave integrated circuits (MMICs). One of the most critical features of the models developed for individual devices at radio frequency (RF) ranges, is the wideband accuracy. For the microwave and mm-wave ranges, the operation of the devices become distinctly different than their low-frequency counterparts and performance degradations are normally observed in their behavior. The developed equivalent circuit models for these operating bands are comprised of intrinsic- and extrinsic-level elements and the performance drop is generally associated with both of these sections [4]. Hence, for establishing universally-satisfactory circuit models, which incorporate the complicated device topology, the properties of different materials used in fabrication, and underlying physical behavior of the device, care must be taken in identifying the extrinsic parasitic elements of the device interconnects and they must be considered as important components similar to the bias-dependent active elements.

The parasitic couplings of the devices operating at high frequency ranges are mainly referred to as linear elements which depend on the electrode structures, interconnects, and probe pad models. These elements are primarily extracted based on characterizing the fabricated device according to the measurement data. In other words, for a circuit model to be developed when there is a slight variation in the configuration, a new device based on the updated topology must be fabricated and characterized. This process is not cost-efficient and requires long processing times. Additionally, this procedure demands using numerical curve-fitting practices which suffer from convergence to physically-illogical local minima [5]. The key objective for developing a circuit model is to have a simulation platform that provides a tool for design optimizations before the fabrication stage.

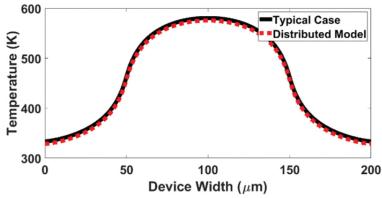

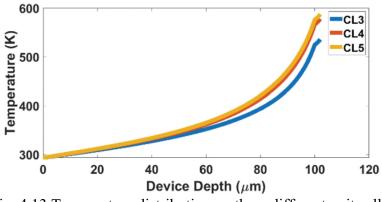

In this research, an equivalent circuit model is developed for the analysis of a GaN transistor for the W-band frequencies and beyond. This model is developed solely based on the physical structure of the device and according to the conformal mapping theorem and incremental inductance rule without utilizing the experimental data of the fabricated device. Moreover, the model incorporates the electromagnetic-wave propagation effects and wave-particle interactions by taking advantage of the distributed concepts. This ensures that the model maintains its accuracy at higher frequency bands. The simulation results are provided for different operating modes and the model is validated by the measurement results obtained from the fabricated device. A brief explanation of the model development along with the preliminary results is presented here.

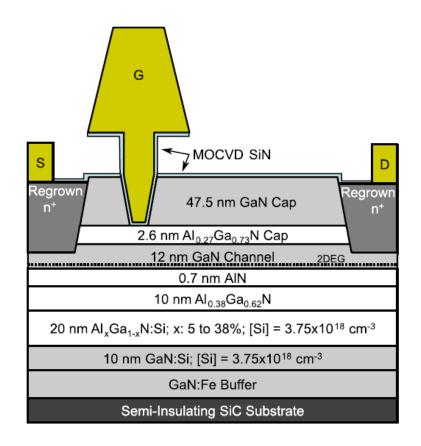

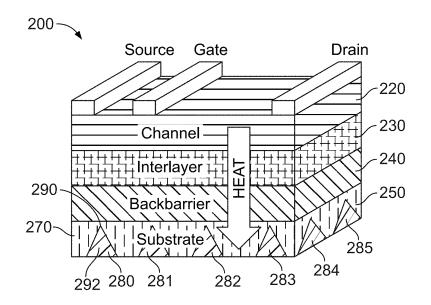

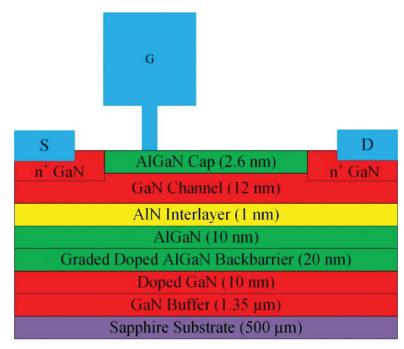

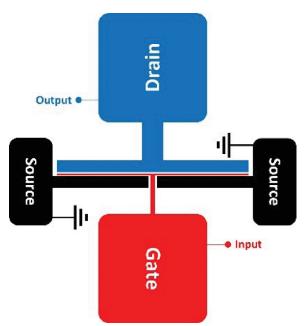

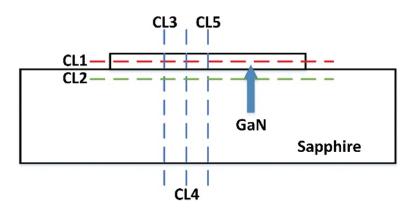

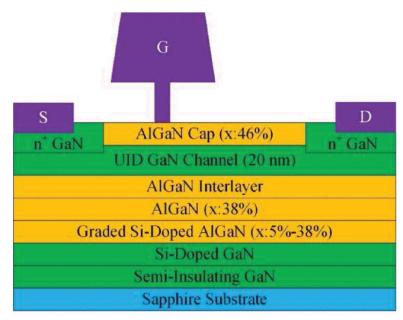

#### 1.3.1 Device structure and circuit model development

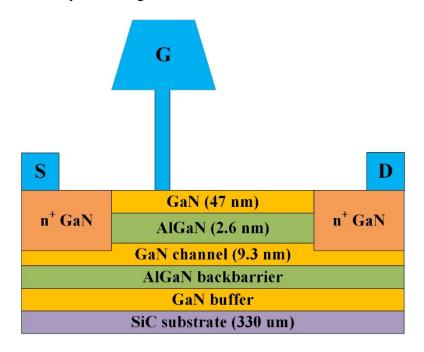

The configuration of a nitrogen-polar mm-wave GaN MISHEMT device fabricated by Guidry *et al.* is demonstrated in Fig. 1.1 [6]. The device is grown on a silicon carbide substrate and consists of a GaN buffer layer, an AlGaN back-barrier, a 9.3 nm GaN channel, a 2.6 nm AlGaN layer, and a 47 nm GaN cap. The gate stem height is 250 nm and the trapezoidal form of the gate top ensures the sufficient reduction of the parasitic resistance on the input electrode. The device has a 25  $\mu$ m width for each of its fingers and the multi-finger layout of the device is designed based on a T-configuration.

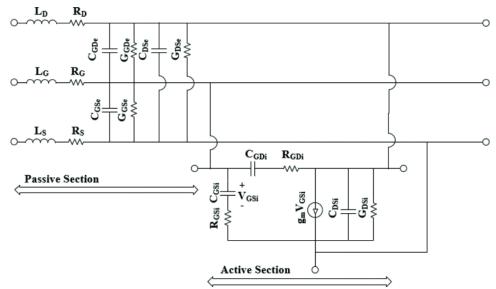

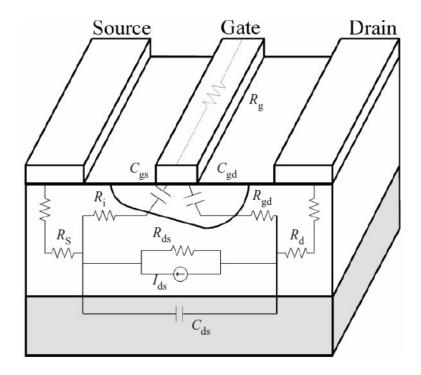

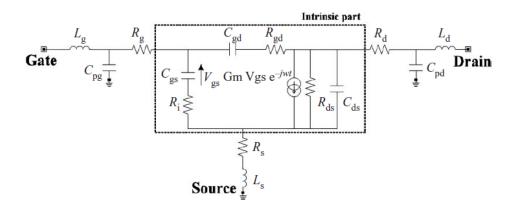

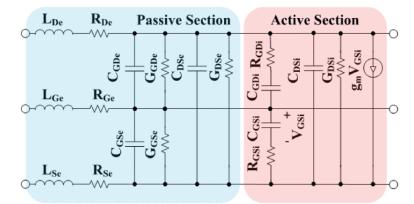

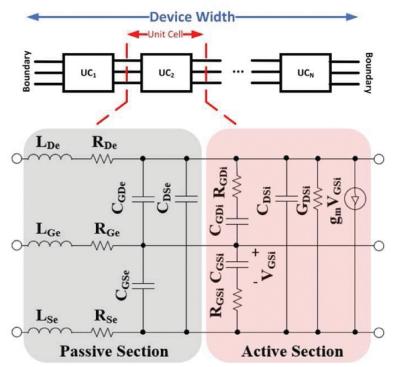

The frequency at which the device is operating determines the electromagnetic wavelength of the guided wave inside the device. At higher operating frequencies, the device width and the active component dimensions become comparable to the wavelength, which makes the lumped-element conventional small-signal equivalent circuits inaccurate for modeling, due to the phase velocity mismatch in the input and output. In order to take into account the wave propagation effects, the intrinsic equivalent circuit is combined with the transmission line system, called the extrinsic section, and the resulting configuration is depicted in Fig. 1.2. This model is a typical 19-element small-signal equivalent circuit and is considered as the unit-cell for the distributed model utilized at higher frequencies. In order to simplify the element extraction technique, a quasi-transverse electromagnetic (quasi-TEM) approximation, valid for microwave range operating frequencies, is also considered. The parameters are extracted as follows:

**Extrinsic Capacitance:** To obtain the values for the coupled capacitors between drain, source, and gate electrodes, the proposed model in is simulated in COMSOL Multiphysics. This tool is used as the 3D Laplace solver for our equations. The conductors are considered to be made of gold and all the boundary conditions are defined accordingly. Since the coupling effects

must be observed on these elements, one of the conductors is excited with a defined voltage and the charge is measured on the other two conductors. The capacitance value is equal to the observed charge divided by the voltage.

Fig. 1.1 GaN MISHEMT cross-section.

Fig. 1.2 19-element small-signal equivalent model for high frequency transistors and the representative of a unit-cell for the distributed model.

**Extrinsic Inductance:** According to quasi-TEM approximation, the magnetic field solution around the device is not affected by the presence of III-Nitride semiconductor layers and the substrate under the conductors. Therefore, similar to obtaining the capacitance, the same device is structured in COMSOL Multiphysics without considering the semiconductor layers. First, the capacitance on each line is measured by exciting one electrode and observing the charge on that same electrode. Then, as the phase velocity is the same as the speed of light in free space, the inductance of each line is calculated using Equation (1.1). *c* is the speed of light in free space and *L* and *C* are the inductance and capacitance per unit width of the device, respectively.

$$L = \frac{1}{C \times c^2} \tag{1.1}$$

**Extrinsic Conductance:** Similar to the approach implemented for finding the extrinsic capacitance, the device structure is arranged in COMSOL. To define the conductivity parameter of the semiconductor layers, carrier concentration and mobility of electrons and holes are considered. This parameter is mostly controlled by the characteristics of the channel layer and the 2DEG (two-dimensional electron gas) layer in high-frequency devices. Due to the coupling nature of the conductance in this model, a voltage is applied on a conductor and the current is observed on the other two electrodes.

**Extrinsic Resistance:** The conductor loss for all the electrodes is obtained using Wheeler's incremental inductance rule [7]. As the magnetic field penetrates into the electrode, an internal inductance is created. To obtain the value of the internal inductance, first, the external inductance is calculated as mentioned above. Then, all the dimensions of the conductors are reduced by half the skin depth and the external inductance is calculated again. The difference

between the external inductance of these two cases is equal to the internal inductance, which is multiplied by the angular frequency to give us the value of resistance on each line.

**Intrinsic Elements:** The parameters for the intrinsic section of the device are also obtained using the already developed extraction methods as explained in [8]. These parameters are dependent on the bias point and represent the active characteristics of the transistor. The obtained values for the full small-signal equivalent model are summarized in Table 1.1. The parameters are provided in per-unit width of the device.

| <b>Extrinsic Parameters</b> |                        | Intrinsic Parameters             |

|-----------------------------|------------------------|----------------------------------|

| $L_S = 2.40 \ nH/cm$        | $C_{GDe} = 314  fF/cm$ | $C_{GSi} = 8.38  pF/cm$          |

| $L_G = 2.58  nH/cm$         | $C_{GSe} = 898  fF/cm$ | $R_{GSi} = 5.56 \ m\Omega. \ cm$ |

| $L_D = 4.48 \ nH/cm$        | $C_{DSe} = 572  fF/cm$ | $C_{GDi} = 332  fF/cm$           |

| $R_S = 60 \ \Omega/cm$      | $G_{GDe} = 22 \ mS/cm$ | $R_{GDi} = 238 \ m\Omega. \ cm$  |

| $R_G = 165  \Omega/cm$      | $G_{GSe} = 63 \ mS/cm$ | $C_{DSi} = 21.5 \ pF/cm$         |

| $R_D = 60 \ \Omega/cm$      | $G_{DS} = 29 \ mS/cm$  | $G_{DSi} = 1.70  S/cm$           |

|                             |                        | $g_m = 6.10  S/cm$               |

Table 1.1 Small-Signal parameter values

#### **1.3.2 Distributed model**

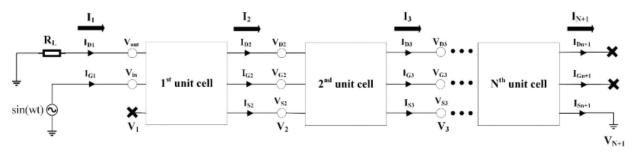

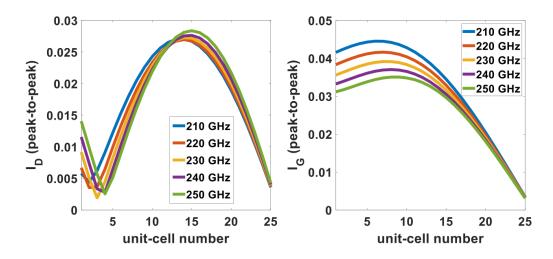

The distributed model applied in this research begins with connecting N unit cells of the small-signal equivalent model, shown in Fig. 1.2, to represent the whole width of the device. To decide on the value for N, the wavelength of the propagating signal is calculated and as a rule of thumb, the unit cell length ( $\Delta Z$ ) must be at least 10 times smaller than that. The source and boundary conditions are then incorporated into the distributed model. For analyzing the governing equations to find the voltage and current values at different operating frequencies, a

finite-difference time-domain approach is utilized. Initially, all the parameters are set to zero and then all the currents and voltages are updated at each time interval. Initially, the finite difference method was solved based on an explicit scheme, where the current was updated first and then the new value for the voltage was obtained based on that [8-9]. Since the explicit method is potentially unstable, to satisfy the Courant stability condition and the convergence of the proposed method, the temporal step size,  $\Delta t$ , was on the order of  $10^{-16}$  seconds. This value was very small and increased the computation time of the simulation.

In a later study, the proposed scheme becomes an unconditionally stable implicit method. All the currents and voltages are defined in a coupled set of equations and to obtain the solution, iterative or matrix techniques are utilized, starting from initial transient states to a final steadystate condition. The two governing relations in Equations (1.2) and (1.3) denote the behavior of the parameters on different lines and nodes and the implicit finite difference scheme is applied to them. The time step  $\Delta t$  for this scheme is on the order of  $10^{-13}$  seconds, which makes the computation time become much smaller than the explicit case.

$$V + RI + L\frac{\partial I}{\partial t} = V_s \tag{1.2}$$

$$I + GV + C\frac{\partial V}{\partial t} = 0 \tag{1.3}$$

#### 1.3.3 Simulation results and model validation

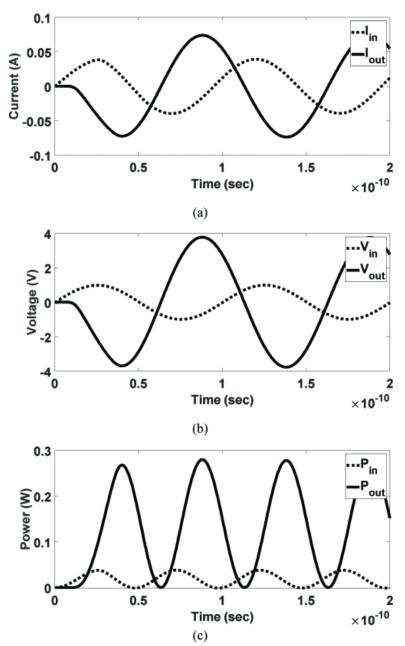

Fig. 1.3 (a) depicts the current in the input and output of the device. It is obtained for a  $\Delta Z$  of 20 µm and a temporal step size of 2e-16 seconds (explicit scheme). The input current is the gate current at the very first cell and the output is the current on the drain line of the last cell. The current gain of the device is 5.5 dB. As illustrated in this figure, it takes some time for the output current to start to have some values. This is the time at which the wave reaches the end of

the device and the calculated velocity using this time needs to satisfy the Courant condition if the solution is stable.

Fig. 1.3 Obtained results at the input and output of the device over time.

Similarly, Fig. 1.3 (b) and (c) show the input and output voltages and powers for the same analysis. The voltage gain and power gain are 11.7 dB and 17.2 dB, respectively. It is clear that the power gain is the sum of current and voltage gains. The proposed model here is merely a

small-signal model and will not be able to handle any DC or large signal analysis. Comparing the obtained current gain with the results in [10] signifies a good agreement mainly in higher frequency ranges (6-67 GHz).

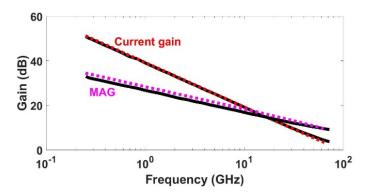

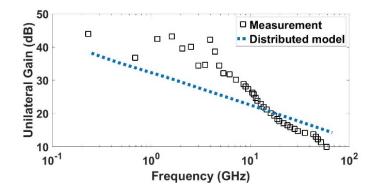

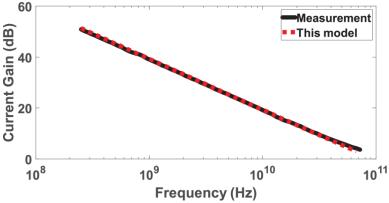

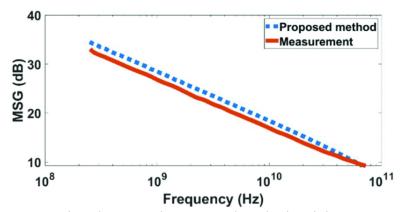

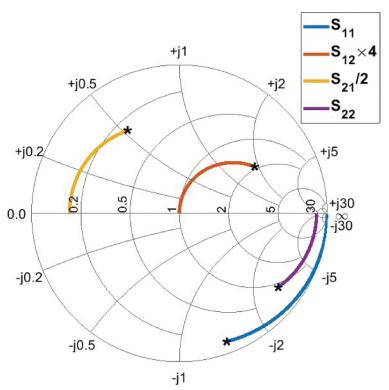

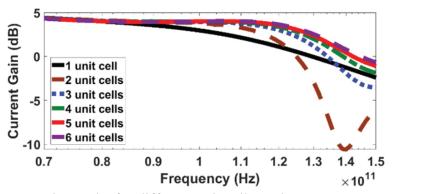

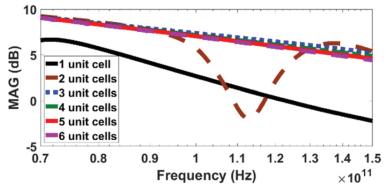

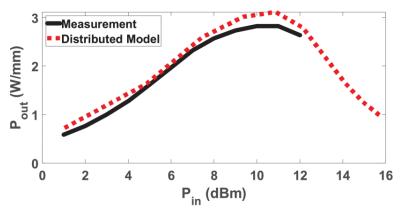

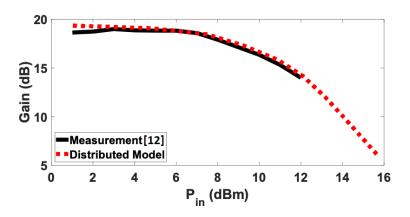

After developing the distributed model, the boundary conditions are applied based on the multi-finger configuration of the device and pad layouts. The small-signal results are obtained under 12 V and 500 mA/mm class-AB bias condition. Fig. 1.4 and Fig. 1.5 show the comparison between the simulation and measurement results for the  $2\times25 \ \mu m$  GaN MISHEMT device. The current gain (h<sub>21</sub>), maximum available gain (MAG), and unilateral gain (U) are obtained over the frequency range of 0.25-67 GHz. According to the device width and the maximum operating frequency, using two unit-cells is sufficient for ensuring that the wave propagation effects are included in the model. For the case of current gain, the load impedance is set to zero and for the MAG, the impedance at the output is matched to the circuit. For obtaining the U gain through simulation, the internal feedback is ignored in the circuit model. The obtained simulation results have a good agreement with the measurement results, which validates the proposed method in this research.

Fig. 1.4 Simulated (dashed) and measured (solid) current gain and MAG results over 0.25-67 GHz.

Fig. 1.5 Unilateral gain comparison results over 0.25-67 GHz.

For extending the small-signal model to the large-signal model, the values for the intrinsic elements need to be obtained for different bias points. Subsequently, the data points are incorporated in the FDTD code, and the results are obtained according to the applied input power. It is worth noting that the extrinsic elements will remain the same for different bias points and operating frequencies as they represent the electrode configurations and device pad layouts. The detailed explanation of how to account for the nonlinear effects and electromagnetic wave propagations, and how to solve the phase mismatch issues will be presented in Chapters 4 and 5.

#### 1.4 Optimized electrode design

The wave propagation effects and mismatch issues have a significant impact on how the devices are fabricated and operated. Here is an example where these effects are explained, and a solution is provided. The wavelength for a wave propagating in free space at 60 GHz is equal to 5 mm. However, for a guided wave operating at the same frequency inside a semiconductor device such as HEMT, since the propagation speed is almost one-third of that in free space, the guided wavelength becomes roughly 1.67 mm. If the device width is assumed to be equal to 0.3 mm, since the number is not smaller than at least one-tenth of the guided wavelength, this

dimension becomes comparable to it. As a result, the electromagnetic-wave propagation effects will be significant and there will be a phase velocity mismatch at the input and output ports of the device. In order to have a point of comparison, the value for the current gain of the mentioned device operating at 60 GHz is calculated, which is equal to 3.85 dB.

In order to assess and compare the effects of the mismatch on the device gain, the phase velocity is obtained on the gate and drain electrodes. First, the device is simulated in an even or gate excitation mode and the per-unit-width extrinsic capacitance on the gate line is calculated. Adding the capacitance from the intrinsic section of the model to this value yields the total capacitance for the even mode analysis. By incorporating the per-unit-width value for the gate inductance in Equation (1.4) the input phase velocity is calculated. Similarly, another simulation is conducted for analyzing the device in an odd or drain excitation mode condition and the extrinsic capacitance of the drain line is obtained and then added to the intrinsic value. Subsequently, the resultant capacitance and the drain inductance value is plugged in Equation (1.4) to obtain the phase velocity value on the drain conductor. Table 1.2 demonstrates the parameter values for the two analyses along with the obtained phase velocities.

$$\nu_{ph} = \frac{1}{\sqrt{LC}} \tag{1.4}$$

Table 1.2 Parameter values associated with calculating the phase velocity for the even/odd mode analyses.

| Electrode         | Extrinsic<br>Capacitance<br>(F/cm) | Total<br>Capacitance<br>(F/cm) | Line<br>Inductance<br>(H/cm) | Phase<br>Velocity<br>(cm/s) |

|-------------------|------------------------------------|--------------------------------|------------------------------|-----------------------------|

| Gate<br>(input)   | 1.21e-12                           | 1.04e-11                       | 2.58e-9                      | 6.10e+9                     |

| Drain<br>(output) | 8.26e-13                           | 2.95e-12                       | 4.48e-9                      | 8.70e+9                     |

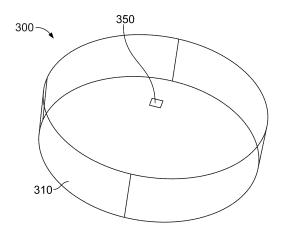

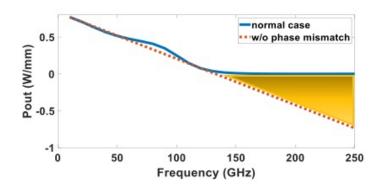

Clearly, there is a 43% phase velocity mismatch on the input, gate electrode, and output, drain electrode, which will affect the gain of the device. To improve the performance of this transistor, and other millimeter-wave transistors in general, the electrodes must be designed so as to provide matched phase velocities on the ports. In other words, the optimized electrode layouts will compensate for the mismatch in phase velocity induced by the intrinsic properties of the transistor. The proposed design approach in this work is to utilize the metamaterial concepts for redesigning the electrodes. The technique is to arrange the electrode layouts in some defined repeating patterns to enable the device to manipulate the electromagnetic waves. The transistors designed based on the new electrode configurations may be realized in wider fingers due to the matched phase velocities at the input and output ports. In other words, the electromagnetic-wave effects are compensated and the limitation of keeping the transistor width less than one-tenth of the guided wavelength is eliminated. Consequently, a much smaller number of wider devices will be capable of providing a certain power and the losses, discontinuities, and transistor footprint will be significantly reduced.

The proposed metamaterial concept is applied to the drain electrode in order to achieve a matched phase velocity at the input and output ports. The aforementioned even mode analysis procedure is utilized for the new design and the new values are obtained for the per-unit-width capacitance and inductance of the drain line. The new phase velocity on the drain conductor is calculated and the results are presented in Table 1.3. Evidently, the new drain phase velocity is identical to the phase velocity of the gate electrode. The current gain for the new design is calculated for the device with a width of 300  $\mu$ m and operating frequency of 60 GHz. This value increased by a factor of 130% compared to the conventional case and reached the value of 8.86

dB. Chapter 5 will explicitly explain how this approach is developed and an example of the electrode configuration will also be provided.

Table 1.3 Parameter values associated with calculating the phase velocity on the metamaterial drain electrode.

| Metamaterial   | Ietamaterial Extrinsic T |          | Line       | Phase    |

|----------------|--------------------------|----------|------------|----------|

| Electrode      | Capacitance Capacitance  |          | Inductance | Velocity |

|                | (F/cm)                   | (F/cm)   | (H/cm)     | (cm/s)   |

| Drain (output) | 1.39e-12                 | 3.51e-12 | 7.35e-9    | 6.22e+9  |

#### **1.5 Dissertation objectives and motivation**

One of the major challenges in developing systems for high-frequency applications is the lack of accurate, comprehensive, and universally satisfactory modeling approaches. To make sure that the systems in 5G and 6G technologies have the required efficiency to provide enough output in the designated frequency ranges, every aspect of the device operation must be optimized. This optimization is generally performed by the modeling approaches developed for transistors. However, the already developed approaches have several limitations. These models are mainly developed after the fabrication process and the measurement results are utilized in obtaining the model. This is probably the most important limitation with the available modeling approaches. The optimization must be performed before the fabrication stage to save money, time, and resources. Additionally, in mm-wave ranges, the models are generally developed for a specific device type and frequency range and if the operating mode changes, the model does not yield accurate results. Hence, there is a huge demand for modeling techniques that addresses the mentioned limitations.

The overall objective of this research is to develop a technique that can be utilized for modeling transistors regardless of the device type, operating mode, and frequency range. For this purpose, the technique needs to be based on the physical structure of the device to make sure that any device type can be modeled using this technique and the tool is available before the fabrication stage. Additionally, the model needs to include some physical phenomena, specific to the mm-wave frequency range, to make ensure that the developed approach is accurate independent of the operating frequency. Moreover, to make sure that the developed model is comprehensive, both the electrical and thermal properties of the device must be considered in the process.

#### **1.6 Dissertation organization**

This dissertation is organized into six chapters. Chapter 1 introduces the background, problems to be addressed in this research, preliminary results, and motivations and objectives. Chapter 2 explains the review of relevant literature for this research related to the device types, different modeling approaches, and their applications. Chapter 3 presents the thermal modeling procedure of the transistor along with a patented fabrication technique for enhancing the heat dissipation capabilities of the device. Chapter 4 discusses the developed small-signal model along with the device analysis and model validation process. Chapter 5 presents the large-signal analysis of the device, and a patented fabrication technique is also demonstrated which solves the device limitations for operating at higher frequency bands. Lastly, chapter 6 summarizes the research and presents the contributions and future work.

#### **1.7 References**

[1] S. Cheng, C. Li, C. Liu, and P. Chou, "Characterization and thermal analysis of packaged AlGaN/GaN power HEMT," 2011 6th International Microsystems, Packaging, Assembly and Circuits Technology Conference (IMPACT), 2011, pp. 195-197.

[2] A. Syed, M. J. Islam, S. M. Hasanuzzaman, A. K. Podder, M. S. Islam, and A. G. Bhuiyan, "Theoretical analysis of substrate effects on the DC performance of AlGaN/GaN high electron mobility transistor," 2016 5th International Conference on Informatics Electronics and Vision (ICIEV), pp. 961-966, 2016.

[3] G. Greczynski, J. Jensen, and L. Hultman, "CrNx Films Prepared by DC Magnetron Sputtering and High-Power Pulsed Magnetron Sputtering: A Comparative Study," *IEEE Transactions on Plasma Science*, vol. 38, no. 11, pp. 3046-3056, Nov. 2010.

[4] Y. Karisan, C. Caglayan, G. C. Trichopoulos and K. Sertel, "Lumped-element equivalentcircuit modeling of millimeter-wave HEMT parasitics through full-wave electromagnetic analysis," in IEEE Trans. Microw. Theory Techn., vol. 64, no. 5, pp. 1419-1430, May 2016.

[5] F. Y. Huang, X. S. Tang, Z. N. Wei, L. H. Zhang, and N. Jiang, "An improved small-signal equivalent circuit for GaN high-electron mobility transistors," in IEEE Electron Device Lett., vol. 37, no. 11, pp. 1399-1402, Nov. 2016.

[6] M. Guidry et al., "Small-signal model extraction of mm-wave N-polar GaN MISHEMT exhibiting record performance: analysis of gain and validation by 94 GHz loadpull," 2016 IEEE MTT-S Int. Microw. Symp. (IMS), San Francisco, CA, 2016, pp. 1-4.

[7] H. A. Wheeler, "Formulas for the skin effect," *Proceedings of the IRE*, vol. 30, no. 9, pp. 412-424, 1942.

[8] A. G. Avval and S. M. El-Ghazaly, "A new small-signal modelling approach for analyzing HEMTs over a broad frequency range," 2019 IEEE 62nd International Midwest Symposium on Circuits and Systems (MWSCAS), pp. 706-709, 2019.

[9] A. Ghadimi and S. Asadi, "Modelling of composite right/left-handed active multiconductor transmission lines (AMCTL) in time domain," *Int J Numer Model.*, 2018.

[10] X. Zheng et al., "High frequency N-polar GaN planar MIS-HEMTs on sapphire with high breakdown and low dispersion," 2016 Lester Eastman Conference (LEC), pp. 42-45, 2016.

#### Chapter 2

#### Heterojunction field effect transistors

Authors: Amirreza G. Avval, Emmanuel Larique, Samir M. El-Ghazaly

#### 2.1 Introduction

A FET is essentially a semiconductor current path whose conductance is controlled by applying an electric field perpendicular to the current. This field and the carrier density in the semiconductor channel are changed by a voltage imposed on a metal gate. The more electrons in the channel, the higher its conductivity and better performance is obtained from the transistor. Moreover, with the development of heterostructure science and technology, heterojunction FETs now offer potential advantages in microwave, millimeter-wave, and high-speed digital integrated circuit applications over the former homojunction devices [1].

Contrary to the conventional GaAs metal semiconductor field effect transistor (MESFET) which has been one of the most widely used device structures for microwave applications [2], heterojunction field effect transistors (HFET) are more mature semiconductor components of the new generation of III-V transistors. Different names are used for these devices signifying the underlying physical mechanism or structural configuration. Examples are high electron mobility transistor (HEMT), selectively doped heterojunction transistor (SDHT), modulation-doped FET (MODFET), and two-dimensional electron gas FET (TEGFET). For convenience, only the HEMT types will be covered in this chapter. Despite their different names, all these components are based on the same physical theory.

With the recent advancements in mobile communication applications, TV broadcasting, and satellite communications, microwave transistors and wide bandgap materials have been the area of focus for many research groups and these components play a critical role in many technology viewpoints. Table 2.1 presents the material properties of some microwave

semiconductors where the advantages of GaN semiconductor over its counterparts can be readily explained [3]. A high output power per unit width and high temperature operation require a semiconductor material with higher bandgap. This leads to fabricating compact devices that are easily matched when integrated with other circuit elements and the need for extra cooling will be either eliminated or reduced. For using a device in high power mode, a high voltage operation is necessary for the device, and this is fulfilled by using a material with high breakdown field. This will either reduce or completely eliminate the need for a step-down converter in devices. A high gain and high velocity are the two enabling features of the demand for a low noise device generally used in all types of receivers with a high dynamic range. Additionally, a high electron velocity in a HEMT topology will have a performance advantage of an optimum band allocation and it is required that the material used in the device indicate a high linearity and high frequency operation. All these demands and features make GaN devices be a reliable choice for many advanced operations [4].

| Material | Mobility | Dielectric Constant | Bandgap | Breakdown Field     | Tmax   |

|----------|----------|---------------------|---------|---------------------|--------|

| Si       | 1300     | 11.4                | 1.12    | 0.3*10 <sup>6</sup> | 300 °C |

| GaAs     | 5000     | 13.1                | 1.42    | $0.4*10^{6}$        | 300 °C |

| 4H-SiC   | 260      | 9.7                 | 3.2     | $3.5^{*}10^{6}$     | 600 °C |

| GaN      | 1500     | 9.5                 | 3.4     | $2.0*10^{6}$        | 700 °C |

Table 2.1 Properties of competing semiconductor materials [3].

There are many reports on GaN HEMTs operating at high frequencies as power amplifiers with high output power densities and power added efficiencies. Some high-power examples are 10.5 W/mm operating at 40 GHz [5], 13.7 W/mm at 30 GHz [6], and 41.4 W/mm

at 4 GHz [7]. Millimeter-wave N-polar GaN MISHEMT on SiC substrate with 6.5 W/mm power density operating at 94 GHz [8] and a 4.2 W/mm device at the same operating frequency fabricated on sapphire substrate [9] are also two reports on high frequency operations of GaN HEMTs.

#### 2.2 Passive and active characteristics of HEMTs

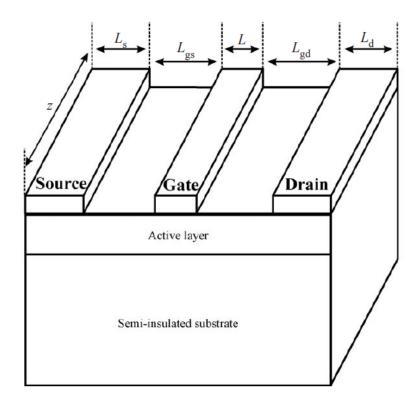

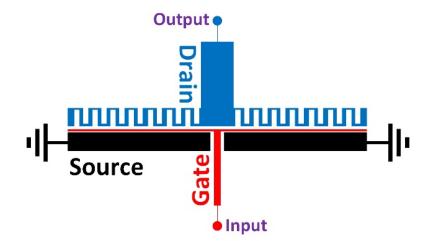

#### 2.2.1 Metallic passive structure

The cross-section of a HEMT is illustrated in Fig. 2.1. Three metal electrode contacts are made to the surface of the semiconductor structure. These contacts are named source, gate, and drain. The figure shows several important geometric dimensions: L, z, L<sub>gs</sub>, L<sub>gd</sub>, L<sub>s</sub>, and L<sub>d</sub>. The most important dimension that characterizes the HEMT physical structure is the gate length L. This dimension is critical in determining the maximum frequency limits for HEMT structures. The cutoff frequency ( $f_i$ ) is given by Equation (2.1), where  $v_s$  is the saturation velocity of the carrier. The gate width z affects the device performance significantly. It can vary from about 100 to 2000 times the gate length. The device current is directly proportional to gate width because the cross-sectional area available for channel current is proportional to z.

$$f_t = \frac{v_s}{2\pi L} \tag{2.1}$$

The range of these dimensions used in the fabrication of HEMTs is typically identical to that used in MESFET fabrication, so the physical layouts of HEMTs and MESFETs are usually identical [10]. For both MESFETs and HEMTs a transistor referred to as a  $4\times75$  µm device is composed of four gate electrodes, each being 75 µm wide. However, the important phenomena controlling the operation of MESFETs and HEMTs are different. Indeed, the HEMT structure is significantly more complex than the MESFET one. This complexity is associated with

fabrication difficulties, added costs, and lower yields. The primary motivation for pursuing such a structure is a notable improvement in the high frequency and power performance.

Fig. 2.1 A HEMT structure along with important dimensions.

#### 2.2.2 Intrinsic semiconductor structure

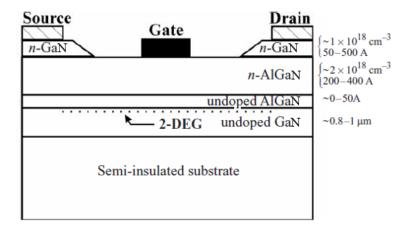

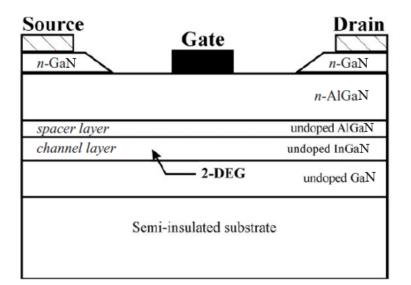

The heterojunction FETs are formed between semiconductors of different compositions, lattice constants, and bandgaps, such as AlGaN/GaN and InGaAs/InP. A schematic cross-section of a conventional n-AlGaN HEMT structure is shown in Fig. 2.2. Typical doping densities and thicknesses of the various epitaxial layers are indicated. The dimensions of both the n-type AlGaN and the undoped AlGaN spacer layer are critical in determining the device behavior. The idea of modulation doping is to separate the carriers from ionized impurities so that they can attain a mobility that is not affected by scattering phenomena due to crystal structure defects, lattice vibrations excited thermally, and impurities in the crystal [11]. To grow a device wafer,

several different layers are grown on a semi-insulating substrate: first, an undoped GaN layer, then an undoped AlGaN spacer, and finally an n-type GaN layer below the drain and source contacts.

Fig. 2.2 Layer structure of a conventional HEMT.

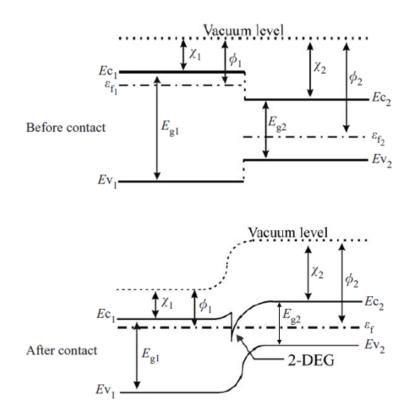

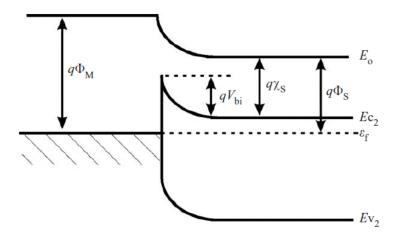

With this multilayered structure, electrons are naturally transferred from the upper doped n-AlGaN (higher bandgap) to the lower undoped GaN layer (lower bandgap), thus forming a two-dimensional electron gas (2-DEG) layer with a high sheet carrier concentration at the heterostructure interface. Since the conduction band edge of GaN lies below the donor states in AlGaN, free electrons diffuse out of the donor states of AlGaN into the donor states of GaN. The band diagrams of the two semiconductors, with their Fermi energies  $\mathcal{E}_{f1}$  and  $\mathcal{E}_{f2}$ , work functions  $\phi_1$  and  $\phi_2$ , electron affinities  $X_1$  and  $X_2$ , and bandgap energies  $E_{g1}$  and  $E_{g2}$ , are shown in Fig. 2.3, before and after the junction is made. The work function is the energy needed to excite an electron from the Fermi level into vacuum, while the electron affinity is the energy required to excite an electron from the bottom of the conduction band into vacuum.

Fig. 2.3 Electron energy band diagram before and after contact formation.

The resulting electron potential energy profile suggests how charge contributed by the dopant atoms transfers into the GaN layer just to the right of the heterojunction. The transferred electrons are confined to the GaN layer due to the energy barrier at the heterointerface. In the design of a FET this 2-DEG layer is used as the channel region. The sheet carrier concentration (n<sub>s</sub>) is controlled by the application of a potential at the metal Schottky barrier gate placed on the n-AlGaN layer. Increasing the negative bias applied to the gate decreases the depth (in electron energy) of the potential well at the AlGaN/GaN boundary. Note that in the MESFET, bias on the gate terminal controls the depth of the undepleted channel, while in the HEMT, gate bias controls the carrier density. However, both of these effects result in control of the maximum channel current [12].

The flow of channel current occurs via the drain and source ohmic contacts placed on either side of, and parallel to, the gate metallization. For low values of drain-to-source bias, a current flows from the drain to the source through the electron gas. In this case, the average velocity of carriers is linearly proportional to the field strength. This is demonstrated in Equation (2.2), where *E* is the electric field strength and  $\mu_n$  is the low field electron mobility. This mobility is usually a strong function of doping density. For high electric field values, when the drain to source bias level is increased, the steady-state carrier velocity becomes limited and the current levels saturate. The saturation current is determined primarily by the sheet carrier density of the 2-DEG that forms in the structure.

$$\nu = \mu_n E \tag{2.2}$$

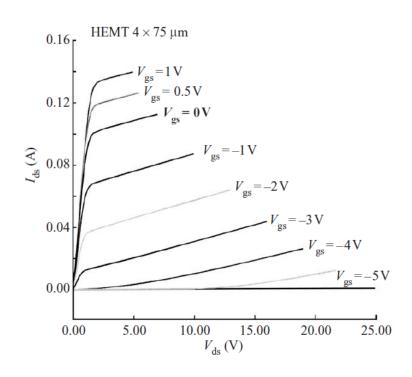

For this reason, an undoped AlGaN layer between the n-type AlGaN and undoped GaN is added [13]. This layer is referred to as a spacer layer and serves to separate the electrons flowing in the 2-DEG from the dopant ions in the wide-bandgap material. Without such a layer, electrons in the 2-DEG may collide with an ionized doping impurity. These collisions are termed scattering events and have the effect of temporarily randomizing the direction of movements for the particles. Then again, the electric field begins to accelerate the particles until the next scattering event occurs. This scattering reduces electron mobility and, therefore, diminishes the effect exploited in the device. Fig. 2.4 presents the classical I-V characteristics of a 4×75 µm HEMT.

So far only the conventional AlGaN/GaN HEMT has been considered. However, to obtain better noise and power performances, pseudomorphic HEMTs are now often used. One way of improving the performance of the HEMT is to use InGaN as the two-dimensional electron gas channel material instead of GaN. The benefits of using a thin InGaN layer as the pseudomorphic channel in a HEMT include the enhanced electron transport in InGaN compared with GaN, improved confinement of carriers in the quantum well channel, and the layer conduction band discontinuity at the AlGaN/InGaN heterointerface which allows even higher sheet charge density and, hence, higher current density and transconductance than is possible with an AlGaN/GaN conventional HEMT. As seen in Fig. 2.5, the GaN-based pseudomorphic HEMT differs from the conventional AlGaN/GaN HEMT in that a thin layer of InGaN is inserted between the doped AlGaN barrier layer and the GaN buffer. There is a lattice constant mismatch between the InGaN channel layer and the AlGaN donor and GaN buffer layers, but the strain from this lattice mismatch is taken up entirely in the thin InGaN quantum well.

Fig. 2.4 I-V characteristics for the conventional HEMT.

## 2.2.3 Schottky and ohmic contacts

Connections between the bulk semiconductor and other electrical components or equipment are established via a number of different types of semiconductor contacts. The properties of these contacts are as critical to overall device performance as the properties of the semiconductor.

Fig. 2.5 Layer structure of a pseudomorphic HEMT.

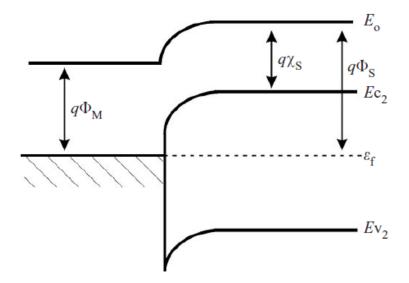

Schottky gate contact: These junctions are special cases of the more general class of metal-semiconductor contacts. The current-voltage characteristics of these junctions are very similar to that of a p-n junction, although there are important differences in the mechanism of current flow and carrier type participation. Both electrons and holes contribute to the current in p-n junctions, whereas Schottky diodes are unipolar devices. Fig. 2.6 shows the equilibrium band diagram of a metal of work function  $\phi_m$  and an n-type semiconductor of work function  $\phi_s$ . The electron affinity of the semiconductor, measured in energy from the edge of the conduction band to the vacuum level, is X<sub>s</sub> [14]. It is assumed that the Fermi level in the metal is lower than that of the semiconductor.

When a contact is made between the metal and the semiconductor, electrons are transferred from the semiconductor to the metal until the Fermi levels are aligned. The current in the metal-semiconductor contact under bias is determined by the flow of electrons from semiconductor to metal and vice-versa. When the metal is biased positively with respect to the semiconductor, the barrier from the semiconductor to the metal is lowered and the electron flow from semiconductor to metal is enhanced. Under reverse bias the barrier increases and the probability of an electron moving into the metal decreases. Finally, applying an appropriate bias voltage can effectively control the 2-DEG sheet charge concentration. Moreover, for an appropriately selected n-AlGaN thickness, the maximum 2-DEG sheet carrier concentration ( $n_{so}$ ) can be realized with the application of a gate bias voltage. It would maintain the borderline between the state of a complete depletion and the onset of the carrier conduction in the n-AlGaN layer under the gate electrodes.

Fig. 2.6 Electron energy band diagram for a Schottky contact.

**Ohmic drain and source contacts:** The electron energy band diagram for a metalsemiconductor junction with  $\phi_s > \phi_m$  is shown in Fig. 2.7. The electrical characteristics of an ideal ohmic contact are purely resistive in nature. This means that the current through the contact is linearly proportional to the voltage drop across it. Good ohmic contacts to semiconductor devices are essential for the realization of near-ideal device performances. The common technique to form reliable ohmic contacts is to heavily dope the region under the metal contact. It serves the purpose of preventing oxidation of the AlGaN layer and of reducing the parasitic source resistance by providing a conduction path parallel to the 2-DEG.

Fig. 2.7 Electron energy band diagram for an ohmic contact.

## 2.2.4 Fabrication of heterojunction FETs

These high-speed device structures are most commonly prepared by molecular beam epitaxy (MBE) or metal-organic chemical vapor deposition (MOCVD) because of the high degree of compositional and dimensional control coupled with the precise placement of donors. The HEMT material quality is affected mainly by impurities, defects, heterointerface roughness, and compositional mismatch strain. High material quality and optimal layer design are the keys to achieve good device performance. For a successful monolithic integration of digital or microwave HEMTs, surface morphology, layer thickness, and doping uniformity should also be well controlled.

The growth by MBE is accomplished under non-equilibrium conditions and is principally governed by surface processes. MBE is a controlled thermal evaporation process under ultrahigh vacuum conditions. It is achieved by the evaporation or sublimation of heated sources, such as aluminum, gallium, and arsenic, thereby forming molecular beams that impinge on a heated substrate such as GaN. The layer composition and doping level are controlled by the molecular beam fluxes and hence the temperature of the cells. The MOCVD growth technique has emerged as being technologically important for the production of single layers, heterojunctions, and quantum well structures with excellent control over layer thickness and doping and the achievement of hyper-abrupt isotype and anisotype junctions. The main advantages of MOCVD are high throughput and multilayer growth. Other than the MBE and MOCVD technologies, another technology for HEMT growth is metal-organic molecular beam. This new growth technique combines the advantages of MOCVD and MBE.

#### 2.3 New design of AlGaN/GaN HEMT

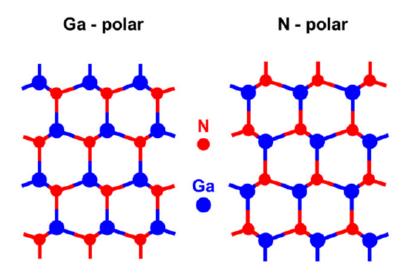

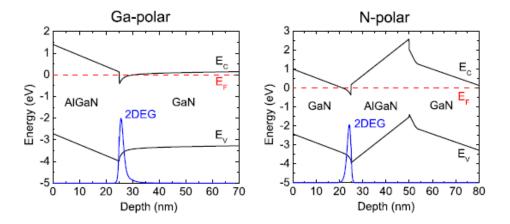

There are two different polarizations for a GaN crystal. Fig. 2.8 shows the atomic structure for N and Ga polarizations [15]. In N-polar heterostructures the electric field induced through the polarization is in the opposite direction of this field in Ga-polar configuration. This results in formation of a 2-DEG in the N-polar structure which is above the wide bandgap AlGaN shown in Fig. 2.9 [16]. In GaN HEMT structure with N polarity, the first layer of GaN will be deposited on the substrate to account for the buffer layer. The next AlGaN or AlN layer is the barrier layer and the other GaN layer comes on top as the channel layer. The reduction in effective gate-channel length is a result of fabricating the N-polar GaN HEMTs which leads to scaling shorter gate lengths. Additionally, as the channel layer has a narrower bandgap and low barrier to electrons, the contact to 2-DEG is made through here and a low contact resistance can be obtained [16]. Furthermore, the presence of AlGaN barrier reduces the short channel effects in N-polar devices.

Fig. 2.8 Atomic structure for Ga-polar and N-polar GaN [15].

Fig. 2.9 Energy band diagram of Ga-polar and N-polar heterostructures [16].

A new GaN HEMT design is presented in Fig. 2.10 [17]. The current is maximized by high mobility along with large electron densities. A layer of  $Al_xGa_{1-x}N$  is combined with a cap and a gate dielectric so as to minimize gate leakage and have a high breakdown voltage. The substrate used here is SiC with a good heat conductivity and mechanical strength. The intrinsic device performance is sometimes degraded in higher frequencies. This is mainly due to parasitic resistances formed at very thin gate lengths. Therefore, the gate in this configuration is made in a

mushroom or T shape configuration in order to increase the cross-sectional area that carries the current which results in the reduction in resistance. A higher power added efficiency and output power densities are obtained using this device compared to the conventional HEMT structures [17].

Fig. 2.10 The cross-section of a new N-polar HEMT design [17].

# 2.4 HEMT modeling

A great number of different semiconductor device models exist. The most usually employed is certainly the equivalent circuit model, which is based on the electrical performance of the device at its external terminals. There are two main advantages of equivalent circuit models. First, they are easy to implement in circuit design and analysis procedures. Most computer-aided design (CAD) tools used today can only accept circuit models because most models were initially developed to model the circuit's electrical properties at low alternating current or radio frequencies. The second, and the most important, advantage of equivalent circuit models is the computational efficiency. This is a very important factor, particularly for circuit optimization, where several simulation iterations are required for the analysis of large-scale integrated circuits. Some numerical methods have shown a good compatibility with most of these circuit models [18]. This topic has been thoroughly discussed and different approaches are evaluated throughout the chapters of this dissertation.

#### 2.4.1 Electrical equivalent models

Two types of models have been developed: small-signal and large-signal model.

**Small-signal model:** HEMT models provide a link between measured S parameters and electrical processes occurring within the device. From the section view in Fig. 2.11, which shows the physical origin of the circuit, we can obtain the model topology in Fig. 2.12, where each element provides a lumped element approximation to some aspects of the device. Although other circuit topologies involving additional elements have been described in the literature, this topology developed for microstrip technology has been shown to provide an excellent match to measure S-parameters through 30 GHz [19].

Basically, this conventional small-signal equivalent circuit can be divided into two parts: the intrinsic elements, which are functions of the biasing conditions, and the extrinsic elements that are independent of the biasing conditions. The transconductance,  $g_m$ , varies directly with the gain. It is a measure of the incremental change in the output current  $I_{ds}$  for a given change in input voltage  $V_{gs}$ , at constant  $V_{ds}$  (Equation (2.3)).

$$g_m = \frac{\partial I_{ds}}{\partial V_{gs}}\Big|_{V_{ds}=const}$$

(2.3)

Fig. 2.11 Physical origin of the equivalent circuit model for HEMT.

Fig. 2.12 Small-signal HEMT model.

The conductance,  $G_d$ , is a measure of the incremental change in output current  $I_{ds}$  for a given change in output voltage  $V_{ds}$ , at constant  $V_{gs}$  (Equation (2.4)).

$$G_d = \frac{1}{R_{ds}} = \frac{\partial I_{ds}}{\partial V_{ds}} \Big|_{V_{gs} = const}$$

(2.4)

The capacitances  $C_{gs}$  and  $C_{gd}$  model the change in the depletion charge under the gate with respect to the gate-source and gate-drain voltages, respectively (Equations (2.5) and (2.6)).

$$C_{gs} = \frac{\partial Q_g}{\partial v_{gs}} \Big|_{V_{ds} = const}$$

(2.5)

$$C_{gd} = \frac{\partial Q_g}{\partial V_{gd}}\Big|_{V_{gs}=const}$$

(2.6)

$C_{ds}$  takes into account the electromagnetic coupling between the highly doped regions under the source and drain contacts.  $R_i$  and  $R_{gd}$  represent the channel resistances.  $L_g$ ,  $L_d$ , and  $L_s$ arise primarily from metal contact pads deposited on the device surface. In microstrip technology  $L_s$  is due to via-holes.  $R_s$  and  $R_d$  account for the contact resistances of the ohmic contacts as well as any bulk resistance leading up to the active channel. The gate resistance  $R_g$  results from the metallization resistance of the gate Schottky contact.  $C_{pg}$  and  $C_{pd}$  are the pad capacitances of the HEMT and depend on the calibration measurements realized to characterize the transistor. Combined with  $L_g$  and  $L_d$  inductances, they provide a simple representation for the metal contact pads.

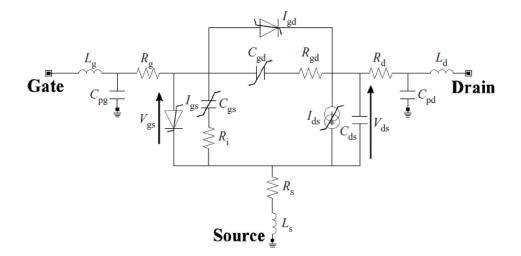

Large-signal model: The complete topology of the classical nonlinear model is shown in Fig. 2.13. Compared with the previous model in Fig. 2.12, several elements have been added or modified so as to take into account the bias dependency. The drain-source current,  $I_{ds}$ , is controlled by voltages  $V_{gs}$  and  $V_{ds}$  and is the main transistor nonlinearity. A mathematical function including adjustable parameters approximates some I-V measurements. A time constant  $\tau$  represents the electron transit time under the gate. Two diodes  $I_{gs}$  and  $I_{gd}$  characterize the input gate current. They are also modeled by analytical expression. On the other hand, reactive nonlinearities are extracted from S-parameter measurements.  $R_i$ ,  $R_{gd}$ ,  $\tau$ , and  $C_{ds}$  are usually independent of the gate and drain excitation voltages, while  $C_{gs}$  and  $C_{gd}$  are highly dependent on

the gate and drain excitation voltages, so it is very important to consider these elements to be nonlinear. These capacitances are mainly described by analytical model.  $C_{gs}$  and  $C_{gd}$  are controlled by voltages  $V_{gs}$  and  $V_{gd}$ , respectively.

Fig. 2.13 Large signal HEMT model.

For high-frequency applications, equivalent circuit models become increasingly complex to describe accurately the operation of the device. In most cases, the circuit elements have a strong dependence on operating conditions. The bias conditions, operating frequency, temperature, and signal level influence the values of equivalent circuit elements. This limits the usefulness of these models. Another major problem associated with equivalent circuit models is the fact that it is difficult to relate circuit element values to physical and process parameters, such as device geometry, doping profile carrier types, and mobility. Consequently, it is practically impossible to use equivalent circuit models to design and develop new types of devices. In these cases, it is necessary to use physics-based models.

Limitations of the electrical equivalent model: In all equivalent circuit models, there is an underlying assumption that separates the electronic physics inside the device from the electromagnetic wave propagation. While this assumption is acceptable at radio frequencies and the lower end of microwave range, it is no longer obvious at the high end of the microwave frequency range and the millimeter wave range for several reasons:

- (I) Device dimensions become comparable with the electromagnetic wavelength and distributed effects due to wave propagation become important and must be accounted for in the model. This can be achieved only with a full-wave modeling technique.

- (II) The electromagnetic wave period becomes of the same order as the charge carrier transit time and relaxation times. Consequently, the coupling between the electromagnetic wave and the charge carriers becomes important in carrier transport and the transient response of the devices.

- (III) Under large-signal operation conditions, time-varying fields can be large compared to DC bias fields. The wave-particle interaction is highly nonlinear and involves multi-frequency conversion and the generation of several harmonics. Hence, accurate analysis of circuit-device interactions requires simulations over very wide frequency bands in order to detect all the relevant harmonics content that affects the circuit performance. This reinforces the need for full-wave electromagnetic device models.

#### 2.4.2 Physics-based models

In contrast to equivalent circuit models, physical models are based on the physics of carrier transport inside the device. These models can provide better insight and understanding of the device operation under different operating conditions. Physical models also provide a link between physical and process parameters (doping profile, gate length, recessed gate depth, etc.) and electrical performance parameters (DC characteristics, RF transconductance, junction capacitances, etc.). For these reasons, physical device models should be essential tools, not only in the development of new devices, but also in performance and yield optimizations of microwave circuit design. The major limitation of such models, however, is that they are computationally intensive, preventing their direct use in circuit design. In most cases, it is inevitable to introduce simplifying assumptions in order to make the model computationally tractable.

The most commonly used physics-based models can be classified into two categories: particle-based models and fluid-based or hydrodynamic models. The first category is represented by the Monte-Carlo technique. The second is based on a set of conservation or continuity equations that can be derived from the Boltzmann transport equation (BTE). These models usually involve several approximations that vary from the simplest to the more complex: analytical models, drift-diffusion models, energy models, and full-hydrodynamic models. Up until the 1970s semiconductor devices were well modeled with the drift-diffusion transport approach. This approach includes a drift velocity controlled by the electric field and carrier diffusion density gradients. In a spatially homogeneous system, it reduces to Ohm's law for low electric fields. It assumes that the microscopic distribution of momentum and energy over the charge carriers at any location and time inside the device is equal to which one would find in a large sample with a DC field equal to the local instantaneous field.

The assumptions in the drift-diffusion model, however, break down for submicron devices, where carrier transport is predominantly nonstationary. For small-signal devices with gate lengths of less than  $0.5 \ \mu m$  nonstationary transport effects, such as hot electron effects and

39

velocity over-shoot, become very important and must be accounted for in the device model. Semi-classical device models have been developed to include energy and momentum relaxation effects while at the same time providing computationally efficient models. These models deal with charge carriers as classical particles whose motion properties, such as effective mass and scattering effects, are derived from quantum models.

Attempts to develop simpler models that can take into account the nonstationary effects such as velocity over-shoot have culminated in the formulation of the hydrodynamic model. This model consists of the set of coupled and highly nonlinear conservation equations derived from the zero, first, and second order moments of the Boltzmann transport equation. An alternative to these previous models is a full-wave electromagnetic analysis of the passive distributed metallic part of the transistor combined with a physics-based device simulation used to characterize the active contribution of the component. This approach is known as the global modeling of circuits.

## **2.5 HEMT applications**

The main characteristics of HEMTs are:

- high electron mobility

- small source resistance

- high cutoff frequency  $(f_t)$  due to high electron velocity in large electric fields

- high transconductance due to small gate to channel separation

- high output resistance

- high Schottky barrier height due to deposition of Schottky metal on AlGaN instead of on GaN

By using these characteristics engineers have developed a great number of microwave circuit applications. A list of applications where heterojunction FETs have enabled some improvements is discussed below:

- Low-noise and small-signal amplifiers (LNA) are circuits designed to operate as linear gain blocks, with specific requirements determined by their location within the system. They are typically operated at input power levels well below power saturation and may keep the overall system noise figure small [20].

- Power amplifiers are typically used in communication systems to provide sufficient signal power to allow transmission from one site to another. They are usually designed for maximum efficiency rather than linearity or low noise.

- Oscillators are used to perform frequency conversion of a desired signal. To obtain extremely low noise HEMT oscillators, the dielectric resonator is integrated for stabilization [21].

- Mixers are three-port devices that function to convert an input RF signal in conjunction with LO signal to an intermediate signal IF. The IF signal may be either the sum or the difference between LO and RF signals. Ideally, a mixer performs this frequency conversion with perfect fidelity, without intermodulation distortion, with high isolation between all three ports and a low noise figure.

- HEMTs can also be used in a variable attenuator, which is defined as a two-port device that allows adjustment of the signal amplitude by application of an external voltage or current.

## **2.6 Conclusion**

The analysis of device performance and structural characteristics of high electron mobility transistors have been discussed in this chapter. Based on the available literature, GaN seems to be the reliable choice to be used as the active section in HEMT devices offering a high output power density, high operational frequency, and satisfactory power added efficiency. The typical thicknesses and doping densities for different layers are provided and the formation of contacts are explained. Layer growth methods are briefly discussed and a new HEMT device along with the structural modifications is described. Furthermore, a small-signal model is depicted to account for the equivalent circuit in a frequency range lower than 30 GHz. The limitations for the small-signal model are also explained and a description of physical-based models are presented. Last but not the least, some general HEMT applications are discussed both for high and low operating frequencies. Performance characteristics reported in this article for microwave and millimeter-wave heterojunction FETs continue to improve. Minimum noise figures are reduced, while the frequencies of operation and maximum output powers are increased. These factors ensure that interest in HEMT will continue for a long time.

### 2.9 References

[1] F. Ali, A. Gupta, *HEMTs & HBTs: Devices, Fabrication and Circuits*, Artech House, 1991.

[2] M. Shur, GaAs Devices and Circuits, Plenum, New York, 1987.

[3] M. Golio, *RF and Microwave Semiconductor Handbook*, Ed. Boca Raton, FL: CRC, 2003.

[4] U. K. Mishra, P. Parikh, and Yi-Feng Wu, "AlGaN/GaN HEMTs-an overview of device operation and applications," *Proceedings of the IEEE*, vol. 90, no. 6, pp. 1022-1031, Jun 2002.

[5] T. Palacios *et al.*, "High-power AlGaN/GaN HEMTs for Ka-band applications," *IEEE Electron Device Letters*, vol. 26, no. 11, pp. 781-783, Nov. 2005.

[6] Y. F. Wu, M. Moore, A. Abrahamsen, M. Jacob-Mitos, P. Parikh, S. Heikman, and A. Burk, "High-voltage millimeter-wave GaN HEMTs with 13.7 W/mm power density," *IEEE IEDM Tech. Dig.* 405-407, 2007.

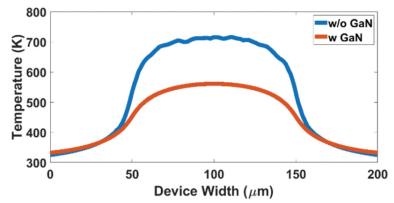

[7] Y. F. Wu, M. Moore, A. Saxler, T. Wisleder, and P. Parikh, "40-W/mm Double Field-plated GaN HEMTs," *Proc. 64th Device Res. Conf.*, pp. 151–152, 2006.