University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

5-2021

# Memory Module Design for High-Temperature Applications in SiC CMOS Technology

Affan Abbasi University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Electrical and Electronics Commons, Engineering Physics Commons, and the Power and Energy Commons

#### Citation

Abbasi, A. (2021). Memory Module Design for High-Temperature Applications in SiC CMOS Technology. *Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/etd/3990

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact ccmiddle@uark.edu.

Memory Module Design for High-Temperature Applications in SiC CMOS Technology

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering with a Concentration in Electrical Engineering

by

Affan Abbasi King Saud University Master of Science in Electrical Engineering, 2014 Sir Syed University of Engineering & Technology Bachelor of Science in Electronic Engineering, 2008

### May 2021 University of Arkansas

This dissertation is approved for recommendation to the Graduate Council.

H. Alan Mantooth, Ph.D. Chair

Jia Di, Ph.D. Committee Member Zhong Chen, Ph.D. Committee Member

Jeff Dix, Ph.D. Committee Member

#### Abstract

The wide bandgap (WBG) characteristics of SiC play a significant and disruptive role in the power electronics industry. The same characteristics make this material a viable choice for high-temperature electronics systems. Leveraging the high-temperature capability of SiC is crucial to automotive, space exploration, aerospace, deep well drilling, and gas turbines. A significant issue with the high-temperature operation is the exponential increase in leakage current. The lower intrinsic carrier concentration of SiC (10<sup>-9</sup> cm<sup>-3</sup>) compared to Si (10<sup>10</sup> cm<sup>-3</sup>) leads to lower leakage over temperature. Several researchers have demonstrated analog and digital circuits designed in SiC. However, a memory module is required to realize a complete electronic system in SiC that bridges the gap between data processing and data storage. Designing memory that can process massive amounts of data in harsh environments while consuming low power opens doors for future electronics.

A novel static random-access memory (SRAM) cell is designed and implemented in a SiC 1  $\mu$ m triple well CMOS process for high-temperature applications in this work. The prevalent issues encountered during SiC fabrication and the uncertainties in device performance led to 6T SRAM cell design modifications that enable adaptability to the worst and the best cases. However, design trade-offs are made in the design size, the number of transistors, number of I/Os, and the cell's power consumption. The novel SRAM cell design mitigates the effect of poor p-type contacts after the device fabrication by controlling the cell's drive strength via an additional pull-up network. The design also includes two parallel access transistors and separate wordlines that control both access transistors. This individual control enables post-fabrication tunability in the cell ratio (CR) and the pull-up (PR) ratio of the cell. It also allows tuning the access transistors' effective width during a data read operation, and a data write operation, independently. Along with the SRAM cell

design, the conventional latch-based sense amplifier is also designed in the SiC CMOS process to realize the monolithic memory IC modules.

The SRAM cell performance is evaluated on the basis of static noise margin (SNM), write SNM (WSNM), read SNM (RSNM), leakage current, and read access time over a wide temperature range (25°C to 500°C) on three uniquely processed wafers. The noise margins measured on Wafer #2 show a lower leakage current of ~500 nA at 500°C with the supply voltage of 10 V. The SNM of 6.07 V is measured at 500°C with a 10 V of power supply. The read access time at 400°C is ~7.5 µs at a supply voltage of 10 V.

©2021 by Affan Abbasi All Rights Reserved

#### Acknowledgments

First and foremost, thanks to the ALLAH (The GOD), the Almighty, for HIS showers of blessings throughout my research and my life.

I want to express my deep and sincere gratitude to my research advisor, Prof. H. Alan Mantooth, for giving me the opportunity to do research and provide invaluable guidance throughout this degree. His critical thinking, vision, motivation, and dynamic personality have deeply inspired me. It was a great honor and privilege to work and study under his supervision. I would also like to thank him for his empathy and great sense of humor.

I want to thank my advisory committee members, Prof. Jia Di, Prof. Zhong Chen, and Prof. Jeff Dix, for their support and cooperation.

My completion of this research could not have been accomplished without the IC group members' support: Aminta, Arman, Asif, Asma, Ayesha, Maksud, Marvin, Sajib, and Robert. Thank you very much.

Thanks to Tobias, Alexander, Christian, Matthaeus from Fraunhofer-IISB for supporting and fabricating this work.

I am incredibly grateful to my father: Intikhab A. Abbasi, and my mother: Riffat Abbasi, for their love, prayers, caring, and sacrifices for educating and preparing me for my future. I am grateful to my parent's in-law for their continuous financial support and for building my career. Also, I express my gratitude to my brothers, sisters, brother-in-law, and sister-in-law for their support and valuable prayers. My special thanks go to my father-in-law Prof. Shuja Abbasi for the keen interest shown to complete this thesis successfully.

Finally, to my caring, loving, and supportive wife, Rubayya. Your encouragement when the times got rough are much appreciated and duly noted. My heartfelt thanks.

## Dedication

I dedicate this work to my daughter Manal and my rest of the family. Thank you so much. It could not have happened without you all.

| 1 | Table of Contents       1     Introduction |                                                      |                                      |    |  |  |  |  |

|---|--------------------------------------------|------------------------------------------------------|--------------------------------------|----|--|--|--|--|

|   | 1.1                                        | Background and Motivation1                           |                                      |    |  |  |  |  |

|   | 1.2                                        | Literature Review                                    |                                      |    |  |  |  |  |

|   | 1.3                                        | Research Objective and Problem Definition            |                                      |    |  |  |  |  |

|   | 1.4                                        | Key Contributions                                    |                                      |    |  |  |  |  |

|   | 1.5                                        | Overview of the Dissertation                         | ion                                  | 7  |  |  |  |  |

| 2 | Sta                                        | te of the Art: SiC-based Inte                        | egrated Circuit Technologies         | 9  |  |  |  |  |

|   | 2.1                                        | SiC Bipolar Integrated Circ                          | rcuit Technology                     | 9  |  |  |  |  |

|   | 2.2                                        | SiC JFET Integrated Circuit Technology9              |                                      |    |  |  |  |  |

|   | 2.3                                        | SiC CMOS Integrated Circuit Technology10             |                                      |    |  |  |  |  |

|   | 2.4                                        | Fraunhofer's SiC 1 µm CMOS 1P1M Process Technology10 |                                      |    |  |  |  |  |

|   | 2.5                                        | SiC Design Enablement11                              |                                      |    |  |  |  |  |

|   |                                            | 2.5.1 PDK Developm                                   | nent                                 | 11 |  |  |  |  |

|   |                                            | 2.5.2 Fabrication of 1                               | μm CMOS 1P1M Process Technology      | 13 |  |  |  |  |

|   |                                            | 2.5.3 SiC Circuit Desi                               | sign Approach for RUN #1             | 14 |  |  |  |  |

|   |                                            | 2.5.4 Characterization                               | n Results of SiC MOSFETs from RUN #1 | 14 |  |  |  |  |

| 3 | De                                         | sign of an SRAM in RUN #                             | #1                                   | 20 |  |  |  |  |

|   | 3.1                                        | Introduction to SRAM and                             | d Sense Amplifiers                   | 20 |  |  |  |  |

|   | 3.2                                        | SRAM Test Structures in F                            | RUN #1                               | 23 |  |  |  |  |

|   | 3.3   | DC & Transient Measurements                                      | 5 |

|---|-------|------------------------------------------------------------------|---|

| 4 | Th    | e Novel SiC SRAM Cell Design in RUN #23                          | 1 |

|   | 4.1   | Process Module change from RUN #1 to RUN #2                      | 1 |

|   | 4.2   | Proposed SiC SRAM Cell for RUN #2                                | 2 |

|   | 4.3   | High-Temperature Sense Amplifier Architectures                   | 4 |

| 5 | Te    | st-plan for SRAM & Sense Amplifiers3                             | 8 |

|   | 5.1   | Testplan for DC Characterization of the Memory Cell4             | 0 |

|   | 5.2   | Test-plan for the Sense Amplifiers4                              | 9 |

|   | 5.3   | Test-plan for the Transient Characterization of the Memory Cell5 | 0 |

| 6 | Re    | sults and Analysis5                                              | 4 |

|   | 6.1   | Static Noise Margin                                              | 4 |

|   | 6.2   | Read Static Noise Margin6                                        | 4 |

|   | 6.3   | Write Static Noise Margin6                                       | 8 |

|   | 6.4   | Data Retention Voltage7                                          | 0 |

|   | 6.5   | Transient Analysis7                                              | 5 |

| 7 | Co    | nclusions and Future Work8                                       | 3 |

|   | 7.1   | Conclusions                                                      | 3 |

|   | 7.2   | Future Work                                                      | 4 |

|   | Refer | ences                                                            | 5 |

|   | Appe  | ndix A8                                                          | 8 |

|   | Appe          | ndix B1                                 | 02 |  |  |  |  |  |

|---|---------------|-----------------------------------------|----|--|--|--|--|--|

| 1 | <b>B</b> 1    | B1500A Semiconductor Device Analyzer102 |    |  |  |  |  |  |

| 2 | Co            | nnection Guide10                        | 03 |  |  |  |  |  |

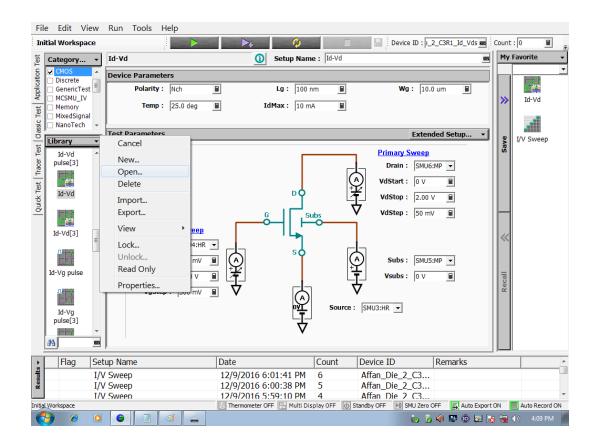

| 3 | EasyEXPERT103 |                                         |    |  |  |  |  |  |

|   | 3.1           | Application Test10                      | 04 |  |  |  |  |  |

|   | 3.2           | Edit Test Definition10                  | 05 |  |  |  |  |  |

|   | 3.3           | Classic Test10                          | 07 |  |  |  |  |  |

| 4 | Ex            | port Data1                              | 10 |  |  |  |  |  |

|   | Appe          | ndix C1                                 | 14 |  |  |  |  |  |

# List of Figures

| Fig. 1. Cross-section of a SiC NMOS device. The NWELL layer is an isolation layer between the PWELL and the P-type epitaxial layer |

|------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 2. Cross-section of a SiC PMOS device15                                                                                       |

| Fig. 3. Output characteristics of SiC NMOS at temperatures of (a) 25°C and (b) 300°C16                                             |

| Fig. 4. Output characteristics of SiC PMOS at temperatures of (a) 25°C and (b) 300°C16                                             |

| Fig. 5.(a)Transconductance variation over the temperature for NMOS (b)Transconductance variation over the temperature for PMOS     |

| Fig. 6. $I_{DS}$ vs $V_{GS}$ for PMOS with channel width = 20 $\mu$ m and channel length = 1.5 $\mu$ m                             |

| Fig. 7. 6T SRAM bit cell                                                                                                           |

| Fig. 8. Full complementary positive feedback sense amplifier                                                                       |

| Fig. 9. SRAM cell layouts25                                                                                                        |

| Fig. 10. SNM at 25°C and 300°C27                                                                                                   |

| Fig. 11. Half SRAM cell structure                                                                                                  |

| Fig. 12. Transient analysis of an SRAM Cell on the probe station at various temperatures30                                         |

| Fig. 13. Novel SiC SRAM cell for RUN #2                                                                                            |

| Fig. 14. Novel SiC SRAM cell layout in RUN #2                                                                                      |

| Fig. 15. Improved latch type sense amplifier                                                                                       |

| Fig. 16. Probe level measurements of an improved latch type sense amplifier                                                        |

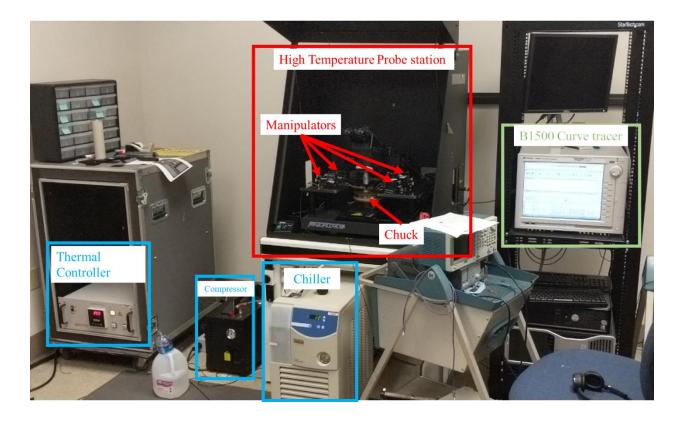

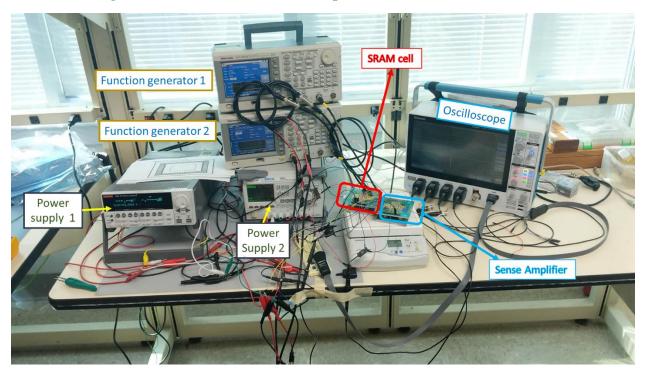

| Fig. 17. High temperature probe level test setup                                                                                   |

| Fig. 18. SNM testplan #1, VTC of the right side inverter40                                                                         |

| Fig. 19. SNM testplan #2, VTC of the left side inverter                                                                            |

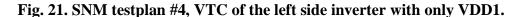

| Fig. 20. SNM testplan #3, VTC of the right side inverter with only VDD141                                                          |

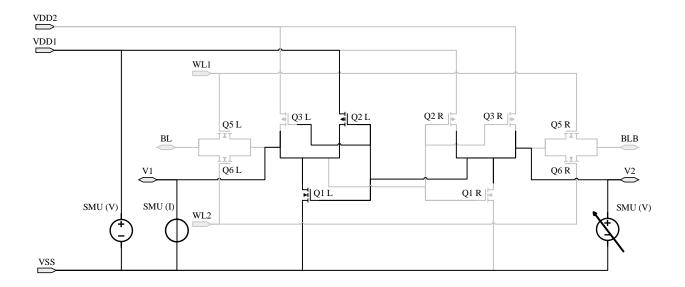

| Fig. 21. SNM testplan #4, VTC of the left side inverter with only VDD1                                                             |

| Fig. 22. SNM testplan #5, VTC of the right side inverter with only VDD2                                                            |

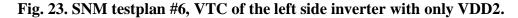

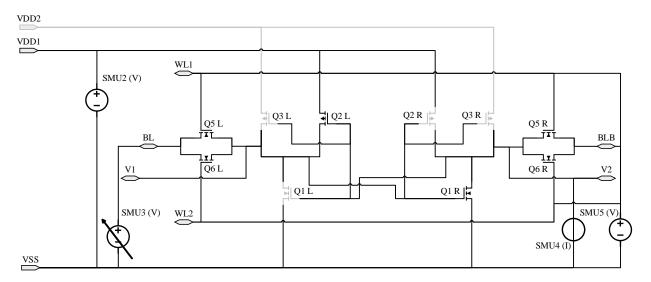

| Fig. 23. SNM testplan #6, VTC of the left side inverter with only VDD2          | 43 |

|---------------------------------------------------------------------------------|----|

| Fig. 24. RSNM testplan #1, right side with both wordlines active                | 44 |

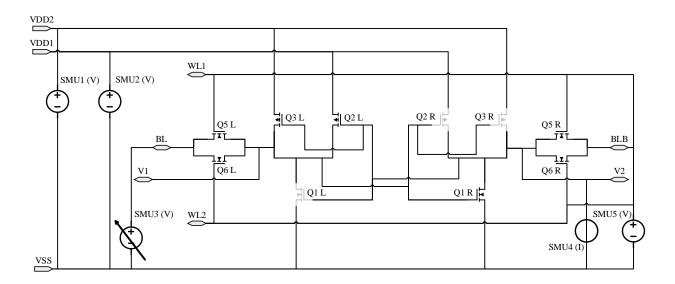

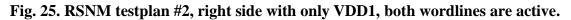

| Fig. 25. RSNM testplan #2, right side with only VDD1, both wordlines are active | 44 |

| Fig. 26. RSNM testplan #3, right side with only VDD2, both wordlines are active | 45 |

| Fig. 27. RSNM testplan #4, right side with only WL1 active.                     | 45 |

| Fig. 28. RSNM testplan #5, right side with only WL1 and VDD1 active             | 46 |

| Fig. 29. RSNM testplan #6, right side with only WL1 and VDD2 active             | 46 |

| Fig. 30. RSNM testplan #7, right side with only WL2 active.                     | 47 |

| Fig. 31. RSNM testplan #8, right side with only WL2 and VDD1 active             | 47 |

| Fig. 32. RSNM testplan #9, right side with only WL2 and VDD2 active             | 48 |

| Fig. 33. WSNM testplan #1, right side with both wordlines active                | 48 |

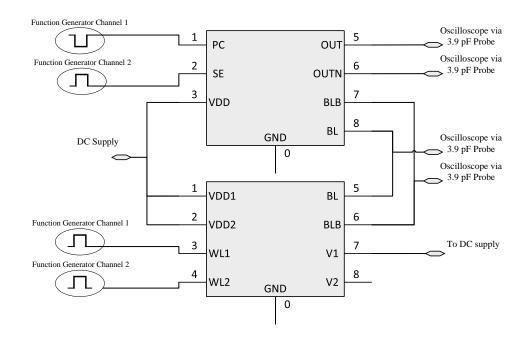

| Fig. 34. Test setup for conventional sense amplifier.                           | 49 |

| Fig. 35. Test setup for improved conventional sense amplifier                   | 50 |

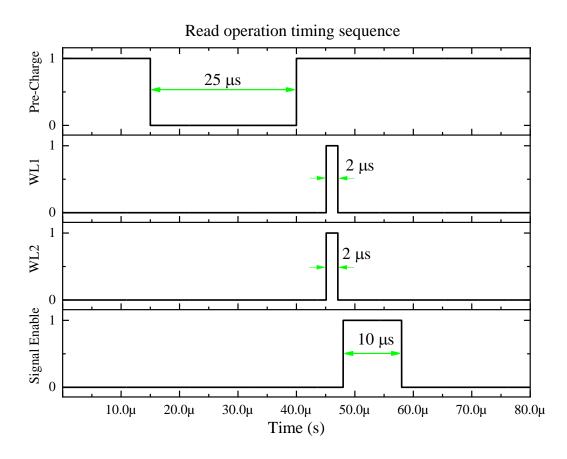

| Fig. 36. The timing sequence of the signals required for the read operation     | 52 |

| Fig. 37. The illustration of test setup for transient characterization          | 53 |

| Fig. 38. The actual test setup for transient characterization.                  | 53 |

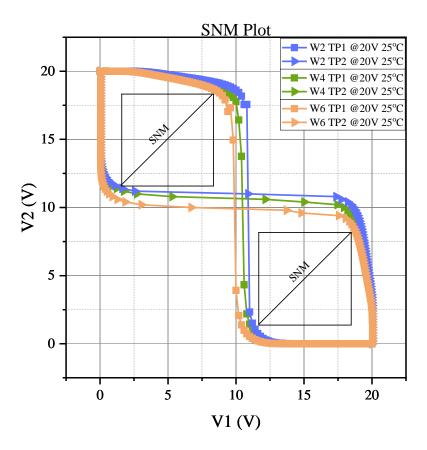

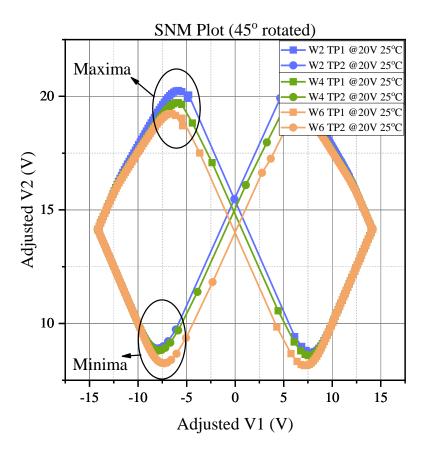

| Fig. 39. SNM plots from TP1 and TP2.                                            | 56 |

| Fig. 40. 45° rotated SNM plot.                                                  | 57 |

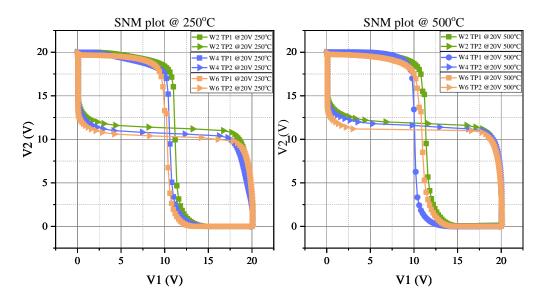

| Fig. 41. SNM plot at 250°C and 500°C.                                           | 58 |

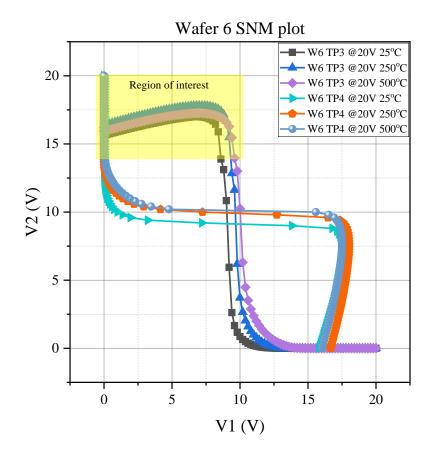

| Fig. 42. SNM plot from Wafer 6 at a wide range of temperatures.                 | 59 |

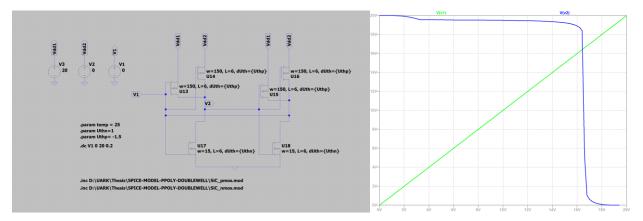

| Fig. 43. PMOS Output curve at 25°C from foundry provided model                  | 61 |

| Fig. 44. Testbench and VTC results from foundry provided SPICE models           | 61 |

| Fig. 45. Transformation of PMOS I-V to common coordinate set [34]               | 62 |

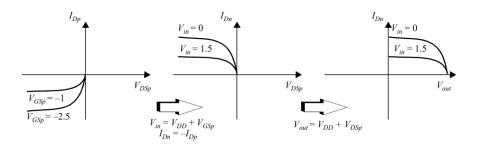

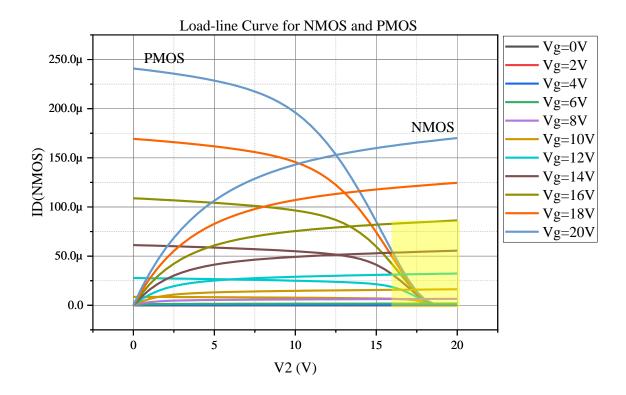

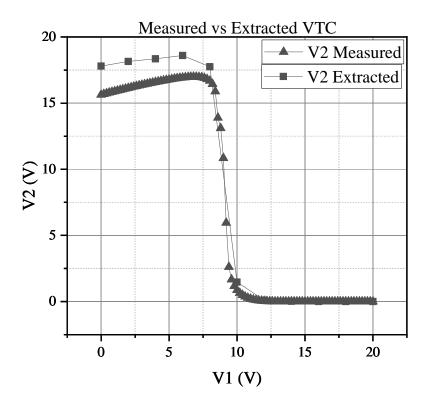

| Fig. 46. Load curves for NMOS and PMOS transistors. The yellow region represents the effect of poor p-type contacts in PMOS                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 47. Measured vs. Extracted VTC64                                                                                                                         |

| Fig. 48. RSNM illustration                                                                                                                                    |

| Fig. 49. RSNM plots (a) At 25°C (b) At 500°C67                                                                                                                |

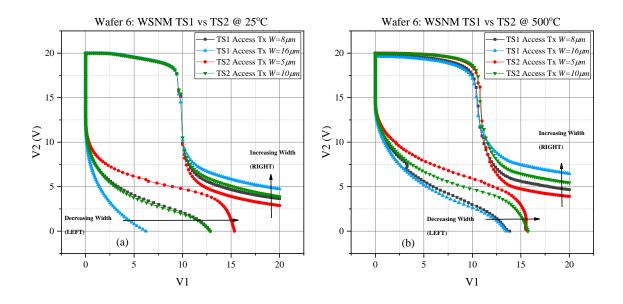

| Fig. 50. WSNM plots (a) At 25°C (b) At 500°C69                                                                                                                |

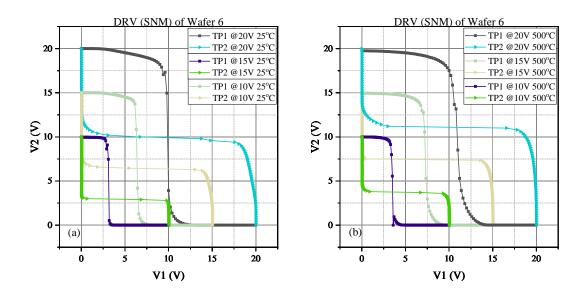

| Fig. 51. DRV (a) At 25°C (b) At 500°C71                                                                                                                       |

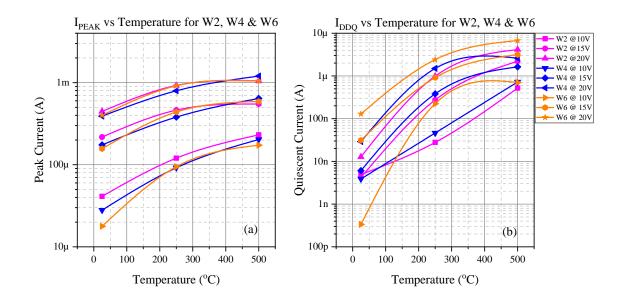

| Fig. 52. W2, W4, and W6 comparison between (a) I <sub>PEAK</sub> vs. Temperature and (b) I <sub>DDQ</sub> vs. Temperature                                     |

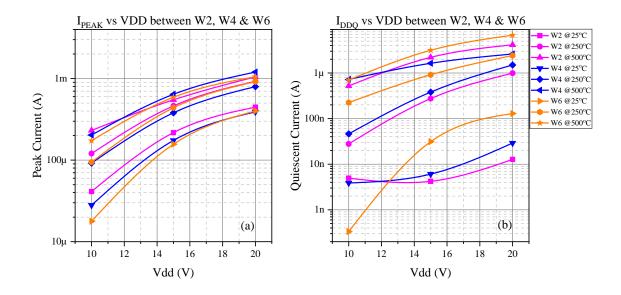

| Fig. 53. W2, W4, and W6 comparison between (a) IPEAK vs. VDD and (b) IDDQ vs.VDD73                                                                            |

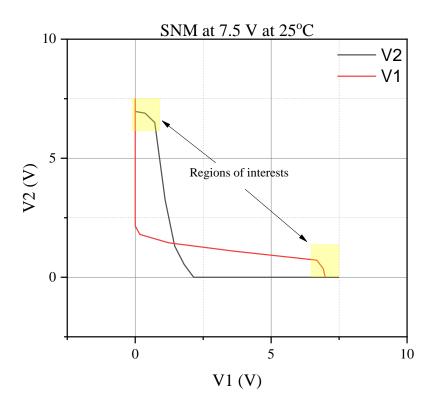

| Fig. 54. SNM from Wafer 2 at 7.5 V and 25°C74                                                                                                                 |

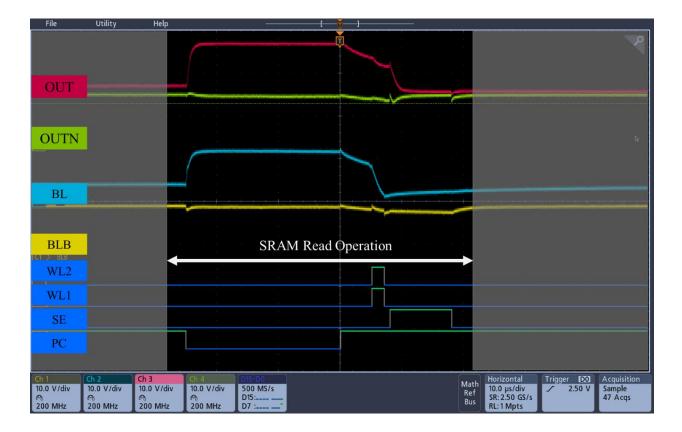

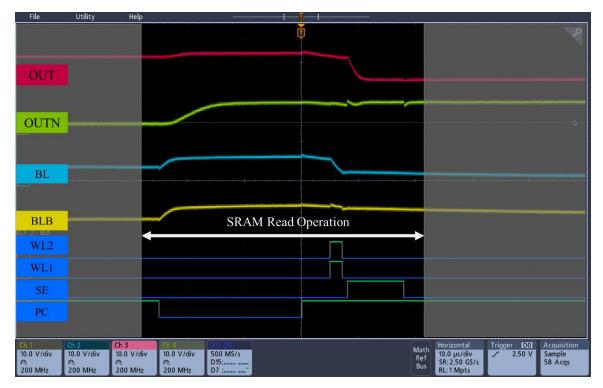

| Fig. 55. Reading logic '0' at VDD=10 V and Temperature=400°C                                                                                                  |

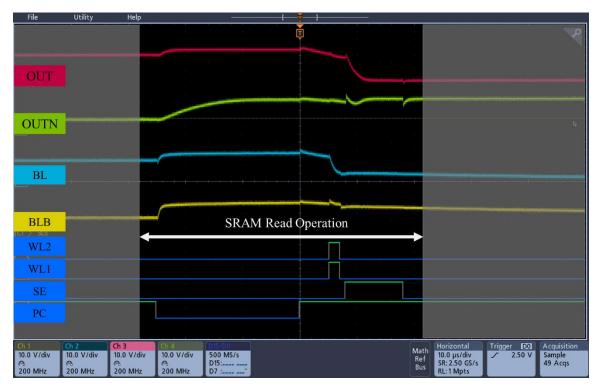

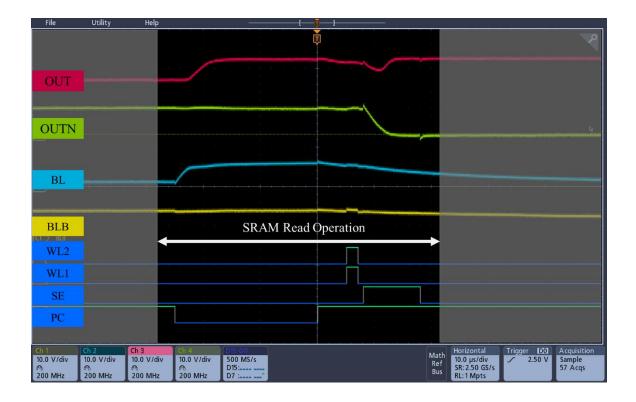

| Fig. 56. Reading logic '1' at VDD=10 V and Temperature=400°C                                                                                                  |

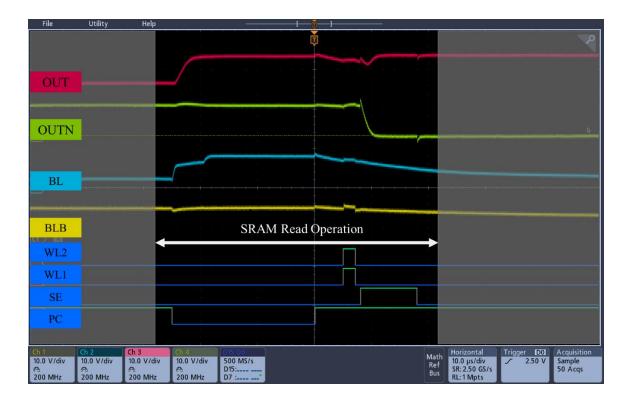

| Fig. 57. Reading logic '0' at VDD=7.5 V and Temperature=400°C                                                                                                 |

| Fig. 58. Reading logic '1' at VDD=7.5 V and Temperature=400°C                                                                                                 |

| Fig. 59. Reading logic '0' at VDD=6 V and Temperature=400°C78                                                                                                 |

| Fig. 60. Reading logic '1' at VDD=6 V and Temperature=400°C79                                                                                                 |

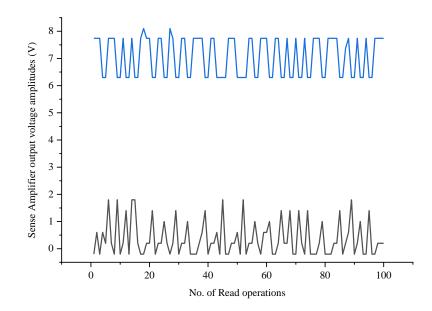

| Fig. 61. At VDD=7.5 V and temperature=400°C81                                                                                                                 |

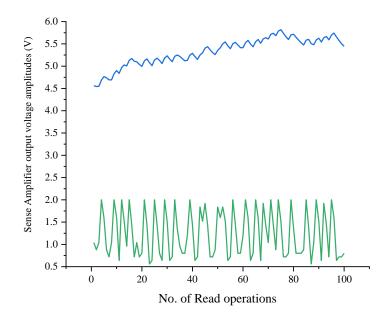

| Fig. 62. At VDD=6.5 V and temperature=400°C81                                                                                                                 |

| Fig. 63. At VDD=6 V and temperature=400°C82                                                                                                                   |

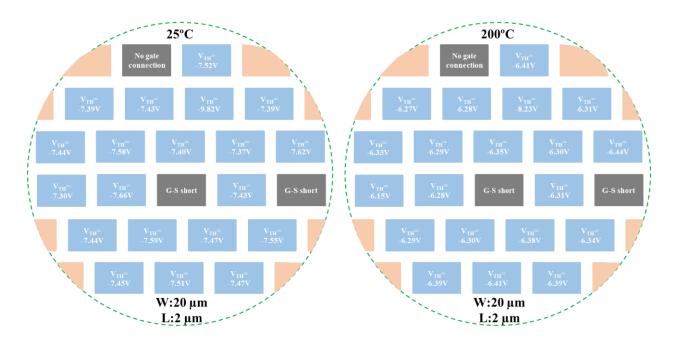

| Fig. 64. The NFET $V_{TH}$ wafer map at room temperature and for channel lengths of 1.5 $\mu$ m and 2 $\mu$ m. The width of each device tested is 20 $\mu$ m  |

| Fig. 65. The NFET $V_{TH}$ wafer map at 200 °C and for channel lengths of 1.5 $\mu$ m and 2 $\mu$ m. The width of each device tested is 20 $\mu$ m            |

| Fig. 66. The PFET $V_{TH}$ wafer map at room temperature and for channel lengths of 1.5 $\mu$ m and 20 $\mu$ m. The width of each device tested is 20 $\mu$ m |

| Fig. | 83. Edit test definition            | 106 |

|------|-------------------------------------|-----|

| Fig. | 84. Id-Vd test definition.          | 107 |

| Fig. | 85. I/V sweep classic test          | 108 |

| Fig. | 86. I/V sweep measurement tab       | 109 |

| Fig. | 87. To enable automatic data export | 111 |

| Fig. | 88. Test results data auto export   | 112 |

| Fig. | 89. Graph window                    | 113 |

# List of Tables

| Table 1. Si/SOI SRAM Cell Performance Comparison at High Temperatures             | 3  |

|-----------------------------------------------------------------------------------|----|

| Table 2. SiC SRAM Cell Performance Comparison at High Temperatures                | 5  |

| Table 3. The PFET to NFET Ratios for Various Channel Lengths and a Fixed Width of | •  |

| Table 4. The SNM and RSNM at CR=0.5                                               | 28 |

| Table 5. Wafer Split for 12 100 mm SiC Wafers for RUN #2                          | 32 |

| Table 6. Novel SRAM Cell Transistor Sizes                                         | 33 |

| Table 7. The Summary of the SNM Testplans                                         | 54 |

| Table 8. Temperature Dependency on SNM at VDD =20 V                               | 58 |

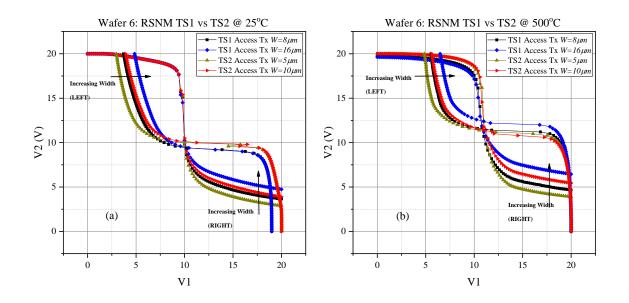

| Table 9. Summary of the RSNM Testplans                                            | 65 |

| Table 10. RSNM for Wafers 2, 4, and 6 at 20V with Varying Temperatures            | 67 |

| Table 11. Summary of the WSNM Testplans                                           | 68 |

| Table 12. WSNM for Wafer 2, 4, and 6 at 20 V with Varying Temperatures            | 70 |

| Table 13. DRV (SNM) at Varying Temperatures                                       | 71 |

| Table 14. Voltage Drop with Varying Supply Voltage                                | 75 |

| Table 15. Read Access Time at Varying Supply Voltage and Temperature              | 80 |

| Table 16 Sheet Resistances Comparison from RUN #1 and RUN #2                      | 97 |

| Table 17 Contact Resistances Comparison from RUN #1 and RUN #2                    | 97 |

#### **1** Introduction

#### **1.1 Background and Motivation**

Electronic systems capable of withstanding high temperature environments are in high demand in various applications such as logging-while-drilling (LWD) systems and embedded electronics which are in the core of gas turbine engine controls. Designing memory that can process massive amounts of data in harsh environments while consuming low power opens doors for next generation, smart, high temperature electronic systems.

Decades of research and development of wide bandgap (WBG) semiconductors has paved the way for implementation of these materials in high temperature, high frequency, high voltage, and radiation hardened applications. Silicon carbide (SiC) and gallium nitride (GaN) are the two most commonly used and produced WBG semiconductor materials. SiC has emerged as the most mature of the WBG semiconductors with the release of commercial 6H-SiC bulk substrates in 1991 and 4H-SiC substrates in 1994 [1].

Leveraging the high temperature capabilities of SiC ICs is crucial to automotive, aerospace, deep well drilling, and wireless telemetry systems [2]. Although building blocks for extreme environment data acquisition have been demonstrated in [3], a memory module is necessary to enable data storage and therefore a more robust electronic system. Therefore, this work highlights the design challenges of SiC CMOS monolithic ICs and the need of having a memory module that can operate at temperatures above 400°C along with its peripheral circuitry. The evolving nature of the SiC CMOS process and the resulting process variation encourages the design of a new memory cell. The Static Random Access Memory (SRAM) cell is designed by using a triple-well, 1 µm single poly, single metal (1P1M) SiC CMOS process fabricated at Fraunhofer IISB in

Erlangen, Germany. In addition, various sense amplifier architectures are designed and will be the focus of this work.

#### **1.2** Literature Review

The most prominent issue in conventional silicon based high temperature electronics is leakage current, which increases exponentially with temperature. SOI technology has been widely used for high temperature operation due to its lower leakage capability gained from the reduced junction area beneath the transistor as a result of the buried oxide layer, however, the maximum operating temperatures are limited to 300°C due to the same leakage problems. Therefore, high temperature electronics present a unique challenge to the design of CMOS logic and memory circuits. SRAM modules are the most important component in the modern high-performance System-on-Chips (SoCs) designed to operate at high temperatures. There is a strong market demand for such products. In 1996, Honeywell introduced the High Temperature Electronics products for commercial use, mainly targeting aerospace applications. They presented the world's first commercially available 32 kB SRAM module to operate at 225°C. In competition with Honeywell, Texas Instruments (TI) also launched a commercial product line for High Reliability Components for Extreme Environments which was initially targeting oil-drilling applications. Later on, the products advanced with the radiation hardness capabilities and also was used for space exploration applications. TI introduced the world's first 32 MB Flash memory module that can operate at 210°C. Commercially available products encourages the researchers to stretch the operating temperature range beyond 250°C. In [4], R. Cojbasic and Y. Leblebici showed the reliable operation for 6T SRAM up to 260°C. They realized 6T SRAM in 0.18 µm SOI CMOS process and proposed a D-Latch type 6T-SRAM cell. The proposed SRAM showed better operating frequency than the conventional SRAM over temperature with the tradeoff being the

extra transistors in the D-Latch. In 2013, Kim, et al. presented an 8T SRAM module operating at 300°C [5]. They used a 1 µm SOI CMOS process to realize the design. Due to the high leakage currents at high temperatures, read operations failed because the bitlines could not sustain the charging voltage. In order to mitigate this, they added a sensing margin enhancement technique in the sense amplifiers by having a current source node on the bitlines. In [6] and [7], temperatureaware low-voltage SRAM is demonstrated at 25°C to 300°C and realized in a 1 µm SOI CMOS process. Similar to [5], an increase in sensing margin is implemented with the dynamic control source node on the bitlines. Gogl, et al., [8] presented a 1kbit EEPROM to operate at 250°C, with the significance of this work being the integration of a floating gate process in the SOI technology, which the author called SIMOX technology. Tai-Hua, et al., [9] explained the leakage problems in a bulk silicon process and demonstrated a radiation-hardened SRAM design that can operate at 225°C. The article published from this thesis [10] is the first implementation of SiC CMOS-based 6T SRAM cell, the cell operated at 500°C. However, the fabrication challenges in SiC CMOS, especially low resistive ohmic contacts, have deteriorated the cell's performance. Table 1 compares the operating temperatures, maximum frequency, and total power consumption performances of the aforementioned high-temperature memory literature.

|                  | Honeywell | TI    | [4]                   | [4]                   | [5]                | [6]        | [7]         | [8]                           | [9]               | [10]                 |

|------------------|-----------|-------|-----------------------|-----------------------|--------------------|------------|-------------|-------------------------------|-------------------|----------------------|

| Process          |           |       | SOI<br>CMOS<br>0.18µm | SOI<br>CMOS<br>0.18µm | 1µm<br>SOI         | 1μm<br>SOI | 1µm<br>SOI  | 1.6μm<br>SIMOX<br>Technology  | Bulk Si<br>0.13µm | SiC<br>CMOS<br>1µm   |

| SRAM<br>Topology |           | Flash | D-<br>Latch           | 6T                    | 8T                 | 8T         | 8T          | EEPROM                        | 6T                | 6T                   |

| Тјмах            | 225°C     | 210°C | 275°C                 | 260°C                 | 300°C              | 300°C      | 300°C       | 250°C                         | 200°C             | 300°C                |

| f <sub>MAX</sub> | 20MHz     | 12MHz | 10MHz                 | 5MHz                  | 1MHz               | 1MHz       | 15MHz       | -                             | -                 | ~1kHz                |

| Ртот             | 100mW     |       | 410mW                 | 1120<br>mW            | 1mW                | 35.5<br>mW | 25.56<br>mW | -                             | -                 | 4.52 mW<br>@ 400°C   |

| Size             |           |       | -                     | -                     | 560µm <sup>2</sup> | -          |             | 1200µm <sup>2</sup>           |                   | 10792µm <sup>2</sup> |

|                  |           |       |                       |                       |                    |            |             | Additional<br>steps<br>needed |                   |                      |

Table 1. Si/SOI SRAM Cell Performance Comparison at High Temperatures

The conventional silicon CMOS process is prone to leakage currents at high temperatures. Leakage currents are comprised of diode diffusion currents, which are proportional to intrinsic carrier concentration ( $n_i$ ). The thermally generated carrier concentration exceeds that due to dopants, and control of carriers in the device is lost at sufficiently high temperatures. In Si, the bandgap decreases by 0.083 eV between 25°C and 300°C. These factors combine to raise the intrinsic carrier concentration in Si to approximately  $10^{16}$  cm<sup>-3</sup> at 300°C [9]. Due to these considerations, high bandgap semiconductors such as SiC and GaN are more suited for high-temperature operations. Research into SiC began with power electronics being the central focus. Power semiconductors made from silicon carbide are capable of withstanding voltages up to 10 times higher than ordinary silicon. This, in turn, has several implications for system complexity and cost. The proliferation of electronic products throughout the world means many types of devices that must operate in variable or harsh conditions, such as higher temperatures. Silicon carbide shines here as well. There has been a growing demand for high-temperature capable circuitry in a multitude of other applications.

SiC is particularly suited for these applications due to its intrinsic carrier concentration being approximately 19 orders of magnitude lower than silicon [11]. This leads to SiC transistors having lower leakage current than bulk silicon devices and is paramount in achieving hightemperature operation. The maximum operating temperatures of bulk silicon and silicon-oninsulator (SOI) are limited to approximately 150°C and 300°C, respectively [12], [13]. With SiC ICs, this boundary is extended to over 500°C for both analog and digital circuitry [14]-[16]. So far, there is no work other than [10] reported on the CMOS memory design and realization of SiC memory. However, literature surveys showed considerable interest in the SiC-based memory designs. An article published in Physics World in November 1992 [17] shows the promises that SiC memory can make for the future of electronics. Another article [18] describes the potential of SiC as a memory material by demonstrating the electronically-passivated SiC-SiO<sub>2</sub> interface. In 2018, Elgebra, et al., [19] validates the potential of developing memory architectures in the 4H-SiC BJT process. The authors proposed the 4T-SRAM cell and characterized the design with the help of models. Thus, no actual memory cell has been fabricated.

In [20], SiC JFET process technology with two levels of metal interconnects demonstrated a 4x4 SRAM array and  $\div 2/\div 4$  clock generator. The successful test for two SRAM chips proves that the SiC JFET technology is reliable at 500°C. However, the supply voltage requirements, including the positive voltage of 25 V and negative voltage of -25 V, make this technology less attractive. And, it is not easy to use this type of SRAM in existing electronic system approaches that are widely adopted and use CMOS technology. Similar to Table 1, a comparison of performance metrics is extracted from the SiC SRAM design literature as shown in Table 2.

| [19] [20]               |                               | [10]                   | This work                |                       |

|-------------------------|-------------------------------|------------------------|--------------------------|-----------------------|

| Process                 | SiC BJT                       | SiC JFET               | SiC CMOS 1 µm            | SiC CMOS 1 µm         |

| SRAM<br>Topology        | 4T                            | 6T with resistors      | 6Т                       | Novel 6T              |

| Tj <sub>MAX</sub>       | Тј <sub>МАХ</sub> 500°С 500°С |                        | 300°C                    | 500°C                 |

| <b>f</b> <sub>MAX</sub> |                               |                        | ~1 kHz                   | 133 kHz               |

| Ртот                    | NA                            | *12.125mW              | 4.52 mW @ 400°C Vdd=20 V | 2200 µW @ VDD=10 V    |

| Size                    | Simulated work                | *62128 μm <sup>2</sup> | 10792 μm <sup>2</sup>    | 31320 μm <sup>2</sup> |

Table 2. SiC SRAM Cell Performance Comparison at High Temperatures

\*Values are estimated from the given information & pictures in the article.

#### **1.3** Research Objective and Problem Definition

Fabrication of low voltage SiC ICs is an ongoing challenge. Due to the stronger bonds of SiC between silicon and carbon atoms, diffusion rates are very low. Therefore, the only option to add dopants in the wafer is to use ion implantation. Annealing is required as a subsequent step to repair the damage that occurs during ion implantation. Recursive ion implantation followed by annealing leads to permanent damage in parts of the SiC crystal structure that impacts the performance of a device. Processing of low resistance ohmic contacts is another challenge in SiC. Achieving high active p+-doping concentrations in 4H-SiC through ion implantation remains a challenge due to compensation with ion-implantation generated defects. The interface state between SiC/SiO<sub>2</sub> generates trapped charges in the conduction band of SiC, and due to this intermediate trapped charge the threshold of the device shifts significantly at room temperature and as well as at high temperatures. Also, due to the high energy ion implantation, the polysilicon must be deposited after the implants eliminating the opportunity to make a self-aligned device.

Designing a circuit in SiC to meet the certain specifications is difficult due to the fabrication challenges. Furthermore, the process characteristics changes from one fabrication run to another run given the lack of process control currently available in SiC. Threshold voltage variation that leads to unwanted transistor mismatch is a primary source for huge variation in voltage offsets in the differential pair of an operational amplifier, for example. Conventional silicon processes also deal with the threshold variation and other process related variations, but their impact is not as significant. Additionally, the process control and PDK support helps the designer to simulate the design over every possible corner with local and global variation parameters, along with Monte Carlo simulations.

This research's prime focus is to develop an SRAM memory module that can operate at high temperatures (>400°C) and consume low power. Due to the process variation and run-to-run changes in the SiC process, designing a circuit to meet the specifications is challenging. Therefore, an adaptable, robust SRAM cell is designed that can be tuned to particular performance metrics regardless of run-to-run changes and process variations. The SiC technology used in this work offers a high threshold PMOS (~7.5V), limiting the operating voltages to be higher than the

PMOS's threshold, which resulted in higher power consumption than expected. However, as the operating temperature increases, the threshold voltage drops for both PMOS and NMOS. Therefore, the SRAM design leverages this intrinsic effect, and careful sizing of the transistors with an informed estimation is determined to operate the memory at lower voltages of  $\sim 6$  V.

#### **1.4 Key Contributions**

The key contributions of this research as described in this dissertation are:

- Developed the SiC PDK, tailored to Cadence Virtuoso suite

- Developed physical design rule checks (DRC and LVS) codes, custom-built for Mentor Graphics CalibreDRC & CalibreLVS

- Device characterization to enable the SiC IC design efforts

- Design, implementation, and characterization of first SiC CMOS 6T SRAM cell

- Design, implementation, and evaluation of various sense amplifiers

- Design, implementation, and characterization of novel SiC SRAM cells to mitigate design challenges introduced by the SiC fabrication technology.

#### **1.5** Overview of the Dissertation

This dissertation is organized into seven chapters. Chapter 1 covers the motivation and the background of high-temperature memory design in SiC. This chapter also includes the literature review to give the readers insight into current technological development in high-temperature memory designs. The author concludes this chapter with the key contributions, problem statement, and research objective. Chapter 2 describes state-of-the-art SiC-based integrated circuit technologies, emphasizing the SiC integrated circuit process used in this work. Moreover, the design enablement in SiC, fabrication challenges, and the device characteristics are also

incorporated in this chapter. Following that, in Chapter 3, the first design of the SiC-based SRAM cell and various sense amplifier architectures are described. The shortcoming of the process technology used is addressed in Chapter 4 by developing the new SRAM cell that mitigates the fabrication challenges at the design level without going through another design cycle. Chapter 4 also includes the RUN #2 sense amplifier designs and their results. Chapter 5 defines the DC and transient testing methodology of the new SRAM cell and its testplan with the sense amplifiers. Chapter 6 contains the measurement results from multiple samples under various test configurations to successfully demonstrate the SRAM cell's functionality. Finally, conclusions and future work are given in Chapter 7. An Appendix contains device characterization results, the MATLAB code, and a brief B1500 tutorial written in the course of completing this work.

#### 2 State of the Art: SiC-based Integrated Circuit Technologies

#### 2.1 SiC Bipolar Integrated Circuit Technology

A SiC bipolar process for low voltage designs is being developed at the Electrum Lab at KTH in Stockholm, Sweden [21]. The developed bipolar process is completely ion-implantation free and therefore suffers less from surface interface traps. Emitter, base, and collector mesas are created by dry etching of CVD-grown epitaxial layers. The silicidation of contacts to P-type and N-type regions are performed in separate steps due to difficulty in forming a good ohmic contact in P-type SiC. This process only has NPN devices and no PNP device. The NPN devices exhibit a room temperature gain of approximately 100. However, the gain drops as temperature increases. The process has shown working analog and digital circuits above 500°C. The main weaknesses of the SiC BJT process are the excess standby power consumption and the lack of PNP transistors to realize complementary circuit designs. KTH is also working on developing a CMOS process but the PMOS devices have a very high threshold (currently ~ 22 V at the time of this writing). KTH also developed the process module to integrate ferroelectric materials into their CMOS process, which in future can be the basis of a memory cell.

#### 2.2 SiC JFET Integrated Circuit Technology

The SiC JFET technology reported in [22] and [23] has three primitive devices: the nonplanar depletion mode N-type JFET, a resistor (i.e., the N-type channel layer of a JFET), and a capacitor in between two metal layers. Circuits fabricated in this process are capable of operating at temperatures of up to 800°C and with reliable functionality for more than 1000 hours under bias at temperatures above 500°C [22], [23]. However, designing circuits in this technology specifically a memory cell, is challenging without the P-type device. Moreover, the need for a dual power supply, meaning positive and negative voltage output rails, is undesirable or infeasible in many applications. Also, the fabrication turnaround time for this process is over 1 year.

#### 2.3 SiC CMOS Integrated Circuit Technology

Cree began developing a 4H-SiC all-NMOS process as reported in [24]. Raytheon also started developing a CMOS process although it ultimately decided to close its foundry. As a result, SiC low power CMOS technology is still in the developmental phase and facing some daunting difficulties in the fabrication process. There are two main primary issues. First, the effective inversion-channel mobility is substantially lower than the theoretical value and secondly the thermally grown SiC-SiO<sub>2</sub> interface exhibits a higher density of interface states than a traditional silicon process. Due to these issues, SiC low power MOSFETs are prone to threshold voltage shifts, gate leakage, and gate oxide failures. Nevertheless, there have been many reports demonstrating the potential and usefulness of SiC CMOS IC technology. In comparison to the bipolar and JFET processes previously discussed, the SiC CMOS process is superior since it offers low power consumption and a full rail-to-rail output swing.

#### 2.4 Fraunhofer's SiC 1 µm CMOS 1P1M Process Technology

The SiC integrated circuits designed for this research are fabricated at the Fraunhofer Institute for Integrated Systems and Device Technology (Fraunhofer-IISB) in Erlangen, Germany. Fraunhofer-IISB focuses on developing lateral P-type and N-type MOSFETs that can operate at high-temperature where the conventional silicon process cannot operate. They developed a technology computer-aided design (TCAD) model to achieve their goal, but did not develop the process design kit (PDK) that is necessary to realize a complex circuit topology or even a circuit design with many transistors. Consequently, during this thesis research, work to develop a SiC PDK tailored to the Cadence Virtuoso platform and physical design verification rule checks for Mentor Graphics Calibre (DRC ad LVS) was required. As a result, two 20 mm × 15 mm reticles, each for 100 mm wafers, were designed over three years using this PDK and design rule checker. The PDK development effort also helped in increasing the device portfolio of Fraunhofer's technology.

#### 2.5 SiC Design Enablement

#### 2.5.1 PDK Development

Generally, semiconductor foundries generate the transistor and passive component models for each process for use in the IC design tools such as Cadence Virtuoso. Circuit designers use these models to design integrated circuits. Before submitting the design layout to the foundry, the layouts are verified for the technology-specific Design Rule Checks (DRC), Layout Vs. Schematics (LVS) checks, and Parasitics Extraction (PEX) simulations. The PDK combines all the device models and physical verification checks into a set of files. Thus, the designer uses the PDK to design, simulate, layout, and verify the design before releasing the chip for fabrication. The accuracy of the PDK, particularly the design verification, is considered crucial and increases the chances of a successful first-pass tapeout.

The design, simulation, and layout part of the Fraunhofer PDK is built for the Cadence Virtuoso platform. The physical design rule checks are tailored for Mentor Graphics tools: CalibreDRC and CalibreLVS. Cadence Virtuoso and Calibre tools allow interoperability; hence the PDK is set up to run Calibre tools under the Cadence Virtuoso environment. The design flow and the libraries and rules sets are created to support these two platforms. Following are the components of the PDK that were developed:

- A primitive design library (Cadence Virtuoso)

- Device parameters

- o PCells

- Symbols

- Technology data (Cadence Virtuoso)

- o Layer definition files, layer names, layer and purpose pairs

- Display attributes (Colors)

- Process constraints

- Physical Verification decks (Mentor Graphics: CalibreDRC and CalibreLVS)

- o DRC

- $\circ$  LVS

- Simulation models of primitive devices (HSPICE)

- o Transistors

- $\circ$  Diodes.

Fraunhofer provided the technology-specific design rules in an Excel sheet with the minimum dimensions and overlapping layer requirements for all seven layers of the process. The design rules translated into Standard Verification Rule Format (SVRF), a programming language for Mentor Graphics semiconductor design tools [25]. The technology file needed for Cadence Virtuoso to set up Fraunhofer technology's environment is created using a programming language called SKILL [26], [27]. The number of layers, display attributes, via layers, type of contacts, layer purpose, etc., are defined in the technology file.

Developing the PDK also helped extend the portfolio of the primitive devices, as the foundry was only focused on developing MOSFETs. With the help of PDK, several passive

devices, different laterally-diffused metal oxide semiconductor (LDMOS) structures, bipolar transistors (BJT), diodes [28], optocoupler structures, and electrostatic discharge (ESD) devices [30] were designed and tested successfully after the tapeout. Hence, the PDK development contributed to elaborating the true potential of the SiC technology and the capability to have higher density circuits for various applications.

#### 2.5.2 Fabrication of 1 µm CMOS 1P1M Process Technology

Fabrication of low voltage SiC devices is not as mature as conventional silicon technology. Due to the requirement of higher ionization levels for adding dopants, incomplete ionization at room temperature, and slow diffusion rates, SiC fabrication typically relies on ion implantation and annealing at a high temperature. "High-temperature annealing needs to be done after every implant that leads to unwanted crystal structure destruction in parts of the SiC wafer. In addition to these challenges, the existing manufacturing capabilities result in high wafer costs and a longer lead time for the delivery of fabricated SiC wafers. It should be noted that significant investments are being made to rapidly expand the manufacturing capacity."[28]

The fabrication started with the commercially available Cree N-type 4H-SiC wafers. At first, the P-type epitaxial layer is grown on the wafers. Subsequently, alignment marks were processed to align the subsequent masks with the wafer. A total of eleven masks were used to process the following layers: ALIGN, NWELL, PWELL, P+, N+, ACTIVE, POLY, POLYVIA, NOHM, POHM, and METAL. Wells and diffusion layers were deposited through ion implantation. After the implantation, the poly layer is patterned. Subsequently, the N+ and P+ ohmic contacts were formed on the wells to create a low resistance contact to the metallization layer. The P+ ohmic contact formation suffered from a high contact resistance; the foundry claimed

that it is due to the unintentional over-etching of the NWELL region. To provide a comparison, the measured resistivity of the N+ region is 0.0017 m $\Omega$ ·cm2 whereas the P+ region has a resistivity of 44 m $\Omega$ ·cm2, which is a significant increase for the same size contacts. This resulted in undesirable performance for the PMOS devices [28]. Thus, the foundation of this research was established to mitigate the impact of inadequately performing PMOS devices.

#### 2.5.3 SiC Circuit Design Approach for RUN #1

The RUN #1 circuits were designed from old Raytheon process models [29] because, at the time of RUN #1 tapeout, Fraunhofer did not have any device models. Instead, they provided SiC sample MOSFET devices having channel lengths of 3  $\mu$ m, 5  $\mu$ m, and 10  $\mu$ m with a fixed width of 100  $\mu$ m for each. To develop a basic MOSFET model, wide/long, narrow/long, wide/short, and narrow/short MOSFET dimensions are required [29]. The sample devices have an oxide thickness of 25 nm, and their processing modules are also different than the selected modules for RUN #1. Based on the sample die's measurement data, the PFET to NFET ratio is estimated to be 5:1. Coincidently, Raytheon's process also used a 5:1 ratio for the inverter. Therefore, the circuits in RUN #1 were designed with Raytheon's model. The intention of RUN #1 was primarily to characterize the Fraunhofer process and develop models for future fabrication tapeouts. It took Fraunhofer a year to return the fabricated wafers once the designs were delivered for fabrication.

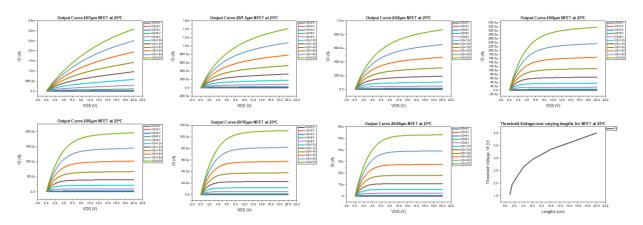

#### 2.5.4 Characterization Results of SiC MOSFETs from RUN #1

"The RUN #1 CMOS devices with varying widths and lengths were characterized over the temperature range of 25°C to 300°C. The Fraunhofer-IISB's SiC CMOS technology supports a minimum channel length of 0.8  $\mu$ m. However, the yield for smaller channel length devices was

heavily affected by the mask sets' misalignment. Therefore, the devices with smaller channel lengths (for example,  $0.8 \,\mu\text{m}$  and  $1 \,\mu\text{m}$ ) were not characterized.

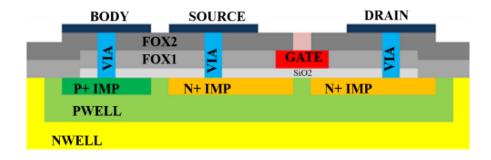

The cross-sections of the NMOS and PMOS devices are shown in Fig. 1 and 2, respectively. The NMOS device can be isolated by forming a PWELL inside an NWELL, as shown in Fig. 1. This isolation gives a designer the flexibility to cascode several NMOS devices while still connecting each device's body and source terminals. This eliminates the body effect and the corresponding threshold voltage increase.

Fig. 1. Cross-section of a SiC NMOS device. The NWELL layer is an isolation layer between the PWELL and the P-type epitaxial layer.

Fig. 2. Cross-section of a SiC PMOS device.

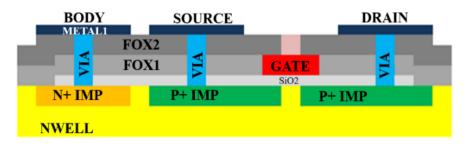

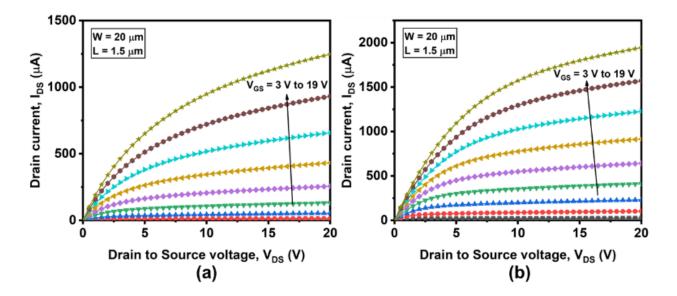

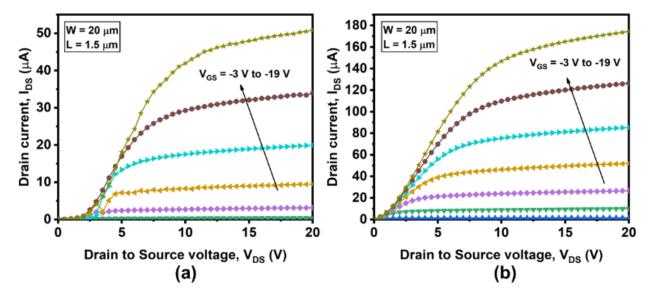

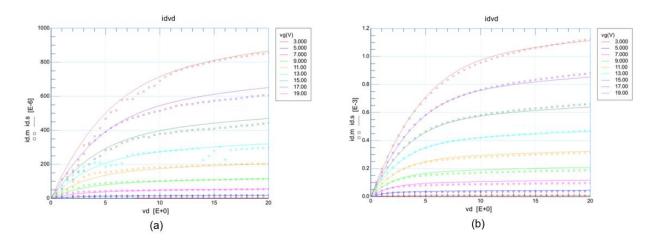

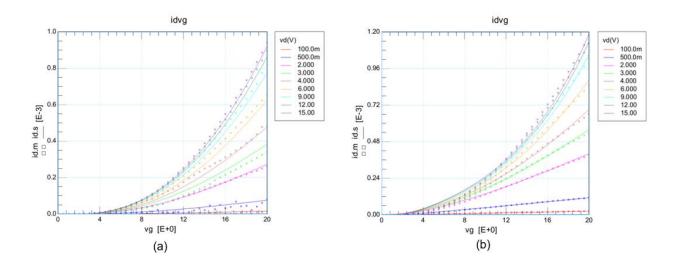

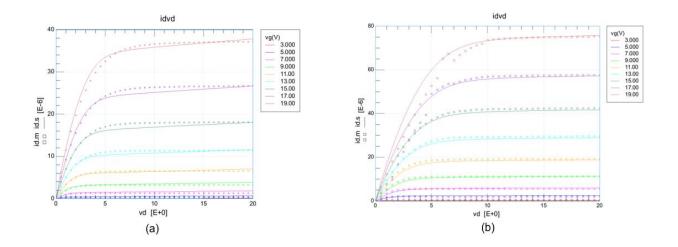

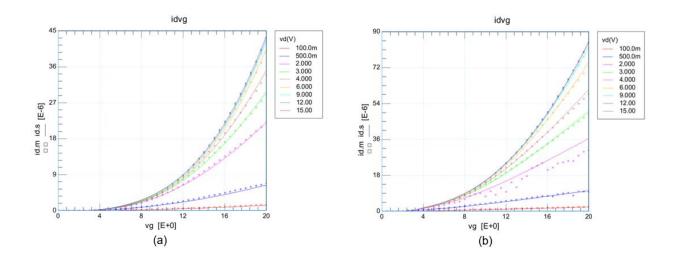

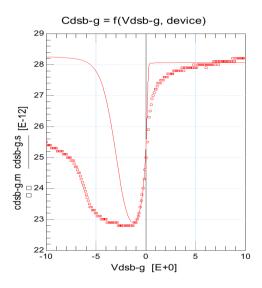

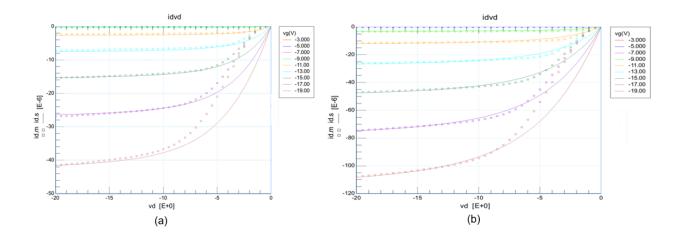

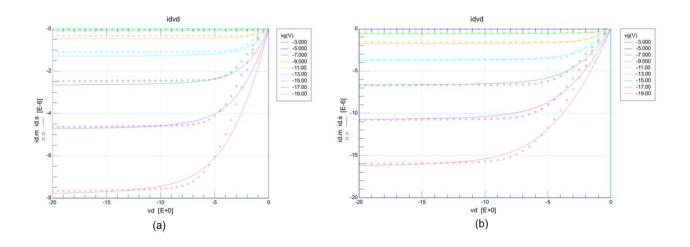

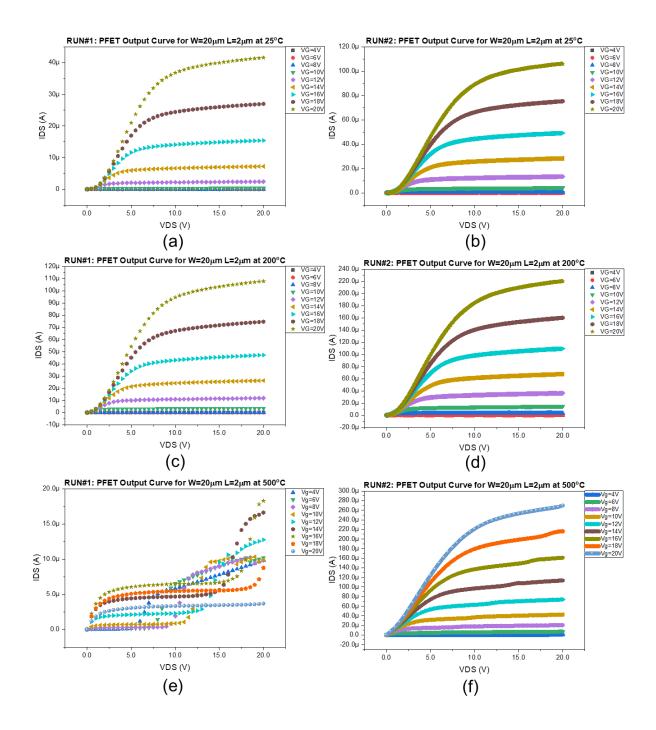

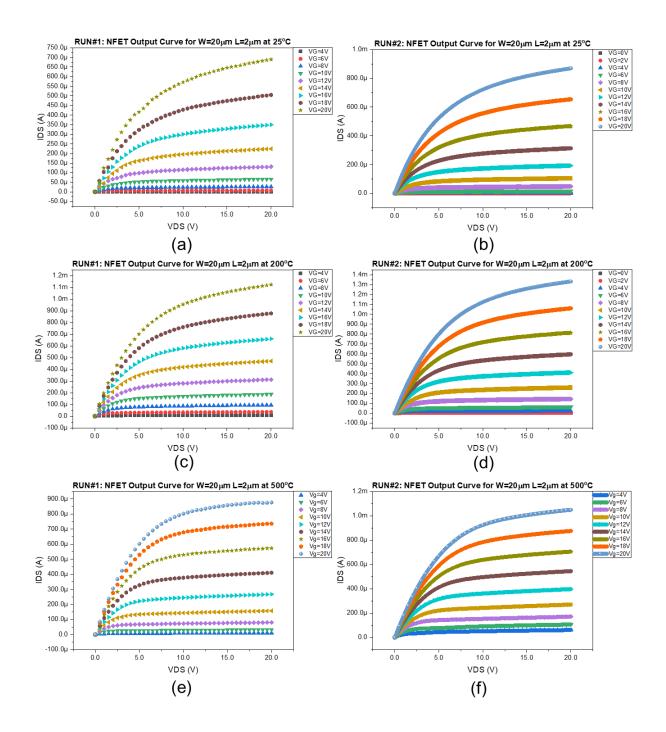

A channel width of 20  $\mu$ m is selected for representing the DC output characteristics and small-signal parameters of both the NMOS and PMOS transistors. Output characteristics of the SiC NMOS and PMOS devices are shown in Fig. 3 and 4, respectively. These devices have a channel length of 1.5  $\mu$ m. The drain-source voltage (V<sub>DS</sub>) is swept from 0 V to 20 V with a step size of 0.5 V with a gate-source voltage (V<sub>GS</sub>) varying from 3 V to 19 V with a step size of 2 V.

The drain current increases over temperature for NMOS and PMOS devices, which is due to increasing channel mobility and intrinsic carrier concentration. As previously mentioned, the P+ regions of PMOS drain and source contacts were over-etched during fabrication. Instead of forming an ohmic contact, a diode contact was formed, which can be observed from the linear region of the output characteristics plot shown in Fig. 4 for a PMOS device.

Fig. 3. Output characteristics of SiC NMOS at temperatures of (a) 25°C and (b) 300°C.

Fig. 4. Output characteristics of SiC PMOS at temperatures of (a) 25°C and (b) 300°C.

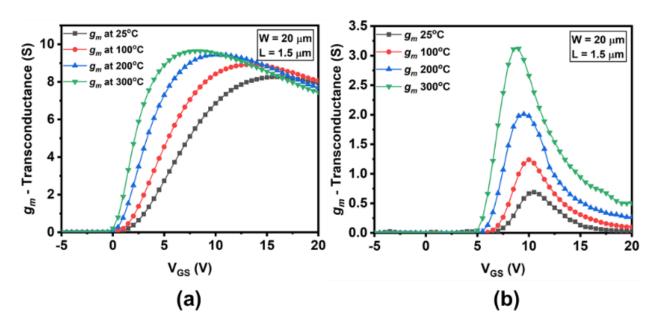

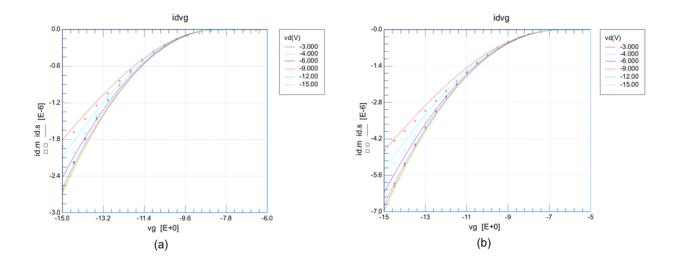

The transconductance  $(g_m)$  of NMOS and PMOS devices is shown in Fig. 5 (a) and (b), respectively. Measured results show the increase in  $g_m$  with the increase in temperature, which contradicts the conventional silicon-based MOSFETs. This inconsistency is primarily due to the thermally grown SiC oxide, which is prone to higher levels of interface state densities, charge trapping, and other effects. These interface trapped charges release additional carriers at higher temperatures, which cause an increase in the drain current. The  $g_m$  drops at higher V<sub>GS</sub> for both NMOS and PMOS due to reduced effective carrier mobility [31].

Fig. 5.(a)Transconductance variation over the temperature for NMOS (b)Transconductance variation over the temperature for PMOS.

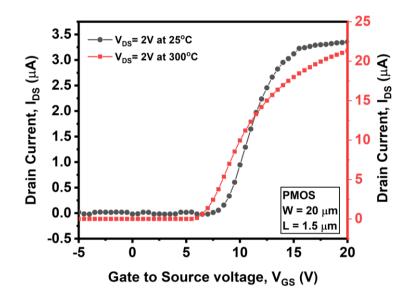

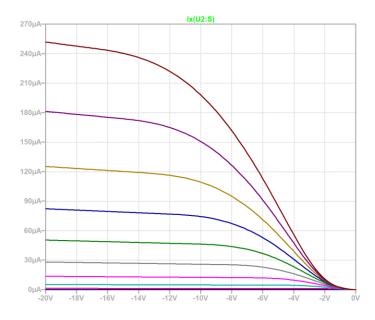

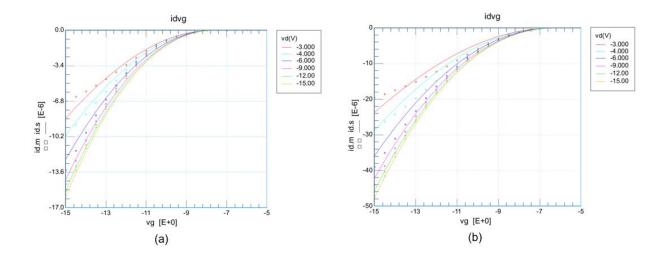

However, the drop in transconductance at higher  $V_{GS}$  is sharper for the PMOS devices than for NMOS devices. To better understand this behavior, the I<sub>D</sub> vs.  $V_{GS}$  (at  $V_{DS} = 2$  V) plot for the SiC PMOS are provided in Fig. 6. As  $V_{GS}$  increases above 8 V in Fig. 6, the drain current starts to saturate. This behavior is a result of the previously mentioned poor P+ contact formation during fabrication that results in the PMOS drain/source contacts having high resistance and limiting the drain current as  $V_{GS}$  increases." [28]

Fig. 6.  $I_{DS}$  vs  $V_{GS}$  for PMOS with channel width = 20  $\mu$ m and channel length = 1.5  $\mu$ m.

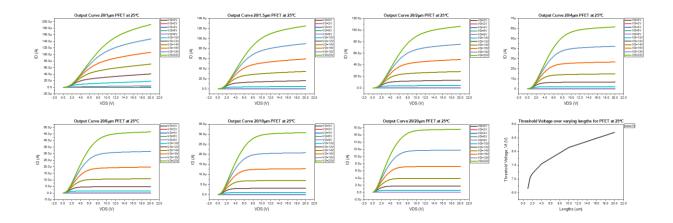

Due to the developing nature of Fraunhofer's SiC CMOS technology, the RUN #1 efforts revealed several issues related to the fabrication of different modules in the process. The resulting PFET to NFET ratio was 25:1 at room temperature for a 1.5  $\mu$ m channel length device. Table 3 shows the PFET to NFET ratio with increasing channel lengths. The PFET to NFET ratio decreased for larger device sizes, indicating that the contacts were the primary source of this issue.

| Table 3. The PFET to NFET Ratios for | Various Channel Lengths and a Fixed Width of |

|--------------------------------------|----------------------------------------------|

|                                      | 20 μm                                        |

| Temperature (°C) | Size (W/L) (µm) | PFET (µA) | NFET (µA) | Ratio |

|------------------|-----------------|-----------|-----------|-------|

| 25               | - 20/1.5 -      | 50        | 1250      | 25    |

| 200              |                 | 174       | 1960      | 11.15 |

| 25               | 20/2            | 41.6      | 690       | 16.6  |

| 200              |                 | 136       | 1250      | 19.19 |

| 25               | 20/4            | 25        | 235       | 9.4   |

| 200              |                 | 77        | 512       | 6.65  |

| 25               | 20/6            | 18.4      | 141       | 7.69  |

| 200              |                 | 54.2      | 322       | 5.94  |

| 25               | 20/10           | 13.5      | 78.3      | 5.80  |

| 200              |                 | 36        | 185       | 5.13  |

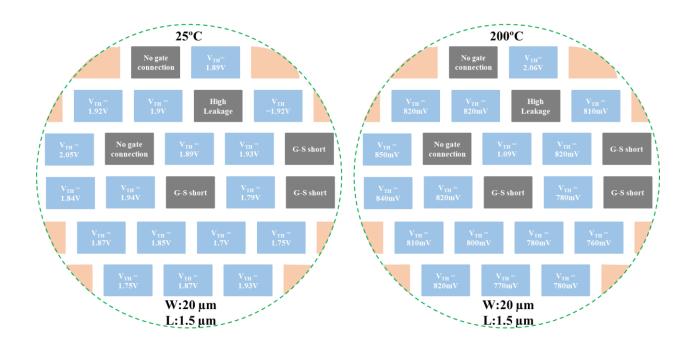

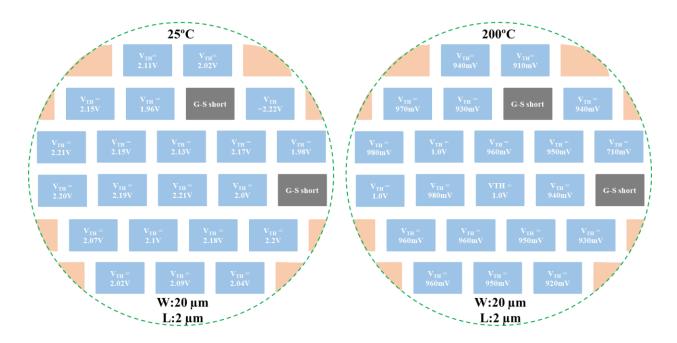

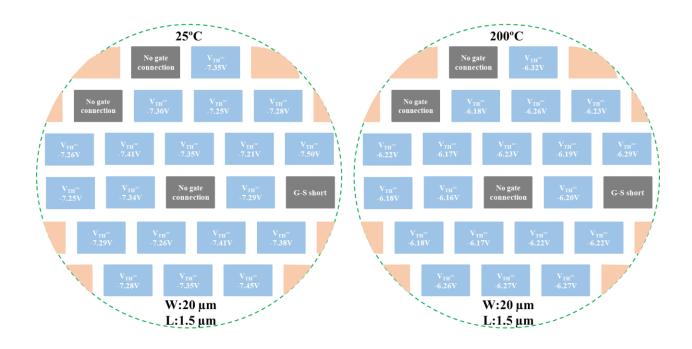

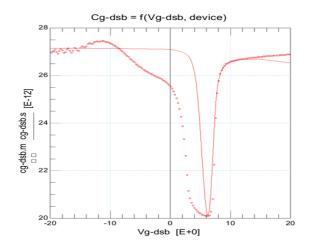

Additional results from RUN #1 and RUN #2 are added in Appendix A. It includes the wafer maps for RUN #1 MOSFETs for  $1.5 \,\mu m$  and  $2 \,\mu m$  channel length devices. It also shows the playback for BSIM 4.7.0 compact model with the measured data. The exercise of compact model

fitting was accomplished to support the circuit design efforts for RUN #2. Unfortunately, the circuit's performance did not match with the simulated performance because the several process changes were made between RUN #1 and RUN #2 to attempt to correct problems. The comparison between RUN #1 and RUN #2 devices is also shown in Appendix A.

#### **3** Design of an SRAM in RUN #1

#### 3.1 Introduction to SRAM and Sense Amplifiers

Static random-access memory (SRAM) is a type of semiconductor memory. It stores each bit by adopting bistable latching circuitry (such as a flip-flop). It retains data remanence, but in the traditional sense, it is still volatile. When the memory is not powered on, the data will eventually be lost. Because of positive feedback in an SRAM cell design, it does not need periodic data refreshing. The data from SRAM can be read/written faster, but it requires more area and its dynamic power can be significant depending on the memory size and frequency. It is usually used for the CPU cache. There are some advantages and disadvantages of SRAM memory, which have been listed below:

- Advantages: simplicity (without performing a refresh circuit), performance, reliability, low idle power consumption.

- Disadvantages: price, density, high operational power consumption.

On the other hand, SRAM used at a slightly slower speed, such as in applications with moderately clocked microprocessors, consumes very little power and consumes almost negligible power at idle, around a few microwatts.

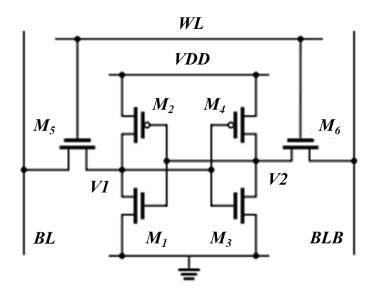

The SRAM IP block is divided into four main sub-blocks: Memory/bit Cell, Sense Amplifier, Row Decoder, and Column Decoder. In RUN #1, bit cells and sense amplifiers were implemented. There are a couple of topologies for designing SRAM bit cells, such as 6 transistor (i.e., 6T), 7 transistor, 8 transistor, and 9 transistor topologies. For RUN #1, the 6T SRAM bit cell topology was chosen because it has fewer transistors and utilizes less area than other topologies. The schematic of the 6T SRAM cell is shown in Fig. 7. It consists of two CMOS inverters (M1 & M2, M3 & M4) and two NMOS *access* transistors (M5 & M6). The CMOS inverters are connected

in a cross-coupled fashion (i.e., a latch) and form a bistable circuit, and the access transistors form a "make or break" path between storage latch outputs and read-write circuits by connecting it to bitlines. The SRAM cell has two bitlines that control both the input and output of data from the cell.

Fig. 7. 6T SRAM bit cell.

The SRAM cell operates in three modes: standby, read, and write modes. In standby mode, access transistors are turned off by grounding the Wordline (WL), so the latch retains its stored value for an indefinite time as long as the power supply is there. The WL selects the cell and allows values to be read from or written to the cell. In read mode, the sense amplifier is used to measure the differential voltage between the two bitlines. These bitlines are pre-charged to the supply voltage. When access transistors turn on, one of the bitlines starts to discharge through the pull-down transistor of the inverter that is latched to zero potential. There are two main categories of sense amplifiers Differential Mode sense amplifiers (also known as *voltage* sense amplifiers) and Non-Differential Mode sense amplifiers (also known as *current* sense amplifiers). Generally, voltage sense amplifiers are used because they are reliable and straightforward. Furthermore, they

are more area efficient than current-mode sense amplifiers. The performance of voltage sense amplifiers is dependent on the bitlines' capacitance. Larger bitline capacitance makes large RC time delays for the system, and because of this delay, the time taken by the bitlines to generate differential voltage is also high. Typically, a 300 mV to 500 mV differential voltage is enough for the sense amplifier to detect the value and latch the output.

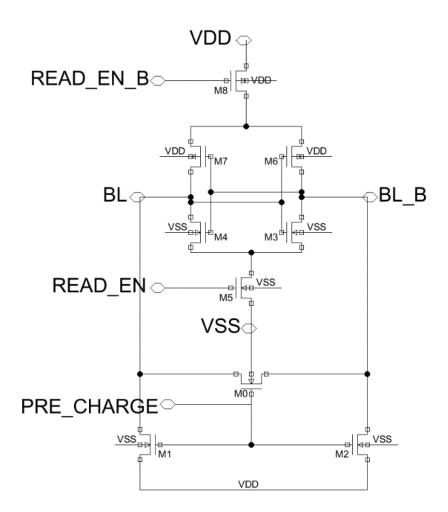

A variety of differential voltage sense amplifiers are in use, such as the Simple Differential Voltage Amplifier and Full Complementary Positive Feedback Voltage Sense Amplifier A schematic for the Full Complementary Positive Feedback Voltage Sense Amplifier is shown in Fig. 8. It is selected for implementation in RUN #1 and consists of two cross-coupled inverters (M4 & M7, M3 & M6), which use positive feedback to cause latching behavior. The Pre-Charge circuitry includes M1, M2, and M0, which charge the bitlines before the read operation. The read enable transistors (M5 and M8) are used to isolate the cross-coupled inverters when the SRAM cell is in the hold state. In addition to that, it does not require active current mirrors and a biasing circuit, which makes this sense amplifier a better choice for high-temperature environments. There are other amplifier variations, but this one is the most straightforward and reliable choice.

Fig. 8. Full complementary positive feedback sense amplifier.

#### 3.2 SRAM Test Structures in RUN #1

"Stability and cell area are the two important aspects for SRAM cell design. Cell stability is usually defined using static noise margin (SNM), which is the maximum DC noise voltage that can be tolerated by the cell without having any effects on the stored bit. The bit cell is most vulnerable to static noise voltage when it is in the read mode. This is due to pre-charged bit lines being connected to the storage nodes that can increase the potential of the storage nodes with a logic '0' value and cause a stored bit to flip to a logic '1'. To perform a nondestructive read operation, the ratio of current driving strength for the access transistor as compared to the pulldown transistor must be carefully selected. This is critical to avoid unintentionally increasing the voltage of the storage node when it ideally has a logic '0'. The ratio between the access transistor and pull-down transistor is termed cell ratio (CR), which is expressed below.

$$Cell \ Ratio = \frac{W_{PD}/L_{PD}}{W_{AD}/L_{AD}}$$

$W_{PD}$ ,  $L_{PD}$ ,  $W_{AD}$ ,  $L_{AD}$  are the widths and lengths of the pull-down and access transistors, respectively.

Like CR, there is another sizing parameter referred to as the pull-up ratio (PR). This term refers to the ratio of the pull-up transistor to the access transistor. The restoring strength (current driving capability) of the pull-up transistor must be higher than the strength of access transistors for a cell to perform a write operation. An expression for the PR is provided below.  $W_{PU}$  and  $L_{PU}$  are the width and length of the pull up transistors, respectively.

$$Pull Up Ratio = \frac{W_{PU}/L_{PU}}{W_{AD}/L_{AD}}$$

Due to the nature of the fabrication process and the early development phase of SiC integrated technology, multiple variants of SiC SRAM cells have been implemented for fabrication in RUN #1. Different values of CR (0.5, 1, 1.5, 2, 2.5) and PR (1, 2, 3, 4, 5, 6) are selected in order to determine the optimal cell size from the various performance parameters measured over temperature for each cell. SNM values for the different combinations of CR and PR are calculated using the model developed by Seevinck, et. al. [32]. Each cell variant is designed using minimum length NMOS and PMOS transistors (L = 1  $\mu$ m). Fixed width NMOS (W = 4  $\mu$ m) is used in the cross-coupled inverters, where the width of the PMOS increases to increase the pull-up ratio from 2:1 to 12:1.

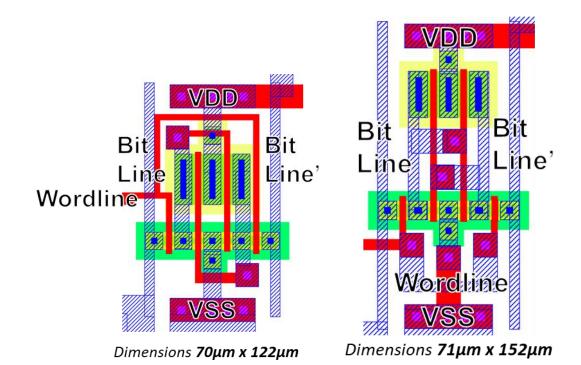

Layouts for the cells are optimized for this process, but are affected by the limitation of the availability of only a single metal layer for routing. Thus, poly has been used as a second routing

layer. Poly is a more resistive routing layer ( $R_{sh} = 15 \ \Omega/\Box$ .) and an effort was made to minimize its use in the various layouts. Two different layouts are designed to have reduced dimensions. Fig. 9 shows both the layouts with their dimensions. The shown SRAM cells have a CR = 0.5 and PR = 6.0. In order to make bitline routing less resistive, only the metal layer is used. The downside to these layout decisions is that the power rails of a cell are routed on poly wherever bitline is crossing."[10]

Fig. 9. SRAM cell layouts.

# 3.3 DC & Transient Measurements

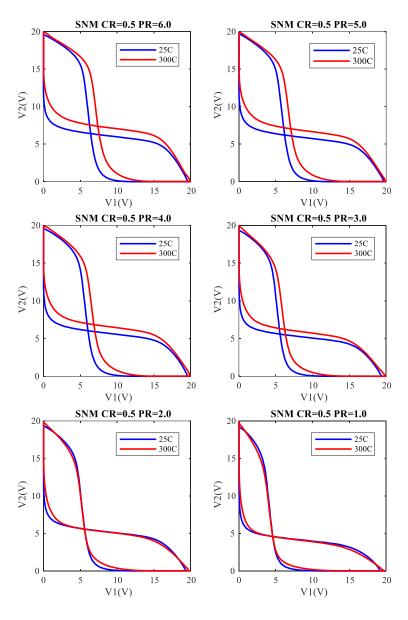

In all the combinations of CR and PR, the pull-down network always dominates, and the pull-up network cannot pull the node to VDD. In the implemented cell designs, the minimum CR is equal to 0.5, which means the pull-down network is at its lowest drive strength, and the maximum PR is set to 6.0. A PR of 6.0 indicates that the pull-up network is the strongest. CR and PR values are selected based on the PMOS to NMOS ratio of 5:1 and 6:1. However, due to the

unexpected drive strength ratios of fabricated PMOS and NMOS being 23:1 at 25°C and 10:1 at 300°C, the pull-up strength is lower for all the implemented CR and PR combinations. The CR of 0.5 means the pull-down transistor (M1 and M3 in Fig. 7) is at it's minimum size (4  $\mu$ m / 1  $\mu$ m) and the access transistor (M5 and M6 in Fig. 7) is two times the size  $(8 \mu m / 1 \mu m)$  of pull-down transistor. The PR of 1 means that the pull-up transistor (M2 and M4 in Fig. 7) is at the same size  $(8 \,\mu\text{m} / 1 \,\mu\text{m})$  as access transistor. The increase in the size of the pull-up transistor, increases the PR. For the PR of 2 the pull-up transistor is two times the size  $(16 \,\mu\text{m} / 1 \,\mu\text{m})$  of the access transistor. Likewise, for PR of 3 it is three times ( $24 \,\mu m / 1 \,\mu m$ ) and so on. Fig. 10 shows the SNM results for the CR of 0.5 with varying PR at 25°C and 300°C. The V1 is the voltage that is swept from 0 V to 20 V at the gate of the inverter (M3 and M4) of the SRAM cell shown in Fig. 7. The V2 is the voltage measured at the output of the inverter (M3 and M4). The result captured from the voltage sweep is the voltage transfer characteristics (VTC) of the first inverter (M3 and M4). The SNM for the SRAM is measured from the two back-to-back inverters. The VTC is plotted as V2 vs. V1, where V2 is on the vertical axis, and V1 is on the horizontal axis. The second inverter (M1 and M2) is identical to the first inverter, therefore first inverter VTC is used again but the axes are swapped. Now, the V2 is on the horizontal axis, and V1 is on the vertical axis. The backto-back VTC of the inverters is called butterfly plot and the diagonal of the largest square that fits within the back-to-back DC characteristics is the value of the SNM. The MATLAB code is developed (see Appendix C) to extract the value of the SNM from the butterfly curve. At high temperatures, the device performance gets better. Therefore, a minor increase in the pull-up network's performance can be noticed in Fig. 10. Also as the PR is increasing the eye of the butterfly plot is also increasing, resulting in higher SNM values.

Fig. 10. SNM at 25°C and 300°C.

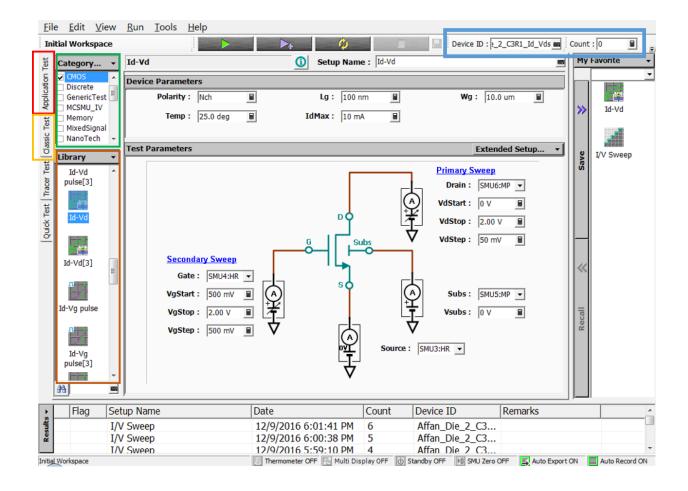

All the measurements are performed on a Signatone probe station. A Keysight B1500 DC curve tracer has been used for sweeping the input voltages. Room temperature measurements were performed on all the SRAM cells, and then high-temperature measurements were subsequently performed. At temperatures above 300°C, the threshold voltage of NFETs dropped below 1 V, and the threshold of PFETs lowered down to -4 V from -8 V (at room temperature), which results in

lower SNM for the cells. A lower threshold for NFETs leads to the storage node being pulled down stronger than the PFETs can pull it up.

An SNM of 4.71 V at 25°C and 4.65 V at 300°C demonstrates that the cell is capable to sustain this much of noise voltage at the supply voltage of 20 V. The noise can be triggered from the read or write operation. From Fig. 10, it can be seen that the implemented cells have the capability to hold the stored data at high temperatures, and the cross-coupled inverters are retaining their bistable states. An RSNM of 1.94 V at 25°C and 1.90 V at 300°C for CR=0.5 and PR=6.0 shows some robustness against the noise generated from precharged bitlines during the read operation. But the RSNM values are not sufficient, and there is a room for improvement to guarantee a proper read operation without disrupting the stored bits. The WSNM cannot be evaluated because of the unanticipated poor drive strength of PFETs. The performance of the SRAM cell is expected to improve significantly with the improvement in the SiC CMOS process.

| PR | SN   | IM(V) | RSNM(V) |       |  |  |

|----|------|-------|---------|-------|--|--|

|    | 25°C | 300°C | 25°C    | 300°C |  |  |

| 1  | 4.31 | 4.28  | 1.58    | 1.51  |  |  |

| 2  | 4.39 | 4.27  | 1.65    | 1.62  |  |  |

| 3  | 4.46 | 4.3   | 1.77    | 1.72  |  |  |

| 4  | 4.51 | 4.42  | 1.83    | 1.79  |  |  |

| 5  | 4.57 | 4.53  | 1.85    | 1.82  |  |  |

| 6  | 4.71 | 4.65  | 1.94    | 1.90  |  |  |

Table 4. The SNM and RSNM at CR=0.5

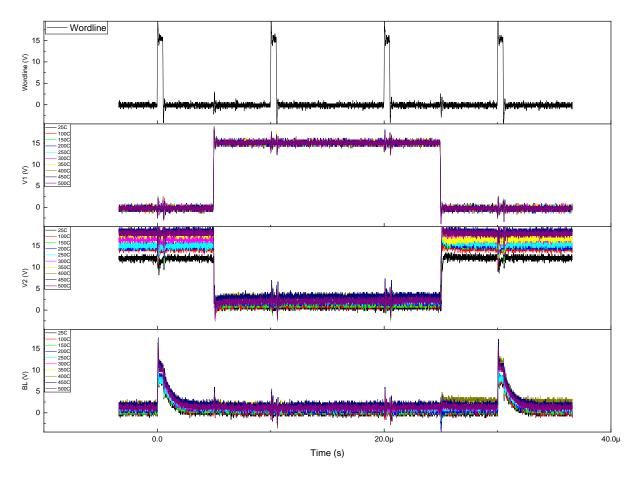

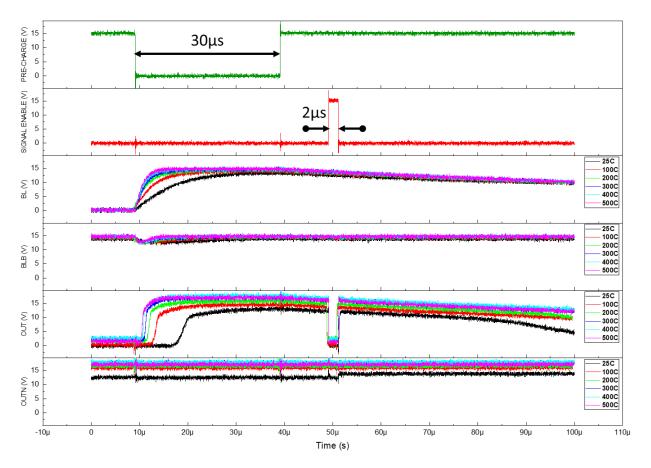

The test structure used for transient analysis has the CR = 0.5 and PR = 6.0. The test structure schematic is shown in Fig. 11. This analysis aims to check the operation of access transistors and the storing capability of the SRAM cell at elevated temperatures. Measurements were conducted on a high-temperature probe station from room temperature to 500°C.

Fig. 11. Half SRAM cell structure.

During the initial test setup, the stored bit flips whenever the wordline was asserted. This was due to the 13 pF load of the oscilloscope on the V2 pad of the test structure. Later, a picoprobe was connected at the output because it has only 0.1 pF of load. To see the functionality of the access transistors, four equal width pulses were triggered onto the wordline. During the first pulse, the V1 node was set to logic 0, resulting in logic 1 at V2. When the wordline triggers, the bitline copies the signal from the V2 node. Similarly, the second pulse of wordline V1 was set to 1, which resulted in logic 0 at V2. At this instance, the bitline is already discharged to 0 V before the wordline triggers, and it stays logic 0 when the wordline triggers. The bitline signal is connected to a cell through the access transistors, and whenever that transistor turns on, it passes the signal from the cell to the bitline. Due to the poor PMOS drive strength, the bitline node cannot be pulled to the VDD rail. However, as the temperature increases, the rail voltage of the bitline also increases. The V2 signal showed an offset with the increase in temperature due to the picoprobe amplifier DC offset. Fig. 12 shows the captured results at probe station with temperatures between 25°C to 500°C.

Fig. 12. Transient analysis of an SRAM Cell on the probe station at various temperatures.

#### 4 The Novel SiC SRAM Cell Design in RUN #2

#### 4.1 Process Module change from RUN #1 to RUN #2

RUN #1 measurement results revealed several issues related to the fabrication of different modules in the process. The lessons learned from RUN #1 were considered to improve the fabrication process of RUN #2. For the RUN #2 fabrication, foundry personnel decided to start with NWELL implants as the first ion implantation module in order to avoid P+ implants overetching. They also optimized the hard mask etching sequence. Additional process control modules are added in RUN #2 to avoid oxide residual during the formation of gate vias and also to monitor the formation of the ohmic contacts.

The RUN #2 processing started with twelve wafers with various wafer splits, as shown in Table 5. After the completion of all the ion implantation modules, six wafers were set aside as a backup. Four wafers received a lower NWELL doping of 3E15 cm<sup>-3</sup> that is expected to decrease the threshold voltage of PFETs. In RUN #1, the NWELL doping concentration was set to 5E15 cm<sup>-3</sup>. P-doped polysilicon is selected for four wafers, and of these four wafers, two received the RUN #1 doping, and the other two received the adjusted NWELL doping.

In RUN #1, an N-doped polysilicon was used. Changing to P-doped polysilicon type was estimated to increase the  $V_{THN}$  of NFETs by 1 V and decrease the  $V_{THP}$  magnitude of PFETs by 1 V. Altering to P-doped poly resulted in higher interconnect resistance due to its larger sheet resistance value of 40  $\Omega$ / $\Box$  compared to 15  $\Omega$ / $\Box$  for n-doped poly. For P-doped poly wafers, local polycided interconnections were used to minimize the interconnect trace resistance. Aluminum and platinum metallization options were added in an effort to evaluate the high-temperature characteristics of each.

| Wafer                                     | 1           | 2 | 3 | 4 | 5 | 6 | 7                              | 8 | 9       | 10 | 11 | 12 |

|-------------------------------------------|-------------|---|---|---|---|---|--------------------------------|---|---------|----|----|----|

| Isolation Type                            | field oxide |   |   |   |   |   |                                |   |         |    |    |    |

| Gate Oxide                                | 50 nm       |   |   |   |   |   |                                |   |         |    |    |    |

| PASS0 Doping Reference                    | Х           | Х |   |   |   |   |                                |   |         |    |    |    |

| Adjusted NWELL Doping                     |             |   | Х | Х | Х | Х |                                |   |         |    |    |    |

| Polycided (TiSi) Local<br>Interconnection | X           |   | Х |   | Х |   |                                |   |         |    |    |    |

| P-doped Polysilicon                       | Х           | Х | Х | Х |   |   | These wefers are in process    |   | rocossi | na |    |    |

| 1 Layer Al and 1 Layer<br>PolySi          |             | X |   | Х | Х | X | These wafers are in processing |   | ng      |    |    |    |

| 1 Layer Pt and 1 Layer<br>PolySi          | X           |   | Х |   |   |   | ]                              |   |         |    |    |    |

| Passivation                               | Х           | Х | Х | Х |   |   |                                |   |         |    |    |    |

Table 5. Wafer Split for 12 100 mm SiC Wafers for RUN #2

# 4.2 Proposed SiC SRAM Cell for RUN #2

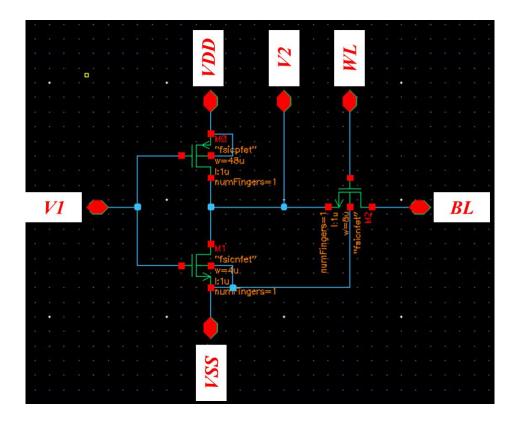

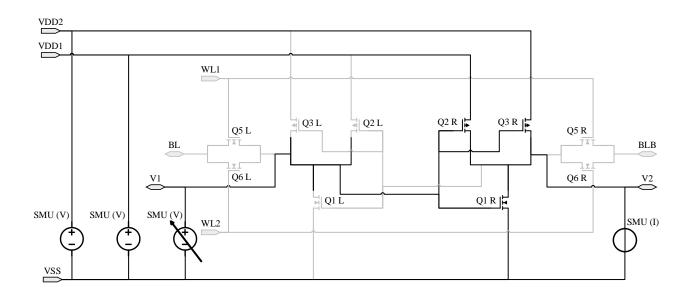

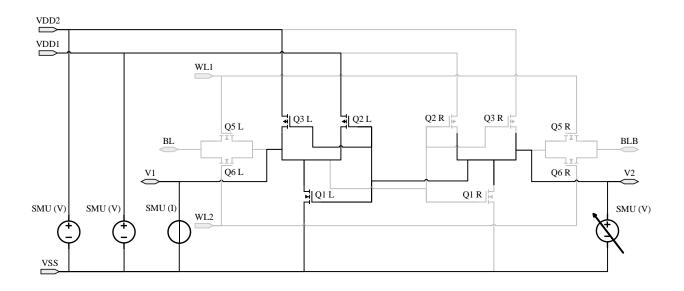

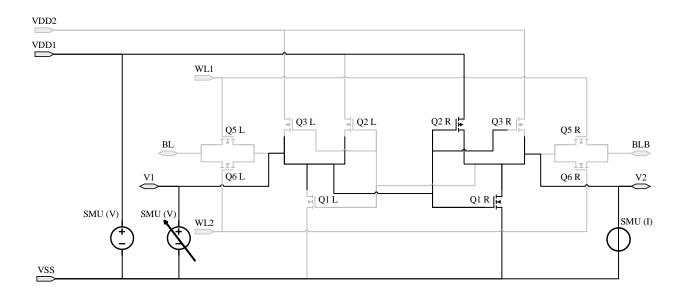

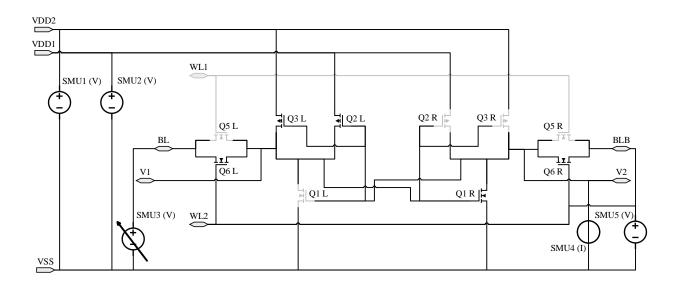

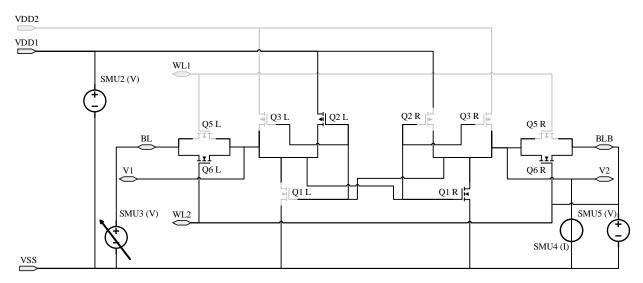

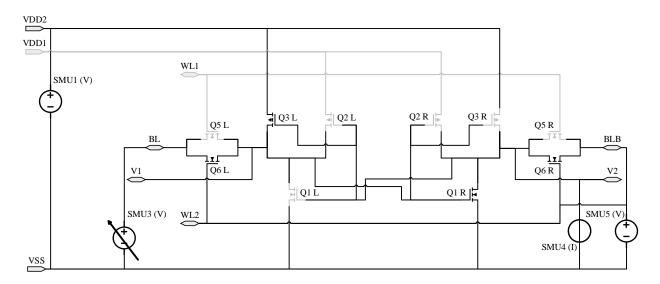

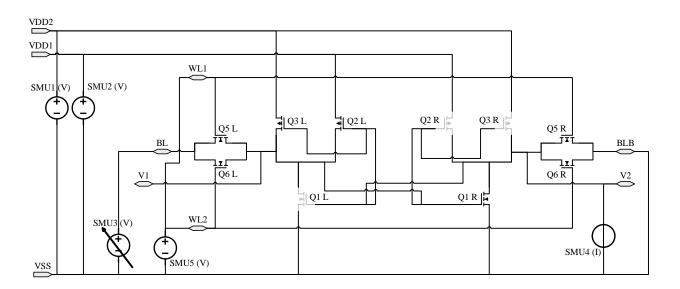

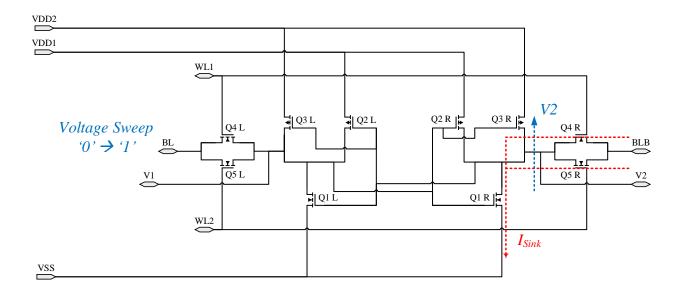

Given the significant changes from RUN #1 to RUN #2, new cell designs with additional pull-up strength and access transistors were created. The schematic for a novel SRAM cell is shown in Fig. 13. The issues encountered in RUN #1 and the uncertainty in the device performance of RUN #2 encouraged the design of an SRAM cell that is adaptable to the worst and the best cases. However, the tradeoff is made in the design size, number of I/Os, and the power consumption of the cell.

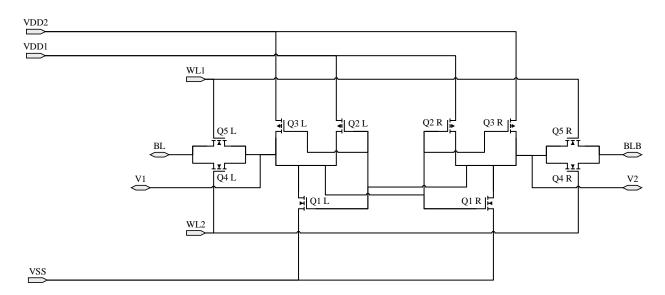

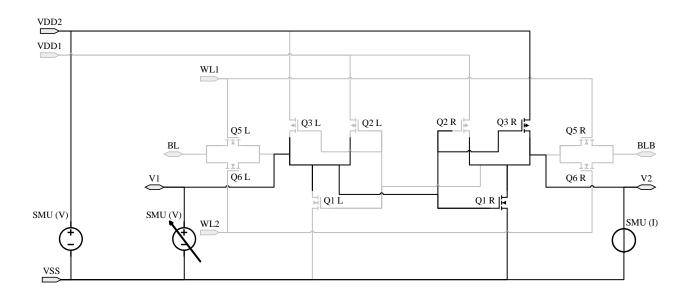

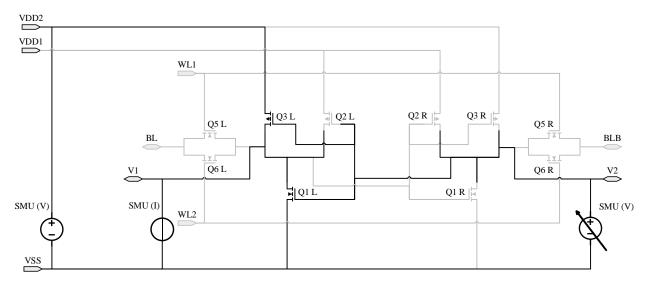

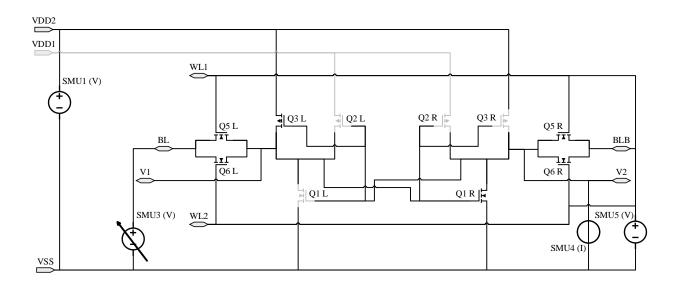

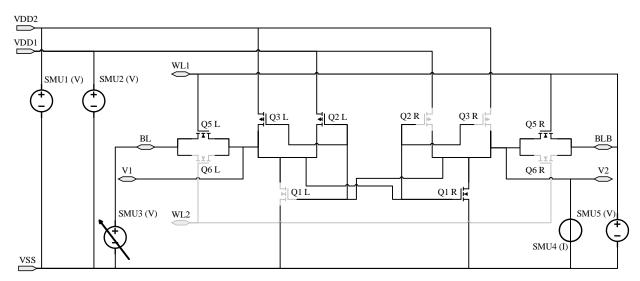

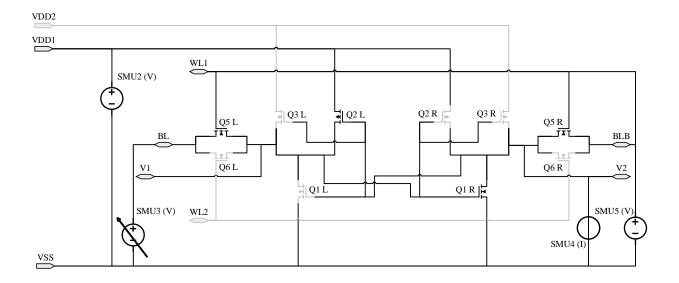

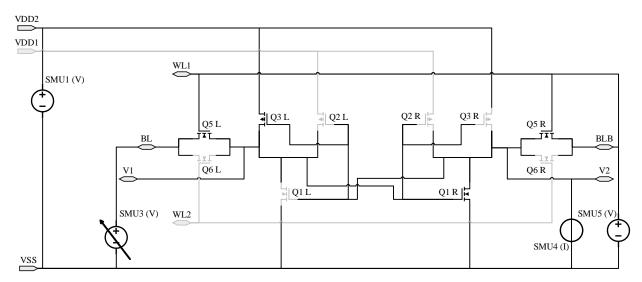

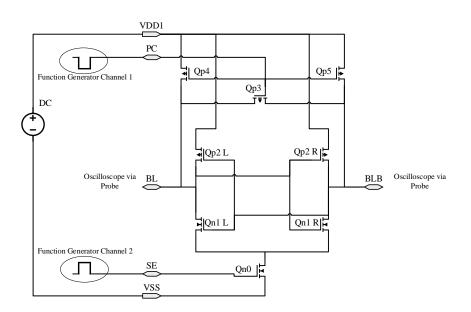

Fig. 13. Novel SiC SRAM cell for RUN #2.

The designed cell consists of an additional PFET in the inverters of the standard 6T SRAM cell, labeled as Q3 L and Q3 R in Fig. 13. These two transistors are connected to a separate supply, VDD2, offering flexibility to tune the drive strength for the pull-up network of the SRAM cell. Since the performance of the PFETs in RUN #2 was unknown, this design approach supports both worst and best cases in terms of PFET's performance. The pull-up and pull-down networks must be precisely scaled to retain the stored bit in the SRAM cell. In addition to that, the access transistors are the key to perform the read and write operations. Due to unknown PFET behavior, parallel access transistors are added in the design (Q4 R, Q5 R, Q4 L, and Q5 L) controlled from two separate wordlines (WL1 and WL2). This allows for additional flexibility in the read and write operations without going through another design iteration. Two test structures are designed with different access transistor sizing; Table 6 shows the transistor sizing of the designed cell.

Table 6. Novel SRAM Cell Transistor Sizes

| Transistor         | Q1 L | Q2 L | Q3 L | Q4 L | Q5 L | Q1 R | Q2 R | Q3 R | Q4 R | Q5 R |

|--------------------|------|------|------|------|------|------|------|------|------|------|

| TS1 Widths<br>(µm) | 5    | 50   | 50   | 8    | 8    | 5    | 50   | 50   | 8    | 8    |

| TS2 Widths<br>(µm) | 5    | 50   | 50   | 5    | 5    | 5    | 50   | 50   | 5    | 5    |

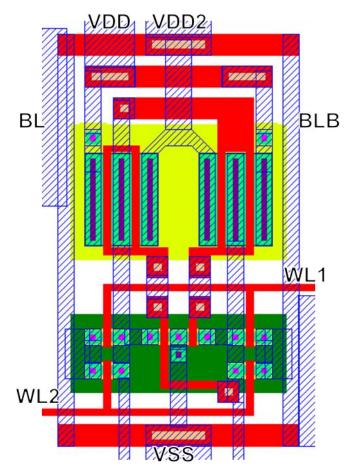

The layout of the cell designed in RUN #2 is shown in Fig. 14. The trade-off is made in the cell area, and it is at least two times larger than RUN #1 SRAM cell. The availability of only one metal layer in the process made the layout a challenge. Therefore, to keep the cell density smaller, the poly layer is used as a second routing layer. Even though the poly layer has higher resistance, it is used to route the power nets. The metal layer is used to route the bitlines because they need to be less resistive to perform read and write operations faster.

Dimensions 135µm x 232µm

# Fig. 14. Novel SiC SRAM cell layout in RUN #2.

# 4.3 High-Temperature Sense Amplifier Architectures

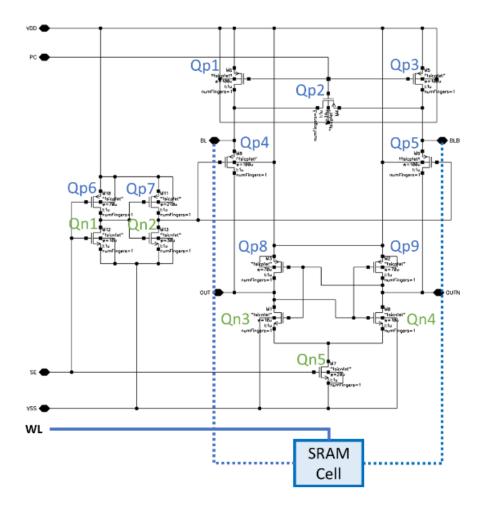

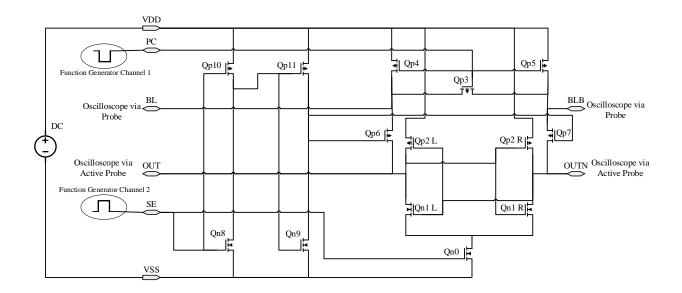

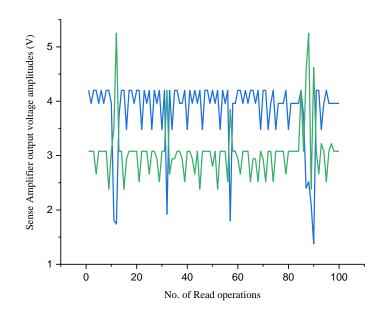

Voltage sense amplifier architectures are designed in RUN #2. A conventional CMOS latch type sense amplifier (shown in Fig. 8) and an improved latch type sense amplifier (shown in Fig. 15) were designed and characterized at high temperatures using a probe station.