University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

5-2021

# Design and Assembly of High-Temperature Signal Conditioning System on LTCC with Silicon Carbide CMOS Circuits

Sajib Roy University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Electrical and Electronics Commons, Power and Energy Commons, Signal Processing Commons, and the Systems and Communications Commons

#### Citation

Roy, S. (2021). Design and Assembly of High-Temperature Signal Conditioning System on LTCC with Silicon Carbide CMOS Circuits. *Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/etd/3957

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact ccmiddle@uark.edu.

Design and Assembly of High-Temperature Signal Conditioning System on LTCC with Silicon Carbide CMOS Circuits

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering with a concentration in Electrical Engineering

by

Sajib Roy East West University Bachelor of Science in Electrical and Electronic Engineering, 2009 Linkoping University Master of Science in Electrical Engineering, 2011

## May 2021 University of Arkansas

This dissertation is approved for recommendation to the Graduate Council.

H. Alan Mantooth, Ph.D. Ph.D. Advisor Jia Di, Ph.D. Committee Member

Zhong Chen, Ph.D. Committee Member Jeff Dix, Ph.D. Committee Member

#### Abstract

The objective of the work described in this dissertation is to develop a prototype electronic module on a low-temperature co-fired ceramic (LTCC) material. The electronic module would perform signal conditioning of sensor signals (thermocouples) operating under extreme conditions for applications like gas turbines to collect data on the health of the turbine blades during operation so that the turbines do not require shutdown for inspection to determine if maintenance is required. The collected data can indicate when such shutdowns, which cost \$1M per day, should be scheduled and maintenance actually performed. The circuits for the signal conditioning system within the prototype module must survive the extreme temperature, pressure, and centrifugal force, or G-force, present in these settings. Multiple fabrication runs on different integrated silicon carbide (SiC) process technologies have been carried out to meet the system requirements. The key circuits described in this dissertation are a set of two-stage op amp topologies and a voltage reference, which were designed and fabricated in a new SiC CMOS process. The SiC two-stage op amp with PFET differential input pair showed 48.9 dB of DC gain at 500°C. The voltage reference is the first in SiC CMOS technology to employ an op amp-based topology. The op amp circuit in the voltage reference is a two-stage topology with an NFET differential input pair that uses the indirect compensation technique for the first time in a SiC CMOS process to provide 42.5 dB gain at 350°C. The designed prototype module implemented with these circuits was verified to provide signal conditioning and signal transmission at 300°C. The signal transmission circuit on the module was also verified to operate with a resonant inductive wireless power transfer method at a frequency of 11.8 MHz for the first time. A second prototype module was also developed with a previously fabricated set of circuits in a 1.2 µm SiC CMOS process. The second module was successfully tested (with wired power supply) to operate at 440°C inside a probe station and also

verified for the first time to sustain signal transmission (34.65 MHz) capability inside a spin-rig at a rotational speed of 10,920 rpm, which corresponds to approximately 16,000 Gs. All designed modules have dimensions of 68.5 mm by 34.3 mm to conform to the physical size requirements of the gas turbine blade.

©2021 by Sajib Roy All Rights Reserved

#### Acknowledgements

I am most thankful to my Ph.D. advisor Dr. H. Alan Mantooth, for allowing me to learn, understand, and thrive by allowing me to work on challenging research projects. Along with that, his valued mentorship has helped me throughout my degree program. I have learned valuable lessons from him on proficiently writing research papers and carrying out research work in an organized form.

I want to thank my advisory committee members, Dr. Jia Di, Dr. Zhong Chen, and Dr. Jeff Dix, for the support and cooperation they showed to me.

I want to thank my IC group members, Robert, Affan, Asif, Logan, Justin, Marvin, and Jose for their help. Also would like to give special thanks to John Fraley and Brett Sparkman from Wolfspeed for their help.

I want to thank John Fraley (from Wolfspeed) and Andrew Kommos (from Siemens) for providing instrumentation equipment for electronic module testing.

I want to thank Aerodyn-Global and Mr. Chris Brunnemer for their assistance in the spin testing. The research work presented in this dissertation was funded by the U.S. Department of Energy under grant # FE0026348. I would like to give my regards to the DOE for their financial support.

# Table of Contents

| Chapter 1. | Introduction1                                                           |

|------------|-------------------------------------------------------------------------|

| 1.1.       | Motivation1                                                             |

| 1.2.       | Design Approaches                                                       |

| 1.3.       | Research Objectives                                                     |

| 1.4.       | Key Contributions7                                                      |

| 1.5.       | Dissertation Outline                                                    |

| Chapter 2. | SiC Process Selection and Device Characterization11                     |

| 2.1.       | SiC Bipolar Process: KTH PASS0 and PASS1 Fabrication Runs 11            |

| 2.2.       | SiC CMOS Process: Fraunhofer PASS0 and PASS1 Fabrication Runs 17        |

| 2.2.1      | Transistor Characterization from Fraunhofer PASS0 Run                   |

| 2.2.2      | PASS0 Circuit Characterization and HSpice Model Parameter Extraction 21 |

| 2.2.3      | Changes in PASS1 Fabrication                                            |

| 2.2.4      | Transistor Characterization from Fraunhofer PASS1 Run                   |

| Chapter 3. | Design of Silicon Carbide Circuits in the Fraunhofer CMOS Process<br>35 |

| 3.1.       | Operational Amplifiers: Design Approach and Simulation                  |

| 3.2.       | Voltage Reference Circuit: Design Approach and Simulation               |

| 3.3.       | Fraunhofer SiC CMOS Circuits: Die Micrographs of the Circuits           |

| 3.4.       | Fraunhofer SiC CMOS Circuit Measurement Results                         |

| 3.4.1      | Two-stage PFET Differential Pair Op amp47                               |

| 3.4.2      | Two-stage NFET Differential Pair Op amp 50                              |

| 3.4.3      | Two-stage Folded-Cascode Op amp                                         |

| 3.4.4      | Voltage reference Circuit                                               |

| Chapter 4. | Silicon Carbide Signal Conditioning System Prototypes on LTCC58         |

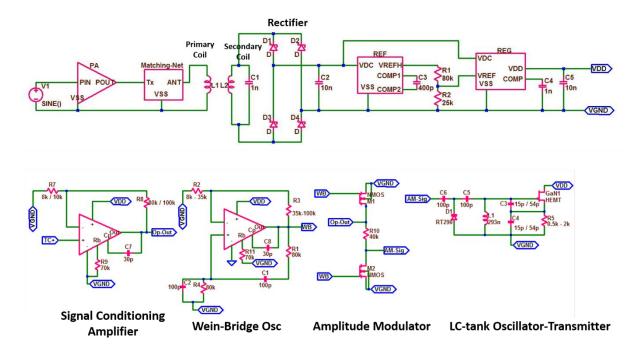

| 4.1.       | RUK LTCC Module Schematic                                               |

| 4.2.       | RUK LTCC Module Simulation Results                                      |

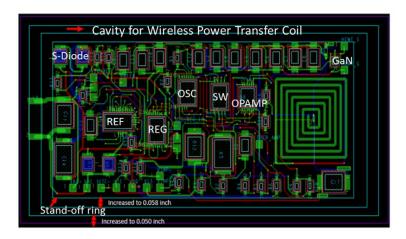

| 4.3.       | RUK LTCC Module Layout                                                  |

| 4.4         | RUK LTCC Module           | Assembly                                |  |

|-------------|---------------------------|-----------------------------------------|--|

| 4.5         | Fraunhofer LTCC Mo        | dule Schematic                          |  |

| 4.6         | Fraunhofer LTCC Mo        | dule Layout                             |  |

| 4.7         | Fraunhofer LTCC Mo        | dule Assembly                           |  |

| Chapter 5.  | LTCC Module Test          | Results                                 |  |

| 5.1         | Colpitts Oscillator Tes   | sting on the RUK and Fraunhofer Modules |  |

| 5.2         | RUK Module Individu       | al Blocks and System Testing            |  |

| 5.3         | Receiver Set-up for Si    | gnal Detection from the LTCC Modules    |  |

| 5.4         | Spin Testing on the R     | UK Module                               |  |

| 5.5         | High-Testing of the R     | UK Module                               |  |

| 5.6         | Fraunhofer Module Te      | esting 106                              |  |

| 5           | 6.1 Rectifier Circuit Tes | ting                                    |  |

| 5           | 6.2 Fraunhofer Module-    | 2 High-Temperature Testing 117          |  |

| 5           | 6.3 Fraunhofer Module-    | 3 Functional Testing 120                |  |

| Chapter 6.  | Conclusions and Fu        | ture Work 124                           |  |

| 6.1         | Conclusion                |                                         |  |

| 6.2         | Future Work               |                                         |  |

| Bibliograph | y 128                     |                                         |  |

| Appendix    | 132                       |                                         |  |

| Ap          | pendix-1                  |                                         |  |

| Appendix-2  |                           |                                         |  |

| Appendix-3  |                           |                                         |  |

| Ap          | Appendix-4                |                                         |  |

| Ap          | pendix-5                  |                                         |  |

# List of Figures

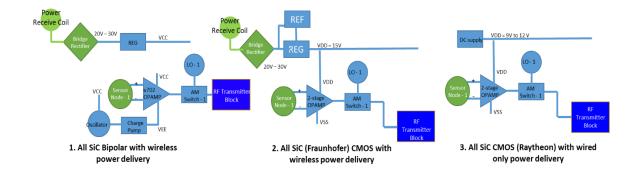

| Fig. 1. Top-level design approaches for signal conditioning system: (i) SiC bipolar based, (ii) 1.5         |

|-------------------------------------------------------------------------------------------------------------|

| $\mu m$ new SiC CMOS (Fraunhofer) based, and (iii) 1.2 $\mu m$ old SiC CMOS (Raytheon) based 4              |

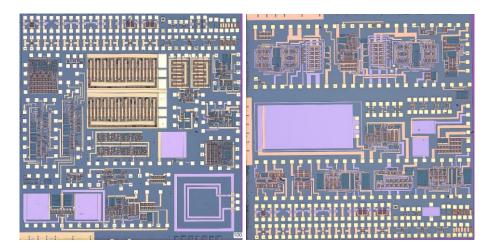

| Fig. 2. Die micrograph of the complete 10 mm by 5 mm reticle from SiC BJT PASS1 run 12                      |

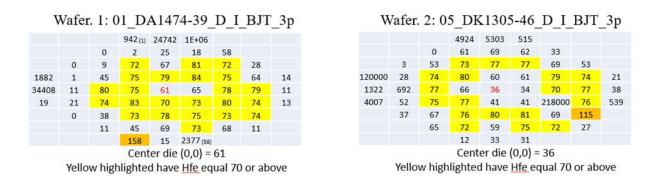

| Fig. 3. Wafer map showing the SiC BJT current gain variation for the two PASS1 wafers 13                    |

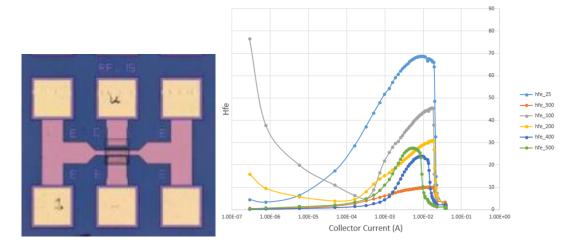

| Fig. 4. (Left) Die image of the 40 $\mu$ m by 15 $\mu$ m SiC NPN transistor, (Right) current gain variation |

| of the NPN device over temperature                                                                          |

| Fig. 5. Schematic view of the multi-stage SiC Bipolar op amp with Darlington input pair 15                  |

| Fig. 6. Layout view of the multi-stage SiC Bipolar op amp with Darlington input pair                        |

| Fig. 7. Schematic view of the SiC Bipolar linear regulator to provide 12 V, 40 mA output 16                 |

| Fig. 8. Layout view of the SiC Bipolar linear regulator to provide 12 V, 40 mA output 17                    |

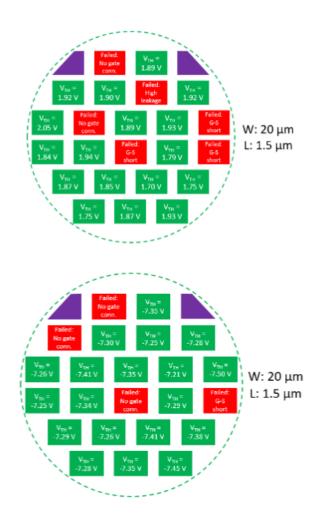

| Fig. 9. Wafer map on $V_{TH}$ variation of 20 $\mu$ m by 1.5 $\mu$ m NFET (top) and PFET (bottom) devices   |

| from Fraunhofer SiC CMOS PASS0 run                                                                          |

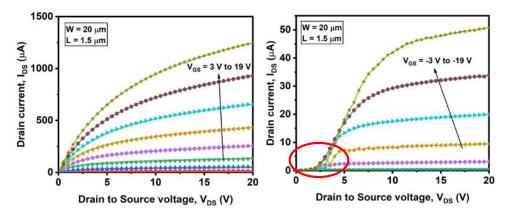

| Fig. 10. NFET (Left) and PFET (Right) I-V plots from PASSO wafer #1                                         |

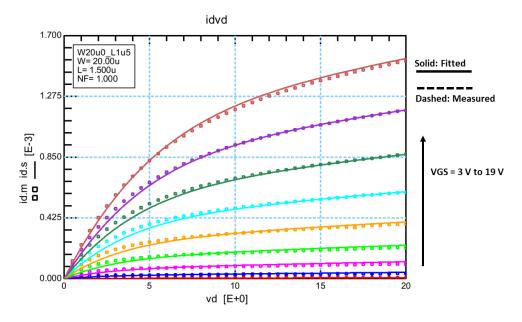

| Fig. 11. IC-CAP plot showing the fitted I-V and the measured I-V curve for the 20 $\mu m$ by 1.5 $\mu m$    |

| NFET device                                                                                                 |

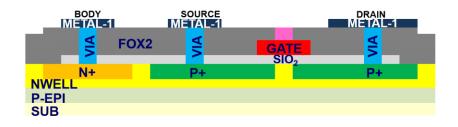

| Fig. 12. Cross-section of NFET (top) and PFET (bottom) for PASS1                                            |

| Fig. 13. Threshold voltage ( $V_{TH}$ ) variation over temperature for NFET (top) and PFET (bottom)         |

| from PASS1 wafers #3, #4, and #6                                                                            |

| Fig. 14. PASS1 wafer #3 I-V plots for 20 $\mu$ m × 2 $\mu$ m PFET at 25°C                                   |

| Fig. 15. PASS1 wafer #3 I-V plots for 20 $\mu$ m × 2 $\mu$ m PFET at 500°C                                  |

| Fig. 16. PASS1 wafer #4 I-V plots for 20 $\mu$ m × 2 $\mu$ m PFET at 25°C                                   |

| Fig. 17. PASS1 wafer #4 I-V plots for 20 $\mu$ m × 2 $\mu$ m PFET at 500°C                                  |

| Fig. 18. PASS1 wafer #3, I-V plots for NFETs at 25°C                                               |

|----------------------------------------------------------------------------------------------------|

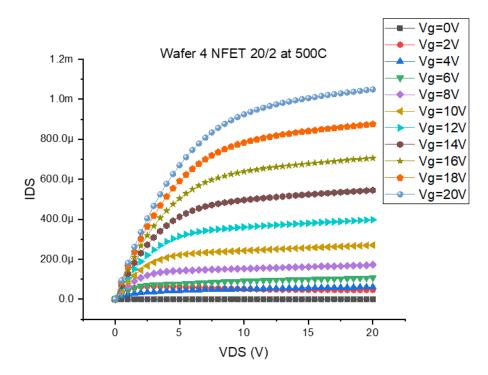

| Fig. 19. PASS1 wafer #3, I-V plots for NFETs at 500°C                                              |

| Fig. 20. PASS1 wafer #4, I-V plots for NFETs at 25°C                                               |

| Fig. 21. PASS1 wafer #4, I-V plots for NFETs at 500°C                                              |

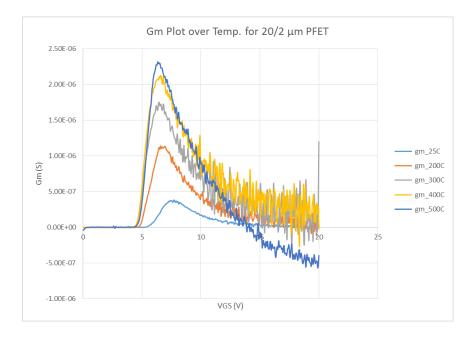

| Fig. 22. PASS1 20 $\mu$ m × 2 $\mu$ m PFET transconductance over temperature                       |

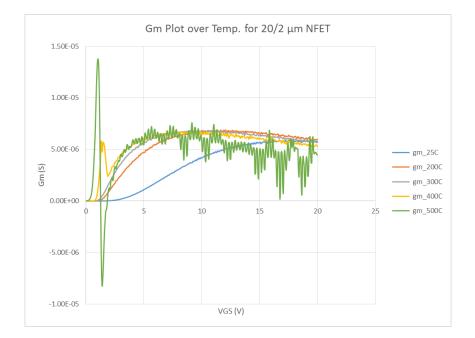

| Fig. 23. PASS1 20 $\mu$ m × 2 $\mu$ m NFET transconductance over temperature                       |

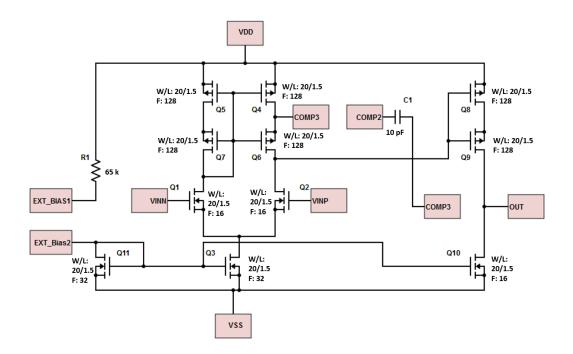

| Fig. 24. Schematic of the two-stage op amp with PFET differential input pair designed on the       |

| Fraunhofer SiC CMOS PASS1 run                                                                      |

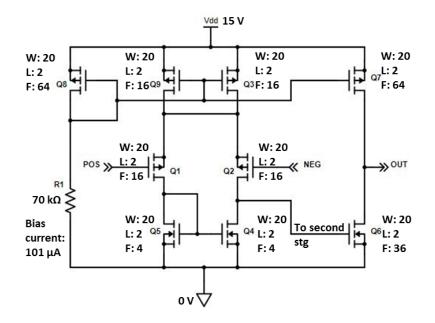

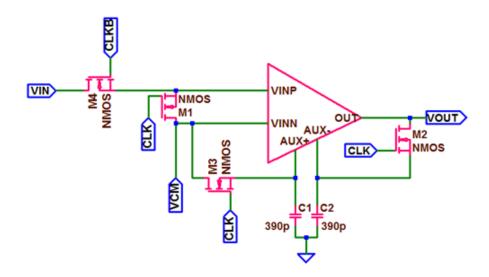

| Fig. 25. Schematic of the two-stage op amp with NFET differential input pair designed on the       |

| Fraunhofer SiC CMOS PASS1 run                                                                      |

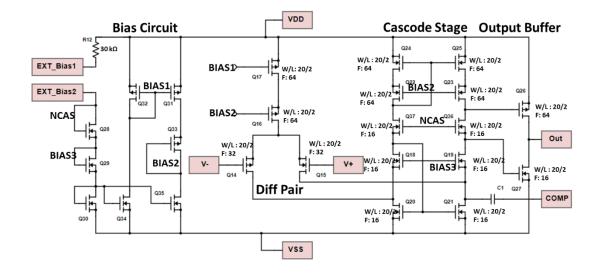

| Fig. 26. Schematic of the two-stage folded-cascode op amp with PFET differential input pair and    |

| class AB buffer output, designed on the Fraunhofer SiC CMOS PASS1 run 40                           |

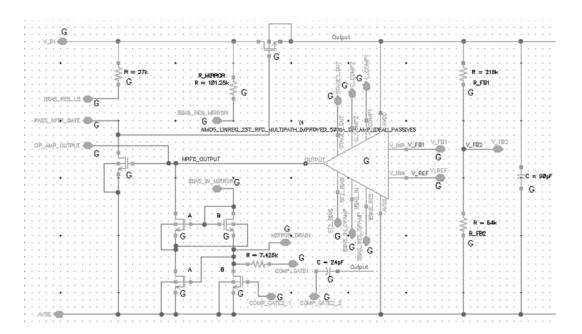

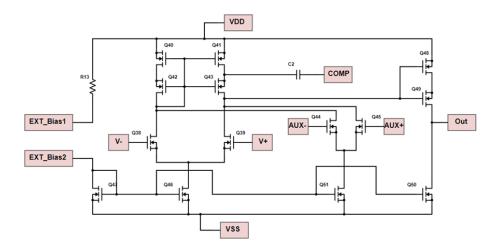

| Fig. 27. Schematic of the voltage reference circuit designed in the Fraunhofer SiC CMOS PASS1      |

| run                                                                                                |

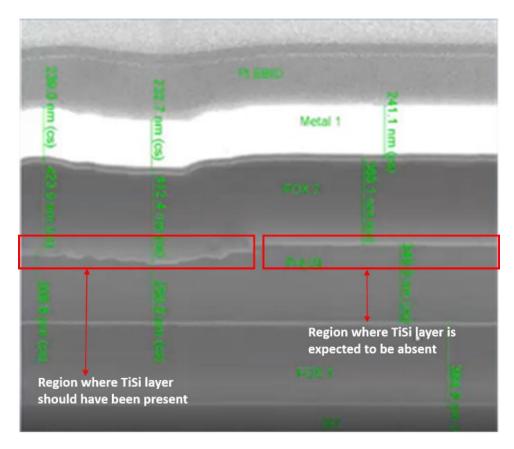

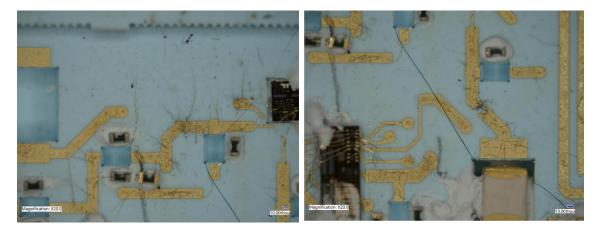

| Fig. 28. FIB image on wafer#3 indicating the place where the titanium layer is absent over the     |

| polysilicon layer                                                                                  |

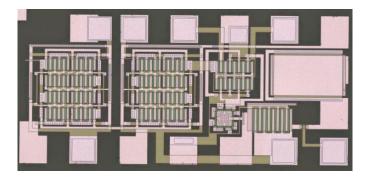

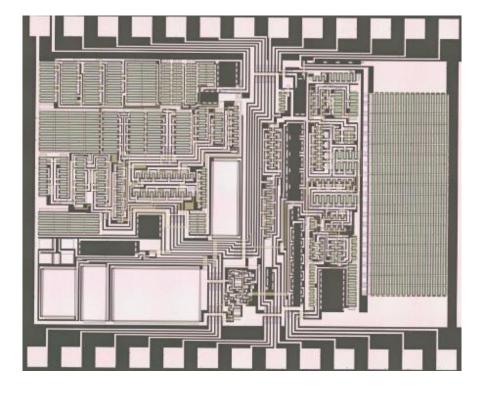

| Fig. 29. Die micrographs of (a) PFET two-stage op amp, (b) folded-cascode two-stage op amp,        |

| and (c) voltage reference with the NFET two-stage op amp                                           |

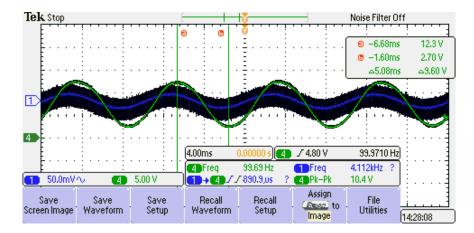

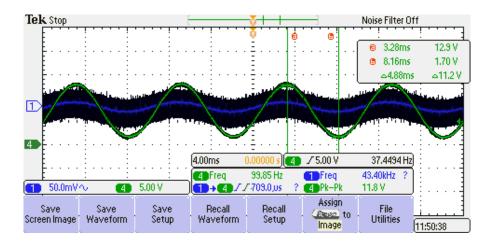

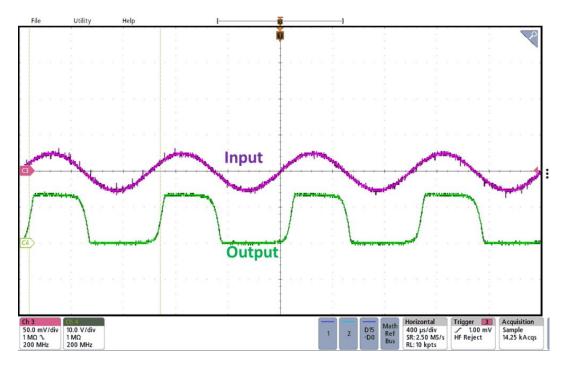

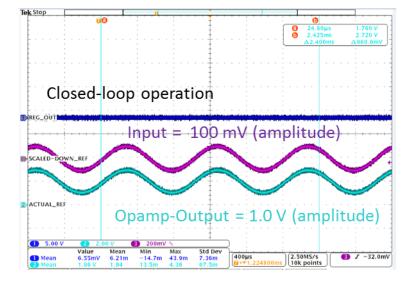

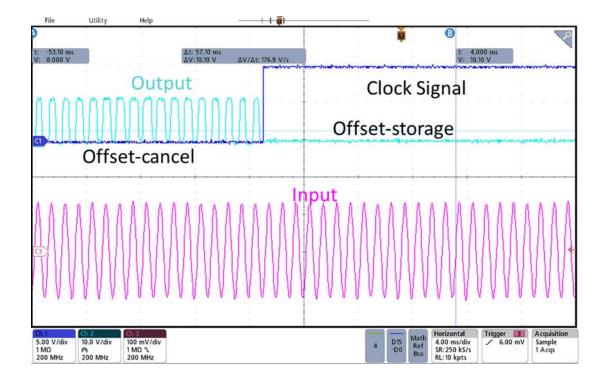

| Fig. 30. Input-Output waveforms on the oscilloscope for the two-stage PFET differential input pair |

| op amp at 25°C                                                                                     |

| Fig. 31. Input-Output waveforms on the oscilloscope for the two-stage PFET differential input pair |

| op amp at 500°C                                                                                    |

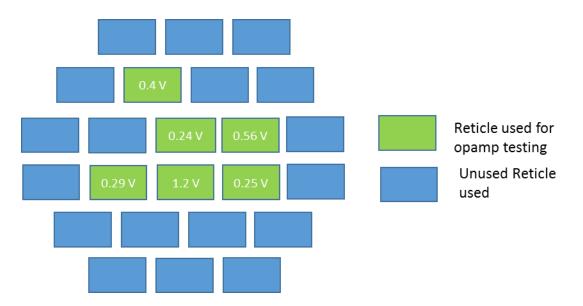

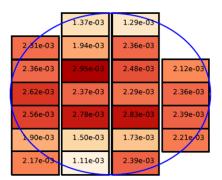

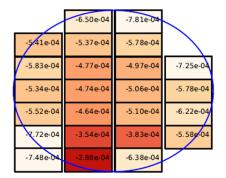

| Fig. 32. Wafer #4 map indicating offset variations on the five tested op amps with PFET          |

|--------------------------------------------------------------------------------------------------|

| differential input pair 50                                                                       |

| Fig. 33. Input-Output waveforms on the oscilloscope for the two-stage NFET differential input    |

| pair op amp at 25°C                                                                              |

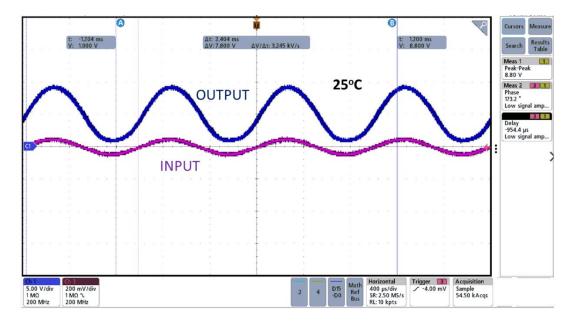

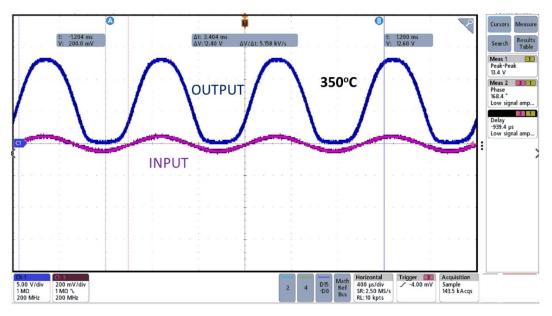

| Fig. 34. Input-Output waveforms on the oscilloscope for the two-stage NFET differential input    |

| pair op amp at 350°C                                                                             |

| Fig. 35. Oscilloscope Input-Output waveforms for the two-stage folded-cascode op amp in an       |

| open-loop configuration                                                                          |

| Fig. 36. Input-Output waveforms on the oscilloscope for the two-stage folded-cascode op amp      |

| under closed-loop                                                                                |

| Fig. 37. RUK LTCC module schematic                                                               |

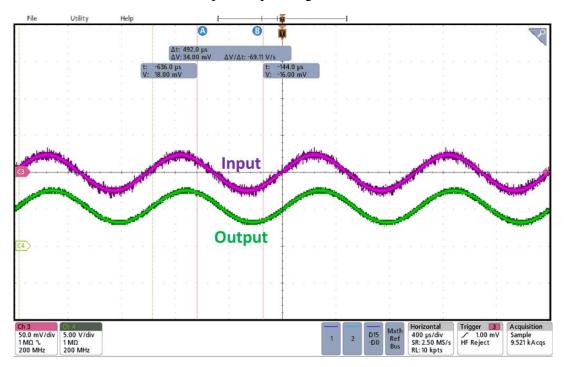

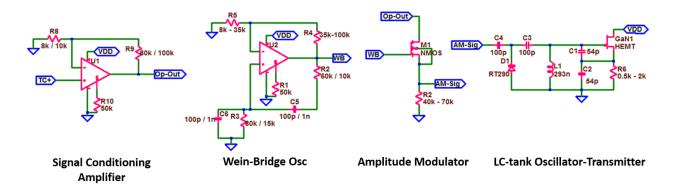

| Fig. 38. Simulation results for the RUK signal conditioning op amp and amplitude modulator       |

| circuit                                                                                          |

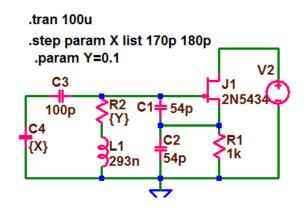

| Fig. 39. Frequency modulator schematic in LTSpice to verify the LC-tank oscillator architecture. |

|                                                                                                  |

| Fig. 40. Simulated FFT plot of the output of the LC-tank oscillator in Fig. 39                   |

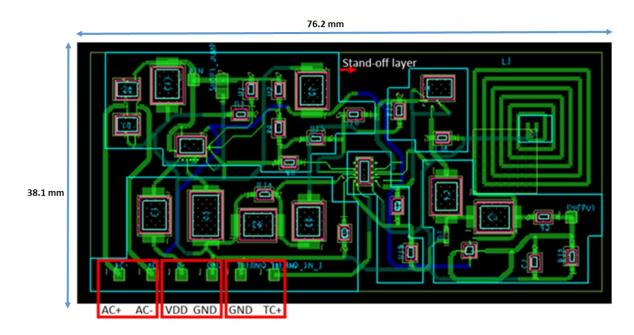

| Fig. 41. The layout of the RUK LTCC module                                                       |

| Fig. 42. (Top) complete CMC housing structure, and (bottom) CMC base structure where the         |

| LTCC module sits                                                                                 |

| Fig. 43. The second layout of the RUK LTCC module with a stand-off layer designed on the outer   |

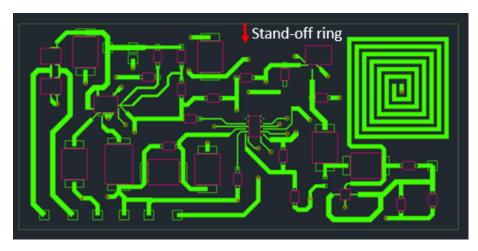

| periphery                                                                                        |

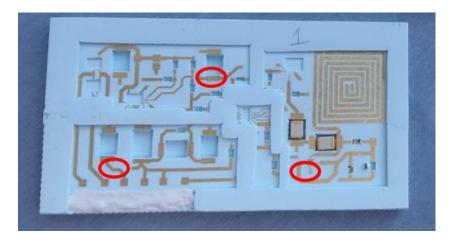

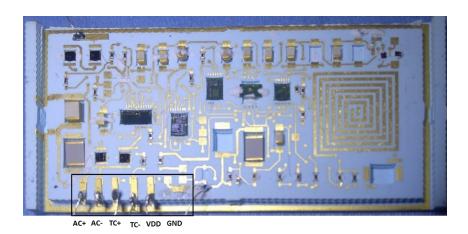

| Fig. 44. Fabricated RUK LTCC module-1 with stand-off layer routed over the inner area of the     |

| module (red circled sections indicate places with VIA opening)                                   |

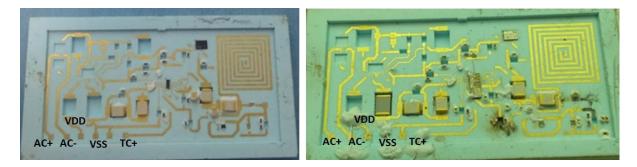

| Fig. 45. RUK LTCC module-2 (for high-temperature test -left) and (spin test -right) with            |

|-----------------------------------------------------------------------------------------------------|

| assembled components                                                                                |

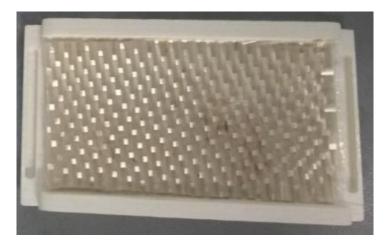

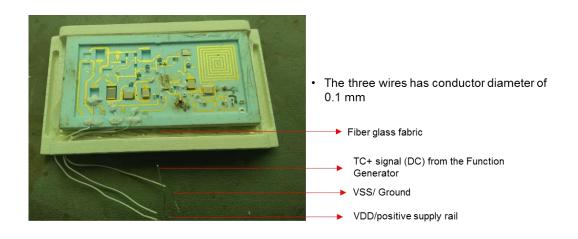

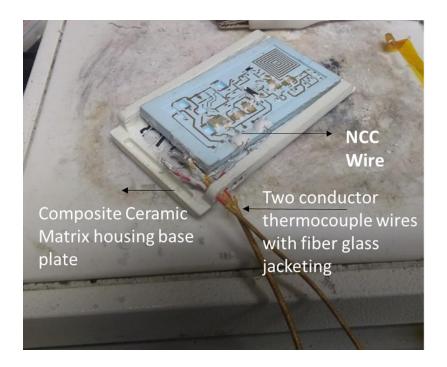

| Fig. 46. Image of the Nextel fiber-glass fabric on the base of the CMC housing structure 71         |

| Fig. 47. Wire assembly on the RUK LTCC module and placement on the CMC housing structure            |

| (housing top cover (or lid) not shown in the image)                                                 |

| Fig. 48. Schematic of the Fraunhofer LTCC module                                                    |

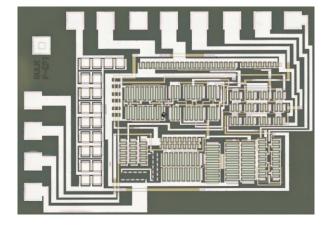

| Fig. 49. The layout of the initial version of the Fraunhofer module                                 |

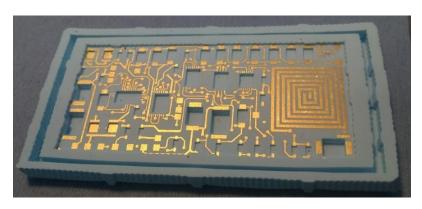

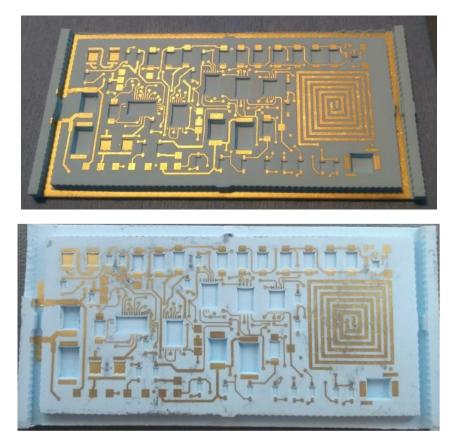

| Fig. 50. The initial version of the fabricated Fraunhofer module                                    |

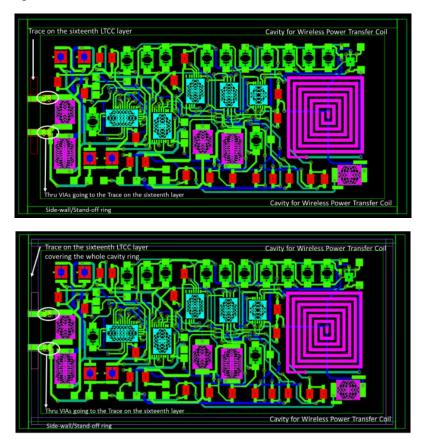

| Fig. 51. Two modified layouts for the second version of the Fraunhofer module                       |

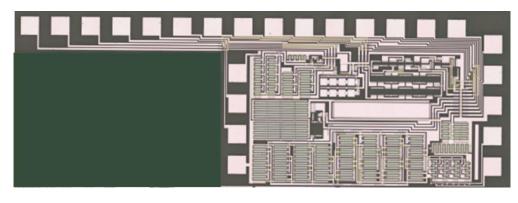

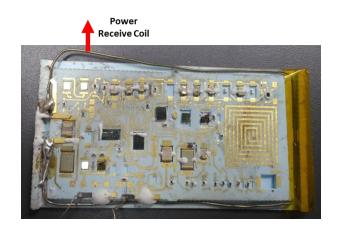

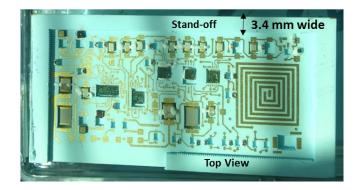

| Fig. 52. (Top) Thick-film gold trace for depositing silver paste for creating power receiving coil  |

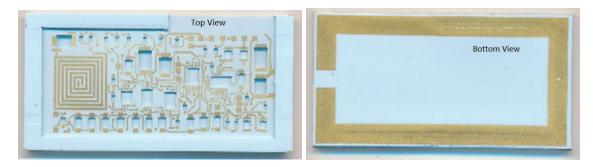

| (module-1), and (bottom) partial gold trace to assemble wire coil for wireless power reception      |

| (module-2)                                                                                          |

| Fig. 53. The third version of the Fraunhofer module with wider gold trace on the back of the        |

| module for power reception coil                                                                     |

| Fig. 54. Fraunhofer module-1 (with the complete thick gold trace on the outer periphery) after      |

| complete assembly                                                                                   |

| Fig. 55. Fraunhofer module-2 after assembly of the components and the power receiver coil to        |

| test/validate the full-bridge rectifier and wireless power transfer method                          |

| Fig. 56. Fraunhofer module-3 with stand-off layer and receive coil on the back of the module 81     |

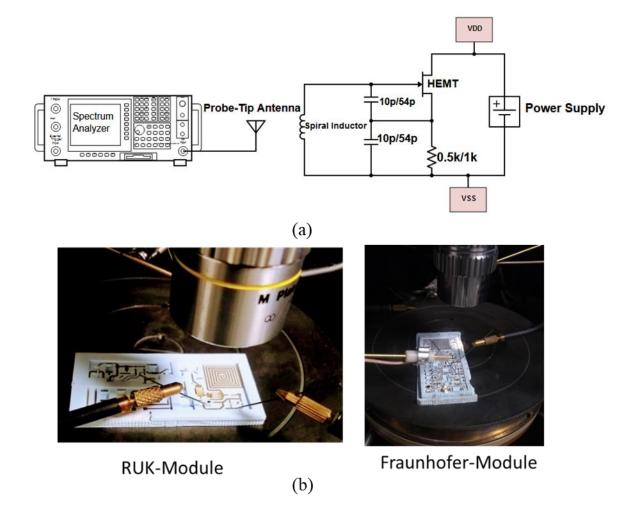

| Fig. 57. (a) Test setup configuration schematic for the Colpitts oscillator testing on the modules, |

| (b) Probe station setup for testing the Colpitts oscillator both the RUK and Fraunhofer modules at  |

| 500°C                                                                                               |

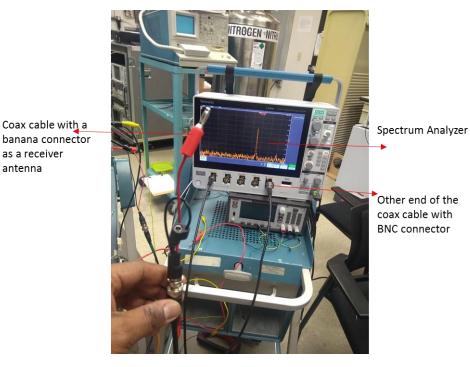

| Fig. 58. A banana connector hooked to a coaxial cable with BNC termination acting as an antenna  |

|--------------------------------------------------------------------------------------------------|

| to receive the transmitted signal from the Colpitts oscillator                                   |

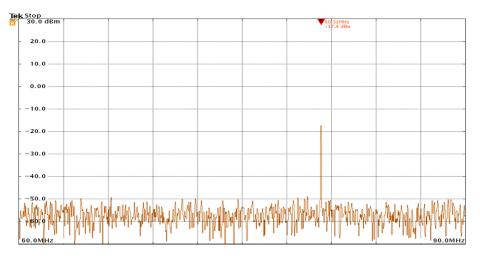

| Fig. 59. Colpitts oscillator (Fraunhofer module) output signal centered at 80.31 MHZ detected on |

| the spectrum analyzer                                                                            |

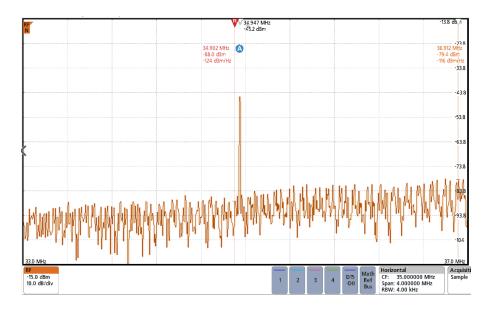

| Fig. 60. Colpitts oscillator (RUK module) output signal centered at 34.94 MHz detected on the    |

| spectrum analyzer                                                                                |

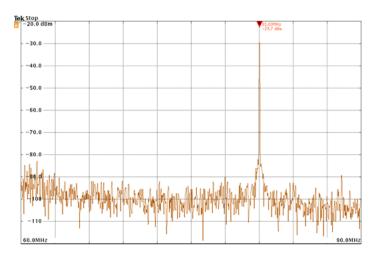

| Fig. 61. Colpitts oscillator output signal detected on a spectrum analyzer at 500°C              |

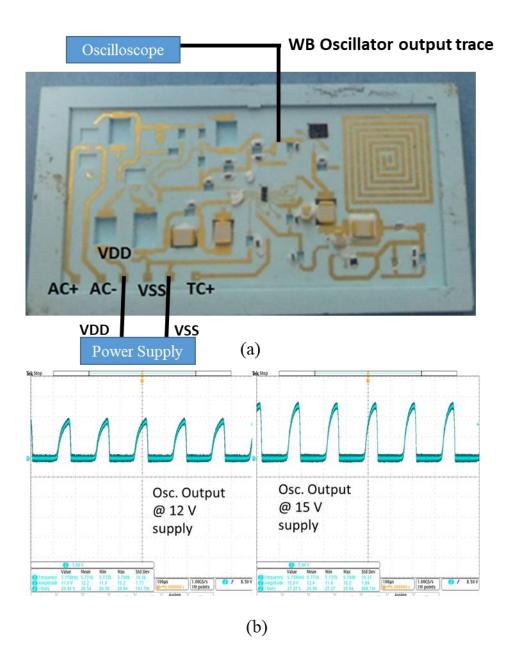

| Fig. 62. (a) Test setup to detect the Wien-Bridge oscillator output on the RUK module, (b) Wien- |

| bridge (WB) oscillator output                                                                    |

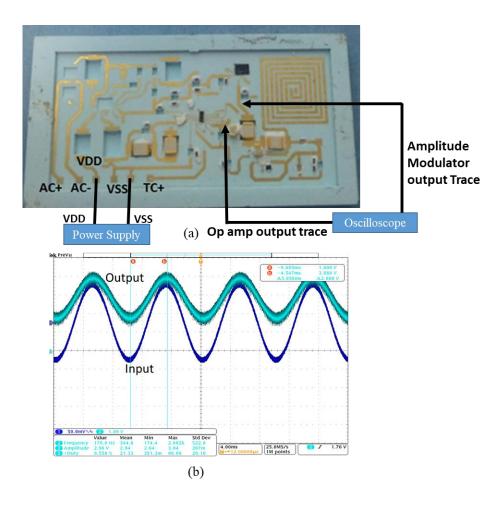

| Fig. 63. (a) Test setup to detect the op amp and amplitude modulator output on the RUK module,   |

| (b) RUK SiC op amp output for a sinusoidal input on the RUK module                               |

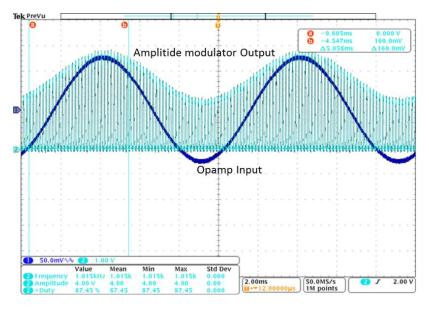

| Fig. 64. Amplitude modulator output on the RUK module                                            |

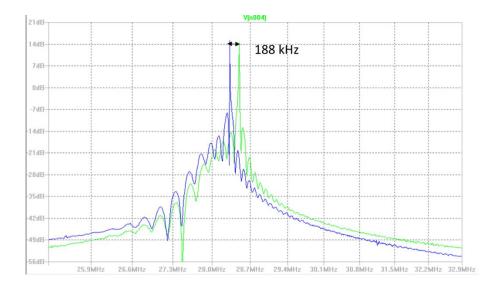

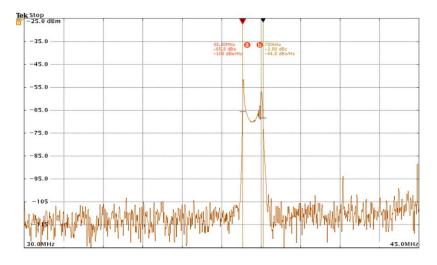

| Fig. 65. Frequency modulated signal from the RUK module detected on the spectrum analyzer.       |

|                                                                                                  |

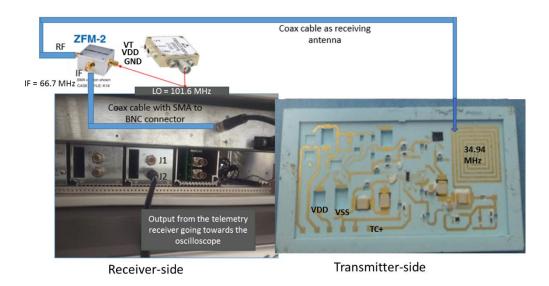

| Fig. 66. Bench-top setup of the receiver module to demodulate the FM signal from the RUK         |

| module                                                                                           |

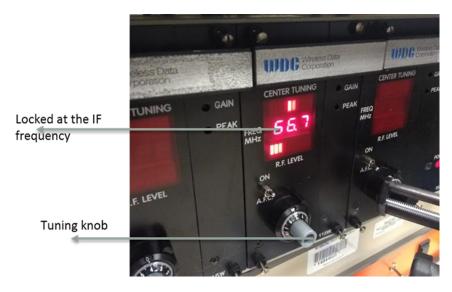

| Fig. 67. Front-side view of the receiver unit locked at the intermediate frequency (IF)          |

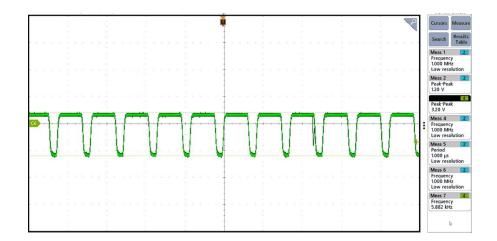

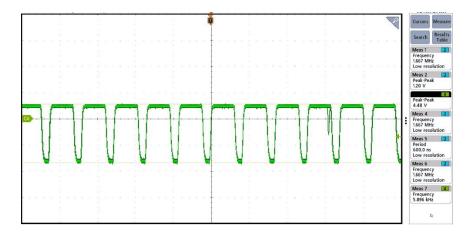

| Fig. 68. Demodulated output from the receiver unit (top) for 100 mV input to the RUK SiC op      |

| amp and (bottom) 150 mV input to the RUK SiC op amp                                              |

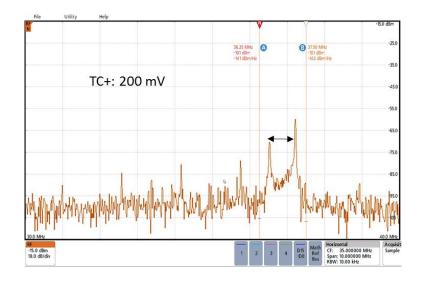

| Fig. 69. Observed distortion of the demodulated output for 200 mV applied input to the RUK SiC   |

| op amp                                                                                           |

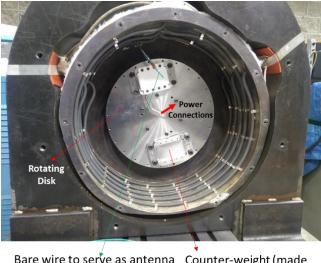

| Fig. 70. Spin-rig setup with the CMC housing (RUK module inside) mounted on the bracket          |

| attached to the spinning disk                                                                    |

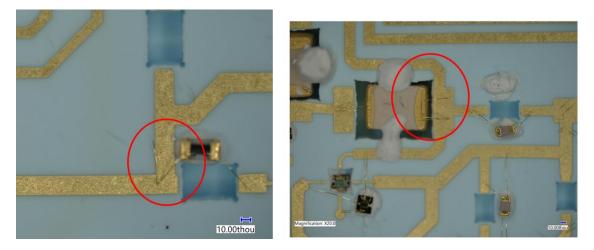

| Fig. 71. Visible cracks on the RUK module post-spin-testing.                                  | 97       |

|-----------------------------------------------------------------------------------------------|----------|

| Fig. 72. Visible wirebond tear on the RUK module post-spin-testing                            | 98       |

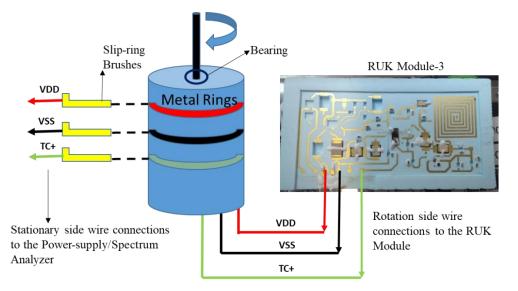

| Fig. 73. Assembled RUK module-3 for the second spin-testing with block diagram of the sl      | lip-ring |

| setup                                                                                         | 99       |

| Fig. 74. (Left) Bracket mounting of the new RUK module within the CMC housing for             | second   |

| spin testing, (right) bracket with the CMC housing attached to the spin disk                  | 99       |

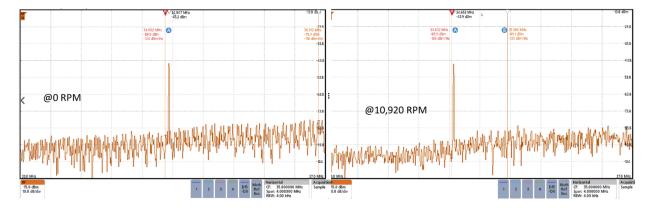

| Fig. 75. Spectrum analyzer output detecting the Colpitts oscillator signal at – (left) 0 rpm, | (right)  |

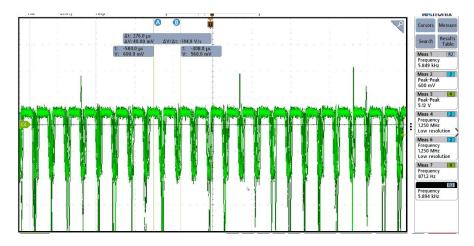

| 10,920 rpm                                                                                    | 100      |

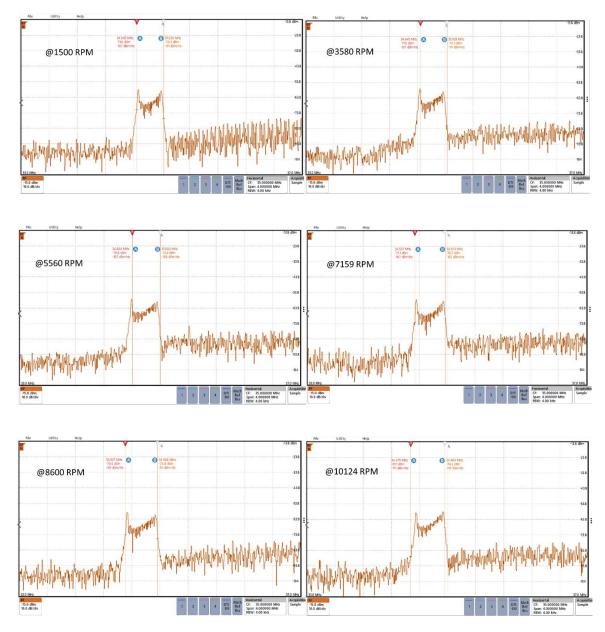

| Fig. 76. Spectrum analyzer detection the FM signal from the RUK module at $VDD = 7 V.$ .      | 101      |

| Fig. 77. Spectrum analyzer output showing a variation on the detecting FM signal due to the   | change   |

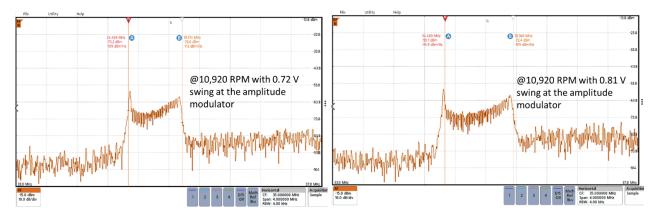

| in the swing of the amplitude modulator output.                                               | 102      |

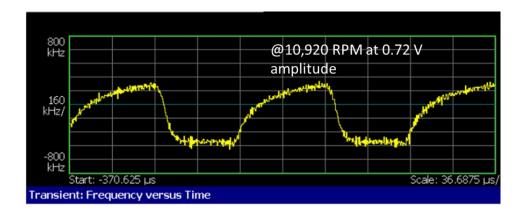

| Fig. 78. Real-time spectrum analyzer detecting RUK module output during the spin test, sh     | howing   |

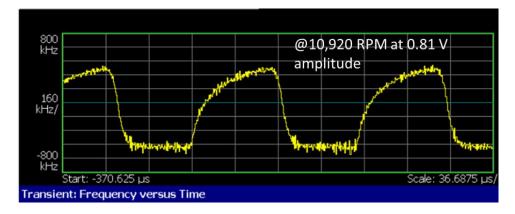

| the frequency vs. time plot for - 0.72 V amplitude and 0.81 amplitude from the AM circuit     | 103      |

| Fig. 79. Visible wirebond tear (non-critical) on the RUK module used for second spin testi    | ng.103   |

| Fig. 80. Wire assembly on RUK module-3 for both temperature and spin-testing.                 | 104      |

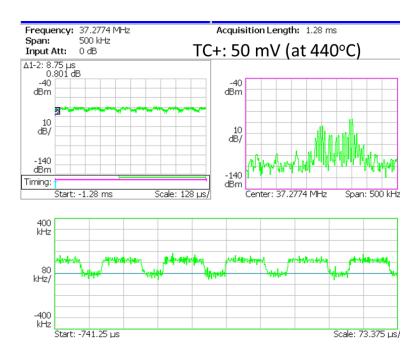

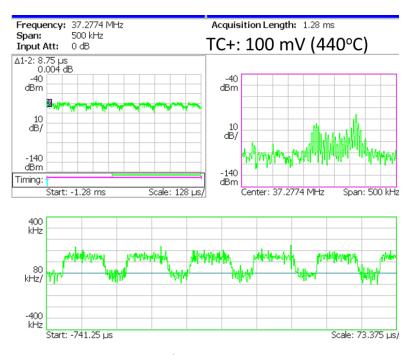

| Fig. 81. RUK module-3 output at 440°C for 50 mV DC input to the sensor amplifier              | 105      |

| Fig. 82. RUK module-3 output at 440°C for 100 mV DC input to the sensor amplifier             | 106      |

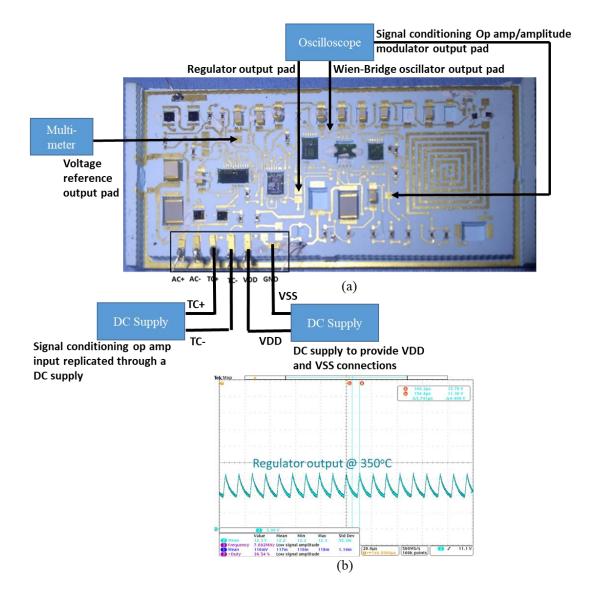

| Fig. 83. (a) Test setup configuration for individual circuit testing on the Fraunhofer mode   | ule, (b) |

| Fraunhofer SiC Regulator output on the Fraunhofer module at 350°C.                            | 108      |

| Fig. 84. Visible damage (red-circled) on the reference circuit die due to VDD trace blow      | ving up  |

| during $350^{\circ}$ C testing with a static current draw of 35 mA at VDD = 30 V              | 109      |

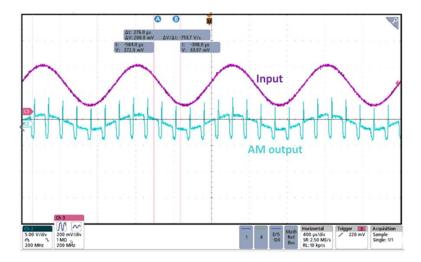

| Fig. 85. Amplitude modulator output on the Fraunhofer module at 25°C                          | 109      |

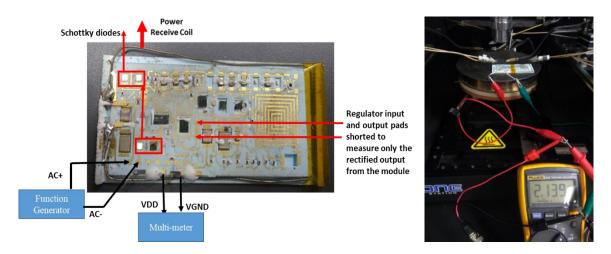

| Fig. 86. (Left) Half-wave rectifier assembly on the dummy/spare Fraunhofer module, (right)            |

|-------------------------------------------------------------------------------------------------------|

| bench-top setup for the half-wave-rectifier test with wireless power transfer                         |

| Fig. 87. (Left) Module configuration to test the full-bridge rectifier, (right) robe station setup to |

| test the full-bridge rectifier circuit on the Fraunhofer module over temperature                      |

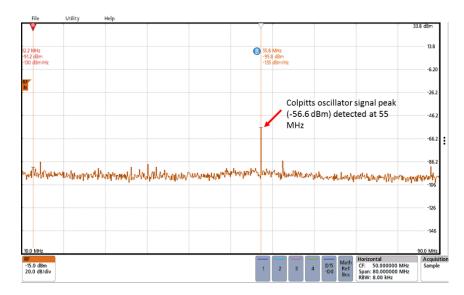

| Fig. 88. Colpitts oscillator output on the Fraunhofer module at 5 V prior to the wireless power       |

| transfer/delivery test                                                                                |

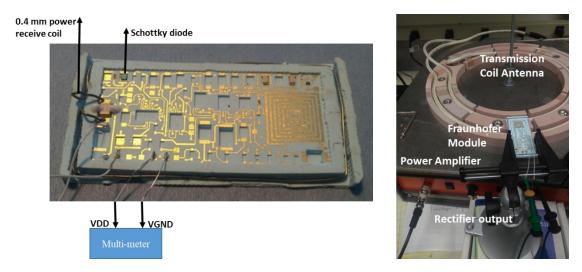

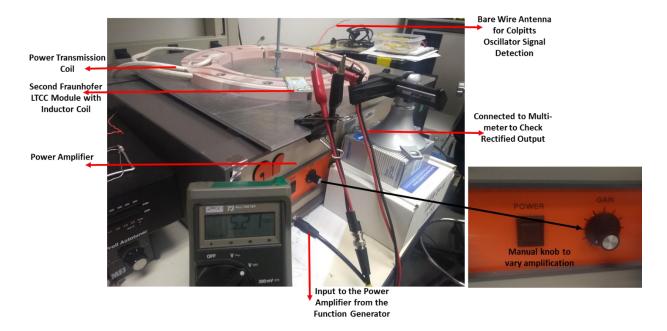

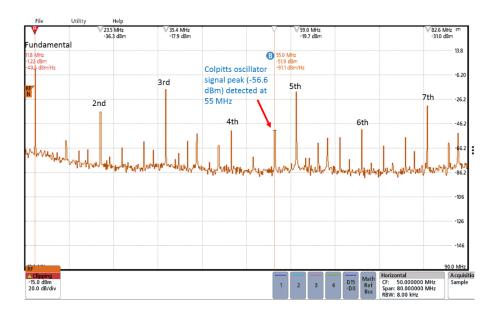

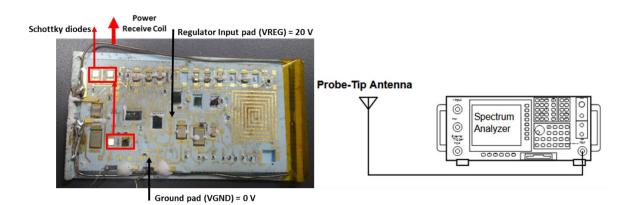

| Fig. 89. Bench-top setup for testing the wireless power transfer with full-bridge rectifier powering  |

| the Colpitts oscillator                                                                               |

| Fig. 90. Spectrum analyzer output detecting the wireless power transmission frequency, its            |

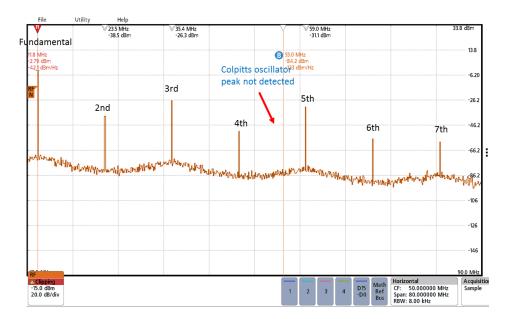

| harmonics, and the Colpitts oscillator output frequency                                               |

| Fig. 91. Spectrum analyzer output detecting the wireless power transmission frequency and its         |

| harmonics but not the Colpitts oscillator output frequency                                            |

| Fig. 92. Configuration of the Fraunhofer module for the full-system testing                           |

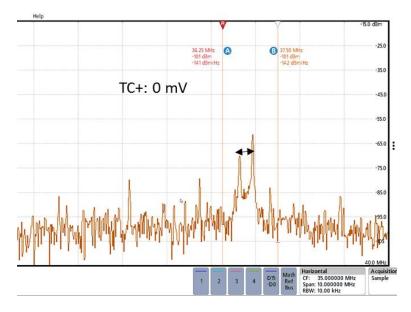

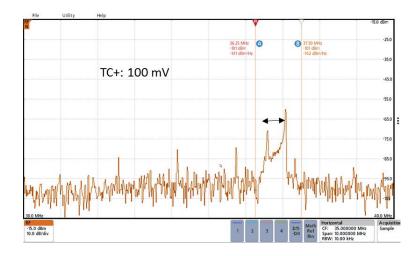

| Fig. 93. Spectrum analyzer output for the Fraunhofer module-2 signal conditioning system testing      |

| at 300°C                                                                                              |

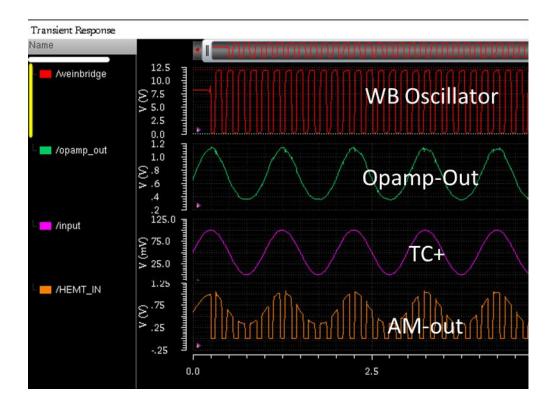

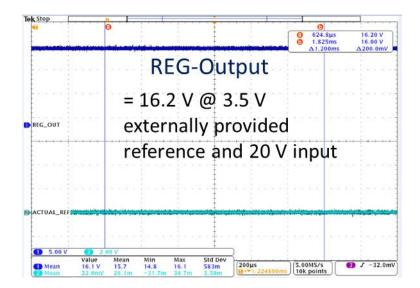

| Fig. 94. Fraunhofer module-3 regulator output 122                                                     |

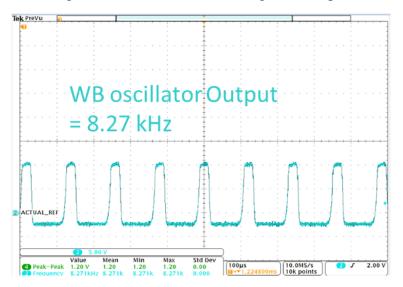

| Fig. 95. Fraunhofer module-3 Wein-Bridge oscillator output 122                                        |

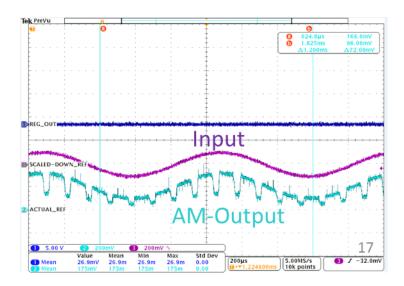

| Fig. 96. Fraunhofer module-3 amplitude modulator output 123                                           |

| Fig. 97. Fraunhofer module-3 signal conditioning op amp output 123                                    |

# List of Tables

| Table I. Initial system specification of the circuits for the signal conditioning system       |

|------------------------------------------------------------------------------------------------|

| Table II. Measured specifications of the Raytheon Module    8                                  |

| Table III. Measured specifications of the Fraunhofer Module                                    |

| Table IV. PFET-to-NFET Drain current ratio from PASS0 run for different W by L sizing 21       |

| Table V. Contact resistivity/sheet resistance for n+ and p+ regions of all the PASS0 wafers 21 |

| Table VI. PASS1 wafer splits.    25                                                            |

| Table VII. Contact resistivity of p+ region from pass1 wafers                                  |

| Table VIII. Simulated DC for the Fraunhofer SiC CMOS PASS1 designed circuits using PASS0       |

| fitted model                                                                                   |

| Table IX. Layout area and pad counts for the Fraunhofer SiC CMOS PASS circuits                 |

| Table X. The output of the reference circuit vs. input supply at 25°C                          |

| Table XI. Reference circuit output (scaled down) over temperature for $VDD = 20 V$             |

| Table XII. Passive components for the RUK module and their footprint codes                     |

| Table XIII. WB oscillator output across temperature and supply voltage                         |

#### **Chapter 1. Introduction**

#### 1.1. Motivation

There is a need for increased efficiency and reduced emissions from applications like combustion engines or natural-gas driven power generators due to their impact on global greenhouse gas emissions. In the case of the gas-fueled power generators, the system uses turbines that have multiple components that operate under extreme temperature (>> 350°C), pressure/G-force (> 10,000 RPMs or 16,000-Gs), and a corrosive environment resulting in degradation of these components. These degradations will lead to the failure of critical components like the turbine blades and eventually affect the power generation system's efficiency and increase the cost of producing electric power. To counter these issues, research and development of long-term monitoring capability of the turbines' components are necessary. Such effort would require sensors with signal conditioning, power supply, and interfacing electronics to operate under the gas turbines' harsh ambient conditions. Established process nodes on bulk silicon or silicon-oninsulator (SOI) can provide excellent electrical performance. However, at temperatures above 350°C compounded with 16,000 G force (due to high rotation speed), silicon electronics cannot sustain such conditions. The intrinsic carrier concentration of silicon rises significantly at high temperatures, causing high leakage current to flow, resulting in channel flooding, excess carriers, and thermal runaway to eventual device damage. SOI process nodes can handle up to 300°C, above which the SOI circuits' functionality and reliability degrade [1]. Besides, sustaining the combination of the temperature and high G-force will be challenging for SOI devices.

Wide-bandgap materials and the research in silicon carbide (SiC) integrated electronics [2] can provide the platform to design the sensor front-end electronics that can operate at the extreme ambient conditions. SiC electronics can provide the capability to perform long-term component health monitoring for gas-powered generator systems. Siemens has implemented Chromel-Chromel thermocouple sensors inserted on the gas turbine blades to monitor the component's health. However, such thermocouples' sensed signal is in 10s to 100s of millivolts in range and therefore requires a signal conditioning system to boost the sensed signal. In addition to that, modulation schemes and signal transmission capability are also necessary as receiving the conditioned sensed signal through a wired medium will result in signal loss. Finally, the signal conditioning circuits require power to operate. Henceforth, the supportability of power delivery through both wired and wireless mediums must be present with limited wire feedthrough paths.

Previously, such sensor electronic systems [3], [4] have been designed on ceramic modules using a SiC JFET process from the NASA Glenn Research Center [5]. The developed sensor electronic system using the SiC JFET circuits was tested at high-temperature. However, no literature was found mentioning the electronic system operating under high rotational speeds or high G-force of above 10,500 RPM. Additionally, the JFET signal conditioning system lacked an op amp for sensor signal amplification, instead used only a differential amplifier which makes the gain of the amplifier difficult to control. In the op amp case, the gain can be controlled by using a ratioed resistor under closed-loop. The Glenn Research Center has performed more than a decade of research in developing the SiC JFET devices and has shown SiC circuits operating at 500°C for long hours [6-8]. However, the process does suffer from long fabrication times along with lacking the compatibility of a complementary device, requires dual-rail supplies, and is incapable of incorporating any compact digital circuit block for mixed analog-digital (i.e., mixed-signal) circuits. Other reported SiC processes include a bipolar process from KTH and the, now defunct, SiC CMOS process (called HiTSiC<sup>®</sup>) from Raytheon Systems Limited in the United Kingdom (RUK).

The SiC bipolar circuits from KTH have previously shown the capability of operating at 500°C. However, similar to the JFET, the process only supports a non-scalable NPN device and, due to the bipolar nature, exhibits high power dissipation [9-13]. The wafer-to-chip turn-around time for this bipolar process is approximately eight months.

The SiC CMOS process from Raytheon UK (RUK), in collaboration with the University of Arkansas (UA), demonstrated analog and complex mixed-signal circuits capable of operating at temperatures above 350°C [14-17]. The op amps in the Raytheon process had shown functionality at 400°C, and digital circuits like the ring oscillator had shown to sustain operation for 30 hours at 470°C. However, with the Raytheon SiC foundry's shutdown back in 2017, a renewed interest in developing another SiC CMOS process technology has grown. Later on, the UA IC-MSCAD team collaborated with the Fraunhofer IISB foundry to develop the process flow, form design rules, and create integrated circuits with higher density and temperature sustainability on a new SiC CMOS process [18]. Therefore, the target with a newly developed SiC CMOS process would be to support the design and operation of the electronic modules or systems to perform signal conditioning of sensed signals under the extreme ambient specifications.

### 1.2. Design Approaches

As the research is directed towards a signal conditioning system design on LTCC material using the advantages of SiC integrated circuits operating at temperatures of 350°C and above, three design approaches, based on three different process-technologies, have been investigated to realize the signal conditioning system with wired and wireless power delivery. Fig. 1 shows the top-level block diagram of the three design approaches.

Fig. 1. Top-level design approaches for signal conditioning system: (i) SiC bipolar based, (ii) 1.5 μm new SiC CMOS (Fraunhofer) based, and (iii) 1.2 μm old SiC CMOS (Raytheon) based.

The first two design approaches are intended to operate with both wired and wireless power supplies, whereas the third approach would only support wired power supply. The third design approach uses the old SiC CMOS process from Raytheon that lacks the reference circuit that would meet the requirement for the regulator circuit. The regulator circuit on the Raytheon process requires separate biasing circuitry for the internal op amp which would mean insertion of additional components. The system is intended to operate above 400°C while sustaining functionality after thermal cycling. This means the signal conditioning system needs to function at room temperature after a successful operation at high-temperature. The first two design approaches would facilitate the fabrication of new circuits to support wireless power delivery, shown in Table I. The first design approach involves the complete signal conditioning system design in a SiC bipolar process that requires dual (positive and negative voltage rails) supplies. This is necessary to lower the common-mode of the sensor amplifier (op amp) in order to amplify low voltage signals from thermocouple sensors. To realize the negative rail, a charge pump and oscillator circuit are required. The positive rail will be provided from the regulator, which stabilizes the rectified output from the rectifier circuit. The SiC bipolar circuits are intended to operate at 500°C as the process has previously shown circuits that operated at 500  $^{\circ}$ C. For the second design approach on the new SiC CMOS process, a new reference and regulator circuit are designed to regulate the rectified

output. The circuits on this new SiC CMOS process are designed on two separate metallizations - (i) Aluminum (Al) and (ii) Platinum (Pt) - with the latter intended to operate at temperatures up to  $500^{\circ}$ C with repeatability of circuit functionality after thermal cycling. The aluminum metallization circuits are intended for operation at  $350^{\circ}$ C.

| Speed                                    | Design<br>Approach 1                          | Design<br>Approach 2  | Design<br>Approach 3                |

|------------------------------------------|-----------------------------------------------|-----------------------|-------------------------------------|

| Specs                                    | Range/Value<br>(unit)                         | Range/Value<br>(unit) | Range/Value<br>(unit)               |

| Rectified<br>Supply                      | 20-30 V                                       | 20-30                 | -                                   |

| Regulated<br>VDD/VCC                     | 10 V                                          | 15 V                  | 9-12 V                              |

| VSS/VEE                                  | - 4V                                          | 0 V                   | 0 V                                 |

| Max. Operable<br>Temperature             | $450^{\circ}\mathrm{C}-500^{\circ}\mathrm{C}$ | 400°C - 450°C         | 350°C (Al)<br>450°C – 500°C<br>(Pt) |

| Reference<br>Voltage for<br>Regulator    | 4.5 V – 5 V                                   | 3.5 V – 4.5 V         | -                                   |

| System current<br>consumption            | 30 mA                                         | 30 mA                 | 10 mA                               |

| Center<br>frequency for<br>FM modulation | 30 - 40 MHz                                   | 30 - 40 MHz           | 30 - 40 MHz                         |

Table I. Initial System Specification of the Circuits for the Signal Conditioning System

#### 1.3. Research Objectives

In addition to designing integrated circuits in SiC bipolar and the new CMOS process technologies, the broader objective of this research was to develop and assemble a signal-conditioning system on a low-temperature co-fired ceramic (LTCC) module using SiC circuits that could be embedded with the sensors on the turbines or combustion engines of gas-fueled power generators. The electronic module should operate both at high-temperature and high rotational speeds/G-force to allow continuous monitoring of the key components within the turbine system. The application requirements pose significant challenges in selecting the circuit components to design the signal conditioning system including: transmit/receive the sensed signal, passive parts, epoxy materials, and wiring. Assembly methods and techniques to deliver power over the wireless medium to the circuits was also a challenge. The purpose of this research involves addressing these challenges in the following steps:

- a. Selection of SiC process (KTH-Bipolar or Fraunhofer-CMOS) and carry out fabrication runs in two phases – (i) first tapeout intended to characterize the device structures to understand the issues and limitation of the process. (ii) second tapeout intended to utilize the results from device characterization to design SiC analog circuits for fabrication

- b. Test and characterize the fabricated circuits over temperature for functionality and performance analysis. Based on the results, select the circuits to implement the signal conditioning system

- c. Design the signal conditioning module with signal transmission capability in two phases

(i) Implement the first module with the proven and functional circuits from Raytheon SiC CMOS, or HiTSiC<sup>®</sup>, process, and (ii) Implement the second module design with recently fabricated circuits from KTH-Bipolar and Fraunhofer-CMOS processes

- d. Establish the setup to receive the signal from the module and also the method to deliver power to the circuits on the module

- e. Establish the assembly method to attach the components and wiring to the module to support high-temperature and high rotational speed testing

6

#### 1.4. Key Contributions

The dissertation establishes few key contributions to the research areas of high-temperature SiC CMOS circuit design and high-temperature telemetry module design in LTCC material. These important contributions discussed in this dissertation are listed below:

- a. Design of low quiescent signal conditioning circuits in SiC bipolar process technology

- b. Design different multi-stage op amp topologies in a new SiC CMOS process technology

- c. Design the first op amp based reference circuit in SiC CMOS process

- d. Design multiple electronic modules on LTCC material with SiC circuits from Raytheon and Fraunhofer to implement the signal conditioning system with signal transmission capability

- e. Successful testing of the signal conditioning system on the Raytheon LTCC module at temperature up to 440°C and rotational speed of 10,920 RPM

- f. Layout methods on LTCC modules to implement wireless power transfer resonant inductive coupling

- g. Develop wire-assembly methods on LTCC modules to support spin testing at high-speed and high-temperature

- h. Verification of wireless power transfer with SiC CMOS circuits

- i. Published two articles [21], [36] and one under revision [37] in reputed peer-reviewed journals on topics related to the research described in Chapter 2 and Chapter 3 of this dissertation.

Table II and Table *III* show the summarized measured specifications of the different versions of the Raytheon and Fraunhofer modules. Both modules are designed with dimensions of 68.5 mm by 34.3 mm. Raytheon module-1 had multiple via openings resulting in the module not being used for system assembly, testing, or verification.

| Supports wired<br>power delivery                                                 | Raytheon<br>Module-2    | Raytheon<br>Module-3    | Comments                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------|-------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applied supply<br>range                                                          | 9 - 12 V                | 9 - 12 V                |                                                                                                                                                                                                                                                                         |

| Current Draw at 25°C                                                             | 4 mA                    | 6 mA                    |                                                                                                                                                                                                                                                                         |

| LC-tank oscillator<br>source resistance                                          | 2.4 kΩ                  | 1.6 kΩ                  |                                                                                                                                                                                                                                                                         |

| Transmission center<br>frequency                                                 | 34.25 MHz               | 34.94 MHz               |                                                                                                                                                                                                                                                                         |

| High-speed test                                                                  | Failed at 10,124<br>RPM | Passed at 10,920<br>RPM |                                                                                                                                                                                                                                                                         |

| Temperature test                                                                 | Functioned at 350°C     | Functioned at<br>440°C  | The second iteration of<br>module-2 failed to<br>provide signal<br>transmission above 410°C<br>due to higher source<br>resistance (the first<br>iteration got damaged<br>during high-speed<br>testing). Module-3<br>operated at 440°C due to<br>lower source resistance |

| System function<br>repeatability at<br>room temperature<br>after thermal cycling | Passed for full system  | Passed for full system  |                                                                                                                                                                                                                                                                         |

| Lowest sensor input<br>signal applied to<br>detect frequency<br>deviation        | 50 mV                   | 50 mV                   | The signal applied to the<br>signal conditioning op<br>amp (op amp input offset<br>is below 30 mV for op<br>amps on both the<br>modules)                                                                                                                                |

Table II. Measured Results of the Raytheon Modules

| Supports wired<br>and wireless<br>power delivery                                    | Fraunhofer<br>Module-1                                              | Fraunhofer<br>Module-2                | Fraunhofer<br>Module-3                           | Comments                                                                                                                                                      |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rectified supply                                                                    | 20 V                                                                | 20 V                                  | 20 V                                             | (maximum can go up<br>to 25 V due to<br>minimizing leakage<br>current)                                                                                        |

| Current Draw at<br>at 25°C                                                          | 19 mA                                                               | 19 mA                                 | 21 mA                                            |                                                                                                                                                               |

| LC-tank oscillator<br>source resistance                                             | 1.6 kΩ                                                              | 1.6 kΩ                                | 1.5 kΩ                                           |                                                                                                                                                               |

| Transmission<br>center frequency                                                    | failed                                                              | 34.25 MHz                             | 34.94 MHz                                        | The transmission<br>circuit failed to<br>operate on the<br>module-1                                                                                           |

| High-speed test                                                                     | -                                                                   | -                                     | -                                                | Fraunhofer modules<br>not tested at high-<br>speed                                                                                                            |

| Temperature test                                                                    | Op amp<br>failed and<br>regulator<br>output<br>unstable at<br>350°C | Full system<br>functioned at<br>300°C | Individual<br>circuits<br>functional at<br>350°C | Module-2 provided the<br>full system<br>functionality with<br>modulated signal<br>transmission. Tested at<br>300°C due to use of<br>95/5 Pb/Sn solder         |

| System function<br>repeatability at<br>room temperature<br>after thermal<br>cycling |                                                                     | Passed for full<br>system             | Passed (for<br>individual<br>blocks)             | Failure of the signal<br>conditioning op amp<br>die                                                                                                           |

| Lowest sensor<br>input signal<br>applied to detect<br>frequency<br>deviation        |                                                                     | 50 mV                                 | 50 mV                                            | The signal is applied<br>to the signal<br>conditioning op amp.<br>Op amps on module-2<br>and module-3 have 1.8<br>V and 0.6 V of input<br>offset respectively |

Table III. Measured Results of the Fraunhofer Module

## 1.5. Dissertation Outline

The main contents of this dissertation are divided into four chapters:

• Chapter 2: Silicon Carbide Process Selection and Device Characterization

- Chapter 3: Overview of Designed Silicon Carbide Circuits in the Fraunhofer CMOS Process

- Chapter 4: Silicon Carbide Signal Conditioning System Prototypes on LTCC

- Chapter 5: LTCC Module Test Results

#### Chapter 2. SiC Process Selection and Device Characterization

This chapter focuses on detailing the two SiC processes investigated to design the circuit blocks required to realize the extreme environment signal conditioning system. Two fabrication runs with the SiC bipolar process from the KTH Electrum lab were completed, with each run taking approximately eight months of turnaround time from submission to completion (i.e., wafer-to-chip). The first bipolar run (or PASS0) focused on developing functional analog circuit blocks (op amp, charge pump, regulator, and reference circuit) with a low quiescent current. The second bipolar run (or PASS1) focused on improving the circuit performance from PASS0.

Similar to the bipolar run, the SiC CMOS process from Fraunhofer IISB was used for two fabrication runs, with the first tape-out (PASS0) requiring 18 months of wafer-to-chip turnaround time and the second tape-out (PASS1) requiring nine months. The PASS0 run was intended to establish the SiC CMOS fabrication flow and characterize fabricated devices for high-temperature operation. The PASS1 run focused on improving the fabrication flow, minimizing the shortcomings observed on the PASS0 run, and design fundamental analog circuit blocks (op amp, reference generator, voltage regulator, and oscillators).

#### 2.1. SiC Bipolar Process: KTH PASS0 and PASS1 Fabrication Runs

The SiC bipolar fabrication is ion implantation-free. All the necessary base, collector, and emitter nodes on the transistor are formed by etching each layer. Both the PASS0 and PASS1 followed the same fabrication steps. The complete fabrication flow for this bipolar process, including the routing metallization, has been illustrated in detail in the literature [19], [20]. The description of the circuit operation and performance over temperature from PASS0 are also detailed in the literature [21], [22]. This dissertation paper will not describe the fabrication flow/steps for the SiC

bipolar process and the PASS0 circuit performance. Instead, this section will briefly describe the designed circuits for PASS1 and discuss the reason for the circuits' post-fabrication failure.

The PASS1 run, similar to PASS0, used CREE's 100 mm 4H-SiC wafers. Two wafers were fabricated in the PASS1 run. Each wafer has 58 reticles diced on 10 mm  $\times$  5 mm individual die. Each of these reticles is later sub-diced in two 5 mm  $\times$  5 mm die for testing and characterization. The images for the two 5 mm  $\times$  5 mm diced die are shown in Fig. 2. All the diced 5 mm  $\times$  5 mm die include non-scalable 40 µm  $\times$  15 µm NPN structures. All the circuits are designed using this 40 µm  $\times$  15 µm NPN device, which imposes fairly strict limitations. Fig. 3 shows the mapping of the NPN transistor current gain variation across the two PASS1 wafers. Fig. 4 (Left) shows the die image of the NPN transistor. The probing/connection pads on the NPN transistor are 100 µm  $\times$  100 µm. The resulting current gain for most NPN structures from the PASS1 run is comparatively lower than PASS0, which provided a current gain of greater than 90. The NPN structures from wafer #1 showed higher current gain compared to wafer #2. The die with the transistor current gain of 84 was selected to characterize the current gain variation over temperature. Fig. 4 (Right) shows the NPN transistor current gain variation over temperature.

Fig. 2. Die micrograph of the complete 10 mm by 5 mm reticle from SiC BJT PASS1 run.

Fig. 3. Wafer map showing the SiC BJT current gain variation for the two PASS1 wafers

Fig. 4. (Left) Die image of the 40 µm by 15 µm SiC NPN transistor, (Right) current gain variation of the NPN device over temperature.

The current NPN transistor's current gain decreases until 300°C, after which it starts to increase. This behavior was also observed in PASS0 NPN devices and is caused due to occurrence of two opposing phenomena over temperature. As the temperature increases from room temperature to 300°C, the emitter injection efficiency drops as more ionization takes place in the base, resulting in the drop of current gain. The drop in the emitter efficiency is due to the increase in base doping (in standard silicon base doping is kept lower to minimize recombination of emitter injected electrons) as temperature increases causing the probability of emitter injected carrier (electron) to recombine in the base to increase. However, at temperatures above 300°C, the complete ionization has already taken place but the carrier lifetime begins to increase which causes the base recombination rate to decrease resulting in a slightly improved current gain.

As addressed earlier, the designed circuits in PASS1 were meant to be improved versions of the PASS0 circuits, although the bipolar fabrication was clearly not repeatable and did not improve, or even remain the same, from PASS0 to PASS1. Nonetheless, the key circuit blocks include –

- The voltage regulator, designed to provide 12 V regulated output at 40 mA load current. The input supply variation over which the regulator was expected to operate safely was 20 to 40 V. This is due to the V<sub>CE</sub> (collector-to-emitter) breakdown for the NPN devices in both PASS0 and PASS1 was approximately 45 V.

- The voltage reference circuit with a diode clamp network was designed to provide 3.1 V reference output for a supply voltage range of 12 V to 20 V. The additional diode clamping network limits the supply voltage from crossing over 20 V.

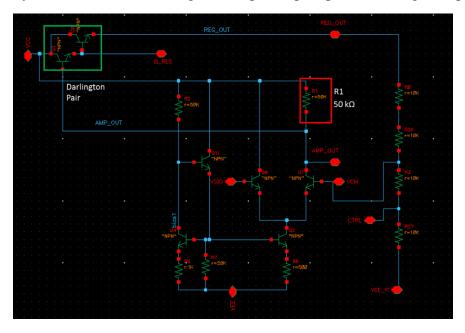

- 3. The multi-stage op amp was designed with Darlington input pair NPN transistors to increase the op amp's input impedance. The high input impedance limits sourcing current to the op amp input nodes. It is necessary for sensing applications where the thermocouple sensors cannot source current above 10 nA.

- 4. The negative charge pump circuit was designed to provide a negative supply rail as the SiC bipolar process requires a dual-rail supply to attain a low common-mode range for signal conditioning op amps.

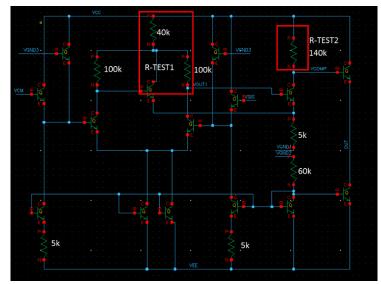

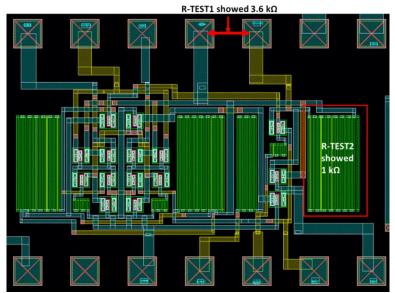

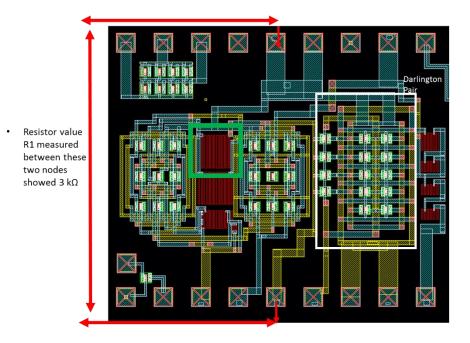

None of the circuits from PASS1 provided functionality during post-fabrication testing. The cause for the failure was traced to the large-valued collector resistors' improper fabrication [21], which were used as passive loads for all the circuits. The schematic view of Fig. 5. Schematic view of the multi-stage SiC Bipolar op amp with Darlington input pair. The layout view of Fig. 6. Layout view of the multi-stage SiC Bipolar op amp with Darlington input pair is shown in Fig. 6. The load resistor values ( $R_{TEST1}$  and  $R_{TEST2}$ ) are indicated in the figures. During post-fabrication measurements on this circuit, the measured load resistor values are significantly low. The measured values are given in Fig. 6. Layout view of the multi-stage SiC Bipolar op amp with Darlington input pair. The rest of the failed circuits showed similar problems. Fig. 7 and Fig. 8 show the schematic and layout view, respectively, for the voltage regulator circuit where the same issue with the collector resistor showing much lower values. The cause of failure of these collector resistors was traced to the incomplete etching of the collector layer on the resistor locations. As the resistors are laid out in a serpentine format using individual unit resistors, each of those unit resistors must be isolated from any nearby devices. To verify whether the isolation is formed correctly or not, after the collector layer's etching process, a pn-junction check for isolation steps were not performed, and subsequently, the issues with shorted resistors went unnoticed.

Fig. 5. Schematic view of the multi-stage SiC Bipolar op amp with Darlington input pair

Fig. 6. Layout view of the multi-stage SiC Bipolar op amp with Darlington input pair

Fig. 7. Schematic view of the SiC Bipolar linear regulator to provide 12 V, 40 mA output

Fig. 8. Layout view of the SiC Bipolar linear regulator to provide 12 V, 40 mA output

2.2. SiC CMOS Process: Fraunhofer PASS0 and PASS1 Fabrication Runs

The first fabrication run, PASS0, included six wafers to establish the design rules and validate the fabrication flow. The critical challenges in the fabrication of SiC CMOS devices to standard silicon CMOS are high-energy ion implantation and the high temperature annealing. Due to the higher bandgap energy and strength of SiC bonds in the lattice structure, the standard diffusion techniques for well or channel doping are no longer viable. Ionization energies as high as 540 keV for PWELL implantation and 810 keV for NWELL implantation are required to attain desired doping depths on the SiC wafers. Nitrogen and aluminum dopants were to create the n-type and p-type doping. The high-energy ionization leads to crystal defects, and to minimize those defects, high-temperature annealing at 1700°C is necessary. Similar to the bipolar run, both the Fraunhofer fabrication runs used Cree's N-type 100 mm 4H-SiC wafers for fabrication. Before starting the fabrication at the facility, an n+-buffer layer and a p-type (Al) epitaxial layer were grown on the wafers from Ascatron. Ten masks set were used for processing the PASS0 run. The included mask

layer names are as follows: ALIGN, NWELL, PWELL, P+, N+, ACTIVE, POLY, POLYVIA, OHMIC CONTACTs (one layer for both n/p-type contacts), and METAL-1. In the PASS1 run, two other masks were included - POLYCIDE (for poly silicidation with titanium) and PASSIVATION. The initial doping concentration levels for the wells in PASS0 were selected by the foundry using TCAD simulations to attain 50 V of blocking capability between the NWELL and PWELL/P-epi.

The PWELL and the P+ regions were patterned first, followed by the NWELL and N+ regions to fabricate the transistors. The lithography sequence caused a reduction in P+ doping levels during the etching procedure for NWELL patterning. In PASS0, 500 nm thick n-type polysilicon was deposited on all the wafers. Before the polysilicon layer deposition, a 400 nm thick field oxide layer was formed using thermal oxidation at 1400°C. The ohmic contacts for the P+ and N+ regions in the drain/source/body connections were formed via 2.6% of Nickel-Aluminum (Ni-Al) silicidation [23], [24]. All transistor structures had a minimum via-opening of 9  $\mu$ m<sup>2</sup>. Both PASS0 and PASS1 had a single layer of metallization deposited through the chemical vapor deposition (CVD) process. Two metallization options for routing and bond pad formation were explored – (i) Titanium-Aluminum stack and (ii) Platinum-Titanium stack. The aluminum metallization used the resist based etching method for patterning, and the platinum metallization used the lift-off method. Bond pads for probing the transistor structures were 100  $\mu$ m × 100  $\mu$ m in dimensions.

### 2.2.1 Transistor Characterization from Fraunhofer PASS0 Run

Initial characterization was performed at the wafer-level through measuring the threshold variation across the wafer. The second wafer, or wafer #2, was selected to plot the change in threshold for a  $20 \,\mu\text{m} \times 1.5 \,\mu\text{m}$  PFET and NFET device at room temperature. Fig. 9 shows the wafer map and the respective change in threshold voltage for both PFET and NFET devices. The critical concern is

the low threshold of the NFET devices and the high threshold voltage of the PFET devices. The SiC transistors are expected to operate at high temperatures. However, with the NFET threshold being initially low, this threshold would drop significantly at higher temperatures, resulting in an unacceptable noise margin in applications such that the devices might turn on too easily. Additionally, for PFET devices with a high threshold, any cascode amplifier approach would require a larger supply voltage headroom to allow transistors to operate safely in the saturation region.

Fig. 9. Wafer map on  $V_{TH}$  variation of 20  $\mu$ m by 1.5  $\mu$ m NFET (top) and PFET (bottom) devices from Fraunhofer SiC CMOS PASS0 run.

Further characterization included measuring the output transfer characteristics for the  $20 \,\mu\text{m} \times 1.5$ µm NFET and PFET devices from the PASSO wafer #2 using Keysight Curve Tracer. The measured gate-oxide breakdown voltage for the transistor devices is 25 V at 10 pA of gate leakage current. Hence, the input or output DC characteristic curves were performed by sweeping the  $V_{DS}$ (drain-source) and V<sub>GS</sub> (gate-source) voltages up to 20 V. Fig. 10 shows the NFET I-V plots for the applied  $V_{GS}$  0 V to 19 V and  $V_{DS}$  of 0 to 20 V. For the PFET, the applied  $V_{GS}$  and  $V_{DS}$  are 0 V to -19 V and 0 V to -20 V, respectively. The PFET-to-NFET drain-current ratio is approximately 1:25 when both the devices are operating at a gate-source voltage of 19 V. The maximum drain current for the PFET devices is expected to be lower than the NFET devices due to higher threshold and lower hole mobility. However, the P-to-N drain-current ratio for the PASS0 run is significantly worse than expected. In a standard silicon process, this ratio is often 1:2 or at worst 1:3, and in the case of the previous SiC CMOS process from Raytheon, the ratio was 1:5. Table IV shows the drain current ratio at room temperature for various channel lengths with a fixed gate-source voltage. The drain current ratio tends to improve as channel length increases, primarily due to the reduction in short channel effects at higher channel lengths. The PFET I-V characteristics show a non-ohmic behavior (red circled) at lower drain-source voltage, which indicates that the P+ ohmic contacts on the PFET are not properly silicided during fabrication. The sheet resistance and contact resistance values for the P+ and N+ region for the six PASS0 wafers at room temperature are shown in Table V. The P+ contact resistivity is high. Typically, the contact resistivity for P+ contacts is expected to be within 0.5 to 1 m $\Omega$ ·cm<sup>2</sup> in standard silicon process technologies. The N+ contact resistivity is, however, significantly lower in comparison.

Fig. 10. NFET (Left) and PFET (Right) I-V plots from PASSO wafer #1.

Table IV. PFET-to-NFET Drain Current Ratio from PASS0 Run for Different W by L Sizing

| W/L<br>(μm/ μm) | I <sub>D</sub> -Ρ<br>(μΑ) | <b>I</b> <sub>D</sub> -N<br>(μA) | Ratio |

|-----------------|---------------------------|----------------------------------|-------|

| 20/1.5          | 50                        | 1250                             | 1:25  |

| 20/2            | 41.6                      | 690                              | 1:17  |

| 20/4            | 25                        | 235                              | 1:10  |

| 20/6            | 18.4                      | 141                              | 1:8   |

| 20/10           | 13.5                      | 78.3                             | 1:6   |

Table V. Contact Resistivity/sheet Resistance for n+ and p+ Regions of all the PASS0 Wafers

| N+ in PWELL                               | W1   | W2   | W3   | W4   | W5   | W6   |

|-------------------------------------------|------|------|------|------|------|------|

| R-sheet [kΩ/sq]                           | 1.15 | 1.20 | 1.17 | 1.20 | 1.20 | 1.12 |

| Contact-resistivity [μΩ·cm <sup>2</sup> ] | 1.72 | 0.9  | 0.59 | 0.9  | 4.2  | 4.2  |

| P+ in NWELL                     | W1   | W2    | W3   | W4   | W5   | W6   |

|---------------------------------|------|-------|------|------|------|------|

| R-sheet [kΩ/sq]                 | 89.4 | 112.1 | 91.6 | 159  | 83.2 | 76.3 |

| Contact-resistivity<br>[mΩ·cm²] | 44.3 | 8280  | 162  | 58.5 | 89.2 | 86.8 |

2.2.2 PASSO Circuit Characterization and HSpice Model Parameter Extraction

The PASS0 included basic analog (two-stage op amp) and digital (standard logic gates and ring oscillators) circuit blocks designed with the minimum sized devices. Due to the unexpected poor

performance of the minimum-sized PFETs, the analog circuits failed to operate. Some digital logic gate circuits performed poorly for the same reason. Others failed due to the circuits' PFETs not being isolated. All the PFETs were fabricated within the same NWELL resulting in the wrong body-node connection for logic circuits with two cascaded PFETs.

The curve fitting and parameter extraction on the PASS0 device were performed on the IC-CAP tool. The tool utilizes BSIMv4 models to generate model parameters values from the measured transistor characteristics. The literature [25] details the steps to perform the parameter extraction tasks. Fig. 11 shows the IC-CAP plot for the 20  $\mu$ m × 1.5  $\mu$ m NFET's measured output I-V curves with I-V curves from the model. In the case of the PFETs, the curve fitting method did not include the non-ohmic diode effect observed at lower V<sub>DS</sub>. It is to be noted that the PASS1 fabrication run incorporated a number of changes concerning the fabrication of the PFETs, which would diminish the accuracy of the fit model. Regardless, the model with the extracted parameter would serve as a preliminary foundation to design the basic functional analog CMOS circuit blocks for PASS1 to develop an extreme environment signal conditioning system. The parameters were extracted for the following transistor (PFET and NFET) sizing –

- 1. For NFET: Length = 1  $\mu$ m, 1.5  $\mu$ m, 2  $\mu$ m, 4  $\mu$ m, 10  $\mu$ m, 20  $\mu$ m

- 2. For NFET: Width = 3  $\mu$ m, 5  $\mu$ m, 10  $\mu$ m, 20  $\mu$ m, 100  $\mu$ m

- 3. For PFET: Length = 1  $\mu$ m, 1.5  $\mu$ m, 2  $\mu$ m, 4  $\mu$ m, 10  $\mu$ m, 20  $\mu$ m

- 4. For PFET: Width = 7  $\mu$ m, 10  $\mu$ m, 20  $\mu$ m, 100  $\mu$ m

Fig. 11. IC-CAP plot showing the fitted I-V and the measured I-V curve for the 20  $\mu m$  by 1.5  $\mu m$  NFET device

A model netlist file in HSPICE was created to combine all the extracted parameters from the different transistor sizing. The HSPICE file allowed simulation of the designed circuits for the PASS1 fabrication with the HSPICE simulator in the Cadence<sup>TM</sup> ADE tool. As mentioned earlier, the PASS1 run would incorporate significant changes in the fabrication steps. The objective of simulating the circuits with PASS0 parameters was to observe the circuits' functionality with the sizing selection of the transistors. It also has to be mentioned that the PASS1 circuits were not subjected to any post-layout simulations with parasitic extracted models due to their unavailability.

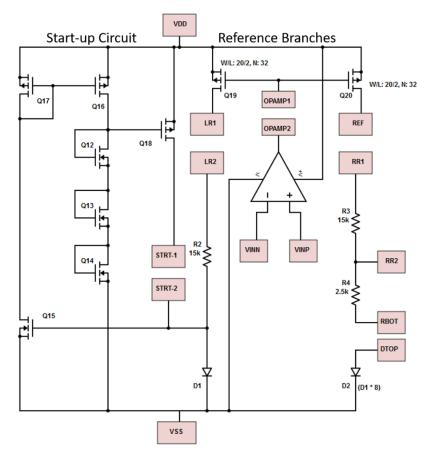

# 2.2.3 Changes in PASS1 Fabrication

The PASS1 fabrication run produced another six 100 mm 4H-SiC wafers, similar to PASS0. For PASS1 fabrication, the intention was to lower the PFET devices' threshold and, on the flip-side, increase the threshold of the NFET devices to improve the PFET-to-NFET drain-current ratio. This was attempted in two steps – (i) reducing the NWELL doping from 5E15 /cm<sup>2</sup> to 3E15 /cm<sup>2</sup> [26], and (ii) changing the n-type polysilicon to p-type to increase the NFET threshold voltage by +1 V

and lower the PFET threshold by +1 V. However, the p-type polysilicon has three times higher the sheet resistance of n-type polysilicon. The high sheet resistance would impact circuit performance as the polysilicon acts as the second routing layer. To lower the sheet resistance of p-type poly silicidation on the polysilicon, a titanium-silicide (TiSi) layer was suggested [27]. The down side to this approach is that it would introduce new processing steps that were not performed in the PASS0 run. The suggested TiSi layer was therefore decided to be applied on three wafers only. The fabrication sequence was also changed for PASS1 with NWELL implantation performed before P+ implantation to improve the P+ contact resistivity by reducing the chances of overetching of the P+ region. The Ni-Al silicidation concentration was kept the same as PASS0 for both the N+ and P+ contact regions. The NFET and PFET devices for PASS1 also included an NWELL isolation layer to provide electrical isolation for the transistors and reduce body effect issues. The cross-sectional diagrams for the SiC NFET and PFET for PASS1 in Fig. 12 show the NWELL isolation layer.

The circuits block in the PASS1 were designed using specific transistor sizing (20/1.5, 20/2, and 20/4), with multiple "fingers" being used to increase the effective width of an FET device as necessary. The drain-current ratio between PFETs and NFETs was expected to be 1:5 with the process changes made for PASS1. However, the devices with smaller channel lengths were expected to exhibit variations due to short channel effects.

| BODY<br>IME <mark>TA</mark> L-1 | SOURCE             | DRAIN<br>METAL-1 |

|---------------------------------|--------------------|------------------|

|                                 | 2 <mark>M</mark> 🚺 |                  |

| P+                              | N+                 | N+               |

| PWELL<br>NWELL                  |                    |                  |

| P-EPI<br>SUB                    |                    |                  |

Fig. 12. Cross-section of NFET (top) and PFET (bottom) for PASS1

As the PASS1 run includes various changes over the PASS0 run, processing of the PASS1 wafers were performed in different wafer splits. Table VI shows the split plan for the PASS1 wafers. Wafer#1 and #2 had the same PASS0 doping profiles for the transistors. Wafer#1 and wafer#3 used platinum metallization that is intended to perform circuit functionality testing at 500°C temperatures. As mentioned earlier, the polysilicidation is performed only on the three wafers #1, #3, and #5.

| PASS1 wafer #         | 1  | 2  | 3  | 4  | 5  | 6  |

|-----------------------|----|----|----|----|----|----|

| Modified NWELL doping |    |    | Х  | Х  | Х  | Х  |

| PASS0 doping          | X  | Χ  |    |    |    |    |

| P-type poly           | X  | Х  | Х  | Х  |    |    |

| N-type poly           |    |    |    |    | Х  | Х  |

| Poly silicidation     | Х  |    | Х  |    | Х  |    |

| Metal-1 (Al, Pt)      | Pt | Al | Pt | Al | Al | Al |

| Passivation           | Х  | Х  | Х  | Х  |    |    |

**Table VI. PASS1 Wafer Splits**

#### 2.2.4 Transistor Characterization from Fraunhofer PASS1 Run

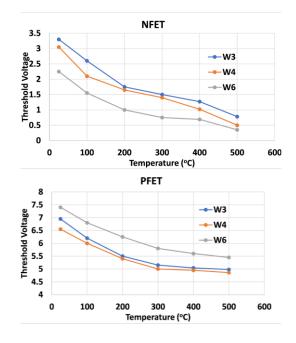

Post fabrication, the NFET and PFET devices from wafer #3, wafer #4, and wafer #6 were characterized over temperatures on the probe station. Fig. 13 shows the variation in the threshold for NFET and PFET devices from each of these wafers, with the  $20 \,\mu\text{m} / 2 \,\mu\text{m}$  dimensions, over the temperature range of  $25^{\circ}$ C to  $500^{\circ}$ C.

Fig. 13. Threshold voltage (V<sub>TH</sub>) variation over temperature for NFET (top) and PFET (bottom) from PASS1 wafers #3, #4, and #6.

As expected, for each wafer, the threshold voltage for NFET and PFET devices drops due to increased carrier concentration at higher temperatures. The key phenomenon to notice from Fig. 13 is the increase in the NFET threshold voltage and decrease in the PFET threshold voltage for wafer #3 and wafer #4 compared to wafer #6. The deposition of the p-type polysilicon, therefore, provided the expected results. The PFET and NFET threshold voltages on wafer #6 are comparable to the PASS0 results as the transistors on wafer #6 still uses n-type polysilicon. Therefore, lowering the NWELL doping did not drop the PFET device's threshold, which is unusual.

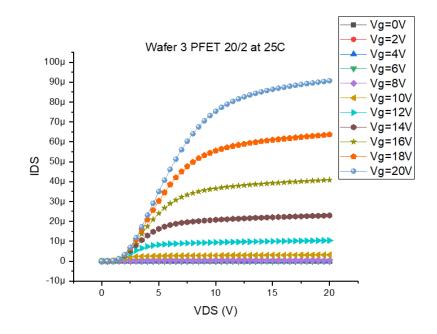

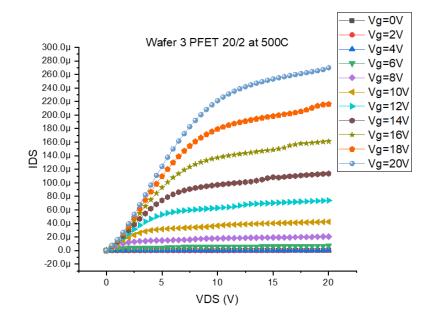

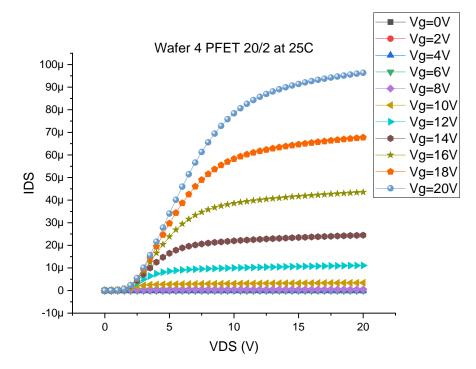

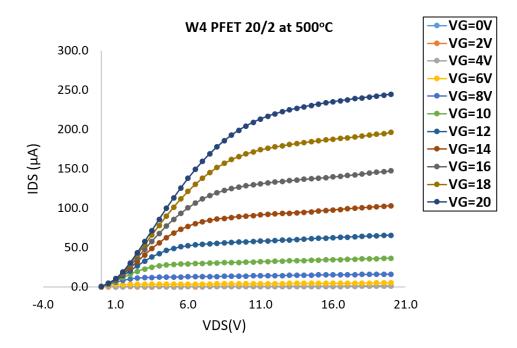

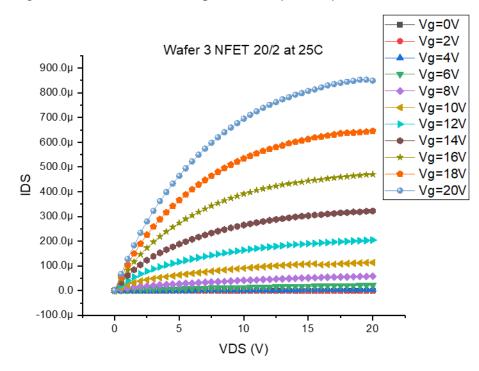

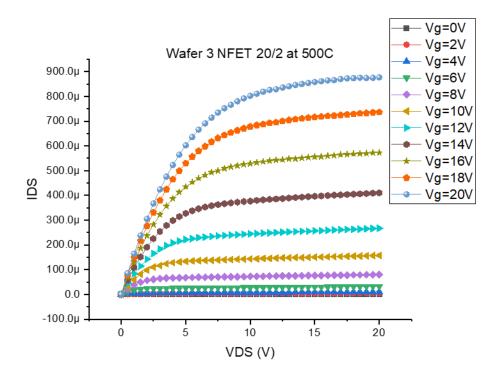

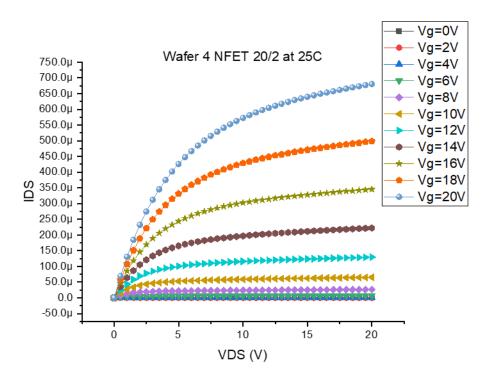

The output I-V characteristics over temperature, for the  $20 \ \mu m \times 2 \ \mu m$  PFET, from wafer #3 and wafer #4 are shown in Fig. 14-Fig. *17*. For the NFET, the output characteristics plots are shown in Fig. 18-Fig. 21. The PFET-to-NFET drain current ratio for both wafers has improved to approximately 1:8 in comparison to the PASSO value of 1:17 for the same sized transistors. However, the drain-current ratio's progress is not satisfactory compared to previous devices from the Raytheon SiC CMOS process (Appendix-1). The transistors on both the wafers show an

increase in the drain current as temperature increases. This is due to the increase in intrinsic carrier concentration and the higher rate of threshold drop. It can be shown using the I-V plots and square-law equations that the effective mobility for the PFET and NFET increases at higher temperatures. For PFET, the mobility ( $\mu_p$ ) increased by 2.5 times as temperature increased from 25°C to 500°C. In the case of the NFET, the mobility ( $\mu_n$ ) increased by 1.7 times as temperature increased from 25°C to 500°C. However, it does not reflect on the real electron or hole channel mobility behavior. The I-V plots also show non-ohmic behavior at lower V<sub>DS</sub> on the PASS1 PFET devices. The P+ contact region, or the Ni-Al material for the silicidation process. A possible replacement to Ni-Al could be titanium-aluminum (Ti-Al) [28]. At the time of writing this dissertation, the Fraunhofer IISB had already started investigating Ti-Al-based silicidation to form better P+ contacts on SiC wafers. The P+ contact resistivity for PASS1 wafers #3, #4, and #6 were measured from the transfer-length measurement or TLM structures and are shown in Table VII.

Fig. 14. PASS1 wafer #3 I-V plots for 20  $\mu$ m × 2  $\mu$ m PFET at 25 °C.

Fig. 15. PASS1 wafer #3 I-V plots for 20  $\mu$ m × 2  $\mu$ m PFET at 500°C.

Fig. 16. PASS1 wafer #4 I-V plots for 20  $\mu$ m  $\times$  2  $\mu$ m PFET at 25 °C.

Fig. 17. PASS1 wafer #4 I-V plots for 20  $\mu$ m × 2  $\mu$ m PFET at 500°C.

Fig. 18. PASS1 wafer #3, I-V plots for NFETs at 25°C.

Fig. 19. PASS1 wafer #3, I-V plots for NFETs at 500°C.

Fig. 20. PASS1 wafer #4, I-V plots for NFETs at 25°C.

Fig. 21. PASS1 wafer #4, I-V plots for NFETs at 500°C.

Table VII. Contact Resistivity of P+ Region from PASS1 Wafers

| Wafer # | Contact Resistivity (mΩ·cm <sup>2</sup> ) |

|---------|-------------------------------------------|

| 3       | 8206.93                                   |

| 4       | 8825.62                                   |

| 6       | 47813.74                                  |

The concerning observation from Table VII is the noticeably high contact resistivity for the P+ region for the PASS1 run. It is essential to mention that the fabricated circuits on the PASS1 run were designed to operate at a quiescent current under 1 mA. Therefore, any voltage drop across the highly resistive P+ contacts will be negligible.

The output characteristics for wafer #2 PFET and NFET devices, with 20/2  $\mu$ m sizing, at 25 °C and 500 °C were also measured. The maximum drain current for the NFET device showed no significant change compared to wafer #3 or #4. However, the maximum drain current for the PFET device (for example, at V<sub>GS</sub> = 20 V, I<sub>Drain</sub> = 75  $\mu$ A) was less compared to the wafer #3 and #4 PFETs

(measured  $I_{Drain} = 95 \ \mu A @ V_{GS} = 20 \ V$ ). The reason for this variation is the lowering of the NWELL doping on wafer #3 and #4, which in the case of wafer #2 is not included.