#### University of Thessaly

#### **DOCTORAL THESIS**

# Novel techniques for timing analysis of VLSI circuits in advanced technology nodes

Author:

Dimitrios GARYFALLOU

Supervisors:

Prof. Nestor EVMORFOPOULOS

Prof. Georgios STAMOULIS

Prof. Fotios PLESSAS

A thesis submitted in fulfillment of the requirements for the degree of Doctor of Philosophy

in the

Department of Electrical and Computer Engineering Electronics Lab

October 19, 2021

# **Declaration of Authorship**

I, Dimitrios Garyfallou, declare that this thesis titled, "Novel techniques for timing analysis of VLSI circuits in advanced technology nodes" and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

| Signed: |                  |  |

|---------|------------------|--|

| Date:   | October 19, 2021 |  |

Copyright © 2021 Dimitrios GARYFALLOU All rights reserved. To my family with eternal gratitude

#### UNIVERSITY OF THESSALY

#### Abstract

Department of Electrical and Computer Engineering

Doctor of Philosophy

#### Novel techniques for timing analysis of VLSI circuits in advanced technology nodes

by Dimitrios GARYFALLOU

Timing analysis is an essential and demanding verification method used during the initial design and iterative optimization of a Very Large Scale Integrated (VLSI) circuit, while it also constitutes the cornerstone of the final signoff that dictates whether the chip can be released to the semiconductor foundry for fabrication. Throughout the last few decades, the relentless demand for high-performance and energy-efficient circuits has been met by aggressive technology scaling, which enabled the integration of a vast number of devices into the same die but brought new problems and challenges to the surface. In nanometer technology nodes, on-chip VLSI interconnects are more resistive and have an ever-increasing impact on gate and interconnect delay, while nonlinear transistor and Miller capacitances imply that signals no longer resemble smooth and saturated ramps. At the same time, manufacturing process variations have become significantly more pronounced, which in turn calls for sophisticated timing analysis techniques to reduce the uncertainty in timing estimation. From another perspective, the timing guardbands enforced by the traditional design paradigm to protect circuits from variation-induced timing errors are overly pessimistic since they are estimated using Static Timing Analysis (STA) under rare worst-case timing conditions, ignoring the workload variability and leaving extensive dynamic timing margins unexploited. To this end, this dissertation presents novel techniques for accurate and efficient timing analysis of VLSI circuits in advanced technology nodes, which address different aspects of the problem, starting from gate and interconnect delay calculation and moving to timing analysis under process variation and Dynamic Timing Analysis (DTA).

In the first part of this thesis, we focus on gate and interconnect delay calculation, which is the heart of any timing analysis technique. On the gate side, we present an iterative algorithm that accurately approximates the nonlinear signal waveforms by piecewise linear ramps, using multiple effective capacitance values to take the resistive shielding effect into account. Contrary to prior works, our approach is compatible with industrial Current Source Models (CSMs), considers the Miller effect, and is computationally efficient since it relies on closed-form formulas and convergences in very few iterations. We demonstrate that our method achieves greater accuracy than related schemes that assume a single effective capacitance value or ignore the impact of Miller capacitance. On the interconnect side, we propose a sparsity-aware Model Order Reduction (MOR) technique for efficient signoff timing analysis of large interconnects with many ports. As opposed to well-established MOR techniques, our method produces sparse reduced-order models by applying key congruence transformations on the original interconnect model and then exploiting the correspondence between Laplacian matrices and circuit graphs. Moreover, the generated models can be straightforwardly realized into equivalent compact RC networks and utilized in several other analysis steps of the design flow. We show that a high sparsity ratio of the reduced system matrices can be achieved without significant accuracy loss, leading to enhanced simulation runtimes compared to a well-known MOR technique that produces dense matrices.

In the second part, we introduce a novel statistical methodology based on Monte Carlo (MC) simulation and Extreme Value Theory (EVT) for timing analysis of VLSI circuits under process variations in gate and interconnect parameters. In contrast to corner-based or traditional statistical approaches, our method provides fast yet accurate results regardless of the underlying timing models and any assumption about the propagated distributions, thus being very suitable for both transistor-level and gate-level timing analysis. Experimental results indicate that our method requires only a few thousand MC trials to yield highly accurate worst-case delay estimates, providing a speedup of six orders of magnitude over exhaustive MC simulation.

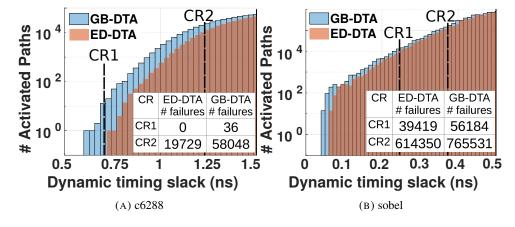

Finally, the concept of gate-level event-driven simulation is leveraged to develop an accurate DTA framework that identifies the dynamic timing slacks existing during the operation of a VLSI circuit according to the processed data. Contrary to conventional graph-based DTA that inherently relies on worst-case assumptions, the proposed event-driven DTA considers the actual data-dependent timing properties of the activated paths. Thus, it reveals significantly more dynamic timing slack, especially for the most critical paths, enabling the opportunity for substantial dynamic frequency or voltage scaling and considerably more accurate estimation of timing failures.

#### ΠΑΝΕΠΙΣΤΗΜΙΟ ΘΕΣΣΑΛΙΑΣ

# Περίληψη

Τμήμα Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών

Διδακτορικό Δίπλωμα

Καινοτόμες τεχνικές ανάλυσης χρονισμού κυκλωμάτων πολύ μεγάλης κλίμακας ολοκλήρωσης σε προηγμένες τεχνολογίες

από τον Δημήτριο ΓΑΡΥΦΑΛΛΟΥ

Η ανάλυση χρονισμού ανέκαθεν αποτελούσε το σημαντικότερο βήμα της διαδικασίας επαλήθευσης της λειτουργίας χυχλωμάτων πολύ μεγάλης χλίμαχας ολοχλήρωσης (Very Large Scale Integration - VLSI). Πρόχειται για μια χρίσιμη και απαιτητική ανάλυση, η οποία χρησιμοποιείται τόσο κατά την αρχική σχεδίαση και την επανειλημμένη βελτιστοποίηση του χυχλώματος, όσο και στην τελιχή επαλήθευση που είναι καθοριστιχής σημασίας για την ορθή κατασκευή και λειτουργία του ολοκληρωμένου κυκλώματος. Κατά τις τελευταίες δεκαετίες, η αμείλικτη ζήτηση για γρηγορότερα και χαμηλότερης ισχύος κυκλώματα VLSI ικανοποιείται με τη συνεχή κλιμάκωση της τεχνολογίας, η οποία έχει οδηγήσει σε ολοένα και πιο περίπλοκες σχεδιάσεις, φέρνοντας στην επιφάνεια νέα προβλήματα και προκλήσεις. Στις προηγμένες τεχνολογίες ολοχλήρωσης των μεριχών νανομέτρων, οι αγωγοί διασύνδεσης έχουν ολοένα και αυξανόμενη επίδραση στην καθυστέρηση του κυκλώματος, καθώς εισάγουν μεγαλύτερη παρασιτική αντίσταση, ενώ παράλληλα τα λογικά σήματα αδυνατούν πλέον να προσεγγιστούν με αχρίβεια από απλές γραμμιχές χυματομορφές λόγω των μη γραμμικών παρασιτικών χωρητικοτήτων των τρανζίστορ, συμπεριλαμβανομένων των χωρητικοτήτων Miller. Επιπρόσθετα, οι διαχυμάνσεις των σχεδιαστικών παραμέτρων γίνονται ολοένα και πιο έντονες, δημιουργώντας την ανάγκη για εξελιγμένες στατιστικές τεχνικές ώστε να μειωθεί η αβεβαιότητα κατά την ανάλυση χρονισμού. Προκειμένου να προστατέψουν τα χυχλώματα από σφάλματα που οφείλονται στις συγχεχριμένες διαχυμάνσεις, οι σχεδιαστές εισάγουν επιπλέον περιθώρια καθυστέρησης, τα οποία είναι άχρως πεσιμιστικά διότι παραδοσιακά υπολογίζονται μέσω στατικής ανάλυσης χρονισμού (Static Timing Analysis - STA) κάτω από παραδοχές χειρότερης περίπτωσης, αγνοώντας τις διαφοροποιήσεις των εισόδων, αφήνοντας έτσι ανεχμετάλλευτα εχτενή δυναμιχά περιθώρια χρονισμού. Βάσει των παραπάνω, η παρούσα διδακτορική διατριβή προτείνει νέες τεχνικές για αχριβή και αποδοτική ανάλυση χρονισμού κυκλωμάτων VLSI, οι οποίες αντιμετωπίζουν διαφορετικές πτυχές του προβλήματος, από τον υπολογισμό της καθυστέρησης πυλών και διασυνδέσεων έως και την ανάλυση χρονισμού κάτω από διακυμάνσεις των σχεδιαστικών παραμέτρων και τη δυναμική ανάλυση χρονισμού (Dynamic Timing Analysis - DTA).

Το πρώτο μέρος της διατριβής επιχεντρώνεται στον υπολογισμό της χαθυστέρησης πυλών και διασυνδέσεων, ο οποίος αποτελεί τον πυρήνα οποιασδήποτε τεχνιχής ανάλυσης χρονισμού. Σχετικά με την ανάλυση καθυστέρησης των πυλών, παρουσιάζεται ένας αχριβής επαναληπτικός αλγόριθμος, ο οποίος προσεγγίζει τα μη γραμμικά σήματα με τμηματικά γραμμικές χυματομορφές, υπολογίζοντας την ισοδύναμη χωρητικότητα των διασυνδέσεων σε πολλαπλές περιοχές, προχειμένου να λάβει υπόψη τη δυναμική της συμπεριφορά. Αντίθετα με προγενέστερες προσεγγίσεις, ο προτεινόμενος αλγόριθμος βασίζεται σε πρόσφατα βιομηχανικά μοντέλα πηγής ρεύματος (Current Source Models – CSMs), συνυπολογίζει το φαινόμενο Miller, ενώ παράλληλα είναι εξαιρετικά αποδοτικός μιας και αξιοποιεί απλές μαθηματικές εκφράσεις κλειστού τύπου για τους υπολογισμούς και επιτυγχάνει σύγκλιση εντός ελάχιστων επαναλήψεων. Η πειραματική αξιολόγηση του αλγορίθμου δείχνει πως

πετυχαίνει καλύτερη ακρίβεια σε σύγκριση με μεθόδους που είτε θεωρούν μοναδική ισοδύναμη χωρητικότητα είτε αγνοούν το φαινόμενο Miller. Όσον αφορά τους VLSI αγωγούς διασύνδεσης, προτείνουμε μια τεχνική μείωσης τάξης μοντέλου (Model Order Reduction - MOR) για ακριβή και γρήγορη ανάλυση χρονισμού μεγάλων παρασιτικών RC μοντέλων με πολλές θύρες εισόδου/εξόδου. Αντίθετα με καθιερωμένες τεχνικές MOR που οδηγούν σε πυκνούς πίνακες μειωμένης τάξης, η προτεινόμενη τεχνική προσεγγίζει τους πυκνούς πίνακες με τους κοντινότερους πίνακες που έχουν αντιστοιχία με γράφους και στη συνέχεια εφαρμόζει τεχνικές αραιοποίησης γράφων για να παράγει αραιά μειωμένα μοντέλα. Τα πλεονεκτήματα της μεθόδου είναι πως τα αραιά μοντέλα οδηγούν σε επιτάχυνση της προσομοίωσης με μικρή απώλεια στην ακρίβεια εκτίμησης της καθυστέρησης, ενώ επίσης μπορούν να μετατραπούν σε ισοδύναμα RC δίκτυα μεγέθους πολύ μικρότερου του αρχικού και να επαναχρησιμοποιηθούν κατά τη σχεδίαση.

Στη συνέχεια, εισάγουμε μια νέα στατιστική μεθοδολογία βασισμένη στην προσομοίωση Monte Carlo και στη θεωρία ακραίων τιμών, για την ανάλυση χρονισμού κυκλωμάτων VLSI υπό διακύμανση των φυσικών παραμέτρων των πυλών και των διασυνδέσεων. Συγκριτικά με τεχνικές που επικεντρώνονται στις ακραίες περιπτώσεις διακύμανσης και με παραδοσιακές στατιστικές τεχνικές, η μεθοδολογία μας δεν βασίζεται σε απλουστευμένες παραδοχές για τον τύπο της κατανομής καθυστέρησης σε κάθε κόμβο του κυκλώματος και είναι ανεξάρτητη των υποκείμενων μοντέλων καθυστέρησης, με αποτέλεσμα να είναι κατάλληλη για ανάλυση τόσο σε επίπεδο τρανζίστορ όσο και σε επίπεδο πυλών. Τα πειραματικά αποτελέσματα υποδεικνύουν ότι η συγκεκριμένη μέθοδος απαιτεί μόλις μερικές χιλιάδες δοκιμές Monte Carlo ώστε να παρέχει γρήγορη και ακριβή εκτίμηση της χειρότερης καθυστέρησης, επιτυγχάνοντας έως και έξι τάξεις μεγέθους επιτάχυνση συγκριτικά με μια πλήρη προσομοίωση Monte Carlo.

Τέλος, αναπτύσσεται ένα εργαλείο DTA βασισμένο σε προσομοίωση επιπέδου πύλης οδηγούμενη από γεγονότα (event-driven gate-level simulation), το οποίο υπολογίζει με αχρίβεια τα δυναμικά περιθώρια χρονισμού που υπάρχουν κατά τη λειτουργία του κυκλώματος σύμφωνα με τα επεξεργαζόμενα δεδομένα. Σε αντίθεση με συμβατικές graph-based μεθόδους, οι οποίες θεωρούν καθυστερήσεις χειρότερης περίπτωσης σε κάθε στοιχείο του κυκλώματος, η προτεινόμενη event-driven DTA προσέγγιση λαμβάνει υπόψη τα πραγματικά χαρακτηριστικά χρονισμού των ενεργοποιημένων μονοπατιών. Έτσι, αναδεικνύει σημαντικά περισσότερα δυναμικά περιθώρια χρονισμού, ειδικά για τα κρισιμότερα μονοπάτια, προσφέροντας τη δυνατότητα για αξιοσημείωτη δυναμική μεταβολή της συχνότητας λειτουργίας και της τάσης τροφοδοσίας του κυκλώματος, παρέχοντας παράλληλα ακριβέστερη εκτίμηση των σφαλμάτων χρονισμού.

## Acknowledgements

As this long endeavor has reached its end, I would like to express my sincere gratitude to a group of people who provided me with guidance, assistance, support, and encouragement. It is certain that without their help, I would not have been able to complete my Ph.D. studies.

First and foremost, I am deeply grateful to my advisors, Professor Nestor Evmorfopoulos and Professor Georgios Stamoulis, who not only gave me the opportunity to start this journey but also believed in my work and trusted me even during tough times. They have always been there to inspire me with new ideas and guide my research career. Being very different characters but at the same time outstanding personalities, they have managed to create a powerful team bringing extraordinary results. Their diligence, intelligence, and wisdom have had a great influence on my research development. I would also like to thank Professor Fotios Plessas, Professor Georgios Karakonstantis, and Professor Christos Sotiriou from the University of Thessaly, Professor Dimitrios Karampatzakis from the International Hellenic University, and Professor Labros Bisdounis from the University of Peloponnese, for providing insightful comments on my thesis.

My sincere appreciation to all my fellow labmates in the Electronics Lab of the University of Thessaly, for the fruitful discussions, for the sleepless nights we were working together before deadlines, and for all the fun we have had these years. Especially, I would like to thank Dr. Charalampos Antoniadis, Dr. George Floros, and Panagiotis Giannakou, with whom I have been collaborating since the beginning of my Ph.D. Moreover, I would like to extend my sincere thanks to Professor Georgios Karakonstantis and Dr. Ioannis Tsiokanos for our excellent collaboration and the great time we had during my stay at Queen's University Belfast. Immense thanks to Dr. Nikolaos Sketopoulos and (soon to be Dr.) Stavros Simoglou for contributing to quality publications. Also, I would like to wholeheartedly thank my closest friends, Achilleas, Christos, and George, for providing happy distractions to rest my mind outside of my research. Special gratitude is due to Faviola for her constant support and patience throughout my Ph.D. studies.

Last but not least, my deepest gratitude goes to my parents, Konstantinos and Styliani, for their unconditional support, love, and sacrifices for making this dissertation possible. Even if my research seems "Greek" to them, they were always there for me. The least I can do in recognition is to dedicate this dissertation to them.

This research was partially supported by the Center of Research, Innovation, and Excellence of the University of Thessaly, Greece and the European Union's Horizon 2020 Programme under grant agreement numbers 688540 (UniServer) and 687698 (HiPEAC).

# **Contents**

| De  | clarat     | tion of A                        | Authorship                                                      | iii              |

|-----|------------|----------------------------------|-----------------------------------------------------------------|------------------|

| Ab  | strac      | t                                |                                                                 | vii              |

| Πε  | ρίληψ      | η                                |                                                                 | ix               |

| Ac  | know       | ledgem                           | ents                                                            | xi               |

| Lis | st of F    | igures                           |                                                                 | xv               |

| Lis | st of T    | ables                            |                                                                 | xvii             |

| Lis | st of A    | lgorith                          | nms                                                             | xix              |

| Lis | st of A    | bbrevi                           | ations                                                          | xxi              |

| 1   | 1.1<br>1.2 | 1.1.1<br>1.1.2<br>1.1.3<br>1.1.4 | ntion                                                           | 1<br>2<br>2<br>2 |

| 2   |            | •                                | Estimation with Current Source Models & Effective Capacitance   | 5                |

|     | 2.1        |                                  | action                                                          |                  |

|     | 2.2        |                                  | d Work                                                          |                  |

|     | 2.3        | _                                | round                                                           |                  |

|     |            | 2.3.1                            | Gate modeling and library compatible CSMs                       |                  |

|     |            | 2.3.2                            | Modeling the $RC$ interconnect with a single $C_{eff}$          |                  |

|     | 2.4        | 2.3.3                            | Challenges in gate delay estimation using CSMs and $C_{eff}$    |                  |

|     | 2.4        |                                  | sed Approach                                                    |                  |

|     |            | 2.4.1<br>2.4.2                   | Computation of a single $C_{eff}$ considering the Miller effect |                  |

|     |            | 2.4.2                            | Computation of multiple $C_{eff}$                               | 14               |

|     |            | 2.4.3                            | and multiple $C_{eff}$                                          | 15               |

|     | 2.5        | Experi                           | mental Evaluation                                               |                  |

|     | 2.5        | 2.5.1                            | Accuracy results                                                |                  |

|     |            | 2.5.2                            | Runtime results                                                 |                  |

|     | 2.6        | Chapte                           | er Summary                                                      |                  |

| 3  | Inte  | rconnect Delay Estimation via Sparsity-Aware Model Order Reduction | 23 |

|----|-------|--------------------------------------------------------------------|----|

|    | 3.1   | Introduction                                                       | 23 |

|    | 3.2   | Background                                                         | 24 |

|    |       | 3.2.1 Electrical modeling of a VLSI interconnect                   | 24 |

|    |       | 3.2.2 Interconnect delay estimation methods                        | 24 |

|    |       | 3.2.3 Laplacian matrices                                           |    |

|    | 3.3   | Proposed Approach                                                  |    |

|    | 3.4   | Experimental Evaluation                                            |    |

|    | 3.5   | Chapter Summary                                                    |    |

| 4  | EVI   | G-based Worst-Case Delay Estimation Under Process Variation        | 31 |

|    | 4.1   | Introduction                                                       | 31 |

|    | 4.2   | Background on EVT                                                  |    |

|    |       | 4.2.1 Modeling extreme and rare events                             |    |

|    |       | 4.2.2 Limiting distributions                                       |    |

|    |       | 4.2.3 Estimation of a finite upper end point $\omega(F)$           |    |

|    | 4.3   | Background on Worst-Case Delay Analysis                            |    |

|    |       | 4.3.1 Impact of design parameter variations on maximum delay       |    |

|    | 4.4   | Proposed Approach                                                  |    |

|    |       | 4.4.1 Machine learning enhancements                                |    |

|    | 4.5   | Experimental Evaluation                                            |    |

|    | 4.6   | Chapter Summary                                                    |    |

|    | 7.0   | Chapter Summary                                                    | 72 |

| 5  | •     | amic Timing Analysis Using Event-Driven Simulation                 | 43 |

|    | 5.1   | Introduction                                                       |    |

|    | 5.2   | Background                                                         |    |

|    |       | 5.2.1 Static timing analysis                                       |    |

|    |       | 5.2.2 Dynamic timing analysis                                      |    |

|    | 5.3   | Proposed Approach                                                  |    |

|    |       | 5.3.1 Event-Driven DTA (ED-DTA)                                    | 47 |

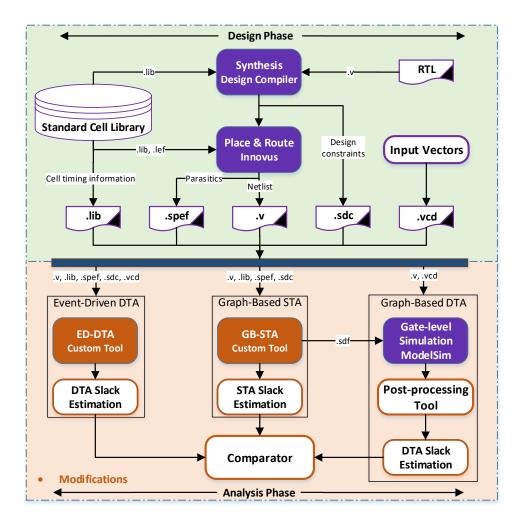

|    |       | 5.3.2 Realization of the proposed approach                         | 48 |

|    | 5.4   | Experimental Evaluation                                            |    |

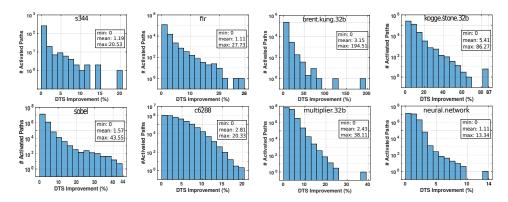

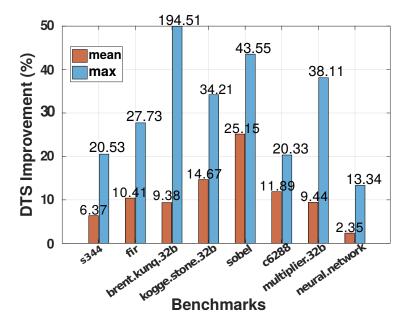

|    |       | 5.4.1 Evaluation of DTS                                            | 50 |

|    |       | 5.4.2 DTS & dynamically activated critical paths                   | 51 |

|    |       | 5.4.3 Dynamic frequency scaling & timing failures                  |    |

|    |       | 5.4.4 ED-DTA runtime                                               |    |

|    | 5.5   | Chapter Summary                                                    | 53 |

| Pu | blica | tions                                                              | 55 |

| Re | feren | nces                                                               | 63 |

# **List of Figures**

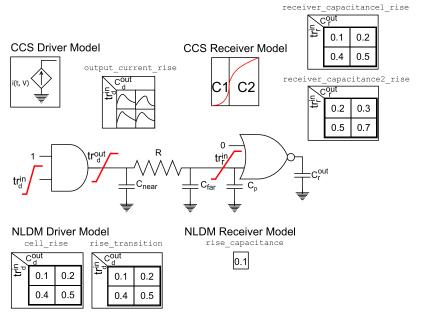

| 2.1 | NLDM vs CCS timing model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

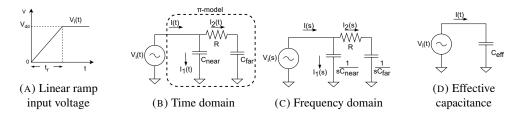

| 2.2 | Effective capacitance calculation for a $\pi$ -model with linear ramp input volt-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|     | age waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10 |

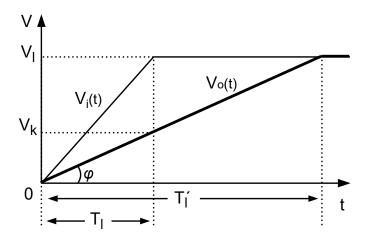

| 2.3 | Output voltage waveform and slew calculation for a $\pi$ -model with linear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|     | ramp input voltage waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12 |

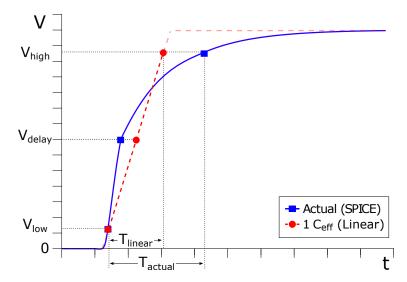

| 2.4 | Comparison between the linear ramp voltage waveform computed using a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|     | single $C_{eff}$ and the actual SPICE waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14 |

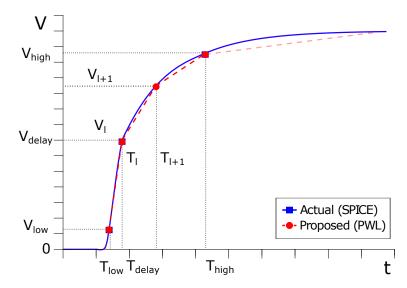

| 2.5 | Comparison between the PWL voltage waveform computed using multiple                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|     | $C_{eff}$ and the actual SPICE waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15 |

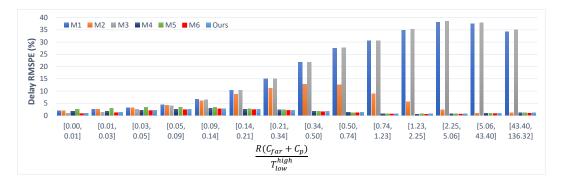

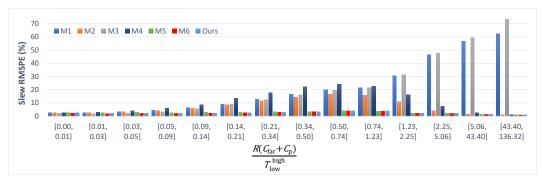

| 2.6 | Gate delay and output slew RMSPE against Synopsys HSPICE® on a testcase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|     | with 50k stages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20 |

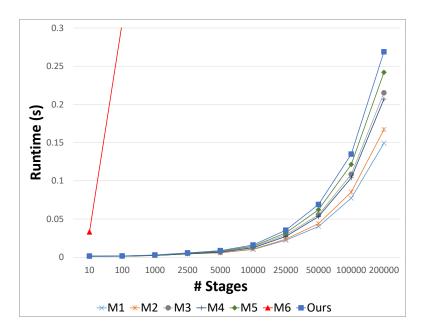

| 2.7 | Graphical comparison between the runtimes of the examined methods for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|     | testcases varying from 10 to 200k stages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22 |

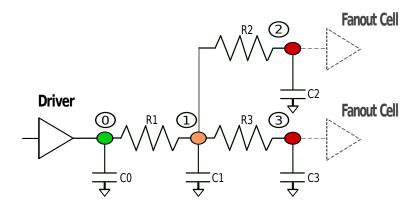

| 3.1 | Distributed <i>RC</i> interconnect of a gate driving two fanout cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25 |

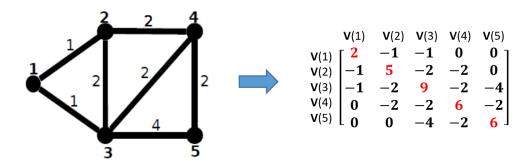

| 3.2 | A weighted graph and the corresponding Laplacian matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26 |

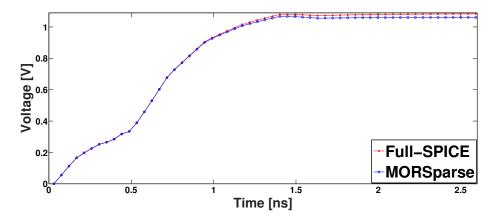

| 3.3 | Voltage response at port inst_41217:A1 of vga_lcd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30 |

| J.J | voltage response at port hist_11217.711 of vga_iea.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50 |

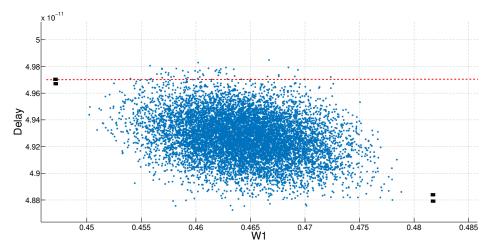

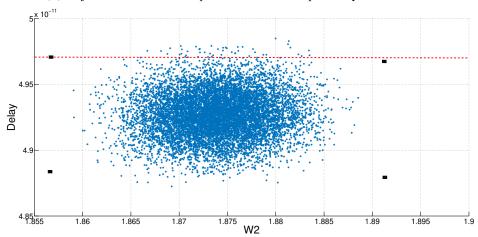

| 4.1 | Scatter plot of a two-inverters path delay derived from an MC simulator for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|     | 10,000 different (W1, W2) pairs. The delays at (W1, W2) corners are high-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|     | lighted with black squares. Notice that there are a lot of points over the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|     | red-dotted line that indicates the maximum delay from the set of delays corre-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|     | sponding to $(W1, W2)$ corners, namely $\{(W1_{min}, W2_{min}), (W1_{min}, W2_{max}), (W1_{min}, W2_{max}), (W1_{min}, W2_{max}), (W1_{min}, W2_{min}), (W1_{min}, W2_{max}), (W1_{min}, W2_{min}), (W1_{min}, W2_{max}), (W1_{min}, W2_{min}), (W$ |    |

|     | $(W1_{max}, W2_{min}), (W1_{max}, W2_{max})\}. \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37 |

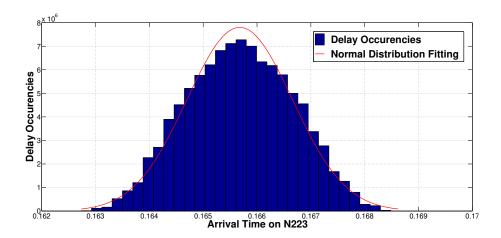

| 4.2 | Probability distribution of AT on N223 after an MC simulation of 10M trials.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 42 |

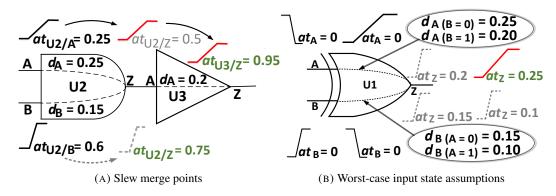

| 5.1 | Main sources of pessimism in graph-based analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45 |

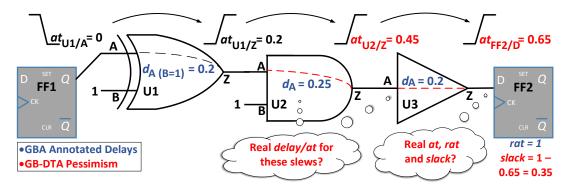

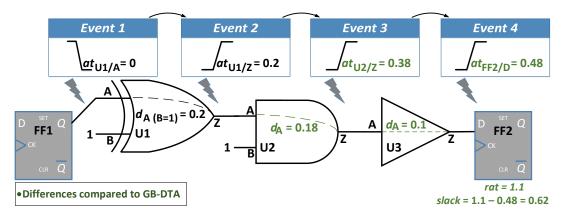

| 5.2 | Graph-based analysis pessimism in GB-DTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46 |

| 5.3 | Accurate DTA using event-driven simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 47 |