## University of Thessaly

#### **DOCTORAL THESIS**

# Models and Algorithms for Soft Error Rate Estimation in ICs

Author: Georgios-Ioannis Paliaroutis

Supervisor:

Pr. Nestor Evmorfopoulos

Pr. Georgios Stamoulis

Pr. Ioannis Moudanos

A thesis submitted in fulfillment of the requirements for the degree of Doctor of Philosophy

in the

Electronics Lab

Department of Electrical and Computer Engineering

March, 2021

## **Declaration of Authorship**

I, Georgios-Ioannis Paliaroutis, declare that this thesis titled, "Models and Algorithms for Soft Error Rate Estimation in ICs" and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

| Signed: |  |  |

|---------|--|--|

| Date:   |  |  |

"Life is like riding a bicycle. To keep your balance you must keep moving."

Albert Einstein

#### UNIVERSITY OF THESSALY

## **Abstract**

Department of Electrical and Computer Engineering

Doctor of Philosophy

#### Models and Algorithms for Soft Error Rate Estimation in ICs

by Georgios-Ioannis Paliaroutis

In state-of-the-art technologies utilized to design Integrated Circuits (ICs), failures, called Soft Errors caused by factors such as radiation or alpha particles, constitute a significant threat for circuit reliability. Many studies have focused on analyzing Soft Errors' effect on memory elements such as flip-flops, DRAMs and SRAMs. On the other hand, the protection of the ICs combinational part to external parameters has several shortcomings. For this reason, the evaluation of systems susceptibility to Soft Errors, regarding combinational logic as the primary part of the analysis, by an accurate and fast tool would be beneficial for the technology community.

The continuous downscaling of device feature size and the reduction in supply voltage in CMOS technology tend to worsen this severe problem. Many methodologies have tried to model and simulate transient glitches induced by particle strikes. However, some of them are not considered accurate since they analyze transient faults without taking into account all the appropriate parameters, and others are not fast enough. This PhD dissertation describes a fast simulator based on a methodology, which focuses on the modeling of glitches generation and their propagation at the circuit gate level. Therefore, ICs susceptibility to these effects is evaluated, calculating Soft Error Rate (SER). Furthermore, SER estimation of ICs, taking into consideration multiple transient faults, is a necessary process and is a fundamental aspect of the particular work.

A reliable tool was developed, basing on Monte-Carlo simulations, the modeling of masking mechanisms (Logical, Electrical, and Timing), and the consideration of placement information. ISCAS' 89 benchmarks were designed, utilizing two different technologies, and their SER is evaluated in FIT (failure in time), which is equivalent to the number of failures per one billion hours. Furthermore, SER is estimated, considering some significant factors such as sensitive regions, reconvergence pulses, the RC models, since they have a critical impact on the proposed analysis. The experiment results execution time for circuits is quite satisfactory, and the process is accelerated even more by implementing parallel programming. Finally, TCAD and SPICE simulations are employed to characterize transient faults and verify results obtained by the proposed tool.

#### ΠΑΝΕΠΙΣΤΗΜΙΟ ΘΕΣΣΑΛΙΑΣ

## Greek Abstract

Τμήμα Ηλεκτρολόγων Μηχανικών & Μηχανικών Υπολογιστών

Διδακτορική Διατριβή

Μοντέλα & Αλγόριθμοι για την Εκτίμηση της Συχνότητας Μεταβατικών Σφαλμάτων σε Ολοκληρωμένα Κυκλώματα

Γεώργιος - Ιωάννης Παλιαρούτης

Στις σύγχρονες τεχνολογίες που χρησιμοποιούνται για τον σχεδιασμό ολοκληρωμένων κυκλωμάτων, οι διαταραχές που χαρακτηρίζονται ως Soft Errors που προκαλούνται από εξωτερικούς παράγοντες, όπως η ακτινοβολία και τα σωματίδια α αποτελούν σημαντική απειλή για την αξιοπιστία των κυκλωμάτων. Μέχρι στιγμής, μια πληθώρα μελετών επικεντρώθηκε στην ανάλυση της επίδρασης των Soft Errors σε στοιχεία μνήμης όπως τα flipflops, τις DRAMs και τις SRAMs. Από την άλλη πλευρά, η προστασία του συνδυαστικού μέρους των ολοκληρωμένων κυκλωμάτων (λογικές πύλες) από τους εξωτερικούς παράγοντες έχει ακόμη αρκετά μειονεκτήματα. Για το λόγο αυτό, η αξιολόγηση της ευαισθησίας των συστημάτων στα Soft Errors από ένα αξιόπιστο και γρήγορο εργαλείο θα ωφελούσε σημαντικά την επιστημονική κοινότητα.

Η συνεχής μείωση του μεγέθους των τρανζίστορ όπως επίσης και η μείωση της τάσης τροφοδοσίας τείνουν να επιδεινώσουν το προαναφερθέν σοβαρό πρόβλημα που σχετίζεται με την ύπαρξη σφαλμάτων. Πολλές μεθοδολογίες έχουν προσπαθήσει να μοντελοποιήσουν και να προσομοιώσουν τις διαταραχές που προκαλούνται. Ωστόσο, ορισμένα από αυτά τα εργαλεία δεν είναι αρκετά ακριβή, καθώς προσομοιώνουν παροδικά τα σφάλματα χωρίς να λαμβάνουν υπόψη όλες τις κατάλληλες παραμέτρους ενώ επίσης άλλες μεθοδολογίες δεν είναι αρκετά γρήγορες. Συνεπώς, η συγκεκριμένη διατριβή περιγράφει έναν γρήγορο και αξιόπιστο προσομοιωτή βασισμένο σε μια μεθοδολογία που εστιάζει στην μοντελοποίηση της εμφάνισης και της διάδοσης των δυσλειτουργιών στο επίπεδο των λογικών πυλών κάθε κυκλώματος. Συνεπώς, η ανθεκτικότητα των ολοκληρωμένων κυκλωμάτων αξιολογείτε υπολογίζοντας το Soft Error Rate (SER). Επιπλέον, η πιθανότητα ύπαρξης πολλαπλών σφαλμάτων, είναι απαραίτητη και αποτελεί βασική πτυχή της συγκεκριμένης μεθοδολογίας.

Το συγκεκριμένο εργαλείο που παρουσιάζεται αναπτύχθηκε βασιζόμενο στην τεχνική των Monte-Carlo προσομοιώσεων, στην μοντελοποίηση των μηχανισμών που αποτρέπουν την διάδοση των σφαλμάτων (logical, electrical και timing masking) και την χρησιμοποίηση της χωρικής διάταξης των λογικών πυλών του κάθε κυκλώματος. Τα κυκλώματα στα οποία εφαρμόσαμε την προτεινόμενη μεθοδολογία είναι τα ISCAS '89 τα οποία σχεδιάστηκαν χρησιμοποιώντας δύο διαφορετικές τεχνολογίες. Επιπλέον, το SER υπολογίζεται λαμβάνοντας υπόψη ορισμένους σημαντικούς παράγοντες, όπως η εύρεση των ευαίσθητων περιοχών κάθε πύλης, η πιθανότητα οι παλμοί που σχετίζονται με το ίδιο σφάλμα να συγκλίνουν στην ίδια πύλη από διαφορετικά μονοπάτια παρόμοιες χρονικές στιγμές και τα μοντέλα RC, καθώς έχουν κρίσιμο αντίκτυπο στην προτεινόμενη ανάλυση. Ο συγκεκριμένος παράγοντας υπολογίζεται τόσο ως πιθανότητα αλλά και σε FIT (failure in time) που ισοδυναμεί με τον αριθμό των βλαβών που προκαλούνται ανά ένα δισεκατομμύριο ώρες.

Ο χρόνος εκτέλεσης των πειραμάτων για τα συγκεκριμένα κυκλώματα είναι αρκετά ικανοποιητικός κάτι το οποίο επιτεύχθηκε κάνοντας χρήση και ενσωματώνοντας την τεχνική

του παράλληλου προγραμματισμού στην συγκεκριμένη μεθοδολογία. Τέλος, τα εργαλεία Synopsys Sentaurus TCAD και Synopsys HSPICE χρησιμοποιούνται για τον χαρακτηρισμό των δυσλειτουργιών και την επαλήθευση των αποτελεσμάτων που λαμβάνονται από το προτεινόμενο εργαλείο.

## Acknowledgements

I would like to thank a couple of people, without whom I would not have been able to complete my dissertation. Their knowledge and plentiful experience have encouraged me in all the time of my academic research.

Firstly, I would like to express my thanks to my supervisor Professor Nestor Evmorfopoulos who has supported and advised me throughout my doctoral dissertation. I benefited a lot from his helpful comments and suggestions. Furthermore, I am notably grateful to Professor George Stamoulis and Professor Ioannis Moudanos for their generous support and guidance that inspired me all these years. Their ideas and comments significantly improved the quality of the particular thesis. I would also like to thank my thesis committee members, Professor Fotis Plessas, Professor Michael Dossis, Professor Antonis Dadaliaris, and Professor Dimitris Karampatzakis, for evaluating and accepting the particular dissertation.

From the bottom of my heart, I would like to thank my family for supporting me to complete my studies at the University of Thessaly. Their love, trust, endless patience, and encouragement helped me follow and fulfill my dreams in very intense academic years. Finally, I cannot forget to thank my co-authors and friends for all the unconditional support.

## **Contents**

| D  | eclara                                                      | ation of Authorship                                                                                                                                                                                                                                       | iii                                                            |

|----|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Al | bstrac                                                      | et ·                                                                                                                                                                                                                                                      | vii                                                            |

| G  | reek A                                                      | Abstract                                                                                                                                                                                                                                                  | ix                                                             |

| A  | cknov                                                       | vledgements                                                                                                                                                                                                                                               | xi                                                             |

| 1  | 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6                      | Introduction  Key Definitions  Digital - Sequential Circuits  Contribution  Objectives  Thesis Organization                                                                                                                                               | 1<br>1<br>2<br>2<br>3<br>5<br>5                                |

| 2  | Rela                                                        | ated works                                                                                                                                                                                                                                                | 7                                                              |

| 3  | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9 |                                                                                                                                                                                                                                                           | 11<br>11<br>12<br>13<br>14<br>14<br>15<br>15<br>16<br>17<br>17 |

| 4  | 4.1                                                         | Masking Effects 4.2.1 Logical masking 4.2.2 Electrical masking 4.2.3 First electrical masking modeling technique 4.2.4 Second electrical masking modeling technique 4.2.5 Timing masking Static Timing Analysis Implementation 4.3.1 Gates inertial delay | 19<br>19<br>19<br>20<br>21<br>21<br>24<br>25<br>26<br>28       |

|   | 4.4  | 4.3.4 Interconnection delay effect                               |    |

|---|------|------------------------------------------------------------------|----|

| 5 | SPIC | CE - TCAD Simulation                                             | 31 |

|   | 5.1  | SPICE Simulation                                                 |    |

|   | 0.1  | 5.1.1 Introduction                                               |    |

|   |      | 5.1.2 SPICE characterization                                     |    |

|   |      | 5.1.3 SET pulse characterization                                 |    |

|   | 5.2  | SPICE Verification                                               |    |

|   | 5.3  | TCAD Simulation                                                  |    |

|   | 0.0  | 5.3.1 Introduction                                               |    |

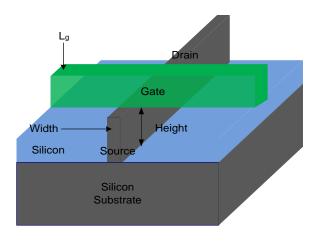

|   |      | 5.3.2 FinFET description                                         |    |

|   |      | 5.3.3 Sentaurus TCAD tool                                        |    |

|   | 5.4  | Modeling of TFs Impact                                           |    |

|   | 5.5  | Current Pulse Modeling                                           |    |

|   |      |                                                                  |    |

| 6 |      | Methodology                                                      | 41 |

|   | 6.1  | Introduction                                                     |    |

|   | 6.2  | Methodology for METs                                             |    |

|   |      | 6.2.1 Sensitive zones                                            |    |

|   |      | 6.2.2 SEMTs ananlysis                                            |    |

|   | 6.3  | Transient Faults Simulation                                      |    |

|   | 6.4  | Proposed Algorithm Description                                   |    |

|   |      | 6.4.1 Masking mechanisms                                         |    |

|   |      | 6.4.2 Algorithm for SER evaluation                               |    |

|   |      | 6.4.3 Function of errors generation                              |    |

|   |      | 6.4.4 Latching probability function                              |    |

|   | 6.5  | Optimization Issues                                              |    |

|   |      | 6.5.1 Speed-up SER process                                       |    |

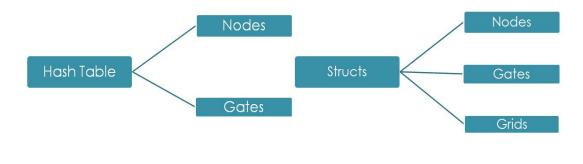

|   |      | 6.5.2 Data structures                                            |    |

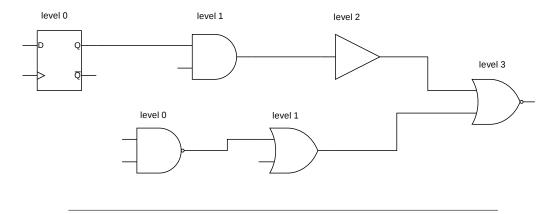

|   |      | 6.5.3 ICs levelization                                           |    |

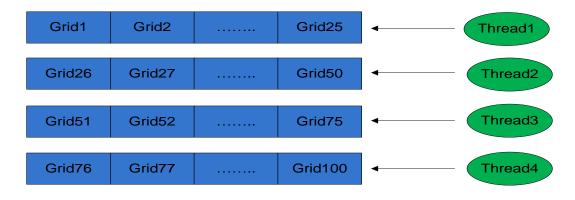

|   |      | 6.5.4 Parallel programming                                       |    |

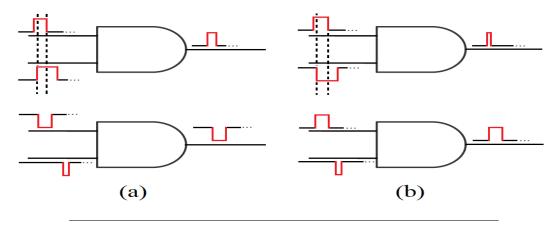

|   | 6.6  | Reconvergent Faults                                              |    |

|   | 6.7  | Gate Sensitivity                                                 | 53 |

| 7 | Expe | erimental Results                                                | 55 |

|   | 7.1  | Introduction                                                     |    |

|   | 7.2  | Planar and FinFET Transistors                                    |    |

|   | 7.3  | Grids Analysis                                                   |    |

|   | 7.4  | Masking Mechanisms - Temperature Impact on SER                   |    |

|   | 7.5  | SER Estimation Results                                           |    |

|   |      | 7.5.1 ISCAS '89 benchmark circuits                               |    |

|   |      | 7.5.2 Electrical and timing verification using SPICE             |    |

|   |      | 7.5.3 SER estimation for different timing cases                  |    |

|   |      | 7.5.4 Electrical masking impact on SER                           |    |

|   |      | 7.5.5 Consideration of SEMTs and SET                             |    |

|   |      | 7.5.6 Comparison of the unified and individual evaluation of SER |    |

|   | 7.6  | Verification of the STA and Gates Sensitivity                    |    |

|   |      | 7.6.1 Accuracy of the implemented static timing analysis         |    |

|   |      | 7.6.2 Gates sensitivity process reliability                      |    |

|   | 7.7  | Overall SER                                                      | 68 |

|    |             | Effect of MTFs and operational frequency on SER estimation Speed-up SER evaluation |    |

|----|-------------|------------------------------------------------------------------------------------|----|

| 8  | Conclusion  | as And Further Research                                                            | 73 |

| 9  | Publication | ıs                                                                                 | 77 |

| A  | HSPICE Co   | ode                                                                                | 79 |

| Bi | bliography  |                                                                                    | 80 |

## **List of Figures**

| 1.1<br>1.2 | Description of sequential circuit                                                        |    |

|------------|------------------------------------------------------------------------------------------|----|

| 3.1<br>3.2 | D Flip-Flop description                                                                  |    |

| 3.3        | A simple presentation of a particle hit                                                  | 13 |

| 3.4        | Alpha particles component                                                                |    |

| 3.5        | Alpha particle effect on active and in-active transistors                                | 16 |

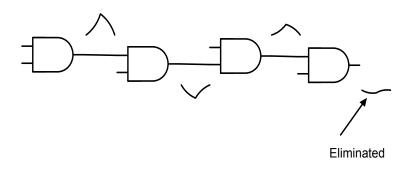

| 4.1        | Logical masking description.                                                             |    |

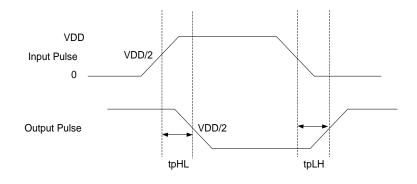

| 4.2        | Electrical masking modeling.                                                             |    |

| 4.3        | Propagation delay of a gate                                                              |    |

| 4.4        | Timing masking description                                                               |    |

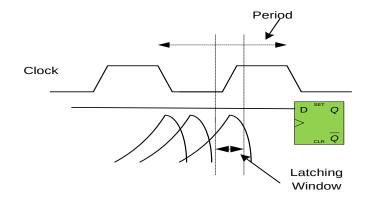

| 4.5        | The impact of latching window on the masking of SETs                                     | 24 |

| 5.1        | Transistor Pulse Injection                                                               | 31 |

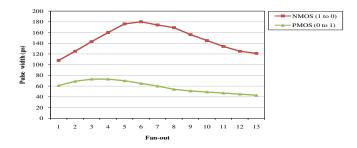

| 5.2        | Pulse widths for various fan-out when NMOS and PMOS is affected                          | 32 |

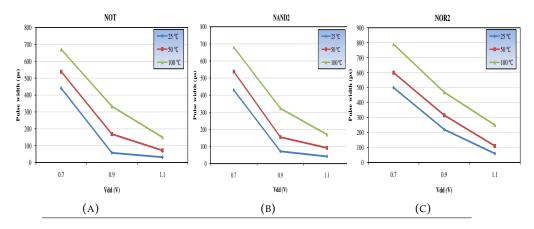

| 5.3        | Pulse widths for different supply voltages and temperatures of NOT, NAND2 and NOR2 gates | 33 |

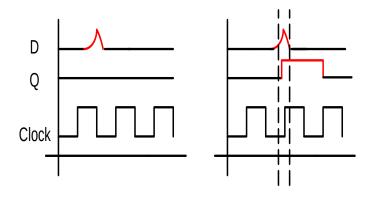

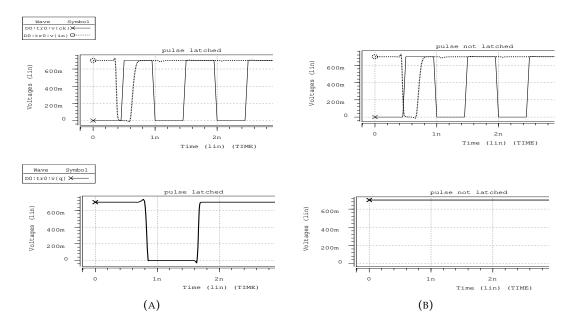

| 5.4        | Transient pulse when it is latched and it is not latched                                 |    |

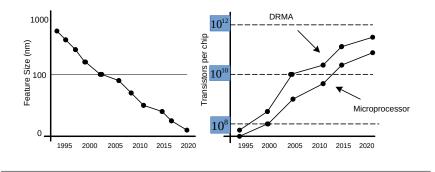

| 5.5        | Transistors size and number per chip according to Moore's Law                            |    |

| 5.6        | Structure of FinFET transistor                                                           |    |

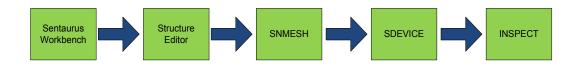

| 5.7        | Sentaurus simulation process                                                             |    |

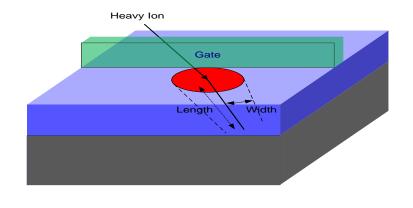

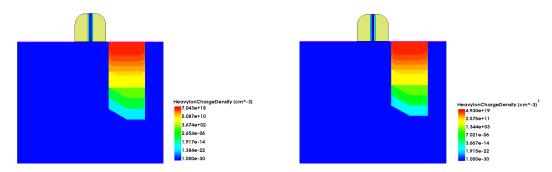

| 5.8        | Heavy-ion simulation                                                                     |    |

| 5.9        | Charge generation caused by a heavy ion for different LETs                               |    |

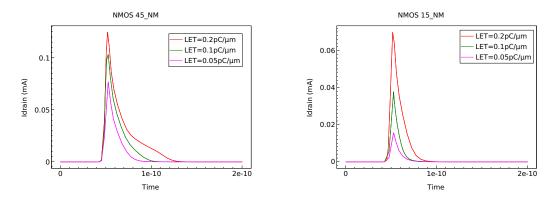

| 5.10       | The drain current for different LETs for both technologies                               |    |

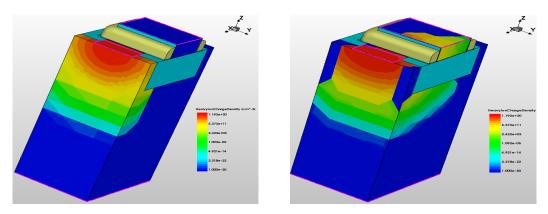

| 5.11       | The impact of particle hits angle on charge density                                      |    |

| 5.12       | J                                                                                        | 20 |

| E 12       | command file.                                                                            |    |

|            | Heavy-ion modeling and generation                                                        |    |

| 6.1        | DEF files information                                                                    |    |

| 6.2        | Sensitive zones determination                                                            |    |

| 6.3        | Particle strikes of different energy.                                                    | 43 |

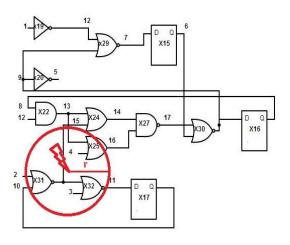

| 6.4        | s27 affected by a particle hit                                                           |    |

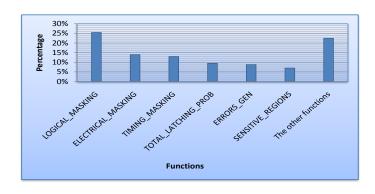

| 6.5        | CPU utilization of the proposed tool's functions                                         |    |

| 6.6        | Using unsigned integers in simulation process                                            | 50 |

| 6.7        | Data structures utilized                                                                 |    |

| 6.8        | Gates level evaluation.                                                                  |    |

| 6.9        | Parallel programming implementation.                                                     |    |

|            | Reconvergent pulses for AND gate                                                         | 53 |

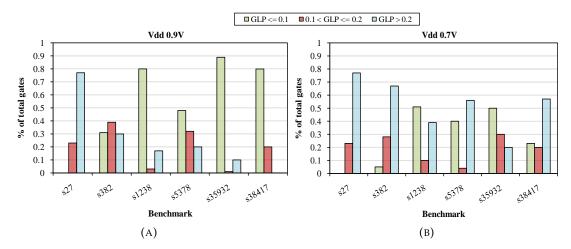

| 6.11       | Distribution of gate sensitivity for 6 benchmarks with supply voltage                    |    |

|            | (a) 0.9V and (b) 0.7V                                                                    | 54 |

#### xviii

| erall SER evaluation process                                         | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

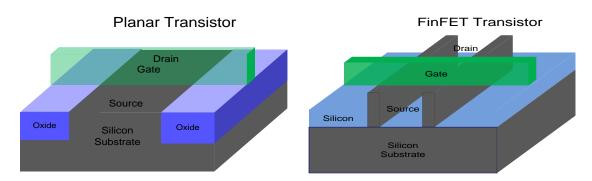

| mparison of planar and FinFET transistors.                           | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

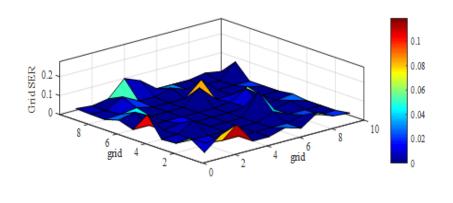

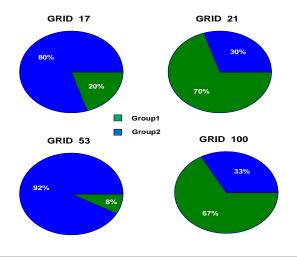

| ds SER and distribution of components for S35932 benchmark           | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ds SER for s35932 benchmark                                          | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| tes connectivity with FFs of S35932                                  | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

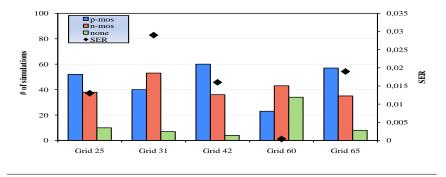

| mber of affected transistors for 100 simulations for some grids of   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 850 with the corresponding SER values                                | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

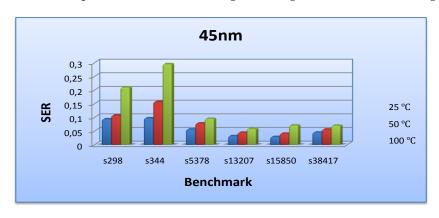

| R of a set of benchmarks for three different temperatures - 45nm     | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

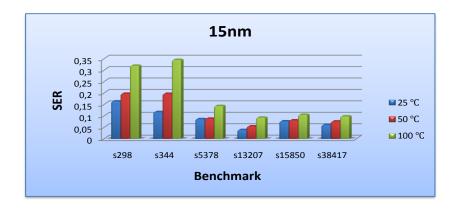

| R of a set of benchmarks for three different temperatures - 15nm     | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

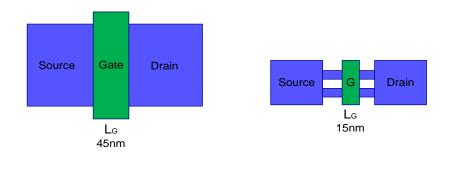

| imple description of planar MOSFET and FinFET transistors            | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

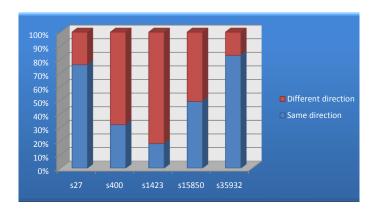

| e percentage of reconvergent pulses with different and same direc-   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>1</b>                                                             | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

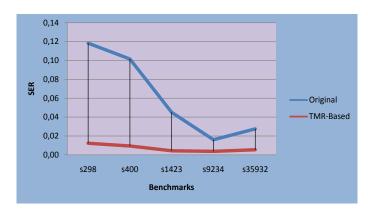

| e effect of TMR mitigation technique, based on gate sensitivity pro- |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| s, on SER evaluation.                                                | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

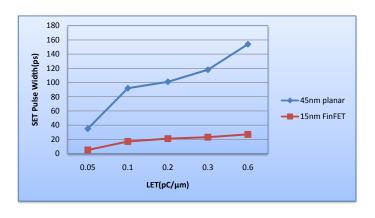

| Γ pulse width of Inverter for different values of the parameter LET. | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| R evaluation using HSPICE                                            | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| in Contract Residence Services                                       | mparison of planar and FinFET transistors.  ds SER and distribution of components for S35932 benchmark.  ds SER for s35932 benchmark.  es connectivity with FFs of S35932  mber of affected transistors for 100 simulations for some grids of 850 with the corresponding SER values.  d of a set of benchmarks for three different temperatures - 45nm.  d of a set of benchmarks for three different temperatures - 15nm.  imple description of planar MOSFET and FinFET transistors.  percentage of reconvergent pulses with different and same direction.  effect of TMR mitigation technique, based on gate sensitivity prosponses, on SER evaluation. |

## **List of Tables**

| 4.1<br>4.2 | Propagation delays and output pulse widths for the transition 0->1->0. Propagation delays and output pulse widths for the transition 1->0->1. | <ul><li>22</li><li>23</li></ul> |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 5.1        | SER verification comparing the proposed tool with Hspice                                                                                      | 34                              |

| 6.1        | Average affected area                                                                                                                         | 43                              |

| 6.2        | Coordinates, radius of particle hits and the number of affected gates                                                                         | 43                              |

| 6.3        | Name and type of affected gates of each particle hit                                                                                          | 44                              |

| 7.1        | The percentage of the injected TFs that become logically, electrically and timingly masked for some grids of s15850                           | 59                              |

| 7.2        | The percentage of the injected TFs that become logically, electrically and timingly masked utilizing the second technique for the modeling    |                                 |

| 7.3        | of the electrical masking                                                                                                                     | 60                              |

|            | ferent technologies                                                                                                                           | 62                              |

| 7.4        | Comparison of the proposed electrical and timing masking models                                                                               |                                 |

|            | with Spice on SET pulse propagation paths                                                                                                     | 63                              |

| 7.5        | SER estimation considering LE, NLDM and RC interconnection ap-                                                                                |                                 |

|            | proaches for 45nm and 15nm                                                                                                                    | 63                              |

| 7.6        | Clock period that is obtained, implementing LE method and STA anal-                                                                           |                                 |

|            | ysis for both technologies                                                                                                                    | 64                              |

| 7.7        | SER considering an approximate pulse propagation function and SPICE-                                                                          |                                 |

|            | orientated technique for 45nm and 15nm                                                                                                        | 64                              |

| 7.8        | SER evaluation considering SETs and SEMTs for 45nm and 15nm                                                                                   | 65                              |

| 7.9        | SER evaluation and comparison of Individual and Unified approach                                                                              |                                 |

|            | on circuits designed with FinFET technology at 15nm                                                                                           | 66                              |

| 7.10       | The comparison of the critical path, obtained from the proposed anal-                                                                         |                                 |

|            | ysis with the corresponding of the Innovus EDA tool                                                                                           | 67                              |

| 7.11       | Propagation delays of each gate                                                                                                               | 67                              |

| 7.12       | Circuits failure probability - 45nm and 15nm Nangate technologies                                                                             | 69                              |

| 7.13       | SER evaluation in terms of FIT.                                                                                                               | 69                              |

| 7.14       | Clock period of some circuits for both technologies                                                                                           | 70                              |

| 7.15       | The overall number of multiple affected gates, the number of hits im-                                                                         |                                 |

|            | plemented and the percentage of particles, which provoke MTFs.                                                                                | 71                              |

| 7.16       | The Distribution of SETs, SEMTs and unaffected gates by particle strikes.                                                                     | 71                              |

|            | Comparison the execution time of old and optimized approach of the                                                                            |                                 |

|            | proposed tool                                                                                                                                 | 72                              |

## List of Abbreviations

CMOS Complementary Metal-Oxide-Semiconductor

**DEF** Design Exchange Format

**DRAM** Dynamic Random Access Memories

DTA Dynamic Timing AnalysisEDA Electronic Design Automation

FFs Flip Flops

FinFET Fin-Shaped Field Effect Transistor

FIT Failure In Time

FPGA Field Programmable Gate Array

GDSII Graphic Data System

LE Logical Effort

LET Linear Energy Transfer

LUTs Look Up TablesMBUs Multiple Bit Upsets

METs Multiple Events Transients

NLDM Non Linear Delay Model

PDF Probability Density Function

P&R Placement and Route

**SEMTs** Single Event Multiple Transients

**SER** Soft Error Rate

SET Single Event TransientSEU Single Event UpsetSOI Silicon On Insulator

**SPEF** Standard Parasitic Extraction Format

SPICE Simulation Program with Integrated Circuit Emphasis

**SRAM** Static Random Access Memories

STA Static Timing Analysis

TCAD Technology Computer-Aided Design

TF Transinet Fault

TMR Triple Module RedundancyVLSI Very Large-Scale Integration

xxiii

Dedicated to my family ...

## Chapter 1

## Introduction

#### 1.1 Introduction

VLSI Integrated Circuits (ICs) constitute integral parts of modern systems. For this reason, their reliability and performance have always been a matter of great concern and a challenge for designers, let alone in recent years, since chips are more vulnerable to radiation-induced hazards due to the continuous shrinking of the CMOS technology. Many malfunctions to critical devices can be created by failures induced by external parameters. In other words, the aspect that only space systems can be affected by cosmic radiation has been refuted since it is well known now that terrestrial applications are sensitive to ionizing particles and necessitate higher reliability levels [1]. Alpha particles emitted from radioactive impurities in package material and high-energy particles from cosmic radiation may strike the silicon of an IC, resulting in unexpected behavior for systems. In particular, when such an incident occurs on a transistor, several electron-hole pairs are created, which, in turn, may be collected by the depletion region. This disturbance may momentarily cause a change at a gate's output logic state, which is well-known as a Single Event Transient (SET). Therefore, the evaluation of SETs behavior is an essential process and can increase systems efficiency. The particular procedure should be implemented in many circuits taking into account the ICs timing and placement information to ensure that chips functionality can be correct even in the presence of malfunctions. Hence, conclusions about ICs reliability requirements can be obtained, which can be exploited by VLSI designers to create more reliable chips.

Permanent and transient faults are the types of disturbances, which may have an impact on circuit performance. The former are caused during the ICs fabrication and testing phase, while the latter occur during application operation. The proposed methodology focuses on the Transient Faults (TFs) analysis provoked mainly by alpha particles emitted from radioactive impurities in the packaging material of the ICs, and high-energy particles, mostly neutrons, from terrestrial cosmic rays. Due to transient glitches, the IC functionality is momentarily affected without causing permanent damage to devices. However, according to many studies, this type of fault is considered a significant problem since many failures are transient. Therefore, TFs influence analysis on circuits combinational part is crucial, especially for critical systems that should function properly. Their simulation is considered a complicated process, comparing with the modeling of the permanent failures. In other words, the time at which a particle hits a circuit should be taken into account as well as the ICs' electrical properties should be analyzed. Therefore, an electrical level simulator such as SPICE would be very beneficial. SPICE simulations provide accurate results, even though transient faults simulation, especially for large-scale circuits, is a time-consuming process since, at any time, any cell can be affected by a particle hit.

### 1.2 Key Definitions

**Soft Error Rate (SER)** is defined as the rate or probability of soft errors, which occur in a device or an application. A **Soft Error** at circuit level is an error that may result in a change of a Flip-Flop (FF) state. It is called "soft" since it does not cause permanent damage to ICs, but circuits proper operation may be affected temporarily, leading to unpredictable results. The reliability of modern systems depends on **soft errors** that can be caused by radiation-induced faults. The principal sources are high-neutrons, which derive from the atmosphere and the alpha particles in chip packaging. Therefore, their characterization, taking into account some critical parameters, i.e., different values for the temperature and supply voltage, is a significant process of the particular methodology.

**Particle hits** are induced by the impact of **alpha particles** or **radiation-induced particles** on circuits. **Alpha particles** usually are generated by material package impurities, while **high energy particles** are caused by cosmic radiation.

A **SET** in the combinational part of an IC is a transient disturbance caused on a gate's output voltage pulse due to a **particle hit**. The logic state of the affected gate may be changed if the particle's energy is sufficient to affect its behavior. Transient disturbances propagate through a circuit and may approach memory elements.

The **Monte-Carlo** method belongs to the category of algorithms based on repeated random experiments to extract numerical results. In the particular methodology, a sufficient number of **Monte-Carlo** simulations with random input parameters are conducted to have an accurate SER estimation.

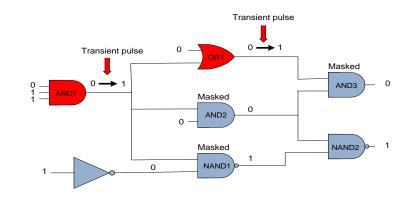

**Masking Effects** are the three mechanisms (logical, electrical, timing) that prevent transient faults from propagating through ICs and causing soft errors.

Due to Multiple Events Multiple Transients - Single Event Multiple Transients (MEMTs-SEMTs), multiple transient faults are induced in circuits. The former case means that multiple particle hits can affect ICs, while in the latter situation, multiple disturbances can be provoked by a single particle hit.

## 1.3 Digital - Sequential Circuits

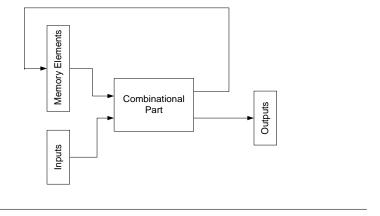

FIGURE 1.1: Description of sequential circuit.

Digital circuits are electronic devices, which process information using digital signals. In other words, values 0 and 1, i.e., the low and high voltages, constitute the discretization of the analog signals. The operation of the digital circuits is more simplistic in comparison with the analog systems functionality. In other words, it

1.4. Contribution 3

is easier the simulation of an electronic device, which switches into several known states, than to a continuous range of values. Therefore, the former can be more easily programmed and analyzed in comparison with the latter. Digital circuits comprise logic gates and memory elements, and more complex systems can be manufactured, combining these components. For this reason, sequential circuits (Figure 1.1) were used to analyze the proposed SER methodology. Binary information can be stored by FFs, as systems output depends on the logic value of inputs for many clock cycles.

The nature of TFs, as mentioned before, is non-destructive, but it may affect the proper digital ICs operation leading to malfunctions. A drawback associated with the downscaling of the ICs device feature size is that it renders them more vulnerable to radiation threats [2]. The analysis of the radiation-induced hazards, commonly called soft errors, is a significant aspect since their impact on circuit functionality is vital. Therefore, the necessity of identifying the impact of such errors on the ICs function has become imperative, and the contribution of fault simulators to the development of error-resistance chips tends to be critical. For this reason, the SER evaluation, which is the metric that indicates the grade of a sequential circuit susceptibility to radiation-induced faults, is a considerable and necessary process.

#### 1.4 Contribution

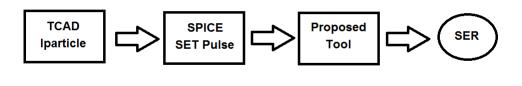

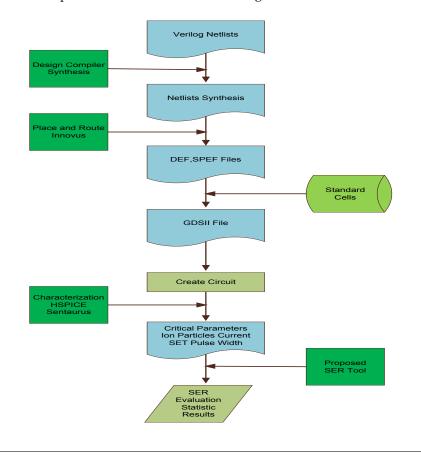

FIGURE 1.2: Methodology basic steps.

Memory elements (DRAM, SRAM) cover a considerable part of systems and, the effect of the soft errors on them is analyzed extensively until now. In other words, the probability of Single Event Upsets (SEUs) occurrence has decreased because many techniques have been designed to harden memory elements against the disturbances [3, 4, 5, 6, 7, 8]. On the other hand, recent studies show that the SER of logic circuits has risen considerably due to mainly critical charge ( $Q_{crit}$ ) reduction [9]. Furthermore, ICs susceptibility has increased due to the continuous evolution of the VLSI technology, hence SER evaluation constitutes a significant challenge. However, ICs' power, performance, and area are worsened, implementing SER mitigation techniques in the combinational part [10]. Therefore, it is necessary to develop a methodology to provide sufficient data about ICs vulnerability concerning the transient faults to harden and protect ICs with the minimum cost [11].

SER estimation of ICs is a demanding process, which requires a comprehensive model and can be affected by many parameters. The particular thesis describes the evaluation of soft error effects in the VLSI circuits combinational parts. In Figure 1.2 a synoptic overview of the proposed methodology is presented. The analysis of IC susceptibility and reliability utilizing EDA tools is an imperative procedure. For this reason, initially, TCAD simulations are implemented to extract currents, which correspond to different high-energy particles. Then, the pulses of the TFs that have been resulted from SPICE simulations through gates characterization, and the

data obtained by the previous steps, are used by the proposed tool to evaluate ICs SER. As mentioned before, SER in combinational logic has increased, and thus, the modeling of soft errors impact constitutes a considerable motivation of the particular dissertation.

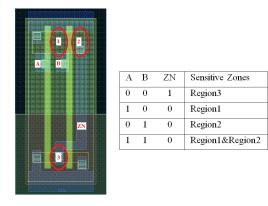

The neutron flux has been studied extensively in recent years [12] and is a factor, which poses difficulties to accurate SER evaluation since it varies based on location. Furthermore, the Linear Energy Transfer (LET) is another significant parameter, which describes the amount of energy transferred by the heavy-ion particle to semiconductor material and depends on ICs technology. Therefore, for the proposed methodology, approximate values are considered for the abovementioned parameters. Furthermore, the probability that a high-energy particle will affect a set of gates should be taken into account since distances among cells have decreased due to the down-scaling of technology. Analysis of chip susceptibility to radiation-induced TFs constitutes a crucial part of a reliable chip design process. Therefore, in the particular thesis, the proposed tool bases on an algorithm designed to model multiple glitches. SEMTs are quite possible to be generated by a single particle hit and to propagate through a circuit. Thus, Design Exchange Format (DEF) and Graphic Design System II (GDSII) files, for the corresponding ISCAS '89, are utilized to identify sensitive zones considering circuit placement information.

TFs are modeled considering their generation and propagation in circuits. They can be caused by a high-energy particle strike on a transistor's depletion region (an off transistor of a gate). Fortunately, the generated glitches do not damage the transistor, though they may momentarily flip the state of the gates output node, and their intensity is characterized through simulations. Furthermore, the most considerable difference between the SER evaluation of combinational logic and memory structure modeling is that masking effects are taken into account by the former analysis [13]. For this reason, for an accurate SER estimation of digital ICs, masking effects are modeled and incorporated into the proposed methodology. In other words, SETs that may occur on any gate may propagate through the subsequent cells and lead to soft errors if some of them are latched by memory elements. However, this fact can be prevented by masking phenomena, which are logical, electrical, and timing masking [14].

A key element in the modeling of both electrical effect and timing masking is the timing analysis that is implemented by the proposed methodology. Based on the results of the Static Timing Analysis (STA) analysis taking into consideration the fall, rise delays, and the SPICE simulations, we can determine the SET pulse width as it propagates through the logic gates. The modeling of electrical masking becomes dynamic since the output pulse width depends on the input that the SET emerges, which implies different fall and rise delays. Furthermore, various timing-aware aspects that may affect the timing masking are taken into account. In particular, the impact of the STA methodology - incorporated into the baseline tool for the logic gate delay estimation - on SER estimation is compared with the straightforward, but less accurate, Logical Effort (LE) method. The contribution of the actual interconnect delay of the design to SER is considered, unlike previous approaches that neglect it. Finally, the experimental results show that the utilization of a realistic timing mechanism analysis leads to a more accurate SER estimation.

1.5. Objectives 5

### 1.5 Objectives

The particular thesis focuses on the design of a software tool to evaluate the vulnerability of the ICs to external parameters such as cosmic radiation, basing on the selection of the appropriate analysis. Furthermore, the impact of ICs physical design (layout) on SER evaluation is examined, identifying the affected area of particle hits. This factor is quite crucial and can be exploited by the industry to design more reliable circuits. Another significant issue is the implementation and combination of the masking mechanisms in the best possible way. These effects constitute crucial factors for our analysis since they prevent malfunctions from propagating through circuits and leading to soft errors. Therefore, their modeling and incorporation into the proposed tool is a very crucial process.

The main objectives are to:

- Design a tool to estimate ICs SER for different technologies.

- Synthesize ISCAS '89 benchmarks, using 45nm and 15nm Nangate Open Cell libraries [15].

- Utilize ICs placement information (parse DEF, GDSII files) in order to model Multiple Transient Faults (MTFs).

- Analyze gate sensitivity and reconvergent pulses since SER evaluation is influenced by the particular factors.

- Model masking mechanisms (Logical, Electrical, Timing).

- Incorporate a timing simulator and RC model into the proposed tool since the timing and electrical masking analysis is based on ICs timing information.

- Characterize TFs through TCAD and SPICE simulations.

- Design SPICE circuits to verify the proposed methodology.

## 1.6 Thesis Organization

The basic Chapters of the particular PhD thesis are the following. Chapter 2 summarizes the related work on SER analysis; Chapter 3 introduces the basics of the SETs as well as the characterization of their pulse width; Chapter 4 describes the masking effects and gate delay calculation using STA methodology; Chapter 5 underlines the usefulness of SPICE and TCAD simulations; The modeling of SEMTs and the proposed methodology for SER estimation are described in Chapter 6; Chapter 7 presents the experimental results on the used benchmarks, whereas Chapter 8 concludes this PhD dissertation.

## Chapter 2

## Related works

In this section, we present a variety of works related to the field of radiation-induced soft errors. As technology shrinks, the ICs complexity and low supply voltages have an impact on integrated circuits reliability and can lead to an increased number of failures [16]. Some of these circuits are parts of medical, military, or space applications utilized for significant purposes. Therefore, soft errors evaluation and mitigation can be characterized as mandatory [17]. The [18] was one of the first works, which studied the soft errors and their effect on space applications. The most prevalent causes of such hazards are the alpha particles emitted from radioactive impurities in the ICs package material, and heavy ions from terrestrial cosmic rays that may strike the silicon material of the chips [19, 20, 21]. In recent years, many tools are designed based on the methodologies developed in the past years to deal with these dangerous threats of the VLSI field. Therefore, there are many approaches, which characterize failures caused in terrestrial circuits and measure SER cell libraries in terms of FIT [22]. Furthermore, an accurate SER estimation is obtained basing on Monte-Carlo simulations and considering ICs layout information [23]. For the modeling of the ICs reliability, Monte-Carlo is a widely-used method utilized to characterize circuit behavior [24, 25]. In [26] semiconductor devices SER is calculated, implementing the aforementioned technique and taking into account alpha particles emission, circuits placement information, and critical charge at sensitive zones. However, the whole process is quite time-consuming, even though it provides accurate analysis.

Over recent decades, extensive research was done on SER analysis and mitigation of the ICs. These studies deal with the challenges of the technology node downscaling. A significant part of the scientific researches involves SET pulse measurements through neutron beam testing setups that generate particles from a wide energy spectrum. The actual measurements in [27, 28, 29, 30] provide useful results regarding the direct impact of radiation on ICs of various technology nodes and under different conditions. Although the real-time experiments comprise a vital step to comprehend the behavior of modern chips in an environment of radiation fluxes, simulations are necessary to succeed scalability and obtain accurate results in a reasonable time. Furthermore, many methodologies implement the three natural masking mechanisms that mitigate SER, i.e., logical, electrical, and timing masking [22, 31, 32, 33, 34, 35]. There are works, which provide an accurate and fast evaluation of circuits timing information contributing to the modeling of the above parameters [36, 37]. Statistical static timing analysis is employed to characterize transient faults propagation based on rising and falling transitions times [38]. Furthermore, the possible situation of reconvergent pulses is modeled and is incorporated into the particular methodology. An analytical model is employed in [39] to characterize electrical masking. In particular, lookup tables per gate for drain current and capacitance model are utilized. The works in [14, 33, 40] are based on probabilistic

models and statistical methods for SER estimation. In [33] a fault simulation is provided, using a probabilistic theory and the masking effects modeling. It succeeds in a speedup process over Monte Carlo simulation, but the primary shortcoming of the particular methodology is that it is implemented mainly on small circuits.

Transient faults injection has been the basic idea for a considerable amount of studies. SEUs occur on SRAM, DRAM and FPGAs due to alpha particles something reported in [41, 42, 43]. SRAM susceptibility on SEUs is analyzed through 3D device simulations in [44]. Furthermore, FinFET and SOI technologies are utilized to design SRAMs and to characterize their vulnerability [45, 46]. The ICs effectiveness under external parameters such as heavy-ions is described in [47, 48]. On the other hand, there are researches, which study transient faults impact on combinational parts of ICs to analyze gates effectiveness and their resistance to particle hits [25, 49, 50, 51, 52]. This process is quite beneficial to investigate circuits behavior and how they can deal with transient faults. However, modern chips tend to be more vulnerable to high-energy particle strikes due to the technology downscaling, which means that the reduction in the distance among the cells has increased the occurrence of MTFs caused by a single particle strike [53, 54, 55, 56, 57]. Therefore, the SER evaluation in the presence of SEMTs is a necessary process, and for this reason, heavy-ion experiments are conducted to characterize them [54]. In [57, 58], the authors introduce the identification of the gates sensitive regions for SER estimation. METs generation, propagation, and their impact on ICs combinational logic are analyzed, taking into consideration currents injection process and the identification of sensitive zones [50, 59]. Some approaches consider that SEMTs occur at the output of physically adjacent gates [60, 61]. Nevertheless, if only logic-level netlists are used for the determination of the ICs error sites, neglecting the layout-level adjacency of the cells may result in inaccurate estimation. Therefore, other approaches provide a more realistic and reliable SER estimation analysis by taking into consideration circuit layout [50, 57, 58, 62, 63, 64]. Furthermore, it is possible MBUs to be caused by a particle hit on SRAMs, something modeled in [65].

In [66, 67, 68], the authors characterize the SET pulse generation and propagation under different design parameters through SPICE and TCAD simulations. In particular, in order to characterize transient pulses TCAD tools are utilized by many works [69, 70, 71]. In SPICE-level simulations, SER is calculated taking into consideration TFs generation and propagation, offering a comprehensive evaluation, for this reason, the particular process is utilized by many works to verify their extracted results. [9, 50, 49, 72, 73, 74, 75, 76]. Synopsys®HSPICE<sup>TM</sup>is a device-level tool and is used to characterize gate sensitivity to particle strikes and to estimate circuits SER [77]. Critical charge ( $Q_{crit}$ ) is the minimum charge required for a particle hit to provoke a TF, is a fundamental parameter utilized in SER evaluation, and is obtained through HSPICE simulations [78]. Transient fault impact on memory elements and logic gates is evaluated by the particular simulator. The proposed methodology in [75] uses binary decision diagrams (BDD) for the propagation of the transient glitches and SPICE simulations to characterize the pulse generation. A logic cell and flip-flop characterization are performed, obtaining the parameters used in the calculation of SER in [76]. Furthermore, another critical parameter, which influences SETs propagation and generation is temperature. Therefore, the modeling of SET pulse width should be conducted, taking into consideration this key factor, as it is a function of operating temperature [79]. Increasing the temperature pulse widths become more intense, leading to a more elevated SER [25, 80].

Many of the aforementioned works follow a similar process with the methodology described in the particular PhD thesis having, albeit some severe shortcomings.

MTFs generation and propagation through ICs are modeled, utilizing probability methods by some of them. However, this process does not provide accurate results and can be described as deficient since it does not focus on ICs design and operation. Furthermore, other approaches provide only gates characterization using the current pulses of high-energy particles and capacitance values of input and output nodes of each gate. Nevertheless, this procedure is not complete since MTFs-SEMTs influence is not analyzed. In the particular dissertation Monte-Carlo-based approach for an accurate estimation of the vulnerability of ICs to radiation-induced faults is proposed, taking into consideration MTFs and SEMTs. In this direction, the placement details of each circuit are utilized to identify multiple transient glitches. This analysis provides to VLSI designers information about the sensitivity of particular parts of a chip and could facilitate the process of error-resistant circuit development. Furthermore, SER evaluation is closely related to the analysis of the masking mechanisms and especially the electrical and timing masking. Therefore, in this work, comprehensive modeling of these factors is presented, and their impact on SET pulse propagation is discussed. TCAD characterization provides the current pulses that are utilized for SET pulse generation with SPICE. The experimental results on different technologies demonstrate the significance of an accurate timing analysis on SER estimation.

## **Chapter 3**

## Background

#### 3.1 Introduction

A considerable innovation of the technology community is to improve ICs performance. However, due to the rapid evolution of CMOS technology, circuit reliability has become a major challenge for designers. In particular, TFs induced by neutron strikes constitute a serious threat to the susceptibility of modern chips since they may lead to soft errors. Cosmic radiation and specifically high-energy particles that strike the silicon are considered to be the prevalent causes of such errors. Fortunately, these malfunctions are not catastrophic and do not damage the devices. However, corrupted functionality may be induced due to a wrong logic state of a gate. Previous studies focused on the analysis of the particular phenomenon mainly for space applications. Nevertheless, it has now been observed that terrestrial systems are sensitive to neutrons derive from the atmosphere owing to the down-scaling of transistor size.

### 3.2 D Flip-Flop Description

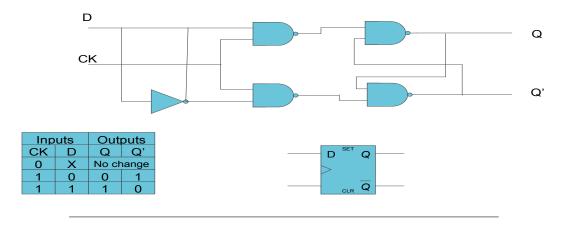

FIGURE 3.1: D Flip-Flop description.

Sequential digital circuits are used to implement the proposed methodology, and according to their structure, memory elements are controlled by the clock. Logic gates and Flip-Flops (FFs) are the components of these circuits, and the latter are driven by the combinational logic and lead to gates. The FF is a modern sequential element used to store data information, and its outputs respond to input when the clock pulse is applied as input. In other words, FFs are utilized as memory components since their state can be maintained and may be changed when an appropriate

input signal is implemented. Benchmarks circuits, designed, include D FFs as memory elements. This type of FF is called D FF, from the ability to hold data. It has only two inputs, the D and clock, and Figure 3.1 shows its truth table and its schematic circuit symbol.

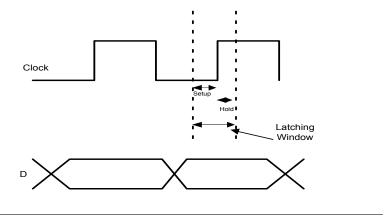

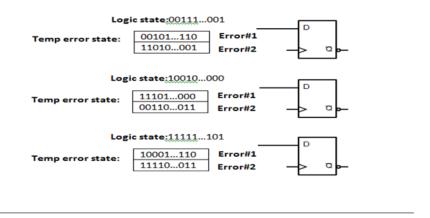

Setup time and hold time are two critical parameters and are the factors that determine the timing constraints under which FFs operate. In particular, the setup time is the minimum amount of time the data signal should be held steady before the clock's active edge so that to be latched correctly. On the other hand, the hold time is the minimum amount of time the data signal should be held steady after the clock event. Furthermore, the latching window is estimated as the sum of the aforementioned factors as Figure 3.2 shows. In other words, the latching window is determined by the setup and hold time, and the input signal should be stable inside this time interval to be reliably latched. Otherwise, FFs output value may be corrupted.

FIGURE 3.2: Determination of latching window

### 3.3 Soft Errors Generation

A logic state of a node can be changed when a high-energy particle strikes on the silicon region of a transistor since several electron-hole pairs are generated. A node, which is affected by a particle hit, may be an internal transistor node or a gate's output leading to the generation of voltage pulse at the output of the corresponding cell. The propagation of TFs is modeled using masking mechanisms analyzed at each stage to assure the accuracy of our methodology.

Change in gates logic state, and as a result, corruption in ICs performance can be provoked due to an energetic particle strike. In the circuit combinational part, a malfunction, induced owing to the radiation, propagates and a soft error may be caused if the transient fault is latched by a memory element. They are called soft because the impact of hardware failures on circuit functionality is momentary. In other words, this category of faults can be mended and is different from permanent disturbances, which may cause severe damages to systems. Even though soft errors are not severe threats for the applications, a tool that characterizes their behavior is necessary to ensure high levels of systems reliability.

Soft errors temporarily affect sub-micron devices and are not catastrophic for their functionality. High energetic ions and alpha particles are the principal causes of these disturbances. The interaction of high-energies ions with the silicon material of systems should be analyzed further to model the soft errors caused by radiation. In other words, transistors constitute the fundamental components of modern circuits. Hence, the impact of the high-energetic particles on particular structures should be studied. The charge, collected due to the interaction of a heavy-ion with the p-n junction of a transistor, is affected by the electron-hole pairs created as a particle propagates through the silicon. Therefore, an additional current pulse is created on the transistor node, which is due to the movement of the generated charge carrier toward the p-n junction and the collection of redundant electrons by the depletion region.

### 3.4 Current Pulse Model

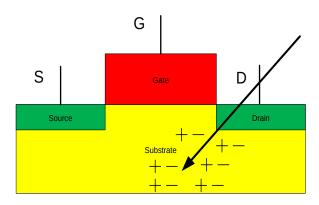

Electron-hole pairs are generated, when the silicon layer of a circuit is affected by a particle hit due to cosmic radiation, as shown in Figure 3.3 or are deposited by alpha particles found in ICs packaging materials. When a depletion region of a gate collects the resultant ionization track, then a current pulse is formed at its internal node. Therefore, the generated pulse may exceed the threshold level, i.e., the half of supply voltage, and settles to logic 1 or 0 if the resultant collected charge exceeds the critical charge ( $Q_{crit}$ ) of the particular gate.  $Q_{crit}$  is the minimum charge required for a particle strike to provoke a TF, and its value has been decreased due to the continuous technology shrinking, which means that even particles of smaller energies can cause a malfunction in the circuit operation.

FIGURE 3.3: A simple presentation of a particle hit.

Particle strikes are represented by independent current sources connected to NMOS or PMOS transistors of the affected gate, and their result is reflected in the output pulse. A widely used model for the radiation-induced current is the double-exponential current pulse, which is expressed by Equation:

$$I_{particle}(t) = \frac{Q_{coll}}{\tau_{\alpha} - \tau_{\beta}} (e^{-t/\tau_{\alpha}} - e^{-t/\tau_{\beta}})$$

(3.1)

where  $Q_{coll}$  denotes the collected charge,  $\tau_{\alpha}$  is the time moment the electron-hole pairs are deposited in the p-n junction, and  $\tau_{\beta}$  is the time moment the particle hits the silicon [81]. These time values are the rise and fall time constants respectively of the current pulse. Furthermore,  $Q_{coll}$  depends mainly on the energy of the particle strike, its angle and the characteristics of the device, whereas  $Q_{crit}$  is solely related to the device characteristics and can be estimated, through spice simulations, from

the integral of  $I_{particle}$  with respect to time, as Equation 3.2 shows:

$$Q_{crit} = \int_0^t I_{particle}(t)dt \tag{3.2}$$

The critical charge depends on the supply voltage and capacitance node, whereas particle energy, transistors size, and doping value are some of the parameters, which have an impact on the collected charge value. In general, a soft error is induced by a particle hit or alpha particles when the  $Q_{coll}$  is greater than  $Q_{crit}$ . Furthermore, due to the reduction in supply voltage and transistors size, the factor  $Q_{crit}$  of gates has been decreased, which means the number and the importance of soft errors have been increased considerably.

## 3.5 Soft Errors Causes

TFs constitute a significant concern for VLSI systems reliability since they propagate through circuit gates and may lead to soft errors if some of them are latched by a memory element. The most common soft error sources are alpha particles and highenergy neutrons. The former can be found in circuits packaging material as there are radioactive elements such as uranium and thorium, which generate alpha particles. While the latter, induced due to cosmic radiation in the atmosphere, may strike the silicon of an IC resulting in TFs. In order to succeed an accurate SER evaluation, the aforementioned sources should be accounted for.

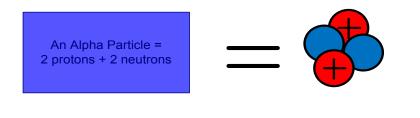

## 3.5.1 Alpha particles

FIGURE 3.4: Alpha particles component.

Transient glitches in package material are caused by particles emitted by radioactive impurities. Two protons and neutrons, bounded together as shown in Figure 3.4, are the alpha particles components. They are emitted through a radioactive decay process called alpha decay, which means that radioactive isotopes uranium and thorium can generate alpha particles affecting semiconductor devices. Their energy is lower than those of heavy-ions, but they may have an impact on circuit functionality. In particular, alpha particles energy is in the range of 1-9 Mev, and this amount is sufficient to generate a charge. In other words, a dense track of electron-hole pairs is generated as an alpha particle is penetrated in silicon, causing an imbalance in a circuit's electrical properties. Also, another factor, which affects the number of electron-hole pairs besides alpha particles energy is the material density [82]. Therefore, the quality of material utilized to fabricate sub-micron devices affects the emission of alpha particles. To be generated approximately one million electron-hole pairs, only energy at 3.4eV is needed to cause an additional charge, which is enough

to change the logic state of a gate. However, many studies focus now on the SER evaluation due to neutrons induced by radiation since alpha particles can be coped with techniques, which concentrate on changing ICs packaging material.

#### 3.5.2 Cosmic radiation

The second source of transient faults, which may lead to soft errors, is associated with cosmic radiation. In other words, if a system is affected by a heavy ion, the resulting deposited charge may induce transient faults. Protons and neutrons are the principal heavy ions, which may cause ionization in susceptible ICs. These radioactive elements are derived from cosmic rays, which are of galactic or solar origin. The protons have energies greater than 30 MeV, whereas the energies of neutrons range from 10 to 800 MeV.

Neutrons, which can cause disturbances to IC functionality, is regarded as a sub-atomic particle. In particular, atoms consist of particles called protons, electrons, and neutrons. The protons have a positive charge and are in the nucleus of the atoms, while the electrons are negatively charged and are contained on the electron shells. Atoms include the same number of protons and electrons and, thus, are regarded as neutral elements. On the other hand, the third type of particles is found in the nucleus and uncharged. When an atom disintegrates, then neutrons, which cause soft errors on circuits, are generated. In other words, terrestrial cosmic rays are caused when space particles hit the atmospheric atoms.

Furthermore, high-energy ions have a different interaction with the devices in comparison with typical alpha particles [83]. In particular, when a neutron collides with the silicon of a device, ionized particles are produced, which next generates electron-hole pairs with greater energies than those generated by alpha particles. In other words, alpha particles cause direct charge generation, interacting with electrons, while secondary particles are generated from the collision of neutrons with the semiconductor. Therefore according to the latter situation, TFs are provoked under systems by electron-hole pairs caused by these nuclear secondary elements. That is a notable reason why many studies have focused on SER evaluation due to cosmic radiation.

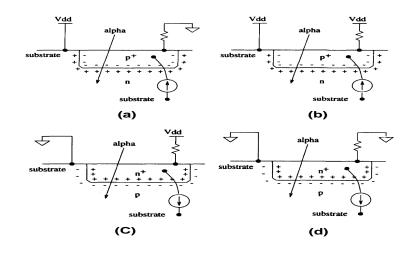

### 3.5.3 Electron-holes generation

The modeling of circuits logic level under the existence of ionized and alpha particles, i.e., the influence of particle strikes on MOS transistors, is the main subject of the particular section. An inverter is employed to present logic and electrical level analysis since it is a simple gate, and the other components are modeled similarly. Electron-holes pairs are created when a high-energy particle hits a gate's transistor. Electrical field existence in the depletion region and the deposition of the aforementioned elements in p-n junction result in charge collection modeled by double-exponential current pulse as described in Equation 3.1.

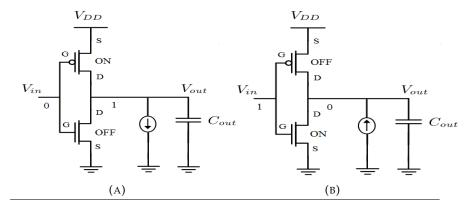

Four cases describe the flow of the holes and electrons due to charge injection as shown in Figure 3.5 [66]. In the two former cases, the voltage value rises approaching Vdd voltage, while in the latter, the voltage temporarily decreases. According to the second and fourth cases, transistors' logic states will not be affected because both of them are in an active state. In other words, the PMOS transistor is connected to the supply voltage while the NMOS is to the ground. However, in the remaining cases, transistors may be affected by particle hit changing their logic state.

FIGURE 3.5: Alpha particle effect on active and in-active transistors.