## A Flexible Ultralight Hardware Security Module for EPC RFID Tags

by

Ahmed Ayoub

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2021

© Ahmed Ayoub 2021

### Examining Committee Membership

The following served on the Examining Committee for this thesis. The decision of the Examining Committee is by majority vote.

| External Examiner:                       | Arash Reyhani-Masoleh<br>Professor, Dept. of Electrical and Computer Engineering,<br>Western University                                                                                               |  |  |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Supervisor:                              | Mark Aagaard<br>Associate Professor, Dept. of Electrical and Computer Engineering,<br>University of Waterloo                                                                                          |  |  |

| Internal Members:                        | Guang Gong<br>Professor, Dept. of Electrical and Computer Engineering,<br>University of Waterloo<br>Hiren Patel<br>Professor, Dept. of Electrical and Computer Engineering,<br>University of Waterloo |  |  |

| Internal-External Member: Martin Karsten |                                                                                                                                                                                                       |  |  |

| nal-External Member: | Martin Karsten                                            |

|----------------------|-----------------------------------------------------------|

|                      | Associate Professor, Cheriton School of Computer Science, |

|                      | University of Waterloo                                    |

### Author's Declaration

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Due to the rapid growth of using Internet of Things (IoT) devices in daily life, the need to achieve an acceptable level of security and privacy for these devices is rising. Security risks may include privacy threats like gaining sensitive information from a device, and authentication problems from counterfeit or cloned devices. It is more challenging to add security features to extremely constrained devices, such as passive Electronic Product Code (EPC) Radio Frequency Identification (RFID) tags, compared to devices that have more computational and storage capabilities.

EPC RFID tags are simple and low-cost electronic circuits that are commonly used in supply chains, retail stores, and other applications to identify physical objects. Most tags today are simple "license plates" that just identify the object they are attached to and have minimal security. Due to the security risks of new applications, there is an important need to implement secure RFID tags. Examples of the security risks for these applications include unauthorized physical tracking and inventorying of tags. The current commercial RFID tag designs use specialised hardware circuits approach. This approach can achieve the lowest area and power consumption; however, it lacks flexibility.

This thesis presents an optimized application-specific instruction set architecture (ISA) for an ultralight Hardware Security Module (HSM). HSMs are computing devices that protect cryptographic keys and operations for a device. The HSM combines all security-related functions for passive RFID tag. The goal of this research is to demonstrate that using an application-specific instruction set processor (ASIP) architecture for ultralight HSMs provides benefits in terms of trade-offs between flexibility, extensibility, and efficiency. Our novel application specific instruction-set architecture allows flexibility on many design levels and achieves acceptable security level for passive EPC RFID tag. Our solution moves a major design effort from hardware to software, which largely reduces the final unit cost.

Our ASIP processor can be implemented with 4,662 gate equivalent units (GEs) for 65 nm CMOS technology excluding cryptographic units and memories. We integrated and analysed four cryptographic modules: AES and Simeck block ciphers, WG-5 stream cipher, and ACE authenticated encryption module. Our HSM achieves very good efficiencies for both block and stream ciphers. Specifically for the AES cipher, we improve over a previous programmable AES implementation result by  $32\times$ . We increase performance dramatically and increase/decrease area by 17.97/17.14% respectively. These results fulfill the requirements of extremely constrained devices and allow the inclusion of cryptographic units into the datapath of our ASIP processor.

#### Acknowledgements

First and foremost, I would like to praise and thank God who has granted countless blessing, knowledge, and opportunity to me so that I have been finally able to accomplish this thesis.

I would like to express my sincere appreciation to my supervisor, Professor Mark Aagaard for his tremendous support, guidance, encouragement and patience during my study at University of Waterloo. I have learned a lot from his vast experience and technical knowledge. Without his continuous support for my research and my personal life, this thesis would not have been possible.

I would like to express my appreciation to Professor Guang Gong for her support, and guidance. Many thanks for discussions, explanations, and clarifications during communications security lab (ComSec) seminars. I would like to thank my committee members, Professor Hiren Patel, Professor Martin Karsten, and Professor Arash Reyhani-Masoleh. For their time, good questions, and valuable comments.

I would like to give special thanks to all my colleagues and friends during my PhD studies. Special thanks to Nusa Zidaric, Gangqiang Yang, Bo Yang, Marat Sattarov, Jenny Yu, and all other past and present members of the ComSec lab.

Also, thanks to my former supervisors at Cairo University Professor Serag El-Din Habib, and Professor Hossam Fahmy who guided me through my BSc and MSc and taught me how to keep learning, be more productive and develop on the personal level.

I would like to express my gratitude to my parents Nagwa, and Abdelmordy. Without their encouragement, I would never reach to this point. All of my accomplishments through my life have been realized by endless love and support of them. Thanks to my sister Nahla and my brother Mohammad for their support and unconditional love.

Last but not least, I would like to express my deepest appreciation to my wife Hoda, my son Hamza, and my daughter Yasmine for their cooperation, sacrifices, and friendship during my PhD journey. Their love and friendship are great gifts in my life.

### Dedication

This thesis is dedicated to my family, friends, and all the people who helped me to get this work done.

## **Table of Contents**

| Li                    | List of Tables xii       |                  |           |                                              |    |  |

|-----------------------|--------------------------|------------------|-----------|----------------------------------------------|----|--|

| Li                    | List of Figures xiv      |                  |           |                                              |    |  |

| Li                    | List of Abbreviations xv |                  |           |                                              |    |  |

| 1                     | Int                      | roduct           | ion       |                                              | 1  |  |

| 2                     | Bac                      | ckgrou           | nd        |                                              | 6  |  |

|                       | 2.1                      | Securi           | ty and Cr | ryptography                                  | 6  |  |

|                       |                          | 2.1.1            | Symmet    | ric-key cryptography                         | 10 |  |

|                       |                          |                  | 2.1.1.1   | Stream ciphers                               | 10 |  |

|                       |                          |                  | 2.1.1.2   | Block ciphers                                | 11 |  |

|                       |                          |                  | 2.1.1.3   | Mode of operations in block ciphers          | 12 |  |

|                       |                          |                  | 2.1.1.4   | Pseudorandom number generators               | 14 |  |

| 2.1.1.5Hash functions |                          | Hash functions   | 15        |                                              |    |  |

|                       |                          | ght cryptography | 16        |                                              |    |  |

|                       |                          | security         | 18        |                                              |    |  |

|                       |                          | 2.1.4            | Hardwar   | e security module                            | 19 |  |

|                       |                          |                  | 2.1.4.1   | Secure Hardware Extension                    | 20 |  |

|                       |                          |                  | 2.1.4.2   | Payment Card Industry Data Security Standard | 20 |  |

|   |     |        | 2.1.4.3 Trusted Execution Environment       | 21        |

|---|-----|--------|---------------------------------------------|-----------|

|   |     |        | 2.1.4.4 Trusted Platform Module             | 22        |

|   |     | 2.1.5  | Security validations standards              | 22        |

|   |     |        | 2.1.5.1 FIPS 140-2                          | 22        |

|   |     |        | 2.1.5.2 Common criteria                     | 23        |

|   | 2.2 | Digita | l Hardware Circuits                         | 25        |

|   |     | 2.2.1  | Digital hardware circuits design approaches | 25        |

| 3 | EPO | C RFI  | D Systems                                   | <b>27</b> |

|   | 3.1 | RFID   | standards                                   | 27        |

|   | 3.2 | RFID   | system components and overall behaviour     | 29        |

|   |     | 3.2.1  | Types of RFID tags                          | 29        |

|   |     |        | 3.2.1.1 power supply source                 | 30        |

|   |     |        | 3.2.1.2 Frequencies, Coupling method        | 31        |

|   |     |        | 3.2.1.3 Overall behaviour                   | 33        |

|   | 3.3 | EPC I  | RFID tag specifications                     | 35        |

|   |     | 3.3.1  | RFID Tag reading range and Power            | 35        |

|   |     | 3.3.2  | RFID Tag speed and response time            | 35        |

|   |     | 3.3.3  | RFID tag microchip and memory banks         | 36        |

|   |     | 3.3.4  | Reader stages/commands and Tag states:      | 37        |

|   |     |        | 3.3.4.1 Tag states:                         | 38        |

|   |     |        | 3.3.4.2 Reader commands:                    | 40        |

|   | 3.4 | The E  | PC tag requirements                         | 41        |

|   |     | 3.4.1  | Functional Requirements:                    | 42        |

|   |     | 3.4.2  | Security Requirements:                      | 42        |

|   |     | 3.4.3  | Performance Requirements:                   | 42        |

|   |     | 3.4.4  | Area Requirements:                          | 43        |

|   |     | 3.4.5  | Power Requirements:                         | 44        |

|   | 3.5  | Relate | ed Work                                                    |       | 44 |

|---|------|--------|------------------------------------------------------------|-------|----|

|   |      | 3.5.1  | Security for RFID tags                                     |       | 44 |

|   |      | 3.5.2  | Hardware architectures for RFID tags                       |       | 46 |

|   |      |        | 3.5.2.1 Software-based approach                            |       | 46 |

|   |      |        | 3.5.2.2 Specialized hardware approach                      |       | 47 |

|   |      |        | 3.5.2.3 ASIP-based approach                                | <br>• | 47 |

| 4 | Syst | tem le | evel design                                                |       | 48 |

|   | 4.1  | Top-le | evel design                                                |       | 48 |

|   | 4.2  | The E  | EPC tag digital baseband responsibilities                  |       | 50 |

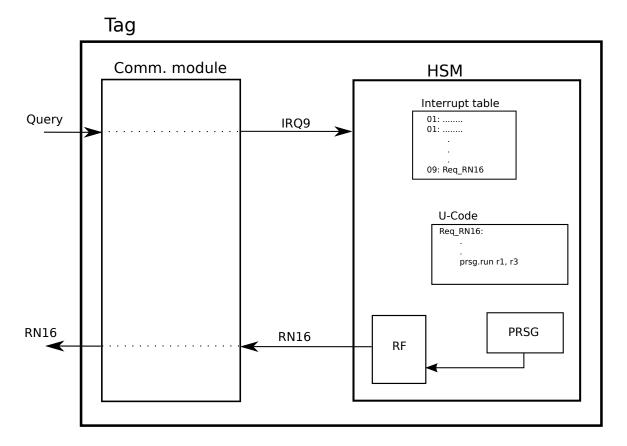

|   | 4.3  | The in | nteraction between the HSM and the CM                      | <br>• | 55 |

| 5 | The  | • HSM  | I Architecture                                             |       | 59 |

|   | 5.1  | The o  | verall architecture                                        |       | 59 |

|   | 5.2  | Instru | action-set architecture                                    |       | 61 |

|   | 5.3  | Instru | ction Formats                                              |       | 62 |

|   |      | 5.3.1  | Register Format (R-type)                                   |       | 62 |

|   |      | 5.3.2  | First Immediate format (I1-type)                           |       | 65 |

|   |      | 5.3.3  | Second Immediate format (I2-type)                          |       | 66 |

|   | 5.4  | Instru | ction format design decisions                              |       | 66 |

|   |      | 5.4.1  | Three-operand vs. two-operand ISA architectures            |       | 67 |

|   |      | 5.4.2  | Stack-based vs. register-based ISA architectures           |       | 67 |

|   |      | 5.4.3  | Variable length instructions vs. fixed length instructions |       | 68 |

|   | 5.5  | The A  | ASIP HSM features                                          |       | 68 |

|   |      | 5.5.1  | Interrupt driven control                                   |       | 69 |

|   |      | 5.5.2  | Input/output operations                                    |       | 70 |

|   |      | 5.5.3  | Instruction-set extension                                  |       | 73 |

|   |      | 5.5.4  | Accelerated mode support                                   |       | 78 |

|   |       | 5.5.5   | Instruction fetch unit and control stack                                       | 78    |

|---|-------|---------|--------------------------------------------------------------------------------|-------|

|   |       | 5.5.6   | Special-purpose registers                                                      | 79    |

|   |       | 5.5.7   | Memory management unit (MMU)                                                   | 80    |

| 6 | Res   | ults ar | nd Evaluations                                                                 | 83    |

|   | 6.1   | HSM     | architecture and results                                                       | 83    |

|   | 6.2   | Other   | work results                                                                   | 85    |

|   | 6.3   | Comp    | arison between our ASIP and Plos's and Groß's processor architecture           | es 87 |

|   | 6.4   | Crypt   | ographic algorithms implementation results                                     | 92    |

|   |       | 6.4.1   | Area considerations, ROM efficiency, and encryption/decryption ef-<br>ficiency | 94    |

|   |       | 6.4.2   | AES block cipher                                                               | 96    |

|   |       | 6.4.3   | Block ciphers: Present and Simeck                                              | 101   |

|   |       | 6.4.4   | Stream ciphers: Trivium and WG-5                                               | 105   |

|   |       | 6.4.5   | ACE authenticated encryption module                                            | 108   |

| 7 | Cor   | nclusio | n and Future Work                                                              | 113   |

|   | 7.1   | Concl   | usion                                                                          | 113   |

|   | 7.2   | Future  | e works                                                                        | 115   |

|   |       | 7.2.1   | Implementation of more security services                                       | 115   |

|   |       | 7.2.2   | Security validations                                                           | 115   |

|   |       | 7.2.3   | The communication module architecture                                          | 116   |

| R | efere | nces    |                                                                                | 117   |

| A | PPE   | NDIC    | ES                                                                             | 126   |

| A | EPO  | C commands               | 127 |

|---|------|--------------------------|-----|

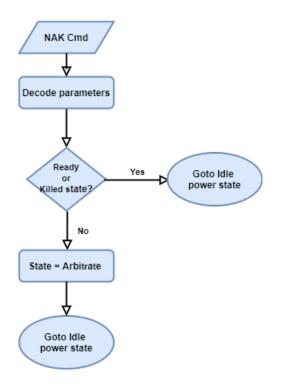

|   | A.1  | NAK command              | 127 |

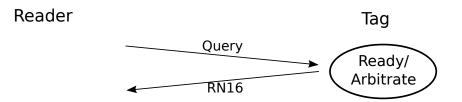

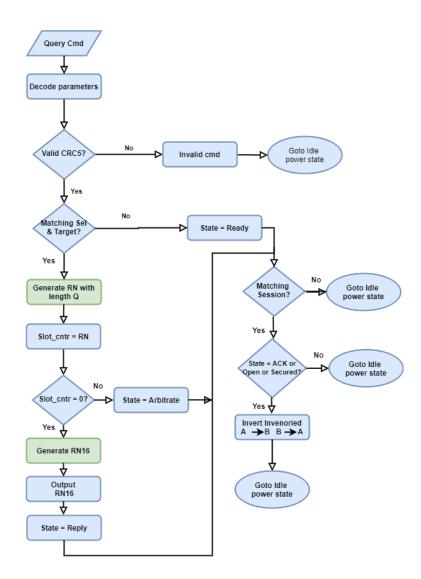

|   | A.2  | Query command            | 128 |

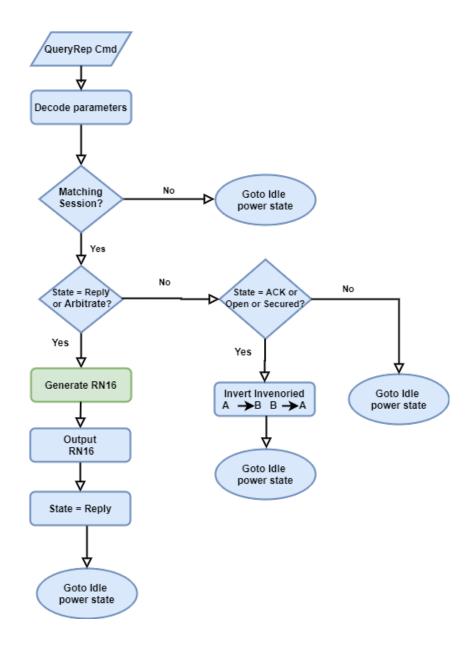

|   | A.3  | QueryRep command         | 129 |

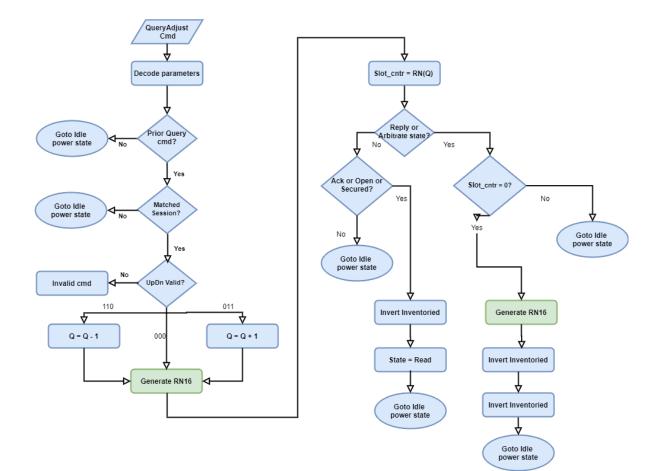

|   | A.4  | QueryAdjust command      | 130 |

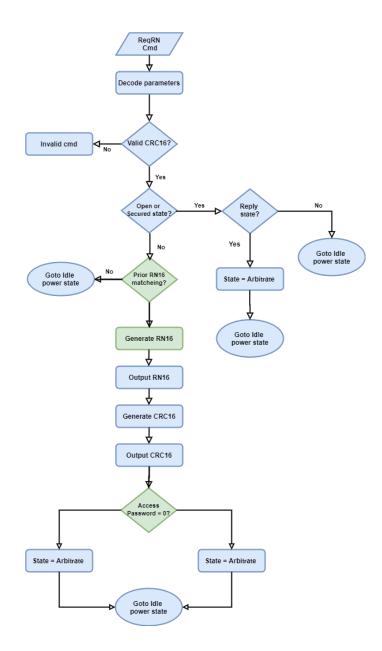

|   | A.5  | ReqRN command            | 131 |

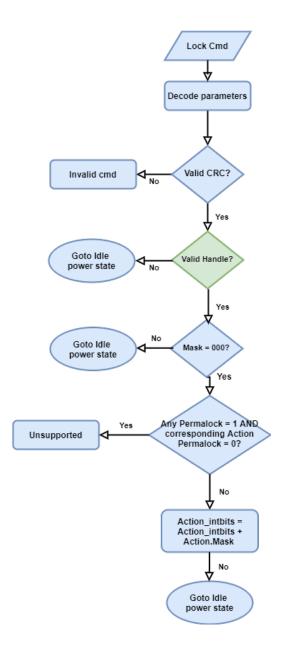

|   | A.6  | Lock command             | 132 |

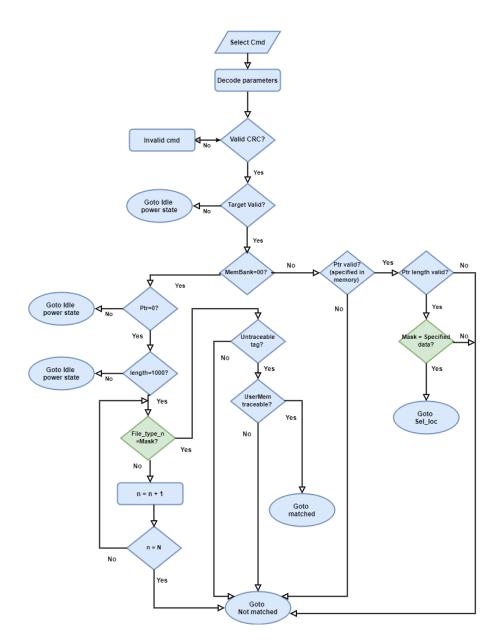

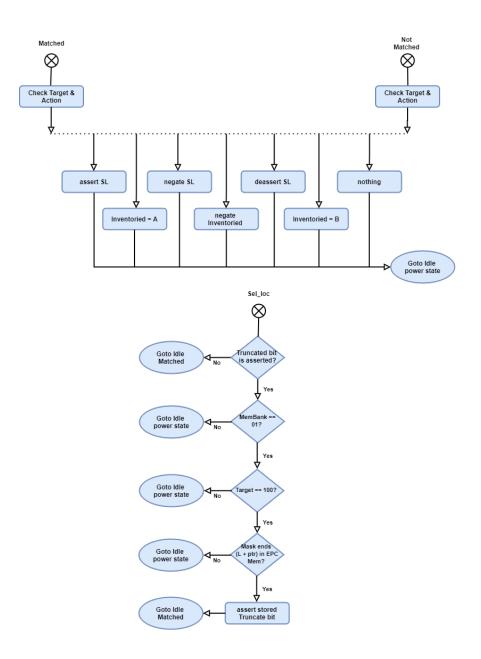

|   | A.7  | Select command           | 133 |

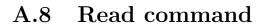

|   | A.8  | Read command             | 135 |

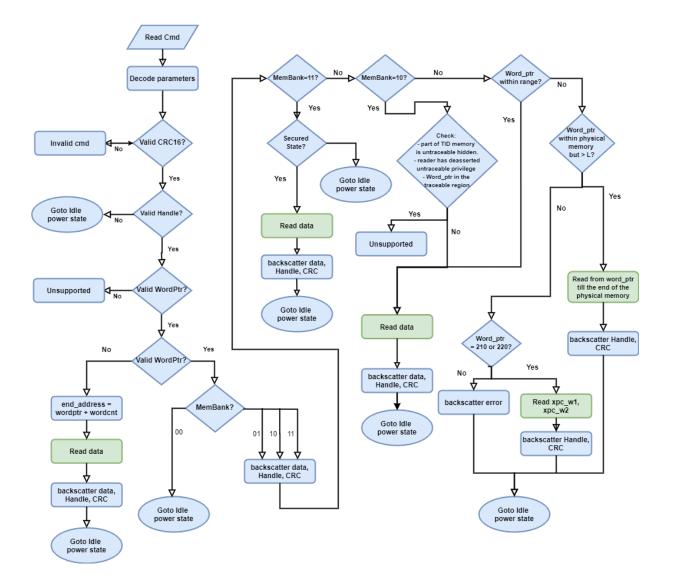

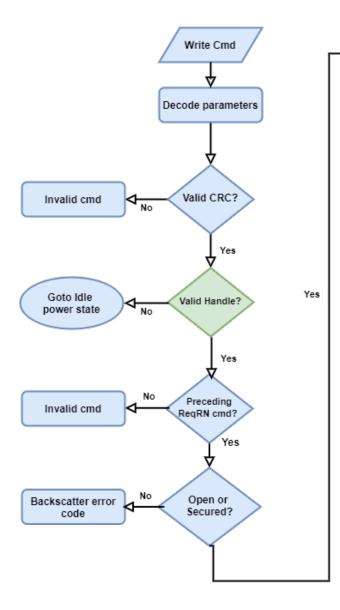

|   | A.9  | Write command            | 136 |

| В | Inst | ruction-set architecture | 137 |

|   | B.1  | Memory/move instructions | 137 |

|   | B.2  | Arithmetic instructions  | 138 |

|   | B.3  | Branch instructions      | 138 |

|   | B.4  | Output instructions      | 139 |

|   | B.5  | Custom instructions      | 139 |

# List of Tables

| 2.1 | The difference between the three hardware architectures                                                                       | 26 |

|-----|-------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | RFID operating frequencies and characteristic                                                                                 | 32 |

| 3.2 | $T_1$ timing and available clock cycles $\ldots \ldots \ldots$ | 43 |

| 4.1 | Responsibilities in the communication module and the HSM $\ldots$                                                             | 53 |

| 4.1 | Responsibilities in the communication module and the HSM $\ldots$                                                             | 54 |

| 5.1 | The meaning and the encodings of the supported instructions $\ldots \ldots \ldots$                                            | 63 |

| 5.2 | Examples of custom instructions encodings and meanings                                                                        | 64 |

| 5.3 | Output instructions                                                                                                           | 73 |

| 5.4 | Custom cryptographic instruction assembly code examples for different options                                                 | 76 |

| 5.5 | Branch/control instructions                                                                                                   | 79 |

| 5.6 | Permission bits structure example                                                                                             | 82 |

| 6.1 | The chip area results for the ASIP design components                                                                          | 84 |

| 6.2 | The related work implementation results                                                                                       | 86 |

| 6.3 | The chip area results                                                                                                         | 88 |

| 6.4 | The selected cryptographic algorithms properties                                                                              | 93 |

| 6.5 | Encryption/decryption operations efficencies for some cryptographic algo-<br>rithms                                           | 95 |

| 6.6 | AES Block encryption operation results in our ASIP HSM                                                                        | 97 |

| 6.7  | Synthesis results of some AES algorithm implementations                    | 98  |

|------|----------------------------------------------------------------------------|-----|

| 6.8  | AES Block encryption operation results in the related work                 | 100 |

| 6.9  | Synthesis results of some block ciphers implementations                    | 101 |

| 6.10 | Block encryption/decryption operation results                              | 103 |

| 6.11 | Encryption/decryption operation results using Simeck 32/64 on our ASIP HSM | 105 |

| 6.12 | Synthesis results of some stream ciphers implementations                   | 106 |

| 6.13 | Stream encryption/decryption operation results                             | 107 |

| 6.14 | Encryption/decryption operation results using WG-5 on our ASIP HSM         | 108 |

| 6.15 | Loading/initialization execution time for ACE in our ASIP HSM              | 109 |

| 6.16 | Encryption/decryption operation results for ACE in our ASIP HSM            | 110 |

| 6.17 | ACE instruction options in our ASIP HSM                                    | 111 |

| 6.18 | Area results for ACE using our ASIP HSM                                    | 112 |

# List of Figures

| 2.1  | CIA triad                                                  | 7  |

|------|------------------------------------------------------------|----|

| 2.2  | Symmetric-key cryptography system                          | 7  |

| 2.3  | Overview of cryptanalysis                                  | 9  |

| 2.4  | General structure of the stream/block cipher               | 11 |

| 2.5  | General structure of the stream cipher                     | 11 |

| 2.6  | One round function in block cipher                         | 12 |

| 2.7  | Block cipher structures                                    | 13 |

| 2.8  | ECB encryption mode                                        | 13 |

| 2.9  | CBC encryption mode                                        | 14 |

| 2.10 | CTR encryption mode                                        | 15 |

| 3.1  | RFID system components                                     | 30 |

| 3.2  | Command-response communication protocol                    | 34 |

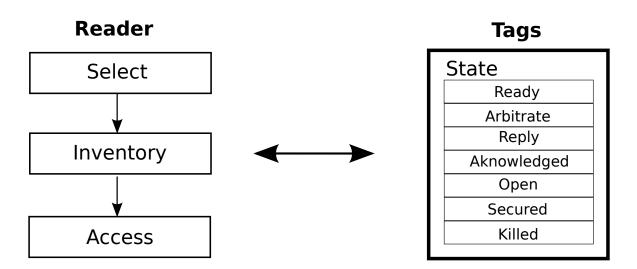

| 3.3  | Reader stages and tag states                               | 38 |

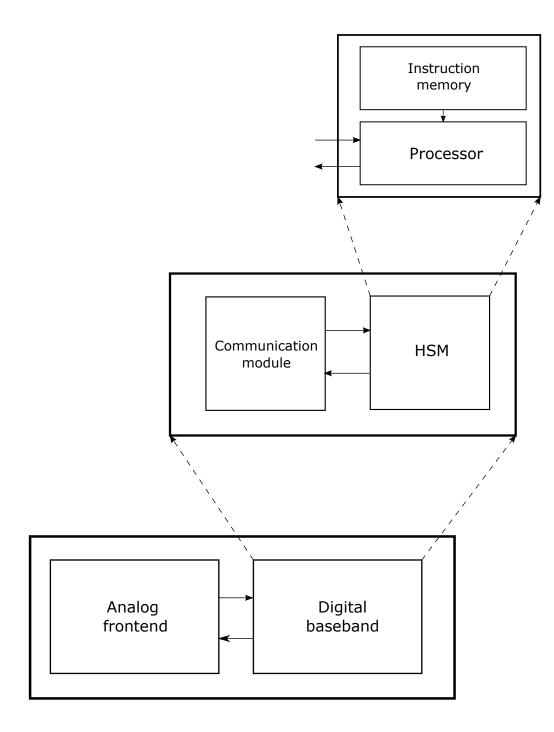

| 4.1  | Tag device components                                      | 49 |

| 4.2  | Tag digital baseband architecture                          | 52 |

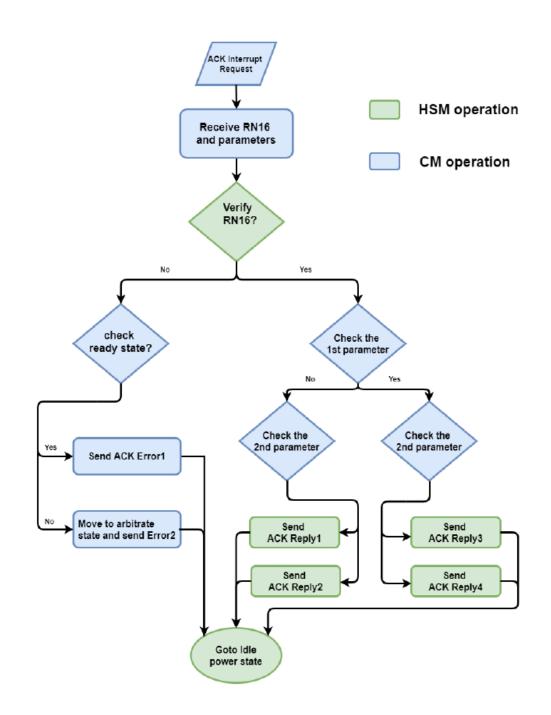

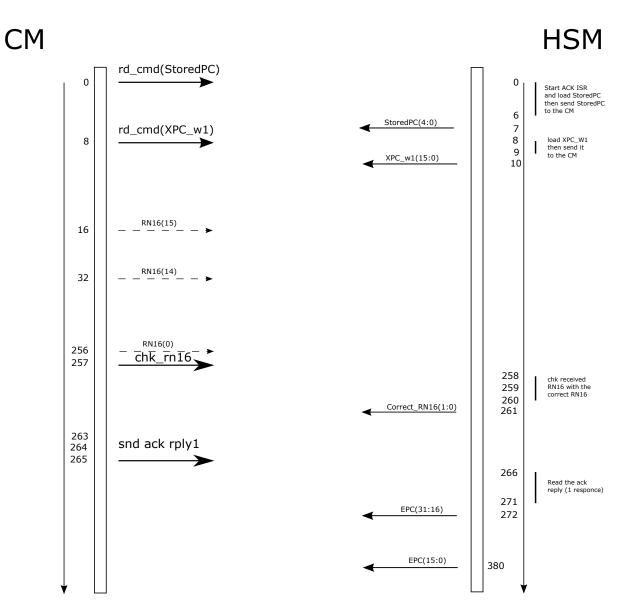

| 4.3  | ACK command operations division between the CM and the HSM | 56 |

| 4.4  | ACK command operations division between the CM and the HSM | 58 |

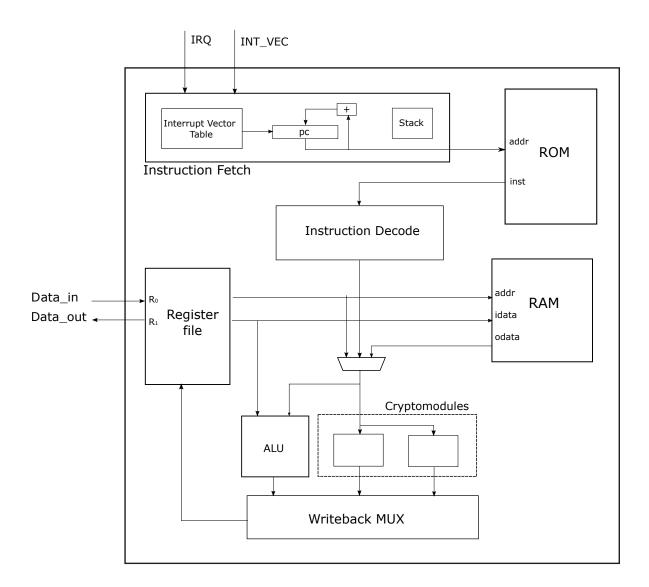

| 5.1  | The microarchitecture datapath for the ASIP HSM            | 60 |

| 5.2  | R-type instruction format                                  | 65 |

| 5.3  | I1-type instruction format                                                                                                                     | 65 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|----|

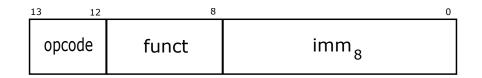

| 5.4  | I2-type instruction format                                                                                                                     | 66 |

| 5.5  | The input/output interface signals                                                                                                             | 69 |

| 5.6  | $R_0$ input register control logic                                                                                                             | 71 |

| 5.7  | $R_1$ output register control logic $\ldots \ldots \ldots$ | 73 |

| 5.8  | The input/output interface for a cryptomodule                                                                                                  | 74 |

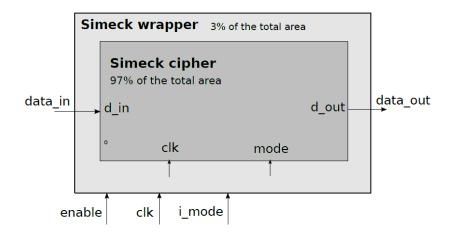

| 5.9  | The included Simeck cipher in the ASIP processor                                                                                               | 75 |

| 5.10 | The cryptomodule interface connections                                                                                                         | 77 |

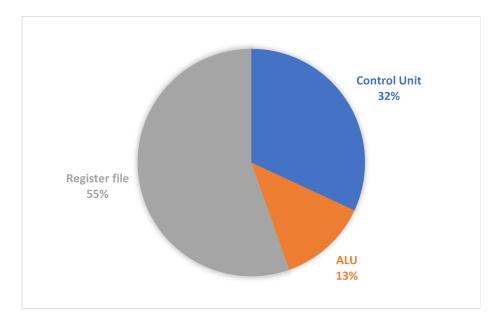

| 6.1  | Our ASIP processor area components                                                                                                             | 89 |

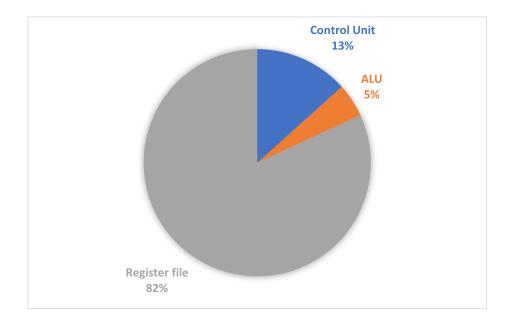

| 6.2  | Plos's processor area components                                                                                                               | 90 |

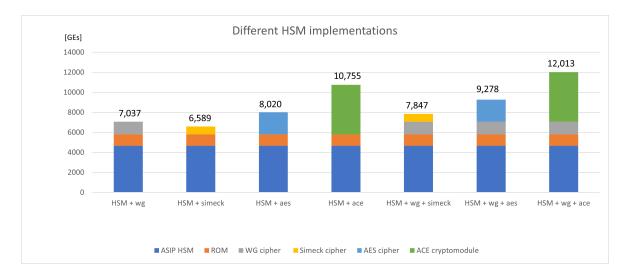

| 6.3  | HSM implementations using different cryptomodules                                                                                              | 91 |

# List of Abbreviations

| AEAD        | Authenticated Encryption with Associated Data  |

|-------------|------------------------------------------------|

| AES         | Advanced Encryption Standard                   |

| ALU         | Arithmetic Logic Unit                          |

| ASIP        | Application Specific Instruction-set Processor |

| CBC         | Cipher Block Chaining mode                     |

| CBC         | Common Criteria Standard                       |

| CC<br>CM    | Communication Module                           |

| Command     | EPC standard command                           |

|             |                                                |

| CRC         | Cyclic Redundant Check                         |

| CTR         | Counter mode                                   |

| DES         | Data Encryption Standard                       |

| ECB         | Electronic CodeBook mode                       |

| EPC         | Electronic Product Code                        |

| EPCglobal   | Electronics Product Code Global Incorporated   |

| FIPS        | Federal Information Processing Standards       |

| FSM         | Finite State Machine                           |

| GE          | Gate Equivalent                                |

| GPP         | General-Purpose Processor                      |

| HASH        | Hash function                                  |

| HF          | High Frequency                                 |

| HSM         | Hardware Security Module                       |

| IEC         | International Electrotechnical Commission      |

| Instruction | What the user writes in assembly code          |

| ISA         | Instruction Set Architecture                   |

| IRQ         | Interrupt Request                              |

| ISO         | International Organization for Standardization |

| ISR         | Interrupt Service Routine                      |

| IoT         | Internet of Things                             |

|             | 0                                              |

| IV      | Initialization Vector                            |

|---------|--------------------------------------------------|

| LF      | Low Frequency                                    |

| NIST    | National Institute of Standards and Technology   |

| NRE     | Non-recurring engineering                        |

| NVM     | Non Volatile Memory                              |

| PCI-DSS | Payment Card Industry Data Security Standard     |

| PRSG    | Pseudo Random Sequence Generator                 |

| PRNG    | Pseudo-Random Number Generator                   |

| RAM     | Random Access Memory                             |

| RF      | Radio Frequency                                  |

| RFID    | Radio-frequency identification                   |

| RISC    | Reduced Instruction-set Computer                 |

| RN16    | 16-bit random number                             |

| ROM     | Read Only Memory                                 |

| SHA     | Secure Hash Algorithm                            |

| sLiSCP  | Simeck-based Permutations for Lightweight Sponge |

|         | Cryptographic Primitives                         |

| SPN     | Substitution-Permutation Network                 |

| SHE     | Secure Hardware Extension                        |

| SOC     | System-on-chip                                   |

| TEE     | Trusted Execution Environment                    |

| TID     | Tag Identification                               |

| TPM     | Trusted Platform Module                          |

| UHF     | Ultra High Frequency                             |

|         |                                                  |

## Chapter 1

## Introduction

The Internet of Things (IoT) is a worldwide network that contains billions of interconnected physical devices. This network enables these devices to collect and exchange data. New applications require security and privacy with minimal possible cost. Radio Frequency Identification (RFID) is one of the technologies that is used to implement IoT applications.

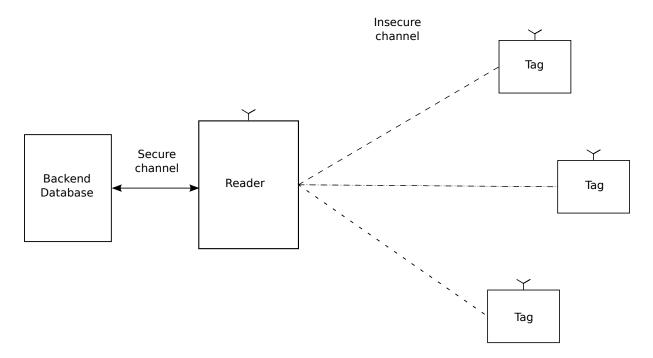

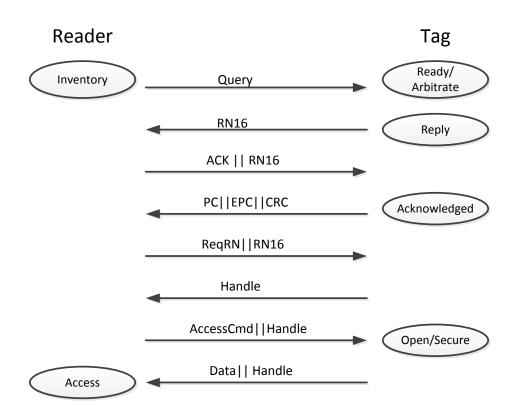

RFID systems are widely used to perform automated identification for physical devices using radio frequency signals. Typically, an RFID system consists of three components: a tag, a reader and a back-end database. The tag is a microchip connected with an antenna, which can be attached to an object as the identifier of the object. The RFID reader communicates with the RFID tag using radio waves. The main advantage of RFID technology is the automated identification that promises changes across a wide range of business activities and aims to add new functionalities to systems that currently use bar codes.

One of the most popular RFID protocols is the EPC Class 1 Gen 2 standard. An Electronic Product Code (EPC) is a unique number that is stored in an EPC tag. Most tags today are simple "license plates" that just identify the object they are attached to, and have only minimal security. Due to the security risks of the new applications, there is an important need to implement cryptographically secure EPC tags. At the same time, adding these services is a significant challenge because of the strict cost, power consumption, and area limitations for the EPC tags.

This thesis presents an optimized application-specific instruction set processor (ASIP) for an ultralight Hardware Security Module (HSM). HSMs are physically separated computing devices that protect cryptographic keys and provide cryptographic operations for a device. We choose EPC tags as a prototype device. The HSM combines all security-related functions for an EPC tag. The goal of this research is to demonstrate that using an ASIP architecture for ultralight HSMs provides benefits in terms of trade-offs between flexibility, extensibility, and efficiency. Our ASIP processor can be implemented with 4,662 gate equivalent units (GEs) for 65 nm CMOS technology excluding cryptographic units and memories. We integrated and analysed four cryptographic modules: Simeck block cipher, WG-5 stream cipher, AES cipher, and ACE authenticated encryption module. We used existing implementations that can be easily plugged in our HSM. We increase performance dramatically and increase area by a small amount in comparison to previous works on adding cryptographic functions to EPC tags.

The main research questions for this thesis can be stated as follows: how feasible is using HSM design for such constrained devices such as EPC tags? And, how effective is using a flexible ASIP-based architecture for EPC tags? HSMs are typically implemented as extension cards or appliances for compute servers and other large, high systems. We have not seen a HSM design for constrained devices as EPC tags that have very limited hardware resources and power consumption. The other gap that we try to fill is adding high level of flexibility to EPC tags by using an ASIP architecture. This flexibility has many benefits in terms of simplicity of the design process to support different applications and to produce different tag models in one fabrication process.

Current EPC tag designs use two approaches: the specialised hardware approach, and the software-based approach. The specialised hardware approach can achieve the lowest area and power consumption and the highest performance for EPC tag designs, however it lacks flexibility and extensibility. The design process in this approach takes a long time and is relatively expensive. On the contrary, the designs that use the software-based approach are much slower and consume more energy. The main advantages of using software-based approach is the high flexibility and the relatively short time to market. The proposed ASIP-based approach can achieve a balance between rich functionality, low cost chips, high performance, and reasonable security requirements as well as high level of flexibility.

The ASIP-based design approach can be almost as efficient as the specialised hardware approach. The ASIP-based approach adds more hardware components and power consumption compared to the specialised hardware approach. However, ASIP processors are designed for specific functions and include only the necessary hardware units. This results in low chip size and low power consumption, similar to that of specialised circuit designs. ASIP architecture allows flexibility and extensibility for EPC tags. In this thesis, flexibility is meant to be the ability to add cryptographic modules into the ASIP processor. The added cryptographic modules can be then accessed using custom instructions. Extensibility is the ability to write different software programs using same or different added cryptographic modules. In other words, extensibility is the ability to implement different tag models by writing different software programs.

Our proposed ASIP architecture for EPC tags has the potential to reduce the unit cost of tags with rich functionality. Compared to specialised hardware approach, the major part of the design effort in the ASIP-based approach is moved from the hardware (i.e. relatively expensive) to the software (cheap). This reduces the non-recurring cost (NRE). The ASIP-based approach allows large scale production by combining more than one tag model in one fabrication process. These tag models have same hardware components but they behave differently according to the included software programs.

The hardware development cost can be amortized over an extremely large number of tag units sold. Hence, the tag unit cost is reduced. The following example shows the potential effect of using the ASIP-based approach on the final unit cost. Suppose that the whole development cost is one million dollars. To get an amortized development cost of 0.1 dollars per tag, 10 millions tag units have to be produced. This does not include the manufacturing cost or profit, which also need to be included in the total price of the tag.

Today's license plate tags are simple; they don't have unique features for different applications. Many applications can use the same tag so it is possible to have demand for 10 millions or more license plate tags. Rich functionality leads to the need for different tag models (i.e. same hardware but different software programs) for different applications. It is possible to combine more than one tag model in one fabrication process to produce the same large number of tags using the ASIP-based approach.

The contributions of this thesis are listed as follows:

1. Introducing the idea and demonstrating the feasibility of creating an HSM that satisfies the constraints of RFID tags. Previous efforts to add security features to RFID tags have integrated the security functionality with the normal functionality. Our system architecture separates the HSM from the standard functionality.

- 2. Developing an ASIP architecture for an ultralight HSM that is significantly more *efficient* in performance vs. area than previous efforts to add security to RFID tags. Our HSM achieves very good efficiencies for both block and stream ciphers. Specifically for the AES cipher, we improve over a previous programmable AES implementation result by  $32\times$ .

- 3. Demonstrating that our ASIP architecture provides significant *flexibility* in plugging in a variety of cryptographic modules with minimal effort. Our ASIP instruction set provides customizable instruction for different ciphers and our micro-architecture provides a flexible but standardized interface to cryptographic modules. The cost of incorporating a cryptographic module into our HSM ranges from an area overhead of 2.37% and 40 lines of assembly code for the AES cipher to 10.39% overhead and 109 lines of code for the ACE authenticated cipher.

- 4. Demonstrating that our ASIP architecture provides significant *extensibility* in adding new functionality to the HSM. Adding support for authenticated encryption did not require any changes to the HSM instruction set or architecture.

- 5. In addition, the novel features of our HSM include:

- Two registers in the register file are used for input/output operations, these registers allow for different serial/parallel loading modes.

- The accelerated mode support; the ASIP can repeat the execution of one instruction multiple times without using a branch or loop instruction.

- Implicit operations can be run after writing some value to the status register or to the accelerated mode/output counter register.

- The integration of extended hardware units is done by using a generic interface. It may be required to design a wrapper for the added unit if its interface is not same as the used generic interface. The other traditional way for integrating a unit uses an intermediate standard bus to interact with the added unit.

- An efficient instruction set optimized for HSMs. The instruction set doesn't include some common operations in most processors like multiplications and cryptographic operations. The main purpose of our ASIP processor is to move data between the memory, the input/output interface, and the extended hardware modules. Complex cryptographic computations are performed by the extended modules.

The rest of the thesis is organized as follows. Chapter 2 provides a background for the related topics and gives a review of the related works focused on secure implementations and lightweight security protocols for passive RFID tags. Chapter 3 discusses the system level architecture for the proposed tag design and explains the functions and the interface of each design's component. Chapter 4 provides a detailed description for the proposed ASIP HSM micro-architecture and its instruction-set architecture. Chapter 5 discusses the obtained results for our design and compares them to the other designs results followed by a conclusion and future works in Chapter 6.

## Chapter 2

## Background

### 2.1 Security and Cryptography

Security is the protection of the computer systems and its information from unauthorized access, disclosure, disruption, modification, inspection, recording or destruction. It is general term used with any form of data such as: electronic form, or physical form.

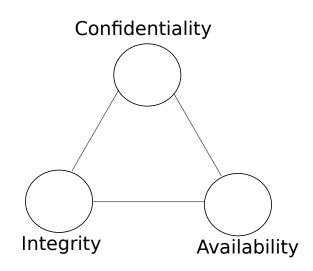

FIPS 199 Standard for Security Categorization of Federal Information and Information Systems by National Institute of Standards and Technology (NIST) [76] lists confidentiality, integrity, and availability as three security objectives for information and information systems, the three basic security objectives are known as the CIA triad as shown in Figure 2.1.

The FIPS-199 standard defines the confidentiality as preserving authorized restrictions on information access and disclosure, including means for protecting personal privacy and proprietary. In other words, a loss of confidentiality or privacy is the unauthorized disclosure of information. The integrity is defined as guarding against improper information modification or destruction, and includes ensuring information non-repudiation and authenticity. Availability is defined as ensuring timely and reliable access to and use of information.

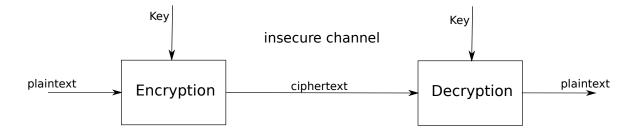

The privacy and authentication of information are two security problems which cryptography studies and solves. The first term "privacy" can be achieved by encryption process which transforms a plaintext, the data in its original form, into a ciphertext. The function that transforms a plaintext message to a ciphertext message is called a cipher. The

Figure 2.1: CIA triad

plaintext message afterwards could be recovered by the process of decryption. The second problem that cryptography solves is authentication. Message "authentication" means that the received message is actually sent by the true sender. Figure 2.2 shows a symmetric-key cryptography system that the cipher and the decipher has the same secret key.

Figure 2.2: Symmetric-key cryptography system

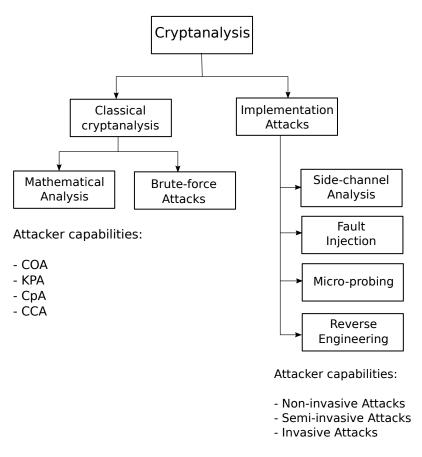

The classical cryptanalysis is a reverse function of cryptography, which studies methods for obtaining the meaning of encrypted information, without access to the secret information such as the secret keys. The method that tries to break a crypto-system is called an attack. The attacks in the classical cryptanalysis are classified into four scenarios depending on the adversary capabilities. The adversary may eavesdrop the communications among the entities, this attack is called *Ciphertext-Only Attack* (COA). For all wireless communication systems, the adversary has this capability to intercept communications among the different entities.

The second scenario is when the adversary has access to a limited number of pairs of plaintext and its corresponding ciphertext, this type is called *Known-Plaintext Attack* (KPA). The adversary has more opportunity to succeed by knowing more plaintext ciphertext pairs. In the third attack scenario (CPA), the adversary has the ability to generate a sequence of plaintexts of its choice and it has access to their corresponding ciphertexts. The last one is the most powerful model, called *Chosen-Ciphertext Attack* (CCA). In this attack model, the adversary can choose arbitrary ciphertext and have access to plaintext decrypted from it, it also can choose arbitrary plaintext and have access to the resulting ciphertext encrypted from it.

Another type of cryptanalysis relies on implementation attacks in which the attacker has physical access to a crypto-system such as smart cards, USB tokens, and RFID tags. This physical access may be gaining information from the implementation (i.e. side-channel attack), manipulating with the device to provoke an error (i.e. fault attack), or even spying on inner components of the chip (i.e probing attack).

The implementation attacks can be categorized according to their mechanical invasiveness or the attackers capabilities: non-invasive attacks, semi-invasive attacks, and invasive attack. Non-invasive attacks are considered usually as low-cost cryptanalysis which observe or manipulate with the device without physical harm. Semi-invasive attacks are more expensive than non-invasive attacks but the semiconductor chip is de-packaged but internal structure remains same as before. Invasive attacks are the most expensive method, the attacker has unlimited capabilities to extract information from chips and understand their functionality using expensive equipments. The different categories for cryptanalysis is shown in Figure 2.3. The focus of this thesis is on the hardware design for the HSM and demonstrating that the proposed ASIP architecture is more efficient than previous solutions. Security analysis is outside the scope of this thesis.

Modern cryptography is divided into two typical types: Symmetric-key cryptography and Public-key cryptography. In Symmetric-key cryptography, the sender and the receiver share the same secret key. This key is called symmetric key shared between the two parties. Public-key cryptography is a cryptographic system that uses two different keys; a public

Figure 2.3: Overview of cryptanalysis

key and a private key. In case of encryption/decryption processes, a public key is used for encryption and a private key that is used for decryption. The public key is known to everybody but the private key is known only to the owner (as in the decryption entity) or to the owner and the third-trusted party that may generate it.

Both cryptography types have some advantages and disadvantages. The main advantage in symmetric-key cryptography is the speed and less complexity compared to publickey cryptography. The public-key cryptography involves intensive computations so it is not feasible for EPC tags due to area and power constraints. The key management in public-key cryptography is much easier compared to symmetric-key cryptography as the public key is known by everyone and could be shared within an insecure channel. The key in the symmetric-key cryptography should kept secret while transferring to any party. One system may have many keys used for different cryptographic algorithms such as encryption/decryption key, and authentication/verification key. In symmetric-key cryptography, there are shared secret key for encryption/decryption algorithm and there is another shared secret authentication key for the authentication algorithm. On the other hand, a different keys pair is used for the authentication or in the digital signature algorithm, the public authentication key is used for signing while the private authentication key is used for the verification process. The public key could be shared and known by everyone.

In some systems, both cryptography types are used to combine the advantages from both types. Public key cryptography is used for the key establishment and symmetric-key exchange while symmetric key cryptography is used for the communications. In general, the symmetric key cryptography is used when performance is required as in the wireless communication systems.

This thesis uses only lightweight symmetric-key ciphers that are suitable for extremely constrained devices. Both block and stream ciphers have been used. AES is used in this thesis for benchmarking reasons to compare the efficiency to previous solutions. The generic kind of our solution allow for implementing different cryptographic mode of operations in software.

### 2.1.1 Symmetric-key cryptography

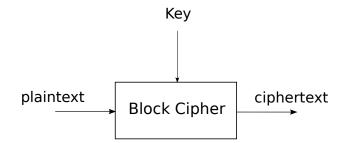

Symmetric-key ciphers are implemented as either block ciphers or stream ciphers. A block cipher encrypts input in blocks of plaintext, examples of the block lengths are 128-bit or 256-bit block lengths. A stream cipher enciphers instantaneously one-bit or a small number of bits such as 8-bit. Figure 2.4 shows a general structure of the stream/block cipher.

### 2.1.1.1 Stream ciphers

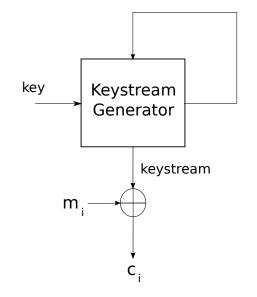

Stream ciphers is one kind of symmetric-key ciphers where a small number of plaintext bits is encrypted instantaneously (i.e. bit by bit or byte by byte). The general structure of the stream ciphers is shown in Figure 2.5. The keystream generator generates a keystream sequence depending on the seed or the input key. The key could be the initial state of the

Figure 2.4: General structure of the stream/block cipher

feedback shift register, the input key is random. The ciphertext bit  $C_i$  is the XOR result between the input plaintext bit  $m_i$  and the keystream bit at a certain time i.

Figure 2.5: General structure of the stream cipher

### 2.1.1.2 Block ciphers

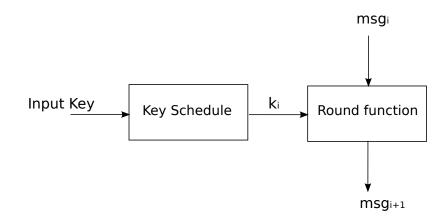

In general, the block cipher consists of two parts: round function and key schedule as shown in Figure 2.6. The round function is iterated multiple times in order to increase the unpredictability between the plaintext and the ciphertext. More rounds increase this unpredictability but it increases the total time to output the ciphertext as well. The key schedule is used for generating new round key  $k_i$  for each round function iteration.

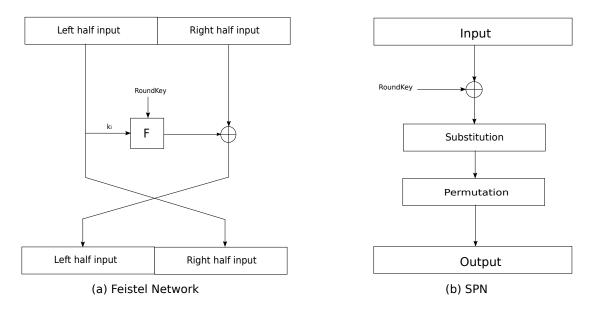

There are two common architectures (structures) for the round function in block ciphers: the substitution permutation network (SPN) and Feistel network.

Figure 2.6: One round function in block cipher

The SPN structure consists of three typical layers: adding the round key, substitution layer, and permutation layer. The well-known example of SPN structure is Advanced Encryption scheme (AES)[22]. In the Feistel Network, the right half output comes directly from the left half input, the left half output is the XORed result of right half input and the output of the function  $\mathbf{F}$  with inputs of the left half input and the Round-Key. One of the common block cipher that uses Feistel network structure is DES which is invented by IBM[33].

#### 2.1.1.3 Mode of operations in block ciphers

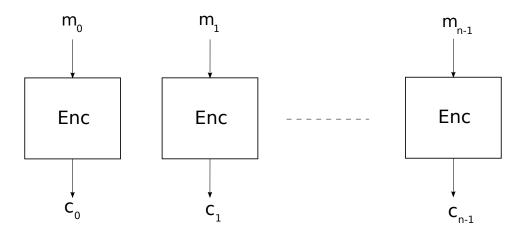

The block ciphers have fixed input/output size, the cipher encrypt one block at time. In case of arbitrary length for the input message, block ciphers mode of operations describe how repeatedly to apply a ciphers's single block operation securely to transfer arbitrary length data larger than a block.

Many mode of operation for the block ciphers have been introduced. ECB or Electronic codebook mode is the simplest mode. In ECB mode, the message is divided into blocks

Figure 2.7: Block cipher structures

and each block is encrypted separately as shown in Figure 2.8. The main drawback of this mode that the repeated plaintext blocks are encrypted into repeated ciphertext blocks however it is easy to implement this mode of operation either in software or in hardware. This mode of operation is not secure under chosen plaintext attack (CPA).

Figure 2.8: ECB encryption mode

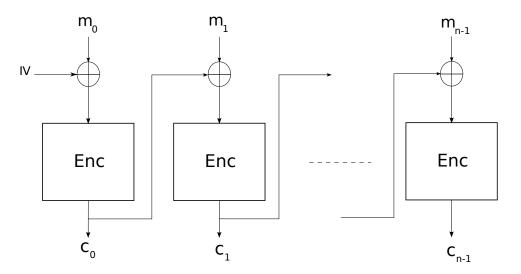

Cipher Block Chaining (CBC) mode is another mode of operation that add some ran-

domization to the encryption algorithm. This leads to get different ciphertext blocks even the same plaintext blocks are repeated. This mode requires generating new random initial vector (IV) every new long message, this IV is sent in clear with the ciphertext blocks. It is most suitable to be implemented in software as every new plaintext message waits the previous ciphertext block to be XORed with it before being encrypted as shown in Figure 2.9.

Figure 2.9: CBC encryption mode

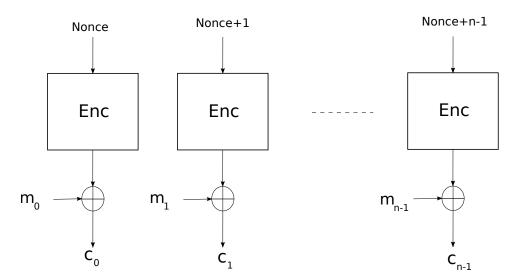

The counter mode ((CTR) combined the benefits of ECB and CBC modes of operation, it generates the next keystream block by encrypting the successive values of a "counter". The "counter" is a sequence of incremented blocks that is initialized by *Nonce* random block. It is easy to be implemented in software or software, both encryption and decryption modes use the same encryption module (Enc) as shown in Figure 2.10. The *Nonce* is chosen randomly every new long message.

### 2.1.1.4 Pseudorandom number generators

Pseudorandom number generator (PRNG) is another important cryptographic module, the main function generates a sequence of random numbers. The generated sequence is not truly random as it is completely determined by the input key or the seed. This because that the function of PRNG is deterministic function. The generated sequence by the PRNG is

Figure 2.10: CTR encryption mode

distinguishable from a truly random number sequence. PRNGs are used to generate random numbers such as *Nonce* or IV or any required random number by a specific application. Also, PRNGs are used to generate keystream random sequence for the stream ciphers.

#### 2.1.1.5 Hash functions

Hash function is another cryptographic module that is used to verify that a certain message maps to a specific hash value. In general, hash functions maps data of arbitrary size to a fixed size short bit string. The hash function is called one-way function as it is infeasible to invert.

Examples of hash function module include: MD5[82], SHA1[88], SHA2[38], SHA3[25]. Not all hash function modules are suitable for low-area low-power devices. Hence, there is a need to use lightweight hash modules, some lightweight hash function module examples include: Quark[11], PRESENT-based[17], PHOTON[47], Lightweight Keccak[57].

### 2.1.2 Lightweight cryptography

Lightweight cryptography is a cryptographic algorithm or protocol tailored for implementation in constrained environments including RFID tags, sensors, contactless smart cards. It targets systems that require a balance between security, cost, performance tradeoffs. In general, it is easy to optimize two of them but it is difficult to consider all of them [26].

In hardware implementations, chip size and energy consumption are two important measures that evaluate the lightweight properties. In software, the smaller code/RAM size is better for lightweight applications. ASIP design is divided between hardware and software, so all of these parameters are considered in our design with support of adequate security.

There are two main approach for implementing lightweight ciphers. The first approach develops hardware optimized implementations for standardized algorithms such as AES and DES block ciphers. The second approach is to design new ciphers suitable for lightweight cryptographic applications.

Several lightweight block cipher algorithms have been introduced such as PRESENT [16], CLEFIA [87]. Various compact hardware implementations of AES have been implemented in [65, 48, 36, 34]. A slight modification of DES cipher causes the appearance of lightweight DESXL cipher [74]. SIMON and SPECK [14] are two recent lightweight block ciphers.

Also some lightweight stream ciphers have been introduced as ECRYPT II eSTREAM project [83], Grain [50], Trivium [19], lightweight WG stream ciphers (WG-5[5], WG-7[62], WG-8[32]). Hummingbird [28] is another lightweight cipher that has a hybrid structure of block cipher and stream cipher.

Lightweight hash functions have been introduced such as Quark [11], PRESENT-based [17]. The standard hash functions such as MD5 and SHA-1 are not suitable for RFID tags due to their large hardware utilization.

PRESENT is an ultra-lightweight block cipher that achieves the required balance between security and hardware efficiency. The block size is 64-bit and the key size can be 80-bit or 128-bit. The non-linear layer is based on a single optimized 4-bit S-box. A problem with block collisions has appeared with block size 64-bit if they are used with large amounts of data [15]. Therefore implementations need to make sure that the amount of data encrypted with the same key is limited and re-keying is properly implemented.

Simon is a family of lightweight block ciphers released by the NSA. Simon has been optimized for performance in hardware implementations, while its sister algorithm, Speck, has been optimized for software implementations [14]. Simeck[91] combines the good design components from both SIMON and SPECK, in order to devise even more compact and efficient block ciphers. Simeck[91] has 10 instances depending on the input block size and number of key words. Simeck32/64, Simeck48/96, Simeck64/128 are some examples of instances have 4 key words and input block size 16, 24, 32 respectively.

Simeck instances [91] are smaller than the similar ones of hardware-optimized cipher SIMON in terms of area and power consumption using same technology. Some security evaluations of Simeck have been done with respect to many traditional cryptanalysis methods, including differential attacks, linear attacks, impossible differential attacks, meet-inthe-middle attacks, and slide attacks. Overall, all of the instances of Simeck can satisfy the area, power, and throughput requirements in passive RFID tags.

Grain is a stream cipher submitted to eSTREAM project in 2004 [50]. Grain is designed primarily for restricted hardware environments. It accepts an 80-bit key and a 64-bit IV. The specifications do not recommended a maximum length of output per (key, IV) pair. A number of potential weaknesses in the cipher have been identified and corrected in Grain 128a which is now the recommended cipher to use for hardware environments providing both 128 bit security and authentication.

Trivium is a lightweight stream cipher designed to provide a flexible trade-off between speed and gate count in hardware, and reasonably efficient software implementation [19]. Trivium was submitted to the Profile II (hardware) of the eSTREAM competition, and has been selected as part of the portfolio for low area hardware ciphers by the eSTREAM project. It generates up to 264 bits of output from an 80-bit key and an 80-bit *IV*. The cipher itself consists of three NLFSRs. Trivium shows remarkable resistance to cryptanalysis for its simplicity and performance, recent attacks leave the security margin looking rather slim. The WG stream cipher family [67] is fast stream ciphers. The original WG is a synchronous stream cipher submitted to the ECRYPT call. The general WG structure uses a word-oriented linear feedback shift register (LFSR) and a filter function based on the Welch-Gong (WG) transformation. Several instances of them have been explored in hardware, such as WG-29, WG-16, WG-7, and WG-5. The lightweight WG stream ciphers, WG-5, WG-7, and WG-8 have been proposed for the resource constrained environments. The lightweight WG ciphers can be used in protecting communication in these constrained devices, such as ensuring data confidentiality and performing entity authentication.

The WG cipher has been designed to produce keystream with guaranteed randomness properties such as: balance, long period, large and exact linear complexity, 3-level additive autocorrelation, and ideal 2-level multiplicative autocorrelation. It is resistant to Time/Memory/Data tradeoff attacks, algebraic attacks and correlation attacks [66].

### 2.1.3 Physical security

Physical security is a barrier to prevent unauthorized physical access to a device. Physical security should resist access, detect, respond, and/or provide evidence of tampering attempts at a later audit. A combination of tamper evidence, response or resistance can be used to create sufficiently strong level of protection to thwart many attacks.

In tamper detection, the device is designed so that it detects tamper attempts are happening. For example, an internal circuit can monitor extremes in the current or electrical properties to indicate a possible tamper event in the device. Tamper response refers to the defensive action taken by the device when tamper occurs. Tamper response typically takes actions such that the security assets in the system are not compromised. For example, making the device non-operational. Tamper evidence refers to auditing or logging the occurrence of a tamper event in the device. The device may have tamper log with more details which further actions can be taken. Tamper resistance is the ability of the device to detect and defend against a threat. The threat may be done by either normal users through normal interfaces or others with physical access to the device. For example, encryption of the sensitive information.

### 2.1.4 Hardware security module

Hardware Security Module (HSM) is a dedicated computing device that protects cryptographic keys and other security assets. It also provides all security services such as encryption/decryption, authentication, and digital signing services. Hardware Security Modules have to be validated for security by one of the security evaluations like FIPS 140-2 [77] or Common Criteria (CC)[1]. HSMs safeguard the cryptographic infrastructure by managing, generating, and storing cryptographic keys inside a protected device.

Including all secure assets in a separate device provides some benefits such as protecting the keys from memory scraping, and protecting the keys from physical theft. Beside these benefits, using hardware rather than software accelerates the cryptographic processing and insures the compliance with security validation evaluations. An HSM can have multiple levels of security and it can possess protection mechanisms to protect against tampering. In general, it works just like any other processing hardware but it is optimized for cryptographic algorithms and secured more thoroughly against physical security threats as well as logical security threats.

HSMs typically could be appliances, cards, or silicon chips. HSMs can be employed in any application that uses cryptographic keys and needs this type of physical protection. Examples of systems that use a HSM include: Card payment system HSMs; SSL, DNS, online banking; mobile payment and verbal banking; smart meters; medical devices; passports, identity cards, electronic passports; credit cards.

There are several specifications/standards in different industries for hardware protected security. The main goal for these specifications is to put a collection of characteristics of hardware mechanisms that are useful to certain industries and to their applications. For example, SAE J3101 [2] is a standard in automotive industry that puts some guidelines for implementing hardware security in ground vehicles. The guidelines cover hardware security related topics such as secure boot, secure storage, secure execution environment, access control, and authentication.

The same concept of including all secure assets in a separate zone has appeared in different names for various applications. Examples include:

• Secure Hardware Extension (SHE)

- Payment Card Industry Data Security Standard (PCI-DSS)

- Trusted Execution Environment (TEE)

- Trusted platform Module (TPM)

#### 2.1.4.1 Secure Hardware Extension

Secure Hardware Extension (SHE) [31] is a specification that defines a set of functions that allows a secure zone (i.e. secure extension within a micro-controller unit) to exist within any electronic control unit installed in a vehicle. It was developed by Escrypt for Audi and BMW via the Hersteller Initiative Software (HIS) group. The secure zone features include storage and management of security keys, authentication, encryption and decryption algorithms that can access through software. Although the standard originated within the German automotive industry, it has since become an open standard accepted at the global level.

The E-safety Vehicle Intrusion proTected Applications (EVITA) has developed a set of guidelines for the design, and the verification of security architectures for automotive electronic control units. EVITA defines the overall functionality of three different hardware security module approaches: full, medium and light. Moreover, it specifies an elaborate set of functions and their parameters for managing security keys as well as encryption and decryption operations.

#### 2.1.4.2 Payment Card Industry Data Security Standard

The Payment Card Industry Data Security Standard (PCI-DSS) [52] defines a set of logical and physical security compliance standards for HSMs specifically for the payments industry. It becomes a fundamental requirement for various payment processes, including PIN processing, card verification, card production, ATM interchange, cash-card reloading and key generation.

A payment platform must address some physical security and logical security requirements. Physical security requirements include:

• Tamper-detection and response mechanisms.

- Resilience to abnormal environmental and operating conditions.

- Protection of sensitive data within the device.

- Preventing disclosure of sensitive information by external monitoring techniques.

- Protection of cryptographic keys inside the device, even if the security boundary is breached.

To be PCI HSM compliant, A HSM software must address the following logical security requirements:

- Resilience against unexpected command sequences or operating modes.

- Secure firmware management.

- Strong authentication prior to running sensitive services.

- Secure key management and key separation to prevent misuse and eliminate exposure of sensitive data and PINs

- Secure audit trail

#### 2.1.4.3 Trusted Execution Environment

Trusted Execution Environment (TEE) is typically offered to provide a secure hardware area in microprocessors. Usually it is built for commercial processors that supports complex operating systems as linux. It guarantees code and data loaded inside to be protected with respect to confidentiality and integrity. The Open Mobile Terminal Platform (OMTP) puts a set of defined threats that the TEE resists against[43]. It also puts two level of security; the first security level, Profile 1, was targeted against only software attacks and while Profile 2, was targeted against both software and hardware attacks. ARM TrustZone [3] TEE is an implementation of the TEE standard.

TEE retains its own hardware unique keys, stored in fuses. These keys are referred as "endorsement keys" or "provisioned secrets" which are embedded directly into the chip during manufacturing. The keys can be used to derive and secure other keys which can be used to uniquely identify the device.

#### 2.1.4.4 Trusted Platform Module

Trusted Platform Module (TPM) is also known as ISO/IEC 11889 standard. It was specified by the Trusted Computing Group (TCG) and then it was standardized by International Organization for Standardization (ISO) and International Electrotechnical Commission (IEC) in 2009 [53] as ISO/IEC 11889, the current version is TPM 2.0[44].

TPM is a dedicated microprocessor designed to secure hardware through integrated cryptographic keys. TPM is usually used in PCs, laptops, mobile phones, and network equipment. Currently TPM is used by nearly all PC and notebook manufacturers.

The TPM allows for hardware-based cryptographic operations. Security functions can leverage the TPM for random number generation; the use of symmetric, asymmetric, and hashing algorithms; and secure storage of cryptographic keys and message digests. It ensures that no unintended users gain access to secret data by either stealing a device or via a software attack or brute force attack.

## 2.1.5 Security validations standards

For applications or devices that include cryptography, U.S. and Canadian federal government agencies are required to use a cryptographic products that has been FIPS 140 (Federal Information Processing Standards) validated or Common Criteria validated. Most Common Criteria protection profiles rely on FIPS validation for cryptographic security.

#### 2.1.5.1 FIPS 140-2

FIPS 140 series are U.S. government computer security standards that specify requirements for cryptography modules. Within the FIPS 140-2 (or 140-1) validations, there are four possible security levels for which a product may receive validation:

- 1. Security Level 1 provides the lowest level of security. It specifies basic security requirements for a cryptographic module.

- 2. Security Level 2 improves the physical security of a Level 1 cryptographic module by adding the requirement for tamper evident coatings or seals, or for pick-resistant locks.

- 3. Security Level 3 requires enhanced physical security, attempting to prevent the intruder from gaining access to critical security parameters held within the module.

- 4. Security Level 4 makes the physical security requirements more stringent, and requires robustness against environmental attacks.

The security level of a particular device does not last forever. It is possible that a low cost attack will be found in the future when the attack tools become cheaper or available at second-hand.

FIPS 140 imposes requirements in different areas such as: cryptographic module specification, cryptographic module ports and interfaces, roles/services and authentication, finite state model, physical security, operational environment, cryptographic key management, electromagnetic interference/compatibility, self-tests, design assurance, and mitigation of other attacks. FIPS 140 standards define many tests that may be used to evaluate certain features in a system. For example, a particular part of FIPS 140-1 standard deals with statistical randomness tests such as: the monobit test, the pokers test, the runs test, and the long run test.

FIPS 140-3 [37] is a new version of the standard which is currently under development. In the first draft version of the FIPS 140-3 standard, NIST introduced a new software security section, one additional level of assurance (Level 5) and new Simple Power Analysis (SPA) and Differential Power Analysis (DPA) requirements.

Although the FIPS standards are developed by the US federal government, they are widely used as standards to specify the security requirements. Many companies acquire FIPS validation to comply with international standards. The FIPS validation will ensure that the proposed product or services meet the requirements standardized by a reputable organization and will make them competitive and open new markets.

#### 2.1.5.2 Common criteria

The Common Criteria (CC) for Information Technology Security Evaluation is an international standard for computer security certification. The current version is 3.1 release 5. The computer system users, vendors, and testing laboratories participate in using Common Criteria by different ways. Computer system users can specify their security functional and assurance requirements, vendors can then implement and/or make claims about the security attributes of their products and testing laboratories can evaluate the products to determine if they actually meet the claims. Common Criteria evaluations are performed on computer security products and systems, these systems may be software and/or hardware products.

The evaluation serves to validate claims made about the system. The evaluation must verify the system's security features. The claims are identified in some documents that are used as a part of the certification process. The protection profile (PP) is the document that is created by a user and provides an implementation independent specification of information assurance security requirements. Another document, that identifies the security properties of the system, is security target (ST) document. The CC 3.1 defines it as an implementation-specific statement of security needs for a specific identified system so it is provided by the vendor of the product. The individual security functions are specified in security functional requirements (SFRs) document.

The evaluation process also tries to establish the level of confidence through two quality assurance processes: security assurance requirements (SARs), and evaluation assurance level (EAL). SARs describe the measures taken during development and evaluation of the product to assure compliance with the claimed security functionality. The requirements may vary from one evaluation to the next. EAL has numerical rating that describes the depth of an evaluation. The increasing assurance levels reflect added assurance requirements that must be met to achieve Common Criteria certification. The intent of the higher levels is to provide higher confidence that the system's principal security features are reliably implemented. The EAL level does not measure the security of the system itself, it simply states at what level the system was tested.

The objectives of the Common Criteria agreement are to ensure that evaluations of IT products are performed to consistent standards and to improve the availability of security-enhanced IT products. It continuously improves, through the different versions, the efficiency and cost-effectiveness of the evaluation and certification/validation process for IT products.

# 2.2 Digital Hardware Circuits

## 2.2.1 Digital hardware circuits design approaches

In general, digital hardware circuits designs are divided into two basic approaches: the general-purpose approach, the special purpose approach. The general-purpose approach relies on hardware circuits like general-purpose processors or microprocessors that provide a fixed set of functionality (i.e. the instruction set of a microprocessor). On the other hand, the special-purpose approach involves design for a specific application. Specialised hardware circuits or application-specific instruction set processors are two hardware architectures that are used to design circuits in this approach.

The instruction set for general-purpose processor (GPP) must be general enough to support general applications. The general-purpose processor compiler should offer compilation for all programs. The main purpose of using general-purpose processors is getting the highest possible flexibility, they are designed to execute multiple applications and perform multiple tasks. So it is expensive especially for small devices that are designed to perform a specific task.

On the contrary, specialised hardware circuits provide the best performance, area, and power consumption but on the other side, they provide poor or no flexibility and extensibility. Any required modification needs the whole design and manufacturing process to start again, so the time-to-market is relatively high compared to GPP and ASIP-based designs.

In between of GPPs and specialised hardware circuits, there are application-specific instruction set processors. An application-specific instruction set processor (ASIP) is a processor which is customized for a certain application. It combines the benefits of the flexibility, and programmability as close to the general-purpose CPUs or the general-purpose processors (GPP) and the low silicon cost, low power consumption, and the performance as close to specialised circuits.

The hardware of ASIP and the instruction-set are designed together for one special application. ASIP designer thinks about the application and cost first. At the same time, ASIPs have reasonable flexibility. ASIP instruction-set is specifically designed to accelerate the most used functions for an application. Some operations that needs an extensive

| Feature                 | General-purpose  | Application-         | specialised hard- |

|-------------------------|------------------|----------------------|-------------------|

|                         |                  | specific             | ware              |

|                         | processor        | instruction-set pro- | circuits          |

|                         |                  | cessor               |                   |

| Flexibility             | Excellent        | Good                 | Poor              |

| Power consumption       | Relatively large | Medium               | Small             |

| Silicon Area            | Relatively high  | Low                  | Lowest            |

| Performance             | Depends on       | High                 | Highest           |

|                         | the application  |                      |                   |

|                         | (mostly Low)     |                      |                   |

| Energy Efficiency/speed | Low              | High                 | Highest           |

| Design Effort           | System level     | More on system       | Hardware          |

|                         |                  | level                |                   |

| Hardware Design         | Small            | Large                | Very large        |

| Software Design         | Large            | Large                | None              |

| Time-to-market          | Lowest           | Relatively low       | High              |

| Cost                    | Mainly on Soft-  | System-on-chip       | Volume sensitive  |

|                         | ware             | (SOC), Hw/Sw         |                   |

| Usage                   | Very wide        | Wide                 | Limited           |

Table 2.1: The difference between the three hardware architectures

computation capabilities, as cryptographic functions, may need a dedicated hardware to perform it. ASIP allows adding dedicated hardware circuits which are accessed by special instructions. ASIP architecture is designed and optimized to implement the assembly instruction set with minimum hardware cost. The goal of an ASIP design is to reach high performance over silicon, over power consumption, as well over the design cost with reasonable level of flexibility. Table 2.1 summarizes the differences between the three digital hardware architectures.

# Chapter 3

# **EPC RFID Systems**

Radio-frequency identification (RFID) is a technology which the physical devices have an automated identification using Radio-frequency signals. In the last years, the RFID technology has found its way into our daily life such as supply chain management, home automation, e-cards, auto-mobiles, identification systems, ubiquitous and pervasive computing. The total RFID market was \$10.1 billion in 2015 and it was expected to rise to \$13.2 billion in 2020 [23]. Electronic Product Code (EPC) standards define the specifications of the tag and its communication protocols set by EPCglobal group. Different classes and generations were proposed, the last version is Class 1, Generation 2, Version 2.1 [40]. This chapter presents background information on Electronics Product Code (EPC) tags presented.

# 3.1 **RFID** standards

There are several RFID standards including ISO 18000 and EPCglobal standards. The standards are used to define the operations and the communication protocols between the RFID system components. These standards enable manufacturers to make products for large scale. It also enables products from different manufacturers to operate or work together.

There are two main organizations that make standards for RFID systems:

• ISO, International Standards Organization

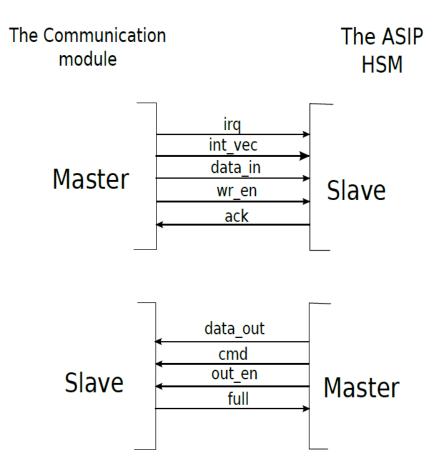

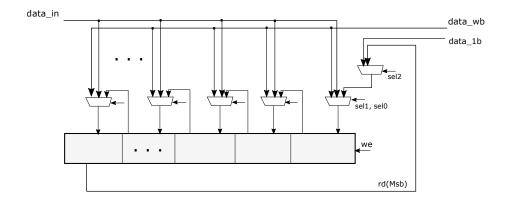

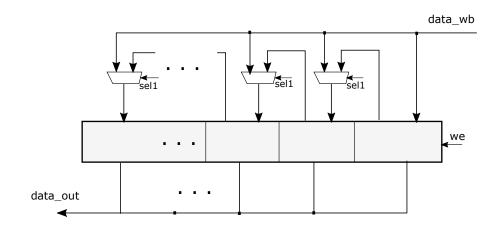

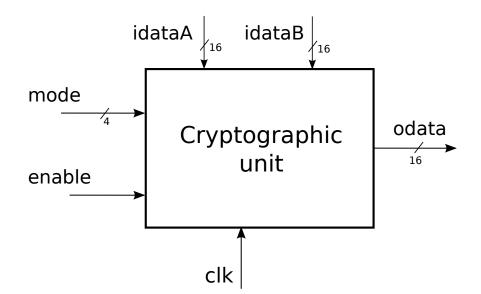

• EPCglobal, Electronics Product Code Global Incorporated