FACULTY OF INFORMATION TECHNOLOGY AND ELECTRICAL ENGINEERING DEGREE PROGRAMME IN ELECTRONICS AND COMMUNICATIONS ENGINEERING

# **MASTER'S THESIS**

# C++ CODING PRINCIPLES FOR HIGH-LEVEL SYNTHESIS

Author

Heikki Vuopio

Supervisor

Jukka Lahti

Second Examiner

Jussi Jansson

Technical Advisor

Teemu Vikamaa

June 2021

**Vuopio H. (2021) C++ CODING PRINCIPLES FOR HIGH-LEVEL SYNTHESIS.** University of Oulu, Faculty of Information Technology and Electrical Engineering, Degree Programme in Electronics and Communications Engineering. Master's Thesis, 63p.

## ABSTRACT

High-level synthesis (HLS) raises the level of abstraction on digital integrated circuit design from traditional register transfer level (RTL) to behavioural system description level. This methodology offers great advantages such as increased designer productivity. The adoption of HLS, however, has been slowed down by the RTL code mistakenly generated with HLS which potentially results in poor quality compared to the traditional hand-written RTL.

This thesis aims to solve this problem by finding the best programming practices for hardware-oriented C++. A digital downconverter and decimator are designed and implemented with Catapult HLS as a case study, where different coding practises are experimented with, and the best ones are generalized and presented. The quality of results of this case study is compared against a hand-written RTL design of the same intellectual property created by other designers. A few examples are presented as well demonstrating that small changes in the source code might have a major effect on the generated RTL.

It is found that understanding how the HLS tool analyses the source code and executes operations in parallel greatly helps to improve the quality of results in the generated hardware. Also, by having a clear target architecture it is a simple task to verify the hardware in Catapult analysis views such as schedule and schematic view. By optimizing the source code, it is possible to generate similar quality hardware compared to traditional RTL flow. In this case, the area of the HLS design is about 19 % smaller than the RTL design with the same throughput, slightly lower latency, and roughly the same power consumption.

Key words: high-level synthesis, HLS, digital IC design, hardware-oriented C++, Catapult HLS.

**Vuopio H. (2021) C++ OHJELMOINTIKÄYTÄNNÖT KORKEAN TASON SYNTEESIIN.** Oulun yliopisto, tieto- ja sähkötekniikan tiedekunta, elektroniikan ja tietoliikennetekniikan tutkinto-ohjelma. Diplomityö, 63p.

# TIIVISTELMÄ

Korkean tason synteesi (HLS) nostaa digitaalisten integroitujen piirien suunnittelun abstraktiotason perinteiseltä rekisterinsiirtotasolta (RTL) systeemikuvaustasolle. Tämä metodologia tuo suuria etuja, kuten suunnittelijan korkeampi tuotteliaisuus. HLS:n laajempaa käyttöönottoa on kuitenkin hidastanut erheellisesti HLS:llä generoitu RTL-koodi, josta usein seuraa heikohko laatu käsin kirjoitettuun RTL-koodiin verrattuna.

Tämän tutkimuksen tavoite on ratkaista tämä ongelma löytämällä parhaat ohjelmointikäytännöt korkean tason synteesiin suunnattuun C++-ohjelmointiin. Digitaalinen alasmuunnin ja desimaattori suunnitellaan ja implementoidaan käyttäen Catapult HLS-työkalua. Eri ohjelmointikäytäntöjä testataan ja parhaat yleistetään ja esitellään, minkä jälkeen tulosten laatua verrataan samaan lohkoon, jonka on ohjelmoinut eri suunnittelijat rekisterinsiirtotasolla. Tutkimus sisältää myös koodiesimerkkejä siitä, miten pienet muutokset lähdekoodissa voivat vaikuttaa merkittävästi lopputulokseen.

Tutkimuksessa todetaan, että synteesityökalun toiminnan ymmärtäminen on kriittistä hyvien tulosten saavuttamisen kannalta. Suunnittelijalla tulisi olla selvä tavoitearkkitehtuuri generoitavasta RTL-koodista, jolloin sen varmentaminen synteesin jälkeen olisi helppoa Catapultin analyysinäkymissä. Optimoimalla lähdekoodia generoidun RTL-koodin tulosten laatu saadaan samaksi kuin käsin kirjoitetun RTLkoodin. Tässä tapauksessa generoidun RTL-koodin pinta-ala on 19 % pienempi kuin käsin kirjoitetun mallin samalla siirtonopeudella. Latenssi on hieman pienempi ja tehonkulutus samaa suuruusluokkaa.

Avainsanat: korkean tason synteesi, digitaalisuunnittelu, laitteistosuuntautunut C++, Catapult HLS.

# **TABLE OF CONTENTS**

| ABS   | FRAC                 | Γ                                       |  |

|-------|----------------------|-----------------------------------------|--|

| TIIVI | STEL                 | MÄ                                      |  |

| TABI  | LE OF                | CONTENTS                                |  |

| FORE  | EWOF                 | D                                       |  |

| LIST  | OF A                 | BBREVIATIONS AND SYMBOLS                |  |

| 1     | INTR                 | ODUCTION                                |  |

| 2     | HIGH-LEVEL SYNTHESIS |                                         |  |

|       | 2.1                  | History                                 |  |

|       | 2.2                  | Research on previous HLS use9           |  |

|       | 2.3                  | Benefits of HLS 10                      |  |

|       |                      | 2.3.1 Productivity                      |  |

|       |                      | 2.3.2 Bug freedom 11                    |  |

|       |                      | 2.3.3 Verification                      |  |

|       |                      | 2.3.4 Scalability 12                    |  |

|       |                      | 2.3.5 Source code readability           |  |

|       |                      | 2.3.6 Design space exploration12        |  |

|       |                      | 2.3.7 Easy source code modifications13  |  |

|       | 2.4                  | Challenges of HLS 13                    |  |

|       |                      | 2.4.1 Tool specificity                  |  |

|       |                      | 2.4.2 Quality of results                |  |

| 3     | C++ .                | AS CATAPULT INPUT LANGUAGE16            |  |

|       | 3.1                  | Overview of C++                         |  |

|       | 3.2                  | Object oriented programming16           |  |

|       | 3.3                  | HLS restrictions and additions to C++17 |  |

|       |                      | 3.3.1 AC datatypes                      |  |

|       |                      | 3.3.2 ac_channel 21                     |  |

|       |                      | 3.3.2.1 Overview                        |  |

|       |                      | 3.3.2.2 Read and write                  |  |

|       |                      | 3.3.2.3 Non-blocking read and write     |  |

|       |                      | 3.3.2.4 Arrays and structs 22           |  |

|       |                      | 3.3.3 File structure                    |  |

|       |                      | 3.3.4 Leaf blocks and top level         |  |

|       | 3.4 Templatizing     |                                         |  |

| 4     | CATAPULT HLS         |                                         |  |

|       | 4.1                  | Overview                                |  |

|       | 4.2                  | Input languages                         |  |

|       | 4.3                  | HLS C++ synthesis                       |  |

|       | 4.4                  | Design flow                             |  |

|       |                      | 4.4.1 Hierarchy                         |  |

|       |                      | 4.4.2 Libraries                         |  |

|       |                      | 4.4.3 Mapping                           |  |

|   |            | 4.4.4 Architecture                    |    |

|---|------------|---------------------------------------|----|

|   |            | 4.4.5 Resources                       |    |

|   |            | 4.4.6 Schedule                        |    |

|   |            | 4.4.7 RTL                             |    |

|   | 4.5        | Top-down / Bottom-up                  |    |

|   | 4.6        | CCORE                                 |    |

| 5 | COD        | DING PRINCIPLES                       |    |

|   | 5.1        | Loops                                 |    |

|   | 5.2        | Conditions                            |    |

|   | 5.3        | IO and memory accesses                | 44 |

|   |            | 5.3.1 Pass by value                   |    |

|   |            | 5.3.2 Pass by reference               |    |

|   |            | 5.3.3 Memory access                   |    |

|   | 5.4        | In context variable declaration       |    |

|   | 5.5        | Multidimensional array access example |    |

|   | 5.6        | Summary of coding principles          |    |

| 6 | CASE STUDY |                                       |    |

|   | 6.1        | Requirements                          |    |

|   | 6.2        | Catapult usage                        |    |

|   | 6.3        | Results                               |    |

|   | 6.4        | Analysis                              |    |

| 7 | DISC       | CUSSION                               |    |

| 8 |            | /MARY                                 |    |

| 9 |            | FERENCES                              | _  |

## FOREWORD

The purpose of this thesis was to find the best practises for HLS-oriented C++ programming. The thesis work was done at Nokia Oulu from late 2020 to summer 2021.

I would like to thank Nokia SoC organization for the opportunity to do this thesis. Special thanks to the thesis supervisor Jukka Lahti for guidance with the thesis work, Teemu Vikamaa for technical advising, and Esa-Matti Turtinen and Richard Langridge from Siemens EDA for the support in tool-related matters and the guidance on the research subject itself.

Finally, I want to thank my family, friends, and my girlfriend Emma for all the support provided during the thesis work and the recent years of studying.

Oulu, June 30, 2021

Heikki Vuopio

# LIST OF ABBREVIATIONS AND SYMBOLS

| AC       | Algorithmic C                                               |

|----------|-------------------------------------------------------------|

| ASIC     | Application Specific Integrated Circuit                     |

| CDFG     | Control Data Flow Graph                                     |

| CCORE    | Catapult C Optimized Reusable Entity                        |

| DCT      | Discrete Cosine Transform                                   |

| DFE      | Digital Front-End                                           |

| DFG      | Data Flow Graph                                             |

| DL       | Downlink                                                    |

| DSE      | Design Space Exploration                                    |

| DSP      | Digital Signal Processing                                   |

| EDA      | Electronic Design Automation                                |

| FIFO     | First-In First-Out                                          |

| FIR      | Finite Impulse Response                                     |

| FPGA     | Field Programmable Gate Array                               |

| FSM      | Finite State Machine                                        |

| GCC      | GNU Compiler Collection                                     |

| GUI      | Graphical User Interface                                    |

| HBF      | Half Band Filter                                            |

| HEVC     | High-Efficiency Video Coding                                |

| HLL      | High-Level Language                                         |

| HLS      | High-Level Synthesis                                        |

| HLV      | High-Level Verification                                     |

| HW       | Hardware                                                    |

| IC       | Integrated Circuit                                          |

| II       | Initiation Interval                                         |

| IO       | Input/Output                                                |

| IP       | Intellectual Property                                       |

| KPN      | Kahn Process Network                                        |

| LSB      | Least Significant Bit                                       |

| MatchLib | Modular Approach to Circuits and Hardware Library           |

| MSB      | Most Significant Bit                                        |

| NCO      | Numerically Controlled Oscillator                           |

| OOP      | Object-Oriented Programming                                 |

| PSD      | Polyphase Sub-band Decimation                               |

| QoR      | Quality of Results                                          |

| RAM      | Random Access Memory                                        |

| ROM      | Read-Only Memory                                            |

| RTL      | Register Transfer Level                                     |

| SoC      | System on Chip                                              |

| SW       | Software                                                    |

| TCL      | Tool Command Language                                       |

| UL       | Uplink                                                      |

| UVM      | Universal Verification Methodology                          |

| VHDL     | Very high-speed integrated circuit Hardware Design Language |

|          |                                                             |

## **1** INTRODUCTION

High-level synthesis [1] (HLS) is a methodology that raises the abstraction level in digital integrated circuit (IC) design. HLS tool takes the untimed or loosely timed high-level source code, technology library, and a set of design constraints as input and outputs the clock accurate register transfer level (RTL) model of the design that is traditionally written by hand.

The first HLS tools were introduced in the 1980s, but only in recent years, HLS has been adopted by a wider audience due to tool development and growing design complexity in digital IC projects [1]. The promises of HLS are great since the tool developers promise similar, or better quality of results (QoR) with greatly decreased design and verification effort and true code reusability across projects via technology-independent source code.

A challenge with HLS is that the synthesis tool abstracts away some details of the generated RTL and the input source code is written in a high-level language that only describes the behaviour of the design. Because of this, it might not be completely clear for the designer how the tool interprets the source code and generates RTL [2]. This may lead to suboptimal quality hardware with the designer having no clue how to improve it since the hardware-oriented programming principles differ from traditional software ones.

In this thesis, the coding style for HLS is being experimented with to find best practices for hardware-oriented C++ and some examples are presented. A digital front end (DFE) IP-block describing a signal process algorithm will be implemented using Siemens EDA Catapult HLS tool and C++ as input language. The IP-block itself has been originally designed in RTL methodology by other designers and this design is used as a reference for evaluating the results of HLS design.

This thesis is done at Nokia in Oulu. Active support from Siemens EDA is applied through the entire design process to guide with both coding style and the HLS tool usage to avoid mistakes and speed up the HLS learning curve since the writer has practically no previous experience in designing hardware in HLS methodology. Some previous trials and studies on HLS have been made within Nokia with reasonable results [3]. These studies have been focusing on different areas and challenges in HLS flow, like HLS-extracted RTL's backend flow compatibility [3] or HLS in IP-based SoC development [4]. Each of these studies includes a case study with comparisons between HLS and RTL designs and the QoR is reported similarly to each other with a little variance.

Chapters 2, 3, and 4 present an introduction to HLS, C++, and Siemens EDA Catapult HLS tool more specifically. Chapter 5 contains hardware-oriented coding principles for C++ and best practices with examples. Chapter 6 presents a case study example exploiting these coding practises and a comparison of results against the handwritten RTL model of the design in terms of QoR and designer productivity. Chapters 7 and 8 contain discussion and summary to provide conclusions and closure to the thesis.

## **2** HIGH-LEVEL SYNTHESIS

High-level synthesis is a system-level abstraction methodology to generate register transfer level code directly for targeted ASIC or FPGA technology from behavioural algorithmic source code using a specific electronic design automation (EDA) tool. Traditionally digital IC's are designed on a register transfer level of abstraction using hardware design languages (HDL) such as VHDL or Verilog. Writing RTL code, however, is time-consuming and prone to bugs. HLS aims to solve these problems by raising the abstraction level from RTL to system-level C/C++ description of the desired algorithm, of which the RTL code can be generated with the HLS tool by an HW designer guiding the process. [7]

## 2.1 History

HLS has had three generations, the first of which originates from the 1980s. The first generation was a commercial failure due to specific input language, the lack of need for such technology, poor quality of results, and domain specialization but it offered vital research for the following generations. [1]

In the second generation, from the mid-1990s to early 2000s, major EDA tool vendors offered HLS solutions that made clear progress from the first generation but failed as well due to overmarketing, narrow applications, and various other reasons specified in [1].

The third generation began in the early 2000s. An actual breakthrough was not made but success stories were heard. Tool vendors promised similar Quality of Results (QoR) to handwritten RTL and although most of the papers and case studies reported poor QoR, the designer productivity was undeniably increased significantly. The third-generation HLS tools accept common input languages such as C to ease the adoption of the HLS tools. The vendors identified a suitable market and therefore, HLS tools focused on data-driven DSP applications as they are more suitable to those than complex control applications. [1]

The ever-increasing complexity of ASIC and FPGA development increases the need to raise designer productivity. In the past years, HLS has been used and experimented with on a variety of applications and tools have been greatly developed. There is great potential in the technology but still, in recent years it has been reported that some synthesis tools may seem like black boxes to designers and it might be unclear what happens in the synthesis. [2]

HLS tools have been even further developed in recent years. Today, the QoR gap is nearly closed and HLS is being adopted by a wider variety of users. Open source MatchLib library by NVidia is also enabling a wider variety of applications for HLS as well as encapsulating some optimization details with preoptimized components that are commonly used in HW design [8].

## 2.2 Research on previous HLS use

There are various case studies about HLS being applied to different designs. They have been analysed from different points of view for example some compare HLS design QoR against hand-written RTL QoR and some analyse software developer's ability to adopt hardware design with high-level synthesis.

Reference [9] compiles 46 different case studies from 2010 to 2016 with acceptable reporting numbers comparing QoR and designer productivity. The main conclusion is that QoR with HLS remains marginally lower than hand-written RTL designs, but designer productivity is highly increased, the development cycle is shorter, and the lines of code number is lower using HLS than traditional RTL design flow. With some exceptions, of course.

When comparing QoR in terms of performance (depending on the application) and resource usage of HLS and RTL designs it seems that results are very similar although RTL slightly outperforms HLS. The big picture indeed suggests that the QoR gap between HLS and RTL would be closing and modern HLS tools generate RTL code with similar quality as handwritten, when used properly. [9]

Designer productivity is compared in terms of development time and lines of code. 25 case studies reported development time. In 72 % of the cases, the development time in HLS is 50 % or less compared to development time in RTL design. Only three of those studies report a longer development time for HLS than RTL. All three come from the same work [10] and the reason as they explain it is the learning of the HLS tool and necessary source code modifications to meet the performance requirements. [9]

35 of the 46 case studies reported lines of code for both RTL and HLS. In 75 % of the reported cases, the number is lower for HLS than RTL. In small designs the nonbehavioural part of the source code in HLS designs becomes dominant and it favours RTL design in this sense. In all the cases where this number was reported larger in HLS design, the total lines of code is less than 250. According to these numbers, it seems indeed undeniably true that HLS remarkably increases designer productivity. [9]

The development time ratio between HLS and RTL projects was plotted as a function of absolute development time to figure out if HLS benefits are upscaling in large-scale designs. Interestingly they found no such correlation. The ratio development time in both large and small-scale applications remained approximately the same [9]. One could imagine that HLS benefits from large-scale applications due to code reusability, verification effectiveness, and scalability of code, especially when the object-oriented programming (OOP) paradigm is used. However, the ratio of lines of code seemed to favour HLS more and more as the design size increased [9].

The designer experience in RTL and HLS is neglected in the case study compilation [9]. In such trials where HLS and RTL are being compared the setting commonly is that it is either software developer or hardware designer that creates the designs compared. In the case of experienced hardware designers, RTL design is familiar and it is easy to create high-quality RTL, but in terms of HLS, the lack of knowledge about the input language and HLS tool might be the limiting factor. Software developers, on the other hand, most probably have no problem describing the algorithm in given HLL but translating that algorithm to hardware with the synthesis tool might lead to poor results if no specific RTL architecture is targeted.

There is also a case study on the compilation paper to verify the results of the quantitative research. In this case study, six people with moderate SW development experience and little experience in HW design implement a DCT algorithm in HEVC encoder with both HLS and RTL methodologies. The results suggest that HLS design flow is easier to adopt than traditional RTL flow. This point of view is not too interesting for this thesis though, because the aim is to produce production-ready RTL with the highest possible QoR with increased design productivity. [9]

## 2.3 Benefits of HLS

When adopted, HLS would augment traditional RTL design flow, so pros and cons should be in reference between these two methodologies. More specifically in this thesis, the target is to produce production-ready high-quality RTL code for ASIC technology with increased productivity. The benefits will be mostly discussed from this point of view and not for example HLS vs RTL adoptability for newcomers in HW design.

#### 2.3.1 Productivity

HLS promises to increase designer productivity [10]. This is one of the biggest and most remarkable factors in HLS adoption as modern digital IC projects take large teams and up to several years of development time before a commercial product is ready.

HLS takes hardware design to a higher level of abstraction allowing the designer to focus on the behavioural model of the desired hardware. Writing higher-level code simply means less code is needed to describe an algorithm which again means the code can be written faster. Of course, writing the code is not the whole process but a big part of it. Higher-level code is usually more intuitive and therefore, faster to write and easier to understand.

HLS abstracts away some details from the designer like finite state machine creation and interface handshaking. These details in RTL design must be written to the source code in each place they are desired, basically leading to code duplication. HLS fully automates some of these features, and if not, the designer still has the power to make modifications in the synthesis tool to control the generated RTL code. This is arguably easier and more intuitive and thus increasing productivity.

## 2.3.2 Bug freedom

As HLS design flow hides some details from the designer and less source code is required to implement the desired functionality the source code is less prone to bugs. As long as the source code compiles and does not conflict with the HLS-friendly coding style, the tool is supposed to generate bugless RTL with identical functionality to the source code.

Algorithmic bugs in the source code functionality are also easier to identify and fix in HLL than RTL. Code reusability allowed by HLS and OOP ensures that bugs are not duplicated in the code. Reusing a buggy class multiple times in the design exposes the bugs more effectively and they only need to be fixed once, unlike in duplicated code. [10]

## 2.3.3 Verification

Verification in traditional RTL flow can take the majority of the time before the product is ready for publishing for the market. Complex digital IC has so much functionality it may take thousands of test cases to reach near 100 % RTL coverage and functional coverage.

In traditional RTL design flow verification is commonly done with simulations. In large RTL designs, this can be very slow as running a single test case can take from minutes to hours depending on the design and test case complexity. Long regression runs might take up to weeks to finish. RTL simulation can only be started when a functional version of the design is completed.

HLS allows the testbench to be created in the same HLL as the design is originally written in. For example, C++ simulations run over a hundred times faster than RTL simulations [10] exposing bugs much faster. The behavioural model of the design can be verified when the source code is written, and no RTL is needed for this. Therefore, the verification process can be started earlier, and the bugs can be fixed faster. Once the RTL is generated, high coverage test cases can be copied to the UVM test environment and run for RTL to quickly achieve high RTL coverage. This way, shorter regressions can be run for RTL and individual UVM test cases can be created to fill the coverage gaps. HLS tools have built-in verification tools, such as Siemens EDA Catapult's SCverify. SCverify is a hardware designer smoke test environment that automatically creates a testbench and verifies the equivalence of the outputs of C++ source code and generated RTL simulations. There are still some structures in the source code that SCverify has trouble with and traditional RTL simulations are needed to verify the correct functioning of such structures, but there is usually a workaround to verify the functionality of such structures in SCverify as well.

### 2.3.4 Scalability

Using OOP in HLS design allows flexible code reusability. Using templatized classes allows modules of similar functionality to be reused with different kinds of interfaces or data types, for example.

Small structures commonly used in RTL architecture like different buffers can be written once and used everywhere. Larger entities like whole IP can also be simply rescaled for different applications. All of this reduces code duplication and increases productivity as designers can focus on creating new instead of modifying old code.

HLS tool also allows easy adjustability of clock frequency and target technology. The same source code can be used when adjusting clock frequency and the HLS tool optimizes the data paths so that the maximum amount of operations is fit into each clock cycle with given constraints. The pieces of timing information in Catapult are only estimates though since the HLS tool has no information about the gate-level structure that is eventually done with RTL synthesis tools such as Design Compiler.

HLS source code is technology-independent [10]. This enables real IP reusability over projects using different technology libraries. Technology retargeting from ASIC to FPGA and vice versa though might require some changes to the source code as the available resources are different.

#### 2.3.5 Source code readability

Easy code readability should always be a goal when writing it. By its low-level nature, RTL code is difficult to read for any other than an experienced HW designer. RTL must be very descriptive and detailed for the compiler and RTL synthesis tool to understand it and create the desired HW.

High-level code is much more intuitive and readable by its nature. Very common programming languages like C++ also help other than HW designers to understand and comment on the functionality of the design. Files describing the same functionality in HLL as RTL are commonly smaller making them easier to read and understand large entities in them. Even though HLS coding style might sometimes even conflict with common coding in SW development, source code readability is also one of the big advantages HLS has to offer.

## 2.3.6 Design space exploration

DSE or architectural exploration is one of the big advantages in HLS compared to traditional RTL. Whereas in RTL design flow usually the algorithm is defined first, then the desired architecture what is needed in the hardware and finally after having a specific target architecture it is being committed to and the actual RTL-coding work can start. At this point, it should be relatively clear what the outcome should look like. In HLS, as the source code itself is high-level code describing the algorithm and the RTL outcome is defined by that and the tool

directives, making changes to the architecture can be done in the late phases of the design flow. Making minor changes to the source code or fine-tuning the tool directives to explore different architectural options and finding the optimal one for the application is called design space exploration or architectural exploration.

Loop handling is one of the features in HLS to exploit parallelism in the C-code. Naturally, C++ does not support parallelism, but the code is executed sequentially which means that lines of code are executed one after another. This applies to loop iterations as well, meaning that a loop iteration is not started before the previous one is finished. In HW this is not always desired as it leads to poor data throughput in the generated RTL. HLS tools allow loops to be unrolled or pipelined. Unrolling a loop means that the loop iterations are executed in parallel, and it can be done for the entire loop or partially [11]. Pipelining a loop means that the next loop iteration is started before the previous one is finished [11]. Loop handling is just one example of design space exploration.

Not all configurations of directives result in optimal RTL. Given a specific set of area and timing requirements, there might be more than one optimal architecture but for sure there are many suboptimal ones. If an architecture has the lowest area possible for a specific latency requirement, it is called Pareto-optimal [12]. Finding the Pareto-optimal architectures can be a complex task especially when targeting an FPGA technology having a specific set of resources available.

DSE is commonly done manually, but research on automatic DSE and the analysis of the results have been made to find the Pareto-optimal results in HLS designs [13]. Targeting ASIC technology, the Pareto-optimal solutions are quite straightforward to find but that is not the case in FPGA [14].

#### 2.3.7 Easy source code modifications

Since the source code is written in a higher level of abstraction in HLS, it allows the designer to make changes to the source code to try different architectural options in the resulted RTL. This is game-changing as in traditional RTL design flow the designer must specify the details of the target architecture before writing the RTL code. Once the architecture is decided and agreed upon the designer must commit to it even if they found out later that there could be a better solution. Writing RTL code targeting specific architecture, change of plan could mean that all the work that has been done was useless. Changing the architecture in the late phase could affect neighbouring IP and other designers as well. HLS allows making changes and experimenting with different architectures even in late phases due to high-level code flexibility and code reusability [10].

## 2.4 Challenges of HLS

Despite the great promises, there are a couple of main challenges that have slowed down the adoption of HLS.

## 2.4.1 Tool specificity

By this day there are over twenty high-level synthesis tools, both academic and industrial, most of which use different input language from each other [9]. The most common input language is C or its subset.

Most high-level languages are natively not designed for hardware description and thus poor for that purpose. The challenges of C-like languages as an HLS tool input language have been discussed in [15], but most of the problems described in the paper have been solved by the day. The paper covers twelve different subsets of C used in HLS for different tools and discusses the strengths and weaknesses of each one from the point of view of hardware description. Even though the paper claims that the main reason for C-like languages to be used in HLS is its familiarity, C/SystemC/C++ has become an industry-standard in HLS.

Having such a high number of HLS tools can be confusing for the users. Before getting to design anything, they must commit to a specific tool and possibly learn a new programming language or at least relearn how to write it as HLS sets specific restrictions to most common HLLs.

The common problems in generating hardware from HLL code are known: specifying parallel algorithms, specifying timing, and having proper data types for hardware. As each of the tools solves these problems their way it seems unclear for the designer how the tools work. For example, there are multiple different arbitrary-precision data type libraries for C used by different HLS tools. Which one is the best? Which one should be used?

Comparison between different tools is also difficult. As they use different input languages it is difficult to directly compare the tools' different properties such as synthesis run-times or "Which tool generates the highest quality hardware?". Committing to a specific product, adopting, and learning it is a relatively big risk to potential customers.

The lack of unified methodology for HLS limits both hardware designers' desire and capability and the tool developers' ability to create the highest quality tools. Only with standardized methods can designers learn to create consistently high-quality hardware and the tool developers could focus on the designers' needs instead of creating another tool that no one but the developers themselves can efficiently use [2]. Surely, sometimes it depends on the application which tool and input language are the optimal ones, but not twenty languages are needed. A lot of research has been made on the topic during the past forty years and agreeing upon some standards could greatly speed up both tool development and adoption for wider use.

## 2.4.2 Quality of results

The main challenge slowing down the adoption of HLS is that the quality of results (QoR) has tended to stay significantly lower compared to handwritten RTL. Significantly doesn't need to be very much in this context since the companies producing ASICs are usually willing to invest a lot of time and money to achieve the optimal results in the area, timing, and power consumption, and anything less than that is not acceptable. However, the QoR gap between HLS generated and handwritten RTL-code has been closing in recent years as the HLS tools have been further developed.

Poor QoR of HLS generated hardware is often related to designers trying to blindly translate software algorithms into hardware. HLLs, like C, are often sequential by nature, and the optimal hardware usually exploits high parallelism. The designer must aim to the optimal RTL architecture in the source code writing phase or the outcome RTL will not be optimal. This must be considered to avoid poor results or even failure in the resulted RTL. Having clear target architecture and an idea of how to describe it in HLL can result in comparable QoR with HLS and handwritten RTL [16].

HLS tools often also fail to capture the programmer's intention, leading to poor QoR. This is a matter of the designer and the tool interpreting the source code differently. Describing algorithms on a system-level C/C++ can be relatively simple, but when targeting ASIC or

FPGA the designer must have an idea of what kind of resources are available and how does the HLS tool uses them.

## **3** C++ AS CATAPULT INPUT LANGUAGE

$C^{++}$  is one of the possible input languages for HLS. More specifically for Catapult HLS tool that will be used in the case study in chapter 6. This chapter introduces  $C^{++}$  as the input language for Catapult HLS tool. The elements of this chapter will be used in the code examples in chapter 5 as well.

#### 3.1 Overview of C++

C++ is a multi-function programming language. C++ is an extension of C as it adds classes and object-oriented paradigm into C. C++ is compiled, strongly typed unsafe language. C++ requires the programmer to know what he or she is doing but allows a lot of control while doing that. [17]

C++ was created by Bjarne Stroustrup. It was published in 1985 with *The* C++ *Programming Language* book [18] as Stroustrup's reference to the language. In 1998 C++ was standardized as C++ ISO/IEC 14882:1998, informally known as C++98. In 2011, C++11 was released, and this standard is also used in the case study [19].

C++ does not have a concept of time. Traditionally C++ programs target standard CPUs assuming there is an operating system allowing system calls and all operations are executed sequentially. Native C++ data types such as int and char have fixed sizes of 8, 16, 32, etc. making them not ideal for HLS as in hardware design it is desired to optimize the resource usage.

## 3.2 Object-oriented programming

C++ supports object-oriented programming (OOP) paradigm. OOP means that the data is processed in the code as objects. All objects are instances of classes that have certain attributes or member variables and methods or member functions [20].

One example of a class could be a vehicle: it has traveller capacity and speed as member variables and turn right, turn left, accelerate, and decelerate as member functions. Classes work as type definitions in the programming language so now it is possible to instantiate multiple different vehicles with different member variables. To further specify that the vehicle is a truck, a class truck is created which has all the attributes and methods that the vehicle does, but they don't need to be rewritten as OOP offers a feature called inheritance. Class truck inherits from the class vehicle and it can have some truck-specific attributes, like storage capacity for example. Another class could be a wheel. A Wheel has a diameter as a member variable and roll as a member function. A truck instantiates four wheels as member variables, optimally with the same diameter. The concept of objects inside objects is called object composition in OOP. A bicycle class would inherit from the vehicle, it would have its member variables and functions and it would instantiate two wheels, etc.

Encapsulation means that both member functions and variables are declared as private or public whether the programmer wants them to be visible outside the class or not. A common practice in SW coding is that member functions are public and member variables are private. If the programmer wants to change the value of member variables from the outside, he or she has to declare a member function that changes the value of the variable for example  $set_x()$ -function to change the value of x.

In OOP, all classes must have a constructor as a member function. Constructor is called when a new instance/object of the class is instantiated. A constructor can be default or parameterized. Default constructor sets default values to member variables and with parameterized constructor programmer can set member variables when instantiating the object.

Figure 1 presents an example class  $example_c$ . In line 1 there is the declaration of the  $example_c$  class. Suffix c is fully optional, and it is just a good practice telling the designer that  $example_c$  is a class and not for example an object. Everything between the wave brackets in lines 1 and 20 is the contents of the class.

Lines 2 and 5 define member visibility outside of the class. Anything declared private can only be accessed from inside the class. The default visibility is private so line 2 is optional but for clarity in this example case, it is written. Common practice is that member variables are declared private and there are specific member functions for accessing those variables.

This class has two attributes, integer type variables *var1* and *var2*. They are declared private. In the constructor starting from line 6, the attributes are initialized to zeros. The class has *set\_var1()*-method to assign *var1* to a specific value that it takes as an argument and *get\_var1()*-method to extract the value of *var1* to the outside of the class. *var2*-attribute cannot be accessed at all from the outside of this class. This is not very practical and in an actual class like this, there would probably be a similar accessing method for *var2* as there is for *var1*. The *print()*-method prints out the values of the attributes.

| 1  | <pre>class example_c{</pre>                                               |

|----|---------------------------------------------------------------------------|

| 2  | private:                                                                  |

| 3  | int varl;                                                                 |

| 4  | int var2;                                                                 |

| 5  | public:                                                                   |

| 6  | example_c(){                                                              |

| 7  | var1=0;                                                                   |

| 8  | var2=0;                                                                   |

| 9  | }                                                                         |

| 10 | <pre>void set_var1(int value1){</pre>                                     |

| 11 | <pre>var1 = value1;</pre>                                                 |

| 12 | }                                                                         |

| 13 | <pre>int get_var1(){</pre>                                                |

| 14 | return var1;                                                              |

| 15 | }                                                                         |

| 16 | <pre>void print() {</pre>                                                 |

| 17 | <pre>std::cout &lt;&lt; "var1 = " &lt;&lt; var1 &lt;&lt; std::endl;</pre> |

| 18 | std::cout << "var2 = " << var2 << std::endl;                              |

| 19 | }                                                                         |

| 20 | };                                                                        |

Figure 1. Example class declaration in C++.

## 3.3 HLS restrictions and additions to C++

OOP suits HLS well since modules in IP design can be similar but have minor differences. Think for example two FIR-filters with a different number of coefficients. OOP in HLS enables the designer not to repeat written code but to reuse it. This makes the design more readable and enables easier bug fixing. Siemens EDA Catapult, which is used in the case study as the synthesis tool, advises the designer to create the designs in class-based OOP rather than traditional function-based code.

Since HLS generates RTL from the C-code that is eventually synthesized to actual hardware, some of the C++ constructs are prohibited in HLS design due to the limited resources in HW. Such constructs are for example dynamic memory allocation, function pointers, and recursive functions [21]. Also, good programming practises in HLS differ a little bit from the common SW practises. In Catapult HLS, all the member variables and functions are declared private except the class constructor and the interface function that must have *#pragma hls\_design interface* before it, if used as module interface [11]. If there is no such pragma, the function will be synthesized as logic within the higher level in the hierarchy.

The constructor in the HLS design is interpreted as a hardware reset [22]. Therefore, there must be only one constructor in an HLS targeted class. All the member variables must be reset in the constructor body if that is desired in the hardware reset. In C++11 it is also possible to initialize a member variable in the variable declaration.

The interface function is treated as a clocked process in HLS design. Interface function has the modules inputs, outputs, and possible controls as parameters, and the module functionality is described in the interface function body. Function calls to classes member functions must occur inside the interface function. Therefore, everything else but the constructor and interface function should be declared private; there is always a chance of user error. [22]

## 3.3.1 AC datatypes

AC (Algorithmic C) data types is an open-source C++ library that includes bit accurate data types for C++ [23]. Native C++ data types, such as int, float, and char, have fixed bit widths. They can be used for HLS design but usually, it would result in poor QoR as in quite rare cases optimal hardware only uses these bit-widths. For this reason, specific arbitrary-precision data types have been developed for HLS. These bit accurate datatypes ensure that enough bits are allocated for every step of the design for maintaining the desired data accuracy and scale without having any unnecessary bits. Table 1 summarizes the AC datatypes used in the examples and case study in chapter 6.

| Туре                             | Description                                  |

|----------------------------------|----------------------------------------------|

| ac_int <w,s></w,s>               | Bit accurate integer signed or unsigned      |

|                                  | variable.                                    |

| ac_fixed <w,i,s,q,o></w,i,s,q,o> | Fixed point variable with specified overflow |

|                                  | mode, quantization mode, and decimal point   |

|                                  | location.                                    |

| ac_complex <t></t>               | Complex type variable with specified         |

|                                  | numeric type T as real and imaginary part.   |

Table 1. Bit accurate data types used in C++ HLS design in Catapult

Data type ac\_int is a fixed-point integer with a bit-width of template parameter W. S is a boolean type template parameter representing signedness. Value *true* means that the variable is signed resulting in two's complement representation in hardware. [11]

Data type ac\_fixed extends the use of ac\_int to be able to represent fractional values. Template parameters W and S work just like in ac\_int defining variables total bit-width and signedness. The parameter I defines the number of integer bits specifying the radix point

location. Q and O are optional parameters defining quantization and overflow modes. The sign bit is counted as one of the integer bits in ac\_fixed. [11]

Data type ac\_complex declares a complex number variable with both real and imaginary parts of type *T* given as a template parameter. ac\_complex doubles the bit width of T as it stores two values for real and imaginary parts of a complex number. [11]

Example ac\_int variable declarations can be seen in figure 2 rows 1 and 2. Now x, declared in row 1 can have values that can be represented with unsigned 3-bit variable, from 0 to 7. Template parameter S is *false* so all the bits represent the absolute value, but negative values cannot be represented. The declaration of y is identical to the x declaration except for the template parameter S being *true* in this case. The MSB of y represents signedness with '1' being negative and '0' positive. Variable y can have values between -4 and 3.

Rows 3, 4, and 5 in figure 2 show example declarations of ac\_fixed variables. Variable x2 is identical to variable x. Having 3 bits total, 3 integer bits and *false* as S, x2 can represent the same values as x. In row 4 z is declared as a two-bit variable with one integer and a sign bit. This means that the only integer bit represents signedness and the other bit of the two represents absolute value. The LSB is on the right side of the radix point, so this variable can have values of -1,  $-\frac{1}{2}$ , 0, and  $\frac{1}{2}$ . Quantization mode is defined as  $AC_TRN$  meaning truncate. If this variable is assigned with higher precision than it can handle, the LSBs are simply clipped away. Overflow mode is defined as  $AC_WRAP$  meaning wrap-around. If this variable is assigned with a greater value than it can represent, the MSBs are clipped away as well. These quantization and overflow modes are the default ones so they could have been just left away in this variable and the same functionality is in x2 and all the ac\_int variables.

Row 5 in figure 2 declares another ac\_fixed variable n. This one has non-default  $AC\_RND$  as quantization mode and  $AC\_SAT$  as overflow mode.  $AC\_RND$  is a rounding mode that rounds up if one bit right of LSB is high.  $AC\_SAT$  is a saturation mode that assigns the variable with the highest absolute value it can have if the variable is assigned with a value that is out of bounds. There are more rounding and saturation modes but using these in HLS code will lead to rounding and saturation logic in resulting hardware so they should be used carefully.

Row 6 shows ac\_complex type declaration. The element type of ac\_complex is now a fivebit unsigned integer making c a 10-bit complex number with 5-bit real and 5-bit imaginary parts.

| 1 | <pre>ac_int&lt;3,false&gt; x;</pre>                     |

|---|---------------------------------------------------------|

| 2 | <pre>ac_int&lt;3,true&gt; y;</pre>                      |

| 3 | <pre>ac_fixed&lt;3,3,false&gt; x2;</pre>                |

| 4 | <pre>ac_fixed&lt;2,1,true, AC_TRN, AC_WRAP&gt; z;</pre> |

| 5 | <pre>ac_fixed&lt;3,2,false, AC_RND, AC_SAT&gt; n;</pre> |

| 6 | ac complex <ac int<5,false=""> &gt; c;</ac>             |

Figure 2. Example declarations of bit accurate variables.

AC datatypes also offer a bunch of different functions as well as overloaded arithmetic operators with them since hardware designer typically wants to perform some specific operations to the bit accurate data types that might not be so typical in software design.

Bit select operation is typical in hardware design. It allows individual bit selection from any of the AC datatypes with square brackets ([]). Bit selections allow getting bit from AC datatypes or assigning specific bit with a value of '1' or '0'. Bit selection can only be used for single bits and longer bit queue selections there are other functions.

In figure 3 row 1 variable k is declared and initialized with a decimal value of ten. The bitlevel representation of the value is shown in the commented section of the row. In rows 2 and 3 two boolean type variables are declared and initialized with a value using the bit select operator from k. b0 is assigned with the LSB of k being '0' in this case and b1 is assigned with the MSB of k being '1' in this case. The designer must be careful not to select a bit out of the variable bounds as it will trigger an error in the compilation or crash the C++ simulation.

Shift operation is also very common in hardware design. Shifting bits left or right can usually be thought of as multiplying or dividing by a factor of two in decimal representation. Shifting a bit over the MSB or LSB of the variable, however, has different functionality compared to multiplying and dividing. Shifted-out bits get removed and empty bits get padded with zeros, or ones in negative numbers MSB.

In figure 3 row 4 a new variable k1 is declared and initialized with a value of k shifted right by one bit. The commented section of the row shows the bit representation of the k1 value. The zero in parenthesis is the original LSB of k that is shifted out and removed. The MSB is padded with a zero. The decimal value equals five so the original value was divided by two.

In row 5 there is a left shift operation to the same k variable and the value is assigned to a new 5-bit variable k2. Since there is one more bit available intuition would say that all the bits are shifted left, LSB is padded with zero and the resulting decimal value would be twenty. This is not what happens. Shift operation always returns the same number of bits that is in the original shifted variable. On the right side of the equals-to operator k gets shifted left, the MSB is removed and LSB is padded with zero. After that, this 4-bit value is assigned to a 5-bit variable and the MSB is padded with zeros. The result is shown in the commented section of the row and the decimal value equals four, which is far from the original value of ten multiplied by two.

Row 6 shows the correct way to maintain all bits when performing the same operation. The return value of the left shift is cast to a specific type, in this case being the same type the value is eventually assigned to. Now the MSB doesn't get removed and the resulting decimal value equals twenty, the original value multiplied by two.

In the bit selection section, it was said that there are functions for extracting or inserting bit queues in AC datatypes. These functions are *slc()* and *set\_slc()* methods. *slc()*-method takes slice width as a template parameter and an LSB bit as a function parameter and returns specified slice width bit queue starting from the specified LSB of the target variable. *set\_slc()*-method takes LSB and AC datatype variable as parameters and inserts given variable to target variable starting from specified LSB. Line 7 shows an example of *slc()* and line 8 shows an example of the *set\_slc()*-method.

ac\_complex datatype has *real()* and *imag()* to insert or extract real and imaginary parts from the complex datatype. The return value will be the same as the one defined for the ac\_complex variable. Lines from 9 to 11 show an example of ac\_complex declaration and separate value assignments for real and imaginary parts.

```

ac_int<4,false> k = 10;

// 4'b1010

1

2

bool b0 = k[0];

// LSB of k

3

bool b1 = k[3];

// MSB of k

4

ac int<4, false> k1 = k >> 1;

// 4'b0101(0)

5

ac_int<5,false> k2 = k << 1;</pre>

// 5'b00100

// 5'b10100

6

k^2 = ac int < 5, false > (k << 1);

7

ac int<2, false> m = k.slc<2>(1); // 2'b01

k2.set slc(0,m);

// 5'b10101

8

9

ac complex<ac int<4,false> > comp;

```

| 10 | <pre>comp.real() = 7;</pre>  | // 4'b0111 |

|----|------------------------------|------------|

| 11 | <pre>comp.imag() = 15;</pre> | // 4'b1111 |

Figure 3. Examples of bit-level operations for AC datatypes.

There is also a helper function for AC type array initialization or un-initialization. Init\_array function takes a constant or "don't care" value as a template parameter and the base address of the array and the number of elements in the array to be initialized as function arguments. For example, the constant value could be  $AC_VAL_0$  meaning that the elements of the array will be assigned to zero. Un-initializing an array can be done by giving the function a "don't care" template parameter  $AC_VAL_DC$ . The reason why one would do this is to prevent the generation of initialization logic of array elements stored in large memories that have limited access bandwidth. After doing this in the constructor, the designer must be careful not to read from the un-initialized memory element before writing there as it may lead to unexpected and undesired behaviour. [11]

## 3.3.2 ac\_channel

## 3.3.2.1 Overview

ac\_channel is a special channel data type used in interconnections between leaf blocks. It is essentially a C++ FIFO that is infinite in C++ simulation, but the depth must be defined in Catapult directives to get the correct FIFO size also in synthesized hardware. FIFO depth 0 removes the FIFO replacing it with only wires. The modelling paradigm used in Catapult HLS to model concurrent HW processes in sequential C++ is called Kahn Process Network (KPN) [24] and ac\_channels are used as infinite FIFOs between processes. ac\_channel can only be used in point-to-point connections. If the same data needs to be routed for more than one block an additional routing block, multiple ac\_channels in the driving end of the FIFO or merging the receiving blocks is required. ac\_channel is a template class that takes the data type of the channel as a template parameter. [11]

#### 3.3.2.2 Read and write

ac\_channels are declared in top-level as private member variables. They are referenced in the interface functions of the leaf blocks to store the data outside of blocks in the channel variables in top-level. ac\_channel has member functions *write()* and *read()* for sending and receiving data from the channel. Channel accesses are bandwidth limited so the functions can only be accessed once in a single clock cycle per channel. This must be considered in the coding and kept in mind if the main function is going to be pipelined or not. If this rule is violated and there are multiple channel accesses within a single clock cycle, Catapult will trigger an error claiming that the design couldn't be scheduled even with unlimited resources.

Using a *read()*-function on an empty channel will trigger an assertion and crash C++ simulation and therefore it should be used with the *available()*-function to make sure that does not happen if the data availability is unknown. *available()*-function should be inside *#ifndef*

<u>SYNTHESIS</u> condition that has the ac\_channel member function since in Catapult synthesis, *read()*-function transforms into a blocking read that stalls until data is available in the channel. *available()* member function takes an integer number as an argument and returns *true* if there is an equal or greater amount of data in the FIFO than the specified integer is. In

RTL synthesis *available()* synthesizes always *true* optimizing away and leaving only the blocking channel read.

#### 3.3.2.3 Non-blocking read and write

If there are multiple ac\_channel inputs for a block and the data availability for each channel is unknown or the block must do something even if there were no input data, a non-blocking read can be used. Whereas the normal *read()* function stall until data is available in the channel and returns the read value from the channel, *nb\_read()* returns boolean value *true* if a value was read from the channel and *false* if the channel was empty. Normal *read()* doesn't take any arguments but *nb\_read()* takes the variable that the value is read to if there is some. This variable must be the same type as specified for the ac\_channel. *nb\_read()* from an empty channel does not trigger assertion nor crash the C++ simulation.

Non-blocking write is a more rarely needed feature of the channel. As a non-blocking read, it takes the value to be written to the channel as an argument and returns boolean *true* or *false*, if the write was successful or not. In C++ simulation the return value will always be *true* since the channel FIFO is infinite. In RTL where the FIFO depth is defined, the return value might be *false* as well. To verify the correct functionality of the C++ source code, manual *false* must be inserted to the "return value".

SCverify co-simulation and equivalence checking might cause data mismatch errors if the design is using non-blocking reads and/or writes. Manual verification of the data correctness or other verification method is needed in this case. Therefore, the use of non-blocking reads and writes should be avoided in the source code if possible, but in some cases, they might be useful and required features.

#### 3.3.2.4 Arrays and structs

Often it is required to send large amounts of data through an interface or there might be some control signals for individual samples travelling through the entire pipeline with the data. An intuitive way of programming this could be to create an array of ac\_channel, each containing its type of data that travels in parallel to keep data in alignment. This is not an optimal way since each ac\_channel synthesizes an interface handshaking logic and a FIFO if the depth is not defined to 0. A general rule is that an ac\_channel array should not be used for point-to-point connections.

A better way to solve the problem is to create a C++ struct that contains all the data that is known to be tied together and travel in parallel. ac\_channel can take a struct as a data type and the amount bits in the struct is directly the sum of bits in the AC data types that the struct contains. This way, all the data gets sent through the same ac\_channel, and only one FIFO or set of wires and handshaking logic is generated, saving area and complexity.

#### 3.3.3 File structure

In traditional C++ programming, it is common that header file includes forward declarations of classes and functions and other data shared by multiple different source files. That practice can be used in HLS as well, but it is also possible to declare a class per header file and all the information that is needed by that class. This is just a matter of designer preference. In this thesis and the following examples, the latter one will be used.

Figure 4 presents an example header file content. This is a very simple example of a class that only writes the data from the input port to the output port when the interface function is called.

Lines 1, 2, and 23 perform a guard preventing multiple inclusions of this class. The first time this class is included *EXAMPLE*\_string is defined, and possible further inclusions are blocked by the *#ifndef* condition. The string must be unique inside the project. After this, there is an empty space for possible file inclusions or constant declarations. This file could include a common type definitions file as the *DATA\_TYPE* used in line 14 in this file is not declared at all in this file. The first two lines and the *#endif* at the end of the file can be replaced with *#pragma once* at the beginning of the file to achieve equivalent functionality.

In HLS design good practice is that all the member variables and those member functions that are not the interface function should be declared private. This is not mandatory, but the variables and functions should not be accessed from the outside of the class, for example, testbench so there is no reason to declare them public. If they are declared private, they will trigger an error in compilation if misuse is occurring. Since this example is very simple, there are no private members in this class.

Only public members can be accessed from the outside of the class. As mentioned before, only the class constructor and exactly one interface function should be declared public in HLS designs. Constructor, found in lines from 9 to 11, is called when a class is instantiated inside another class or in the testbench. The constructor initializes member variables with default values. Catapult only supports the default constructor, meaning no arguments can be given to the function since it is interpreted as a reset in hardware. Default values in the constructor are the reset values to each member.

The interface function in line 14, specified by the *#pragma hls\_design interface* directly above, defines what will be synthesized to hardware. It takes the interfaces, input, output, and possible controls, as function arguments and describes the processing inside it. In this case, the interfaces are ac channel type *din* and *dout* containing *DATA TYPE* type data.

Lines from 15 to 17 make sure of the correct functionality of the class in C++ simulation. <u>SYNTHESIS</u> macro is not defined in C++ simulations, so the condition makes sure there is enough input data available in the channel before trying to read it. Read from an empty channel would crash the C++ simulation. Line 16 makes sure there is always at least one sample in the input channel before trying to read it. The *available()* function always synthesizes to *true*. When the design is being synthesized the lines of code within *#ifndef\_SYNTHESIS\_* condition are ignored.

In line 19 there is the entire functionality of this class. When the interface function is called and if there is data in the *din* channel, one sample is read from the *din* and written to *dout*.

```

1

#ifndef EXAMPLE

2

#define EXAMPLE

3

// file inclusions, constant declarations here

4

class example c{

5

private:

6

// member functions and variables declared here

7

public:

8

// constructor

9

example c() {

10

// member variable initializations here

11

```

```

12

// interface function

13

#pragma hls design interface

14

void run(ac channel<DATA TYPE> &din, ac channel<DATA TYPE> &dout) {

#ifndef ____SYNTHESIS___

15

16

while(din.available(1))

17

#endif

18

{

19

dout.write(din.read());

20

}

21

}

22

};

23

#endif

```

Figure 4. Example contents of a header file containing an example class.

## 3.3.4 Leaf blocks and top-level

Programming larger designs is best to do by dividing the design into a hierarchy according to a predetermined block diagram. Doing this enables easy code reuse and scaling. Functional blocks, that perform the algorithm or whatever is desired in the design, are called leaf blocks or sub-blocks. Top-level is the class where the object declarations of the leaf blocks and ac\_channels are, and no logic is allowed in top-level [11].

Figure 5 shows an example of a small design divided into a few leaf blocks. The signal processing does not make any sense in this example, but the class hierarchy is the point. There are two types of leaf blocks,  $block1_c$  and  $block2_c$  classes. Objects of these classes are declared as private members of the  $top_c$  class, there are two block1 objects and one block2. There are also two ac\_channels declared for interconnections between the leaf blocks.

```

1

#include <ac channel.h>

2

class block1_c{

3

public:

4

block1 c(){}

5

#pragma hls_design interface

void run(ac channel<int> &din, bool control, ac channel<int> &dout) {

6

int dinTmp = din.read();

7

8

if (control) {

9

dout.write(dinTmp);

10

}

11

}

12

};

13

class block2 c{

14

public:

15

block2_c(){}

16

#pragma hls_design interface

17

void run(ac channel<int> din[2], bool control, ac channel<int> &dout){

18

int dinTmp[2];

19

dinTmp[0] = din[0].read();

20

dinTmp[1] = din[1].read();

```

```

21

if (control) {

22

dout.write(dinTmp[0]);

23

} else {

24

dout.write(dinTmp[1]);

25

}

26

}

27

};

28

class top_c{

29

ac channel<int> connect[2];

30

block1 c block1[2];

block2 c block2;

31

32

public:

33

top c() { }

34

#pragma hls design interface

35

void run(ac channel<int> din[2],bool control[2],ac channel<int> &dout) {

36

block1[0].run(din[0], control[0], connect[0]);

37

block1[1].run(din[1], control[0], connect[1]);

38

block2.run(connect, control[1], dout);

39

}

40

};

```

Figure 5. Example of small hierarchical design with three leaf blocks and top-level stitching them together.

As mentioned, ac\_channels can only be used in point-to-point connections. Control signals, however, can be routed for multiple different leaf blocks. An example of this in figure 5 is the *control[0]* signal which is routed for both block1's in top-level class in lines 36 and 37. In Catapult, these control signals must be mapped to *DirectInput* and in testbench, they are assumed to be held stable during the tests to ensure no data in the pipeline won't get corrupted since *DirectInputs* have no synchronization logic. [22]

## 3.4 Templatizing

Templatizing is a great way to enhance code reuse in C++. Being supported by Catapult HLS, DSP blocks and buffers, for example, can be created for different kinds of data with a single template class. A very simple example of a shift register template class is introduced in figure 6. The problem with this kind of template class is that multiple different data types must be supported to get the most use of it. For example, this shift register is desired to be used with AC data types as well as data structs which introduces some challenges for the programmer.

The key to avoiding any compilation errors is the template parameter *isStruct* which, by default, is declared *false*, but if the shift register is used with a data struct it should be manually declared *true*. In the constructor line 7, the *isStruct* parameter is then checked and if it is left *false*, the data type is assumed to be AC data type and the shift register element values are initialized to zero with a loop. *init\_array* function cannot be used in this case since the code needs to compile also in case the data type is a struct, but the functionality of the function and an initialization loop are identical.

```

1

template<class DATA TYPE, unsigned N, bool isStruct = false>

2

class shiftreg c{

3

private:

4

data struct<DATA TYPE,N> reg;

5

public:

6

shiftreg c() {

7

if (!isStruct) { for(int i=0; i<N; i++) reg[i] = (DATA TYPE)0; }</pre>

8

}

9

#pragma hls design interface

void run(DATA TYPE din, data struct<DATA TYPE,N> &dout) {

10

11

#pragma hls_unroll

12

SHIFT:for(int i=N-1;i>0;i--) {

13

reg.data[i] = reg.data[i-1];

14

}

15

reg.data[0] = din;

dout = reg;

16

17

}

18

};

19

#endif

```

Figure 6. An example of a shift register with user-defined depth and data type that can be used with AC data types and data structs.

If a struct is given as data type for the shift register, the example above does not initialize the data at all in the constructor. This comes with an assumption that the struct has a built-in constructor. Figure 7 shows an example of a struct that would work with the shift register. The struct has two ac\_int type data fields and a boolean flag variable. In line 5 there is the struct constructor, similar to a class constructor, where all the data fields are initialized. Line 10 defines the struct behaviour when an integer type is cast to it. This must be defined since in the shift register constructor value 0 is cast to the struct. By default, there is no conversion from an integer to a struct so this would trigger a compilation error even though with the struct as data type, line 7 would never be fully executed because of the condition. In this case, nothing is done when an integer is cast to the struct.

```

1

struct myStruct t{

2

ac_int<8,false> field1;

3

ac int<8,false> field2;

4

bool flag;

5

myStruct t() {

field1 = 0;

6

7

field2 = 0;

8

flag = false;

9

}

10

myStruct_t(int) { }

11

};

```

Figure 7. An example data struct with constructor and definition of behaviour when an integer is cast to the struct.

Another challenge that templates present is that bit widths inside the template in some cases might vary depending on the template parameters. To solve this issue, a group of helper functions is included in the AC data types. Table 2 summarizes these helper functions.

The first one of these, the  $log2\_ceil$  function, is probably the most useful since it returns the base 2 logarithm value of N, which equals the number of bits required to index N elements. The difference to the second one, the  $log2\_floor$  function, is pretty obvious; if N is a power of two, the functions return the same value, but in case of N is anything between these, the two functions round the return value up or down. [11]

The difference between *log2\_ceil* and *nbits* functions is the behaviour at the power of two values. For example, if *N* equals 8 is given to both functions, base 2 logarithm of 8 equals 3, so *log2\_ceil* returns 3. With three bits (unsigned) it is possible to represent numbers from zero to seven, a total of eight different numbers. However, number eight requires one more bit to be represented in binary format, so *nbits* return value 4.

Table 2. Ceil, floor, and nbits helper functions

| Function                    | Description                                    |

|-----------------------------|------------------------------------------------|

| ac::log2_ceil <n>::val</n>  | Returns log2 of N, rounded up                  |

| ac::log2_floor <n>::val</n> | Returns log2 of N, rounded down                |

| ac::nbits <n>::val</n>      | Returns number of bits required to represent N |

## **4** CATAPULT HLS

Siemens EDA Catapult is one of the industrial HLS tools currently in the market. Catapult will be used in the case study in chapter 6. This chapter introduces Catapult's main features and functionality to provide a basic understanding of the HLS tool.

#### 4.1 Overview

Catapult is an HLS tool that generates RTL implementations from C/SystemC/C++ high-level descriptions of desired hardware architecture. Catapult was released in 2004 as a C++ synthesis tool mainly targeting data-driven applications in ASIC, where the design receives an input, processes it, and sends an output, such as found, for example, in wireless communications and video coding. By this day Catapult has evolved into an HLS-tool basically for any hardware application targeting both ASIC and FPGA technologies. [10]

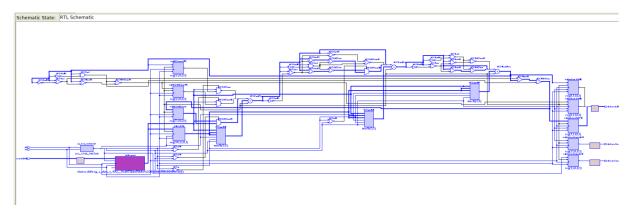

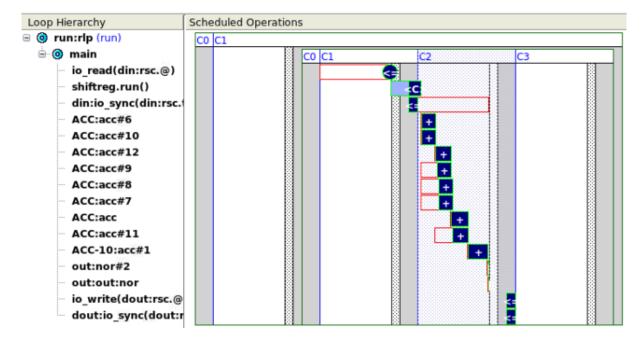

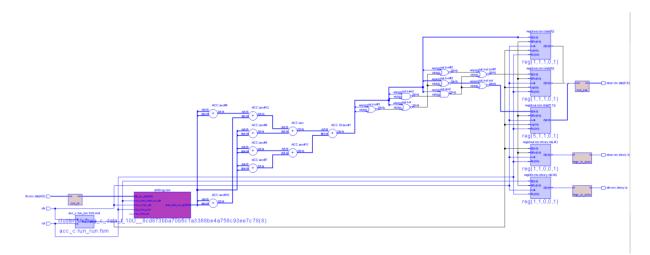

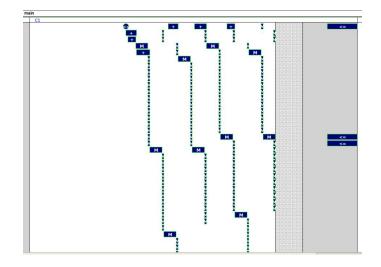

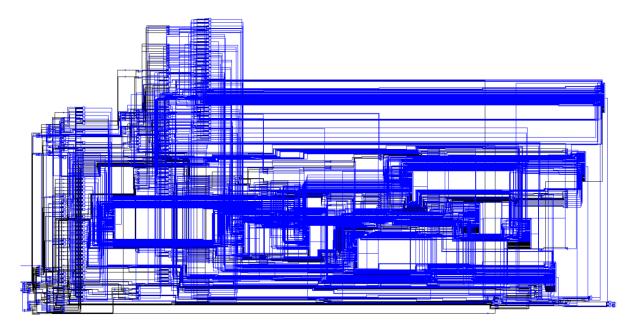

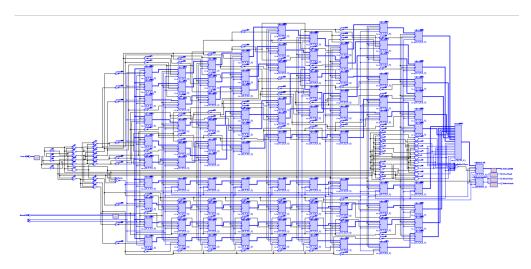

Catapult provides several graphical tools such as Gantt-chart viewer, resource viewer, and schematic viewer for easier design analysing and debugging. Newer versions of Catapult also provide the Design Analyzer tool to enable easy analysis of the relation between the source code and generated RTL, which can otherwise be challenging to interpret. [10]

Catapult integrates HLV-flow that engages the verification team early in the design process to enable early bug catching, even before any RTL is generated. Catapult Design Checker tool enables catching bugs, hard to find with C++ or RTL simulation, without a testbench. Catapult Coverage tool provides complete SystemC/C++ coverage metrics and SCverify verifies the equivalence of C++ and RTL simulation outputs with an automatically generated testbench that runs a co-simulation between the two models. [10]

In terms of numbers, Catapult promises up to ten times more productivity compared to handwritten RTL flow. Up to 80 %, less source code is needed enabling easier code writing, reading, and debugging. The verification team's time and effort are saved due to HLV flow adding up to 80 % saving in verification cost. [10]

## 4.2 Input languages

Catapult supports C/SystemC/C++ as input languages. C++'s class-based hierarchy is preferred over standard C's function-based code. SystemC is a class library addition to C++ that allows clock accurate timing and parallel operations written directly into the source code [25].

Despite the discussion about C-like languages not being optimal for hardware description [15], SystemC and C++ have become the dominant options for input language in HLS. The benefits of using SystemC/C++ are briefly discussed in [7].