# Running Deep Learning Applications on Resource Constrained Devices

by

### **Naveen Vedula**

M.Sc., Simon Fraser University, 2016 B.Sc., National Institute of Technology, Warangal, India, 2010

> Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

> > in the School of Computing Science Faculty of Applied Sciences

### © Naveen Vedula 2021 SIMON FRASER UNIVERSITY Summer 2021

Copyright in this work is held by the author. Please ensure that any reproduction or re-use is done in accordance with the relevant national copyright legislation.

# **Declaration of Committee**

| Name:         | Naveen Vedula                                                                                                                                                                                                                                                                                                                                                              |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Degree:       | Doctor of Philosophy                                                                                                                                                                                                                                                                                                                                                       |

| Thesis title: | Running Deep Learning Applications on Resource<br>Constrained Devices                                                                                                                                                                                                                                                                                                      |

| Committee:    | Chair: Keval Vora<br>Assistant Professor, Computing Science                                                                                                                                                                                                                                                                                                                |

|               | Arrvindh Shriraman<br>Supervisor<br>Associate Professor, Computing Science<br>Zhenman Fang<br>Committee Member<br>Assistant Professor, Engineering Science<br>Alaa R. Alameldeen<br>Examiner<br>Associate Professor, Computing Science<br>Mieszko Lis<br>External Examiner<br>Associate Professor<br>Electrical and Computer Engineering<br>University of British Columbia |

## Abstract

The high accuracy of Deep Neural Networks (DNN) come at the expense of high computational cost and memory requirements. During inference, the data is often collected on the edge device which are resource-constrained. The existing solutions for edge deployment include: i) executing entire DNN on the edge (EDGE-ONLY), ii) sending the input from edge to cloud where the DNN is processed (CLOUD-ONLY), and iii) splitting the DNN to execute partially on the edge and partially on the cloud (SPLIT). The choice of deployment between EDGE-ONLY, CLOUD-ONLY and SPLIT is determined by several operating constraints such as device resources and network speed, and application constraints such as latency and accuracy.

The EDGE-ONLY approach requires compact DNN with low compute and memory requirements. Thus, the emerging class of DNNs employ low-rank convolutions (LR-CONVs) which reduce one or more dimensions compared to the spatial convolutions (CONV). Prior research in hardware accelerators has largely focused on CONVs. The LR-CONVs such as depthwise and pointwise convolutions exhibit lower arithmetic intensity and lower data reuse. Thus, LR-CONVs result in low hardware utilization and high latency.

In our first work, we systematically explore the design space of Cross-layer dataflows to exploit data reuse across layers for emerging DNNs in EDGE-ONLY scenarios. We develop novel fine-grain cross-layer dataflows for LR-CONVs that support partial loop dimension completion. Our tool, X-Layer decouples the nested loops in a pipeline and combines them to create a common outer dataflow and several inner dataflows.

The CLOUD-ONLY approach can suffer from high latency due to the high transmission cost of large input data from the edge to the cloud. This could be a problem, especially for latency-critical applications. Thankfully, the SPLIT approach reduces latency compared to the CLOUD-ONLY approach. However, existing solutions only split the DNN in floating-point precision. Executing floating-point precision on the edge device can occupy large memory and reduce the potential options for SPLIT solutions.

In our second work, we expand and explore the search space of SPLIT solutions by jointly applying mixed-precision post-training quantization and DNN graph split. Our work, Auto-Split finds a balance in the trade-off among the model accuracy, edge device capacity, transmission cost, and the overall latency.

**Keywords:** Cross-layer Dataflow, DNN Accelerator, Edge-Cloud Collaboration, Neural Networks, Mixed Precision, Distributed Inference

# Dedication

To Mom, Dad, Niti, and Sanjana.

## Acknowledgements

X-Layer is the result of my work at Simon Fraser University in collaboration with my supervisor Dr Arrvindh Shriraman, my labmate Reza Hojabr and his supervisor Ahmad Khonsari. The Auto-Split work has been produced at Huawei Technologies in collaboration with Dr Amin Banitalebi Dehkordi, Dr Fei Xia, Dr Lanjun Wang, Dr Jian Pei and Dr Yong Zhang.

I would like to thank my supervisor, Dr Arrvindh Shriraman for staying with me in tough times and providing his useful insights. This journey would not have been possible without you. I would also like to thank my co-supervisor Dr Zhenman Fang for his valuable feedback on my work from time to time. Thank you Dr Yong Zhang for pushing me to think hard about a problem, Dr Amin Banitalebi Dehkordi for your dedication, work ethic and support, and Dr Lanjun Wang for your critical thinking.

I am very thankful to my collaborators for wearing many hats as friends, mentors, and just being there sometimes. Thank you, Dr Snehasish Kumar, Dr Amirali Sharifian, Dr Reza Hojabr, Dr Apala Guha, Dr Viji Srinivasan, Dr Reynald Hoskinson, Changan Chen, Dr Frederick Tung, Dr Greg Mori, Dr Jian Pei, Dr Andreas Moshovos, and Dr Nick W. Sumner. I would like to thank Dr Alaa Alameldeen, Dr Keval Vora, and Dr Mieszko Lis for serving in different roles during the thesis defence on such short notice. Finally, I would like to thank my lovely wife, Sanjana for her support and patience as I worked my way through this arduous journey.

# **Table of Contents**

| De | eclara  | ation of Committee                                     | ii  |

|----|---------|--------------------------------------------------------|-----|

| Al | bstrac  | ct                                                     | iii |

| De | edicat  | tion                                                   | v   |

| A  | cknov   | vledgements                                            | vi  |

| Ta | ble of  | f Contents                                             | vii |

| Li | st of ' | Tables                                                 | x   |

| Li | st of l | Figures                                                | xi  |

| Li | st of A | Abbreviations                                          | XV  |

| 1  | Intr    | oduction                                               | 1   |

|    | 1.1     | AI application pipeline                                | 2   |

|    | 1.2     | Dissertation Contribution                              | 5   |

|    | 1.3     | Dissertation Organization                              | 7   |

|    | 1.4     | Improving latency for Edge-Only Approach               | 8   |

|    | 1.5     | Speedup potential for SPLIT Approach                   | 15  |

| 2  | Bac     | kground                                                | 21  |

|    | 2.1     | Deep Neural Network Basics                             | 21  |

|    | 2.2     | Edge Only Optimizations                                | 27  |

|    |         | 2.2.1 Model optimizations                              | 28  |

|    |         | 2.2.2 Dataflow                                         | 32  |

|    | 2.3     | Distributed Examples                                   | 34  |

| 3  | Con     | nposable Pipelined Dataflows for Low-Rank Convolutions | 38  |

|    | 3.1     | Motivation                                             | 38  |

|    |         | 3.1.1 Emerging DNN characteristics                     | 38  |

|    |         | 3.1.2 Terminology: Outer and Inner Dataflow            | 40  |

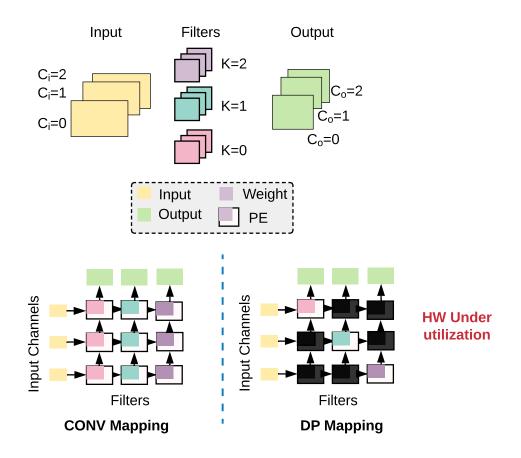

|   |      | 3.1.3    | Partial-order ("p") pipelines for LR-CONV          | 43 |

|---|------|----------|----------------------------------------------------|----|

|   |      | 3.1.4    | Inefficient Mapping of DP layer                    | 44 |

|   |      | 3.1.5    | Heterogeneous Inner Dataflow                       | 44 |

|   |      | 3.1.6    | Heterogeneous Resource Allocation                  | 46 |

|   | 3.2  | Inverte  | ed Residual Layer: A Cross-Layer Example           | 47 |

|   |      | 3.2.1    | Pipeline Overview                                  | 47 |

|   |      | 3.2.2    | Data transformations in pipeline                   | 47 |

|   | 3.3  | X-Lay    | er: Design space and Taxonomy                      | 49 |

|   |      | 3.3.1    | Taxonomy and search space of cross-layer           | 51 |

|   |      | 3.3.2    | Memory Requirement for Cross-Layer dataflows       | 52 |

| 4 | X-L  | ayer Mi  | icroarchitecture and Dataflow Exploration          | 54 |

|   | 4.1  | X-Lay    | er Architecture                                    | 54 |

|   | 4.2  | Quanti   | itative Insights and Evaluation                    | 56 |

|   |      | 4.2.1    | Experimental Setup                                 | 56 |

|   |      | 4.2.2    | Cross-layer for 2-stage depth-separable            | 57 |

|   |      | 4.2.3    | Cross-layer for 3-stage inverse-residual           | 59 |

|   |      | 4.2.4    | 1, 2, and 3 stage pipelines: LR-CONV and CONV      | 61 |

|   | 4.3  | X-Lay    | er vs State-of-the-Art                             | 62 |

|   |      | 4.3.1    | Detailed explanation                               | 63 |

|   |      | 4.3.2    | X-Layer Hardware Summary                           | 65 |

|   | 4.4  | Conclu   | usion                                              | 66 |

| 5 | Auto | o-Split: | A General Framework of Collaborative Edge-Cloud AI | 67 |

|   | 5.1  | Proble   | m Formulation                                      | 67 |

|   |      | 5.1.1    | Basic Setup                                        | 67 |

|   |      | 5.1.2    | Problem Formulation                                | 68 |

|   | 5.2  | AUTO     | -SPLIT Solution                                    | 70 |

|   |      | 5.2.1    | Potential Split Identification                     | 70 |

|   |      | 5.2.2    | Bit-Width Assignment                               | 71 |

|   |      | 5.2.3    | Post-Solution Engineering Steps                    | 72 |

|   | 5.3  | Experi   | iments                                             | 72 |

|   |      | 5.3.1    | Experiments Protocols                              | 73 |

|   |      | 5.3.2    | Accuracy vs Latency Trade-off                      | 73 |

|   |      | 5.3.3    | Overall Benchmark Comparisons                      | 74 |

|   |      | 5.3.4    | Comparison with QDMP + Quantization                | 76 |

|   |      | 5.3.5    | Case Study                                         | 78 |

|   | 5.4  | Ablati   | on Studies                                         | 79 |

|   | 5.5  | Conclu   | usion                                              | 84 |

| 6   | Conc   | clusion and Future Work             | 85  |

|-----|--------|-------------------------------------|-----|

|     | 6.1    | Conclusion                          | 85  |

|     | 6.2    | Directions for Future Work          | 86  |

|     | 6.3    | Reflections                         | 88  |

| 7   | Othe   | er Works of the Author              | 91  |

| Bil | oliogr | aphy                                | 95  |

| Ар  | pendi  | ix A AUTO-SPLIT Engineering details | 104 |

# **List of Tables**

| Table 1.1 | Metrics for Operating constraints and Application requirements                              | 4  |

|-----------|---------------------------------------------------------------------------------------------|----|

| Table 1.2 | AI Application scenario for DISTRIBUTED approach                                            | 16 |

| Table 2.1 | Operations used in DNNs. Inv Res.= Inverted Residual Layers, Depth sep.=                    |    |

|           | Depth separable Layers                                                                      | 25 |

| Table 2.2 | Optimization scope along the DNN stack                                                      | 27 |

| Table 2.3 | Different verticals for considering quantization                                            | 29 |

| Table 3.1 | Hyper-parameters for Design space exploration.                                              | 50 |

| Table 3.2 | Design Parameter Exploration using NSGA-II                                                  | 50 |

| Table 3.3 | Design space of cross-layer dataflows.                                                      | 51 |

| Table 4.1 | Evaluation Organization                                                                     | 57 |

| Table 4.2 | X-Layer vs. State-of-the-Art. CC= $CONV \rightarrow CONV$ , DS= $DP \rightarrow PT$ , PDP = |    |

|           | $PT \rightarrow DP \rightarrow PT$                                                          | 62 |

| Table 5.1 | Hardware platforms for the simulator experiments                                            | 73 |

| Table 5.2 | Comparing $\text{QDMP}_E$ , AUTO-SPLIT, and $\text{QDMP}_E$ +U4                             | 77 |

| Table 5.3 | Evaluation of License Plate Recognition solutions                                           | 79 |

| Table 5.4 | Effect of input or feature compression on solutions                                         | 80 |

| Table 5.5 | Ablation study on network bandwidth.                                                        | 80 |

| Table 5.6 | Potential splits towards the end of ResNet-50                                               | 82 |

| Table 5.7 | Layer indices of the collected output activations                                           | 82 |

| Table 5.8 | Comparison of top two design points for image resolution 608×608 in yolo-                   |    |

|           | v3-spp model                                                                                | 84 |

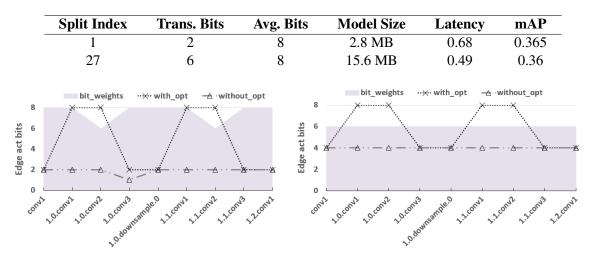

| Table 5.9 | Numerical values for bit assignment of Fig. 5.7. Left: activation bits are traded           |    |

|           | off for weight bits, and right: vice versa.                                                 | 84 |

# **List of Figures**

| Figure 1.1  | The field of artificial intelligence [7]                                           | 2  |

|-------------|------------------------------------------------------------------------------------|----|

| Figure 1.2  | An example of issuing ticket with license plate detection and various meth-        |    |

|             | ods of deployment. The highlighted region shows execution in edge device           | 3  |

| Figure 1.3  | Dissertation Organization                                                          | 8  |

| Figure 1.4  | Spatial vs. Low-rank Convolutions. $F^2 \ll K \ll K \ast F^2$ . In Depth-separable |    |

|             | layer, majority of MAC is allocated to PT, and DP is memory bound due to           |    |

|             | $F^2$ . Typically $F^2 = 9$ and 1, whereas $C, K \in [1, 1000]$ .                  | 9  |

| Figure 1.5  | LR-CONVs vs CONVs                                                                  | 9  |

| Figure 1.6  | Illustration of per-layer schedule and mapping of a CONV layer on a                |    |

|             | hardware accelerator                                                               | 10 |

| Figure 1.7  | Accelerator Overview                                                               | 12 |

| Figure 1.8  | An example cross layer schedule for $PT \rightarrow DP \rightarrow PT$ layer       | 13 |

| Figure 1.9  | X-Layer Overview. DP= Depthwise, PT= Pointwise                                     | 14 |

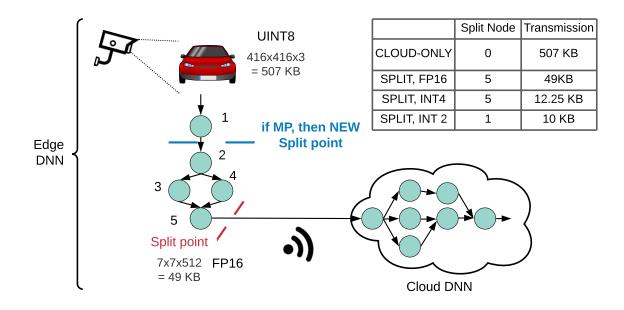

| Figure 1.10 | Transmission cost comparison between CLOUD-ONLY and SPLIT. MP:                     |    |

|             | Mixed precision                                                                    | 17 |

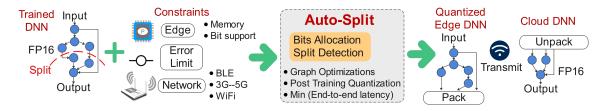

| Figure 1.11 | AUTO-SPLIT overview: inputs are a trained DNN and the constraints, and             |    |

|             | outputs are optimal split and bit-widths                                           | 20 |

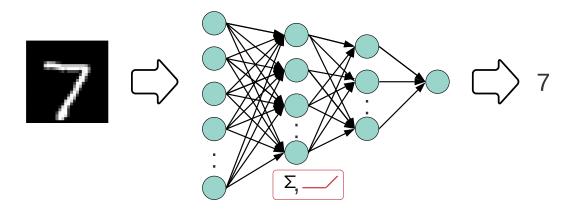

| Figure 2.1  | DNN example of digit classification from MNIST dataset                             | 22 |

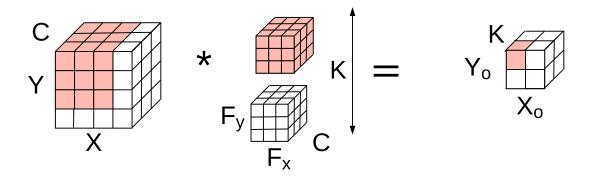

| Figure 2.2  | Spatial Convolution Example                                                        | 23 |

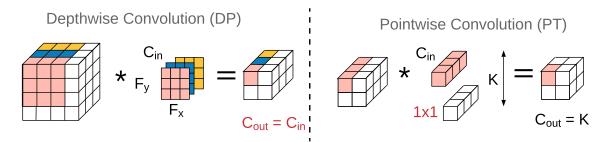

| Figure 2.3  | Depthwise and Pointwise Convolution Example                                        | 24 |

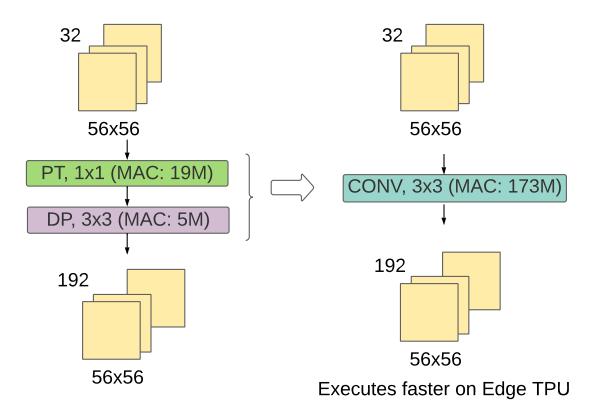

| Figure 2.4  | MAC requirement for CONV vs depth separable(DP + PT) layers [5].                   |    |

|             | CONV executes faster on edge TPU due to $\simeq 3X$ more effective hardware        |    |

|             | utilization                                                                        | 25 |

| Figure 2.5  | Advances in DNN Algorithm designs                                                  | 26 |

| Figure 2.6  | Asymmetric vs Symmetric Quantization methods                                       | 29 |

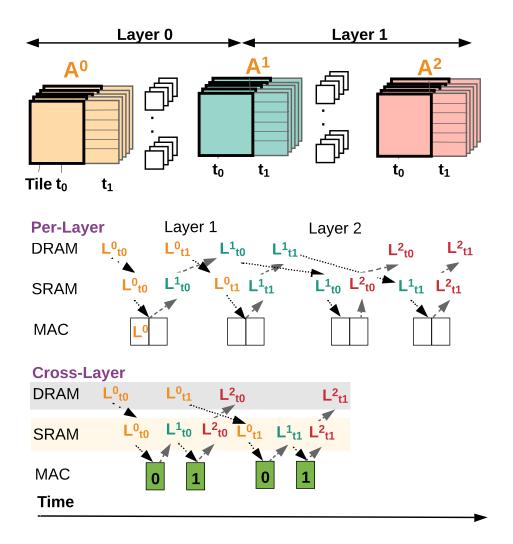

| Figure 2.7  | Per-Layer and a Cross-Layer dataflow                                               | 32 |

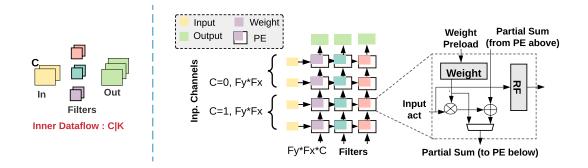

| Figure 2.8  | Mapping of ClK dataflow                                                            | 33 |

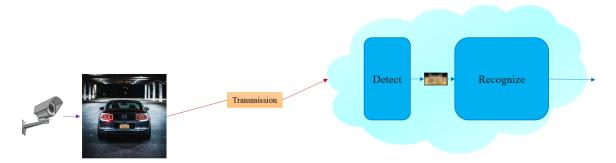

| Figure 2.9  | Cloud-Only: Data is transmitted entirely to the cloud where inference is           |    |

|             | executed                                                                           | 34 |

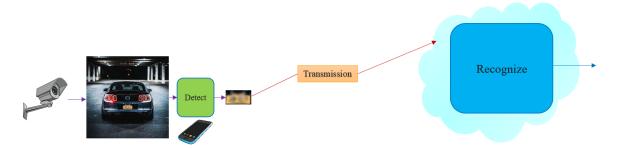

| Figure 2.10  | Cascading approach: The example here is license plate recognition where                                                    |     |

|--------------|----------------------------------------------------------------------------------------------------------------------------|-----|

|              | detection runs on device as it needs less computations. The recognition                                                    |     |

|              | however requires heavier processing and runs on the cloud                                                                  | 35  |

| Figure 2.11  | Multi-exit model: Some features are extracted from the data, and based                                                     |     |

|              | on some criteria it is decided if the rest of the model runs on edge or needs                                              |     |

|              | to be transferred to the cloud. Generally, the edge and cloud side models                                                  |     |

|              | perform the same task, but they have a different size and therefore different                                              |     |

|              | accuracy. The decision criteria tries to evaluate if running the model on                                                  |     |

|              | edge can result in an acceptable accuracy, otherwise, the features data are                                                |     |

|              | transmitted to the cloud.                                                                                                  | 35  |

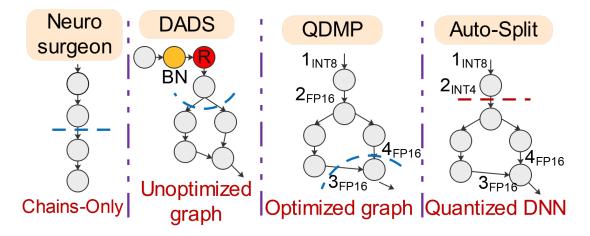

| Figure 2.12  | Different methods of edge-cloud partitioning. Neurosurgeon [58]: handles                                                   |     |

|              | chains only. DADS [49]: min-cut on un-optimized DNN. QDMP [119]:                                                           |     |

|              | min-cut on optimized DNN. All three use Float models. AUTO-SPLIT                                                           |     |

|              | explores new search space with joint mixed-precision quantization of edge                                                  |     |

|              | and split point identification. BN: Batch norm, R: Relu                                                                    | 37  |

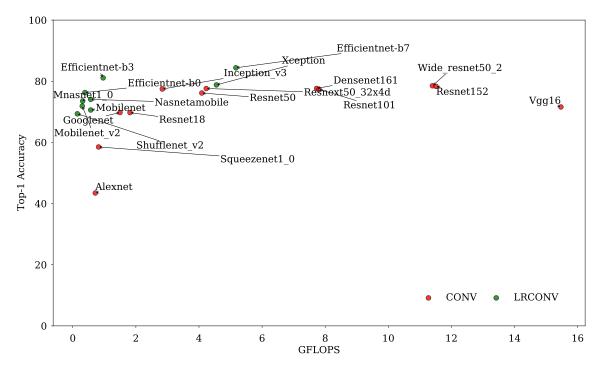

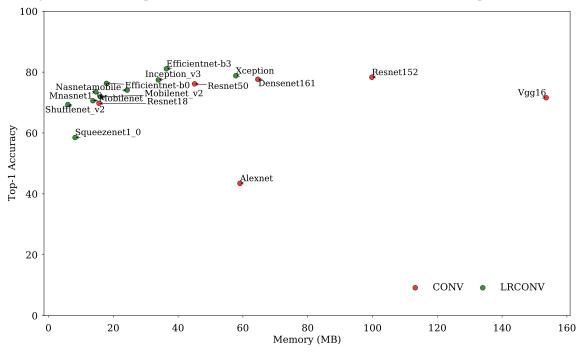

| Figure 3.1   | MAC requirement for LR-CONV vs CONV dominated DNNs. Top-Left is                                                            |     |

|              | best                                                                                                                       | 39  |

| Figure 3.2   | Memory requirement for LR-CONV vs CONV dominated DNNs. Top-Left                                                            |     |

|              | is best                                                                                                                    | 39  |

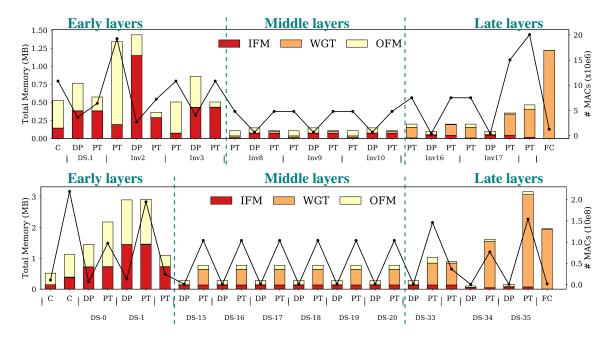

| Figure 3.3   | Mobilnet_v2(top) and Xception(bottom): Breakdown of #MACs (line) and                                                       |     |

|              | memory required per layer (bars). Inverted residual (Inv) : $PT \rightarrow DP \rightarrow PT$ .                           |     |

|              | Depth-separable (DS): (DP $\rightarrow$ PT). The numbers suggest layer index, e.g.,                                        |     |

|              | Inv3 implies third inverted residual layer                                                                                 | 41  |

| Figure 3.4   | Illustration of the PT layer in a cross-layer                                                                              | 42  |

| Figure 3.5   | Cross-layer for CONVs vs LR-CONVs.                                                                                         | 43  |

| Figure 3.6   | CONV vs DP layer ClK mapping strategy                                                                                      | 45  |

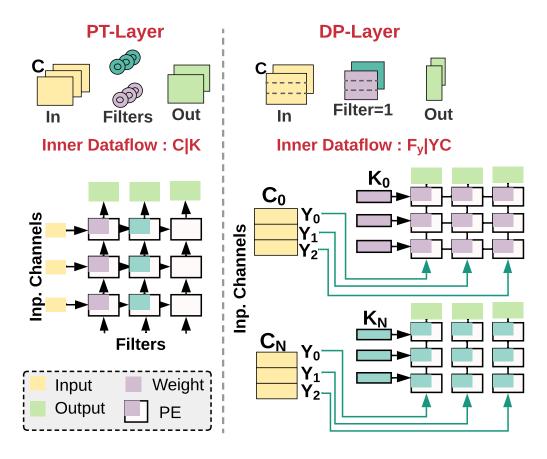

| Figure 3.7   | Mapping LR-CONVs to hardware. Left shows $C K$ dataflow for PT layer                                                       |     |

|              | $(F_x = F_y = 1)$ . Right shows $F_y   Y$ with channel replication for DP layers                                           | 46  |

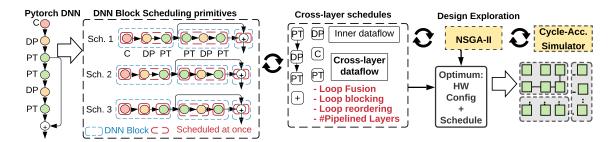

| Figure 3.8   | X-Layer tool flow. C= CONV layers                                                                                          | 48  |

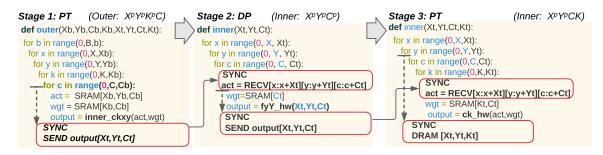

| Figure 3.9   | A cross-layer dataflow example for a an Inverted Residual Layer. The cross-layer dataflow is called $X^{p}Y^{p}K^{p}C-3$ . | 48  |

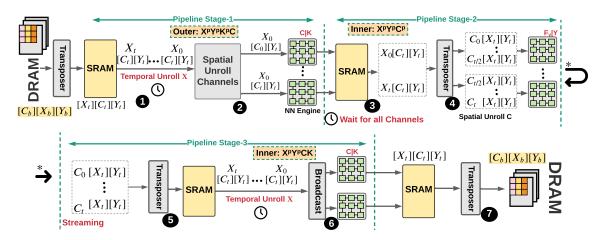

| Figure 3.10  | The Execution Model of a cross-layer Inverse Residual Layer. Please read                                                   | -10 |

| 1 iguie 5.10 | in color.                                                                                                                  | 48  |

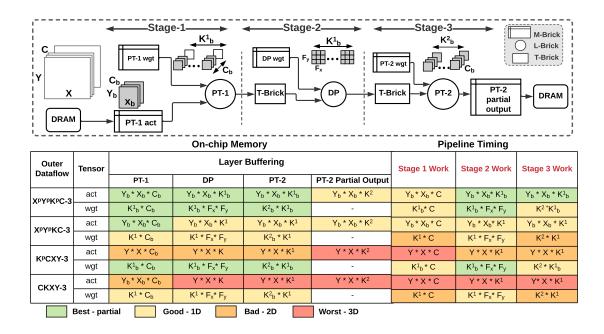

| Figure 3.11  | On chip memory requirement for various Cross-Layer dataflows, for Inverse                                                  | -10 |

| 1 iguie 5.11 | Residual Layers. Layer Buffering indicates on-chip memory required in                                                      |     |

|              | each pipeline stage. Pipeline Timing indicate the size of activations required in                                          |     |

|              | to be computed in each pipeline stage1D, -2D, -3D implies the number of                                                    |     |

|              | complete loop dimensions.                                                                                                  | 53  |

|              | comprete roop unitensions,                                                                                                 | 55  |

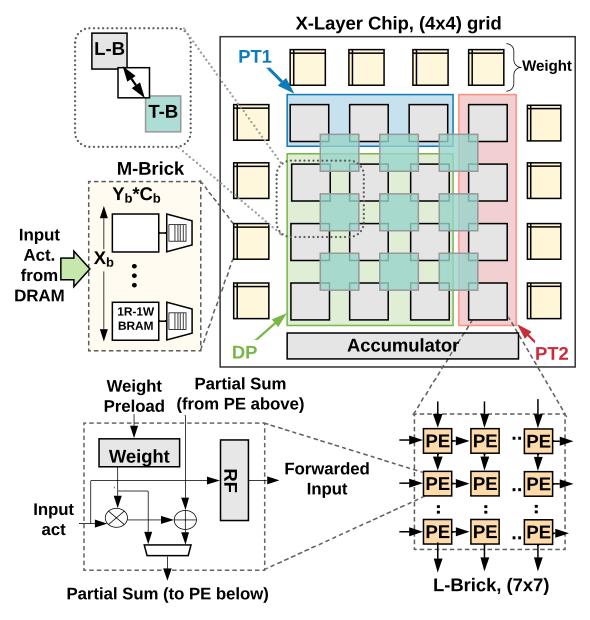

| Figure 4.1  | The grid-style architecture of X-Layer                                                   | 55 |

|-------------|------------------------------------------------------------------------------------------|----|

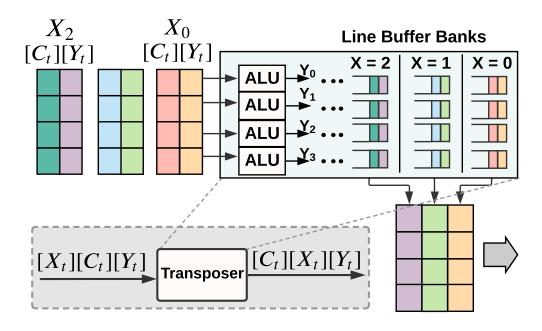

| Figure 4.2  | Overview of T-Brick (trasposer)                                                          | 56 |

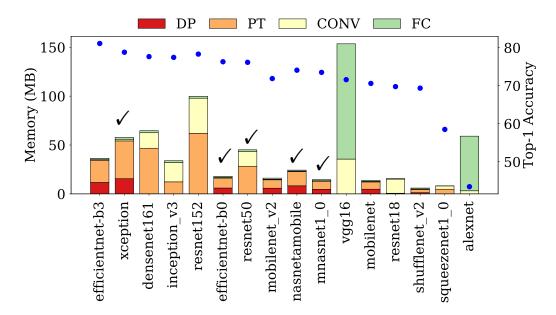

| Figure 4.3  | Total Memory used for LR-CONVs vs CONVs and FC. Benchmarks are                           |    |

|             | sorted in order of Top-1 accuracy shown as points on Second Y-axis. $\checkmark$ :       |    |

|             | Suite we study.                                                                          | 57 |

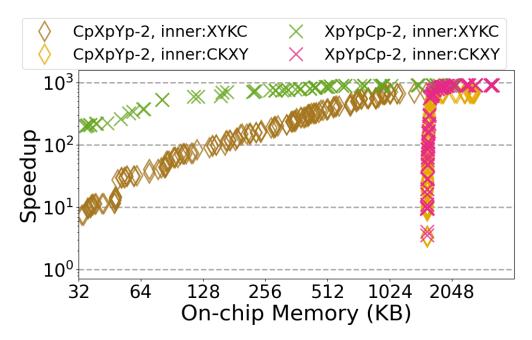

| Figure 4.4  | Cross-layer for Xception. 2-stage pipelines.                                             | 58 |

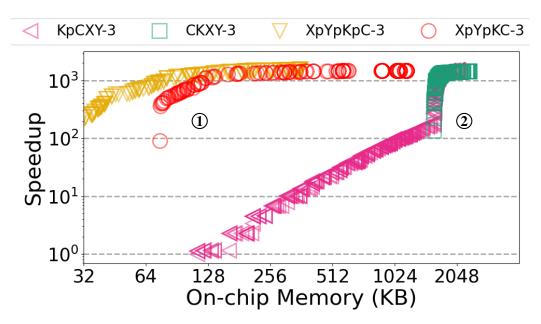

| Figure 4.5  | Cross-layer for Mobilenet_v2. 3-stage pipelines                                          | 59 |

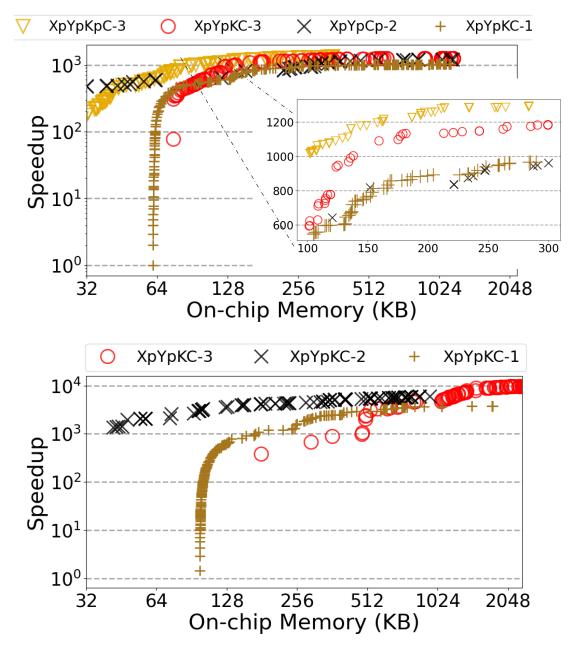

| Figure 4.6  | Mobilenet_v2(Top) and Resnet-50(Bottom).                                                 | 60 |

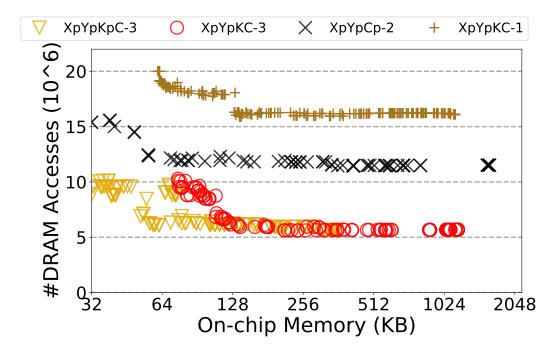

| Figure 4.7  | Mobilenet_v2, scatter plot comparing Million DRAM accesses (Y-axis)                      |    |

|             | with On-chip Memory (X-axis) for different pipeline depths                               | 61 |

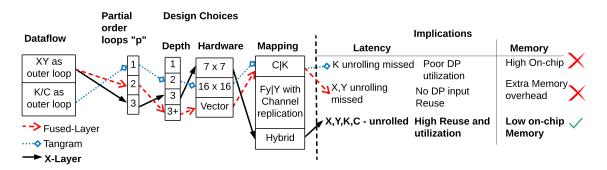

| Figure 4.8  | Design choices and their implications in prior cross-layer architectures                 | 63 |

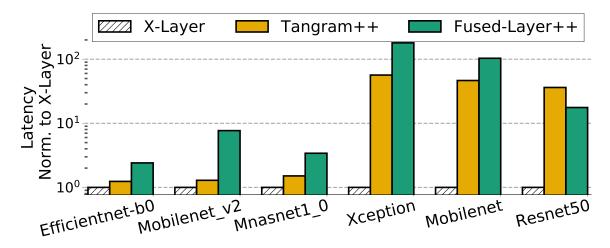

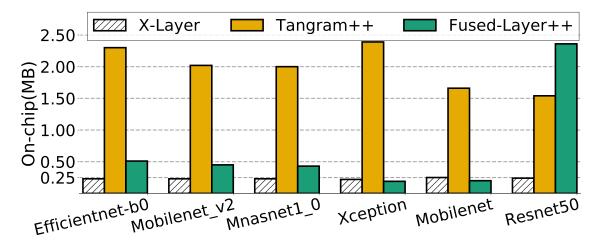

| Figure 4.9  | End-to-End Latency. X-Layer vs. Tangram [36] and Fused-layer [10]. X-                    |    |

|             | Layer=1. Lower is better                                                                 | 64 |

| Figure 4.10 | On-chip Memory used. X-Layer=1. Lower is better                                          | 64 |

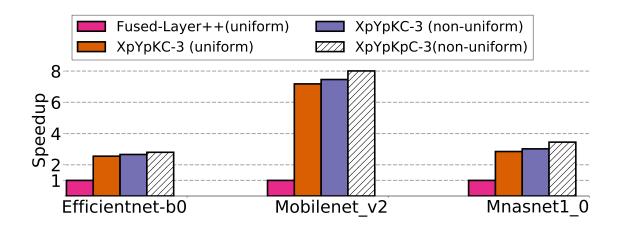

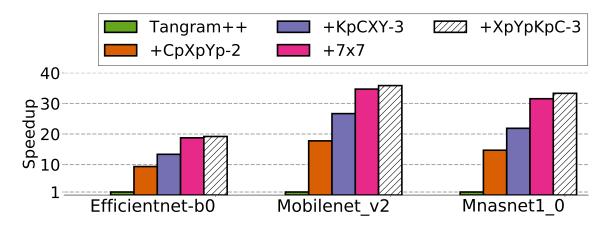

| Figure 4.11 | Speed up breakdown compared to Fused-Layer++ for inverted residual                       |    |

| -           | benchmarks. Higher is better.                                                            | 65 |

| Figure 4.12 | Speed up breakdown compared to Tangram++. Higher is better                               | 65 |

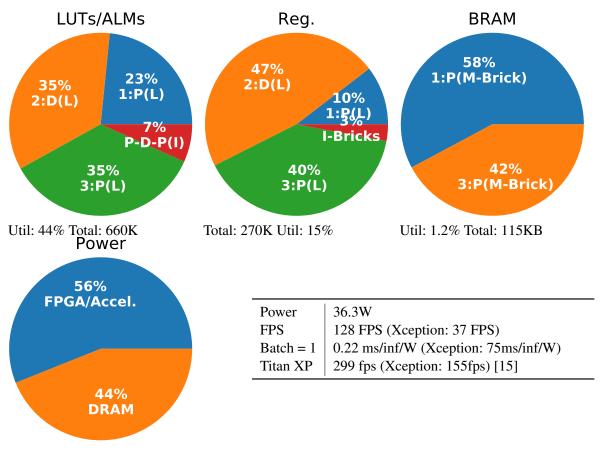

| Figure 4.13 | Hardware Statistics                                                                      | 66 |

| C           |                                                                                          |    |

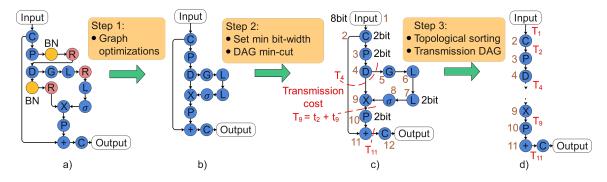

| Figure 5.1  | An example of graph processing and the steps required to calculate the                   |    |

|             | list of potential split points. 4a) is an example of inverted residual layer             |    |

|             | with squeeze & excitation from MnasNet. Step1: DAG optimizations for                     |    |

|             | inference such as batchnorm folding and activation fusion. Step2: Set $\mathbf{b}_i^a =$ |    |

|             | $b_{min}$ for all activations, create weighted graph, and find the min-cut between       |    |

|             | sub graphs. Step 3: Apply topological sorting to create transmission DAG                 |    |

|             | where nodes are layers and edges are transmission costs. C:Convolution                   |    |

|             | P:Pointwise convolution, D:Depthwise convolution, L:Linear, G:Global                     |    |

|             | pool, <i>BN</i> :Batch norm, <i>R</i> :Relu.                                             | 69 |

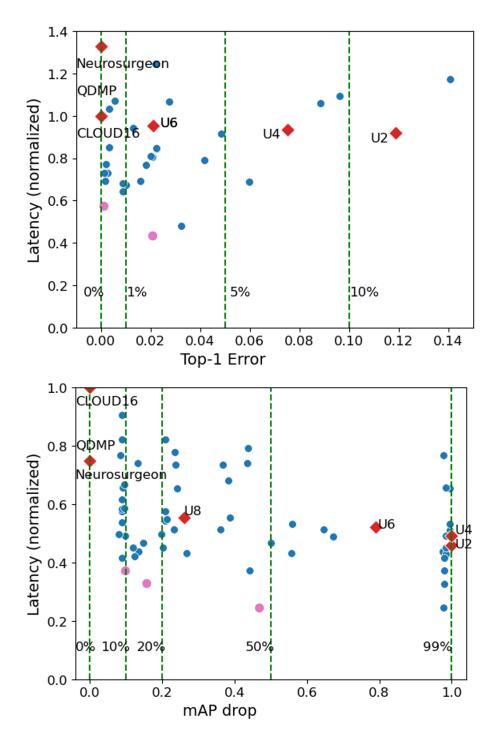

| Figure 5.2  | Accuracy vs latency trade-off for ResNet-50 (top) and Yolo-v3 (bottom),                  |    |

|             | Towards origin is better. U2, U4, U6 and U8 indicate uniform quantization                |    |

|             | (EDGE-ONLY). CLOUD16 indicates FP16 configuration (CLOUD-ONLY).                          |    |

|             | The green lines show error threshold which a user can set. AUTO-SPLIT                    |    |

|             | can provide different solutions based on different Error thresholds                      | 75 |

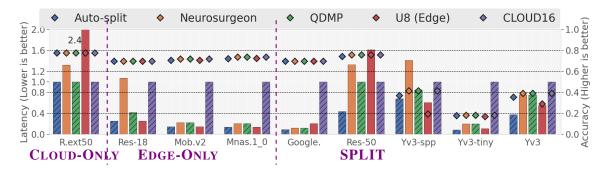

| Figure 5.3  | Latency (bars) vs Accuracy (points) comparison. Depending on the device                  |    |

|             | constraints, DNN architecture, and network latency, the optimal solution                 |    |

|             | can be achieved from CLOUD-ONLY, EDGE-ONLY, or SPLIT. The user                           |    |

|             | error threshold for image classification workloads is 5%, and for object                 |    |

|             | detection workloads is 10%.                                                              | 76 |

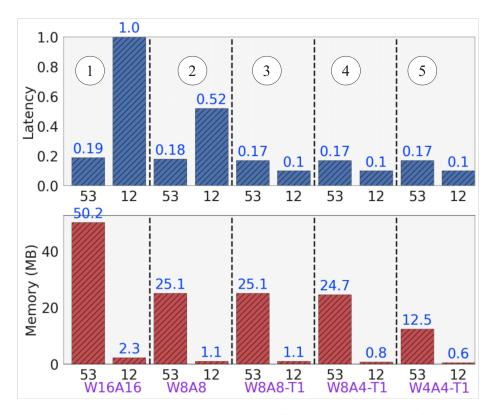

| Figure 5.4 ResNet-50 latency & memory for AUTO-SPLIT (split @12) and QDMI |                                                                                              |    |

|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----|

|                                                                           | (split @53). W8A8-T1 implies weight, activation, and transmission bit-                       |    |

|                                                                           | widths of 8, 8, and 1, respectively. Transmission cost at split 53 is $\simeq 3 \times$ less |    |

|                                                                           | than split 12                                                                                | 77 |

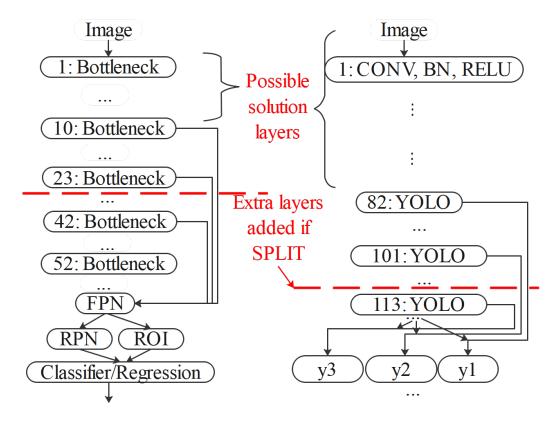

| Figure 5.5                                                                | Split layers for FasterRCNN (left) and Yolov3 (right)                                        | 81 |

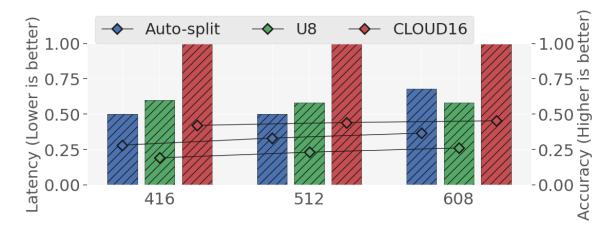

| Figure 5.6                                                                | Yolo-v3-spp latency (bars) and mAP(line) for different image resolutions.                    | 83 |

| Figure 5.7                                                                | A demonstration of bit-width selection for activations w/ and w/o the                        |    |

|                                                                           | optimization of $(5.9)$ . The shaded region shows the bit-width selection for                |    |

|                                                                           | weights in each scenario. Left: activation bits are traded off for weight bits,              |    |

|                                                                           | and right: vice versa.                                                                       | 84 |

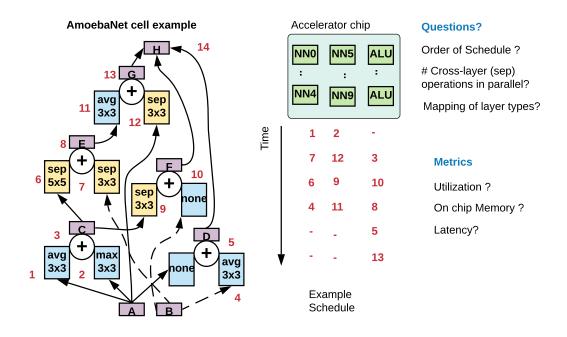

| Figure 6.1                                                                | Scheduling DNN layers for NAS based DNN. sep= Depth-separable layer                          | 87 |

# Abbreviation

AI Artificial Intelligence ASR Automatic Speech Recognition CLOUD-ONLY Cloud Only Approach CNN Convolutional Neural Network **CONV** Spatial Convolution cross-layer Cross-Layer Dataflow **DNN** Deep Neural Network **DP** Depthwise Convolution **EDGE-ONLY** Edge Only Approach FC Fully-Connected Layer HAR Human Activity Recognition IoT Internet of Things LR-CONV Low-rank Convolution LUT Look up Table MAC Multiply Accumulate Operation ML Machine Learning **MP** Mixed Precision Quantization NAS Neural Architecture Search **OCR** Optical Character Recognition PE Processing Element

per-layer Per-Layer Dataflow

- **PT** Pointwise Convolution

- PTQ Post Training Quantization

- **QAT** Quantization Aware Training

- **RNN** Recurrent Neural Network

- SPLIT Split Approach. Partial execution on edge device and partial on cloud device

- WCET Worst Case Execution Time

## **Chapter 1**

## Introduction

DEEP LEARNING [6] is a sub branch of Artificial Intelligence (AI) that imitates the workings of the human brain in processing data and creating patterns for use in decision making. Deep-learning architectures such as Deep Neural Network (DNN), deep belief networks, graph neural networks, Recurrent Neural Network (RNN) and Convolutional Neural Network (CNN) have been applied to fields including computer vision, speech recognition, natural language processing, machine translation, bioinformatics, drug design, medical image analysis, material inspection and board game programs, where they have produced results comparable to and in some cases surpassing human expert performance. In 2012, Alexnet [61], a deep learning algorithm became the winner of the ImageNet challenge [60] beating all traditional handcrafted computer vision algorithms. Since then deep learning algorithms have become the de facto for such applications. Deep learning (Figure 1.1) is a subset of Machine Learning (ML) which comes under the large umbrella of AI. ML is the class of algorithms in which the computers have the ability to learn without being explicitly programmed. The AI refers to the theory and development of algorithms that are able to perform tasks normally requiring human intelligence.

Deep Neural Networks use multiple layers to progressively extract higher-level features from the raw input. For example, in image processing, lower layers may identify edges, while higher layers may identify the concepts relevant to a human such as digits or letters or faces. A DNN has a training phase and an inference phase. Typically, during the training phase, the DNN algorithm learns the task at hand by going through many examples from an example dataset. The DNN model learns by minimizing the error between model prediction and ground truth with an algorithm called backpropagation. The Backpropagation updates the model parameters during the training phase. Once the accuracy is sufficiently high, the DNN algorithm stops learning and runs in the inference stage. In the inference stage, the DNN model is frozen i.e, the model parameters are not updated anymore (no backpropagation) and deployed to a target platform.

DNN algorithms are making exponential advances and have been seeping into many applications. A large number of applications such as Human Activity Recognition (HAR), object detection, face recognition, wearable devices, anti-spoofing, Optical Character Recognition (OCR), Automatic Speech Recognition (ASR), authorization entry, and text prediction require AI application processing

Figure 1.1: The field of artificial intelligence [7]

at the source of the data. This is called EDGE COMPUTING or popularly known as the Internet of Things (IoT). The Edge devices can refer to small devices with limited computing capability such as cameras, phones, microcontrollers and includes any device that collects the data at the source and does the front-end of data processing. The IoT market is estimated to be USD 82.4 Billion in 2020 and is estimated to grow at a compounded annual growth rate of 23% from 2020 to 2028 [8].

We now explain existing solutions for the deployment of AI applications on the edge devices in §1.1. An AI application can choose to i) execute everything on the edge device (EDGE-ONLY), ii) send input data to the cloud for DNN processing on the cloud (CLOUD-ONLY, and iii) Choose to split the AI application to partially execute on the edge and partially on the cloud device (SPLIT). §1.2 discusses the contributions made in this thesis and resulting publications followed by §1.3 which discusses the thesis organization. §1.4 discusses the challenges of deploying Edge Only Approach (EDGE-ONLY) for emerging DNNs based on Low-rank Convolution (LR-CONV). Next in §1.5, we explore the ideas to speed up SPLIT solutions for latency critical applications. We leverage mixed precision post training quantization for the partial DNN executing on the edge device.

### **1.1** AI application pipeline

The DNN's high accuracy comes at the expense of high computational and memory requirements for both the training and the inference phase of deep learning. The efficiency of DNNs during the inference phase is especially important since training occurs once and inference occurs many times. This section explains various approaches to deploy DNNs for inference on edge devices. We also discuss various constraints that lead to the selection of these approaches.

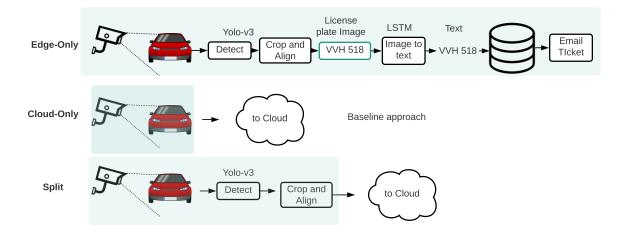

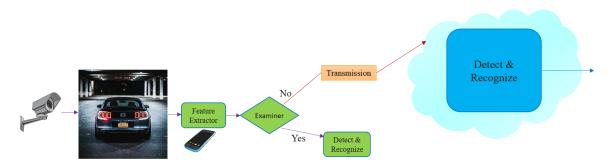

The DNN deployment on the edge is challenging as the data is collected on the edge device which is generally resource-constrained and may not be able to meet the computation and memory requirements of the DNN execution. Existing solutions can be broadly divided into EDGE-ONLY and DISTRIBUTED. In EDGE-ONLY approach the DNN is executed end to end on the edge device itself, whereas in DISTRIBUTED approach a part of the data is executed on the edge device and the rest is sent to the cloud for further processing. The DISTRIBUTED approach can be further divided into i) CLOUD-ONLY and ii) SPLIT solutions. As the name suggests, in CLOUD-ONLY, the input data is directly sent to the cloud for DNN processing. In the Split solution, the DNN is split into two DNNs. The first half of the DNN executes on the edge DNN and the rest is executed on the cloud. Figure 1.2 shows an example of an AI pipeline of license plate detection. First, the camera takes an image of the license plate, then the image is processed and sent to a DNN (Yolo-v3 head) for object detection. The object detection detects the license plate and crops it from the original image. The cropped license plate is then sent to a large recognition DNN (an LSTM) which converts the license plate image into text. The license plate text is the endpoint of DNN algorithms, but in an end to end application, it requires further processing. For example, the license plate text could be utilized to search into a database and issue a ticket to the driver for speeding. The example shows the deployment of the AI pipeline with EDGE-ONLY, CLOUD-ONLY and SPLIT approaches. The choice of deployment approach depends on the operating and application constraints. For example, the EDGE-ONLY approach requires the AI application to fit on the device memory. The CLOUD-ONLY approach requires the network to be stable, and have relatively high bandwidth compared to the input data being transmitted. The SPLIT approach requires a preprocessing stage to split the AI application into the edge task and the cloud task. It also requires AI applications to contain output activation layers where the transmission cost of activations at the split is significantly lower than the input data. Next, we discuss the operating and application constraints which are a key factor in deciding the choice of deployment.

Figure 1.2: An example of issuing ticket with license plate detection and various methods of deployment. The highlighted region shows execution in edge device

|                         | Device: memory, compute      |

|-------------------------|------------------------------|

| Operating Constraints   | Network: Speed, Stability    |

|                         | Latency/Throughput, and Cost |

| Application Requirement | Accuracy                     |

Table 1.1: Metrics for Operating constraints and Application requirements

#### Solution trade-offs based on Operating and Application constraints.

The choice of deployment between EDGE-ONLY, CLOUD-ONLY and SPLIT is determined by operating and application constraints. Table 1.1 shows some choices to consider for operating and application requirements. The operating constraints include factors such as device compute capability and available memory. The application requirements include metrics such as Latency, the DNN model accuracy and device cost. Other important metric is the accuracy of the application. We discuss the application requirements and how it affects the choice of deployment next.

**Latency:** Real-time inference is critical to many applications. For example, in the case of selfdriving cars, the vehicle needs to process the input from camera frames and take a decision within a minimum Worst Case Execution Time (WCET). For example, detecting a pedestrian on the street. Such applications need to use the EDGE-ONLY approach. Since, in a DISTRIBUTED approach, the network conditions can be unreliable such as network speed, stability, and availability of network in remote areas. Some applications may have stable network conditions but require low latency. Such applications would prefer a SPLIT solution, since, transmission cost of large input data to the cloud could be a bottleneck in CLOUD-ONLY approach.

**Accuracy:** An AI application may demand high accuracy. The DNN's high accuracy comes at the expense of high computational and memory requirements. High application accuracy implies larger models, which in turn requires higher processing power and memory. Thus it may not be possible to deploy an EDGE-ONLY solution in such cases. An extreme example of high accuracy is the text prediction models such as GPT-3 which requires up to 350GB memory and 175 Billion parameters. Such models are far beyond the capacity of edge devices and are run on clusters of GPUs. Such applications would deploy either a CLOUD-ONLY or a SPLIT solution.

The aim of the thesis is to enable efficient execution of DNN inference on edge devices especially for EDGE-ONLY and SPLIT approach.

**Challenges of EDGE-ONLY:** The EDGE-ONLY devices are limited by compute and memory requirements. In order to fit the DNN on edge device memory, many software optimizations are made to trade-off model accuracy with model size. Techniques such as i) model compression [13, 17, 24, 32, 32, 34, 56, 59, 105, 108, 116, 120, 124], ii) knowledge distillation, pruning and other hybrid techniques [23, 35, 47, 74, 83] and, iii) Neural Architecture Search (NAS) [68, 84, 98, 99, 108, 109, 112, 114, 126] are used to reduce the model size within the acceptable application constraints. The NAS methods

have led to many compact emerging DNNs with high accuracy and, low compute and memory requirements. These DNNs heavily employ LR-CONVs. An LR-CONV is a convolution which has one or more dimensions reduced compared to the standard convolution operation. For example, in a Pointwise Convolution (PT) layer, the filter height and width are reduced to  $1 \times 1$ . The LR-CONVs have low reuse within a layer. This leads to poor hardware utilization which exacerbates the latency problem in spite of having compact DNN with low Multiply Accumulate Operation (MAC) and memory requirement (see chapter 2, Figure 2.4). We explain the challenges of improving latency for EDGE-ONLY approach, especially for executing LR-CONVs in §1.4.

**Challenges of SPLIT:** When the AI applications are large and do not fit on the edge device, DISTRIBUTED approach has to be used. The SPLIT solutions can be up to  $1.6 \times$  faster than CLOUD-ONLY solutions and can be a good alternative to CLOUD-ONLY solutions for many AI applications. Existing SPLIT solutions can be categorized into cascaded models [117], multi-exit models [100] and graph based DNN splitting [49,58,119]. Only the existing graph based DNN splitting techniques are generic and can be applied to many applications but does not leverage model compression techniques such as quantization to further improve the latency of end to end application. We discuss it in detail in §1.5.

### **1.2 Dissertation Contribution**

To our knowledge, this thesis is the first to explore the design space of cross-layer dataflows for EDGE-ONLY solutions, and explore joint bit-width allocation along with split detection for SPLIT solutions. In this thesis we make two major contributions:

We propose X-Layer which is the first framework to systematically explore the design space of cross-layer dataflows. It supports i) partial order loops enabled by LR-CONVs, ii) variable pipeline depth, and iii) heterogeneous inner and outer dataflows. We propose novel cross-layer dataflows, X<sup>p</sup>Y<sup>p</sup>K<sup>p</sup>C-3 and X<sup>p</sup>Y<sup>p</sup>C<sup>p</sup>-2. They exploit partial order loops to maximize temporal reuse across layers and minimize the amount of on-chip SRAM. We also develop the X-Layer microarchitecture targeting cross-layer dataflows. The primary novelty is Multi-Input Multi-Output (MIMO) queues that support the multitude of data transformations in heterogeneous dataflows. We navigate exponentially large design space (≃ millions) of cross-layer dataflows and evaluate six state-of-the-art DNNs (Mobilenet, Xception, Resnet-50, Mobilenet\_v2, Mnasnet1\_0, EfficientNet-b0). Compared to prior state-of-the-art [10, 36], X-Layer improves performance by 7.8× and 16.6× using only 256KB of on-chip SRAM.

[10, 36] requires up to 2.4 MB of SRAM. X-Layer also demonstrates a wider performance band for varied SRAM configurations (32KB – 2MB) whereas the performance drops steeply for prior state-of-the-art as the on-chip SRAM is reduced.

• We propose AUTO-SPLIT, an algorithm to minimize end-to-end latency by jointly searching for a split point (to divide the DNN into edge and cloud devices), as well as searching for optimal bit-widths for edge DNN layers (under pre-specified device memory constraints, network latency, and an accuracy threshold). We demonstrate that by applying quantization on the edge DNN, AUTO-SPLIT reduces the overall latency by 20–80% compared to the state of the art network partitioning algorithms. AUTO-SPLIT also reduces model size requirements on the edge DNN by 43 – 95 % compared to Uniform 4-bit quantized networks. To demonstrate the generality of our method, we study six image classification networks and three object detection networks, at different model sizes/architecture, and input resolutions.

#### **Publications**

This dissertation includes the works published in two peer-reviewed conferences. These publications are listed below :-

- PACT 2021 X-Layer: Building Composable Pipelined Dataflows for Low-Rank Convolutions. This work is published at the 30th International Conference on Parallel Architectures and Compilation Techniques with co-authors Reza Hojabr, Ahmad Khonsari, and Arrvindh Shriraman.

- I was the main contributor of the X-layer framework including the design, development and evaluation of the work. The X-layer scheduler (TB-Scheduler in the repository) extracts the layer information from the PyTorch DNN model and explores all cross-layer dataflows up to a pipeline depth of three. The latency calculation is done by a cycleaccurate DNN accelerator. The optimal loop blocking and loop tiling parameters are searched with the help of NSGA-II, a genetic algorithm.

- Reza and I came up with the idea of the MIMO queues to realize T-Bricks shown in §4.1.

He then developed the RTL for the X-Layer microarchitecture to evaluate FPGA results (§4.3.2).

- KDD 2021 Auto-Split: A General Framework of Collaborative Edge-Cloud AI. This work is published at the Proceedings of the 27th ACM SIGKDD International Conference on Knowledge Discovery and Data Mining with co-authors Amin Banitalebi-Dehkordi, Jian Pei, Fei Xia, Lanjun Wang, and Yong Zhang. Amin and I are the first authors of this paper.

- I was the main contributor of the AUTO-SPLIT framework, including the idea, algorithm design, framework development, and evaluation of the work. The AUTO-SPLIT framework takes a DNN model in PyTorch and i) collects statistics for each layer to quantize later, ii) applies graph pre-processing and extracts the DNN graph information to collect layer dependencies to find the min-cut in the split, iii) Implements Auto-split algorithm

to find the split and allocate bit-widths to the edge DNN, iv) applies post-training quantization, v) and explores the trade-off in accuracy vs Latency. The Latency estimates are calculated with the help of a mixed-precision edge device cycle-accurate simulator. I also developed the video demo for the face detection application in TensorFlow which i) explores the activation compression techniques, and ii) explores RPC protocols and socket programming for activation transmission from edge device to cloud device.

Amin did the evaluation and development of the license plate detection application shown in §5.3.5. He also helped with writing the paper and filing for the patent.

Chapter 7 explains other contributions made by me which are not included in the thesis. It also includes my third work as the first author – **NACHOS: Software-Driven Hardware-Assisted Memory Disambiguation for Accelerators** which was published in the 2018 IEEE International Symposium on High Performance Computer Architecture, **HPCA 2018** with co-authors Arrvindh Shriraman, Snehasish Kumar, and Nick Sumner.

- I was the main contributor of NACHOS, including the idea, design, development and evaluation of the work. I developed an LLVM Alias analysis framework to replace Load Store queues for memory disambiguation of acceleratable hot paths in SPEC2K, SPEC2K6, and PARSEC workloads. This work is available on https://github.com/sfu-arch/Nachos.

- In this work I leveraged Snehasish's framework NEEDLE for extracting acceleratable regions from the workloads.

### **1.3** Dissertation Organization

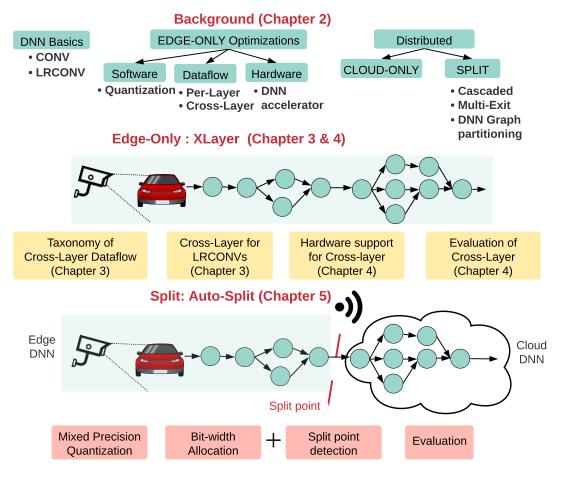

Figure 1.3 summarizes the dissertation organization. Chapter 2 provides the background. First we start by explaining the differences between CONV and LR-CONVs, followed by optimizations for DNN model and dataflow for EDGE-ONLY solutions. Then we provide the background for existing SPLIT solutions.

This thesis discusses two of my works X-Layer and AUTO-SPLIT. Chapter 3 and 4 discuss X-Layer which explores the EDGE-ONLY approach. Chapter 5 discusses AUTO-SPLIT which explores the SPLIT approach. In chapter 3, we provide a taxonomy of cross-layer dataflows and explain the cross-layer pipelining for LR-CONV based DNNs. Chapter 4 provides the DNN hardware accelerator microarchitecture changes required to support all cross-layer dataflows. We then present a comprehensive evaluation of cross-layer dataflows and compare them against the state of the art dataflows.

Chapter 5 provides a distributed approach to jointly detect split point to generate an edge DNN and a cloud DNN, and allocate mixed-precision bit-widths for the edge DNN. The edge DNN executes on the edge device and the cloud DNN executes on the cloud device. Chapter 6 provides a

Figure 1.3: Dissertation Organization

summary of the thesis and directions for future work. Chapter 7 explains other contributions made by me which were published in peer-reviewed conferences.

### **1.4 Improving latency for Edge-Only Approach**

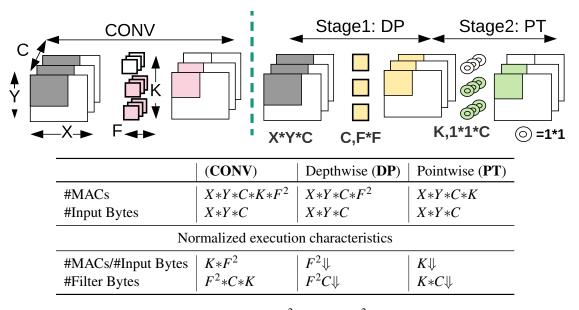

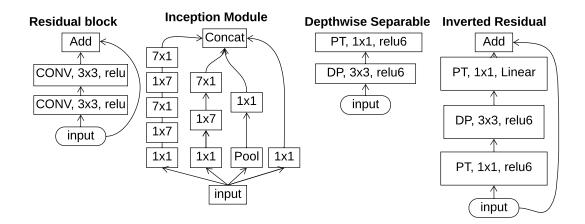

The majority of prior DNN accelerators [1, 19] and dataflow toolflows [62, 115] have targeted spatial convolutions (CONV). However, state-of-the-art networks (see Imagenet leaderboard [4]) employ low rank convolutions (LR-CONVs) for their workhorse layers e.g., AmoebaNet [84], RandWire [112], EfficientNet [99], Mnasnet [98], NasNet [127] and PNasNet [68]. LR-CONV networks have only one or two layers of CONV and spend more than 95% of the time in LR-CONVs. Figure 1.4 illustrates a depth-separable layer commonly used in-lieu of CONVs. An LR-CONV is any convolution that has one or more dimensions reduced compared to CONV. For example, a depthwise convolution (DP) has *Filters*=1. Similarly, a pointwise convolutions (PT) has filter height and width  $=1 \times 1$ . These LR-CONVs are aggregated to create many composite layers such as depthwise-separable and inverted residual layers in emerging DNNs.

Figure 1.4: Spatial vs. Low-rank Convolutions.  $F^2 \ll K \ll K \ast F^2$ . In Depth-separable layer, majority of MAC is allocated to PT, and DP is memory bound due to  $F^2$ . Typically  $F^2=9$  and 1, whereas  $C, K \in [1, 1000]$ .

Given the same input activation of size  $X \times Y \times C$ , the arithmetic intensity of a CONV layer is  $K \times F^2$ . A depth separable layer that can replace a CONV layer has an arithmetic intensity of only  $F^2+K$ . The DP has " $F^2$ " arithmetic intensity and the PT has "K" arithmetic intensity. In DNNs the order of  $F^2 \simeq 9$ , whereas the order of  $C, K \in [1,1000]$ . Thus the depth separable layer,  $DP \rightarrow PT$  combined has much less arithmetic intensity compared to a CONV layer. Similarly, the memory required for weights/filters is also much less compared to the CONV layer.

Figure 1.5: LR-CONVs vs CONVs.

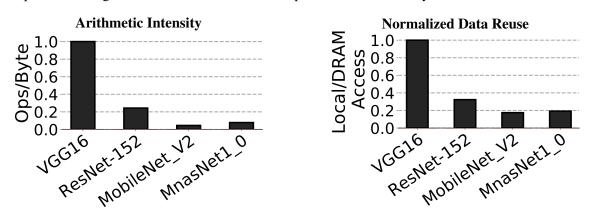

Figure 1.5 compares the Arithmetic Intensity for LR-CONV and CONV. We find that DNNs with LR-CONVs (Mnasnet1\_0 and Mobilenet\_v2) have  $10 \times 10 \times 10 \times 10$  and  $5.6 \times 10^{-10} \times 10^{-10}$  and

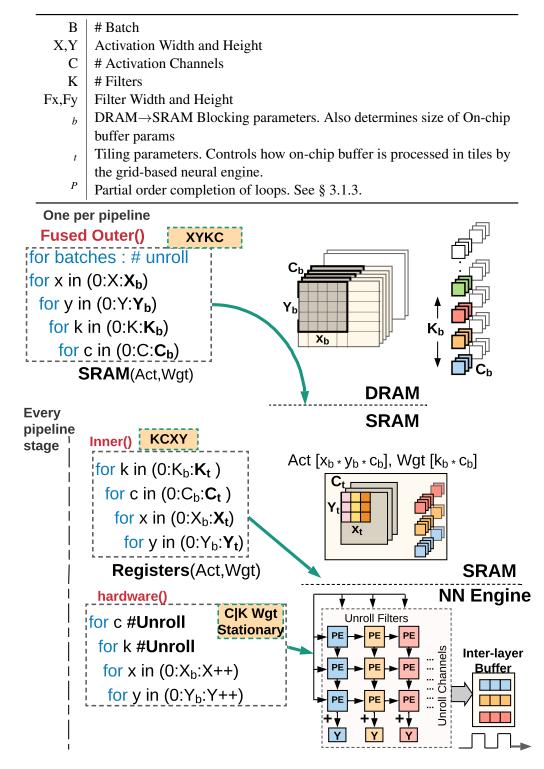

```

В

# Batch

X.Y

Activation Width and Height

С

# Activation Channels

# Filters

Κ

Filter Width and Height

Fx,Fy

DRAM-SRAM Blocking parameters. Also determines size of On-chip buffer

b

params

Tiling parameters. Controls how on-chip buffer is processed in tiles by the

t

grid-based neural engine.

1

# Outer dataflow: by compiler

2

def outer_xykc():

3

for b in range(0,B,Bb):

4

for x in range(0,X,Xb):

5

for y in range(0,Y,Yb):

6

for k in range(0,K,Kb):

7

for c in range(0,C,Cb):

8

act=load_act_onchip(Xb,Yb,Cb)

9

wgt = load_wgt_onchip(Kb,Cb)

10

inner_ck(act,wgt)

11

12

# Inner dataflow: in hardware

13

# (C|K) dataflow

14

def inner_ckxy(): # loads tile

15

for c in range(0,Cb,Ct): #Tile

16

for k in range(0,Kb,Kt): #Tile

17

for x in range(0,Xb,Xt): #Tile

18

for y in range(0,Yb, Yt): #Tile

19

act_tile = \setminus

20

act[x:x+Xt][y:y+Yt][c:c+Ct]

21

wqt_tile = wqt[k,k+Kt][c:c+Ct]

22

conv hw ck(act tile, wqt tile)

23

24

# conv2d: by MAC Units

25

def conv_hw_ck(act_tile,wgt_tile):

26

for c in range(0,Cb,Ct): #unroll

27

for k in range(0,Kb,Kt): #unroll

28

for x in range(0,Xb,Fx): #unroll

29

for y in range(0,Yb,Fy): #unroll

30

conv(act_tile,wgt_tile)

```

Figure 1.6: Illustration of per-layer schedule and mapping of a CONV layer on a hardware accelerator

#### **Per-Layer dataflow**

The Dataflow refers to the scheduling and ordering of the different loops in a DNN. The Baseline DNN accelerators seek to exploit parallelism and reuse in multiple loop dimensions by scheduling

each CONV [1, 19] (per-layer dataflow) independently. They focus on improving the per-layer locality and load data in tiles from DRAM [62, 79, 115]. However, in per-layer, the output of each layer is flushed back to the DRAM and re-fetched by the next layer. We show that state-of-the-art per-layer exhibit low-performance since they seek to exploit per-layer locality, which LR-CONVs do not possess.

Figure 1.6 shows an example dataflow schedule of a CONV layer as used in various baseline hardware accelerators. A CONV algorithm has seven loops comprising of  $b,X,Y,K,C,F_x,F_y$ . However, when scheduling a layer, the seven loops can be split into three groups of X,Y,K,C dimensions. The  $F_x,F_y$  are small dimensions and can be unrolled in either space or time. The outermost loop "outer\_xykc()", is scheduled in software by the compiler and controls the on-chip memory allocation for the layer, we call it the **Outer dataflow**. The inner loop "inner\_ckxy()" or **inner dataflow** is scheduled in hardware and controls the tiles which are loaded to/from on-chip memory to registers for the execution of convolution. The "conv\_hw\_ck()" unrolls the loops in hardware and controls the **mapping** of the MAC units.

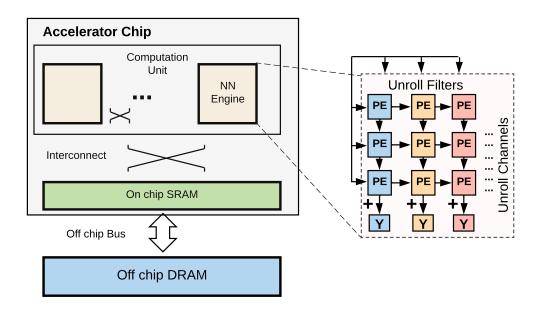

Accelerator Memory Model We assume a hardware memory model similar to [62, 79, 115]. Figure 1.7 shows the high-level logical view of the accelerator memory model. The DNN hardware accelerator design is composed of several major components i) NN Engine, ii) on-chip buffer, iii) external memory and iv) on/off-chip interconnect. An NN engine is a grid of Processing Element (PE). A PE calculates a MAC operation which is the basic computation unit of convolution operations. Due to resource limitations, the data is first cached in on-chip buffers (SRAM) before being fed to the computation unit. The on-chip interconnect is dedicated to communication between NN engines, between PEs, and between NN engines and on-chip buffers.

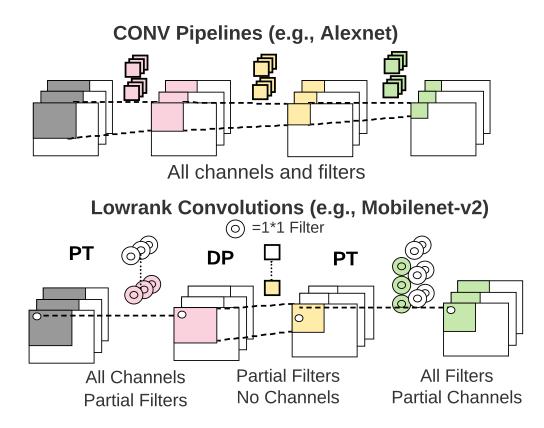

#### **Cross-Layer Dataflows for LR-CONVs**

Since, LR-CONVs are memory bound and have lower arithmetic intensity, they can benefit from inter-layer reuse. A Cross-layer dataflow schedules loops across concurrent layers simultaneously (per-layer serializes the execution of each layer). In LR-CONVs, the majority of the data re-use is across layers i.e., the producer-consumer reuse of the intermediate output activations of each layer. This provides an opportunity for cross-layers to retain the activations on-chip as they move across the layers.

Unlike CONV pipelines, LR-CONVs provide an opportunity for X-Layer to kickstart neighbouring layers in the pipeline with partially completed activations in (height, width, channel and filter dimensions). This shortens the lifetime of inter-layer activations that need to be held on-chip and allows capturing locality with a smaller amount of SRAM.

#### Design space of Cross-Layer dataflows for LR-CONV

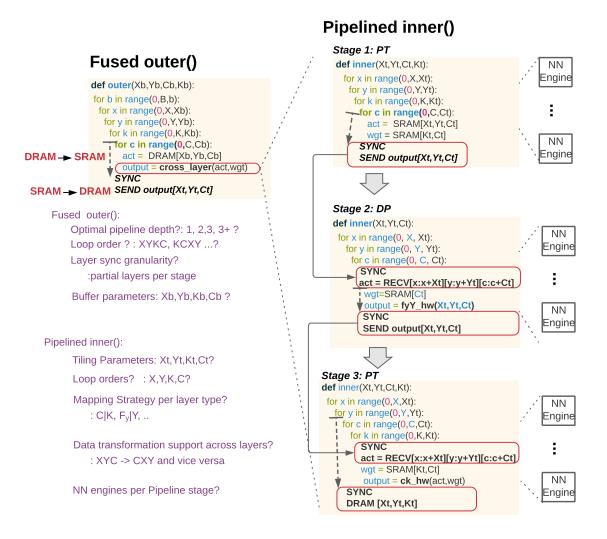

Figure 1.8 shows an example Cross-layer schedule for an inverted residual layer  $(PT \rightarrow DP \rightarrow PT)$ . To schedule multiple layers at a time, they need to be executed in a pipeline. The outermost loop needs

Figure 1.7: Accelerator Overview

to be fused for all pipelined layers which bring the corresponding input activations from DRAM to SRAM and sends the output activations from SRAM to DRAM. Each stage of the layer is executed concurrently with multiple sync points.

This thesis answers the questions such as what is the optimal loop order, pipeline depth, buffer parameters for the fused layer. Within each layer, we seek answers for 1) what are the optimal tiling parameters, 2) optimal loop order, 3) best mapping strategy based on layer type, 4) best mapping strategy and loop orders based on which stage the layer occurs, 5) What are the possible granularities at which different layers can sync based on the layer types and, 6) the optimal number of compute engines (NN) to be allocated per layer.

The outer loop blocking parameters control: i) the minimum on-chip memory required for each pipelined layer stage, ii) the synchronization granularity between layers and how often data is moved between them, and iii) the data reuse across layers and how long data is held on-chip before being consumed by a subsequent stage. The outermost loop has 5 loops, and thus 5!=120 possible loop orders. Within each layer, the buffer parameters vary a lot. For example,  $X,Y \in [3,224]$ , and  $K,C \in [1,1000]$  for image classification DNN which we study in this thesis.

The outer dataflow controls the pipeline granularity, and the inner loop order along with tiling parameters control the amount of work done in each pipeline stage. The number of loop orders per layer quickly explodes as the pipeline depth increases. Assuming a pipeline depth of "N", the possible loop orders are  $(4!)^N$ . Within each layer, the tiling parameters can vary between  $X,Y \in [3,224]$ , and  $K,C \in [1,1000]$ . The optimal hardware mapping also varies based on the layer type CONV, DP and

Figure 1.8: An example cross layer schedule for  $PT \rightarrow DP \rightarrow PT$  layer.

PT which affects hardware utilization. Supporting multiple mapping strategies based on layer type requires dynamic data shape transformation capabilities between layer execution in the hardware.

We systematically explore the search space to find optimal cross-layer dataflow strategies in chapter 3 and provide the hardware microarchitecture which supports shape transformations in chapter 4.

#### **Our Approach: X-Layer**

Our first work is X-Layer where we solve the challenges of executing LR-CONVs efficiently for EDGE-ONLY approach using cross-layer dataflows. We introduce multiple novel ideas: i) **Leveraging Cross-layer dataflows to explore pipelining:** It then proceeds to fuse loop dimensions from multiple layers and schedule them across concurrent stages. This explores the tradeoffs in synchronization between pipeline stages and the size of the sliding window mapped to SRAM to capture inter-layer reuse. ii) Fine-grain partial order loops: We identify that LR-CONVs have different pipeline dependencies than CONVs and this enables a finer-grain dataflow. With LR-CONVs, the channel and filter loops can be partially complete before a subsequent LR-CONV is kickstarted; CONVs do not provide this opportunity. iii) **Fine-grain vs Coarse-grain Dataflow:** We explore that Coarse-grain is sensitive to on-chip memory and performance drops steeply as on-chip memory reduces below 1.5 MB. On the contrary, X-Layer fine-grain dataflows perform well for a wide range of SRAM ( $\geq$  32KB). iv) **Heterogeneous inner dataflow:** We find that each layer type in the cross-layer pipeline requires different inner dataflows. We develop microarchitecture techniques to support the flexible on-chip data movement required by each layer. There has been some work in pipelining CONVs: batch pipelining [36,90,95] and activation pipelining [10, 107]. Their hardware does not support LR-CONVs. Also, their dataflows are coarser and sub-optimal for LR-CONVs. Batch pipelines require 8.3× more on-chip SRAM than X-Layer. Activation pipelines [10] give up XY locality where X-Layer performs 16× faster.

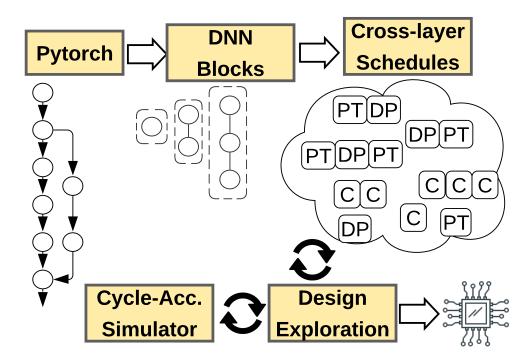

Figure 1.9: X-Layer Overview. DP= Depthwise, PT= Pointwise

Figure 1.9 illustrates X-Layer tool flow. X-Layer first partitions a DNN into composite blocks. The DNN blocks are formed based on the feasibility of pipelining the layers within a block. X-Layer schedules DNN blocks to execute as a concurrent pipeline in a cross-layer schedule. Each layer executes in a decoupled fashion but periodically synchronizes with the next stage in the pipeline to transfer a sliding window of activations. The loop order and blocking control within each layer involves a tradeoff between the size of the sliding window (which impacts on-chip SRAM required), frequency of synchronization (which impacts stage latency), and overall performance. To navigate this design tradeoff and find the Pareto optimal point, we use a multi-objective genetic algorithm [75].

The explorer selects the cross-layer dataflows and allocates on-chip buffers and mac units per layer. Finally, the optimal schedule is mapped onto the underlying hardware. To schedule a cross-layer dataflow, X-Layer splits the convolution loops of multiple layers in the pipeline into a single fused outer dataflow and several inner dataflows which execute in a synchronized manner. The inner dataflows are similar to per-layer dataflows [79]. We lower the scheduled dataflows onto a 2D grid of convolution accelerators. Since multiple layers can be simultaneously active on the hardware, X-Layer also addresses the issue of distributing the compute and SRAM resources in the grid to each layer.

**Engineering efforts while developing X-Layer** Figure 1.8 shows the large large design space and the questions that need to be answered for an optimal cross-layer dataflow design. The dataflow is closely tied to the hardware and it is impossible to explore the design space of Cross-layer dataflows without basic hardware support such as data transformation capabilities within the hardware, different mapping capabilities in the hardware, data movement between NN engines and, controlling the size of NN engines.

The design space of cross-layer dataflow requires developing an infrastructure to fuse multiple outer layer dataflows together. It should support loop order explorations for both single fused outer dataflow and multiple inner dataflows of the pipelined stages. We need to support these capabilities for primarily three-layer types CONV, DP and PT, where each layer type have different loop dependencies. For instance, in a three-stage CONV pipeline, with the loop order  $X \rightarrow Y \rightarrow K \rightarrow C$  for stage 1. Partial loop executions of X,Y,K are allowed but we cannot kickstart stage 2 without finishing all channels (C). Such dependencies vary as the loop order changes.

We first started with a three stage templated cross-layer hardware with a fixed loop order  $X^pY^pK^pC \rightarrow X^pY^pC^p \rightarrow CKXY$ . The "*p*" indicate partial loop orders being executed. This limited microarchitecture solution is similar to prior work Fused-Layer [10] and Tangram [36]. The hardware targeted FPGAs and was regenerated for every DNN. This work did not get published, and we had to iterate multiple times until we realized the extent of the large design space.

We realized that the outermost dataflow controls the granularity of the pipeline and has first-order effects on latency. The inner dataflow of each pipeline stage is tied to the mapping of the hardware and it is sufficient to fix them to the optimal mapping of each layer type.

We had to start from scratch multiple times and we ended up with a configurable ASIC microarchitecture with minimal features such as shape transformations which allowed us to explore the design space of cross-layer dataflows.

### 1.5 Speedup potential for SPLIT Approach

Table 1.2 shows the operating and application constraints when a DISTRIBUTED approach is preferred over an EDGE-ONLY approach. The main scenario is when the AI application does not fit on the

| Constraints | Scenario                                                     |

|-------------|--------------------------------------------------------------|

| Operating   | DNN does not fit<br>Network connection exists                |

| Application | Latency Critical<br>High Accuracy which require large models |

Table 1.2: AI Application scenario for DISTRIBUTED approach

edge device. This is especially true for large scale DNNs that are required for the high accuracy of the application.

Large scale DNN models are typically hosted in cloud servers with unrelenting computational power. At the same time, data is often distributed at the edge of the cloud, that is, the edge of various networks, such as smart-home cameras, authorization entry (e.g. license plate recognition camera), smart-phone and smart-watch AI applications, surveillance cameras, AI medical devices (e.g. hearing aids, and Fitbit), and IoT nodes. However, the gap between huge amounts of data and large deep learning models remains and becomes an arduous challenge for extensive AI applications. Connecting data at the edge with deep learning models at cloud servers is far from straightforward. Through low-power devices at the edge, data is often collected, and machine learning models cannot be loaded into those low-power devices due to the very limited computation capability. Indeed, deep learning models are becoming more and more powerful and larger and larger. The grand challenge for utilization of the latest extremely large models, such as GPT-3 [16] (350GB memory and 175B parameters in case of GPT-3), is far beyond the capacity of just those low-power devices. For those models, the inference is currently conducted on cloud clusters. It is impractical to run such models only at the edge.

Since the input data is generated at the edge, a network connection is required to transmit i) either the input data (CLOUD-ONLY) or, ii) partially executed DNN output activations (SPLIT). Transmitting high resolution, high volume input data all to cloud servers (the Cloud Only Approach (CLOUD-ONLY) solution) may incur high transmission costs, and may result in high end-to-end latency. Moreover, when original data is transmitted to the cloud, additional privacy risks may be imposed. Recently, the DNN graph splitting methods has been explored [49,58,119]. The approach exploits the fact that the data size at some intermediate layer of a deep neural network (DNN for short) is significantly smaller than that of raw input data. This approach partitions a DNN graph into edge DNN and cloud DNN thereby reduces the transmission cost and lowers the end-to-end latency [49, 58, 119]. The edge-cloud collaborative approach is generic, can be applied to a large number of AI applications. Prior work [119] has shown that SPLIT approach can be up to  $1.6 \times$  faster than the CLOUD-ONLY approach. These techniques rely on creating a weighted DNN graph where each edge denotes the transmission cost in case of a split. Then a graph min-cut is calculated to detect the split point with the lowest end to end latency. The existing state of the art SPLIT

approaches such as QDMP [119] execute the edge side of the DNN in floating-point precision which is not optimal.

Figure 1.10: Transmission cost comparison between CLOUD-ONLY and SPLIT. MP: Mixed precision

**Joint bit-width allocation and split detection** Figure 1.10 shows the intuition behind low latency of SPLIT solutions compared to CLOUD-ONLY approach. In the example, the CLOUD-ONLY approach requires 507 KB of data to be transmitted over the network whereas an existing SPLIT approach executing in 16-bit floating point precision (FP16), requires only 49KB of transmission. By leveraging, mixed precision quantization, one can see that the same split point suggested earlier need to transmit only 12.25 KB. However, when a mixed precision quantization is applied Node 1 was allocated 2-bits whereas Node 5 was allocated 4-bits. Thus, the optimal split point is Node 1 with 10 KB of data transmission. This also demonstrates the need for joint bit-width allocation and graph split point detection.

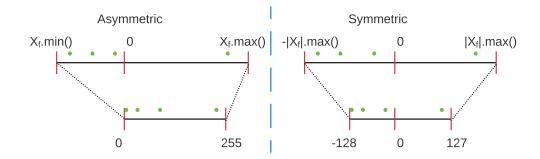

**Mixed Precision Quantization (MP)** The mixed precision quantization allocates different bitwidths to weights and activations of different layers such that the total accuracy of the DNN is within the acceptable limit. The intuition is that some layers are more compressible than others and does not affect the final accuracy. The mixed precision quantization requires the allocation of bit widths for weights and activations for every layer of the DNN. Given a DNN with "*N*" layers, and  $\mathbb{B}=\{1,2,4,6,8\}$  bit-widths to choose, the number of possible combinations is  $\mathbb{B}^{2n}$  which is exponential. Assuming a Resnet-50 example, the allocation of bit widths and execution of a DNN to verify the accuracy can take around  $\simeq 8$  minutes per configuration on a GPU. Thus, a brute force approach will require  $\simeq 5^{2\times50} \times 8 = 6.3 \times 10^{70}$  minutes. The joint bit-width allocation along with split detection increases the search space further.

Next, we argue qualitatively, why the trivial solution of splitting the DNN (QDMP) and then applying MP or vice-versa does not work.

$QDMP \rightarrow MP$ : Finding split points using partitioning algorithms such as [49,58] and then applying mixed-precision quantization on the edge DNN is not sufficient since 1) the split point detected to partition into edge DNN and cloud DNN for reducing end-to-end latency can be different 2) This is because these algorithms do not account for edge device memory to split the DNN. Quantization reduces total memory requirement which in turn allows for deeper layers to be part of the search space for feasible solutions.

$MP \rightarrow QDMP$ : One can also consider applying mixed-precision quantization on the entire DNN first and then use those bit-widths in the edge DNN solution of the partitioning algorithms. (**Mixed precision**  $\rightarrow$  [49,58]). This is also not optimal since: 1) the split point detected did not consider quantization at first and it may be different from the optimal solution. Since the mixed-precision quantization used the entire DNN instead of partial DNN for quantization they will be conservative in assigning low bit-widths, 2) edge DNN quantization in edge-cloud model partitioning approach also requires more compression for activations at the split point, unlike the EDGE-ONLY approach where existing mixed precision techniques treat all layers equally for compression. For example, ZeroQ [17] (page 6) demonstrated mixed-precision quantization for weights and uniform 6-bit quantization for activations to reduce the ResNet-50 model size to 18.27 MB.

We observed that the transmission cost of output activations of the edge DNN can be further reduced by applying mixed-precision quantization along with DNN graph partitioning. However, this raises new challenges: a) existing techniques profile the edge, cloud, and transmission latency of each layer before applying the partitioning algorithm, but a naive mixed-precision quantization method will require this profiling to be done for multiple bit-widths which is computationally expensive, b) bit-widths of DNN layers need to be explored without dropping the accuracy too much.

**Problem Formulation** The problem requires jointly allocating bit-widths for weights and activations along with detecting the optimal split point "*n*". Given a DNN with "*N*" layers, the detected split point should also satisfy the constraints i) the  $Edge_{DNN} \in [1,n]$  fits in the edge device memory, ii) the DNN error caused due to quantization is within the user acceptable limit. To summarize, the AUTO-SPLIT problem can be formulated as follows:-

$$\min_{\mathbf{b}^{w},\mathbf{b}^{a}\in\mathbb{B}^{n},n}\left(\sum_{i=1}^{n}\mathscr{L}_{i}^{edge}+\mathscr{L}_{n}^{tr}+\sum_{i=n}^{N}\mathscr{L}_{i}^{cloud}\right)$$

(1.1a)

$$\mathscr{M}^{w} + \mathscr{M}^{a} \leq M, \tag{1.1b}$$

$$\mathscr{F}(\mathbf{b}^{w},\mathbf{b}^{a}) \leq E, \tag{1.1c}$$

where  $\mathscr{M}^w, \mathscr{M}^a$  is weight and activation memory, M is total edge device memory,  $\mathscr{F}$  is the DNN which is a function of weight and activation bit-width sets, and E is the acceptable Error limit set by the user. The  $\mathscr{L}$  is the non-linear latency function that depends on the edge and cloud device.  $\mathscr{L}_n^{tr}$  denotes the transmission latency of transmitting output activations from  $Edge_{DNN} \rightarrow Cloud_{DNN}$ .

#### **Our Approach: AUTO-SPLIT**

Our second work AUTO-SPLIT improves the end to end latency of AI applications deploying SPLIT solutions on the edge device. This work is explained in detail in chapter 5. In this section, we discuss the problem overview of AUTO-SPLIT. We realize that in SPLIT approach, we can reduce the latency of edge DNNs by leveraging MP. However, this increases the search space of splitting the DNNs further.

Fig. 1.11 shows an overview of our framework. The AUTO-SPLIT applies joint bit-width allocation and split detection to generate a quantized edge DNN which executes on the edge device and a Cloud DNN which executes on the cloud device. The output activations from edge DNN are packed and transmitted to the Cloud device for unpacking and fed as input to the Cloud DNN. Depending on the operating and application constraints, the AUTO-SPLIT can suggest one of the EDGE-ONLY, CLOUD-ONLY and SPLIT approaches. The input to the AUTO-SPLIT can be categorized into i) DNN specific inputs, ii) operating constraints and iii) application constraints. The DNN specific inputs are a pre-trained DNN and sample data for profiling to collect statistics for quantization. The operating constraints such as uplink bandwidth based on the network type (e.g., BLE, 3G, 5G, or WiFi). The application constraints include the error limit acceptable by the application user.

The AUTO-SPLIT is part of an edge-cloud collaborative prototype of Huawei Cloud. This patented technology is already validated on selected applications, such as license plate recognition systems with HiLens edge devices [18, 31, 82], is on its way for broader systematic edge-cloud application integration [33], and is being made available for public use as an automated pipeline service for end-to-end edge-cloud collaborative intelligence deployment [9].

**Engineering challenges incurred while developing AUTO-SPLIT** The Figure 1.11 can be split into input pre-processing, AUTO-SPLIT method and the output post-processing. We list the engineering efforts that were required to develop AUTO-SPLIT framework in each category.

Figure 1.11: AUTO-SPLIT overview: inputs are a trained DNN and the constraints, and outputs are optimal split and bit-widths

**DNN preprocessing:** The DNN input needs to have DNN layers in a specific format for it to be quantized. The guidelines for preparing a DNN for quantization can be found in [3]. Also pre-processing of DNNs for inference on edge devices requires some layers to be in a particular order. For example, the layers  $CONV \rightarrow BatchNorm \rightarrow Relu$ , should be in the order presented for DNN processing to apply BatchNorm folding.

**Mixed precision edge simulator:** At the time of this research, there has been no open source edge device simulator that supports mixed-precision quantization. Existing academia solutions [37,91] did not have the software stack and existing industry solutions [2,5] only supported uniform 8-bit quantization. Thus an edge device hardware simulator had to be built from scratch. Prior work [30] used NAS based methods to explore DNN architectures by getting latency feedback from the edge devices. On further exploration, we found that it used an operator Look up Table (LUT) from the Samsung device. We tried using this setup but it did not work, since, the LUT was specific to only one DNN.