# System-Level Design of Energy-Efficient Sensor-Based Human Activity Recognition Systems

A Model-Based Approach

### **Dissertation**

to obtain the academic degree

**Doktor-Ingenieur (Dr.-Ing.)**

of the Faculty of Computer Science and Electrical Engineering at the University of Rostock

submitted by

Florian Grützmacher

born on 13.01.1990 in Crivitz, Germany

from Rostock

Rostock, March 29th, 2021

### Dieses Werk ist lizenziert unter einer Creative Commons Namensnennung 4.0 International Lizenz.

### **Reviewers:**

### • Prof. Dr.-Ing. habil. Christian Haubelt

Embedded Systems Chair Institute of Applied Microelectronics and Computer Engineering University of Rostock, Germany

### • Prof. Dr.-Ing. Thomas Kirste

Mobile Multimedia Information Systems Chair Institute for Visual and Analytic Computing University of Rostock, Germany

### • Prof. Dr. Andy D. Pimentel

Parallel Computing Systems Chair Informatics Institute University of Amsterdam, Netherlands

Date of submission: 29.03.2021 Date of defense: 12.10.2021

### Acknowledgments

First and foremost, I would like to express my sincere gratitude to Prof. Dr. Christian Haubelt for the confidence he has placed in me and for the superb supervision that I received from him during my time at the University of Rostock. Without him, this thesis would have not been possible. I would also like to thank Prof. Dr. Thomas Kirste and Prof. Dr. Andy Pimentel, who accepted to review this thesis. Moreover, I would like to express my thanks to Dr. Rainer Dorsch and Bosch Sensortec GmbH for their support and provision of various hardware prototypes, Dr. Sander Stuijk and Dr. Bart D. Theelen for the many helpful discussions about the theory of data flow graphs and their analyses, Prof. Dr. Kristof Van Laerhoven and Jochen Kempfle for the cooperation on piecewise linear approximation algorithms, and all other project partners and collaborators during the last years.

Many thanks go to my colleagues from the Institute of Applied Microelectronics and Computer Engineering of the University of Rostock, for the really pleasant working atmosphere and the many scientific and non-scientific, but always interesting and helpful discussions. Especially, I would like to thank Benjamin Beichler, Johann-Peter Wolff, Kai Neubauer, and Dr. Michael Rethfeldt for their support and availability for many fruitful discussions.

Finally, I would like to thank my friends and especially my family for motivating and supporting me in many ways. Special thanks go to my beloved Pily for her support and her patience with me and my frequent mental absence while writing this thesis.

The support of all of you has been instrumental to the success of this work.

### **Abstract**

Today, we are surrounded by a plethora of different processor systems in our everyday life and almost every situation. Mobile and wearable devices are equipped with embedded processors to provide advanced functionality and assistance in everyday situations. Furthermore, embedded systems can be found in our daily vicinity, be it at home, in offices, public places or in transport. Besides pervasive integration, embedded systems have seen a transformation from single processor systems to powerful multi-processor systems on chip, in order to overcome technological limitations in form of heat dissipation. Furthermore, the diversity of processor architectures has increased to heterogeneous multi-processor systems that offer trade-offs between energy demands, computational power, and flexibility for a wide range of application-specific demands. With technological advances, assistive systems have seen a further development by industry and research as well. As a fundamental requirement, in order to provide us with relevant services, our current *activity* needs to be known by the assistive system. Consequently, assistive systems must be able to infer our activities automatically by observations, without additional, possibly obtrusive interaction.

Inertial sensors have gained an important role for such observations, as advances in micro-electro-mechanical systems technology allow them to be manufactured as small and unobtrusive, but also energy-efficient and cheap components. Since then, sensor-based human activity recognition systems have increasingly been subject to research and development towards high recognition accuracy, but also many conceptual and algorithmic optimizations with respect to low latency and energy efficiency have been developed. The diversity and availability of computational resources as well as algorithmic solutions leads to promising possibilities for system designs such that software components can be executed on suitable processing units, in order to meet application-specific requirements on latency, data throughput, and energy consumption.

However, the huge number of possibilities comes at the price of a vast design space, that becomes increasingly hard to explore. In order to reduce design time, methods to quantify and thus substantiate design decisions early in the design process become crucial. The thesis at hand proposes model-based design and analysis techniques as a possible solution. To this end, dataflow models of computation are evaluated towards their ability to capture abstracted behavior of human activity recognition systems. These models can further capture design decisions with respect to mappings, schedules, functional parameters, and existing conceptual optimizations of human activity recognition system, and allow a formal analysis of extra-functional properties.

To this end, the thesis at hand contributes an evaluation of state-of-the-art dataflow models of computation regarding their suitability for a model-based design and analysis of human activity recognition systems, in terms of expressiveness and analyzability, as well as model accuracy. Different aspects of state-of-the-art human activity recognition systems have been modeled and analyzed. Based on existing methods, novel analysis approaches have been developed to acquire extra-functional properties like processor utilization and data communication rates, which directly influence energy consumption of the system. Furthermore, energy consumption models are introduced with which hardware elements can be annotated, in order to estimate the impact of design decisions on the energy consumption at design time.

### Kurzfassung

In unserem heutigen Alltag sind wir von einer Vielzahl verschiedener Prozessorsysteme umgeben. Mobile und tragbare Geräte sind mit unterschiedlichsten Prozessoren ausgestattet, um erweiterte Funktionalitäten und Unterstützung bereitzustellen. Darüber hinaus finden wir eingebettete Systeme in unserer täglichen Umgebung, sei es zu Hause, in Büros, an öffentlichen Orten oder im Transportwesen. Neben allgegenwärtiger Integration haben sich eingebettete Systeme von Einzel-, zu leistungsstarken Multiprozessorsystemen entwickelt, um technologische Einschränkungen durch unzureichende Wärmeableitung zu überwinden. Darüber hinaus hat die Vielfalt an heterogenen Multiprozessorsystemen zugenommen, die Abwägungen zwischen Energiebedarf, Rechenleistung und Flexibilität für anwendungsspezifische Anforderungen ermöglicht. Mit dem technologischen Fortschritt wurden auch Assistenzsysteme durch Industrie und Forschung weiterentwickelt. Als Grundvoraussetzung um uns relevante Dienste bereitstellen zu können, muss unsere aktuelle Aktivität dem Assistenzsystem bekannt sein. Folglich müssen Assistenzsysteme in der Lage sein, unsere Aktivitäten eigenständig durch Beobachtungen abzuleiten.

Inertialsensorik hat für solche Beobachtungen eine wichtige Rolle eingenommen, da sie dank der Fortschritte in der mikroelektromechanischen Systemtechnologie als kleine und unauffällige, aber auch energieeffiziente und kostengünstige Komponenten hergestellt werden können. Seitdem wurden sensorgestützte Aktivitätserkennungssysteme zunehmend erforscht und entwickelt, um eine hohe Erkennungsgenauigkeit zu erreichen. Es wurden jedoch auch konzeptionelle und algorithmische Optimierungen hinsichtlich Latenz und Energieeffizienz entwickelt. Die Vielfalt und Verfügbarkeit von Rechenressourcen sowie Algorithmen bietet vielversprechende Möglichkeiten für den Systementwurf, sodass Softwarekomponenten auf geeigneten Prozessoreinheiten ausgeführt werden können, um anwendungsspezifische Anforderungen zu erfüllen.

Der Entwurfsraum wird mit zunehmender Größe jedoch schwieriger zu explorieren. Um die Entwurfszeit zu verkürzen, werden Methoden zur Quantifizierung und dadurch zur Untermauerung von Entwurfsentscheidungen früh im Entwurfsprozesses von entscheidender Bedeutung. Die vorliegende Arbeit schlägt modellbasierte Entwurfs- und Analysetechniken als mögliche Lösung vor. Zu diesem Zweck werden Datenflussberechnungsmodelle dahingehend bewertet, ob sie das abstrahierte Verhalten von Aktivitätserkennungssystemen erfassen können. Diese Modelle können Entwurfsentscheidungen in Bezug auf Bindung, Ablaufplanung, Funktionsparameter und vorhandene konzeptionelle Optimierungen von Aktivitätserkennungssystemen erfassen und eine extrafunktionale Eigenschaftsprüfung ermöglichen.

Zu diesem Zweck liefert die vorliegende Arbeit eine Bewertung bestehender Datenflussberechnungsmodelle hinsichtlich ihrer Eignung für den modellbasierten Entwurf und Analyse von Aktivitätserkennungssystemen basierend auf ihrer Ausdrucksmächtigkeit und Analysierbarkeit sowie Modellgenauigkeit. Verschiedene Aspekte modernster Aktivitätserkennungssysteme wurden dazu modelliert und analysiert. Basierend auf vorhandenen Methoden wurden neuartige Analyseansätze entwickelt, um extrafunktionale Eigenschaften wie Prozessorauslastung und Datenkommunikationsraten zu berechnen, die den Energieverbrauch des Systems direkt beeinflussen. Darüber hinaus werden Energieverbrauchsmodelle eingeführt, mit denen Hardware-Elemente annotiert werden können, um die Auswirkungen von Entwurfsentscheidungen auf den Energieverbrauch zur Entwurfszeit abzuschätzen.

Contents

### **Contents**

|   | List | of Abbreviations                           | IX       |  |  |  |  |

|---|------|--------------------------------------------|----------|--|--|--|--|

| 1 | Intr | roduction                                  | 1        |  |  |  |  |

|   | 1.1  | Problem Statement and Approach             | 4        |  |  |  |  |

|   | 1.2  | Contributions                              | 6        |  |  |  |  |

|   | 1.3  | Author's Publications                      | 7        |  |  |  |  |

| 2 | Fun  | adamentals                                 | 9        |  |  |  |  |

|   | 2.1  | Dataflow Models of Computation             | 9        |  |  |  |  |

|   |      | 2.1.1 Synchronous Dataflow Graphs          | 9        |  |  |  |  |

|   |      | 2.1.2 Cyclo-Static Dataflow Graphs         | 14       |  |  |  |  |

|   |      | 2.1.3 Scenario-Aware Dataflow Graphs       | 17       |  |  |  |  |

|   | 2.2  | System Modeling                            | 22       |  |  |  |  |

| 3 | Ene  | ergy-Efficient Sensor Networks             | 25       |  |  |  |  |

|   | 3.1  | Related Work                               | 26       |  |  |  |  |

|   | 3.2  | Case Study                                 | 29       |  |  |  |  |

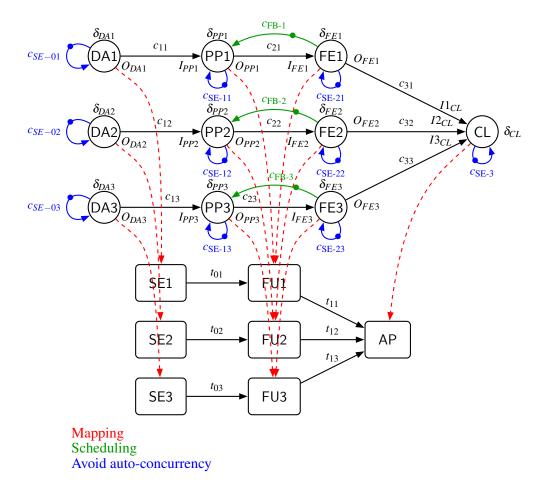

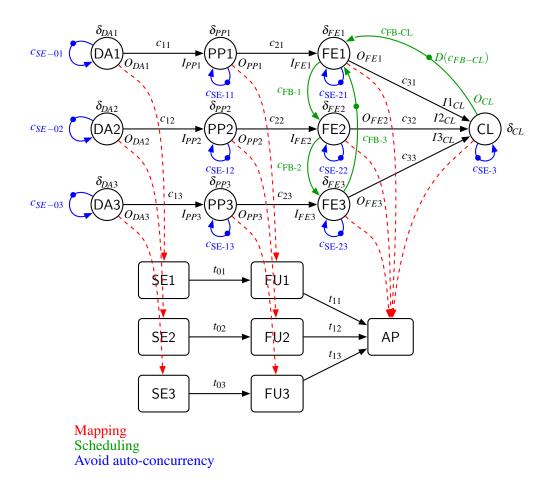

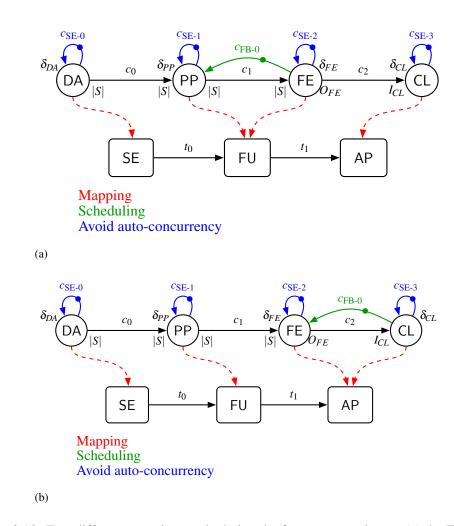

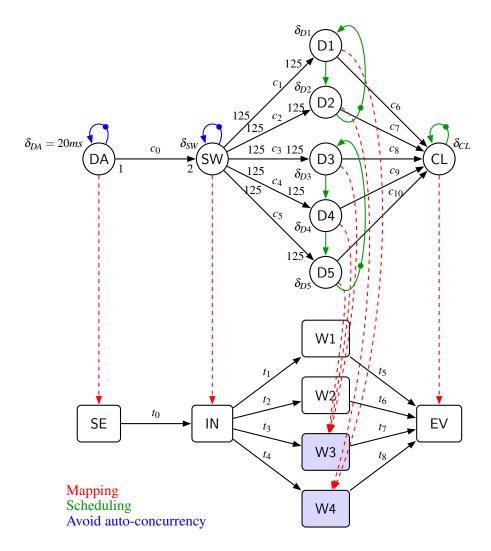

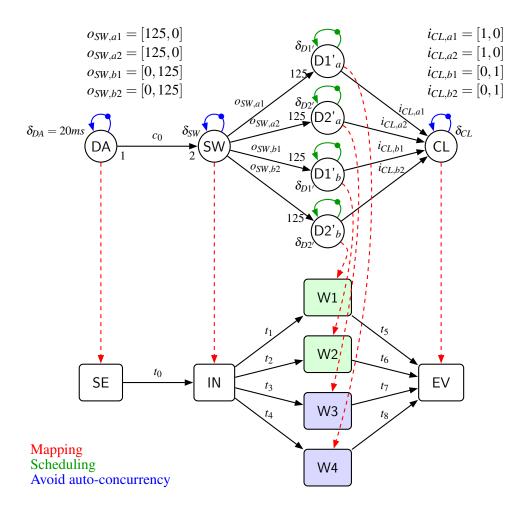

|   | 3.3  | Modeling                                   | 31       |  |  |  |  |

|   |      | 3.3.1 Model Refinement                     | 32       |  |  |  |  |

|   |      | 3.3.2 Application Model                    | 35       |  |  |  |  |

|   |      | 3.3.3 Analysis Model                       | 36       |  |  |  |  |

|   | 3.4  | Analysis                                   | 40       |  |  |  |  |

|   |      | 3.4.1 Real-Time Behavior                   | 40       |  |  |  |  |

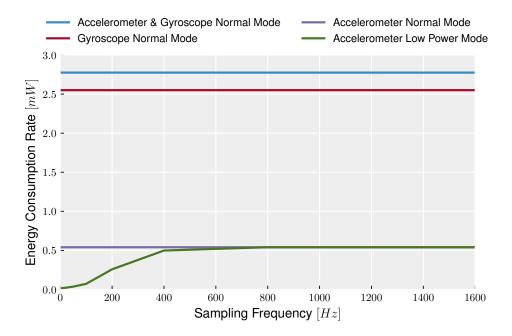

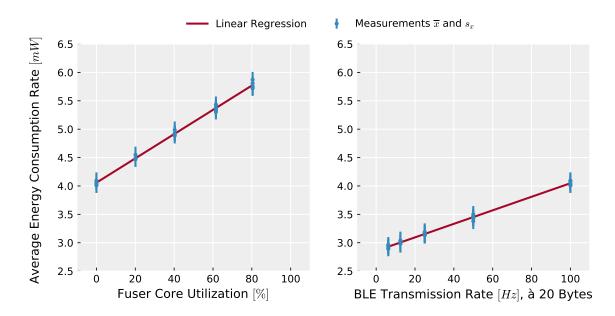

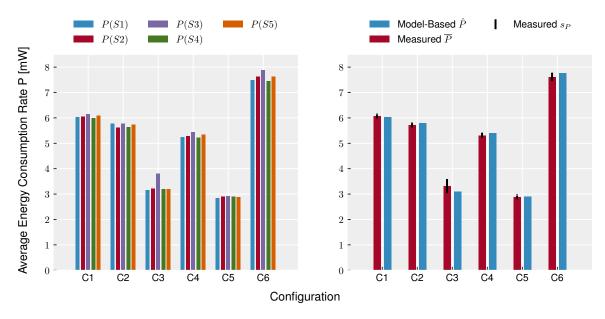

|   |      | 3.4.2 Energy Trade-Off                     | 43       |  |  |  |  |

|   | 3.5  | Experiments                                | 46       |  |  |  |  |

|   |      | 3.5.1 Configurations                       | 46       |  |  |  |  |

|   |      | 3.5.2 Implementation                       | 48       |  |  |  |  |

|   |      | 3.5.3 Model Evaluation                     | 50       |  |  |  |  |

|   |      | 3.5.4 Experimental Setup                   | 51       |  |  |  |  |

|   |      | 3.5.5 Experimental Results                 | 51       |  |  |  |  |

|   | 3.6  | Discussion                                 | 54       |  |  |  |  |

| 4 | Thr  | read-Level Parallelism                     | 55       |  |  |  |  |

|   | 4.1  | Related Work                               | 56       |  |  |  |  |

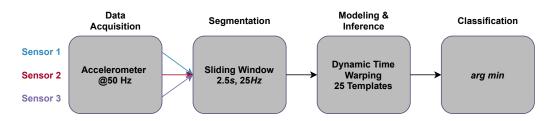

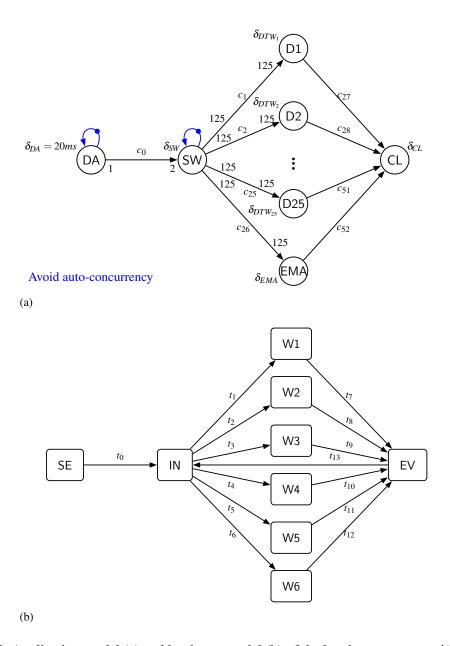

|   | 4.2  | Dynamic Time Warping                       | 58       |  |  |  |  |

|   | 4.3  | Case Study                                 | 59       |  |  |  |  |

|   | 4.4  | Parallelization Approaches                 |          |  |  |  |  |

|   |      | 4.4.1 Intra-Segment Parallelization        | 60<br>61 |  |  |  |  |

|   |      | 4.4.2 Inter-Segment Parallelization        | 63       |  |  |  |  |

|   |      | 4.4.3 Hybrid Parallelization               | 66       |  |  |  |  |

|   |      | 4.4.4 Parallelization Configurations       | 68       |  |  |  |  |

|   | 4.5  | Experiments                                | 69       |  |  |  |  |

|   |      | 4.5.1 Hand Gesture Recognition Application | 69       |  |  |  |  |

VIII Contents

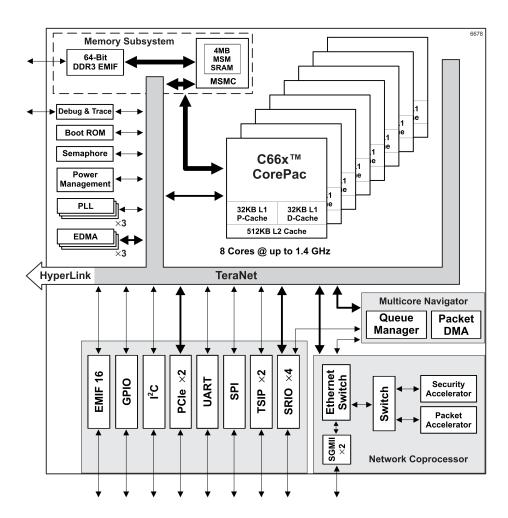

|                                   |         | 4.5.2    | Hardware Architecture                                |       |

|-----------------------------------|---------|----------|------------------------------------------------------|-------|

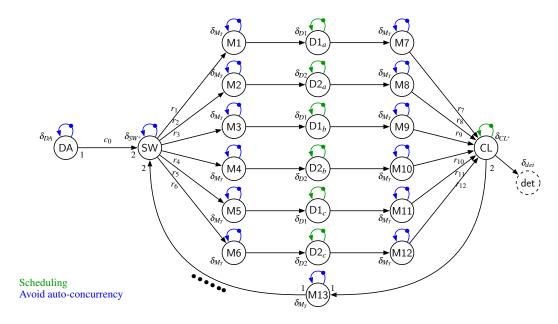

|                                   |         | 4.5.3    | Analysis Model                                       |       |

|                                   | 1.6     | 4.5.4    | Model Refinement                                     |       |

|                                   | 4.6     |          | ttion                                                |       |

|                                   |         | 4.6.1    | Performance assessment                               |       |

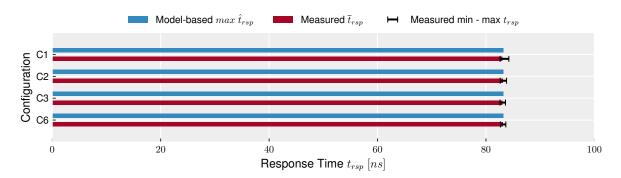

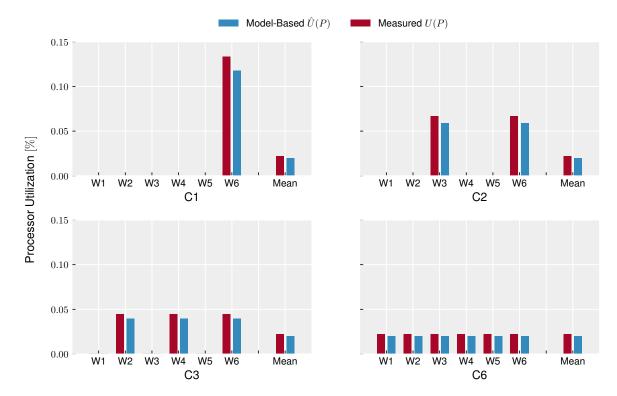

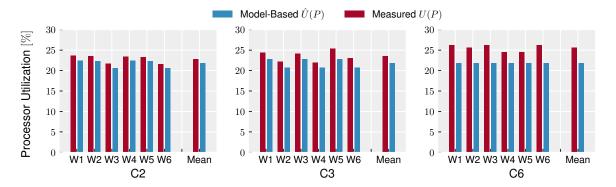

|                                   | 47      | 4.6.2    | Evaluation Results                                   |       |

|                                   | 4.7     | Discus   | sion                                                 | . 91  |

| 5                                 | Con     | text Aw  | areness and Dynamic Behavior                         | 93    |

|                                   | 5.1     | Scenar   | rio-Based Dynamic Behavior                           |       |

|                                   |         | 5.1.1    | Related Work                                         |       |

|                                   |         | 5.1.2    | Modeling Scenario-Based Dynamic Behavior             |       |

|                                   |         | 5.1.3    | Analysis Models                                      | . 101 |

|                                   |         | 5.1.4    | Model Analysis                                       | . 103 |

|                                   |         | 5.1.5    | Experiments                                          |       |

|                                   |         | 5.1.6    | Evaluation                                           | . 105 |

|                                   |         | 5.1.7    | Discussion                                           |       |

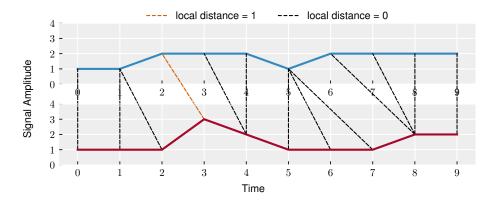

|                                   | 5.2     | Data-E   | Dependent Dynamic Behavior                           | . 117 |

|                                   |         | 5.2.1    | Related Work                                         | . 118 |

|                                   |         | 5.2.2    | Simple Linear Regression                             | . 120 |

|                                   |         | 5.2.3    | Online Piecewise Linear Approximation                | . 122 |

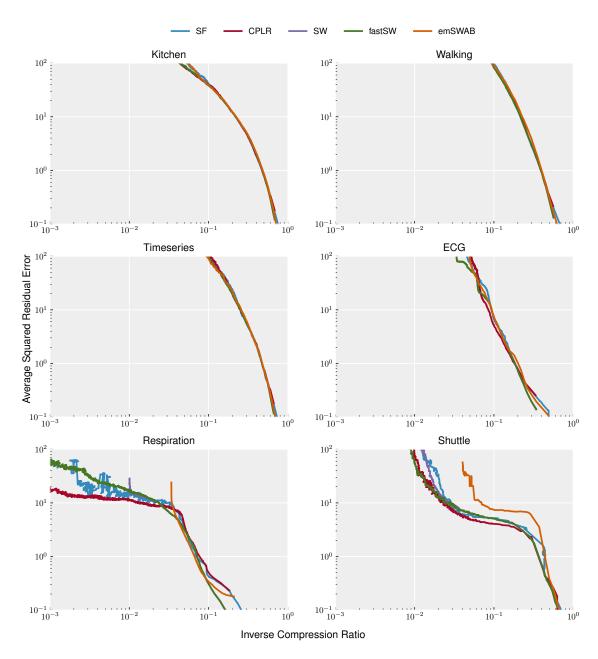

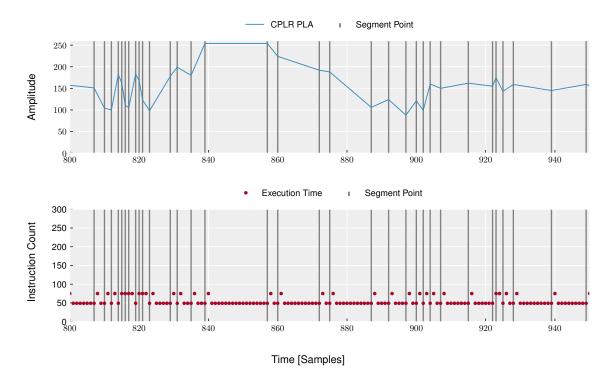

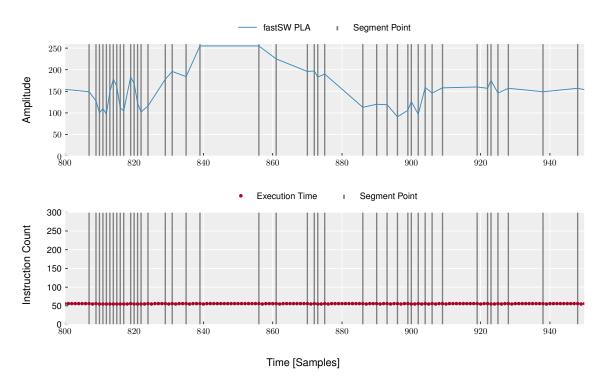

|                                   |         | 5.2.4    | Evaluation                                           | . 130 |

|                                   |         | 5.2.5    | Discussion                                           | . 139 |

| 6                                 | Con     | clusions |                                                      | 141   |

|                                   | 6.1     |          | ary                                                  |       |

|                                   | 6.2     |          | sion                                                 |       |

|                                   | 6.3     |          | tions                                                |       |

|                                   | 6.4     |          | Work                                                 |       |

| Bibliography                      |         |          |                                                      | 145   |

| Li                                | st of I | Publicat | tions                                                | 157   |

| <b>A</b>                          | Imn     | lomonto  | ation Datails on the Hand Costum Decognition System  | 159   |

| A                                 | ımp     | iementa  | ntion Details on the Hand Gesture Recognition System | 159   |

| B Supplementary Experimental Data |         |          |                                                      |       |

List of Abbreviations IX

### **List of Abbreviations**

ANN Artificial Neural Network

ANOVA Analysis Of Variance

AP Application Processor

ARC Activity Recognition Chain

**ASIC** Application-Specific Integrated Circuit

**ASIP** Application-Specific Instruction-Set Processor

BDF Boolean Dataflow

BLE Bluetooth Low Energy

CCW Counter Clockwise CFG Control Flow Graph

**CPLR** Connected Piecewise Linear Regression

CSDF Cyclo-Static Dataflow CV Coefficient of Variation

**CW** Clockwise

DDF Dynamic Dataflow

DIT Decimation In Time

DMA Direct Memory Access

DSP Digital Signal Processor

**DT** Decision Tree

**DTW** Dynamic Time Warping

**DVFS** Dynamic Voltage and Frequency Scaling

**ECG** Electrocardiogram

**EMA** Exponential Moving Average

FFT Fast Fourier Transform

FIFO First-In-First-Out

FPU Floating-Point Unit

FSM Finite State Machine

**FSM-SADF** Finite State Machine Scenario-Aware Dataflow

GCC GNU Compiler Collection GPP General-Purpose Processor GPU Graphics Processing Unit

HAR Human Activity Recognition HMM Hidden Markov Model

**HSDF** Homogeneous Synchronous Dataflow

I<sup>2</sup>C Inter-Integrated Circuit

ICR Inverse Compression Ratio

IFL Inter-Firing Latency

X List of Abbreviations

IMU Inertial Measurement Unit

**k-NN** k-Nearest Neighbors

LCG Linear Constraint Graph

LDA Linear Discriminant Analysis

MACMultiply and AccumulateMCMMaximum Cycle MeanMCRMaximum Cycle Ratio

MEMS Micro-Electro-Mechanical System

MoC Model of Computation

MPSoC Multi-Processor System-on-Chip

MSM Multicore Shared Memory

MSMC Multicore Shared Memory Controller

**NoC** Network-on-Chip

**OLS** Ordinary Least Squares

**PCA** Principle Component Analysis

**PFSM-SADF** Parametrized Finite State Machine Scenario-Aware Dataflow

**PLA** Piecewise Linear Approximation

**SADF** Scenario-Aware Dataflow

SCC Strongly Connected Component

SDF Synchronous Dataflow

**SF** Swing Filter

**SIMD** Single Instruction, Multiple Data

**SiP** Systems-in-Package

SRAMStatic Random-Access MemorySSRSum of Squared ResidualsSVMSupport Vector Machines

**SW** Sliding Window

**SWAB** Sliding Window and Bottom Up

TI Texas Instruments

ToF Time of Flight

VLSI Very Large Scale Integration VPDF Variable-Rate Phased Dataflow

WCET Worst-Case Execution Time

WSN Wireless Sensor Network

### 1 Introduction

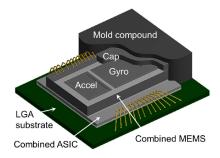

With the advances in microelectronics and computer architectures, *Human Activity Recognition* (HAR) as a research field has increasingly gained attention in the past 25 years. The demand of automatic detection and classification of human behavior by computer systems has been increasing in various social, medical, safety, and security areas. While approaches based on computer vision have been dominating the first attempts, the technological advances in inertial sensor systems have shifted the focus to sensor-based human activity recognition systems. Inertial sensors are composed of accelerometers and gyroscopes that, when attached to an object, allow the measurement of acceleration and angular speed of that object into the direction and around the rotation axis of the sensor, respectively. By integrating three of these sensors perpendicular to each other, the 3D movement and rotation can be captured. Often inertial sensors are combined with magnetometers, in order to measure the magnetic field in each axis, which allows to transform the measured signals into the earth coordinate system and further calculate object orientation from it. Especially the introduction of Micro-Electro-Mechanical System (MEMS) technology into the development, has lead to inertial sensor systems, that are small and unobtrusive enough to be worn on the human body. This can be in form of dedicated sensing devices or integrated in mobile and wearable devices like smartphones, smart watches, fitness trackers, glasses, or ear plugs. Figure 1.1 depicts the package configuration of an BMI260 IMU sensor from Bosch Sensortec GmbH, the dimensions of which are  $3.0x2.5x0.83 mm^3$  [1].

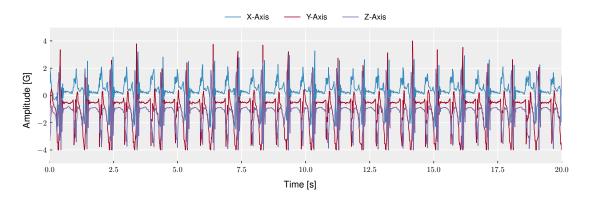

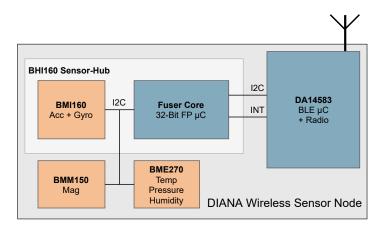

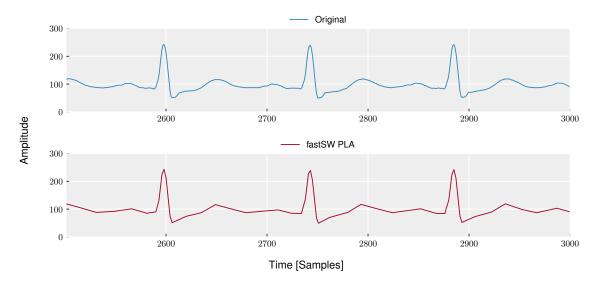

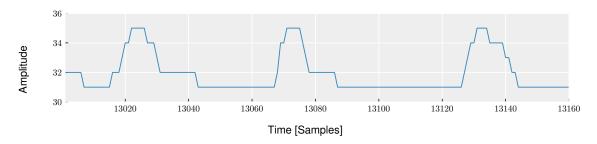

Application-Specific Instruction-Set Processors (ASIPs) can be integrated with MEMS sensors of different modalities as so-called Systems-in-Package (SiP). These ASIPs provide the interface to the host system that the sensor sub-system is embedded into, provide sample timestamps, execute signal correction algorithms for offset or drift compensation, and perform signal fusion to derive further information, e.g., sensor orientation. Modern sensor sub-systems also perform basic gesture or activity recognition, which is executed on their ASIP [2]. The signals acquired from IMU sensors are mostly equidistantly sampled timeseries of multiple dimensions whose sampling frequencies typically span from a few hertz up to one or two kilohertz, which however varies depending on the application domain. In human gesture and activity recognition systems, typical sampling frequencies range from 25-200Hz. In Figure 1.2, the signal from an accelerometer attached to the foot of a walking person is depicted.

In the thesis at hand, sensor-based human activity recognition refers to the classification of human gestures or activities from signals that are derived from IMU sensors, which are attached to the human body, e.g., in form of wearable devices.

Figure 1.1: BMI260 IMU sensor from Bosch Sensortec GmbH. From [1].

2 1 Introduction

Figure 1.2: Sensor signal acquired from an accelerometer attached to the foot of a walking person.

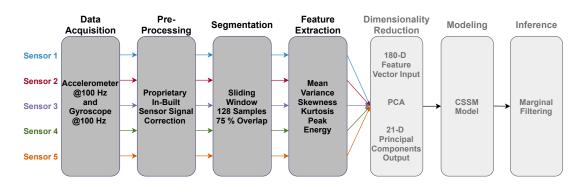

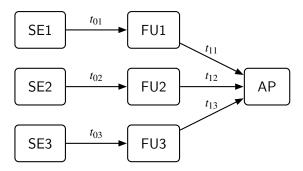

The general principle of sensor-based human activity recognition was summarized by Bulling et al. in [3], in terms of an Activity Recognition Chain (ARC). An ARC consists of several processing stages from raw sensor signals to the final classification results, that can be typically found in state-of-the-art HAR systems in the literature. Generally, the stages involve *data acquisition* from inertial sensors in the first place, and a following *pre-processing*, e.g., the application of smoothing, low-pass, or high-pass filters, or general signal enhancement approaches. The pre-processed, potentially infinitely long signals are then segmented into finite lengths, e.g., by a sliding window, in the *segmentation* stage. For each segment, descriptive features are calculated in the *feature extraction* stage. The resulting feature vectors of each segment are then classified by an appropriate classification algorithm in the *classification* stage. However, due to the possibly high number of dimensions of the feature vector, which can cause a poor discriminative performance of the classification algorithm, a *dimensionality reduction* stage is often implemented after feature extraction, in order to transform the high dimensional feature vector into a lower dimensionality in which decisive characteristics are still retained. Principle Component Analysis (PCA) or Linear Discriminant Analysis (LDA) are commonly applied methods for dimensionality reduction.

Although many HAR systems follow this general pattern, the variety of methods that are utilized for each stage is huge. In the data acquisition stage, sensor data can be sampled from accelerometers, gyroscopes, magnetometers, or a combination of these, which have different energy consumption demands. Pre-processing can range from no pre-processing, to simple moving average filters to computationally intensive sensor fusion algorithms, e.g., Kalman filters. Segmentation methods are typically sliding window approaches. However, window sizes and overlaps have a huge impact on the run time of the feature extraction stage, and on the frequency with which subsequent stages are executed. Other approaches involve segmentation algorithms which lead to dynamically sized windows. Feature extraction can be composed of statistical moments like mean and variance, which can be efficiently computed, but also computationally intensive frequency domain features which involve a Fast Fourier Transform (FFT) to be computed. Therefore, size and type of features have a huge impact on the computational effort, energy consumption, and computation time. Dimensionality reduction is typically performed by PCA or LDA, which have a typically small computational overhead, but again depend on the dimensionality of the input and the output of the stage. Finally, for classification, a huge amount of algorithms exist, ranging from computationally lightweight classifiers like, decision trees, to more computationally intensive algorithms like Support Vector Machines (SVM). Furthermore, computation time and memory demands of classification algorithms are usually a trade-off between

training time and run time. For example, the training time of k-Nearest Neighbors (k-NN), is usually zero<sup>1.1</sup>, as the complete set of training features is provided at run time, to find the k nearest feature vectors in the feature space and classify the sample under test by a majority voting of the k nearest feature vector classes. Execution time for classification and memory consumption therefore depend on the size of the training dataset. On the contrary, other classification algorithms, e.g., SVMs, might need an increased execution time for training to adjust discrimination functions adequately, but a shorter execution time for classification at run time. This variety of parameters and algorithms in each stage leads, therefore, to disparate HAR systems w.r.t. computational effort, memory consumption, and latency, finally depending on the anticipated application, activities to be recognized, and the available sensor sources and their quality. Note that Artificial Neural Networks (ANN) are considered as possible classifiers in the classification stage of the ARC. Yet, due to the focus on systems that follow the ARC structure, approaches that are processing all the steps contained in an ARC in a single ANN with many layers, i.e., deep learning approaches, are not considered in this work in general. However, this limitation could be relaxed for ANNs, which can be structured as several stages that could be processed in a pipelined or distributed manner, e.g., based on a certain degree of sparsity in the weights. This approach however, requires further research and is not covered in this thesis.

Despite the variety of possible ARC setups, many HAR systems share a similar set of requirements, which are first and foremost functional properties regarding recognition accuracy. However, when a suitable ARC setup for the anticipated application has been developed and tested regarding its recognition accuracy, the transformation into a final system must satisfy requirements on extrafunctional properties. In the thesis at hand, the extra-functional properties of interest are real-time performance, latency, and energy consumption. Real-time performance denotes the ability of the HAR system to process the stream of continuously sampled sensor data during run time of the system, without the loss or congestion of sensor data at any ARC stage. As a result, the system throughput is a direct indicator of its real-time performance, which has to be higher than the highest input data rate that can be expected during run time of the system. Latency is defined as the time from sampling a particular sensor sample, until the classification result of the corresponding segment containing that sample is computed by the HAR system. As multiple samples are usually contained in a segment, and segment size can vary, the worst-case latency is decisive. Finally energy consumption of the system, or of components of the underlying hardware architecture is of importance as, e.g., for wearable devices, it directly influences the time until the batteries are drained and thus impacts the usability of the system.

Typically, HAR systems premise all of the aforementioned requirements, but however, these strongly depend on the anticipated application. As an example, the latency requirements of an assistive system for kitchen tasks may be rather relaxed in the range of seconds. An industrial worker assistive system in contrast, may have a requirement of a few milliseconds or even microseconds on latency for the detection of an emergency situation, in order to stop machinery like, e.g., industrial robot arms, to prevent any harm to the worker. Likewise, requirements on throughput and energy consumption are depending on the activities to be recognized, anticipated sensor sampling rates that are required for the recognition task at hand, and on deployed hardware and batteries.

Apart from the aforementioned, there are many more requirements on HAR systems, e.g., memory utilization, robustness, or security, which however, are out of scope in the thesis at hand.

<sup>&</sup>lt;sup>1.1</sup>Here, a standard k-NN approach is assumed, without optimizations as, e.g., space partitioning data structures like K-D-Trees [4], the construction of which would include additional pre-processing.

4 1 Introduction

### 1.1 Problem Statement and Approach

Although many technological, algorithmic, and conceptual approaches exist to accelerate sensor-based human activity recognition systems and to reduce energy consumption of utilized hardware components, the impact of proposed optimizations highly depends on the particular software and hardware that is deployed. Generalized statements about their improvement factor are thus not possible and have to be evaluated per application. Furthermore, the software complexity of human activity recognition systems is steadily increasing by means of individual processing stages from the acquisition of sensor data until the final inference of the currently performed gesture or activity. Likewise, the hardware architecture that is used for human activity recognition systems is getting increasingly complex as well. Sensor subsystems with integrated on-chip microcontrollers for sensor fusion and pre-processing, are combined with low-power wireless controllers on wireless sensor nodes. Possible processor architectures for data aggregation from multiple wireless sensors, i.e., of smartphones, tablets, smart watches, or dedicated on-body devices, are composed of heterogeneous processing units ranging from of ultra low power microcontrollers for data aggregation, heterogeneous general purpose processors (GPPs), to powerful digital signal processors (DSPs), graphics processing units (GPUs), and ASIPs. Further processing units are located in the vicinity of protagonists like home servers, processor architectures in cars, or assistive systems in public buildings or offices. Due to their static location and constant power supply, these can be deployed with powerful Multi-Processor Systems-on-Chip (MPSoCs). The communication between hardware components is composed of equally diverse standards, that are low-power wireless standards like Bluetooth Low Energy (BLE), Narrowband-IoT, or LoRa for unobtrusive and small devices with respectively small batteries, to high throughput standards like WiFi and 5G connecting devices that are less battery-constrained like static servers or wearable devices with increased battery technology and capacities. The resulting possibilities of a suitable hardware platform for human activity recognition systems are huge and constitute a likewise complexity that has to be managed by the system designer. However, the distribution of software to hardware has a huge impact on important extra-functional properties like latency, throughput, and energy consumption. Substantiation of design decisions based on prototype implementations and measurements of said extra-functional properties is unfeasible considering the huge design space spanned by the number of possible software to hardware mappings. In order to approach this problem, design-time analysis methods are crucial to reduce time to market and still provide system designs that meet necessary requirements.

A possible solution are model-based design and analysis approaches. In a model-based design flow, software and hardware are specified as formal models, with which hardware selection, software mapping, and scheduling decisions can be formally specified as a design point. Furthermore, design points can be formally evaluated with respective analysis and optimization methods that have been developed for the modeling formalism that is used. Moreover, analysis results of different design points can be compared, in order to substantiate design decisions at design time.

The thesis at hand proposes a model-based design and analysis of energy-efficient sensor-based online human activity recognition systems to address the aforementioned open problems. The model-based approach is based on Models of Computation (MoC) that have become a quasi-standard in the design of signal processing and streaming applications, i.e., dataflow graph models. To this end, the thesis at hand deals with the following research questions:

## RQ1 Which dataflow MoC is suitable to capture state-of-the-art human activity recognition systems?

There exists a variety of dataflow MoCs that differ in analyzability and expressiveness. As a general trend, the analyzability of available dataflow MoCs decreases with expressiveness. To this end, suitable MoCs have to be identified, that are expressive enough to capture state-of-the-art human activity recognition systems, but still allow for the analysis of important extra-functional properties like latency, throughput, and energy consumption at design time.

# RQ2 How can important extra-functional properties be accurately analyzed from dataflow graph models?

While there exist a plethora of formal analysis techniques for dataflow graphs regarding timing behavior, comparably little research has been undertaken towards the estimation of energy consumption from dataflow graph models in the literature. Furthermore, the accuracy of energy analysis approaches is of interest.

# RQ3 Can existing conceptual optimizations regarding latency, throughput, and energy consumption of sensor-based human activity recognition systems be represented in dataflow graph models?

As indicated earlier, many optimization techniques exist in the literature, that reduce energy consumption and improve timing behavior of human activity recognition systems. However, the impact thereof highly depends on the application structure and hardware selection. Since generalized assumptions on the improvement factor are not possible, a model-based approach should be able to represent such optimizations and their impact should be quantifiable at design time.

# RQ4 Can dynamic behavior of human activity recognition systems be captured by dataflow graph models and corresponding analysis methods?

Many human activity recognition systems are subject to changes at run time, which are based on data-dependent, context-aware, or hardware-related changes in order to improve recognition accuracy, decrease latency, or conserve energy of deployed battery-powered devices. Dynamic behavior is a challenging aspect in the model-based representation of applications, as it often requires a certain degree of expressiveness that contrasts its analyzability. While there exist dataflow MoCs that allow to model a certain degree of dynamic behavior, the proposed model-based analysis techniques w.r.t. energy consumption indicators should be extendable to such MoCs.

In the following section, the contributions of the thesis at hand towards the aforementioned research questions are summarized.

6 1 Introduction

### 1.2 Contributions

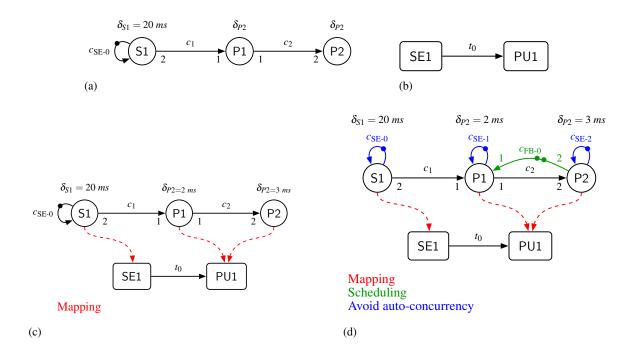

Model-based design and analysis approach of sensor-based human activity recognition systems (Chapter 3) The key contribution of the thesis at hand, is a novel design approach for sensor-based human activity recognition systems based on well-known models of computation, i.e., dataflow graphs. General system structures of HAR systems in the literature have been identified and translated into a model-based representation, allowing further analysis methods to be applied. Based on existing analysis methods, novel approaches have been developed to analyze key properties w.r.t. energy efficiency from dataflow models at design time, that are processor utilization and data communication rate on hardware components. Due to the integration of the input data process into models, introduced analysis methods are enabled to evaluate worst-case behavior at design time.

Energy consumption estimation of hardware components (Chapter 3) Based on the aforementioned analysis methods regarding processor utilization and data transmission rates, energy consumption models have been introduced that capture the relationship to said indicators, allowing to quantify effects of decisions at design time. Introduced energy consumption models differ from existing approaches in the sense, that a long-run average estimate on energy consumption rate can be acquired, in contrast to an absolute energy consumption w.r.t. an execution of a particular sequence of instructions. The latter neglects the rate which the sequence of instructions is executed with. Energy consumption models are estimated from measurements in the thesis at hand which, however, is orthogonal to existing approaches, i.e., can be acquired formally, as proposed in existing literature. Finally, energy consumption models are separated from the dataflow representation of the software and annotated to components of the hardware model, allowing to abstract and encapsulate technological aspects into separate models.

System-level parallelization on multi-processor architectures (Chapter 4) Introduced model-based design and analysis approaches are evaluated w.r.t. their ability to represent state-of-the-art parallelization approaches of computationally intensive processing stages within human activity recognition systems on multi-processor architectures. The representation of system-level parallelization into system models allows to evaluate corresponding effects of system throughput, latency, and the distribution of processor utilization at design time. Furthermore, their trade-offs can be considered to substantiate design decisions and possibilities for further reduction of energy consumption, i.e., clock-gating or dynamic voltage and frequency scaling, can be assessed.

Scenario-based dynamic behavior (Section 5.1) The proposed modeling and analysis approaches have been extended to existing models of computation, that allow the representation of a certain degree of dynamic behavior. That is, dynamic changes between a finite set of static scenarios. This allows, to represent human activity recognition systems, that change their system configuration at run time based on the environment, i.e., context awareness, system properties like battery-level-dependent dynamic sensor or feature selection of wireless sensor nodes, or data-dependent data reduction algorithms like piecewise linear approximation of sensor signals, that confine to a small finite set of static behaviors. Aforementioned approaches have been introduced in the literature to increase recognition accuracy and reduce energy consumption of human activity recognition systems. In order to substantiate design decisions regarding their deployment for the anticipated application, their impact must be quantifiable at design time. To this end, the model-based design approach in the thesis at hand is extended to models of computation that are expressive enough to allow the representation of dynamic changes

between static scenarios, but are still analyzable w.r.t. key properties. Proposed analysis methods w.r.t, processor utilization have been extended for the selected model of computation.

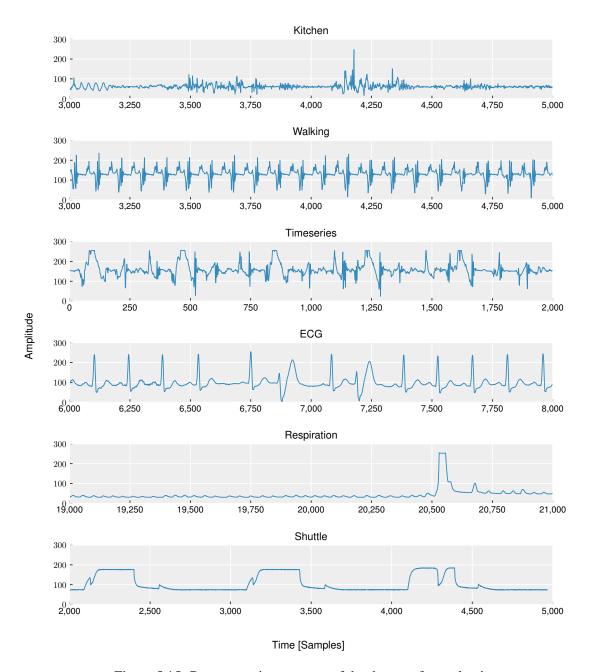

Piecewise linear approximation of sensor signals (Section 5.2) The proposed model-based design and analysis approaches in the thesis at hand, foster awareness of predictability and analyzability of algorithms developed for energy-efficient online human activity recognition systems. A key aspect in this regard is the data-independent timing behavior of algorithms. Apart from model-based design and analysis, the thesis at hand contributes to the algorithmic optimization of existing data- and thus energy consumption reducing techniques based on piecewise linear approximation of sensor signals. Two novel piecewise linear approximation algorithms are proposed in the thesis at hand, that advance existing methods, towards a small and constant per-sample execution time and memory complexity w.r.t. their compression ability. As a result, their execution time per sensor sample and their memory utilization is small enough to be implemented on resource constrained sensor sub-systems without compromising any functional properties regarding their approximation quality. More importantly, their execution time is predictable at design time, allowing them to be modeled and analyzed with the approaches proposed in the thesis at hand.

#### 1.3 Author's Publications

Most of the work presented in this thesis has been previously published by the author. The thesis at hand refines and unifies published concepts and results and provides a consistent presentation of such. In the following, a summary is presented, that relates the key aspects of each chapter to the corresponding publications of the author in which they were initially introduced. Furthermore, the author's contributions to the corresponding publications are highlighted.

Energy-Efficient Sensor Networks (Chapter 3) In Chapter 3, the modeling approach for wireless on-body sensor networks in the context of human activity recognition systems is presented. The motivation of trading-off energy consumption of different hardware components based on their workload stems from initial studies on the topic which was presented in [G1]. The author of this thesis has developed the main concept, performed implementation, and conducted the experiments in [G1]. Furthermore, the analysis of processor utilization as well as data communication rate from dataflow graph models of wireless sensor networks in human activity recognition systems was introduced in [G2] and [G3] and the concept of corresponding energy consumption models was published in [G4]. The author of the thesis at hand developed the presented concepts and implemented, performed, and evaluated corresponding experiments.

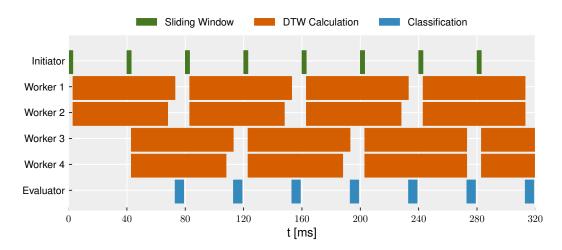

Thread-Level Parallelism (Chapter 4) In Chapter 4, the dataflow-based modeling of parallelization strategies for online gesture and activity recognition systems is presented and evaluated on experimental implementations in different configurations. Model-based analysis results are evaluated with measurements from the experiments. The experimental implementation and evaluation of the presented parallelization approaches have been published in [G5] and [G6]. In [G6], a first dataflow graph model has been introduced to capture respective parallelization approaches, which has been later refined for the thesis at hand, based on the modeling approach in [G2]. The author of the thesis at hand, developed the respective concepts and implemented, performed, and evaluated corresponding experiments in the aforementioned publications.

8 1 Introduction

Scenario-Based Dynamic Behavior (Section 5.1) In Section 5.1, the modeling and analysis approaches are extended to scenario-aware dataflow graphs to support the representation of dynamic changes between static scenarios in the system models. Analysis methods w.r.t. processor utilization have been adapted to the selected MoC. The basic concept of using scenario-aware dataflow graphs as a MoC and a corresponding analysis technique towards processor utilization, was initially published in [G7]. The modeling approach and especially the analysis of processor utilization is thoroughly refined in the thesis at hand, including its limitations to the application domain. The author of this thesis developed the concept and implemented, performed, and evaluated the experiments in [G7]. The analysis of scenario occurrence probabilities from scenario-aware dataflow graphs was conceived and implemented by the co-author Bart D. Theelen.

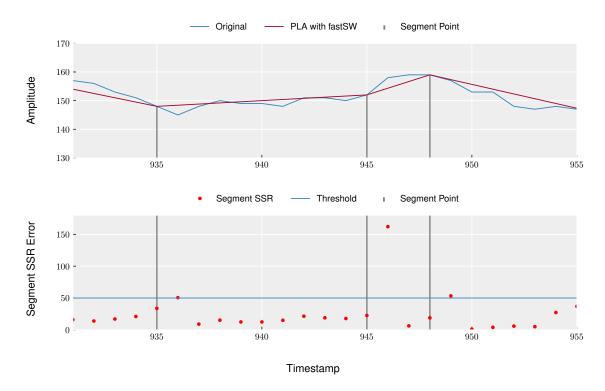

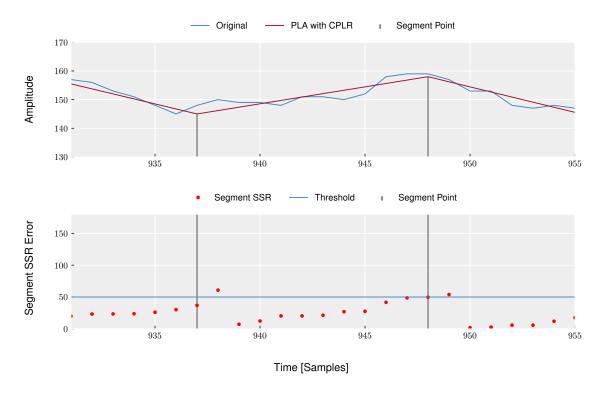

**Data-Dependent Dynamic Behavior (Section 5.2)** In Section 5.2, two novel piecewise linear approximation algorithms for sensor signals are introduced, i.e., CPLR and fastSW. The concept, implementation, and evaluation of CPLR was previously published in [G8]. The concept and implementation of fastSW has not been published at the time of submission of the thesis at hand. The presented evaluation of fastSW in Section 5.2 is based on and integrated into the experimental evaluation of CPLR presented in [G8]. The author of this thesis developed the concept and implemented, conducted, and evaluated the experiments in [G8] and conceived and implemented fastSW.

In the thesis at hand, model-based system-level design and analysis approaches for sensor-based human activity recognition systems are introduced, with which extra-functional properties can be acquired at design time in order to evaluate different system configurations early in the design process. The introduced approaches are based on formal models, i.e., dataflow-based MoCs, and their respective analysis methods. The fundamentals regarding dataflow MoCs on which this thesis builds on are discussed in Section 2.1. In Section 2.2, the system modeling approach that is used throughout the thesis is introduced.

### 2.1 Dataflow Models of Computation

In the literature exist several dataflow MoCs with a considerable range in expressiveness, analyzability, and implementation efficiency [5]. As a general trend, analyzability is inversely proportional to the expressiveness. However, analyzability is generally desirable, e.g., schedules that can be derived at design time, can be implemented statically or quasi-statically and therefore avoid overheads at run time. In contrast, expressiveness is important as well, as with more expressive models, the behavior of the system under design can be captured more accurately. As a result, the selection of appropriate MoCs is a trade-off between analyzability and expressiveness

The MoCs that have been used for modeling HAR systems in the thesis at hand are introduced in the following together with a short reasoning about the respective choices. For a review and classification of a broader range of dataflow MoCs, the interested reader is referred to [5].

#### 2.1.1 Synchronous Dataflow Graphs

Synchronous Dataflow (SDF) graphs are weighted directed graphs and have been introduced by Lee and Messerschmitt in [6]. A notion of timing is associated with SDF graphs, in order to allow analysis of schedules or throughput at design time [7]. In the following, timed SDF graphs are assumed when referred to SDF graphs. Let  $\mathbb{N} = \{1,2,3,\ldots\}$  denote the set of natural numbers. Furthermore, the set of non-negative integers is denoted by  $\mathbb{Z}_{0+} = \{0,1,2,3\ldots\}$  and analogously  $\mathbb{R}_{0+}$  denotes the set of non-negative real numbers including zero.

**Definition 1 (SDF graph)** An SDF graph  $G = (V, E, prod, cons, D_0, \delta)$ , consists of a set of vertices V, directed edges  $E : V \times V$ , production rates  $prod : E \to \mathbb{N}$ , consumption rates  $prod : E \to \mathbb{N}$ , an initial token distribution  $D_0 : E \to \mathbb{Z}_{0+}$ , and an execution time function  $\delta : V \to \mathbb{T}$ .

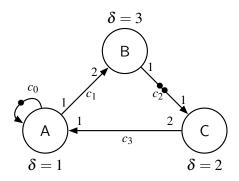

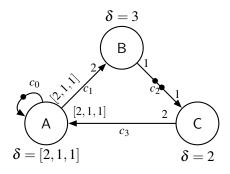

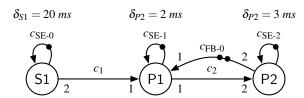

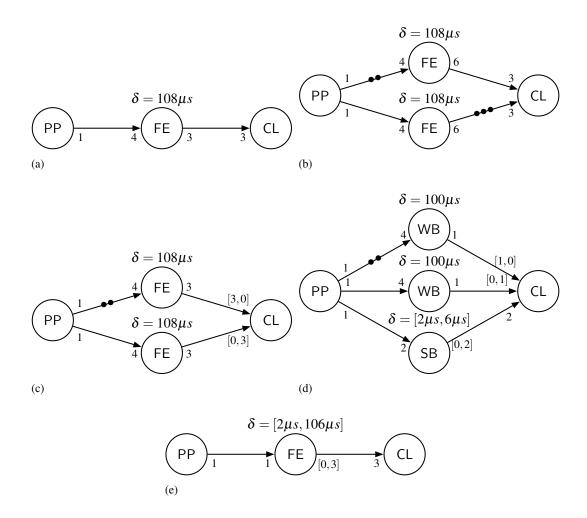

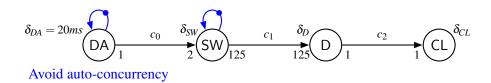

In Figure 2.1, an example of an SDF graph is depicted. Vertices of SDF graphs, so-called *actors V* (A, B, and C in Figure 2.1), are representing function executions and communicate data over unidirectional *channels* with First-In-First-Out (FIFO) semantics, represented by edges  $e = (v, v') \in E$  ( $c_0, c_1, c_2$ , and  $c_3$  in Figure 2.1). Actors v and v' are said to be the source and destination of e = (v, v'), denoted by src(e) and dst(e), respectively. Presence and number of (units of) data on channels is represented by tokens. A number of *initial tokens*  $D_0(e)$  is associated with each channel  $e \in E$ , which is depicted with bullets and can be found on channels  $c_0$  and  $c_2$  in Figure 2.1. In general, each bullet represents one initial token. Alternatively, for the sake of readability, a number next to a bullet may represent the corresponding number of initial tokens. The number of tokens a source actor v produces on an outgoing channel  $e = (v, v') \in E$  is represented by the production rate prod(e) of e. Likewise, the number of

Figure 2.1: Example of a synchronous dataflow graph.

tokens a destination actor  $v' \in V$  consumes from an incoming channel  $e = (v, v') \in E$  is denoted by the consumption rate cons(e) of channel e. Production and consumption rates of channels are expressed as numbers next to edges, e.g.  $prod(c_1) = 1$  and  $cons(c_1) = 2$  in Figure 2.1. For the sake of readability, edges whose production or consumption rates equal one, may be visualized without the corresponding annotation. For example, edge  $c_0$  has a production and consumption rate of  $prod(c_0) = cons(c_0) = 1$  in Figure 2.1. Actor delays  $\delta(v)$  specify an execution time of represented functions and can either be continuous ( $\mathbb{T} = \mathbb{R}_{0+}$ ) or discrete ( $\mathbb{T} = \mathbb{Z}_{0+}$ ). Typically, the latter is the case, which is depicted in Figure 2.1 with annotations next to actors, e.g.,  $\delta(A) = 1$ . Actors without delay annotations are assumed to have zero delay, if not otherwise indicated.

The *channel state* of an SDF graph G is captured by a function  $D: E \to \mathbb{Z}^{0+}$ , that assigns a number of tokens to each channel of G. The channel state of an SDF graph dictates, whether actors are *enabled* to *fire* or not.

An actor is enabled to fire, if a minimum number of tokens, denoted by the consumption rate, is present on each input edge, i.e., an actor v is enabled to fire if  $\forall e = (v', v) \in E : D(e) \geq cons(e)$  holds. When an actor  $v \in V$  fires, cons(e) tokens are removed (consumed) from each incoming edge  $e = (v', v) \in E$  and prod(e') tokens are added (produced) on all outgoing edges  $e' = (v, v'') \in E$  after  $\delta(v)$  time units. In Figure 2.1, only actor C is enabled to fire in the depicted initial channel state.

If the channel state allows, SDF graphs explicitly permit the simultaneous firing of multiple instances of the same actor. This behavior is referred to as *auto-concurrency* and can be constrained by a self-edge  $((v,v) \in E)$  on an actor v with unit production and consumption rate and as many initial tokens as maximal simultaneous firings are desired. In Figure 2.1, the auto-concurrency of actor A is eliminated by self-edge  $c_0$  with unit production and consumption rate and a single initial token. As a result, only a single instance of actor A can be fired at a time, forcing a sequential execution. Self-edges can thus be used to model stateful functions. In contrast, actors B and C are allowed for simultaneous firings. In particular, two instances of actor C are enabled to fire in the initial channel state depicted in Figure 2.1.

**Definition 2 (Consistency)** Let  $\widetilde{\gamma}_G : V \to \mathbb{N}$ , denote a vector, that for each actor  $v \in V$  assigns a number of firings. If a vector  $\widetilde{\gamma}_G$  exists that solves the balance equations  $\forall e = (v, v') \in E : \widetilde{\gamma}_G(v) \cdot prod(e) = \widetilde{\gamma}_G(v') \cdot cons(e)$ , the SDF graph is said to be consistent, i.e., the execution of all actors  $v \in V$  firing exactly  $\widetilde{\gamma}_G(v)$  times, has no net effect on the token distribution of the SDF graph G.

The same channel state of a consistent SDF graph is revisited after  $\widetilde{\gamma}_G(v)$  respective firings of all  $v \in V$ . This furthermore implies, that for a consistent SDF graph, infinitely many vectors  $\widetilde{\gamma}_G$  exist, i.e., all integer multiples of  $\widetilde{\gamma}_G$  solve the balance equations as well. The smallest of such vectors  $\gamma_G = \min \widetilde{\gamma}_G$  with  $\gamma_G(v) \in \mathbb{N}$  for all  $v \in V$  is referred to as *repetition vector*. As a result, the existence of a repetition vector indicates consistency. The example SDF graph in Figure 2.1 is consistent and has a repetition vector of  $\gamma = [2, 1, 1]^T$  with corresponding order  $[A, B, C]^T$ . Hence, A has to be fired twice and both B and C have to be fired once to reach the initial channel state again.

**Definition 3 (Iteration)** *If*  $G = (V, E, prod, cons, D_0, \delta)$  *is a consistent SDF graph, with repetition vector*  $\gamma_G$ , a set of executions in which each actor  $v \in V$  fires exactly  $\gamma_G(v)$  times, is called an iteration.

Consistency guarantees that a channel state of an SDF graph is revisited after a single execution of an iteration. Thereafter, an infinite sequence of iterations can be executed with finite buffer sizes.

**Definition 4 (State)** Let  $G = (V, E, prod, cons, D_0, \delta)$  be a timed SDF graph. Its state can be captured by a tuple  $S = (D, \tau)$ , with D denoting the channel state of G, and  $\tau : V \to \mathbb{T}^*$  a time structure<sup>2.1</sup>, that assigns remaining execution times to all instances of an actor that concurrently execute [8]. The initial state of G is thus,  $(D_0, \tau_0)$ , with  $\forall v \in V : \tau_0(v) = \{\}$ .

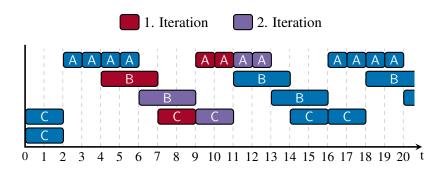

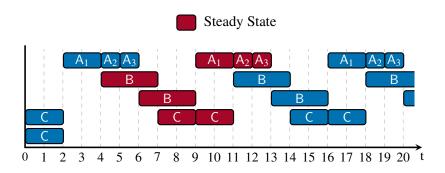

The timing of SDF graphs allows the analysis of timing behavior or schedules. Since execution times may vary due to different hardware aspects like caches, branches, or interrupts, a fully static schedule is often not practical. As a solution, actors are annotated with worst-case execution times of the functions that they represent. This permits so-called *self-timed* schedules [9]. In a self-timed schedule, each actor fires as soon as it is ready to fire. This allows an ordering on actor executions to be determined at compile time when annotated with worst-case execution times, which can be deployed without timing information in a final implementation, thus avoiding run-time scheduling overheads. Furthermore, by assuming self-timed execution, formal analysis of timed SDF graphs considers the best possible timing behavior. In Figure 2.2, the self-timed execution of the SDF graph from Figure 2.1 is depicted.

Due to timing of actors, the initial state  $s_0 = (D_0, T_0) \in S$  may not be reached again in the self-timed execution. However, in [8], Ghamarian et al. prove, that consistent and strongly connected timed SDF graphs reach a steady state in the self-timed execution after a so-called transient phase, i.e., a recurring state  $s' \in S$  is revisited periodically. Ghamarian et al. show furthermore that, for strongly connected and consistent SDF graphs, the steady state in the self-timed execution is an integer multiple (including zero) of an iteration. Note that a zero multiple of an iteration indicates a deadlock. However, efficient methods to check for deadlock freedom in SDF graphs exist as well [6, 8]. In the thesis at hand, only consistent and deadlock-free SDF graphs are considered.

In Figure 2.2, the SDF graph is in its initial state  $s_0 = ((1,0,2,0), \{\{\}, \{\}, \{\}\})$  at time 0 and starts with an immediate state transition to  $((1,0,0,0), \{\{\}, \{\}, \{2,2\}\})$  by starting to fire two instances of C at time 0. The steady-state of the self-timed execution begins at time 4 in state  $((0,0,0,1), \{\{1\}, \{3\}, \{\}\})$ . Note that multiple state transitions without time progress are represented by a combined transition and thus actor A and B started their firing in the final state at time 4 already. The same state is revisited at time 11 after two graph iterations. As a result, the steady-state period takes 7 time units to execute. It is important to note that iterations can overlap in time, as it can be seen in Figure 2.2.

$<sup>^{2.1}</sup>$ Here,  $\mathbb{T}^*$  denotes the Kleene star operator  $^*$  on the set  $\mathbb{T}$ , representing the set of all possible sequences of elements from the set  $\mathbb{T}$ , including the empty set  $\{\}$ .

Figure 2.2: Self-timed schedule of the example SDF graph in Figure 2.1.

In the thesis at hand, strong connectedness is not assumed generally. As a result, the self-timed execution of an arbitrary consistent and deadlock-free SDF graph can lead to unbounded channels [10]. Hence, a self-timed schedule is not guaranteed to form a periodical phase in the execution state space. However, Ghamarian et al. introduce in [10] the property of so-called *self-timed boundedness* and a corresponding analysis method. Self-timed boundedness guarantees, that an arbitrary consistent and deadlock-free SDF graph can execute infinitely often in a self-timed schedule with finite buffer sizes on its channels. The maximum achievable average rate, at which an iteration of a consistent SDF graph G can be executed with finite buffer sizes of all its channels  $e \in E$ , is referred to as the *throughput* TH(G) of graph G. Furthermore, the corresponding maximal average rate at which an actor  $v \in V$  of a consistent SDF graph G can be executed with finite buffer sizes of all its channels  $e \in E$ , is referred to as *actor throughput* TH(v). Due to its consistency, the relationship between TH(G) of SDF graph G and TH(v) and TH(v) of any actors  $v, v' \in V$  is:

$$\forall v, v' \in V : TH(G) = \frac{TH(v)}{\gamma_G(v)} = \frac{TH(v')}{\gamma_G(v')}.$$

(1)

In [10], it is shown, that the throughput of a consistent and deadlock-free SDF graph G, corresponds to the self-timed execution of G if G is self-timed bounded. Furthermore, Ghamarian et al. show in [10], how the throughput TH(G) of an arbitrary consistent and deadlock-free SDF graph G can be acquired by subsequently calculating the throughput of all its Strongly Connected Components (SCCs).

In the thesis at hand, the average time between two consecutive iteration executions in a schedule of a consistent SDF graph G that achieves the throughput TH(G) is referred to as the *average iteration period*  $T_G$ , and is calculated by:

$$T_G = \frac{1}{TH(G)}. (2)$$

The average iteration period of the example SDF graph in Figure 2.1, is 3.5 and its corresponding throughput is  $\frac{1}{3.5}$ .

There exist many different techniques to analyze the throughput of SDF graphs in the literature. A straight forward method is the transformation of an SDF graph in its corresponding Homogeneous Synchronous Dataflow (HSDF) graph, which is the equivalent of the SDF graph w.r.t. actor firings, however with unit production and consumption rates on edges, and a maximum of one initial token on any edge. Furthermore, in contrast to SDF, HSDF graphs are multigraphs, i.e., multiple equally directed edges can exist between two actors. The transformation of an SDF graph into its equivalent

HSDF representation is described in [7]. From this HSDF representation, the throughput of the corresponding SDF graph can be calculated by a Maximum Cycle Mean (MCM) or Maximum Cycle Ratio (MCR) analysis. For a detailed description of SDF to HSDF transformation and a review and comparison of MCM and MCR analysis methods, the interested reader is referred to [7] and [11], respectively. Although originally limited to strongly connected SDF graphs, throughput analysis based on HSDF conversion can make use of the techniques presented in [10], in order to check for self-timed boundedness or to analyze the maximum achievable throughput for bounded executions. Since conversion from SDF to HSDF graphs may result in an exponential growth of the graph, a more efficient method for acquiring the throughput of SDF graphs from their execution state space is explained in [8]. However, this approach is restricted to strongly connected SDF graphs. De Groote et al. introduced another improvement in [12], that converts an SDF graph into a more reduced representation than HSDF graphs, i.e., Linear Constraint Graphs (LCGs), that allow the throughput computation in a shorter time and a more compact representation than HSDF graphs in many cases. Again, that approach can be applied to arbitrary consistent and deadlock-free SDF graphs with the techniques from [10].

Throughput of consistent and deadlock-free SDF graphs is an essential property on which the proposed methods in the thesis at hand are based on. A tool, that has been extensively used for the evaluations in the thesis at hand is the SDF<sup>3</sup> framework of Stuijk et al. [13]. The SDF<sup>3</sup> framework implements a parser for SDF graphs represented in XML format and offers a wide range of analysis techniques, including consistency, deadlock freedom, repetition vector, and throughput.

Their static consumption and production rates as well as execution times allow for a variety of analyses of SDF graphs at design time. However, their expressiveness is limited and often demands a high abstraction and overestimation when modeling and analyzing state-of-the-art dataflow-oriented applications, leading to pessimistic results. Therefore, a more expressive MoC, that still allows for design-time analysis of properties, that the approaches in the thesis at hand build on, is explained in the following section.

### 2.1.2 Cyclo-Static Dataflow Graphs

The Cyclo-Static Dataflow (*CSDF*) MoC was introduced by Bilsen et al. in [14] as an extension of a special form of SDF graphs, namely SDF graphs without the ability for auto-concurrency. Such SDF graphs are extended by the concept of cyclic changing behavior. A formalization of the CSDF concept as a proper extension of SDF graphs, i.e., allowing auto-concurrency, was introduced by Stuijk et al. in [15]. Furthermore, Stuijk et al. introduced a formalization of execution times to CSDF actors, similar to timed SDF. In the thesis at hand, the definition of CSDF graphs is based on this formalization. Let  $i \mod_1 n$  be shorthand notation for  $(i-1) \mod n+1$ , with mod defined as the modulo operator, i.e.,  $a \mod b = a - b \mid \frac{a}{b} \mid$ .

**Definition 5 (CSDF graph)** A CSDF graph G is defined by  $G = (V, E, p, c, D_0, d)$  with vertices V, edges  $E : V \times V$ , production rates  $p : E \to \mathbb{Z}_{0+}^n$ , consumption rates  $c : E \to \mathbb{Z}_{0+}^n$ , an initial token distribution  $D_0(e) : E \to \mathbb{Z}_{0+}$ , and a delay function  $d : V \to \mathbb{T}^n$ .

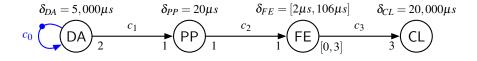

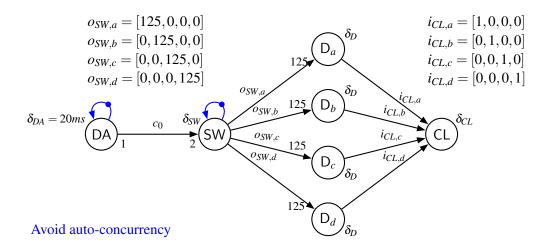

In Figure 2.3, an example CSDF graph is depicted. Similar as timed SDF graphs, CSDF graphs are composed of actors  $v \in V$  represented by vertices, e.g., A, B, and C in Figure 2.3. Actors  $v \in V$ and  $c_3$  in Figure 2.3). Presence and number of tokens on channels, i.e., the channel state is represented by D(e), with initial channel state  $D_0(e)$ , that is depicted by bullets in term of number and presence on edges, e.g., on channels  $c_0$  and  $c_2$  in Figure 2.3. In CSDF, actors  $v \in V$  are associated with a number of phases  $\phi(v) \in \mathbb{N}$ . The phases represent different behaviors of actors that change in a cyclic manner. Accordingly, the production rates  $p(e) = [p_1, p_2, \dots, p_{\phi(v)}]$  and consumption rates  $c(e') = [c_1, c_2, \dots, c_{\phi(v)}]$  of edges  $e = (v, v') \in E$  and  $e' = (v'', v) \in E$  that an actor  $v \in V$  is connected to as source or destination actor, respectively, are sequences of length  $\phi(v)$ . Furthermore, associated delays  $d(v) = [d_1, d_2, \dots, d_{\phi(v)}]$ , representing execution times of an actor  $v \in V$ , are sequences of size  $\phi(v)$ . Execution time sequences d(v), production rate sequences  $p(e), e = (v, v') \in E$ , and consumption rate sequences  $c(e'), e' = (v'', v) \in E$ , represent the behavior of actor  $v \in V$  in its different phases that repeat with a period of  $\phi(v)$ , with  $\forall v \in V, \forall e = (v, v') \in E, \forall e' = (v'', v) \in E : |p(e)| = |c(e')| =$  $|d(v)| = \phi(v)$ . Edges without annotations, are assumed to have unit production and consumption rates in each phase of its source and destination actor, respectively. In Figure 2.3, actor A has three phases, and produces 2 and 1 tokens on channel  $c_1$  and  $c_0$ , respectively, consumes two and one tokens from channels  $c_3$  and  $c_0$ , respectively, and has an execution time of two, in its first firing. Furthermore, CSDF actors  $v \in V$  with  $\phi(v) = 1$  resemble SDF actors. In Figure 2.3, actors B and C each have one phase and thus resemble SDF actors. The number of tokens produced on channel  $e = (v, v') \in E$ by the *i*-th firing of actor  $v \in V$  is represented by function  $prod(e,i) = p_{i \mod_1 \phi(v)}, i \in \mathbb{N}$ . Likewise  $cons(e,i) = c_{i \bmod v} (v), i \in \mathbb{N}$  denotes the number of tokens that actor v consumes from channel e in its *i*-th firing. Finally,  $\delta(v,i) = d_{i \mod_1 \phi(v)}, i \in \mathbb{N}$  denotes the execution time of the *i*-th firing of actor  $v \in V$ .

A CSDF actor v in its current phase  $j \in [1, ..., \phi(v)]$  is enabled to fire, if sufficient tokens on all of its input edges  $(v', v) \in V$  are available, i.e., if  $\forall (v', v) \in E : D(e) \geq cons(e, j)$  holds. When an actor  $v \in V$  fires in its j-th phase, it consumes cons(e, j) tokens from its input channels  $e = (v', v) \in E$ , produces prod(e', j) tokens after  $\delta(v, j)$  time units on all of its output edges  $e' = (v, v'') \in E$ , and changes its phase to  $(j+1) \mod_1 \phi(v)$ . In Figure 2.3, two instances of actor C are enabled in the initial channel state depicted in Figure 2.3. While auto-concurrency of CSDF graphs is assumed throughout the thesis

Figure 2.3: Example of a cyclo-static dataflow graph.

at hand, the presented approaches are applicable for CSDF graphs without auto-concurrent behavior to most extend. This is further detailed at the end of this section.

Note that in contrast to the above definition, the number of phases of all actors  $v \in V$  needs to be equal when using SDF<sup>3</sup> for analysis. The presented methods in [15] however, as well as design and analysis approaches introduced in the thesis at hand, are applicable to CSDF graphs with different lengths of phase sequences among its actors. Furthermore, as stated in [15], the sequence of actor phases can be concatenated for each actor in a way, such that the length of the resulting sequence is equal to the least common multiple of all actors individual lengths of phase sequences before concatenation, to acquire an CSDF graph that can be analyzed with SDF<sup>3</sup>.

The repetition vector  $\gamma_G \in \mathbb{N}^{|V|}$  of a CSDF graph G is composed of  $\gamma_G(v) = \phi(v) \cdot r(v)$  for all actors  $v \in V$ , with  $r \in \mathbb{N}^{|V|}$  being the smallest vector that solves the following balance equations:

$$\forall e = (v, v') \in E : r(v) \cdot \sum_{i=1}^{\phi(v)} prod(e, i) = r(v') \cdot \sum_{j=1}^{\phi(v')} cons(e, j).$$

Similar to SDF graphs, the existence of a vector r and thus a repetition vector  $\gamma_G$  of CSDF graph G guarantees consistency and  $\gamma_G$  describes an iteration of G. Furthermore, after executing an iteration of CSDF graph G, the same channel state as before the execution is reached again. The depicted CSDF graph in Figure 2.3 is consistent and has a repetition vector of  $\gamma = [3,2,2]^T$  with corresponding order  $[A,B,C]^T$ .

In [15], Stuijk et al. generalize from [8]. Hence, the state space of CSDF graphs with bounded storage space consists of a transient phase followed by a steady-state. Consequently, considering the results from [10], the steady-state represents the self-timed execution in case the CSDF graph is self-timed bounded, otherwise it represents the fastest possible schedule in terms of throughput, which can be executed infinitely often with finite buffer size usage on all channels. The self-timed schedule of the example CSDF graph in Figure 2.3, is depicted in Figure 2.4. The CSDF graph is consistent, deadlock free, and strongly connected (and therefore self-timed bounded [10]) and its steady-state begins at time 4 which is revisited at time 11. Its steady-state consists of a single iteration, which is highlighted in Figure 2.4.

Similar to SDF graphs, the throughput TH(G) of a consistent CSDF graph G is defined as the maximum achievable average rate of iterations, that can be executed infinitely often with finite buffer size usage

Figure 2.4: Self-timed schedule of the example CSDF graph in Figure 2.3.

of all channels  $e \in E$ . Accordingly, the actor throughput TH(v) of any actor  $v \in V$  can be derived from the graph throughput TH(G) and the repetition vector entry  $\gamma_G(v)$  by Equation (1). In the thesis at hand, the reciprocal of the throughput TH(G) of a consistent CSDF graph G is denoted as average iteration period  $T_G$ , calculated by Equation (2). The throughput of the example CSDF graph from Figure 2.3, is  $TH(G) = \frac{1}{7}$  and its corresponding average iteration period is thus  $T_G = 7$ .

Throughput of CSDF graphs can be calculated by a transformation into equivalent HSDF graphs and subsequent MCR analysis [14]. For arbitrary consistent CSDF graphs, the subsequent throughput calculation on all SCCs of the HSDF graph can derive the maximum achievable throughput of all infinite schedules with bounded channels [10]. Multiple optimizations have been introduced to transform a CSDF graph into a reduced presentation of SDF graphs [16] or HSDF graphs [12, 17] from which throughput can be calculated by using the techniques of [10].

Since the definition of CSDF graphs in [15] as well the implementation of [13] allow auto-concurrency of CSDF actors, the order of tokens produced on a channel by subsequent firings of an actor can change due to different execution times and thus break so-called *functional determinacy* [17, 18]. That is, in general, the order of actor firings in SDF graphs and thus, the execution times of actors do not influence the result. However, if a concurrent phase of an actor can overtake another, the result might indeed be changed, i.e., the graph is not functionally determinate anymore. However, in the modeling and analysis approach presented in the thesis at hand, analysis models are eliminating auto-concurrency of CSDF actors. Additional actors with enabled auto-concurrency for model refinement may be added to analysis models, as will be explained in Section 4.5.4. However, these additional actors are restricted to SDF actors, which preserves functional determinacy [16].

Due to the cyclic behavior of actors, the CSDF MoC is more expressive than SDF. Although analysis of CSDF graphs may require a higher computational effort, due to subsequent transformations to SDF or directly HSDF graphs and a corresponding increase in graph size [16], design-time analysis of important properties like consistency and throughput is still possible. Thus CSDF graphs allow a tighter modeling of dataflow-oriented applications and systems, that follow a periodic behavior.

However, dynamic behavior, e.g., data-dependent execution, cannot be modeled efficiently with CSDF graphs. There exist a variety of dataflow MoCs allowing for data-dependent behavior, such as Boolean Dataflow (BDF), Dynamic Dataflow (DDF), or Kahn Process Network (KPN), which in general however, are not analyzable w.r.t. throughput, consistency, or deadlock freedom at design time [5]. As a remedy, the scenario-aware dataflow (SADF) MoC allows to represent dynamic behavior that is restricted to a finite number of scenarios for which the behavior is static, but scenario changes can

occur. The SADF MoC is analyzable w.r.t. throughput, consistency, deadlock freedom, and a variety of long-run average metrics, at design time. In the following section, the SADF MoC and the most important properties that can be analyzed from it are explained in more detail.

### 2.1.3 Scenario-Aware Dataflow Graphs

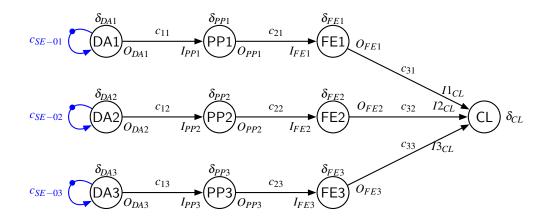

The Scenario-Aware Dataflow (SADF) MoC has been introduced by Theelen et al. in [19]. Scenario-aware dataflow graphs express dynamic behavior in form of finite sets of operational modes of actors with corresponding probabilistic information on possible execution orders. SADF graphs are therefore more expressive than CSDF graphs, but still analyzable at design time.

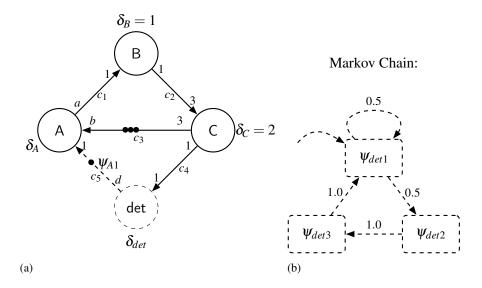

SADF graphs extend SDF and CSDF graphs by the concepts of scenarios. To this end, two kinds of actors exist for SADF graphs, namely *kernels* and *detectors*. Kernels are similar to actors in SDF and CSDF, but can operate in different scenarios. Detectors are special actors, that control the scenarios of kernels. The scenario of a kernel can be controlled by a detector, via a so-called *control channel* that transports *control tokens*, which select the corresponding scenario of the kernel. Dynamic behavior is modeled by scenario transitions. In the SADF MoC that is used in the thesis at hand, scenario transitions are modeled by probabilistic choices, i.e., as a discrete-time Markov chain. Besides the aforementioned, there exists another variant of SADF, namely Finite State Machine (FSM) SADF, that models choices by a finite state machine [5]. In FSM-SADF, however, zero production or consumption rates, like in CSDF, are not allowed, while Markov chain SADF does allow for zero production and consumption rates. In turn, Markov chain SADF does not support auto-concurrency as described in [19], which is possible in CSDF and FSM-SADF. However, as discussed in Section 2.1.2, this does not affect the modeling and analysis approaches introduced in the thesis at hand, as auto-concurrency is removed from final analysis models. Hence, the thesis at hand focuses on Markov chain SADF, which will be referred to as SADF in the following.

Let  $\Psi$  denote a finite set of scenarios. The set of all possible non-empty sequences of scenarios  $\psi \in \Psi$ , is denoted by  $\Psi^{+2.2}$ . A sequence of scenarios is indicated by  $\widetilde{\psi} \in \Psi^+$  and the length of a scenario sequence is denoted by  $|\widetilde{\psi}|$ . Furthermore, a sequence of n equal scenarios  $\psi \in \Psi$  is denoted by  $\psi^n$ .

**Definition 6 (SADF graph)** An SADF graph is defined as  $G = (V, E, p, c, D_0, d)$  with vertices  $V = V_k \cup V_d$ , edges  $E = E_d \cup E_c$ , with  $E_d : V \times V$  and  $E_c : V_d \times V_k$ , production rates  $p : E \to \mathbb{Z}_{0+}^n \cup \Psi^{+n}$ , consumption rates  $c : E \to \mathbb{Z}_{0+}^n$ , an initial token distribution  $D_0 = (D_{d_0}, D_{c_0})$ , with  $D_{d_0} : E_d \to \mathbb{Z}_{0+}$  and  $D_{c_0} : E_c \to \Psi^+$ , and a delay function  $d : V \to \mathbb{T}^n$ .

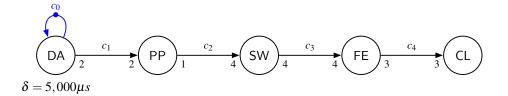

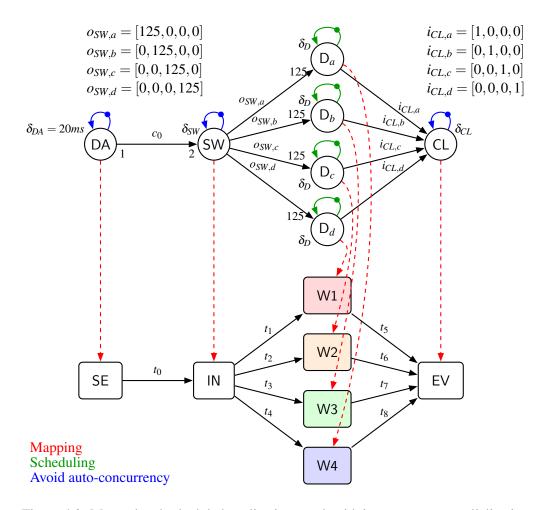

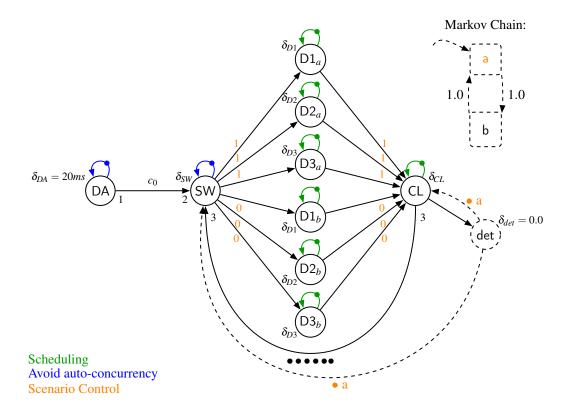

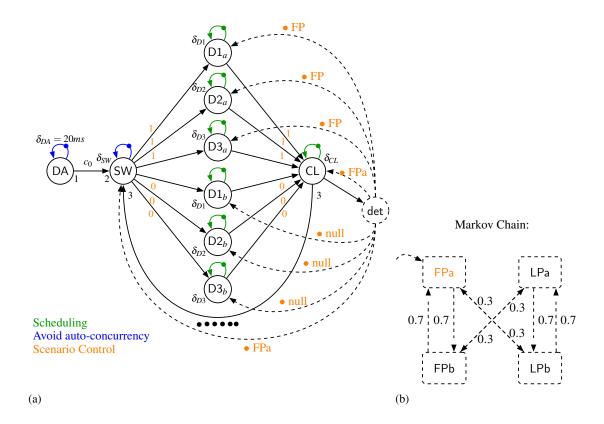

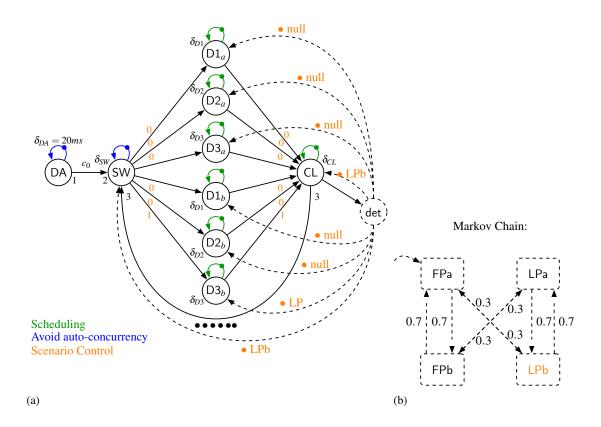

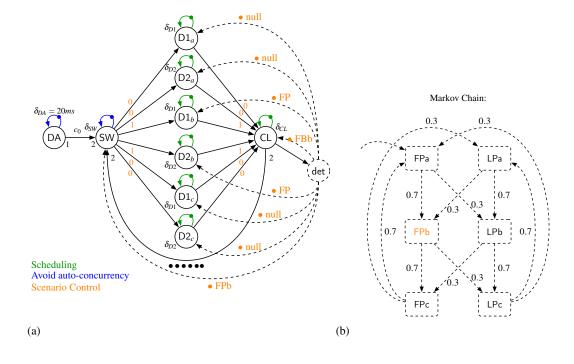

An example SADF graph is depicted in Figure 2.5. Similar to CSDF actor phases, SADF actors  $v \in V$  are associated with a set of *scenarios*  $\Psi_v$ . However, in SADF graphs, scenarios are not necessarily changing in a cyclic manner, but are rather controlled by special actors. To this end, two kinds of actors, i.e., *kernels*  $V_k$  and *detectors*  $V_d$ , build the set of actors  $V = V_k \cup V_d$ , with  $|V_k| \ge 1$ . Actors are depicted as vertices, with solid lines for kernels (A,B, and C in Figure 2.5(a)) and dashed lines for detectors (det in Figure 2.5(a)). According to the original definition in [19], an SADF graph can consist of multiple detectors. However, for the sake of brevity, the number of detectors in  $V_d$  is assumed to equal one in the thesis at hand, i.e.,  $|V_d| = 1$ . Furthermore, an actor  $v \in V$  can either be

<sup>2.2</sup>Here,  $\Psi^+$  denotes the Kleene plus operator  $^+$  on the set  $\Psi$ , representing the set of all possible sequences of elements from the set  $\Psi$ , which are non-empty.

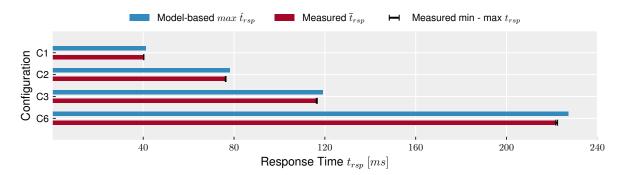

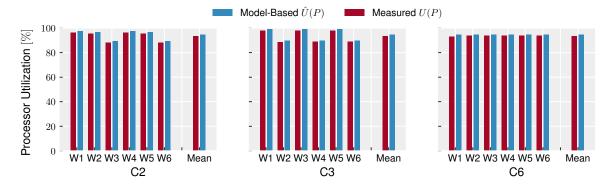

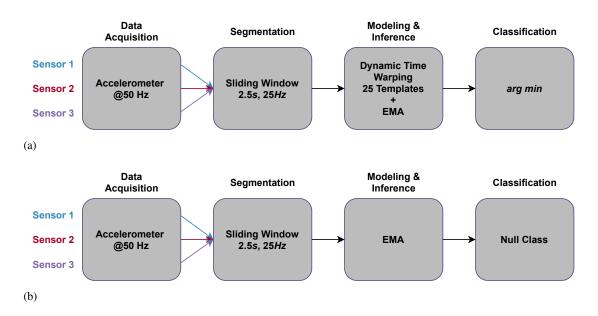

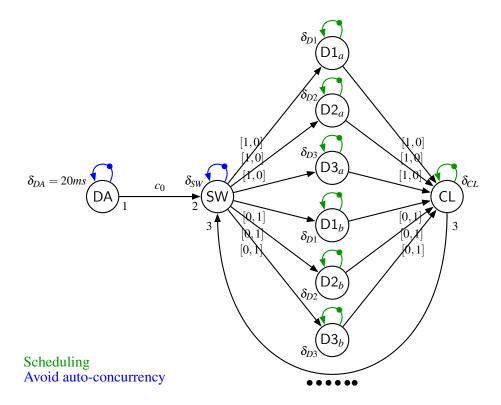

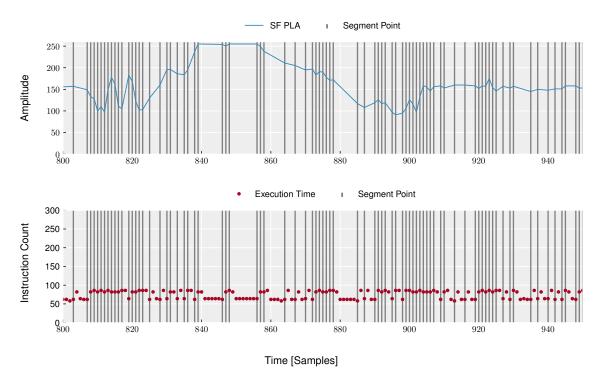

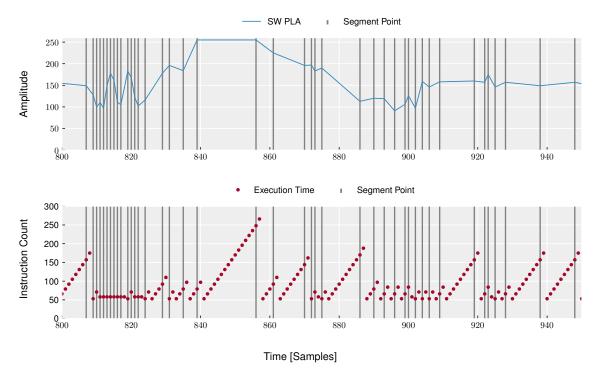

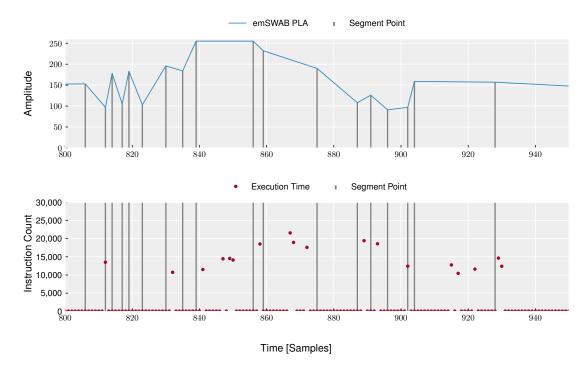

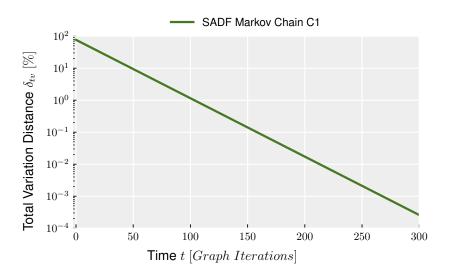

Figure 2.5: Example of a scenario-aware dataflow graph.