# Latch-based RISC-V core with popcount

# instruction for CNN acceleration

Master's thesis University of Turku Department of Computing Embedded electronics 2021 Ohto Myllynen

The originality of this thesis has been checked in accordance with the University of Turku quality assurance system using the Turnitin OriginalityCheck service.

#### UNIVERSITY OF TURKU Department of Computing

OHTO MYLLYNEN: Latch-based RISC-V core with popcount instruction for CNN acceleration

Master's thesis, 54 p., 15 app. p. Embedded electronics May 2021

Energy-efficiency is essential for vast majority of mobile and embedded battery-powered systems. Internet-of-Things paradigm combines requirements for high computational capabilities, extreme energy-efficiency and low-cost. Increasing manufacturing process variations pose formidable challenges for deep-submicron integrated circuit designs. The effects of variation are further exacerbated by lowered voltages in energy-efficient designs. Compared to traditional flip-flop-based design, latch-based design offers area, energy-efficiency and variation tolerance benefits at the cost of increased timing behavior complexity. A method for converting flip-flop-based processor core to latch-based core at register-transfer-level is presented in this work.

Convolutional neural networks have enabled image recognition in the field of computer vision at unprecedented accuracy. Performance and memory requirements of canonical convolutional neural networks have been out of reach for low-cost IoT devices. In collaboration with Tampere University, a custom popcount instruction was added to the cores for accelerating IoT optimized vehicle classification convolutional neural network.

This work compares simulation results from synthesized flip-flop-based and latch-based versions of a SCR1 RISC-V processor core and the effects of custom instruction for CNN acceleration. The latch core achieved roughly 50% smaller energy per operation than the flip-flop core and 2.1x speedup was observed in the execution of the CNN when using the custom instruction.

Keywords: RISC-V, Latch, Energy-efficient, IoT

# Contents

| 1 | Intr                              | introduction 1                |    |  |  |

|---|-----------------------------------|-------------------------------|----|--|--|

| 2 | RISC-V                            |                               |    |  |  |

|   | 2.1                               | Cores                         | 10 |  |  |

|   | 2.2                               | SCR1                          | 12 |  |  |

|   |                                   | 2.2.1 Memory                  | 13 |  |  |

|   |                                   | 2.2.2 Pipeline                | 14 |  |  |

|   |                                   | 2.2.3 Other optional features | 14 |  |  |

|   |                                   | 2.2.4 Configuration           | 15 |  |  |

|   |                                   | 2.2.5 Testbench               | 15 |  |  |

| 3 | CNI                               | ISA extension                 | 16 |  |  |

|   | 3.1                               | Toolchain extension           | 18 |  |  |

|   | 3.2                               | Hardware extension            | 20 |  |  |

| 4 | Latch sequencing 2                |                               |    |  |  |

|   | 4.1                               | Flip-flop                     | 24 |  |  |

|   | 4.2                               | Transparent latch             | 24 |  |  |

|   | 4.3                               | Timing behavior               | 25 |  |  |

|   | 4.4                               | Process variations            | 28 |  |  |

| 5 | Latches — replacing flip-flops 29 |                               |    |  |  |

|    | 5.1   | Methodology                       | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----|-------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 5.2   | Signal dependencies               | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|    | 5.3   | Transform                         | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|    | 5.4   | Latch synthesis                   | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6  | Resu  | ılts                              | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|    | 6.1   | CNN and popcount                  | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

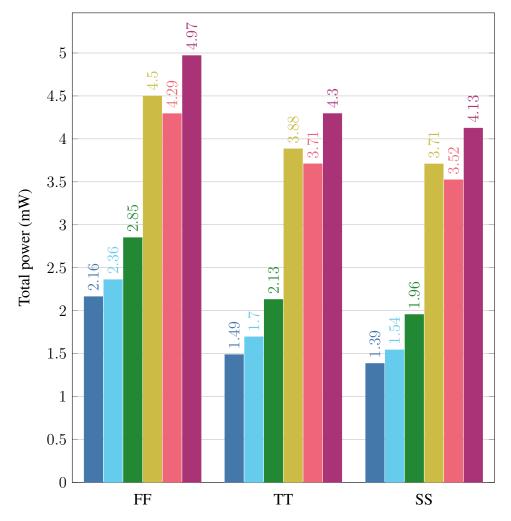

|    | 6.2   | Synthesis corners                 | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|    | 6.3   | Power and energy                  | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7  | Con   | clusions                          | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Re | feren | ces                               | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Ap | pend  | ices                              | m       33         m       33         nthesis       37         43       43         d popcount       45         is corners       45         is corners       45         ind energy       47         50       50         51       50         52       50         52       52         DL.g4 version 0.2.0 patch       A-1         spile script       B-1         straints       C-1         I fix script       D-1         e script       E-1         aints       F-1         x script       G-1 |

| A  | SysV  | VerilogHDL.g4 version 0.2.0 patch | A-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| B  | Flip  | -flop compile script              | B-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| С  | Flip  | -flop constraints                 | C-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| D  | Flip  | -flop hold fix script             | D-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| E  | Lato  | ch compile script                 | E-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| F  | Lato  | ch constraints                    | F-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| G  | Lato  | ch hold fix script                | G-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Н  | Lato  | ch reduce clock gate delay        | H-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## Chapter 1

### Introduction

Energy efficiency is vital for vast majority of battery powered systems. The higher the energy efficiency, the more computations a system can perform between recharges or battery swaps. In the field of mobile and embedded devices, long battery life is often as important or more important feature than computation speed. In addition to prolonging the operating time of such devices, increasing energy efficiency enables countless new applications. More and more complex functionality can be realized with less and less energy. Energy efficiency is one of the key enablers for the growing Internet-of-Things (IoT) market and the technologies of the future. Increasingly wireless, mobile and interconnected systems require massive amounts of data to be processed in real-time, while being operational for extended periods of time without a constant power supply. Advances in neural networks have made many data analysis tasks like image recognition possible with much higher speed and accuracy than ever before. However, in many cases the memory and computation requirements cannot be met by current low-cost IoT devices. To truly reap the benefits of neural networks and to bring them to IoT realm, efficient hardware and optimized algorithms are both required. The amount of transistors in integrated circuits has been growing exponentially in the past decades causing power density and power consumption to increase towards practical limits. Heat dissipation has become a major issue for data centers and high performance computing in general. Offloading some of

#### CHAPTER 1. INTRODUCTION

the computation to the network edges for improved latencies and reduced costs calls for highly energy-efficient hardware. Besides, the available energy to harness is finite. As Jan Rabaey illustrates with his playful extrapolation in [1], the entire energy of the Milky Way galaxy would be spent in just 180 years, if computational requirements are assumed to double every year. This work explores potential benefits of latch-based design in terms of energy-effiency and variation tolerance. Additionally, acceleration of an IoT optimized Convolutional Neural Network (CNN) by adding custom popcount instruction to the core was simulated and confirmed.

Most modern digital devices are built with Complementary Metal-Oxide Semiconductor (CMOS) logic. For digital CMOS circuits energy can be estimated with equation 1.1 [1]<sup>1</sup>. The dynamic energy dissipation is dependent only on the total capacitance Cand voltage V. Leakage energy is defined by the voltage V and leakage current  $I_{leak}$  over operation time t. It is important to notice that energy is not dependent on operating frequency. Leakage current of a gate can be estimated with equation 1.2 [1], where kT/q is thermal voltage and equals roughly 25mV at room temperature [1]. W is the width of the gate and  $V_{th}$  is the threshold voltage.  $I_0$ ,  $W_0$  S, and  $\lambda_d$  are technology specific constants corresponding to minimum current, minimum gate width, sub-threshold swing and Drain Induced Barrier Lowering (DIBL) factor.

Leakage currents of the gates are strongly dependent on drain-source voltage  $V_{DS}$  and threshold voltage  $V_{TH}$ . While lowering the operating voltage impacts mostly energy dissipation at first, it also pushes the threshold voltages down. At a certain point leakage energy starts to dominate when the transistor's ability to turn off diminishes. Additionally, as the voltage lowers propagation delay of the signals starts to increase until the circuit fails. Thus lowering the voltage limits the maximum operating speed of the device as well.

<sup>&</sup>lt;sup>1</sup>Equation 1.1 can be obtained by combining several equations from [1]

$$E_{dyn} + E_{leak} = CV^2 + \frac{VI_{leak}}{t}$$

(1.1)

$$I_{leak} = I_0 \frac{W}{W_0} 10^{\frac{-V_{TH} + \lambda_d V_{DS}}{S}}$$

for  $V > \frac{3kT}{q}$  (1.2)

The capacitance C in equation 1.1 correlates to the amount of transistors switching at a given time. It is also dependent on the CMOS technology and implemented architecture. The capacitance component of energy dissipation can therefore be reduced by migrating to a newer CMOS technology process or by architectural optimizations.

The switching rate of transistors per clock cycle is often estimated by activity factor  $\alpha$ , a percentage of transistors in the device. For processors,  $\alpha$  varies depending on the executed operations and the architectural design of the system. While software optimizations can reduce  $\alpha$  in many cases, ultimately they are bound by the hardware capabilities. Software optimizations relying on nonstandard hardware functionality can further improve the performance at the cost of software portability. Implementing hardware specific optimizations might also require significant efforts on the software side, depending on the software stack. Architectural hardware optimizations are more generic and reliable, since they potentially require little to no additional effort from the software developers. Improving the energy efficiency and speed of most commonly executed instructions and the execution pipeline in general benefits all of the use cases. At some point the benefits gained start to diminish and optimizing the common case is no longer feasible. Another path to improvements, albeit usually more application specific, is adding new instructions. For example, a new instruction can be added to the Central Processing Unit (CPU) for a common instruction pattern. Instead of executing multiple instructions to achieve certain behavior, the task can now be done entirely in hardware by a single instruction. In order to utilize the new instruction, support for its encoding must be added to the toolchain and the software has to be recompiled, possibly after some modifications. For most real world instruction sets modifications are either difficult and prohibitively costly or prohibited all together. Fortunately, free and open RISC-V Instruction Set Architecture (ISA) standard is designed to support instruction set extensions, providing the means to implement custom instructions.

Previously shrinking process nodes have offered gains in performance, energy savings and area reduction for relatively low effort compared to architectural optimization. However, as the feature sizes have started to approach the thickness of just a few atoms, the effects of variation in manufacturing process have magnified. Migrating to new deepsubmicron CMOS nodes has become increasingly difficult and costly due to reduced yields, caused by increased process variation, among other challenges. High local variability adds an element of uncertainty to the timing of the chips, causing higher rates of failure. As a consequence, alternative ways to increase energy-efficiency are becoming more attractive.

The theoretical minimum energy required for a signal to be distinguishable from noise is defined by *Shannon-von Neuman-Landauer limit* to be  $0.29 * 10^{-20}J$  at room temperature [1]. Reaching this limit in practice is not very likely, but it sets the ultimate goal for improvements. Modern devices operate few magnitudes above this limit, based on simulation results from [2]. In practice some voltage margin is added to ensure the functionality of the fabricated devices. In order to confirm that as many of the manufactured devices as possible are functional despite variations in the manufacturing process, the operation of the device is tested on different manufacturing process corners. The process corners represent global inter-die variations affecting the whole chip. Before manufacturing the corners are simulated and the design is tuned to tolerate the variations, often translating to adding margin to the typical case. Common corner choices for testing CMOS process transistor variation are SS (Slow-Slow), TT (Typical-Typical) and FF (Fast-Fast), though other combinations are also possible. The letters signify carrier mobility for NMOS and PMOS transistors respectively. In addition to global variations between chips, local intradie variations are present within each chip. While some local variation sources are deterministic, random local variations are also present. Statistical timing models are needed to predict the effects of random local variations more accurately.

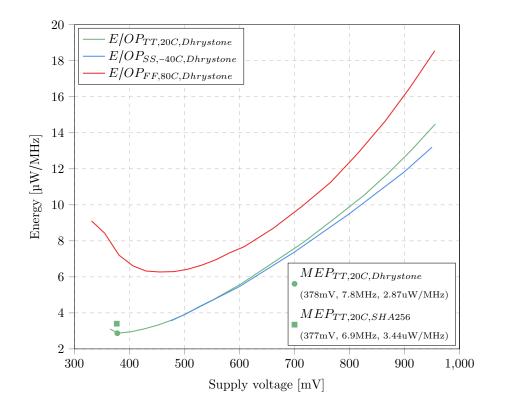

Energy per Operation (EOP) is a commonly used metric to measure processor efficiency. Because reducing the voltage reduces not only the required energy, but it also reduces the maximum operating speed due to increased delays, reducing EOP is a balancing act between energy and performance. There exists a point for optimal EOP also known as Minimum Energy Point (MEP). Hiienkari *et al.* have reached the EOP of 2.87 pJ/cycle with ARM Cortex-M3 CPU by using state-of-the-art energy saving techniques to drastically cut down voltage margins [3]. Figure 1.1 shows EOP measurements from the core manufactured at different process corners over operating voltage range. As shown in figure 1.1 when the operating voltage is reduced the EOP improves at first, but when the voltage is reduced further EOP starts to increase at a certain point. MEP is located at the lowest point of the curve. The core was measured over different process corners and the effects of process variations are evident. In the FF process corner the energy is much higher than in the TT or SS corners.

On the downside as the voltage decreases the the effects of process variation are magnified. Majority of CMOS designs use flip-flop cells for sequencing, due to their relatively simple and well understood timing behavior. As an alternative to flip-flops the sequencing can also be realized with latch cells at the cost of increased timing behavior complexity. While latches and flip-flops are on equal footing in terms of performance under traditional timing models, latches are able to give better yields under statistical timing models. Statistical timing models are used to predict the circuit timing more accurately when process variations become significant. Hurst *et. al* have shown in [4] that transparent latches can reduce the rate of failures by four times compared to flip-flops. Latches are able to meet more timing corners, because in latch-based sequencing the signal propagation window is much wider than in flip-flop-based sequencing. Additional benefit of latch-based designs is that latches are less complex devices than flip-flops and thus they can be constructed

Figure 1.1: ARM Cortex-M3 EOP[3] © 2020 IEEE

with fewer transistors, resulting in area and energy savings.

Focus of this master's thesis is in latch-based energy-efficient design, but other complementing low-power techniques could be added on top of this approach to further increase the energy efficiency of the design. An overview of RISC-V and rationale for choosing an open-source RISC-V core as a starting point for latch-based core is given in chapter 2. Chapter 3 introduces the custom popcount instruction used to accelerate convolutional neural networks. The characteristics of latches and flip-flops from sequencing perspective are detailed in chapter 4. Chapter 5 explores a methodology for latch-based sequencing, conversion of flip-flop-based designs to latch-based designs and related challenges. Simulation results are shown and examined in chapter 6. Finally, the conclusions are presented in chapter 7.

## Chapter 2

# **RISC-V**

RISC-V is fifth generation of an open Instruction Set Architecture (ISA) standard developed originally at UC Berkeley for academic use. While RISC-V began as an academic endeavor to provide a realistic ISA for research and classroom use, it has gained a lot of traction especially in IoT and low power applications. RISC-V ISA is designed with flexibility and extensibility in mind, making it an excellent candidate for creating cores optimized for specific use cases. As a new ISA RISC-V has had the opportunity incorporate the knowledge gained from older ISA specifications and decades of field testing. The base instruction set has been carefully designed to contain only the most universal instructions. Application domain specific instructions can be added in a modular fashion on top of the base instruction set depending on the implementation requirements. This enables software compatibility across different implementations, given that the available software stack is able to emulate optional instructions when they are not supported by the implementation. RISC-V ISA standard is maintained by the RISC-V foundation, which accepts companies as well as individuals as members. The RISC-V specification is freely available for anyone to download and implement without any costs. The specification version used as reference in this work is The RISC-V Instruction Set Manual Volume 1: Unprivileged ISA [5].

Currently, most widely-adopted ISAs are proprietary. To create an implementation

for proprietary ISA lengthy negotiations and expensive licenses are required. Custom implementation of proprietary ISAs has therefore been possible only for a few companies. Most companies have had to settle with integrating premade designs and components to their products. The free and open licensing model of RISC-V permits anyone to create their own RISC-V compatible processor implementations, while allowing proprietary implementations as well. In the light of expensive licensing and possible royalty costs associated with proprietary ISAs the RISC-V is very tempting from a financial point of view.

An ISA is an abstract interface between hardware and lowest level of software. It contains all the details needed to create machine language programs that can be run on the hardware. For a program to be executable in certain hardware it must be written in or translated to a format defined by the ISA. Usually ISA is accompanied with a compiler toolchain capable of transforming high level code, such as C, to a format specified by the ISA. The RISC-V ISA specification avoids implementation style or technology specific details for increased flexibility. RISC-V implementations can range from single core processor to multi-core System-on-a-Chip (SoC) and server clusters with thousands of cores. In [6] Asanović and Patterson, both very closely involved in the creation of RISC-V, argue that ISA, one of the most important interfaces, should not be proprietary. They envision that having a widely used open ISA could lead to increased innovation, shorter time to market, lower costs, fewer bugs and transparency. Ambitiously, the authors set the goal of RISC-V to eventually become the standard ISA for all computing devices.

RISC stands for Reduced Instruction Set Computer as opposed to Complex Instruction Set Computer (CISC). RISC architecture is based on the idea of defining a small, yet comprehensive, set of simple instructions and executing them really fast. CISC architecture on the other hand defines a large set of instructions including complex instructions that can take longer to execute. While CISC implementations have dominated in the high performance domain and RISC implementations have prevailed in the embedded and mobile domain, there is no fundamental reason why RISC architecture could not be used for high performance applications or CISC architecture for energy-efficient designs. In [7] Blem *et. al* compared effects of ISA on performance and energy-efficiency for ARM (RISC) and x86 (CISC) implementations. They found that modern microarchitecture techniques and compiler optimizations help to mitigate CISC implementation overheads. For example, complex instructions are split to RISC-like micro-ops and compilers tend to favor RISC-like instructions over the complex ones. They concluded that the differences between ARM and x86 implementations are largely dependent on the design point and not so much on the ISA. But they also note that for simple very low performance processors CISC ISA such as x86 or even ARM's full RISC ISA would be too complex and add unnecessary overhead.

The IoT domain covers a wide range of applications requiring high energy effiency and low cost. Typically IoT end-nodes stay in sleep mode most of the time to save energy and wake up to quickly execute pending tasks, triggered by external events, before going back to sleep. The computational requirements can range from reading and storing a sensor value to complex signal processing. To cover the wide range of use cases different kinds of programmable cores are needed for various desing constraint combinations. The shared or partially shared RISC-V ISA between various cores brings benefits in terms of bus interconnect, interface and software compatibility.[8]

The RISC-V specification defines four related base integer ISAs and optional extensions. Base ISA is mandatory and can be either RV32I, RV32E, RV64I or RV128I. The base ISA defines the width of integer registers, the number of registers and size of the address space. RV128I is less polished and the primary base ISA variants are RV32I and RV64I for 32-bit and 64-bit architectures respectively. The RV32E base ISA is a variant of RV32I with only 16 registers for small implementations. RV32I and RV64I base ISAs have 32 registers. The base ISAs are considered independent variants to allow better optimization, therefore they might have slight differences in encoding and behavior of the extensions. The memory consistency model of the RISC-V ISA is quite flexible and defaults to RISC-V Weak Memory Ordering (RVWMO), which is the weakest allowed memory model. Under RVWMO memory instructions executed within a hardware thread (hart) appear in order from the perspective of other memory instructions executed in the same hart, but may appear in different order from the perspective of other harts' memory instructions. Further constraints can be added for stricter memory model as needed.

Because the RISC-V specification is still under development a part of the specified extensions might undergo some changes. Commonly used extensions M, A, F, D, Q, C, Zicsr and Zifencei are quite stable and only minor changes, if any, are expected on their specification. M extensions adds multiplication and division instructions for integers. Extension A adds atomic operations for inter-processor synchronization. F, D and Q extensions respectively add single-, double- and quad-precision floating point instructions for reduced instruction memory footprint. Zicsr adds CSR access instructions. Zifencei adds instruction to synchronize writes and fetches to instruction memory. Additionally G shorthand is used to denote IMADZifencei extension combination and floating point extension implicitly include the Zicsr extension.

#### 2.1 Cores

Since RISC-V ISA only defines the interface between software and hardware, but not the actual hardware, how a RISC-V compliant processor core is realized is up to the designer. Digital hardware is described in Register-Transfer level (RTL) with a Hardware Description Language (HDL). RTL code describes the signals, registers and behavior of logic in the circuit at high abstraction level. The circuit behavior is first tested and verified in RTL simulations. Considerable RTL verification effort is required to ensure that the features of the manufactured devices will behave as expected. Correctly functioning RTL description

is the starting point for creating the actual circuit. Since RISC-V ISA itself is not encumbered by restrictions that come with proprietary ISAs, the RTL can be shared much like open source software. By itself the RTL code can be used for Field-Programmable Gate Array (FPGA) implementations, but it is not enough to produce an Application-Specific Integrated Circuit (ASIC), since it does contain any information about the physical implementation.

Numerous proprietary and open source RISC-V implementations are readily available. While some of the available cores utilize latches to some extent, it seems that currently there are no fully latch-based cores available. Therefore to reduce the scope of this work a small, energy-efficient and mature flip-flop-based RISC-V core was chosen as a starting point to be transformed to a latch-based implementation. Naturally, only open source RISC-V cores were considered for this work. Due to the nature of open source the quality of the implementations can range from hobby projects to academic research work and production ready cores equivalent to proprietary solutions on the market. 20 RISC-V cores were compared, in order to find a good candidate to modify. A comparison of the cores can be seen in table 2.1. The RISC-V Foundation provides a compliance test suite to ensure compatibility of the implementation with the RISC-V specification. Cores that were not compliant and the cores for which the compliance was unclear (N/A) as well as cores with too restrictive licensing were deemed unsuitable. Cores built with 64-bit base ISA, like Ariane and BOOM, are targeting towards higher performance and even running multi-user operating systems like Linux. As a consequence they are also considerably more complex. To limit the development effort and since 32-bit ISA is enough for most embedded applications Ariane and BOOM were left out. Support for latch-based digital logic varies among HDLs. Since implicit latches as a result of incomplete conditional expressions are a common source of bugs in RTL code, many HDLs and Electronic Design Automation (EDA) tools have better support for avoiding latches than actually using them. While creating latches is certainly possible in most HDLs, in general the support for latch-based sequencing is quite limited. SystemVerilog was chosen as the target language since it has at least some support for explicitly modeling latched logic and the language itself is quite well supported by EDA tools. After this consideration cores that were not written in SystemVerilog were discarded.

Out of the 20 RISC-V implementations two of them fit the criteria the best: SCR1 and Zero-riscy. Both cores are well tested, very small low power cores written in SystemVerilog. SCR1, maintained by Syntacore, a semiconductor IP company specializing on RISC-V ISA, is mature and highly configurable core. SCR1 repository includes a good quality development environment with easy-to-extend testbench. Zero-riscy<sup>1</sup> was created as a part of Paraller Ultra Low Power (PULP) platform, a joint project between Integrated Systems Laboratory, ETH Zurich and Energy Efficient Embedded Systems group of University of Bologna. Unlike SCR1 Zero-riscy does not come with directly a coupled development environment. Instead it is intended to be used with PULPino single core microcontroller system. Like SCR1 the development environment for Zero-riscy is mature and comes with a testsuite. Development environments of both of the cores have support for FPGA targets as well. Ultimately the choice came down to personal preference. Both cores are well suited for small scale experimentation. SCR1 was chosen as the target core for latch transformation, because it's slightly more configurable and the development environment seemed more straightforward.

### 2.2 SCR1

SCR1 is well documented: the external architecture specification, user manual, and FPGA specific Software Development Kit (SDK) instructions are included in the core repository [9] and in related SDK repository [10]. The core can be configured with either RV32I or RV32E base ISA and optionally with C extension for compressed 16-bit instructions

<sup>&</sup>lt;sup>1</sup>Zero-riscy has been renamed to Ibex and contributed to lowRISC non-profit since this evaluation

| Core             | License             | ISA         | HDL                    | Compliance | Notes                     |

|------------------|---------------------|-------------|------------------------|------------|---------------------------|

| Ariane           | Solderpad Hardwar   | e RV64IMAC  | SystemVerilog          | Yes        | PULP platform             |

|                  | License v. 0.51     |             |                        |            |                           |

| BOOM             | BSD                 | RV64GC      | Scala (Chisel)         | Yes        | Out-of-order              |

| Hummingbird E200 | Apache 2.0          | RV32IMAC    | Verilog                | Yes        | Targeted for Chinese      |

| Minerva          | BSD/LambdaConcept   | RV32I       | Python                 | No         | Uses nMigen toolbox       |

| MR1              | Unlicense           | RV32I       | SpinalHDL              | Yes        | Hobby project             |

| ORCA             | Vectorblox Orca     | RV32IM      | VHDL                   | N/A        | -                         |

| OPenV/mriscv     | MIT                 | RV32I       | Verilog                | No         | -                         |

| PicoRV32         | ISC                 | RV32IEMC    | Verilog                | Yes        | -                         |

| ReonV            | GPL v3.0            | RV32I       | VHDL                   | N/A        | RISC-V port of Leon3 core |

|                  |                     |             |                        |            | (from GRLIB IP library)   |

| Reve-R           | Apache 2.0/BSD      | RV32IMAC    | CDL                    | No         | -                         |

| Roa Logic RV12   | Non-commercial      | RV32 64I    | SystemVerilog          | Yes        | -                         |

| Rocket           | BSD                 | RV32 64G    | Scala (Chisel)         | Yes        | Rocket chip generator     |

| Riscy Processors | MIT                 | RV64IMAFD   | Bluespec SystemVerilog | Yes        | -                         |

| RI5CY            | Solderpad Hardwar   | e RV32IMFC  | SystemVerilog          | Yes        | PULP platform             |

|                  | License v. 0.51     |             |                        |            |                           |

| SCR1             | Syntacore/Solderpad | RV32IEMC    | SystemVerilog          | Yes        | -                         |

|                  | Hardware License    |             |                        |            |                           |

|                  | 0.51                |             |                        |            |                           |

| SERV             | ISC                 | RV32I       | Verilog                | Yes        | Bit-serial core           |

| Shakti           | BSD, 3-clause       | RV32 64IMAC | Bluespec SystemVerilog | Yes        | Core family               |

| SweRV EH1        | Apache 2.0          | RV32IMC     | SystemVerilog          | N/A        | -                         |

| VexRiscv         | MIT                 | RV32IMC     | SpinalHDL              | Yes        | -                         |

| Zero-riscy       | Solderpad Hardwar   | e RV32IMCE  | SystemVerilog          | Yes        | PULP platform             |

|                  | License v. 0.51     |             |                        |            |                           |

Table 2.1: RISC-V core (platform) comparison, collected in Spring of 2019

and M extension for integer multiplication and division instructions. SCR1 implements only machine mode privilege level for running trusted code. The core is quite small and according to documentation synthesizes to only around 11-33 kGates depending on the configuration.

#### **2.2.1** Memory

SCR1 implements harvard architecture i.e. the instruction and data memories have dedicated memories and access buses, but the core also has up to 64 kBytes of low latency dual-port Tightly Coupled Memory (TCM), which is shared by instructions and data. TCM is designed for storing commonly used instructions and data for increased throughput. Memory access interfaces can be configured either as Advanced eXtensible Interface 4 (AXI4) or AMBA High-performance Bus-lite (AHB-lite). The memory is byte addressed and little endian. Instruction and data memories both have 32-bit continuous address space. SCR1 uses strong memory access model, guaranteeing one-to-one match of the sequence and number of memory accesses performed with the executed instructions. The memory is only accessible by load and store instructions.

#### 2.2.2 Pipeline

SCR1 implements in-order 2-4 stage pipeline depending on the configuration. The pipeline is divided to following phases: request to instruction memory, instruction fetch, instruction decode, execution, and commit point. The execution consists of operand fetch, arithmetical and logical operations, load and store operations, and instruction flow control. In 2-stage pipeline configuration the first stage contains request to instruction memory, instruction fetch and instruction decode phases and the second stage contains execution phase and commit point. For 3- and 4-stage configuration a queue can be added before instruction decoding or execution phase or before both phases. Since operand fetch and commit point are always in the same stage SCR1 pipeline has no data hazards. Structural hazards are resolved by stalling execution until the occupied resource becomes available and control hazards are dealt with by simply flushing and restarting the pipeline.

#### 2.2.3 Other optional features

Optionally the core also supports low latency Integrated Programmable Interrupt Controller (IPIC) with up to 32 interrupt signals, vectored interrupts, global clock gating and single cycle integer multiplier. In addition the core comes with optional debugging subsystem with Joint Test Action Group (JTAG) interface.

#### 2.2.4 Configuration

To reduce development efforts the core was configured for RV32IC target with 2-stage pipeline and without any optional blocks. AHB-lite was used for the development and testing, since it's less complex and more energy-efficient than AXI4 [11]. Though, the core top level environment, including the memories and memory bus interface, was not included in the synthesis and only simulated as a part of the testbench in netlist simulations.

#### 2.2.5 Testbench

The testbench of the core has ready made targets for multiple simulators and it integrates with RISC-V compliance tests. After setting up the environment, RISC-V compliance tests and benchmarks were run with Verilator and VCS simulators in order to confirm the correct functionality. Additionally after initial RTL simulation tests DE10-lite FPGA and DE10-lite SDK provied by Syntacore was used to verify core functionality. Since FPGAs in general are not feasible for latch-based designs, no further FPGA experimentation was done beyond verifying that the original RTL is indeed functional. The testbench was augmented with SHA-256 test in addition to the included Dhrystone 2.1 and Coremark benchmark in order to increase the variety of simulated activity. Based on previous experience looping SHA-256 test tends to generate slightly more computationally intensive activity than Dhrystone 2.1. or Coremark. The SHA-256 test is lightly modified version of an implementation by Brad Conte [12] and it runs 1000 rounds of SHA-256 starting from a known plaintext and compares the result to an expected value. In order to avoid timing errors while running the testbench with synthesized design, I/O delays at the boundary have to be compatible with the timing of the synthesized design. Therefore a wrapper module adding delay to the I/O signals was added around the core instantiation in order to simulate I/O delays more realistically.

## Chapter 3

# **CNN ISA extension**

A Convolutional Neural Network (CNN) is a type of artificial neural network that is most commonly utilized for image recognition tasks. Generally CNNs consist of alternating convolutional and pooling layers followed by fully connected layers. Convolutional layers are used to detect features from the image, the pooling layers are used to reduce the dimension of the data and finally the classification is done by fully connected layers. The final layer outputs a value for each type of class the network can detect. The values can be negative or positive and the higher the value the higher confidence the classification has. The class with highest value is the classification the network sees as most likely, but it is also possible that scores are quite close to each other, if the CNN cannot classify the image with high confidence or very low if the image does not fit in any of learned the categories.

Each convolutional layer has at least three dimensions: width, height and depth, where the depth corresponds to the amount of filters in the layer. Filters correspond to the features the layer is attempting to detect. Each filter has associated weights learned during the training of the network. For example, a layer with a depth of three could be used for detecting a feature from each of the color components RGB in an image, but in practice the layers are usually deeper. Each filter is slid over the inputs of the previous layer along width and height dimensions. At each step all of the filter weights are applied to the region producing a single output value. The weights are multiplied with the related inputs in the current region and added together. Typically the output value is passed to the next layer through an activation function, for example max(0, x). If the input pixels of an image are flattened to one dimensional vector the application of weights can be seen as a dot product. In the fully connected layers all of the inputs are connected to each of the outputs, hence the name.

For example, applying three 3x3 filters to equal size input, depending on the implementation, could require nine multiplications, eight additions and a division for each filter and additional three multiplications and two additions for the dot product, if the output is 1x1x1. Additionally 27 weights have to be stored for the filters. It is easy to see that even for relatively small images the computation complexity and memory requirements increase quickly with image size and filter count, given that CNNs used for real life applications contain many filters and multiple fully connected layers.

Advances in CNNs have enabled image recognition at unprecedented accuracy and opened up many new possibilities in the field of computer vision. But the memory and computation requirements have been out of scope for many IoT applications. Payvar *et al.* have developed an IoT suitable CNN for vehicle image recognition. In [13] they used a method of efficiently packing the weights of CNN with minimal loss of accuracy and a method for accelerating CNN operations. In their work they use a binarization method to condense 32-bit floating point weights of the CNN to just 1-bit and pack the weights to 32-bit vectors, saving around 95% in the data memory size, while losing under 5% in accuracy. Additionally they used a popcount instruction in place of multiplication for both convolutional and fully-connected layers to speed up the computation. The popcount calculates hamming weight or the number of the amount of bits with value "1" in a register. The use of popcount instead of multiplication saves energy and potentially chip area, if hardware multiplier is not needed for the use case. Current hardware support for popcount is mostly targeted towards Graphics Processing Units (GPUs), which rules out

```

unsigned int popcount_emulated(unsigned int x) {

1

x = x - ((x >> 1) \& 0x5555555);

// 0x55 is 01010101

2

x = ((x >> 2) & 0x33333333) + (x & 0x33333333); // 0x33 is 00110011

3

x = (x + (x >> 4)) \& OxOFOFOF;

// 0x0F is 00001111

4

x = (x + (x >> 16));

return (x + (x >> 8)) & 0x000003F;

// 0x3F is 00111111

6

}

7

```

#### Listing 1: Software emulation of popcount instruction

IoT applications. Despite the lacking hardware support the authors were able to test their algorithm with software emulated popcount, shown in listing 1, and with RISC-V ISA simulator. In simulation they tested for 55% improvement in execution with hardware popcount instruction compared to emulated popcount. In collaboration with Tampere University, the popcount instruction is implemented in this work to measure the speedup with synthesized RISC-V core.

The emulated popcount algorithm in listing 1 counts the number of "1" bits in 32-bit register with divide and conquer approach. Bit masks are used to filter out unwanted bits. On the first row the register is divided to two bit long bins, each bin containing the amount of bits in in the original register value at each bin location. On the second row the two bit bins are shifted on top of each other and added together producing 4-bit bins. Note that maximum value in each 4-bit bin is only 3-bits wide. The process of shifting and adding the bins is repeated until the values contained in the bins have been added to the beginning of the register. Each time the bin size is increased by a power of two, while the length of the maximum value increases by one bit. Finally, the maximum count of "1" bits is contained in first six bits of the register since  $32_{10}$  equals to  $100000_2$ .

#### 3.1 Toolchain extension

Before hardware implementation of the popcount instruction, the RISC-V GNU toolchain was modified to allow software development with the new instruction. Popcount was

```

unsigned int popcount(unsigned int value) {

1

unsigned int result;

2

asm volatile

3

4

(

"pcnt %[z], %[x], %[y]\n\t"

: [z] "=r" (result)

6

: [x] "r" (value), [y] "r" (value)

7

);

8

return result;

9

10

}

```

Listing 2: Using popcount assembly in a C program

added to binutils and to the RISC-V ISA simulator, Spike. This allows the use of popcount instruction via assembly and simulation of programs utilizing popcount without actual hardware. While adding new instructions to the assembler is somewhat trivial, adding custom instruction support for the compiler is more involved and out of scope for this work. The popcount hardware instruction was added to the CNN C-code as embedded assembly.

A version of the CNN code from [13] was kindly shared by the authors. The received code was slightly modified to include all the CNN weights and the test image inside a single binary instead of separate files. Having a single test binary is preferable from the HDL testbench perspective, since it is more convenient to directly load it to the memory. Additionally, to compare the speed up gained with hardware popcount, two versions of the CNN were compiled. First version was compiled with the software emulated popcount show in listing 1 and the second version was compiled with hardware popcount instruction shown in listing 2. Both versions were first tested with Spike and the CNN with emulated popcount was also tested in SCR1 RTL simulation, before implementing the ISA extension.

Popcount instruction is planned as part of official RISC-V bit manipulation extension (B) standard, but at the time of writing the standard has not yet solidified. To align with current draft version of the bit manipulation extension *pcnt* mnemonic was chosen for

this popcount instruction implementation. The RISC-V ISA specification guarantees that certain instruction encodings will be left unused. These unused encodings are specifically meant for implementation of custom instructions in order to avoid conflict with possible future standard extensions. Custom-0 encoding space was chosen as recommended by the RISC-V instruction set manual for 32-bit implementations. For custom-0 encoding space, the first seven bits of the RISC-V instruction are set to  $0001011_2$ . Since popcount requires only source and destination register, bits 19-15 and bits 11-7 of the instruction respectively, the other fields were fixed to zero.

### 3.2 Hardware extension

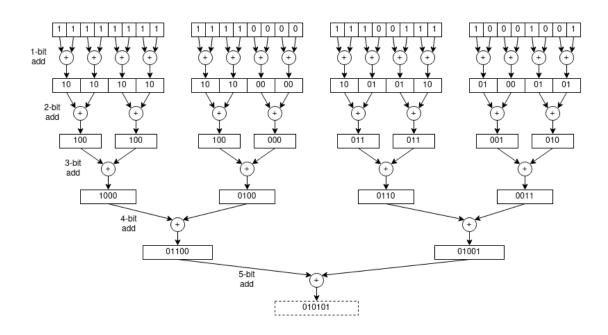

After selecting the instruction encoding format the RTL code of the SCR1 core was modified to support the new instruction. Instruction decoding unit was modified to accommodate for the new popcount instruction and a single cycle implementation of the popcount was added in to the Arithmetic-Logic Unit (ALU). The ALU muxes the correct operation to output depending on the instruction. The adder structure is similar to the parallel incrementer evaluated in [14]. The implementation sums the bits of the register in parallel as shown in figure 3.1. In first layer pairs of one bit values are added in parallel to form two bit values, in the second layer two bit pairs are added to form three bit values and so forth. Because the maximum value for popcount on 32-bit register is 32 (100000<sub>2</sub>), only 6-bits are required to represent the final result. The final register shown in the figure is not actually required since the value can be directly assigned to 32-bit output of the ALU. The verilog code to generate this structure is shown in listing 3. Since the hardware implementation was not on critical timing path no further optimization was done.

Figure 3.1: Parallel popcount example

```

genvar i;

1

2

generate

for (i = 0; i <= 30; i = i + 2) begin : gen_pcnt_L0

3

assign pcnt_L0[i+1:i] = ialu_op1[i+1] + ialu_op1[i];

4

end

5

for (i = 0; i <= 28; i = i + 4) begin : gen_pcnt_L1</pre>

6

assign pcnt_L1[i+3:i] = pcnt_L0[i+3:i+2] + pcnt_L0[i+1:i];

7

end

8

for (i = 0; i <= 24; i = i + 8) begin : gen_pcnt_L2</pre>

9

assign pcnt_L2[i+7:i] = pcnt_L1[i+7:i+4] + pcnt_L1[i+3:i];

10

end

11

for (i = 0; i <= 16; i = i + 16) begin : gen_pcnt_L3</pre>

12

assign pcnt_L3[i+15:i] = pcnt_L2[i+15:i+8] + pcnt_L2[i+7:i];

13

14

end

endgenerate

15

16

always_comb begin

17

pcnt_res = '0;

18

if (ialu cmd == SCR1 IALU CMD PCNT) begin

19

pcnt_res = pcnt_L3[31:16] + pcnt_L3[15:0];

20

end

21

22

end

```

### Chapter 4

# Latch sequencing

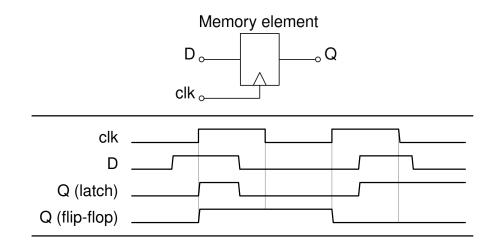

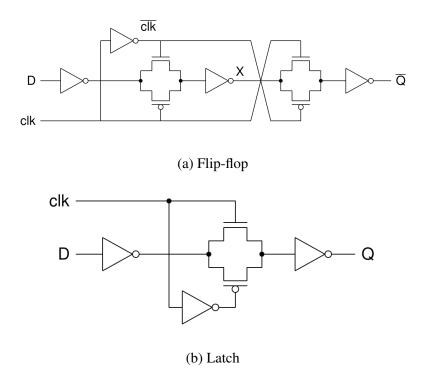

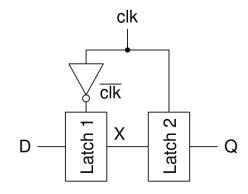

Memory elements are fundamental for the operation of all sequential digital circuits. In addition to storing information from previous states they are used to synchronize various signals traveling through combinational logic stages. Signals traveling through long and complex combinational paths take longer to arrive at an endpoint than signals traveling through short and simple combinational paths. Memory elements are needed to slow down the faster signals in order to synchronize all inputs for the next state to a stable value. If the outputs of previous computation stage were not stable when the computation of next state begins we are bound to get invalid results. From this perspective the main purpose of memory elements is to separate previous state of the computation from the next. While there are many different memory elements most CMOS systems use only edgetriggered flip-flops, transparent latches and pulsed latches [15]. This chapter focuses on edge-triggered flip-flops and transparent latches. Behavioral differences between latches and flip-flops can be seen in figure 4.1. Figure 4.2 shows traditional flip-flop and latch implementations from [15]. Note that output signal of the flip-flop design is inverted. For the latch circuit in figure 4.2 (b) the inverter between clock signal and PMOS, can be moved between clock signal and NMOS to produce a latch operating in opposite phase.

Figure 4.1: Transparent latch and positive edge triggered flip-flop timing behavior

Figure 4.2: Traditional flip-flop and latch implementations

### 4.1 Flip-flop

Flip-flops are edge triggered devices, i.e. they allow the value at the input to propagate to the output only when an edge occurs in the control signal driving the flip-flop. Positive edge triggered flip-flops are the most common way to sequence program execution due to their simple timing behavior. While negative edge triggered flip-flops are also possible, they are not as common as positive edge triggered flip-flops. Mixing positive and negative edge triggered flip-flops can be done, but it is avoided in general to keep the timing of the circuit simpler, unless there is a good reason for it.

### 4.2 Transparent latch

Latches have varying properties depending on the clocking scheme. For example pulsed latches are driven by short clock pulses and usually accompanied by local pulse generators, while transparent latches are usually driven by longer clock pulses in at least in two different phases. This work focuses on transparent latch design and all references to latches mean transparent latches, unless specified otherwise. For simplicity the focus is on latches operating in two complementary phases with 50% duty cycle clocks.

When the control signal is active the latch is said to be transparent (or open). While the latch is transparent, output signal of the latch follows the input signal. While the control signal is not active latch is said to be opaque (or closed). While the latch is opaque, the output signal is "locked in" and does not change with the input signal. Latches can be either active high or active low, but unlike flip-flops at least two alternating active phases are needed for sequencing. As a device latches are simpler to build and require less transistors than flip-flops. In fact two transparent latches placed back to back operating in opposite phases as show in figure 4.3 are behaviorally equivalent to a single flip-flop. Compared to flip-flops latches have a wide window during which a signal can propagate, which gives latches an useful feature called *time-borrowing*. As long as the input data

Figure 4.3: Two latches forming a functionally equivalent flip-flop

stabilizes to correct value before the latch becomes opaque the timing will not be violated. Because data does not have to stabilize before the active clock edge, the delays between latches do not have to be as evenly divided as delays between flip-flops. Instead the logic in some stages can borrow time from subsequent stages. The timing will be met if some parts of the subsequent stages are fast enough to compensate for the delays introduced in the slower stages.

### 4.3 Timing behavior

In digital circuit design the timing of the circuit is the most important aspect of the design. If the design fails to meet it's timing requirements the manufactured chip will not be functional. While in digital domain signals can have only values 0 and 1, in real devices signal transitions are not instantaneous. Each cell in the design has a *propagation delay*, which is the time it takes for a change in input signal value to appear on the output of the cell. All cells and wires, through which the signal propagates, add delay to the signal. To successfully capture a signal value to a memory element the signal must be stable while the value is being stored. Otherwise the captured values become unpredictable causing the system to fail.

Sequential systems introduce overhead which increase the clock cycle time from three sources: propagation delay, setup time and clock skew [15]. The time a signal must be

stable before an edge is called setup time ( $\Delta_{DC}$ ) and the time a signal must be stable after an edge is called hold time ( $\Delta_{CD}$ ). If a signal does not meet setup or hold requirements the captured value becomes unpredictable. The maximum clock frequency for which a path can meet the timing requirements is limited by max-delay consisting of the total propagation delay of logic ( $\Delta_{logic}$ ) on the path and a sequencing overhead  $(T_c = \Delta_{logic} + overhead)$ . If two or more memory elements are placed back-to-back without any logic between them, a common way to delay a signal, care must be taken to make sure the signal takes at least *min-delay* amount of time to propagate. Otherwise the subsequent memory elements might capture an incorrect value. While a system violating max-delay can still function at lower frequencies, usually min-delay violations cannot be compensated afterwards and they can render the system inoperable. Even for relatively small systems distributing a completely synchronous clock signal to all clocked components is not possible in practice. The clock will arrive to different parts of the system at slightly different times. Therefore some margin needs to be added for compensating the clock skew  $t_{skew}$  to ensure correct operation. For example, if the clock arrives late to a memory element and early to a subsequent memory element, the time the signals has for propagating through the logic between the memory elements is reduced.

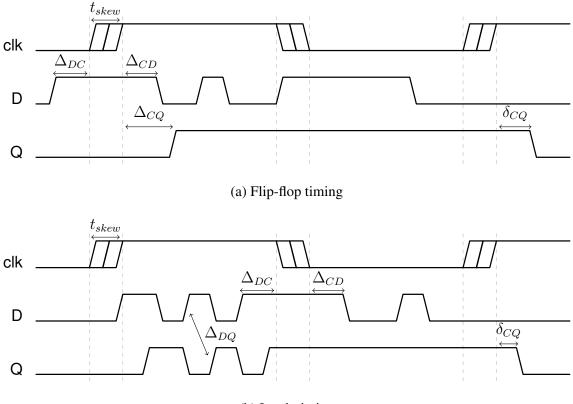

Table 4.1[15] shows comparison of flip-flop and latch performance. For latches the  $t_{nonoverlap}$  denotes the time between clock falling and rising edge of subsequent stages. For 50% duty cycle two-phase complementary clocks the  $t_{nonoverlap}$  is zero. Reducing the duty cycles of the clocks would increase the non-overlap time. For sequencing overhead of flip-flops the data propagation delay at clock edge  $\Delta_{CQ}$ , setup time before the clock rises again  $\Delta_{DC}$  and clock skew  $t_{skew}$  must be taken in to account. Sequencing overhead of latches depends only on propagation delay  $2\Delta_{DQ}$  (two latches in clock cycle  $T_c$ ). The min-delay requirement for both latches and flip-flops are quite similar. The  $\delta_{CQ}$  denotes the minimum time from clock switching until the data at the output becomes valid. The related delays are visualized in figure 4.4.

| Element           | Sequencing overhead                    | Time borrowing                                            | Min-delay                                               |

|-------------------|----------------------------------------|-----------------------------------------------------------|---------------------------------------------------------|

| Flip-flop         | $\Delta_{CQ} + \Delta_{DC} + t_{skew}$ | 0                                                         | $\Delta_{CD} + t_{skew} - \delta_{CQ}$                  |

| Transparent latch | $2\Delta_{DQ}$                         | $\frac{T_c}{2} - \Delta_{DC} - t_{skew} - t_{nonoverlap}$ | $\Delta_{CD} + t_{skew} - \delta_{CQ} - t_{nonoverlap}$ |

|                   |                                        |                                                           | (in each half-cycle)                                    |

Table 4.1: Flip-flop and latch performance

(b) Latch timing

Figure 4.4: Positive edge triggered flip-flop and transparent latch timing delay components visualized

#### 4.4 **Process variations**

Essentially, all properties of all components of a circuit are subject to Process, Voltage, and Temperature (PVT) variations. Detailed PVT analysis is out of scope for this work, and here the clock skew is surrogate for all PVT variations. Depending on the location of the memory elements, the phase of the clock signal is skewed slightly. While careful clock tree design can mitigate the clock skew it cannot be completely eliminated. Process variations, which are especially troublesome in low-power designs, reduce the manufacturing yields. Latches offer some benefits over flip-flops for designs which are subjected to large manufacturing process variations. Hurst et. al have shown in [4] that transparent latches can reduce the rate of failures by four times compared to flip-flops. While under traditional timing models the maximum performance of latches does not differ from flip-flops, under high variation and statistical timing model latches have advantage over flip-flops. Because each manufactured instance has unique timing characteristics it is impossible to create an optimal timing for every scenario at design time. Instead only the best solution for largest number of devices can be selected. Flip-flops are affected by variations more than transparent latches, because they can only capture value at the clock edges. Transparent latches have a much wider window for the signals to propagate, allowing a larger number of the possible variations to meet the timing.

## Chapter 5

# Latches — replacing flip-flops

As explained on previous chapter latches have some advantages over flip-flops for designs affected by large manufacturing process variations. Because latches are also simpler devices it is expected that latch-based design would also have smaller area than equivalent flip-flop-based design. Since no open-source latch-based RISC-V cores were available, SCR1 was previously selected as a target for transforming the flip-flop-based logic to latch-based logic, while keeping the core behaviorally intact. This chapter presents an HDL approach developed for transforming the flip-flop-based core to a latch-based core. A SystemVerilog analysis tool and simple python preprocessor were developed to generate signal dependency graphs. The analysis tool replaces each flip-flop vertex in the graph with a single latch, assigns phases to the signals and detects feedback loops which need additional latch inserts.

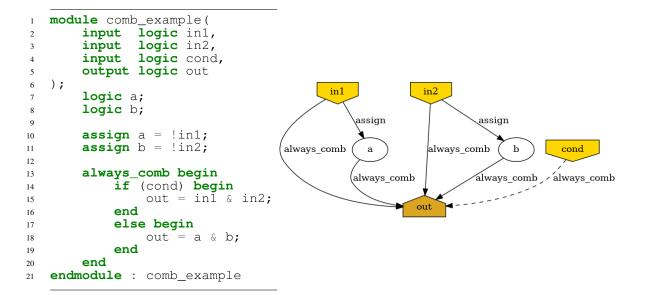

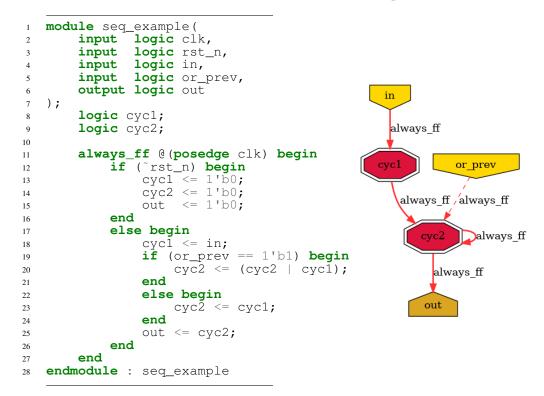

Synthesis tools transform the RTL description of the circuit to gate level representation by mapping the described logic to cells. The cells are picked based on what kind of logic the RTL description implies, the properties of available cells and the given constraints. In order to synthesize latches instead of flip-flops and vice versa, the RTL has to be written in a way that implies the desired type of cells. While it is possible to specify cells explicitly, doing so at scale quickly becomes tedious and error prone. Explicit definitions are also tied to specific cell libraries and reduce portability between different libraries. The SCR1 core is written in SystemVerilog. In SystemVerilog it is possible to express designer intent more strongly than some in other HDLs commonly used in the industry, such as Verilog or VHDL. SystemVerilog standard [16] specifies separate always\_ff and always\_latch procedures which allows user to define explicitly the *intent* to generate flip-flops or latches. However, if the statements inside always\_ff or always\_latch procedures do not also *imply* flip-flops or latches then something else will be generated. SystemVerilog does not enforce checks on whether logic inside always\_latch block is really representing a latch, but it urges tools to check and generate warnings in case of mismatch. Separate blocks for flip-flops and latches improve readability and help with debugging.

### 5.1 Methodology

Latch-based design requires a slightly different methodology than flip-flop-based design. Usually most flip-flops operate in the same clock phase, while in transparent latch designs the latches operate in alternating phases.

In latch-based circuit operation each signal is either stable when the driving latch is opaque or unstable when the driving latch is transparent. Wide signal propagation window of transparent latches introduces some constraints that are not present in flip-flop-based designs. In flip-flop designs connecting two positive edge triggered flip-flops back-to-back delays the signal by one clock cycle. Connecting two latches operating in a same phase rarely make sense, because this would create a one long path, where the second latch acts as a delay buffer. To keep the circuit "sane" there are several rules on how the signal phases can be connected. Connection rules are shown in table 5.1 in terms of HDL assignments, where "RHS" denotes right-hand side of the assignment and "LHS+cond" denotes left-hand side of the assignment and conditionals affecting the assignment. The rationale for forbidden connections is shown in table 5.2. In HDL code it is perfectly

| RHS/LHS+cond | Comb. s1 | Comb. s2 | Latch s1 | Latch s2 |

|--------------|----------|----------|----------|----------|

| Comb. s1     | Yes      | No       | No       | Yes      |

| Comb. s2     | No       | Yes      | Yes      | No       |

| Latch s1     | Yes      | No       | No       | Yes      |

| Latch s2     | No       | Yes      | Yes      | No       |

Table 5.1: Allowed and forbidden connection matrix.

legal to mix phases in a way that can mess up the synchronization of the signals. Due to differences in timing behavior writing latch-based HDL code requires a slightly different mindset than writing flip-flop code. Managing multiple phases increases the complexity from timing perspective compared to traditional positive clock edge triggered flip-flop design. Coherent signal names are very valuable for debugging signal phase related issues in the design. A signal naming scheme shown in table 5.3 based on scheme proposed in [15] was adopted. Adding a suffix indicating the signal phase and assignment type helps to identify timing problems. Suffixes "\_s1" and "\_s2" indicate continuous assignment stable in phase 1 and phase 2 respectively. Additional letter "1" indicates that the signal originates from an assignment implying a latch. Special cases "\_12t1" and "\_11t2" signify a latch inserted to delay the signal by a half-cycle and change the phase of the signal from phase 2 to phase 1 and from phase 1 to phase 2, respectively, without any logic in between.

### 5.2 Signal dependencies

Signal dependencies of a circuit described in RTL can be represented by a directed graph, where each vertex is a signal node and directed edges represent dependencies formed between the vertices by assignments. The underlying functions of the assignments are

| Forbidden connection                         | Reason                                                            |

|----------------------------------------------|-------------------------------------------------------------------|

| 1. Latch $\rightarrow$ latch, same phase     | Second latch acts as a buffer instead of synchronization element. |

| 2. Comb $\rightarrow$ latch, same phase      | Latch acts as a buffer instead of synchronization element.        |

| 3. Comb $\rightarrow$ comb, different phase  | Signal becomes unpredictable, because phases are mixed.           |

| 4. Latch $\rightarrow$ comb, different phase | Comb signal is not stable in the intended phase.                  |

Table 5.2: Rationale for forbidden connections for two phase transparent latch design

| Output type | Output stable | Input type    | Input stable | Output suffix |

|-------------|---------------|---------------|--------------|---------------|

| Comb        | Phase 1       | Comb or Latch | Phase 1      | _s1           |

| Comb        | Phase 2       | Comb or Latch | Phase 2      | _s2           |

| Latch       | Phase 1       | Comb          | Phase 2      | _s11          |

| Latch       | Phase 2       | Comb          | Phase 1      | _s21          |

| Latch       | Phase 1       | Latch         | Phase 2      | _12t1         |

| Latch       | Phase 2       | Latch         | Phase 1      | _11t2         |

Table 5.3: Signal naming methodology

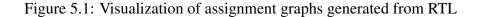

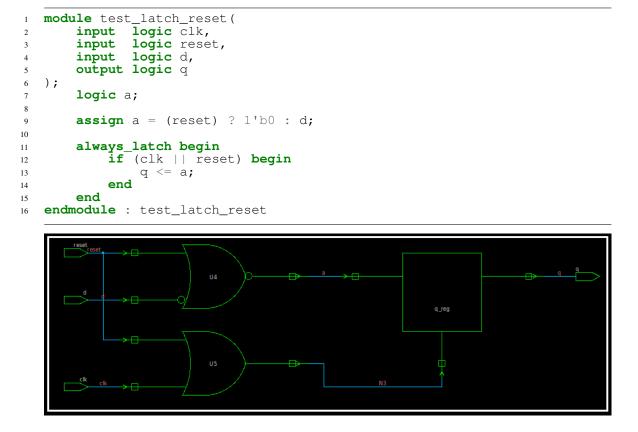

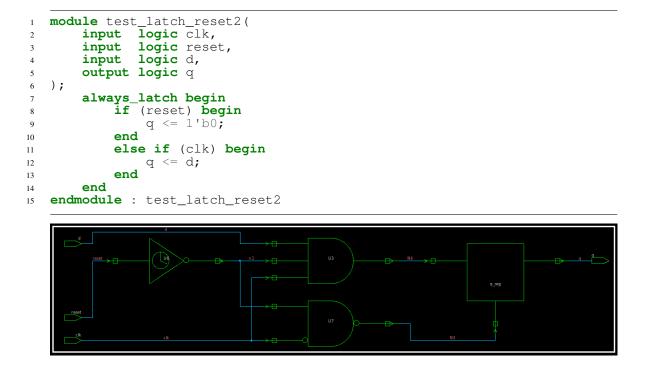

not relevant for the dependency graph. Signal assignments can be either sequential or combinational and either conditional or direct dependencies. Propagation of sequential assignments is controlled by a clock signal and combinational assignments propagate constantly. Dependency is conditional if the signal is not directly assigned to dependent signal, but it has an effect to the evaluation of the assignment via conditional statements. Each vertex and edge in the graph is "colored" to be either sequential or combinational as defined by the RTL assignment expression. Additionally each edge can be direct or conditional. Example visualizations of graphs and of the RTL code the graph was generated from can be seen in figure 5.1. Input and output ports are represented by bright and dark yellow nodes. Signals values flow from input to output. As can be seen in figure 5.1 (a) both assign statements and blocking assignments inside always\_comb blocks result in combinational dependency. Dashed edges denote conditional dependency. In figure 5.1 (b) all assignments are sequential. Notice that the cyc2 signal has a dependency to itself, because it needs the previous value of itself to evaluate correctly, depending on the state of or\_prev signal. With flip-flops feedback from cell output to it's input is allowed, because the signal can only propagate on clock edge.

#### 5.3 Transform

Transforming flip-flop-based design to a latch-based design could be accomplished by simply replacing all instances of flip-flops with two back-to-back latches. On the other hand the transformation could be done by replacing a flip-flops with just one latch and then adjusting the signal phases and inserting latches to feedback paths when necessary. The latter approach was chosen, because the resulting RTL code is truly in latch-based style.

Before the input files are parsed by the analysis tool, they are run through a preprocessor. A simple python preprocessor was developed for the purpose of making the job

(a) Combinational example

of analysis tool easier. The preprocessor handles expansion of macros, preprocessor conditionals and include statements. Preprocessor outputs a single file which combines all the included files, has all macro values expanded and contains only the blocks selected by conditional macros.

A SystemVerilog analysis tool was developed to identify logical dependencies in the circuit. The tool was built with ANTLR4 parser generator. Given a grammar description of a formal language ANTLR4 generates lexer and parser. First the lexer tokenizes the input for the parser. Each token represents character strings of the code with distinct meaning, such as keywords, identifiers, comments, etc. Based on the token stream the parser then generates a parse tree data structure describing the code in a structured manner.

Lexer and parsers are commonplace in compiler front-ends and various tools have been developed for generating parsers from formal grammar definitions. Complex languages, such as SystemVerilog, often have relatively complicated grammar. Fortunately Carr *et al.* have developed SystemVerilog ANTLR4 grammar for Microsoft's static analysis platform, gNOSIS [17], and released it under MIT license. Additionally the grammar of SystemVerilog is comprehensively described in [16]. While the grammar file was in quite good shape, it required minor tweaks (appendix A) before the code was parsed properly. Given a grammar description, ANTLR4 generates a parser skeleton, which by itself does nothing with the parse tree. Additional functionality was added to the parser to generate a directed graph of the signal dependencies with JGraphT library while traversing the parse tree.

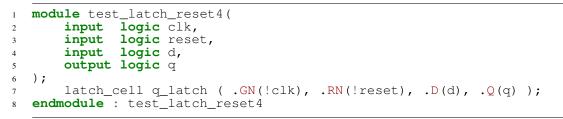

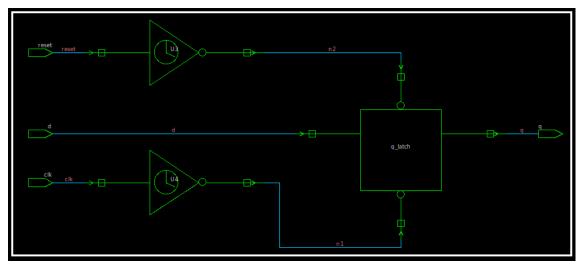

As the parse tree is being traversed, for each new signal encountered a vertex representing the new signal is added to the graph. If a vertex corresponding to the signal already exists, only the edges representing dependencies are updated. Vertices or signals from which the assignment depends are connected by a directed edge. Dependencies are categorized either as direct dependencies or conditional dependencies. Direct dependencies of an assignment are defined by the right-hand side of the assignment statement, i.e. what is being assigned to the signal node. Signals can also be conditionally dependent on another signal. For example, if an assign statement for signal A is chosen based on value of signal B, but the signal B is not directly assigned to signal A, a conditional dependency is created. After the graph is constructed clock and reset signal nodes are removed, because they are not dependent on any other signal.