#### FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# Design of an Ultra-Low Power RTC for the IoT

### David Rosenberger Fernandes Ferrão

FINAL VERSION

Mestrado Integrado em Engenharia Electrotécnica e de Computadores

Supervisor: Cândido Duarte

Co-Supervisor: Francisco Gonçalves

### Resumo

A infraestrutura da Internet das Coisas (IoT) está a crescer a um nível exponencial. O potencial de mercado aumenta consequentemente, pois as utilidades previsíveis das implementações possíveis são extremamente diversas, com imensos proveitos ainda por detectar. Por isso, uma crescente procura por componentes que tenham um consumo muito reduzido (ULP) está a ocorrer, pois estes cumprem os requisitos necessários para uma implementação numa rede IoT.

Um nó IoT é composto por uma unidade de gestão de potência, um receptor/emissor RF para comunicações externas, sensores, um processador e um relógio de tempo real (RTC). O RTC é um dos circuitos responsáveis pela gestão do modo de operação num nó IoT e, consequentemente, do seu consumo de potência pois este passa a maioria do seu tempo em "sleep mode" com o único circuito ligado sendo o RTC, que requer um design que tenha em atenção um consumo ULP. Realizar o design customizado do circuito e o layout físico deste torna-se um trabalho com imensos detalhes que necessitam de uma atenção considerável.

O trabalho desenvolvido apresenta o desenvolvimento de um RTC com consumos ULP, com componentes analógicos e digitais projetados de forma independente e depois interconectados. A componente analógica é responsável pela criação de uma estrutura que fornece uma independência de variações PVT ao Current-Starved Ring Oscillator com uma frequência de saída estável de 32.768 kHz, a consumos ULP, que subsequentemente é injetada no bloco digital. Diferentes componentes foram desenhados para a implementação analógica: referências de tensão, oscilador e regulador charge pump. Estes blocos individuais foram desenvolvidos com variações PVT reduzidas, operando com consumos ULP.

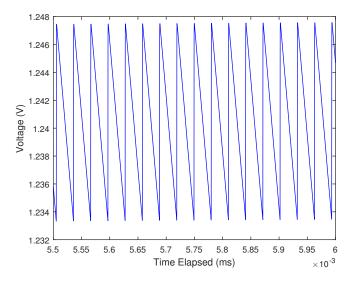

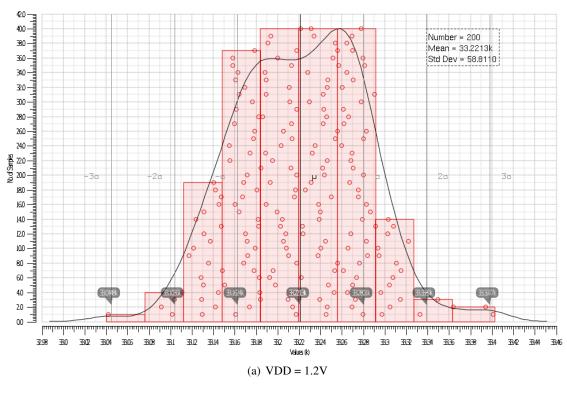

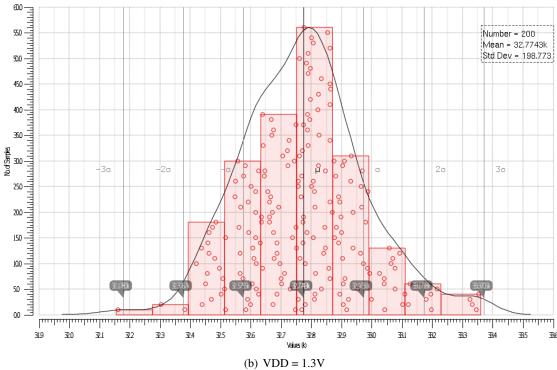

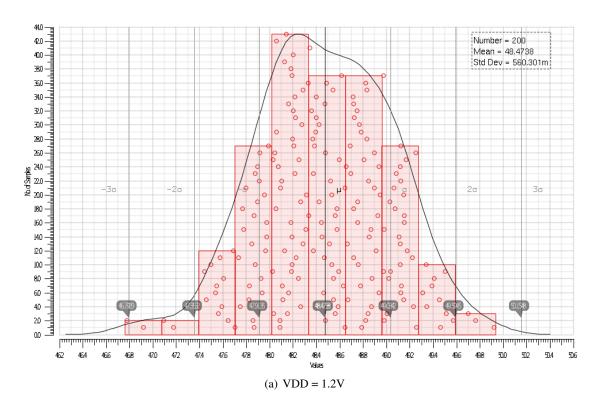

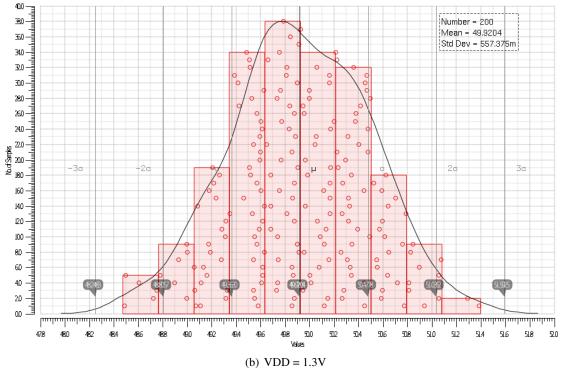

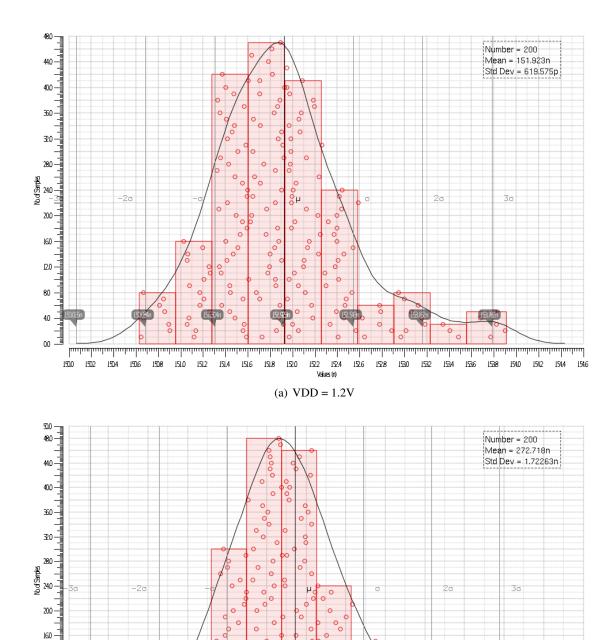

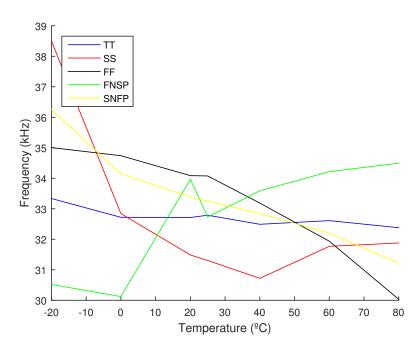

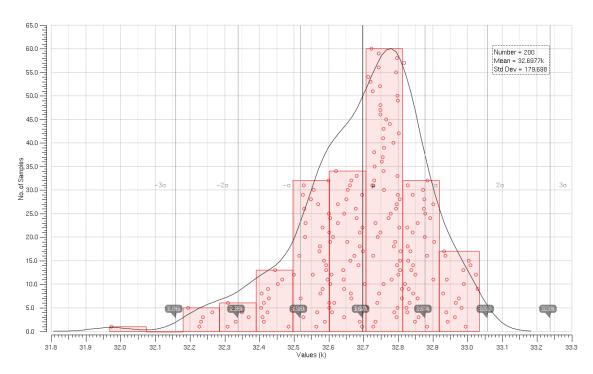

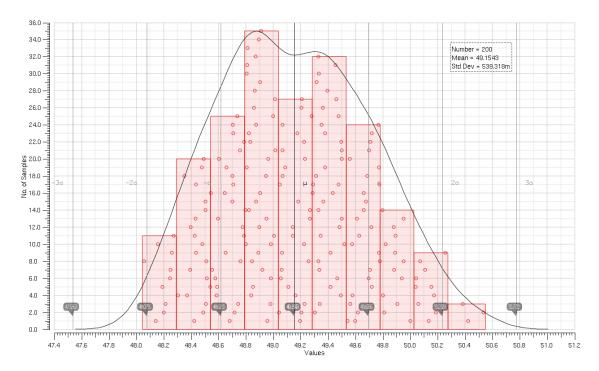

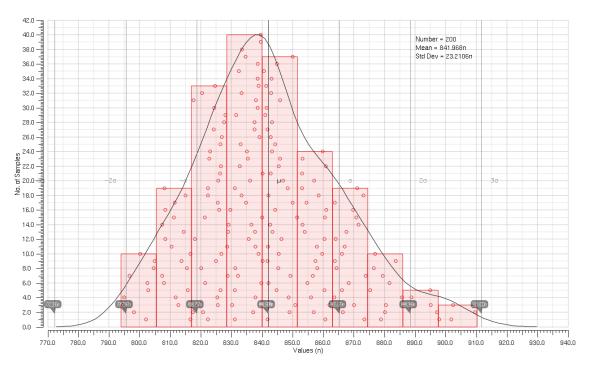

Isto produz um circuito com um valor de energia/ciclo de 25.7 pJ para um intervalo de temperatura que vai desde os -20 ° C até a 80 ° C, com um coeficient de temperatura de 291 ppm/°C com uma variação máxima de frequência em comparação com o objectivo de 1.74% a -20 ° C e uma mínima de 0.063% a 25 °C. Simulações Monte Carlo no corner TT do circuit extraído do layout atingem um consumo do bloco analógico de 841.97 nW para uma frequência de saída média de 32.698 kHz e um desvio padrão de 179.7 Hz.

### **Abstract**

The emerging Internet of Things (IoT) infrastructure is growing at an exponential rate. Thus market potential for these technologies is huge, since the foreseeable applications are extremely diverse. Subsequently, there is an increasingly high demand for the development of ultra-low power (ULP) components that meet the performance requirements of this IoT network.

An IoT node is composed of a power management unit, a processor, an RF transceiver for external communications, sensor components and a real-time clock (RTC). The RTC is the circuit responsible for the management of the time in an IoT node, being an always-on circuit. This is intertwined with the node power consumption, as it stays most of its operational life in sleep mode with the only on circuit the RTC, which requires an ULP design of the RTC. Hence, designing the full-custom circuitry and physical layout of an RTC becomes a job that has a lot of details that need considerable attention.

The work displayed comprehends the development of an ULP mixed-signal RTC, with the analog and digital blocks developed independently and then interconnected. The analog component is responsible to guarantee an independent to the PVT conditions Current-Starved Ring Oscillator with a stable output frequency of 32.768 kHz, at ULP, which is then injected to the digital block. Different individual components were designed for the analog implementation such as: voltage references, regulated charge pumps and a oscillator. These individual blocks were developed with low PVT variations while operating in an ULP consumption mode.

This produces a circuit with an energy/cycle value of 25.7 pJ for a temperature range of -20 °C to 80 °C, a temperature coefficient of 291 ppm/°C, with a maximum absolute frequency variation relative to the proposed objective of 1.74% at -20 °C and a minimum of 0.063% at 40 °C. Monte Carlo simulations in the TT corner of the layout extracted circuit achieve an analog block power consumption of 841.97 nW for an average output frequency of 32.698 kHz with a standard deviation of 179.7 Hz.

# Agradecimentos

Em primeiro lugar, quero agradecer á minha família, por sempre me ter apoiado em tudo o que quis fazer na minha vida e de me ter dado esta oportunidade de prosseguir os estudos num curso que sempre adorei. Esta tese representa a realização de um sonho de alguém que já não está cá, mas que tenho a certeza absoluta que teria um enorme gosto em ver o quanto conquistei e o que consegui fazer, independentemente do que a vida me tenha posto á frente.

Quero também agradecer a uma rapariga muito importante na minha vida, a Leonor, por me ter acompanhado durante grande parte do meu percurso académico e me ter suportado nos meus altos e baixos, estando sempre lá para me ouvir e ajudar mesmo quando tudo parecia perdido. Por ter tido a paciência de estar comigo e subsistir, mesmo enquanto estava demasiado focado nos diversos projectos extracurriculares nos quais estive envolvido.

Um grande agradecimento vai também para um pequeno grupo de pessoas com o qual tive a oportunidade de aprender a "viver" e "conviver". E, no fundo, ainda estou a aprender (lentamente). Ao Rodriguez, o Greg e ao Winnie, três pessoas com as quais sempre pude contar para o que quer que fosse na minha vida, independentemente das horas que fossem ou da quantidade de loiça que estivesse por arrumar.

Ao meu ano, com o qual passei imensos momentos nesta Faculdade que, mais do que um estabelecimento de ensino, considero a minha Casa. À Ginny, ao T-Rex , à Escritora, à Alumínio, o Winnie (novamente), ao Surfista e à Missões: um grande abraço e isto tudo não teria sido possível sem vocês. Apesar de não ter sido sempre um dos vossos, acabámos por nunca nos afastar. Em jeito de desabafo, ás vezes é preciso haver sacrifício para haver progresso. Ou simplesmente tentar algo diferente.

À boa gente de Bragança, cujo destino decidiu trocar as voltas e dispersar-nos pelo país fora. As reuniões trimestrais sempre valeram a pena e vocês nunca foram esquecidos, por mais que a minha experiência universitária no Porto se tenha assemelhado a um semestre ERASMUS de 5 anos.

Por fim, quero também agradecer ao meu co-orientador, o Francisco Gonçalves, um senhor cuja paciência e boa vontade foram dois dos grandes combustíveis para a realização desta dissertação. Um grande obrigado por toda a sabedoria e experiência que me me foi passada. Também uma palavra de apreço para o Professor Cândido Duarte, o meu orientador, que sempre me soube ajudar e por me ter dado a oportunidade de trabalhar neste tema que, quanto mais se estudava, mais interessante se tornava.

David Ferrão

"O burro nunca aprende, o inteligente aprende com sua própria experiência e o sábio aprende com a experiência dos outros"

# **Contents**

| 1 | Intr | oduction                              |

|---|------|---------------------------------------|

|   | 1.1  | Wireless Sensor Networks              |

|   | 1.2  | WSN Node Power Consumption            |

|   | 1.3  | Motivation                            |

|   | 1.4  | Problem Statement                     |

|   | 1.5  | Document Outline                      |

| 2 | Sub  | threshold Operation Regime            |

|   | 2.1  | CMOS Power Consumption                |

|   |      | 2.1.1 Dynamic Power                   |

|   |      | 2.1.2 Short Circuit Current           |

|   |      | 2.1.3 Static Power Dissipation        |

|   | 2.2  | MOS EKV Model                         |

|   |      | 2.2.1 Process                         |

|   |      | 2.2.2 Voltage                         |

|   |      | 2.2.3 Temperature                     |

|   |      | 2.2.4 Delay and Operational Frequency |

| 3 | Real | I Time Clock Integrated Circuits      |

|   | 3.1  | Review of the RTC IC Market           |

|   | 3.2  | Oscillators                           |

|   |      | 3.2.1 Crystal Oscillators             |

|   |      | 3.2.2 RC Oscillators                  |

|   |      | 3.2.3 Relaxation Oscillators          |

|   |      | 3.2.4 Ring Oscillators                |

| 4 | Proj | posed Architecture 29                 |

|   | 4.1  | Analog Topology                       |

|   | 4.2  | Digital Implementation                |

| 5 | Pow  | er Management Unit 3:                 |

|   | 5.1  | Voltage Reference                     |

|   |      | 5.1.1 2T Voltage Reference            |

|   |      | 5.1.2 6 Stages Voltage Reference      |

|   | 5.2  | Regulated Charge Pump                 |

X CONTENTS

| 6  | Oscillator Design                   | 57         |

|----|-------------------------------------|------------|

|    | 6.1 Current Starved Ring Oscillator | 58         |

|    | 6.2 Temperature Variation           | <b>5</b> 9 |

|    | 6.3 Process Variation               | 62         |

| 7  | Integration                         | 75         |

| 8  | Conclusions and Future Work         | 83         |

|    | 8.1 Future Work                     | 84         |

| Re | ferences                            | 85         |

# **List of Figures**

| 1.1 | Some applications of the IoT                                               | 1 |

|-----|----------------------------------------------------------------------------|---|

| 1.2 | Conceiving a new dimension                                                 | 2 |

| 1.3 | IoT Architecture                                                           | 3 |

| 1.4 | Ratio of Smart Objects vs Human Population                                 | 3 |

| 1.5 |                                                                            | 4 |

| 1.6 | WSN IoT node main components                                               | 5 |

| 1.7 |                                                                            | 6 |

| 1.8 |                                                                            | 6 |

| 2.1 | The power components of a CMOS digital circuit                             | 0 |

| 2.2 | Components of Leakage Current                                              | 1 |

| 2.3 | MOSFET Drain Current vs Gate to Source Voltage                             | 2 |

| 2.4 | Bias current dependence on temperature variations                          | 5 |

| 3.1 | RTC IC main core functional blocks                                         | 7 |

| 3.2 | Time registers functionality                                               | 9 |

| 3.3 | Minimum Voltage Supply vs Current Consumption in RTC ICs from table 3.2 22 | 2 |

| 3.4 | Conventional XO circuit                                                    | 3 |

| 3.5 | Widely used XO for low power circuits                                      | 4 |

| 3.6 | Relaxation Oscillator circuit                                              | 6 |

| 3.7 | Ring Oscillator circuit                                                    | 6 |

| 3.8 | Current Starved Ring Oscillator circuit                                    | 7 |

| 4.1 | Overall schematic block of the final circuit implemented                   | 9 |

| 4.2 | Analog blocks for implementation                                           | 1 |

| 4.3 | RTC digital blocks                                                         | 2 |

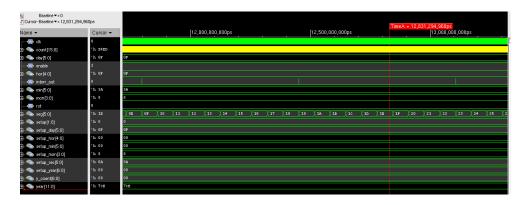

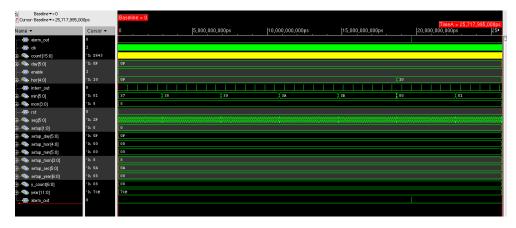

| 4.4 | Setup and Reset verification                                               | 3 |

| 4.5 | Interrupt Validation                                                       | 4 |

| 4.6 | Interrupt and Alarm Validation                                             | 4 |

| 5.1 | Power Management Unit                                                      | 5 |

| 5.2 | 2T voltage reference                                                       | 7 |

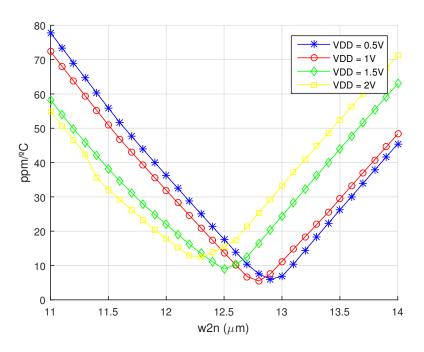

| 5.3 | 2T - TC variation with W1/W2 ratio                                         | 8 |

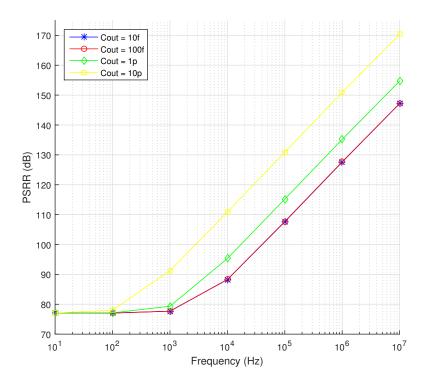

| 5.4 | 2T - PSRR with different output capacitances                               | 9 |

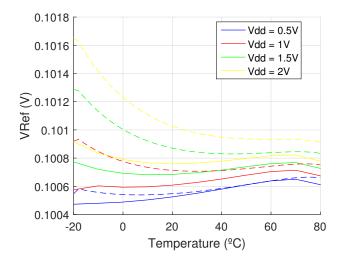

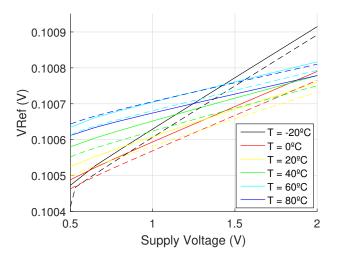

| 5.5 | 2T - Output Voltage Reference versus Temperature                           | 0 |

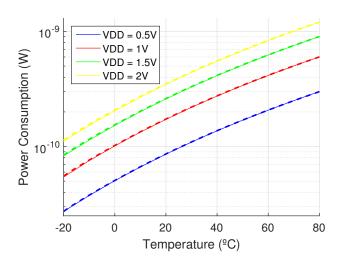

| 5.6 | 2T - Power Consumption versus Temperature                                  | 0 |

| 5.7 | 2T - Output Voltage Reference versus Supply Voltage                        | 1 |

| 5.8 | 2T - Power Consumption versus Supply Voltage                               | 1 |

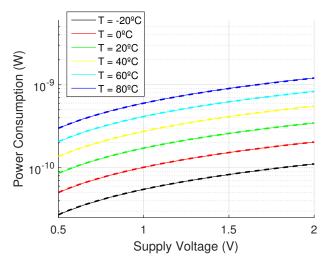

| 5.9 | 2T - Output Voltage Reference versus Process Corners                       | 2 |

xii LIST OF FIGURES

| 5.10              | Layout of the 2T Bandgap Voltage Reference                                       |

|-------------------|----------------------------------------------------------------------------------|

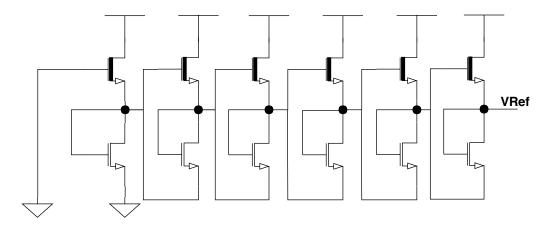

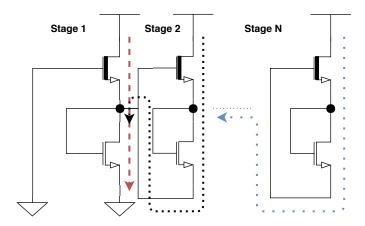

| 5.11              | Voltage Reference with 6 stages                                                  |

|                   | Current flow in the Voltage Reference with N stages                              |

|                   | TC variation with W1/W2 ratio for 6 stages BGR                                   |

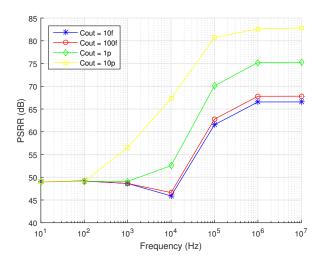

| 5.14              | PSRR - Voltage Reference with 6 stages                                           |

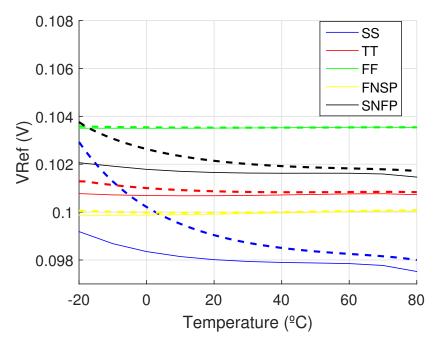

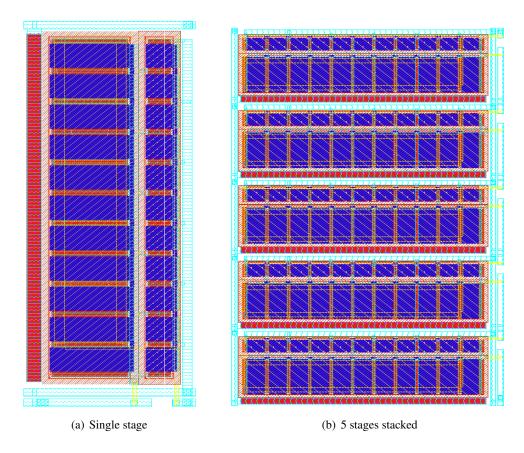

|                   | 6S Voltage Reference Layout stages                                               |

|                   | 6S Voltage Reference Final layout with $C_{out}$                                 |

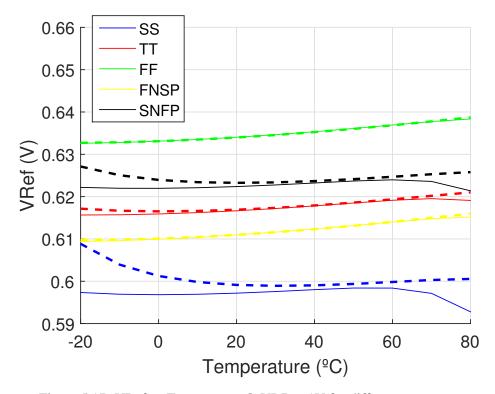

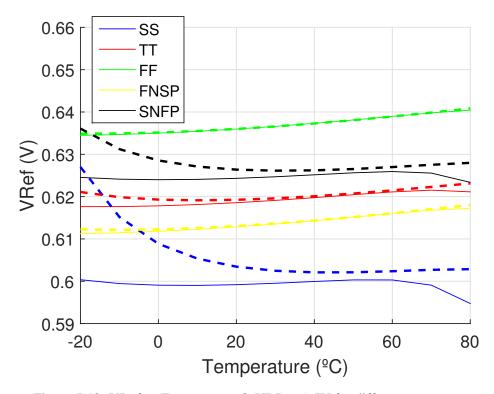

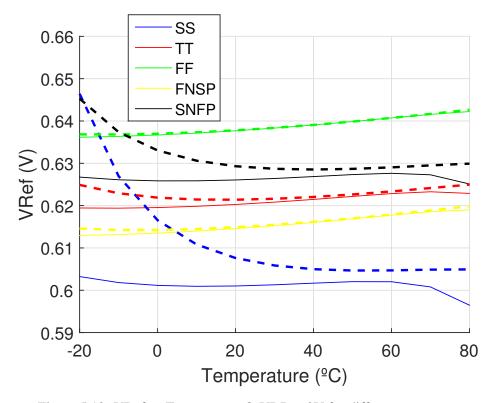

|                   | 6S voltage reference - VRef vs Temperature @ VDD = 1V for different process      |

|                   | corners                                                                          |

| 5.18              | 6S voltage reference - VRef vs Temperature @ VDD = 1.5V for different process    |

|                   | corners                                                                          |

| 5.19              | 6S voltage reference - VRef vs Temperature @ VDD = 22V for different process     |

|                   | corners                                                                          |

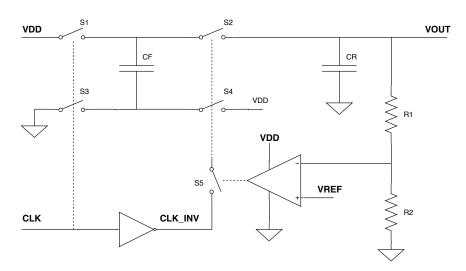

| 5.20              | Regulated Charge Pump                                                            |

| 5.21              | Startup Circuit of the Regulated Charge Pump                                     |

|                   | Startup of the Charge Pump                                                       |

| 5.23              | MOSCAP Layout                                                                    |

|                   | Resistors in the Voltage Divider Layout                                          |

|                   | Output of the Charge Pump                                                        |

|                   | Final Charge Pump Layout                                                         |

| <i>c</i> 1        |                                                                                  |

| 6.1               | Oscillator Design block diagram                                                  |

| 6.2               | Proposed Current Starved Ring Oscillator circuit                                 |

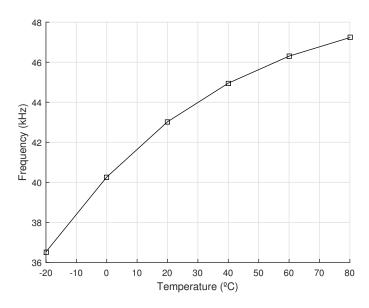

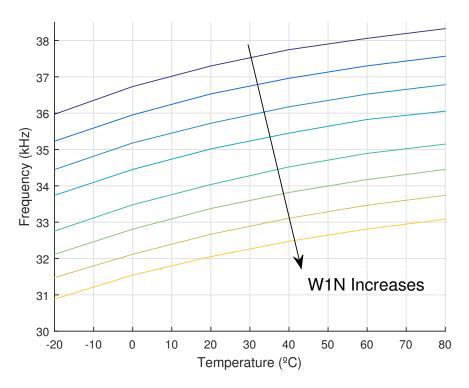

| 6.3               | Frequency variation with temperature in the CSRO                                 |

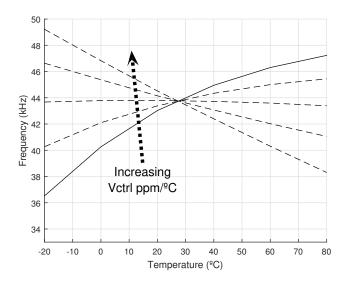

| 6.4               | Frequency variation with temperature in the CSRO - different different values of |

| <i>( 5</i>        | ppm/°C                                                                           |

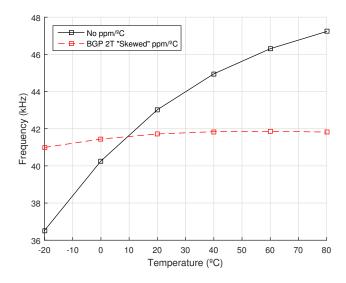

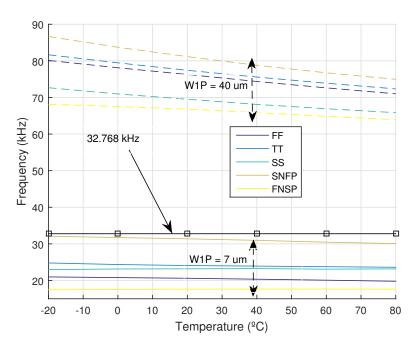

| 6.5               | Output oscillation frequency of the CSRO with a skewed 2T Voltage Reference . 60 |

| 6.6               | 2T Skewed Reference Voltage Layout                                               |

| 6.7               |                                                                                  |

| 6.8               |                                                                                  |

| 6.9<br>6.10       |                                                                                  |

|                   | CSRO current mirror analysis                                                     |

| 0.11              | CSRO frequency variation with $W_{M_{-}N1}$                                      |

|                   | CSRO frequency variation with $W_{P\_N1}$                                        |

|                   | CSRO layout                                                                      |

|                   | Layout results for FF process corner                                             |

|                   | Layout results for FNSP process corner                                           |

|                   | Layout results for SNFP process corner                                           |

|                   | Layout results for SS process corner                                             |

|                   | Layout results for TT process corner                                             |

|                   | Monte Carlo Simulation for the TT process corner - Output Frequency              |

|                   | Monte Carlo Simulation for the TT process corner - Duty Cycle                    |

|                   | Monte Carlo Simulation for the TT process corner - Power Consumption             |

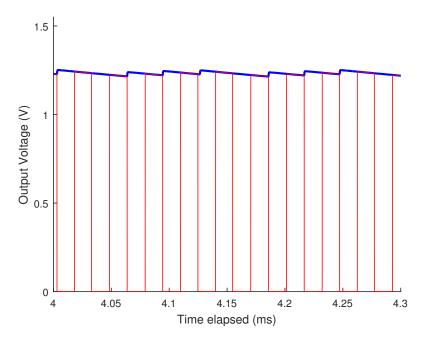

| 6.22              | CSRO Output Signal                                                               |

| - 1               |                                                                                  |

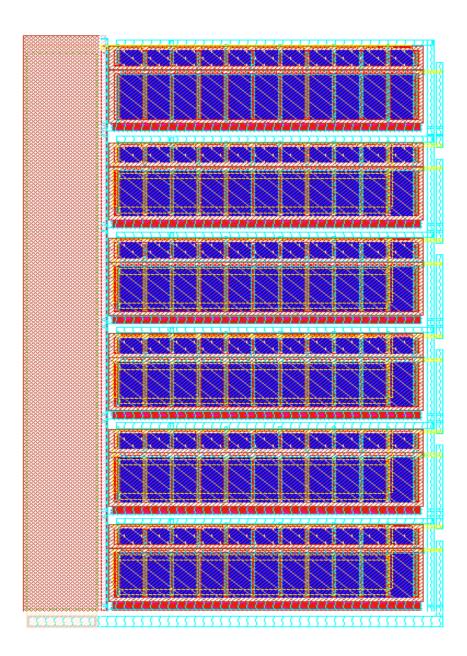

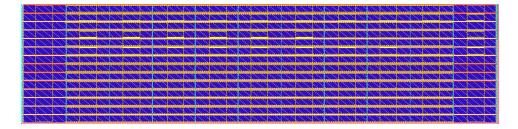

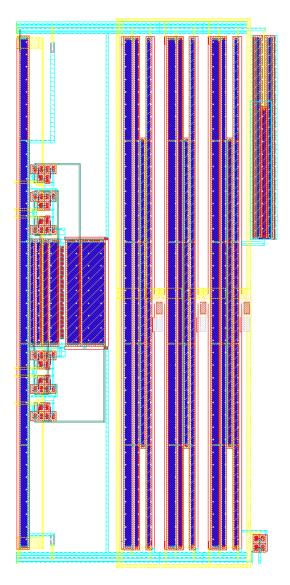

| '/. I             | Final layout of the proposed circuit                                             |

| 7.1<br>7.2        | Final layout of the proposed circuit                                             |

| 7.1<br>7.2<br>7.3 | Final layout of the proposed circuit                                             |

| LIST OF FIGURES | xiii |

|-----------------|------|

|                 |      |

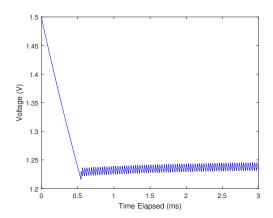

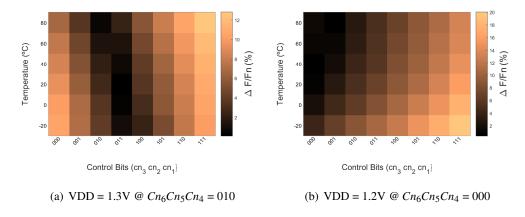

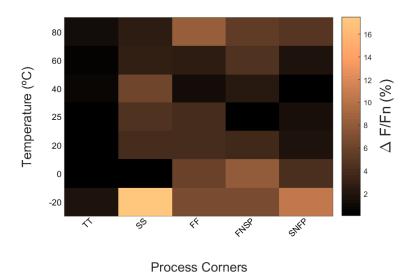

| Frequency Deviation for each process corner at different temperatures | <b>7</b> 9                                                         |

|-----------------------------------------------------------------------|--------------------------------------------------------------------|

| Output Frequency for each process corner at different temperatures    | 80                                                                 |

| Monte Carlo Simulation TT corner - Final Layout - Output Frequency    | 81                                                                 |

| Monte Carlo Simulation TT corner - Final Layout - Duty Cycle          | 81                                                                 |

| Monte Carlo Simulation TT corner - Final Layout - Power Constumption  | 82                                                                 |

|                                                                       | Output Frequency for each process corner at different temperatures |

xiv LIST OF FIGURES

# **List of Tables**

| 3.1 | SQW functionalities from the RV-1805-C3 RTC IC                       | 20 |

|-----|----------------------------------------------------------------------|----|

| 3.2 | RTC IC in the current market                                         | 21 |

| 4.1 | RTC Operation Modes                                                  | 31 |

| 5.1 | 2T Voltage Reference Parameters values                               | 38 |

| 5.2 | TC and Power Consumption comparison with Temperature                 | 40 |

| 5.3 | Line Regulation and Power Consumption Comparison with Supply voltage | 42 |

| 5.4 | Process Corner results                                               | 43 |

| 5.5 | Process Corner results @ VDD = 1V                                    | 48 |

| 5.6 | Process Corner results @ VDD = 1.5V                                  | 49 |

| 5.7 | Process Corner results @ VDD = 2V                                    | 50 |

| 6.1 | 2T BGR Parameters values                                             | 61 |

| 6.2 | Transistor Sizes of the CSRO                                         | 66 |

| 7.1 | Process Corner performance results                                   | 79 |

| 8.1 | Results Comparison                                                   | 83 |

xvi LIST OF TABLES

# **Abbreviations and Symbols**

CMOS Complementary Metal-Oxide Semiconductor

CSRO Current Starved Ring Oscillator

CTAT Complementary to Absolute Temperature

IC Integrated CircuitIoT Internet of ThingsLVT Low Threshold Voltage

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

PL Perception Layer

PMU Power Management Unit PSRR Power Supply Rejection Ratio

PTAT Proportional to Absoulute Temperature PVT Process, Voltage and Temperature

RF Radio Frequency

RTC Real-Time Clock

SQW Square-Wave Output

T2T Thing 2 Thing

TC Temperature Coefficient

ULP Ultra Low power

VLSI Very Large Scale Integration

XOs Crystal Oscillator

WSN Wireless Sensor Networks

# **Chapter 1**

### Introduction

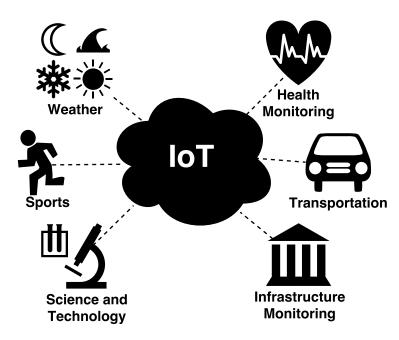

The **Internet of Things** is a concept that theorizes that, eventually, every single component in our work, at home and in the city will be interconnected through the Internet. This is a futuristic idea that is currently in development to be further researched and expanded. There are a number of different applications visualized for this technology and they all take into consideration the advantage of having a real-time monitoring and understanding of the surrounding environment, as seen in figure 1.1. [1].

Figure 1.1: Some applications of the IoT

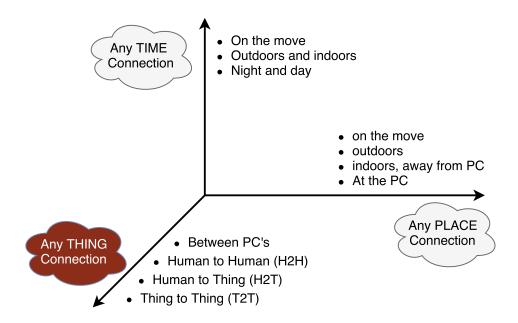

This interface creates a new dimension in the realm of digital information, allowing for the cooperated work between "things" on behalf of humans [2]. Thing to Thing (T2T) interaction is the main objective proposed for the IoT, establishing a new paradigm in our understanding of information, data analysis and transmission, as seen in figure 1.2.

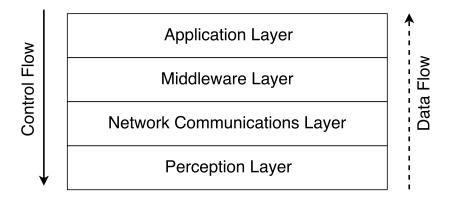

The IoT architecture is composed of 4 main layers [3, 4]. These are described as follows:

Figure 1.2: Conceiving a new dimension [2]

- Perception/Sensing Layer first and most important layer one of the IoT network. The

Perception Layer is integrated with existing hardware and controlling sensors that acquire

information from the environment.

- Network Communications Layer responsible for the transmission of data from the PL and the reception of control information. It provides basic networking interface support for wireless data transmission.

- **Middleware Layer** provides services according to the user's needs and its main focus is to deliver an information processing system that takes actions in an autonomous way taking as reference received data.

- **Application Layer** implements the real-life functionality of IoT operations according to end user requirements and other applications.

Data flows from the sensors in the **perception layer** through the **network layer**. The network processes and transfers the information through a wireless medium. The **middleware** processes the massive amount of incoming data and decides what is useful for the **application layer**. High level application uses this information and makes it available for further implementation according to the **final demands**. The control of the different layers arrives from the end user towards the lower layers [3, 4].

We can begin to visualize the IoT in our everyday lives through *smartphones*, *smart TV's* and other equipment connected to the Internet. These devices are a starting point, an initial concept of

Figure 1.3: IoT Architecture

the IoT since it allows the user to be connected to the Internet anywhere. The building blocks of the IoT are these devices that are known as *smart objects*. Those apparatus are **heterogeneous** and the application layer of IoT allows for their inclusion in a **network of intelligent data**, regardless of their intrinsic characteristics [1].

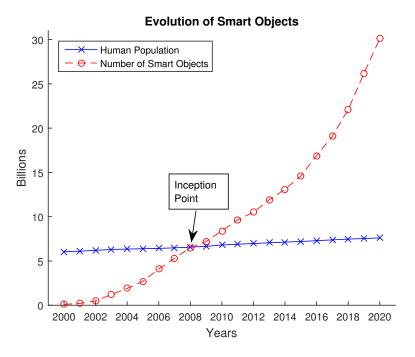

The number of *smart objects* is growing exponentially and it is expected to reach around 20 to 30 billion devices interconnected in the entire world by 2020, according to predictions from different companies [5]. This is seen in figure 1.4, where the inception point represents the moment where the number of smart objects surpassed the human population.

Figure 1.4: Ratio of Smart Objects vs Human Population

#### 1.1 Wireless Sensor Networks

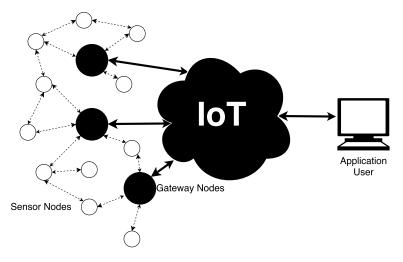

The rapid growth of the IoT caused an exponential increase on the number of interconnected devices. Because of the surge of wireless communication channels, a network is being developed to answer to these specifications known as **Wireless Sensor Networks** (WSN). It is composed of **sensor nodes** and **gateway nodes** (or master nodes) that acquire the data from the connected devices and sends it to the IoT data cloud according to specific application user demands [6].

The IoT data cloud can be specified as a space where the data acquired from the sensors is stored. It can be done in a local register base or through remote servers [2].

Figure 1.5: Concept of an WSN IoT

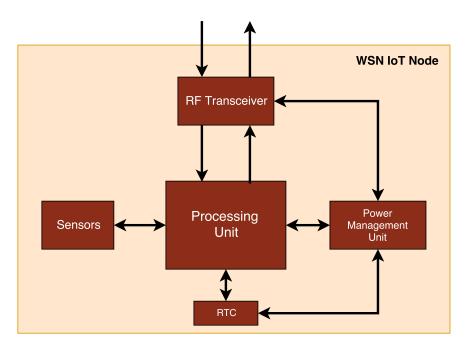

A typical **WSN IoT node** has a processing unit, one or multiple sensors, a transceiver, a RTC and a power management unit, as seen in figure 1.6 [7].

- Processing Unit is core unit of a sensor, processing the data acquired from the sensor and

received from the radiofrequency transceiver. It also manages the general operation of the

node.

- **RF Transceiver** is responsible for sending and receiving data from the outside environment. It is the component that has a higher power consumption, due to the inherent characteristics of a wireless transfer communication.

- Power Management Unit targets the administration of the total power supply of the unit, allowing for different states of consumption according to current state of processes in the node. It can have an internal power supply (e.g. battery) or an external source. For a WSN node, it is typical that internal batteries are used.

- Sensors are the main component of the WSN node. It acquires external data that is sent to the processing unit for internal handling and, consequently, through the RF transceiver to the IoT data cloud.

• RTC is the component of an IoT node that is extremely important for its correct behavior because it is responsible for the management, maintenance and verification of the time inside the device, allowing the node to synchronously communicate with the other nodes. For that, this component has a permanent working status, meaning that it will always keep on running regardless if the rest of the circuitry is engaged or not. It is also responsible for the interruptions that will tell the main system that it needs to "wake up" and perform some tasks.

Figure 1.6: WSN IoT node main components

### 1.2 WSN Node Power Consumption

One of the main requirements of the current IoT implementation is an ultra-low power (ULP) consumption. It has an important impact on the design and development of the components in each node. The current peer-to-peer communication algorithms does not take into account power consumption restrictions of the devices, often leading to an early discharge of the main batteries and, consequently, to its early replacement. Since current software developments have been stagnating due to security issues with the implementation of an IoT network, more focus is being made regarding the hardware components of such IoT networks [4].

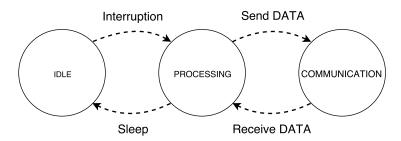

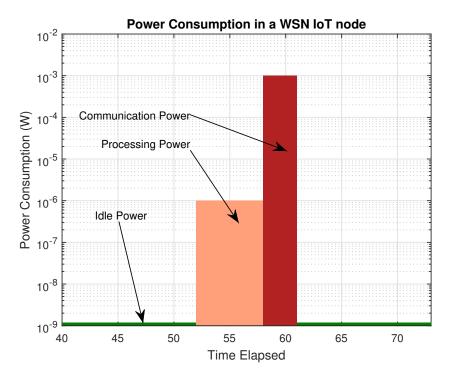

The operation in a WSN node is composed of three states with different power consumption, as seen in figure 1.7:

• **Idle mode** - representing the lowest power consumption, it occupies most of the time and is the main factor in the power budget.

Figure 1.7: State Machine WSN node

- Processing mode happens when the processor is activated, in this case, in order to prepare

data to be transferred. It has a higher power consumption than idle mode, showing how

important the RTC interrupts are in the power budget scenario.

- **Communication mode** It happens on a short period of time and it is the highest power consumer in the operation.

The respective power consumption of these modes is demonstrated in figure 1.8. The node spends most of its time in idle mode, processing the data in a fixed interval of time and communicating in the most efficient way (i.e., in the least amount of time possible). This figure only shows the comparison between the different power consumption of the modes, since the processing mode and communication mode might only be active every second or every 5 minutes, according to different implementations [8].

Figure 1.8: Power consumption in a typical IoT node [9]

1.3 Motivation 7

The fact that the RTC component has a permanent working status means that the total power consumption of the system largely depends on the power consumption of this device. By lowering the necessary power for the correct operation of this device, total power consumption of the IoT node will also be reduced. This assumption is a practical problem to be solved in the IoT research domain, since most of the IoT components are meant to be self-reliable and require them to perform through long time periods (years).

#### 1.3 Motivation

The Internet of Things is growing at an exponential rate. This new perception of reality is being researched even further nowadays because society is starting to develop an interest on these technologies. Market potential is increasing even further, since the foreseeable implementations are diverse and still to be detected. The future applications for the IoT are enthusiastic and they will increase the overall quality of life of the citizens of the world.

Developing a component that is crucial for the sustainability of this implementation is the task that truly motivates the intended work for this project. Designing the full-custom circuitry and physical layout of a Real Time Clock becomes a job that has a lot of minor details that need considerable attention. These technicalities truly tone the developers skill and knowledge of different design principles.

Besides, developing the solution using **ultra low power** CMOS techniques will put emphasis on different technological procedures. Producing devices that are heavily dependent on PVT variations, operational frequency and power consumption define this new task, that needs a stable approach to all these diverse figure of merits, even though they are all interconnected. The study and understanding of these different approaches allows for a more complex in depth grasp of this recent intriguing proceedings.

#### 1.4 Problem Statement

The main purpose of this dissertation is to develop an analysis of the performance of an RTC component when applied to IoT nodes. As said before in the scope of this work, it is expected to design, implement and validate a Real-Time Clock circuit for use in an Internet of Things node, with power consumption being the major performance parameter to leverage in order to fit IoT requirements. Main expected features should also be added for the standard use of this component.

The main objectives of this dissertation are

- Design of an RTC to be used in an Internet of Things context;

- Ultra Low Power Consumption, in the order of sub- $\mu$ W;

- CSRO with an output frequency of 32.768 kHz, with low PVT variation;

- Layout development with a focus on minimum area, sub-mm<sup>2</sup>;

- Implement all the expected features in a typical RTC (time counting, interruptions, alarms...).

#### 1.5 Document Outline

This document is constituted by the following chapters, besides the Introduction, as follows:

#### • Chapter 2 - Subthreshold Operation Regime

Subthreshold operation regime is researched and analyzed. The main factors surrounding its behaviour are described and related to the work.

#### • Chapter 3 - Real Time Clock Integrated Circuits

An extensive research will be performed regarding the current RTC ICs that the market offers. Through that, it will be possible to understand the different functional blocks that it requires to operate as well as different extra funcionalities that can be implemented. Besides, different oscillator implementations are studied and analyzed.

#### • Chapter 4 - Proposed Architecture

The proposed architecture for the implementation of the work is shown. Both analog and digital design blocks are explained.

#### • Chapter 5 - Power Management Unit

The Power Management Unit of the analog block is described and analyzed. Voltage references and regulated charge pump for this block are studied and the results from the layout extraction are shown.

#### • Chapter 6 - Oscillator Design

The structure of the chosen oscillator topology is analyzed and shown. Besides, PVT compensation is explained and the results from the layout extraction are studied.

#### • Chapter 7 - Integration

Power Management Unit and the Oscillator block are connected and the layout parasitic components are extracted. The results from this simulation are shown and analyzed.

#### • Chapter 8 - Conclusions and Future Work

Some final considerations are done and the future work is presented.

# Chapter 2

# **Subthreshold Operation Regime**

Ultra low power micro systems are highly in demand in the IoT market. These micro systems target wireless nodes and battery-powered applications. For such systems, power consumption reduction becomes critical due to battery lifetime extension.

Complementary Metal-Oxide Semiconductor (CMOS) is still the main Very Large Scale Integration (VLSI) technology used in the design of current circuits due to its power characteristics. It consumes power when changing state and not in a steady state. Traditionally, CMOS technologies operate with a strongly inverted channel, meaning that the supply voltage  $V_{DD}$  is above threshold voltage,  $V_T$  [10].

Lowering the supply voltage is the main path in order to reduce the power budget of an IoT node. However, this is not the only approach to decrease power consumption. In this dissertation, some of the transistors will be operating in the subthreshold (or weak inversion) region, since it also allows for low current values. This operation region is achieved when transistors are operating below or near  $V_T$ . Although the subthreshold regime is familiar in the field of circuit design since the 1970s, only now due to the rising popularity of ultra low power systems it is gaining more attention [11, 12].

This weak inversion region is considered a leak current in a strong inversion circuits. Since  $V_{GS} < V_{TH}$ , it is assumed that the device is turned off. This is not true due to the subthreshold current flowing even when the device is below threshold voltage. Total power consumption of the device is still dependent of this leakage, the **subthreshold current**. For ultra low power devices, this current proves to be an effective operation region for the intended objectives.

#### 2.1 CMOS Power Consumption

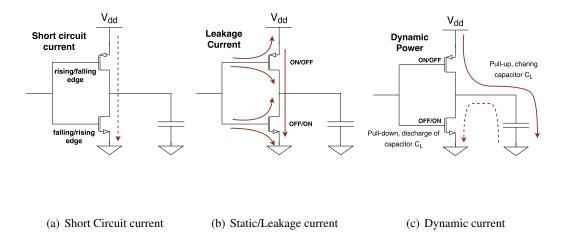

As seen in figure 2.1, in digital circuit CMOS design, power consumption is divided into three sections as described as follows [10]:

$$P_{total} = P_{dynamic} + P_{static} + P_{shortcircuit}$$

(2.1)

Figure 2.1: The power components of a CMOS digital circuit [10]

#### 2.1.1 Dynamic Power

Dynamic power, also known as switching power, comes from the output changing state. It is used to charge the load capacitance through the pMOS transistor with the high voltage level, usually  $V_{DD}$ . When the output changes to 0, it does not draw charge from the supply. However, the energy stored is dissipated through the nMOS pull-down transistor. The dynamic power consumption is described as [13]:

$$P_{dynamic} = \alpha_{0 \to 1} \cdot f_{clk} \cdot C_L \cdot V_{DD}^2 \tag{2.2}$$

Since most switching does not occur in the  $f_{clk}$  but at smaller speeds,  $\alpha_{0\rightarrow 1}$  describes the activity factor,  $0 < \alpha_{0\rightarrow 1} < 1$  (exceptions made regarding clock buffers).  $C_L$  stands for average load capacitance.

As seen in (2), dynamic power consumption is proportional to the clock frequency and the supply voltage squared. It is independent of the rise and fall times of the input gate signal [13].

#### 2.1.2 Short Circuit Current

Short circuit power dissipation happens when both nMOS and pMOS devices are on, creating a direct path between  $V_{DD}$  and GND. This is significant when rise/fall time in the input gate is larger than the rise/fall time in the output since the short-circuit path will be opened for a longer period of time. Short circuit power dissipation is usually insignificant in the desing of a low power logic circuit [13].

#### 2.1.3 Static Power Dissipation

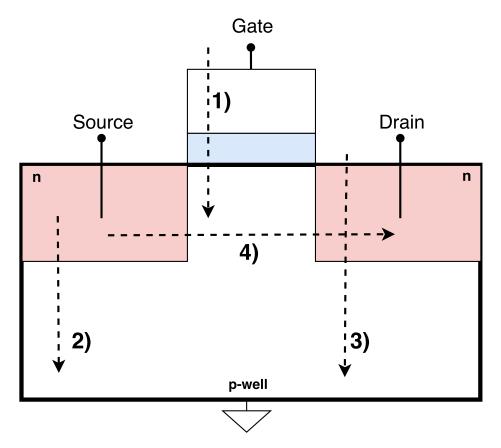

Static/Leakage power dissipation occurs even when the device is in a stable logic state. This leakage is composed of 4 different types of currents, as shown in figure 2.2, that occur for different reasons as follows [10]:

Figure 2.2: Components of Leakage Power [10]. The **gate-oxide leakage current** (1) flows from the gate supply towards the bulk through the oxide. **Reverse-biased diode leakage current** (2) flows from drain and source towards the bulk. **Gate induced drain leakage current** (3) flows from the drain interface with the oxide to the bulk. **Subthreshold leakage current** (4) flows from the source towards the drain when the device is "turned off", i.e., when  $V_{GS} < V_T$

• Gate-oxide tunneling is a current  $I_{ox}$  that is flowing through the oxide layer in the gate. This layer is getting thinner with current developing technologies and can surpass other leakage currents as a dominant leakage mechanism in the future. As voltage supply is lowered, this tunneling effect decreases faster than subthreshold current, making it imperceptible.

- Reverse-biased diode leakage to drain and source to the bulk is composed of two components: electron-hole pair generation inside the depletion region of reverse-biased pn junction and the minority carrier diffusion and drift near the depletion region [14]. Process technologies create devices in a way that this leakage is small compared to subthreshold leakage [12].

- Gate induced drain leakage (GIDL) is due to the high electric field near the interface between the gate oxide and drain, making the silicon surface act like a p region. This current flows from the surface of the drain into the body of the transistor. For subthreshold

operation, low  $V_{DS}$  causes a reduction in the value of this leakage, making it negligible compared to subthreshold current [12].

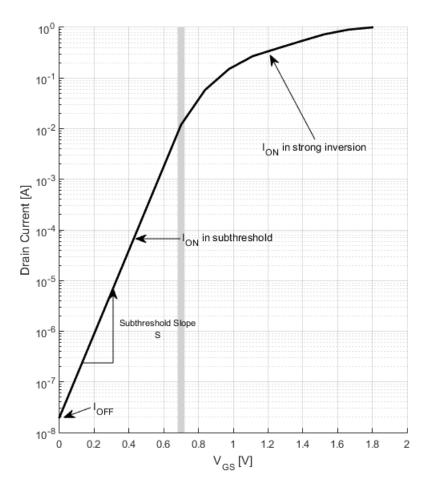

• Subthreshold leakage Subthreshold operation regime occurs when  $V_{GS}$  is below threshold voltage. This region is also called *weak inversion* region. As seen in figure 2.3, an approximation is made regarding a relationship of drain current and gate to source voltage, with  $V_{DD}$  = 1.8V in 0.18  $\mu$ m technology. In subthreshold,  $I_D$  varies exponentially with  $V_{GS}$ . Threshold voltage  $V_T$  is defined as the point where  $I_D$  starts to deviate from its original trajectory. The *subthreshold slope* of a transistor is defined as [12]:

$$S = nV_{th} \ln 10 \tag{2.3}$$

The ideal value of S in room temperature, i.e., T = 300K, is 60mV/dec and it occurs at the limit when n = 1. This parameter represents the effectiveness of the transistor in its ability to be turned off when  $V_{GS}$  is decreased below threshold voltage [14].

Figure 2.3: MOSFET Drain Current vs Gate to Source Voltage[12]

2.2 MOS EKV Model 13

Another effect to consider in subthreshold leakage is the DIBL (Drain-induced barrier lowering) effect. It can affect the channel charge like  $V_G$ , prominent in short-channel devices [14]. In these devices, the proximity of the source and drain makes it so that drain voltage influences the depletion region beneath the channel. It is characterized as the reduction of  $V_{TH}$  due to high drain voltage [10].

These leakages tend to be negligible in comparison to subthreshold current. One case where this is not accurate is in a circuit operating at lower temperature. Since subthreshold current is exponentially related to temperature, gate leakage may become relevant again. Otherwise, for weak inversion operation, only subthreshold current is considered [12].

#### 2.2 MOS EKV Model

The EKV analytical model for MOS transistors was first proposed in [15]. In [12, 16], the compact equation for all operation region current is described as:

$$I_D = I_{D0}e^{\frac{V_G}{nU_T}} \left( e^{-\frac{V_S}{U_T}} - e^{-\frac{V_D}{U_T}} \right)$$

(2.4)

where

$$I_{D0} = I_{spec} e^{-\frac{V_{T0}}{nU_T}} \tag{2.5}$$

is the residual drain current in saturation for  $V_G = V_S = 0$  or channel "leakage" current of CMOS digital circuits and  $I_{spec}$  is the *specific current* of the transistor, given as:

$$I_{spec} = 2n\beta V_T^2 \tag{2.6}$$

and  $\beta$  is the transfer parameter of the transistor:

$$\beta = \mu C_{OX} \frac{W}{L} \tag{2.7}$$

In these equations, these parameters are described as:

- $V_T$  is the threshold voltage;

- n is the subthreshold slope factor which depends on process parameters (capacitive divider effect formed by  $C_{OX}$  and  $C_d$ ) as well as biasing conditions, and is usually between 1 and 1,5 [14];

- $U_T$  is the *thermodynamic voltage* described as:

$$U_T = \frac{kT}{q} \tag{2.8}$$

where k is the Boltzmann constant and q is the elementary charge. For T = 300 (27°C),  $U_T$  is 25.8 mV:

- $C_{OX}$  is the gate oxide capacitance in *farads*;

- $\mu$  is the carrier mobility;

As seen in (2.3), drain current is exponentially proportional to gate, threshold, source and drain voltage. This means that lowering power supply will subsequently reduce power consumption of the device.

The exponential characteristics in the subthreshold EKV model makes it vulnerable to Process, Voltage and Temperature (PVT) variations [12] [17]. There are differences between analog and digital operations. For analog, it is important to have a better control over PVT, since the variations might undermine the overall operation.

#### 2.2.1 Process

Process variations have an impact mainly in the model parameters  $V_{T0}$ , n and  $\beta$ , since transistors with equal structures in the layout do not have equal properties. This is seen in equation (2.3) and can be derived from random dopant fluctuations and small variations in the parameters of physical characteristics [18, 12].

#### 2.2.2 Voltage

In ULP systems, voltage differences are due to variations in the external supply. Since  $I_{on}$  is orders of magnitude lower than in strong inversion operation regime, voltage drops across the on-chip supply distribution network are imperceptible. In battery powered systems, voltage supply is relatively constant. For batteryless devices, these suffer from much more pronounced power supply variations which are handled through voltage regulation circuits [18].

This means that, for an ULP system, the voltage regulation circuit has an important impact in the management of the power supply, since subthreshold devices have an exponential sensitivity to voltage variations.

#### 2.2.3 Temperature

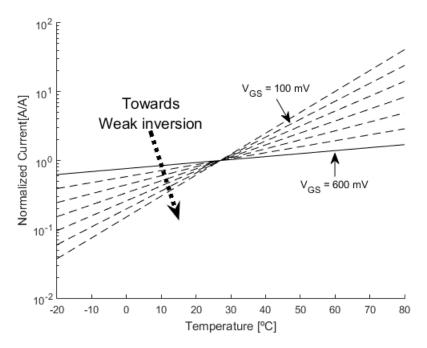

As seen in equations (2.1), (2.2) and (2.5), absolute temperature has an exponential impact on the drain current. In [19], it is shown that, due to its positive temperature dependence, subthreshold  $I_{ON}$  current increases exponentially with temperature while  $\frac{I_{ON}}{I_{OFF}}$  ratio degrades due to the increase in leakage currents. Tolerable subthreshold circuit operation is placed at 25-75°C.

In figure 2.4, it is shown that in subthreshold operation, variations in temperature parameter have a greater impact the closer circuit operation reaches weak inversion. As operation decreases  $V_{GS}$ , temperature variation increases drain current very rapidly[14].

2.2 MOS EKV Model

Figure 2.4: Bias current dependence on temperature variations. In this figure, the bias current is normalized to the nominal bias current at  $T = 27^{\circ}C$

#### 2.2.4 Delay and Operational Frequency

This ultra low power consumption comes at a cost where lower drain current means that it will take longer to charge the output of a device. This latency will therefore affect the maximum operational frequency of a device.

In weak inversion operation, propagation delay for an inverter circuit with an output capacitance  $C_G$  is described as [12]:

$$t_d = \frac{KC_G V_{DD}}{I_{Dsub}} \tag{2.9}$$

where K is a delay fitting parameter. As seen in equation (2.2), since drain current has an exponential behavior this means that if it decreases, propagation delay will increase rapidly. With an increase of this delay, operational frequency will decrease consequently. Subthreshold devices are applied in situations where the frequency of the device is not an important factor.

Some situations are described in [8] where a city can check its waste containers levels to create a route and perform a service in a more efficient way [20] and in [21], where the human body is the target for health monitoring especially in cases like glucose level sensing and electrocardiogram monitoring. Some sensors only need to capture data in relatively great intervals of time (every second or every 5 minutes), allowing for a lower frequency operation of the device. This proves to be an effective solution to these situations, since lowering power consumption is the main objective of such implementations.

Observing subthreshold transistor behaviour, this "leakage current" can be perceived as a valid

operation region for ultra low power circuits. The main considerations to be taken are temperature dependence and the high propagation delays that are characteristic of the weak inversion region.

Since the main objective of the implementation of a WSN IoT node is to lower power consumption, operational frequency is a parameter that can be depreciated. PVT variation must be taken into consideration for a more balanced subthreshold circuit operation.

### **Chapter 3**

## **Real Time Clock Integrated Circuits**

The Real Time Clock (RTC) ICs all have the same functionality, *i.e.* they will keep track of time since a certain point that can be programmed and, if necessary, they can perform interrupts or output different signals. Most of those Integrated Circuits have the same core functional blocks and some of them (that are more expensive and complex) offer extra functionality. A research has been made regarding the Integrated Circuits (ICs) that are available in the actual market.

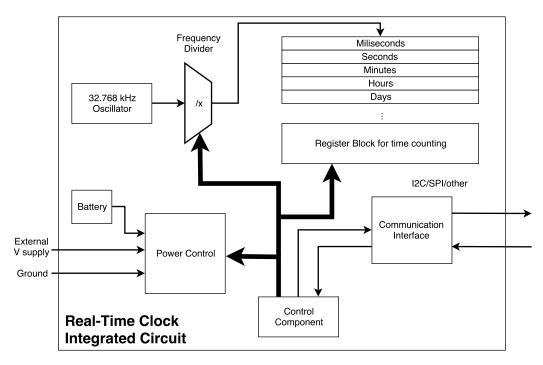

The main core functional blocks that are shared through all of the researched integrated circuits in the market are as shown in figure 3.1.

Figure 3.1: RTC IC main core functional blocks

• **Power Control** - This power control block will define where the supply power will come from. It can either originate from an external device, internal or external battery. This

is important because if the proposed RTC architecture has a low area size and an internal battery, this power supply will need to obey to a certain power characteristic and size limit

- A Memory where it saves the elapsed time since boot The internal memory is divided in different registers that keep track of time in different time magnitudes, *i.e.*, seconds, minutes, hours, days, weeks, months, years and so on. Since most of the available ICs have leap year calculation integrated, it will automatically scale the registers so some of them can be reset when needed, accurately.

- **Communication Interface** This communication interface is necessary so that external devices have the possibility to access the data inside the above mentioned memory. It can be implemented using different protocols (I2C, SPI, 3-wire topology...) and is selected in advance by the manufacturer.

- IC component control This block is the main control of the integrated circuit. It analyses the signals that are being input by the user (trough the communication interface) and selects the data that will be output. It can also allow for different functionalities to be activated in some ICs (*alarms*, *interrupts*, *external signal generator*, *timer...*). It is also the functional block that keeps the time registers in the main memory updated. The time scale used for the updates is defined by the next component.

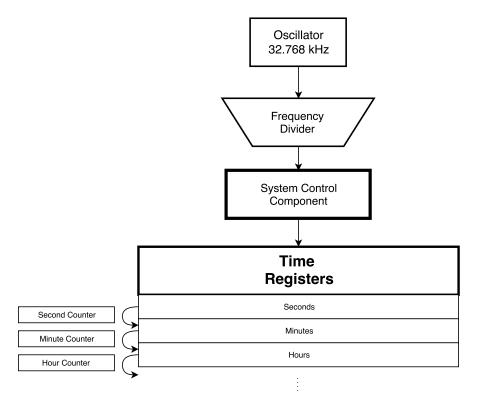

- Oscillator frequency divider/scaler This block will simply select the frequency that the control component will base its calculation. As it performs with higher frequency, the time resolution will drop and the registers will keep track of time using a minor time magnitude. Some integrated circuits also allow for time resolution in the millisecond scale, allowing for more precise and accurate time keeping. In figure 3.2, is shown a brief resumed main interaction between the oscillator and the time registers. In this implementation, the prescaler (divider) defines a ticking 1 Hz clock that updates the second timer. Another counter (second counter) is being updated with the value from the second register and when it hits 60, it increases the minutes register and resets the value inside the second register to 0 and so on.

- A RAM memory useful for intermediate calculations and simple arithmetic operations

when operating through memory addresses and timer registers. In most cases, this RAM is

limited and the number of bytes that it allows reaches a maximum of 512 bytes in the best

option that the market allows.

Figure 3.2: Time registers functionality

For some cases, the integrated circuits available in the market can also allow for an output (Square-Wave Output (SQW) or an analog sinusoidal oscillation) whose frequency can be selected through the prescaler or an internal multiplexer component. This scaling is done by the SQW prescaler register that has a defined number of bits to select different operation frequency. The signal output functionality will also need more power to operate, so in most cases, in order to lower the power consumption of the integrated circuit component, this will be turned off. In table 3.1, we can see, for the specific RV-1805-C3 RTC IC case, some frequencies that are enabled according to different SQW bit selections.

Additionally, some integrated circuits also allow for extra functionalities. Some of these utilities are only implemented if the user wants them to be activated. One has already been shown, the clock signal output. This one in specific consumes more power and should only be activated if needed. Aside from that, Real-Time Clock integrated circuits can also have:

- Calendar functionality that saves the actual date in a specific register. For this to work properly, the component should also have a leap-year calculation logic circuit that analyzes the year, month and day registers of the internal memory to process the days that the current year has.

- 12h/24h mode selection allowing for flexibility regarding different global time measurements.

| SC | <b>SQW</b> bit Selector |   | Functionality | SC | SQW bit Selector |   |   | ctor | Functionality |   |                    |

|----|-------------------------|---|---------------|----|------------------|---|---|------|---------------|---|--------------------|

| 0  | 0                       | 0 | 0             | 0  | 1 century        | 0 | 1 | 1    | 0             | 1 | 4 Hz               |

| 0  | 0                       | 0 | 0             | 1  | 32.768 kHz       | 0 | 1 | 1    | 1             | 0 | 2 Hz               |

| 0  | 0                       | 0 | 1             | 0  | 8.192 kHz        | 0 | 1 | 1    | 1             | 1 | 1 Hz               |

| 0  | 0                       | 0 | 1             | 1  | 4.096 kHz        | 1 | 0 | 0    | 0             | 0 | 1/2 Hz             |

| 0  | 0                       | 1 | 0             | 0  | 2.048 kHz        | 1 | 0 | 0    | 0             | 1 | 1/4 Hz             |

| 0  | 0                       | 1 | 0             | 1  | 1.024 kHz        | 1 | 0 | 0    | 1             | 0 | 1/8 Hz             |

| 0  | 0                       | 1 | 1             | 0  | 512 Hz -default  | 1 | 0 | 0    | 1             | 1 | 1/16 Hz            |

| 0  | 0                       | 1 | 1             | 1  | 256 Hz           | 1 | 0 | 1    | 0             | 0 | 1/32 Hz            |

| 0  | 1                       | 0 | 0             | 0  | 128 Hz           | 1 | 0 | 1    | 0             | 1 | 1/60 Hz (1 minute) |

| 0  | 1                       | 0 | 0             | 1  | 64 Hz            | 1 | 0 | 1    | 1             | 0 | 16.384 kHz         |

| 0  | 1                       | 0 | 1             | 0  | 32 Hz            | 1 | 0 | 1    | 1             | 1 | 100 Hz             |

| 0  | 1                       | 0 | 1             | 1  | 16 Hz            | 1 | 1 | 0    | 0             | 0 | 1 hour             |

| 0  | 1                       | 1 | 0             | 0  | 8 Hz             | 1 | 1 | 0    | 0             | 1 | 1 dav              |

Table 3.1: SQW functionalities from the RV-1805-C3 RTC IC

- **Interruptions** that activates a set output if a specific time has elapsed, allowing for low power consumption since most of the time, the component is in timekeeping mode. Some components have more than one interrupt output.

- Alarms that activate a set output if a specific date and hour has been reached.

- Integrated XO Crystal to allow for a more independent functionality.

In the next subsegment, an extensive research has been made regarding the Real-Time Clock integrated circuits that the current market has and the different functionalities that each one possesses.

### 3.1 Review of the RTC IC Market

In this subsection, an analysis will be performed regarding the main Real-Time Clock integrated circuits that the current market has available. A search has been made focusing on different microelectronics companies. In the scope of this work, only components that have low power or ultra low power consumption will appear in this examination.

A temperature range analysis will also be performed because ultra low power operation region is highly sensitive on absolute temperature. Voltage supply, current consumption and SQW/analog output will also be a figure of merit because the power consumption metrics are heavily influenced by these factors. Since this integrated circuits come in different packages, they only serve as a medium to compare what the market has to offer considering the projected work has different size objectives. This search is important to understand the main functional blocks and different functionalities that are expected from a Real-Time Clock component.

Voltage supply  $(V_{DD})$  is represented as the minimum to maximum range while the communication protocol (I2C,SPI or 3-wire) is activated to make sure that there are no failures during this

operation. This voltage supply can be even lower when communication is not happening. Current consumption parameter shows the value that the component expends while there is no clock output and the communication protocol is disabled since, otherwise, the current expenditure would be greatly increased while the module is transferring data (around  $\mu$ A range).

In table 3.2, an analysis is performed regarding the main subthreshold Real-Time Clock integrated circuits that each manufacturer has for production and sale [22, 23, 24, 25, 26, 27].

Table 3.2: RTC IC in the current market

| Component               | Supply<br>Voltage (V) | Current<br>Consumption (nA) | Communication<br>Protocol | RAM Bytes | SQW Output |  |  |  |  |

|-------------------------|-----------------------|-----------------------------|---------------------------|-----------|------------|--|--|--|--|

|                         |                       | Maxim Integ                 | rated [22]                |           |            |  |  |  |  |

| DS1339A                 | 1.8 to 5.5            | 300                         | I2C                       | None      | Yes        |  |  |  |  |

| DS1308                  | 1.8 / 3 / 3.3         | 250                         | I2C                       | 56        | Yes        |  |  |  |  |

| DS1347                  | 2 to 5.5              | 350                         | SPI                       | 31        | Yes        |  |  |  |  |

| DS1344                  | 1.8 / 3 / 5.5         | 250                         | 3-Wire                    | 96        | Yes        |  |  |  |  |

| DS1342                  | 1.8 / 5               | 220                         | I2C                       | None      | Yes        |  |  |  |  |

| DS1341                  | 1.8 / 5               | 400                         | I2C                       | None      | Yes        |  |  |  |  |

| DS1339                  | 1.8 to 5.5            | 400                         | I2C                       | None      | Yes        |  |  |  |  |

| STMicroelectronics [23] |                       |                             |                           |           |            |  |  |  |  |

| M41T62                  | 1.3 to 4.4            | 350                         | I2C                       | None      | Yes        |  |  |  |  |

| M41T65                  | 1.3 to 4.4            | 350                         | I2C                       | None      | No         |  |  |  |  |

| M41T93                  | 2.38 to 5.5           | 365                         | SPI                       | 12        | Yes        |  |  |  |  |

| M41T82                  | 2.38 to 5.5           | 365                         | I2C                       | 12        | No         |  |  |  |  |

| M41T56                  | 4.5 to 5.5            | 450                         | I2C                       | 56        | No         |  |  |  |  |

|                         |                       | EM Microelect               | tronics [24]              | ·         |            |  |  |  |  |

| V3020                   | 1.2 to 5.5            | 390                         | 1 bit serial              | None      | N/A        |  |  |  |  |

| V3021                   | 2 to 5.5              | 800                         | 1 bit serial              | None      | N/A        |  |  |  |  |

| A3024                   | 2 to 5.5              | 1200                        | 8 bit parallel            | 16        | N/A        |  |  |  |  |

| EM3027                  | 1.3 to 5.5            | 600                         | I2C & SPI                 | 8         | N/A        |  |  |  |  |

|                         |                       | Micro Crystal Sw            | itzerland [25]            |           |            |  |  |  |  |

| RV-8564-C3              | 1.8 to 5.5            | 250                         | I2C                       | 512       | No         |  |  |  |  |

| RV-2123-C2              | 1.6 to 5.5            | 130                         | SPI                       | 512       | No         |  |  |  |  |

| RV-8803-C7              | 1.5 to 5.5            | 240                         | I2C                       | 512       | No         |  |  |  |  |

| RV-8523-C3              | 1.6 to 5.5            | 130                         | I2C                       | 512       | No         |  |  |  |  |

| RV-2251-C3              | 1.8 to 5.5            | 270                         | I2C                       | 512       | Yes        |  |  |  |  |

| RV-1805-C3              | 1.5 to 3.6            | 60                          | I2C                       | 512       | No         |  |  |  |  |

| RV-8063-C7              | 1.8 to 5.5            | 180                         | 3-Wire                    | 512       | Yes        |  |  |  |  |

|                         |                       | NXP Semicond                | luctors [26]              |           |            |  |  |  |  |

| PCF2123                 | 1.8 to 5.5            | 100                         | SPI                       | None      | Yes        |  |  |  |  |

| PCF8523                 | 1.6 to 5.5            | 150                         | I2C                       | None      | Yes        |  |  |  |  |

| PCF8564A                | 1.8 to 5.5            | 140                         | I2C                       | None      | Yes        |  |  |  |  |

| PCF85063A               | 1.8 to 5.5            | 122                         | I2C                       | None      | Yes        |  |  |  |  |

|                         |                       | Ambiq Mic                   | ero [27]                  |           |            |  |  |  |  |

| AM0805                  | 1.7 to 3.6            | 14                          | I2C                       | 256       | Yes        |  |  |  |  |

| AM0815                  | 1.7 to 3.6            | 14                          | SPI                       | 256       | Yes        |  |  |  |  |

As shown in table 3.2, current consumption on the mentioned integrated circuits stands inside the nA magnitude. Besides what is shown, temperature range is almost always the same (-40°C to 80°C), showing that the manufacturing process takes into account this parameter in order to develop a standard temperature operation region. This is relevant due to the great fluctuation in subthreshold transistors intrinsic operation properties caused by temperature variance.

Though it must be taken into account that the power consumption shown in table 3.2 is achieved for some cases where the oscillator component is an external element, such as an XO. For example, in the AM0805 component, the value of 14 nA is obtained while using an internal RC oscillator, whose operating frequency is only 128 Hz.

Besides, most IC's use the same known **communication protocols** (I2C, SPI, SPI 3-wire or serial). RAM bytes are more relative, since some circuits do not have any bytes in the user RAM. Exception made for Micro Crystal Switzerland, that implements a memory register of 512 bytes, significantly higher than the remaining devices.

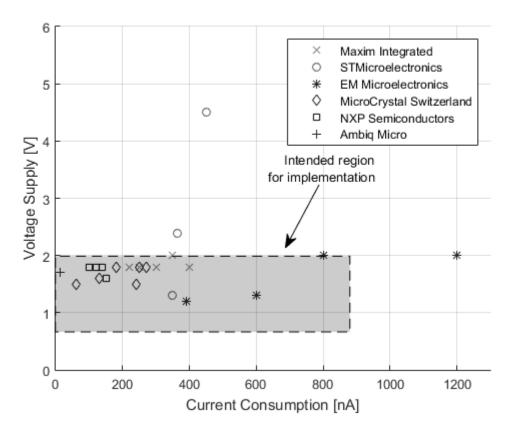

In figure 3.3, a comparison has been made taking into account minimum voltage supply and respective current consumption of the different devices researched in table 3.2. There is a region where researched market IC's are more concentrated. For the pretended circuit development, this is the intended region for implementation. The minimum supply voltage should be around 0.7-2V and current consumption should be lower than 850 nA.

Figure 3.3: Minimum Voltage Supply vs Current Consumption in RTC ICs from table 3.2

3.2 Oscillators

### 3.2 Oscillators

Since most of the time the integrated circuit will be in timekeeping mode, most of its operation will be performed by the oscillator component. **Frequency change in ppm** (*parts per million*) is an important figure of merit since it describes how the oscillator deviates from the nominal value.

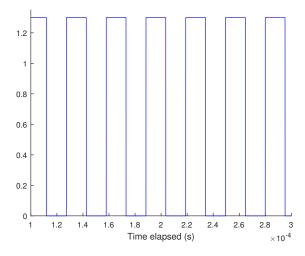

For the intended oscillator, the operational frequency should be **32.768 kHz**. This value is a power of 2 (2<sup>15</sup>), and so the divider component can manage the intended frequency by manipulating only a 4 bit register. This lower frequency also allows for a lower power consumption of the oscillator component, further improving the expected results. This value is chosen for comparison reasons XO types of implemented RTC since this is the most used component in the oscillator industry due to its compromise between performance and cost [28].

### 3.2.1 Crystal Oscillators

Crystal oscillators (X0s) are exceptional frequency generators with low parameter variations in respect to supply voltage, process and temperature [29]. Another advantage is a low jitter noise compared to remaining oscillator architectures [30].

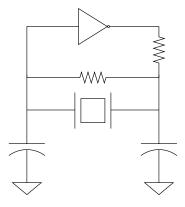

Figure 3.4: Conventional XO circuit [9]

As seen in figure 3.4, an inverter circuit in closed-loop amplifies the input noise to start the oscillation. Simultaneously, it provides a 180° phase shift and generates lost energy each period to maintain oscillation. The resistor forms a low-pass filter with the capacitor to avoid high overtone frequency oscillation. Also, a resistor is put in series at the output to control drive level and create a sinusoidal wave. This implementation, at low supply voltages, can not sustain oscillation due to loss of drive strength. It is a dependency since smaller oscillation leads to a smaller input signal.

Figure 3.5: Widely used XO for low power circuits [9]

In figure 3.5, this is corrected using a circuit that controls the drive current through the source in the current mirror topology, reducing the amplitude of the oscillating signal. This also eliminates the need for a series resistor.

In [9], a circuit is proposed that implements a new XO architecture. This is developed using 180 nm CMOS technology, in an area of 0.3 mm<sup>2</sup>. Voltage supply ranges from 0.94-1.82V and temperature variation is not a conditioning factor, since testing proved that frequency drift in ppm is not severely affected (-4.56 ppm to 133.3 ppm). Minimum power consumption is reported at **5.58 nW** at room temperature.

In [31], a self-charged XO (SCXO) is used to drastically lower power consumption, supply voltage and chip area. It is developed using 28 nm CMOS technology, implemented in an area of 0.03 mm<sup>2</sup>. The SCXO itself only occupies 0.0028 mm<sup>2</sup> and the remaining space is used for the resitors and capacitors. Minimum power consumption is **1.89 nW** from a voltage supply of 0.15 V. Temperature deviation in ppm is reported as 48.8 ppm in a range of -20° to 80°C

In [32], an oscillator uses duty cycle to lower total power consumption from **2.1 nW** to **1.5 nW**, at the cost of an increased but negligible temperature deviation (1.87 ppm/ $^{\circ}$ C in 0-80 $^{\circ}$ C range, reaching -146 ppm at 80 $^{\circ}$ C). With duty cycling, it reaches -150 ppm at 80 $^{\circ}$ C). The circuit is implemented in 130 nm CMOS technology and occupies an area of 0,0625  $mm^2$ .

Since our implementation requires a minimum sizing of less than a  $mm^2$ , a crystal will not be the best option to execute the work since it is bulky and expensive. A more compact alternative is necessary to create a low cost and low area solution to answer the current IoT nodes demands [33].

#### 3.2.2 RC Oscillators

RC Oscillators and Relaxation oscillators operate in the same methodology. They function by charging a capacitor with a constant current and discharging it when it reaches a certain threshold voltage.

3.2 Oscillators 25

In [33], a RC Oscillator (RCO) is proposed, with a simple circuit that differs from a regular RCO (voltage mode) because it uses a current-mode architecture with a charge recycling integrator. Power dissipation is **54.2 nW** at room temperature with 0.85 V voltage supply. It is susceptible to temperature variation (99.5ppm/°C).

In [34], another RCO is proposed with a power consumption of **120 nW** on a voltage supply of 1V, with a small temperature variation in -40 to 90°C range ( $\pm 2500$  ppm). This is developed using 65 nm CMOS technology and the circuit occupies an area of 0,0032  $mm^2$ .

In [35], an RCO is suggested that consists of an RC network, an inverting gain component from a resistor terminal to a capacitor point and another inverter gain element from the common resistor/capacitor terminal back to the resistor terminal. An advantage of this implementation is its ability to easily scale frequency. This was developed using 65 nm CMOS technology, occupying an area of  $0.0015 \ mm^2$  and achieving a power consumption of **190 nW**. Frequency stability is between  $\pm 1100$  ppm and  $\pm 2100$  ppm over the -20 to  $90^{\circ}$ C range.

#### 3.2.3 Relaxation Oscillators

Another type of oscillators used in RTC applications are *relaxation oscillators*. These are favored against XOs because they do not require any external components and can be implemented in CMOS technology in a cheaper way. Besides, they draw less current than a XO oscillator, at the cost of a larger clock jitter. On the other hand, these are more susceptible to temperature variation [29].

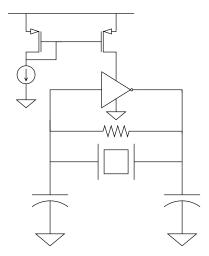

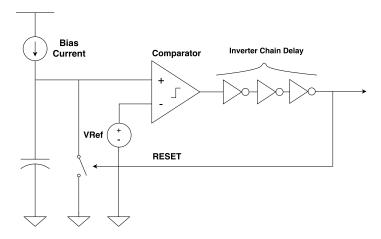

In figure 3.6, the capacitor is charged with a current source (*Bias current I<sub>REF</sub>*) and is reset periodically. A continuous comparator is used to trigger the reset signal, comparing the voltage in the capacitor terminal with a reference voltage (VRef). The inverter chain is responsible for the delay in the reset signal, allowing for a full discharge of the capacitor while reset is active. This produces a **sawtooth waveform** in the capacitor terminal and in the output of the comparator, with a output clock period of:

$$T_{period} = \frac{C_{INT}V_{REF}}{I_{REF}} + 2t_d \tag{3.1}$$

where  $t_d$  is comparator and inverter chain delay.

In [36], in order to address the temperature and supply dependency of the typical relaxation oscillator architecture, a constant charge subtraction circuit scheme has been developed. It achieves a power consumption of **5.58 nW** with a temperature stability of 45 ppm/°C, but operational frequency is limited to 11 Hz.

In [37], a typical relaxation oscillator is restructured in order to be area efficient. It achieves a power consumption of **271 nW**, in 1.1 to 1.3 voltage supply range. Temperature deviation is 135 ppm/°C. This circuit is developed using 65 nm technology and it occupies an area of 0,022 mm<sup>2</sup>.

Figure 3.6: Relaxation Oscillator circuit [29]

In [38], a relaxation oscillator fully on-chip is implemented. At a supply voltage of 1 V, it achieves a power consumption of **472 nW** and an operational frequency of 32.55 kHz. This implementation adopts new compensation architecture to achieve a higher frequency output. It generates a stable oscillation clock pulse with a temperature deviation of 120ppm/°C.

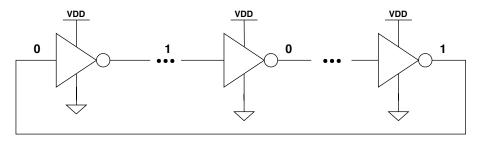

### 3.2.4 Ring Oscillators

Another type of oscillators employed in real-time clock applications is the **ring oscillator** [39]. This topology is developed using an odd number of inverters in a closed feedback loop circuit. Although, at least 5 inverters should be used, an illustration of the typical implementation is shown in figure 3.7. In general, a ring with *N* inverters will oscillate with a frequency of:

$$f_{OSC} = \frac{1}{2Nt_p} \tag{3.2}$$

where  $t_p$  is the propagation delay of an inverters. This circuit also allows for a simple method of measuring the inherent propagation delay in an inverter circuit.

### **Odd number of inverters**

Figure 3.7: Ring Oscillator circuit [39]. The number of inverters should be around 7 or 11, or even higher.

3.2 Oscillators 27

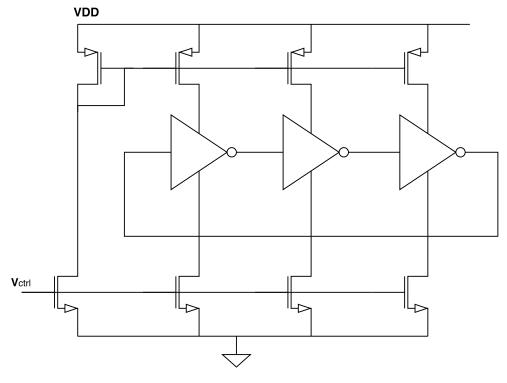

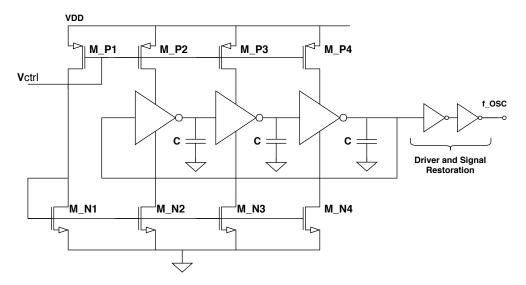

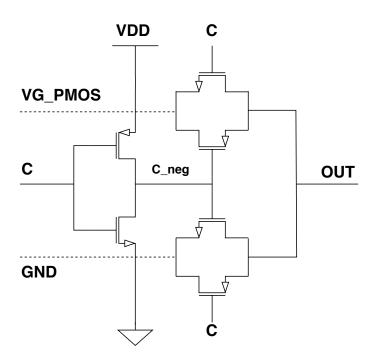

In figure 3.8, a current starved ring oscillator (CSRO) solution is proposed.  $V_{CTRL}$  is assumed as:

$$V_{CTRL} = \sqrt{\frac{f_{OSC} \cdot N \cdot V_{DD} \cdot C_{TOT}}{0.5 \cdot \mu_N \cdot C_{OX} \cdot \frac{W}{L}}} + V_{TH}$$

(3.3)

where  $f_{OSC}$  is the oscillation frequency, N is the number of inverters in the closed chain,  $V_{DD}$  is the supply voltage,  $C_{TOT}$  is the total load capacitor. The mobility carrier  $\mu_N$  and threshold voltage  $V_{TH}$  are dependent on temperature then, consequently,  $V_{CTRL}$  is also dependent on temperature as follows:

$$V_{CTRL} = aT + b (3.4)$$

where *a* and *b* are coefficients. These types of ring oscillators are widely used due to their stability in voltage and temperature variations.

Figure 3.8: Current Starved Ring Oscillator circuit [40]

In [41], an ultra low power voltage controlled ring oscillator (*VCRO*) for a passive RFID application is given. The VCRO occupies an area of 500  $\mu m^2$  and has a power consumption of **3,6 nW** at a voltage supply of 140 mV. This implementation uses quasi-floating gate (QFG) techniques, allowing for an oscillation with a low supply voltage.

In [42], the inverters are substituted by a delay cell, with a biasing network and an output buffer. Altough power consumption is **2.01 mW** at a supply voltage of 1 V, this device is used for Bluetooth applications, with an operating frequency of 4.9 GHz. As demonstrated earlier, power consumption can be lowered with a smaller frequency.

In [43], a temperature sensor using a current starved ring oscillator for IoT applications is presented. It works with a voltage supply of 0.2V with an overall power consumption of **3.75 pW**. This sensor is composed of 3 parts that converts the temperature signal to a digital code.

In [44], a current start VCRO is presented, with a topology that improves the output signal symmetry. It achieves a frequency range of 1.75 kHz to 10 MHz with a power consumption of 1 nW to 3.6  $\mu$ W, respectively.

For this implementation, the current starved ring oscillator is chosen because:

- Crystal oscillators are too big to be integrated in a small chip and have increased costs.

- LC oscillators are circuits used primarily in RF technologies and the implementation of an inductor component with a small area is extremely difficult. Besides, the oscillation frequency is obtained using:

$$\omega_o = \frac{1}{\sqrt{LC}} \tag{3.5}$$

showing that it is dependent of the capacitance and inductor value.

- RC and Relaxation Oscillators obtain their oscillation frequencies through a time constant generated by the values of a resistance and a capacitor.

- Current starved ring oscillators are VCO's that generate a constant frequency by manipulating a current. It also has a great integration capability since it is dependent on the propagation delay of CMOS transistors. Compared to the remaining topologies, it also allows for a more fine tuned oscillation frequency that can be easily trimmed for process corners by changing the current source CTAT and PTAT value.

### **Chapter 4**

## **Proposed Architecture**

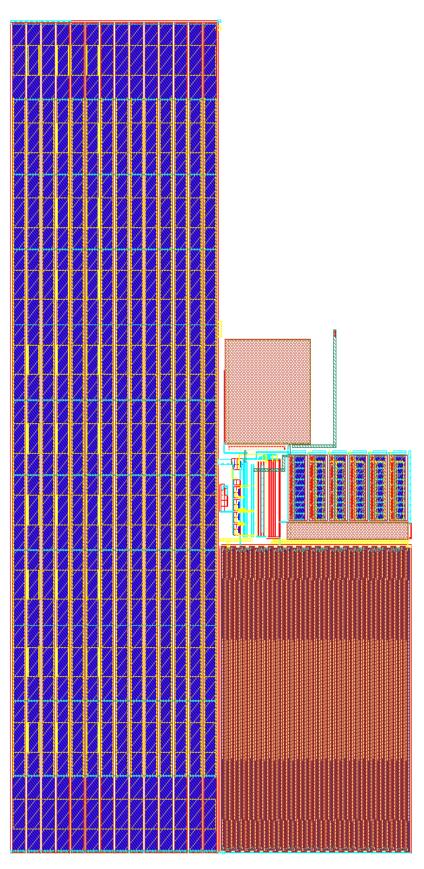

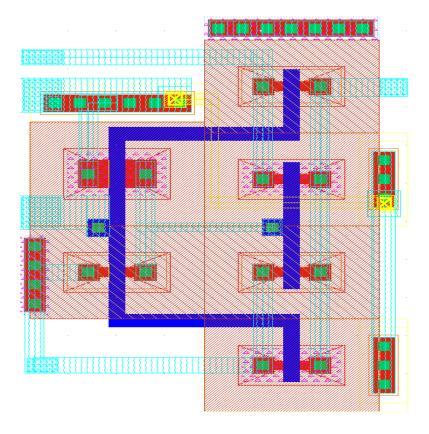

Taking into account the different theoretical considerations regarding the intended work to be done, the implementation of the Real-Time Clock will be performed using the topology as seen in figure 4.1. This modular methodology increases the independence of each component and makes it so that each part can be used for different purposes. The final integration of the whole project is specified in chapter 7.

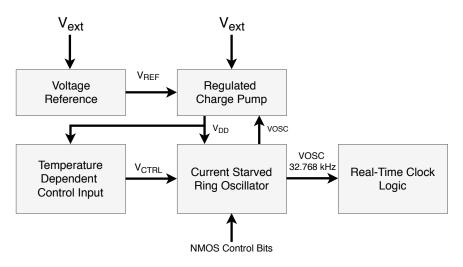

Figure 4.1: Overall schematic block of the final circuit implemented

The circuits will be described independently throughout the following sections, showcasing the different methodologies for the intended implementation. They can be divided in two different domains:

Analog design that is responsible for the development of the Voltage References necessary

for the functionality of the circuit, the regulated charge pump for a voltage supply stability,

the voltage control for temperature compensation and the oscillator, that provides a stable

signal output with a specific frequency as a digital input for the intended logic;

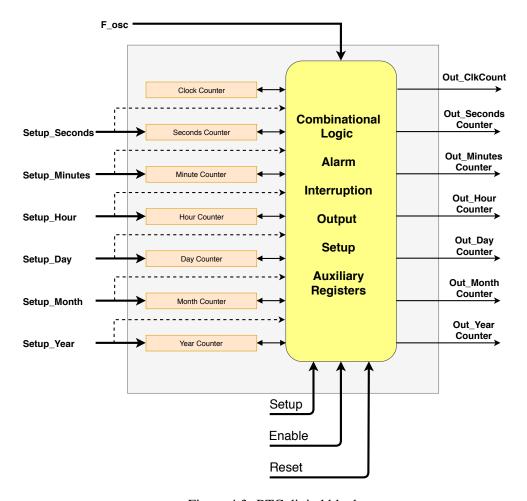

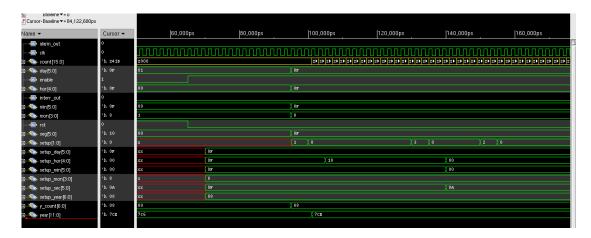

• **Digital design** that handles the input frequency clock and generates the Real-Time Clock functionalities (time counting, alarms and interrupts), mainly done developing a verilog circuit;

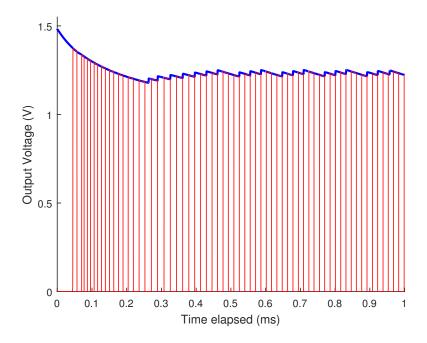

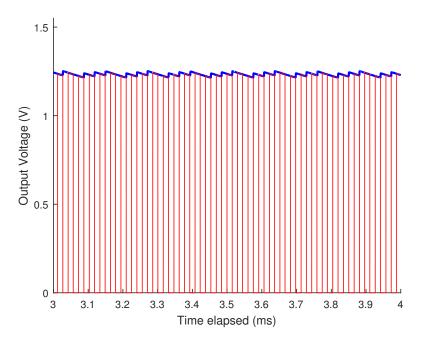

Digital power consumption is inherently low power since the clock signal will be provided by the implemented current starved ring oscillator. As seen in (2.2), dynamic power consumption is proportional to clock frequency. By using a value such as the objective (32.768 kHz), low power digital circuitry is achieved. Since the main objective of this work is to develop an ULP circuit, the analog component of the system is the main endeavor of the implementation. Transistors operating with low current values have an increased sensitivity towards PVT variations.

- Process variation derives from the different corner processes that describe different speeds for NMOS and PMOS devices, resulting in different current values and different threshold voltages.

- Voltage variation comes from the supply voltage. The current available for each transistor

varies if the supply voltage also changes, since an external battery value deteriorates over

time.

- Temperature variation occurs because of the inherent properties of each device. Transistor parameters (threshold voltage  $V_{TH}$ , carrier mobility  $\mu c$  and thermal voltage  $U_T$ ) display a deviation with temperature changes. This is further escalated when low current values are used for implementation.

An oscillator operating in this region is a challenging task to stabilize for different temperatures, voltage supply variation and process variability.

### 4.1 Analog Topology

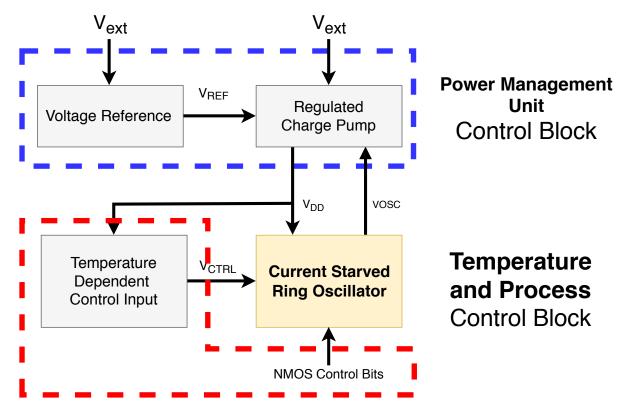

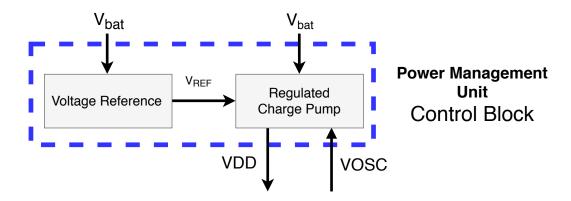

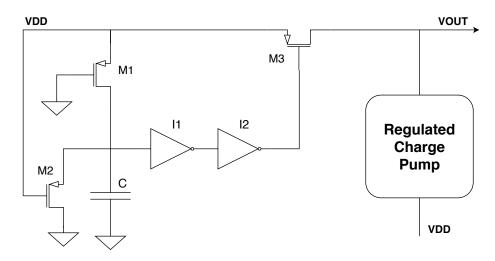

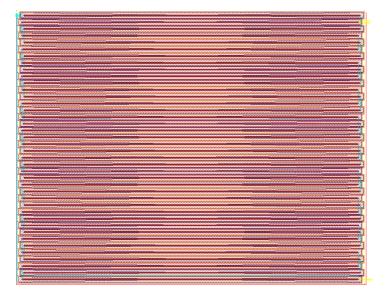

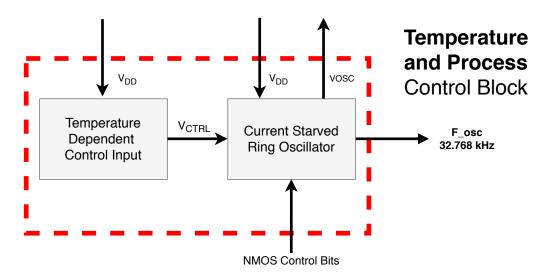

The analog circuit in this work can be described in two parts, as seen in figure 4.2:

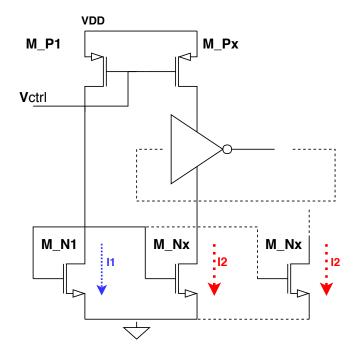

- Power Management Unit that is responsible to feed the oscillator a stable voltage supply  $V_{DD}$  that is independent of the  $V_{EXT}$ , the external voltage supply. This circuit must be able to achieve the same supply voltage for the internal circuit even when the external battery starts to deteriorate over time.

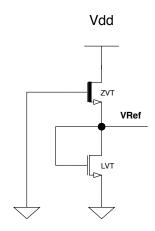

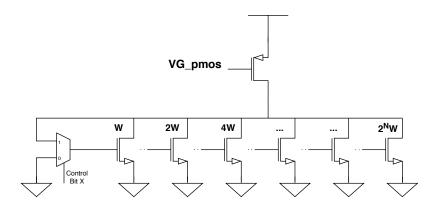

- Temperature and Process Block that overcomes the oscillating frequency deviation according to a signal  $V_{CTRL}$  that is designed to compensate the temperature variation. The process homogeneity is achieved through a trimming section inside the oscillator's schematic;

The main objective of the final analog design is to develop a structure that allows for a stable oscillating frequency that is independent of all process, temperature and voltage variations.