# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# Accelerating Software Test Execution Using GPUs

Vanya Yaneva-Cormack

Doctor of Philosophy Laboratory for Foundations of Computer Science School of Informatics University of Edinburgh 2021

## Abstract

Today, software is all around us, impacting our everyday lives in fundamental ways. Developing software whose behaviour is reliable, predictable and correct is therefore crucial. This has made software testing a critical part of the development process and has led to the emergence of rigorous testing practices and standards. Testing any non-trivial system, however, is time-consuming and takes up the bulk of development time. Modern software engineering practices involve the repeated execution of large test suites, as part of regular build, test and release cycles. A common approach to speeding up testing without sacrificing rigour is distributing test executions among computer clusters and cloud servers, but this can be complex and expensive due to the costs of testing infrastructure and energy consumption.

This thesis presents a novel approach to accelerating test execution by parallelising it using Graphics Processing Units (GPUs) - powerful and low-cost hardware accelerators that are readily available in the majority of modern desktops. It demonstrates that GPUs can be used to dramatically reduce test execution time at a lower cost compared to other parallel approaches. To achieve this, it addresses significant challenges related to usability, performance and scope, and makes three separate contributions:

First, a GPU testing framework, ParTeCL, is developed to automatically transform the system under test into GPU source code and launch test execution in parallel on the GPU threads. ParTeCL performs the entire testing process transparently without requiring any expert GPU programming and architecture knowledge.

Second, two types of systems are used to evaluate the applicability and effectiveness of the approach - sequential C programs form the embedded systems domain and Finite State Machine (FSM) models. To enable testing them on the GPU, compiler-based transformations and FSM implementations are developed and included in ParTeCL.

Finally, GPU performance is extensively analysed and optimised through a combination of standard and domain specific techniques. Evaluation on programs from the two domains demonstrates that the GPU outperforms a standard 16-core Central Processing Unit (CPU) by up to  $4 \times$  (avg.  $1.4 \times$ ) for embedded systems and up to  $9 \times$ (avg.  $4.5 \times$ ) for FSMs.

The techniques developed in this thesis demonstrate the exciting possibilities of using specialised hardware architectures, such as GPUs, for the acceleration of software test execution. Through integration into the testing process, they could provide rapid feedback, reducing the amount of costly bug-fixing in later stages of development.

## Lay Summary

Software testing is the process of ensuring that a given computer program does what we intend it to. It involves the repeated execution of the program, giving it different parameters, and observing if it behaves as expected every time. The parameters used for testing are called test inputs. As a program is developed and grows in size and complexity, so does its set of test inputs. Normally, software engineers execute the set of tests after each change to the program to ensure that the change did not introduce new faults. This is a repetitive process, which is not performed manually by the engineers, but automatically by a computer. As most programs have many tests, executing all of them often can be a very time-consuming process, leading to delays in the software development process and loss of productivity. It is often said that testing accounts for at least 50% of a project's cost.

Graphics processing units (GPUs) are a type of very fast computer processor that is able to perform many of the same operations in parallel, using different inputs. This thesis proposes using them to speed up software testing by executing multiple tests in parallel on them. This is not easy to do, as GPUs are a niche type of processor that is challenging to use without knowledge of its hardware and programming models. The work in this thesis develops tools for software engineers to be able to use GPUs for software testing without the need to program them themselves. It then uses these tools to speed up test execution for two types of computer program and shows that, for these programs, GPUs are indeed faster than conventional computers when executing tests.

## Acknowledgements

First, I would like to thank my supervisor, Dr. Ajitha Rajan, for her invaluable guidance in the past four years. Throughout this time she was a constant source of inspiration and encouragement, continuously helped me see the big picture in our research, and was always available when I needed motivation and support.

I would also like to thank Dr. Christophe Dubach for co-supervising my PhD and providing crucial advice that has helped shape the technical approaches, experimental designs and results analysis in this work.

I would like to thank my colleagues from the University of Edinburgh for the friendships, emotional support and good times. I am deeply grateful to have met you all. The PhD experience would not have been the same without you.

Finally, I would like to thank my lovely parents and sister for always being my champions, and my dear Fraser for being my rock.

## **Declaration**

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified. Some of the material used in this thesis has been published in the following papers:

- Vanya Yaneva, Ajitha Rajan, and Christophe Dubach.

"Compiler-assisted test acceleration on GPUs for embedded software".

In Proceedings of the 26th ACM SIGSOFT International Symposium on Software Testing and Analysis (ISSTA), 2017.

- Vanya Yaneva, Arnav Kapoor, Ajitha Rajan, and Christophe Dubach.

"Accelerated Finite State Machine Test Execution Using GPUs" In *Proceedings of the 25th Asia-Pacific Software Engineering Conference (APSEC)*, 2018.

(Vanya Yaneva)

# **Table of Contents**

| 1 | Intr | oduction                                          | 1  |

|---|------|---------------------------------------------------|----|

|   | 1.1  | Software Testing and GPUs                         | 2  |

|   | 1.2  | Challenges in Using GPUs for Software Testing     | 3  |

|   |      | 1.2.1 Usability                                   | 3  |

|   |      | 1.2.2 Scope                                       | 3  |

|   |      | 1.2.3 Performance and Scalability                 | 3  |

|   | 1.3  | Problem Statement                                 | 5  |

|   | 1.4  | Contributions                                     | 5  |

|   |      | 1.4.1 Automated GPU Test Execution                | 5  |

|   |      | 1.4.2 Accelerated Embedded System and FSM Testing | 6  |

|   |      | 1.4.3 Performance Analysis and Optimisations      | 6  |

|   | 1.5  | Publications                                      | 7  |

|   | 1.6  | Structure                                         | 7  |

|   | 1.7  | Summary                                           | 9  |

| 2 | Bac  | kground                                           | 11 |

|   | 2.1  | Introduction                                      | 11 |

|   | 2.2  | Software Testing                                  | 11 |

|   |      | 2.2.1 Term Definitions                            | 12 |

|   |      | 2.2.2 Example: Linear Search                      | 14 |

|   |      | 2.2.3 Testing Practices                           | 16 |

|   | 2.3  | GPU Architecture and Programming                  | 16 |

|   |      | 2.3.1 Architecture                                | 16 |

|   |      | 2.3.2 Memory Hierarchy                            | 17 |

|   |      | 2.3.3 Programming Model - OpenCL                  | 18 |

|   | 2.4  | Embedded Software                                 | 20 |

|   | 2.5  | Finite State Machines                             | 21 |

|   |      | 2.5.1     | Complete and Partial FSMs                                 | 22 |

|---|------|-----------|-----------------------------------------------------------|----|

|   |      | 2.5.2     | Testing FSMs                                              | 23 |

|   | 2.6  | Summ      | ary                                                       | 25 |

| 3 | Rela | ated Wo   | ork                                                       | 27 |

|   | 3.1  | Introd    | uction                                                    | 27 |

|   | 3.2  | Accele    | erating Software Testing                                  | 27 |

|   |      | 3.2.1     | Minimisation, Selection and Prioritisation                | 27 |

|   |      | 3.2.2     | Parallel Test Execution                                   | 30 |

|   | 3.3  | Using     | GPUs for Software Testing                                 | 31 |

|   | 3.4  | Testing   | g Embedded Software                                       | 32 |

|   | 3.5  | Testing   | g Finite State Machines                                   | 33 |

|   | 3.6  | GPU C     | Code Generation                                           | 34 |

|   | 3.7  | Summ      | ary                                                       | 36 |

| 4 | Para | allel Tes | st Execution Using GPUs                                   | 37 |

|   | 4.1  | Introd    | uction                                                    | 37 |

|   | 4.2  | Genera    | al Approach                                               | 38 |

|   | 4.3  | ParTe(    | CL - Automating Test Execution on the GPU                 | 40 |

|   |      | 4.3.1     | ParTeCL CodeGen                                           | 42 |

|   |      | 4.3.2     | ParTeCL Runtime                                           | 47 |

|   | 4.4  | Extend    | ding Application Scope                                    | 48 |

|   | 4.5  | Optim     | ising Test Transfers to Improve Performance               | 51 |

|   |      | 4.5.1     | Direct Memory Access                                      | 51 |

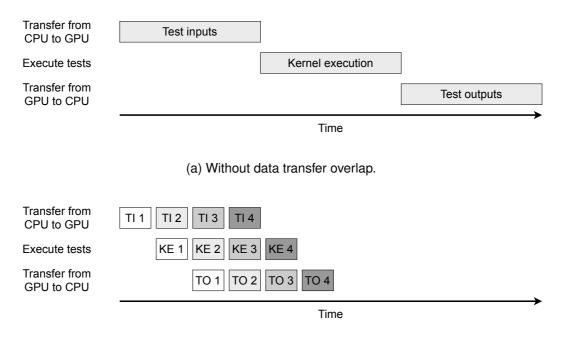

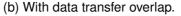

|   |      | 4.5.2     | Data Transfer Overlap                                     | 52 |

|   | 4.6  | Summ      | ary                                                       | 54 |

| 5 | Test | ing Em    | bedded Software: Evaluating Applicability and Performance | 57 |

|   | 5.1  | Introd    | uction                                                    | 57 |

|   | 5.2  | Appro     | ach                                                       | 58 |

|   |      | 5.2.1     | Embedded Systems Benchmarks                               | 58 |

|   |      | 5.2.2     | Analysing Applicability                                   | 58 |

|   |      | 5.2.3     | Evaluating Performance                                    | 63 |

|   | 5.3  | Experi    | imental Setup                                             | 63 |

|   |      | 5.3.1     | Test Generation                                           | 64 |

|   |      | 5.3.2     | Hardware and Measurements                                 | 64 |

|   | 5.4  | Result   | s and Analysis                                                | 65  |

|---|------|----------|---------------------------------------------------------------|-----|

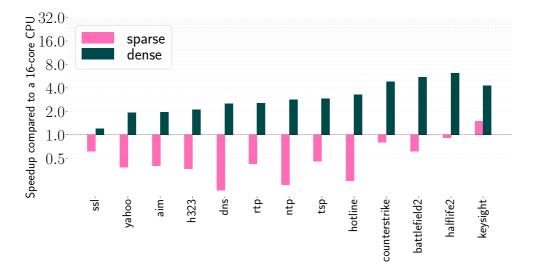

|   |      | 5.4.1    | Q1. GPU vs CPU Execution                                      | 66  |

|   |      | 5.4.2    | Q2. Kernel Execution vs Data Transfer Time                    | 68  |

|   |      | 5.4.3    | Q3. Data Transfer Overlap: Effect on Performance              | 70  |

|   |      | 5.4.4    | Analysis                                                      | 70  |

|   |      | 5.4.5    | Q4. Correctness                                               | 71  |

|   | 5.5  | Summ     | ary                                                           | 72  |

| 6 | Test | ing Fini | ite State Machine Models: Establishing Feasibility            | 73  |

|   | 6.1  | Introd   | uction                                                        | 73  |

|   | 6.2  | Appro    | ach                                                           | 74  |

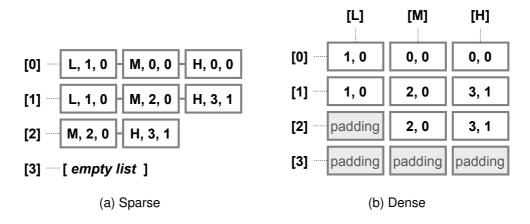

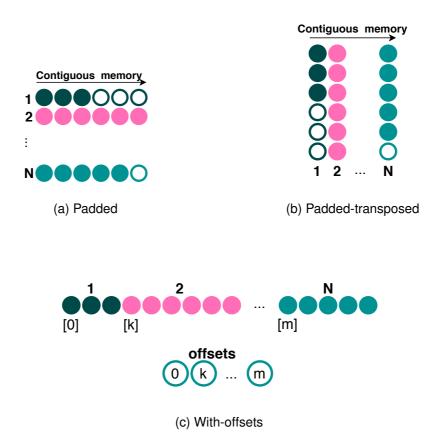

|   |      | 6.2.1    | Memory Layouts                                                | 75  |

|   |      | 6.2.2    | Sorting the Test Sequences Based on Length                    | 78  |

|   |      | 6.2.3    | FSM Input Formats for ParTeCL                                 | 78  |

|   | 6.3  | Experi   | mental Setup                                                  | 80  |

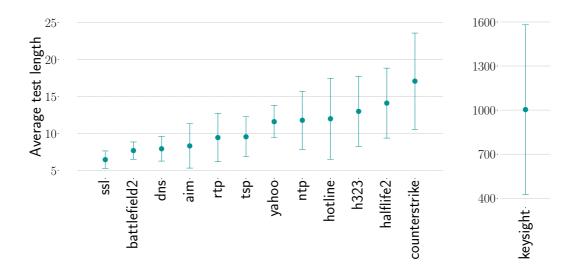

|   |      | 6.3.1    | Subject FSMs and Tests                                        | 81  |

|   |      | 6.3.2    | Hardware and Measurements                                     | 83  |

|   | 6.4  | Result   | s and Analysis                                                | 84  |

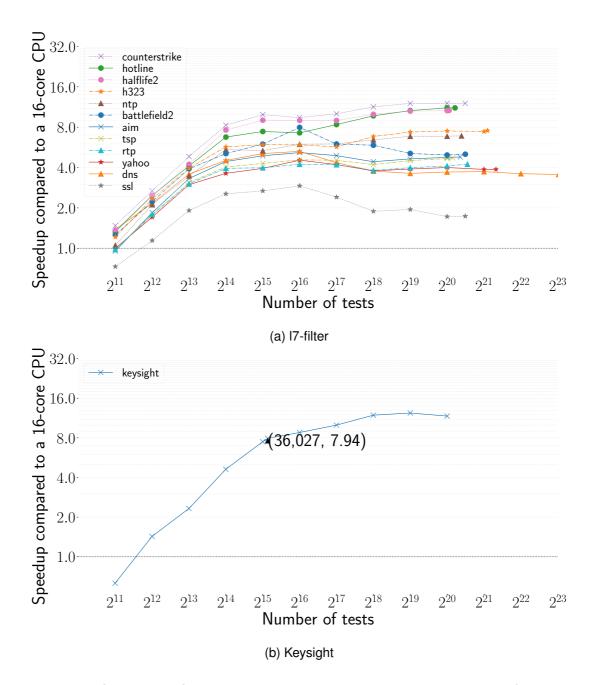

|   |      | 6.4.1    | Q1. GPU Kernel vs Multi-Core CPU Execution                    | 84  |

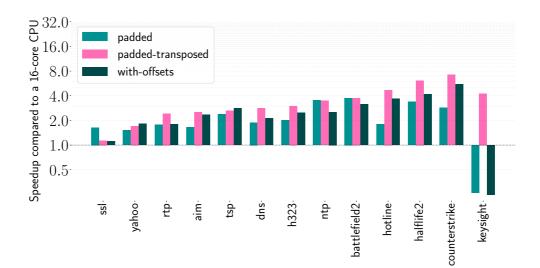

|   |      | 6.4.2    | Q2. Effect of FSM Layout                                      | 86  |

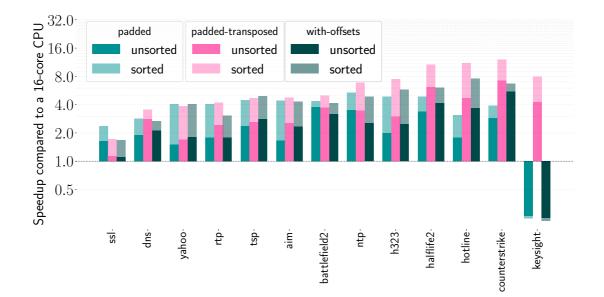

|   |      | 6.4.3    | Q3. Effect of Test Layout                                     | 87  |

|   |      | 6.4.4    | Q4. Effect of Test Sorting                                    | 89  |

|   |      | 6.4.5    | Assessing Data Transfer Overhead                              | 89  |

|   | 6.5  | Summ     | ary                                                           | 91  |

| 7 | Test | ing Fini | ite State Machine Models: Evaluating Performance and Scale    | 93  |

|   | 7.1  | Introd   | uction                                                        | 93  |

|   | 7.2  | Appro    | ach                                                           | 94  |

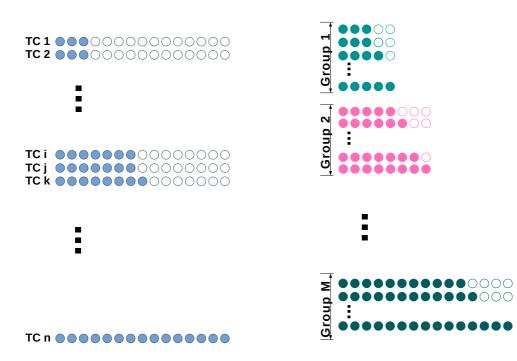

|   |      | 7.2.1    | Data Transfer Overlap: Dynamic Splitting of Tests Into Groups | 95  |

|   |      | 7.2.2    | Generating FSM Test Inputs                                    | 97  |

|   |      | 7.2.3    | Test Suite Reduction                                          | 98  |

|   | 7.3  | Experi   | mental Setup                                                  | 100 |

|   |      | 7.3.1    | Subject FSMs and Tests                                        | 101 |

|   |      | 7.3.2    | Hardware and Measurements                                     | 103 |

|   | 7.4  | Result   | s and Analysis                                                | 103 |

|   |      | 7.4.1    | Q1. Speedup in Total GPU Time, No Data Transfer Overlap       | 103 |

|     |        | 7.4.2    | Q    | 2. ] | Data | a Ti | rans | sfer | 0  | vei  | rlaj | p: | E | fe | ct | or | ı P | Per | fo | rn | nai  | nc | e | • | • | • | • |  | 108 |

|-----|--------|----------|------|------|------|------|------|------|----|------|------|----|---|----|----|----|-----|-----|----|----|------|----|---|---|---|---|---|--|-----|

|     |        | 7.4.3    | Q    | 3. ] | Data | a Ti | rans | sfer | 0  | vei  | rlaj | p: | E | fe | ct | or | ı S | Sca | la | bi | lity | y  |   |   |   | • | • |  | 110 |

|     |        | 7.4.4    | Q    | 4. ′ | Test | Su   | ite  | Re   | du | ctic | on   | •  | • |    |    | •  |     |     |    | •  |      |    |   |   |   | • | • |  | 112 |

|     | 7.5    | Summa    | ary  | •    |      |      | •    |      | •  |      | •    | •  | • |    | •  | •  | •   | •   |    | •  |      | •  | • | • | • |   | • |  | 113 |

|     |        |          |      |      |      |      |      |      |    |      |      |    |   |    |    |    |     |     |    |    |      |    |   |   |   |   |   |  |     |

| 8   | Cone   | clusion  |      |      |      |      |      |      |    |      |      |    |   |    |    |    |     |     |    |    |      |    |   |   |   |   |   |  | 115 |

|     | 8.1    | Contrib  | outi | ion  | s.   |      | •    |      | •  |      |      | •  | • |    | •  | •  | •   | •   |    | •  |      | •  |   | • | • | • | • |  | 115 |

|     | 8.2    | Critical | 1 A  | nal  | ysis | 5.   | •    |      |    |      |      | •  | • |    | •  | •  | •   | •   |    | •  | •    |    | • | • |   | • | • |  | 117 |

|     | 8.3    | Future   | Wo   | ork  |      |      | •    |      | •  |      |      | •  | • |    |    | •  |     |     |    | •  |      |    |   |   |   | • | • |  | 119 |

|     | 8.4    | Conclu   | ıdir | ng l | Ren  | nark | κs   |      | •  |      |      | •  | • |    | •  | •  |     |     |    | •  | •    |    | • | • |   | • | • |  | 121 |

| Bil | bliogr | aphy     |      |      |      |      |      |      |    |      |      |    |   |    |    |    |     |     |    |    |      |    |   |   |   |   |   |  | 123 |

# **List of Figures**

| 2.1 | The software testing process.                                        | 12  |

|-----|----------------------------------------------------------------------|-----|

| 2.2 | GPU architecture                                                     | 17  |

| 2.3 | GPU memory hierarchy                                                 | 18  |

| 2.4 | The OpenCL programming model                                         | 19  |

| 2.5 | A divide-by-3 FSM                                                    | 22  |

| 2.6 | An FSM model of a digital oscilloscope from Keysight Technologies.   | 24  |

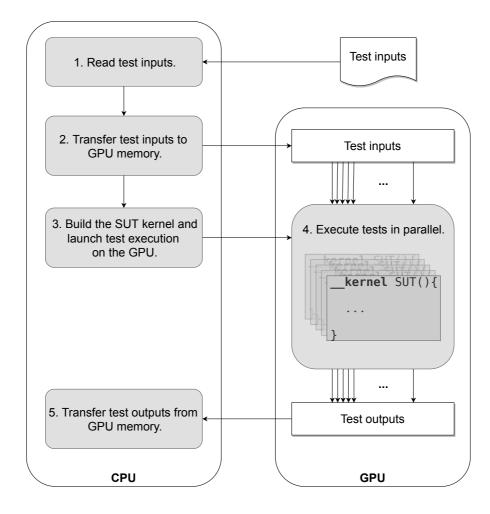

| 4.1 | Executing tests in parallel on the GPU                               | 39  |

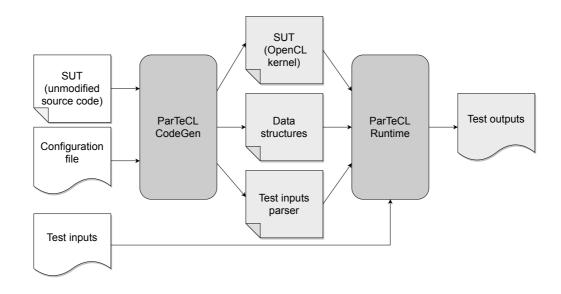

| 4.2 | ParTeCL system overview.                                             | 41  |

| 4.3 | DMA between CPU and GPU memory                                       | 52  |

| 4.4 | Overlapping data transfer with kernel execution                      | 53  |

| 5.1 | Analysing applicability of GPU test execution for embedded software. | 60  |

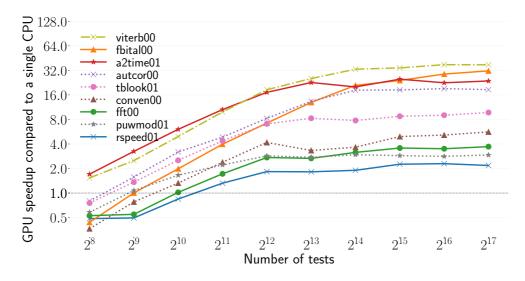

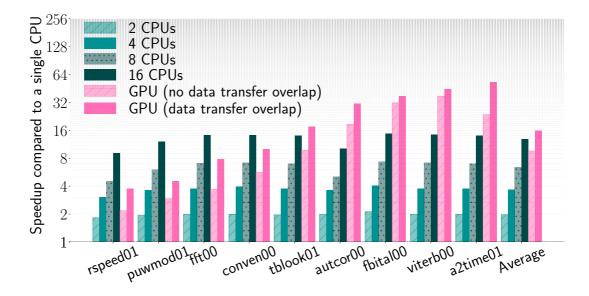

| 5.2 | GPU speedups for embedded software                                   | 66  |

| 5.3 | GPU and multi-core CPU speedups for embedded software                | 67  |

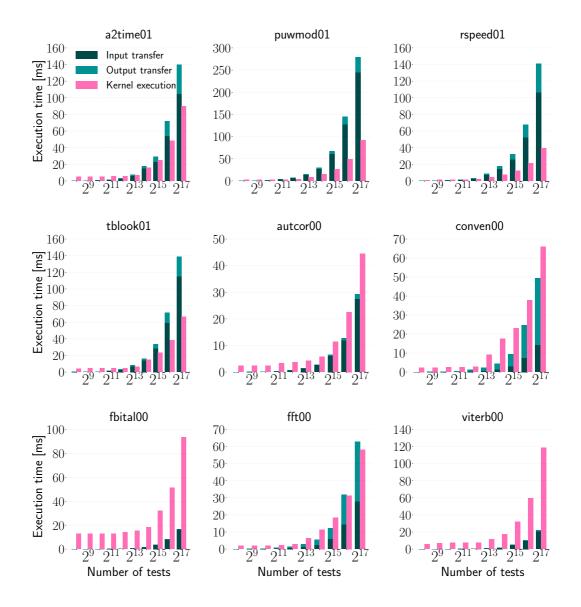

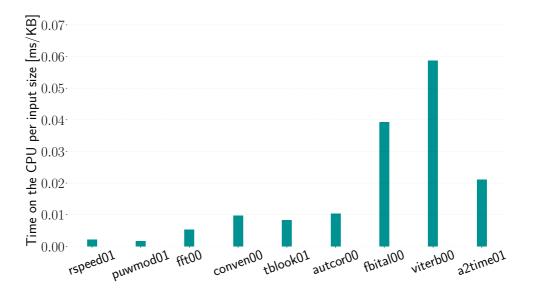

| 5.4 | Breakdown of total GPU time for embedded software                    | 69  |

| 5.5 | Computational intensity of EEMBC benchmarks.                         | 71  |

| 6.1 | GPU memory layouts for the FSM                                       | 76  |

| 6.2 | GPU memory layouts for the FSM test inputs and outputs               | 77  |

| 6.3 | Average test lengths for 17-filter and Keysight FSMs                 | 83  |

| 6.4 | GPU kernel speedups for 17-filter and Keysight FSMs                  | 85  |

| 6.5 | GPU kernel speedups for FSM memory layouts                           | 86  |

| 6.6 | GPU kernel speedups for FSM test memory layouts                      | 87  |

| 6.7 | GPU kernel speedup for sorted and unsorted test suites               | 89  |

| 7.1 | Splitting FSM test inputs into groups for data transfer overlap      | 96  |

| 7.2 | Generating test inputs for the digital oscilloscope FSM              | 97  |

| 7.3 | Average test lengths for snort FSMs                                  | 102 |

| 7.4  | GPU speedups for snort FSMs, without data transfer overlap           | 104 |

|------|----------------------------------------------------------------------|-----|

| 7.5  | GPU and CPU execution efficiency.                                    | 105 |

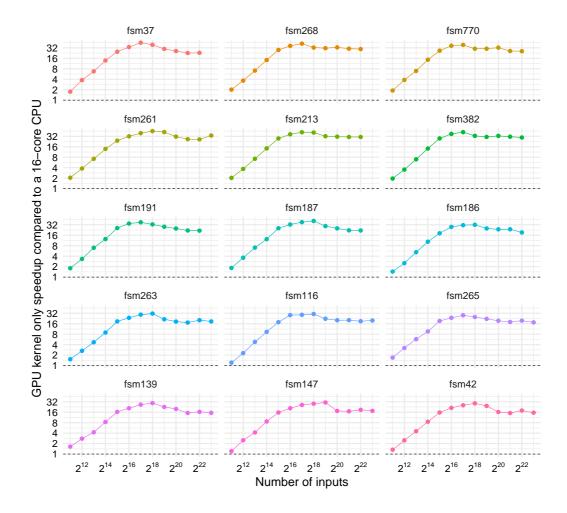

| 7.6  | GPU kernel speedups for snort FSMs                                   | 107 |

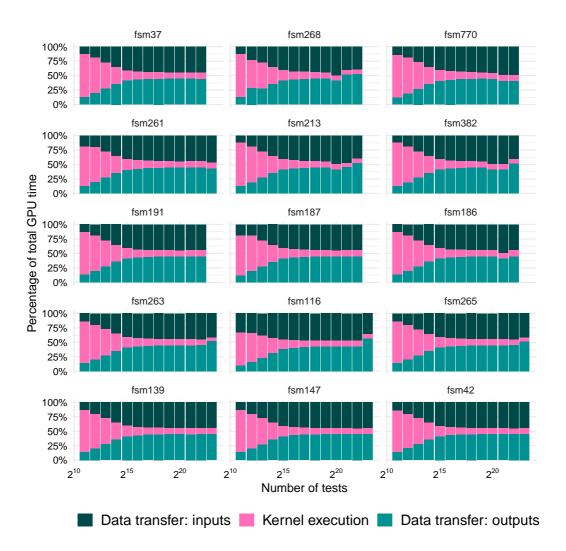

| 7.7  | Breakdown of total GPU time for snort FSMs                           | 108 |

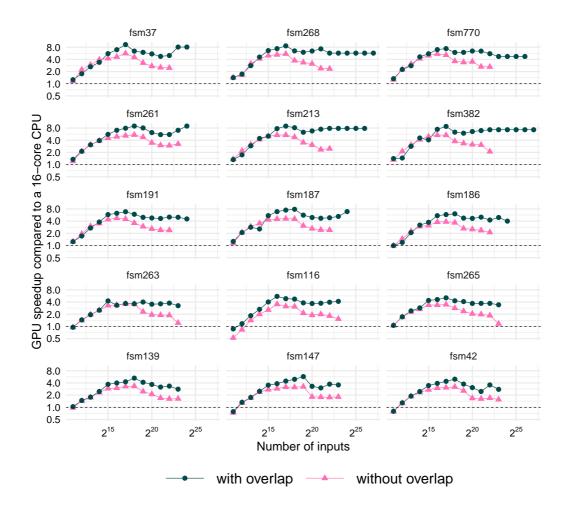

| 7.8  | GPU speedups for snort FSMs, with and without data transfer overlap. | 109 |

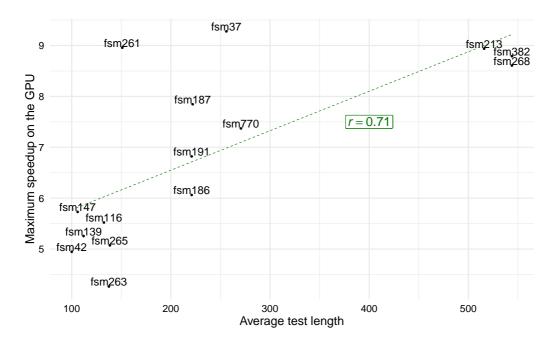

| 7.9  | Correlation between GPU speedup and average test length              | 110 |

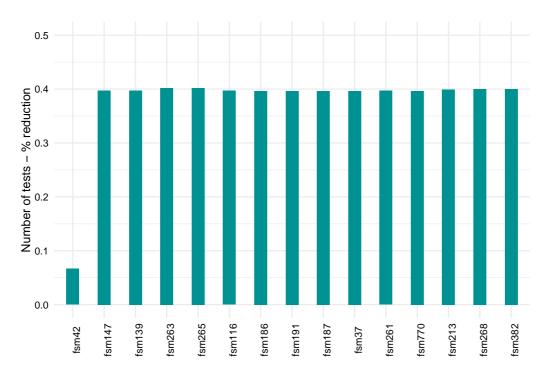

| 7.10 | Percentage change after test suite reduction                         | 112 |

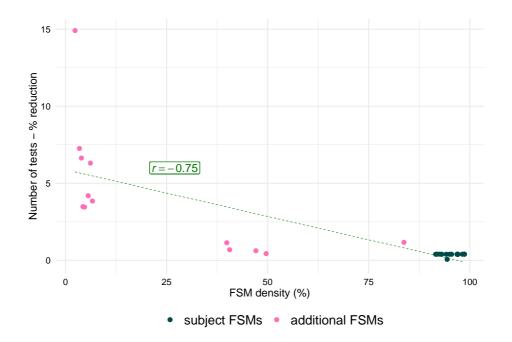

| 7.11 | Correlation between percentage reduction and FSM density             | 113 |

# **List of Tables**

| 1.1 | Thesis contributions and the challenges they address      | 6   |

|-----|-----------------------------------------------------------|-----|

| 1.2 | Thesis chapters, contributions and related publications   | 8   |

| 2.1 | Example tests for the linear search program.              | 14  |

| 4.1 | ParTeCL configuration file syntax.                        | 44  |

| 5.1 | EEMBC benchmark programs                                  | 59  |

| 5.2 | EEMBC programs which are successfully executed on the GPU | 62  |

| 5.3 | EEMBC programs used in performance evaluation             | 65  |

| 6.1 | FSMs used in evaluation - 17-filter and Keysight.         | 82  |

| 6.2 | Data transfer overhead for 17-filter FSMs                 | 90  |

| 7.1 | FSMs used in evaluation - snort.                          | 102 |

| 7.2 | FSM test suite scalability with data transfer overlap     | 111 |

# **List of Listings**

| 2.1 | Example: Linear search program                   | 13 |

|-----|--------------------------------------------------|----|

| 2.2 | GoogleTest example for the linear search program | 15 |

| 4.1 | ParTeCL configuration file for linear search.    | 42 |

| 4.2 | ParTeCL data structures for linear search.       | 42 |

| 4.3 | ParTeCL OpenCL kernel for linear search.         | 46 |

| 4.4 | ParTeCL test input file.                         | 47 |

| 6.1 | FSM example in <i>kiss2</i> format.              | 79 |

| 6.2 | FSM test input format.                           | 79 |

# **Chapter 1**

# Introduction

Software forms the basis of modern technology and is present in all areas of life. Today, software is embedded in household appliances, personal devices and everyday objects. It is widely used in diverse sectors including industry, healthcare, transport, finance and retail, among others.

With the growing use of software, developing reliable systems whose behaviour is predictable becomes critical. This has made rigorous software testing increasingly important, but thoroughly testing any non-trivial system is a complex and time-consuming process. Literature regularly states that testing effort accounts for the majority of the cost of development [1,2]. This problem is heightened with the use of widespread software engineering practices, such as test-driven development and continuous integration [3–5], which rely on systematic testing. They provide improvements to overall system quality and reductions in development costs, but involve the generation of extensive test suites for each system component and regular test executions for every build and release, making testing an even larger portion of the development process.

An important part of these practices is *regression testing* - the process of re-running tests after every change in order to ensure that no errors have been introduced in the existing functionality. As software evolves, new tests are added to the test suites, making regular test execution increasingly expensive and time-consuming.

These observations are confirmed by industry accounts. Facebook [6] and Google [7] state that even with the enormous resources dedicated to testing, they are unable to perform regression testing using all tests for each code change due to the large number of tests and high rate of changes. Google report that on an average day they perform 150 million automatic test executions at enormous compute cost, and they experience increased lag in time between code check-ins and test result feedback to developers.

The research community has developed a body of work addressing this problem. The focus has been on developing techniques to reduce the number of executed tests without sacrificing testing rigour [8] and on distributing test executions across computer clusters and cloud servers [9]. However, the first set of approaches could lead to reduced testing effectiveness [10, 11], while the second could be complex to set up [12] and expensive in terms of the cost and maintenance of the testing infrastructure [7].

This thesis addresses the problem of accelerating test execution by leveraging the high degree of parallelism available on modern Graphics Processing Units (GPUs). GPUs are powerful, readily available and low-cost hardware accelerators aimed at graphics processing, which have been successfully applied to a wide range of applications in other domains [13–16]. This thesis demonstrates that through the parallel execution of tests on separate GPU threads, GPUs can be successfully incorporated into the testing process and used to speed up test execution.

### 1.1 Software Testing and GPUs

The focus of this work is the acceleration of software testing aimed at checking functional correctness. This is the type of testing that ensures that the system behaves as intended, which is distinct from testing for non-functional properties, such as speed, portability or usability. It involves the execution of the program with different test inputs and verifying that it produces the expected outputs. For complex systems, thorough testing requires a large number of tests for each component. As a system evolves, the number of tests in its test suite grows, along with the time necessary to execute them.

GPUs could prove well suited to parallelising test execution and reducing the time it takes. In the general case, tests are both data parallel and independent, as the tested functionality is executed multiple times over separate independent inputs. This is precisely the computation pattern for which GPUs are designed, making a compelling case for their use for test execution. GPUs are also a cost-effective option for acceleration, present in virtually any modern computer. With the right tooling, they could allow developers to execute tests and receive feedback quickly on their local machines, before submitting their changes to shared development environments.

Nevertheless, using GPUs to parallelise test execution has until now remained an unexplored area. This work aims to change this. The following sections present the key challenges and contributions of this thesis.

### 1.2 Challenges in Using GPUs for Software Testing

GPUs could offer reduced test execution time at lower cost compared to other parallel architectures, but there are significant challenges, related to usability, scope and performance, that must be overcome to achieve this goal.

#### 1.2.1 Usability

As a niche architecture targeted at accelerating graphics computations, GPUs are notoriously challenging to program. Writing GPU programs requires expert knowledge and the use of specialist programming models, such as OpenCL [17], CUDA [18] and SYCL [19]. Of these, SYCL provides the highest level of abstraction, allowing programmers to write their GPU programs using standard C++, but even with it understanding of the underlying GPU hardware is necessary. This represents a high barrier to entry in adopting and experimenting with GPU approaches for test acceleration, as the majority of software engineers do not have the necessary GPU programming expertise. This makes automated frameworks that are flexible and intuitive to set up essential for the use of GPUs in software testing.

#### 1.2.2 Scope

GPU programming models and compilers are based on the C/C++ programming languages. As a result, the scope of applications which can be tested using GPUs is limited to C/C++ programs, and to system models which can be implemented in C/C++ code. To evaluate the applicability of using GPUs for software testing, this thesis focuses on two types of systems: (1) sequential C programs from the embedded systems domain and (2) Finite State Machine (FSM) models, using examples from the network intrusion detection and digital signal processing domains.

In addition, due to hardware restrictions, there are standard C features that are not supported for compilation on the GPU. Such features include dynamic memory allocation, global scope variables and standard library functions. They pose further restrictions to the scope of the approach and their impact is evaluated in this thesis.

#### 1.2.3 Performance and Scalability

GPUs achieve high speeds compared to Central Processing Units (CPUs) due to their highly parallel architecture, capable of launching thousands of threads at the same

time, but simply compiling and running an application on the GPU does not guarantee performance. GPU performance is subject to a number of factors related to the architecture, programming model, executed application and associated data. To establish the effectiveness of using GPUs to accelerate test execution, it is crucial to understand their importance in that context. Some of the most common factors that hinder GPU performance are:

*Data transfer overhead.* GPUs have their own memory and data needs to be explicitly copied between it and main memory before and after execution. Depending on the amount of data, these data transfers can be slow, adding considerable overhead to GPU time and severely impacting performance. With respect to testing, test inputs and outputs need to be transferred and the overhead could be significant for the target applications, as it is precisely programs with large test suites that are likely to benefit the most from parallel test execution on the GPU.

*GPU Memory Bandwidth*. In GPUs, memory bandwidth is shared among thousands of threads impacting the performance of memory intensive applications [20]. Applications written by expert programmers specifically for the GPU can alleviate this by taking advantage of *memory coalescing*, in which data used by neighbouring threads is stored in contiguous memory blocks and retrieved from memory at once. However, this is a GPU specific optimisation that cannot be expected in every tested application and shared memory bandwidth could have considerable performance impact.

*Choice of GPU Parameter Values.* Selecting appropriate values for GPU configuration parameters plays an important role in achieving optimal performance. They depend on the specific GPU hardware, the implementation of the program and the structure and size of program data. Finding the optimal configuration for a given GPU architecture is a challenging problem, which has been addressed through the use of dynamic techniques [21,22].

*Limited Memory.* GPUs have a limited amount of memory which tends to be smaller than main memory. In addition, unlike CPUs, GPUs do not have access to a hard disk. This could pose a limitation to the scalability of the approach, as large test suites comprised of large amounts of data may not fit into GPU memory.

### **1.3 Problem Statement**

Thorough software testing is a crucial part of the development process that ensures the correct behaviour, reliability and quality of the developed system. However, testing is often time-consuming and expensive, taking up the majority of development time. Regression testing involves the repeated test executions of large test suites as part of daily development and overnight builds and adds considerable strain to the software development schedule. GPUs are widely available and inexpensive parallel accelerators that could be well suited to speeding up test execution, but using them poses significant challenges in terms of usability, scope, performance and scalability.

The goal of this thesis is to address these challenges by improving the usability of GPUs for the purpose of test execution, evaluating the applicability and extending the scope of the approach and evaluating and improving its performance and scalability.

### 1.4 Contributions

This thesis makes three main contributions. Table 1.1 shows which challenges are addressed by each contribution.

#### 1.4.1 Automated GPU Test Execution

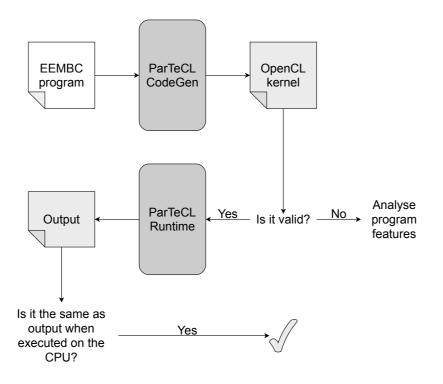

A GPU testing framework, called ParTeCL<sup>1</sup>, is developed to automatically perform test execution in parallel on the GPU, using the OpenCL programming model. ParTeCL performs two tasks: (1) it translates the tested application into an OpenCL program, which can be compiled and executed on the GPU and (2) it launches instances of the tested program on the GPU threads, each with a separate test input.

ParTeCL addresses the usability challenge (Section 1.2.1) by launching test execution on the GPU transparently, relieving programmers from the need to write any GPU-specific code. Furthermore, it facilitates the techniques used to address the scope and performance challenges (Sections 1.2.2 and 1.2.3) by providing an automated framework in which to implement them.

<sup>&</sup>lt;sup>1</sup>ParTeCL - Parallel Testing in OpenCL

#### 1.4.2 Accelerated Embedded System and FSM Testing

The proposed approach is applied to two types of applications: (1) sequential C programs from the embedded systems domain and (2) FSM models from the network intrusion detection and digital signal processing domains. Testing is of paramount importance to both of them and they can both be instrumented using the GPU programming models (Section 1.2.3). Nevertheless, there are still scoping challenges involved in using GPUs to test them. This thesis evaluates the applicability and feasibility of the approach and addresses these challenges by applying compiler-based transformations to C features that are not readily supported on the GPU. Furthermore, additional OpenCL implementations for FSM test execution are implemented in ParTeCL.

#### 1.4.3 Performance Analysis and Optimisations

GPU performance for test execution is optimised using a combination of approaches. First, standard techniques to minimise the latency of data transfer are implemented in ParTeCL. Then, GPU performance for both application domains is analysed and optimisation approaches are developed, implemented and evaluated. Evaluation demonstrates that with optimisations, the GPU is faster than a standard 16-core CPU by up to  $4 \times$  (avg.  $1.4 \times$ ) for embedded systems and up to  $9 \times$  (avg.  $4.5 \times$ ) for FSMs. This addresses the performance challenge (Section 1.2.3) by demonstrating that GPUs can achieve better performance than their counterpart multi-core CPUs available on the same machine.

| Contribution                                        | Challenge                         |

|-----------------------------------------------------|-----------------------------------|

| Automated GPU Test Execution (1.4.1)                | Usability (1.2.1), Scope (1.2.2), |

|                                                     | Performance and Scalabil-         |

|                                                     | ity (1.2.3)                       |

| Accelerated Embedded System and FSM Testing (1.4.2) | Scope (1.2.2)                     |

| Performance Analysis and Optimisations (1.4.3)      | Performance and Scalabil-         |

|                                                     | ity (1.2.3)                       |

Table 1.1: Thesis contributions and the challenges they address.

### 1.5 Publications

The ideas and results presented in this thesis are based on three previous publications and one publication which is currently under revision. Table 1.2 summarises the thesis chapters, the contributions which they make and the publications to which they relate.

The framework for automatic test execution on the GPU (ParTeCL), presented in Chapter 4 was first presented in:

1. Yaneva, V., Rajan, A. & Dubach, C. ParTeCL: Parallel Testing Using OpenCL. In ISSTA 2017. [23]

Chapter 5 presents accelerated testing of embedded systems, which was previously published in:

2. Yaneva, V., Rajan, A. & Dubach, C. Compiler-assisted Test Acceleration on GPUs for Embedded Software. In ISSTA 2017. [24]

FSM testing using GPUs, presented in Chapter 6, was first published in:

3. Yaneva, V., Kapoor, A., Rajan, A. & Dubach, C. Accelerated Finite State Machine Test Execution Using GPUs. In APSEC 2018. [25]

Finally, the approach to improving the scale and performance of FSM testing presented in Chapter 7 is currently submitted and under revision in:

4. Yaneva, V., Rajan, A. & Dubach, C. GPU Acceleration of FSM Input Execution: Improving Scale and Performance. In STVR 2020 (under revision). [26]

This thesis reproduces the experimental results and analysis found in the above publications. It also offers background information (Chapter 2) and a survey of existing literature (Chapter 3), which includes references to recent work in the related fields.

### 1.6 Structure

This thesis is organised as follows:

Chapter 2 provides background information relevant to the motivation, methods, evaluation and results in this thesis. It describes the software testing process and provides details on GPU architecture and programming, embedded systems and FSMs.

| Chapter                                                 | Contribution        | Publication |

|---------------------------------------------------------|---------------------|-------------|

| 2. Background                                           |                     |             |

| 3. Related Work                                         |                     |             |

| 4. Parallel Test Execution Using GPUs                   | 1.4.1, 1.4.2, 1.4.3 | [23]        |

| 5. Testing Embedded Software: Evaluating Applicability  | 1.4.2, 1.4.3        | [24]        |

| and Performance                                         |                     |             |

| 6. Testing Finite State Machine Models: Establishing    | 1.4.2, 1.4.3        | [25]        |

| Feasibility                                             |                     |             |

| 7. Testing Finite State Machine Models: Evaluating Per- | 1.4.2, 1.4.3        | [26]        |

| formance and Scale                                      |                     |             |

| 8. Conclusion                                           |                     |             |

Table 1.2: Thesis chapters, contributions and related publications.

Chapter 3 provides an overview of existing work in five related areas: software test acceleration, the use of GPUs in software testing, testing of embedded systems and FSMs and automatic GPU code generation.

Chapter 4 describes the general method of executing tests in parallel on the GPU. It presents ParTeCL - the automated framework developed for this purpose and describes the general performance optimisations that are included in its implementation. The approach and tools presented in this chapter are used in the rest of the thesis.

Chapter 5 applies the approach to the testing of sequential C programs from the embedded system domain. It provides an evaluation of applicability and performance using applications from the EEMBC industry-standard benchmark suite [27].

Chapter 6 establishes the feasibility of using GPUs to accelerate FSM testing. Different designs for the FSM and test suites are considered, implemented and evaluated in order to choose the optimal implementation in terms of execution time. ParTeCL is extended to support FSM test execution.

Chapter 7 extends the work presented in Chapter 6 by improving the performance and scalability of the approach for FSM test execution. Evaluation using 15 large FSMs from the network intrusion detection domain is performed, demonstrating that, with optimisations, GPUs can execute FSM tests up to  $9 \times$  faster than a 16-core CPU.

Chapter 8 summarises the main findings of this thesis, provides a critical review and discusses potential future work.

## 1.7 Summary

The growing dependence on software in all areas of human life has made software testing a crucial part of the development cycle in order to ensure the correctness, reliability and robustness of the developed systems. While essential, software testing is often a time-consuming and expensive part of the development process. GPUs could prove successful in accelerating test execution with greater performance and at lower cost compared to other parallel approaches. Achieving this requires overcoming three main challenges, concerning usability, scope and performance and scalability. The next two chapters provide technical background and discuss existing related work, while subsequent chapters present and evaluate techniques to address these challenges.

# **Chapter 2**

# Background

### 2.1 Introduction

This chapter provides relevant background information to aid the understanding of the problem and solutions presented in this thesis. First, it presents the software testing process and defines the terms used throughout this thesis in Section 2.2. This is followed by descriptions of the GPU architecture, memory hierarchy and programming model in Section 2.3, focusing on aspects relevant to parallel test execution and the optimisations presented in this work. The application domains to which the approach is applied, embedded systems and FSM models, are introduced in Sections 2.4 and 2.5, respectively. Finally, Section 2.6 concludes.

### 2.2 Software Testing

Program testing can be a very effective way to show the presence of bugs, but is hopelessly inadequate for showing their absence.

Edsker W. Dijkstra

Software testing is a process used to evaluate whether a system meets the *functional specifications* for its behaviour [28]. It aims to demonstrate that a system behaves as intended, by executing it using a range of inputs and checking that the outputs are as expected every time. Testing to ensure that a system meets other non-functional requirements, such as speed, portability or usability, is outside the scope of this thesis.

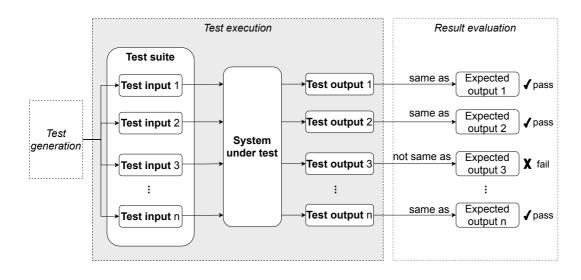

Figure 2.1: The software testing process. It consists of three stages: test generation, test execution and result evaluation. This thesis focuses on using GPUs to accelerate *test execution*.

Figure 2.1 illustrates the software testing process. First, tests are generated (*test generation*). This can be done either through the manual writing of tests or through the use of automated techniques. Tests consist of separate inputs to the system under test (SUT) and expected outputs. Next, the SUT is executed repeatedly, once with each test input, and its outputs are recorded (*test execution*). Finally, the outputs are compared to the expected outputs (*result evaluation*). A test passes if the two outputs are the same and fails if they are not.

#### 2.2.1 Term Definitions

Informal words referring to aspects of software testing can be intuitive and testing terms are not always used consistently in literature. For this reason, it is useful to define the terms used throughout this thesis.

- system/program/application under test (SUT/PUT/AUT) the software system or part of the system that is tested; for simplicity, SUT is used throughout this thesis

- test case or test a set of inputs and a pass/fail criterion, also known as *test oracle*; typically, the oracle is given in the form of an expected output, but could also consist of other criteria

- **test suite** a set of test cases; a test suite for a system may by made up of several test suites for individual modules, subsystems or units

- test input input data for the SUT that is part of a test case

- test output the output produced by the SUT during test execution

- **expected output** the correct output for a given test input, based on the SUT's specification

- **test result** indication whether a test execution passed (i.e. the system met its requirements) or failed.

```

#include <stdio.h>

1

#include <stdlib.h>

2

3

int find(int array[], int n, int number) {

4

for (int i = 0; i < n; i++) {

5

if (number == array[i]) {

6

return i;

7

}

8

9

}

return -1;

10

}

11

12

int main(int argc, char **argv) {

13

14

// input error checking is omitted for brevity

15

16

17

int n = atoi(argv[1]);

int array[n];

18

19

printf("Enter %d array numbers.\n", n);

20

for (int i = 0; i < n; i++) {

21

scanf("%d", array + i);

22

23

}

printf("Enter a number to find.\n");

24

25

int number;

scanf("%d", &number);

26

27

// perform a search

28

int found_idx = find(array, n, number);

29

30

// output answer

31

printf("Number found at idx: %d\n", found_idx);

32

}

33

```

Listing 2.1: Linear search program, implemented in C.

#### 2.2.2 Example: Linear Search

To illustrate software testing, Listing 2.1 shows a simple C program, which performs a linear search. The core function is find() on lines 4-11. It has three inputs: an array of integers *array*, its length *n* and a number *target*, for which to search in the array. It performs a linear search in *array* and returns the first index at which *target* is found, or -1 when *target* is not in the array. The main() function accepts values for *n* through the command line (line 17) and for *array* and *target* through standard input (lines 22 and 26) and calls find() to perform the linear search. Finally, it prints the output in standard output.

The functional specification for linear search is the following:

- 1. It accepts as inputs an array of integer values, the length of the array and an integer number for which to search in the array.

- 2. It returns the first index at which number is present in the array; it returns -1 if the number is not present in the array.

- 3. If the array is empty, it returns -1.

Table 2.1 shows an example test suite for the linear search program based on this specification, which contains four tests. Listing 2.2 shows an implementation for these tests in GoogleTest [29] - an automated testing framework for C/C++ programs. The SUT is the find() function and all tests are structured following the process illustrated in Figure 2.1: (1) the test inputs are declared and initialised, (2) the SUT is executed with the test inputs and the test output is recorded and (3) the test output is compared to the expected output (using the assertions available in GoogleTest, e.g. EXPECT\_EQ).

| Test id |   | Test inpu           | Expected output |    |

|---------|---|---------------------|-----------------|----|

|         | n | array               | target          |    |

| 1       | 5 | $\{1, 2, 3, 4, 5\}$ | 3               | 2  |

| 2       | 5 | $\{1, 2, 1, 2, 1\}$ | 2               | 1  |

| 3       | 5 | $\{1, 2, 3, 4, 5\}$ | 10              | -1 |

| 4       | 0 | {}                  | 5               | -1 |

Table 2.1: Example tests for the linear search program.

```

TEST(linear_search_test, test_id_1) {

1

int n = 5;

2

int array[] = {1,2,3,4,5};

3

int target = 3;

4

int output = find(array, n, target);

5

EXPECT_EQ(output, 2);

6

}

7

8

TEST(linear_search_test, test_id_2) {

9

int n = 5;

10

int array[] = {1,2,1,2,1};

11

12

int target = 2;

int output = find(array, n, target);

13

EXPECT_EQ(output, 1);

14

}

15

16

TEST(linear_search_test, test_id_3) {

17

int n = 5;

18

int array[] = {1,2,3,4,5};

19

int target = 10;

20

int output = find(array, n, target);

21

EXPECT_EQ(output, -1);

22

23

}

24

TEST(linear_search_test, test_id_4) {

25

int n = 0;

26

int array[] = {};

27

28

int target = 5;

int output = find(array, n, target);

29

EXPECT_EQ(output, -1);

30

31

}

```

Listing 2.2: Example tests for the linear search program, implemented in GoogleTest.

#### 2.2.3 Testing Practices

The purpose of software testing is to provide confidence that a system's behaviour conforms to specification. Ideally, test suites will exhaustively sample the entire input space of a system, but in practice this is infeasible, as even trivial programs would need many billions of tests, that would be impossible to execute in any practical amount of time. For example, to exhaustively test a program which takes two 32-bit integers as arguments,  $2^{64} \approx 10^{21}$  tests are needed. At one nanosecond ( $10^{-9}$  seconds) per test, this would take approx.  $10^{12}$  seconds, which is about 30,000 years [28]. For this reason, the goal of software testing is to uncover faults in the system which can be fixed. Sufficient testing should eventually provide enough confidence that no critical faults remain.

Testing can be applied at any level of system granularity - individual functions, modules and entire systems. *Unit testing* checks the behaviour of the smallest functional units of a program. *Integration testing* checks the correctness of the interactions between units and modules. *System testing* focuses on the behaviour of the system as a whole.

**Regression Testing** Regression testing aims to ensure that changes to the existing code do not introduce new faults in the system. It is used regularly in continuous integration and test-driven development, usually as soon as a change to the program is made. Developers often build and test multiple times a day, both locally on their own machines and remotely, on dedicated central servers. Automated overnight builds and test executions for the whole system are also a common practice. These testing practices are repetitive and, combined with large test suites necessary for thorough testing, they are time-consuming, creating a crucial need of time efficient test execution techniques.

## 2.3 GPU Architecture and Programming

GPUs are highly parallel hardware accelerators, designed for the efficient processing of large blocks of data. They do not work by themselves but together with a generalpurpose CPU form a single heterogeneous system.

#### 2.3.1 Architecture

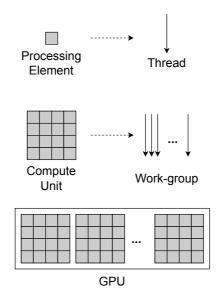

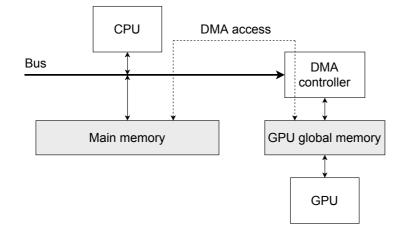

Figure 2.2 illustrates the GPU architecture. GPUs consist of compute units, each of which contains a number of processing elements, which execute the individual GPU threads. The functions executed by the GPU threads are called **kernels**.

Figure 2.2: GPU architecture. GPUs consist of compute units, each of which contains multiple processing elements that execute the individual GPU threads. All threads belonging to a compute unit are organised into a work-group (in the OpenCL programming model). The functions executed by the GPU threads are called **kernels**.

All threads in a compute unit are organised into groups, which in OpenCL are called work-groups<sup>1</sup> [30]. Threads belonging to the same compute unit follow the Single Instruction Multiple Data (SIMD) execution model - each thread executes an instance of the same kernel over different input data. With respect to software testing, this corresponds to running instances of the same SUT with different test inputs.

Threads in the same compute unit share the same instruction counter, and instruction execution is performed in lock-step - all threads execute the same instruction at any one time. If there is control-flow divergence across threads, divergent instructions will be serialised, negatively impacting performance. Similarly, when the workload is not balanced across threads, some threads would stay idle, resulting in reduced performance.

#### 2.3.2 Memory Hierarchy

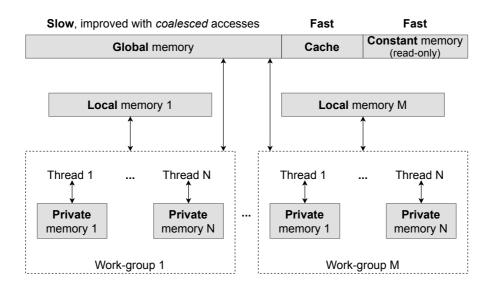

GPUs have a memory hierarchy, which is illustrated in Figure 2.3. The placement of data during GPU execution can have significant impact on performance. The GPU memory hierarchy consists of the following regions:

<sup>&</sup>lt;sup>1</sup>In OpenCL, GPU threads are referred to as work-items. For simplicity, this thesis uses the term *thread* throughout.

Figure 2.3: GPU memory hierarchy. Placement of data during GPU execution can have significant impact on performance.

- Global memory large and slow, shared among all threads in all compute units. Performance is improved, when accesses are *coalesced* during execution, i.e. when all threads access consecutive addresses in global memory. Performance can also be improved through the use of the cache.

- *Constant memory* a read-only portion of global memory, which contains a special cache allowing faster memory access.

- Local memory local to compute units, shared among threads in a work-group.

- Private memory private to individual threads.

GPU memory is usually smaller than main memory and is the only storage available to the GPU, as it has no access to the hard disk. For this reason, input data needs to be moved from main memory to GPU memory before kernel execution. Similarly, output data needs to be moved from GPU memory back into main memory after kernel execution. These data transfers can add considerable overhead to GPU execution time, resulting in negative impact on performance.

#### 2.3.3 Programming Model - OpenCL

GPUs require the use of specialist programming models. They include CUDA [18], OpenCL [17] and SYCL [19]. Based on the C/C++ programming languages, they

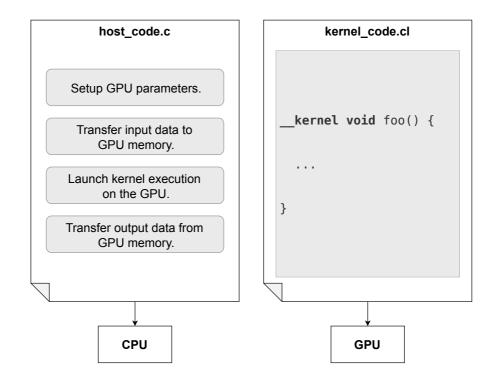

Figure 2.4: The OpenCL programming model. An OpenCL program consists of a host part, executed by the CPU, and a kernel part, executed by the GPU.

expose low-level hardware details and require the programmer to explicitly express the parallelism in terms of the architecture. Each model differs in the degree to which they abstract GPU architecture, but all of them require specialist knowledge from the programmer in order to achieve fast GPU performance.

This work uses OpenCL for multiple reasons. It is an open standard, which is maintained by an industry consortium of over 140 companies that include hardware designers such as the Intel Corporation, NVIDIA, Qualcomm, AMD and ARM. Its C-like syntax allows for the automatic translation of the SUT into an OpenCL kernel. In addition, it provides cross-platform portability, making possible future research on testing with other parallel heterogeneous architectures. Finally, it provides a relatively low level of abstraction for the GPU hardware, allowing for fine-grained performance optimisations and analysis. At the time of writing, OpenCL 1.2 [30] is the version most commonly supported by hardware vendors and is the one used in this thesis.

Figure 2.4 illustrates the basic structure of an OpenCL program. It consists of a host part, executed by the CPU, and a kernel part, executed by the GPU. The host part is written in C or C++ and uses the OpenCL host API. Its role is to setup GPU execution parameters, transfer data to/from GPU memory and compile and run the GPU

kernel<sup>2</sup>. The kernel part is written in OpenCL. During GPU execution, each thread executes an instance of the kernel application, using the input data transferred by the host application.

## 2.4 Embedded Software

Embedded systems are a type of computer that is integrated into a larger system. They consist of hardware and software components that form a computation unit designed to perform a particular function within another system. Crucially, unlike conventional software, embedded systems often operate in interaction with the physical world by reading and reacting to inputs from different environmental sensors.

Embedded systems are ubiquitous. They are found in the consumer, industrial, transportation, telecommunication, medical and military sectors, among others. Developing dependable embedded systems is a critically important, but difficult process, which relies on the use of rigorous methods and standards [31].

Characteristics Common characteristics of embedded systems are:

- 1. Interactions with the environment; embedded systems are designed to react to inputs from the physical world and other components in the larger system, leading to many possible interactions and a high degree of complexity in the software.

- 2. Strict requirements for safety, reliability and availability; as embedded systems are connected to the physical environment and have a direct impact on it, it is critical that their behaviour is dependable.

- 3. Restrictions on resource consumption; these could be memory, power, run-time and code size.

- 4. Majority of embedded software is written in the C programming language.

These characteristics have an impact on the design, development and testing of embedded software. They require a high degree of engineering expertise and knowledge of the application domain and hardware. Particular emphasis is placed on the requirements and design phases of development. Formal methods and model-driven approaches are often used as a way to ensure that all quality requirements and resource consumption constraints are incorporated into the system design [31].

<sup>&</sup>lt;sup>2</sup>The GPU kernel can be compiled by the host application at runtime. Alternatively, it can be compiled beforehand and read as a binary by the host application.

**Testing** Thorough and rigorous testing is another critical part of embedded software development. Ebert and Jones [32] estimate that testing takes up 15% to 50% of total project duration and is a major cost driver for embedded software development.

One of the key challenges associated with embedded software testing is generating tests which accurately represent environmental inputs [33]. Most interfaces in embedded systems are non-human interfaces (e.g. temperature and pressure sensors) which produce a large range of potential inputs. It is crucial for embedded software to behave predictably in the face of different, often unpredictable, inputs. Several methods are used for the generation of embedded software tests. These include tests derived from the system requirements and design models, sampling of input parameter combinations, the use of rigorous code coverage criteria, and the use of static and dynamic analysis [31,34]. In practice, these methods result in large test suites which are time-consuming to execute repeatedly as part of regular regression testing [32,33].

## 2.5 Finite State Machines

This thesis considers FSMs in the context of model-based development - a widespread software development approach, in which software is implemented and verified based on a model of the required system. FSMs are a useful abstraction which is used to model a large variety of systems, including embedded systems, control circuits, signal processing tools and communications protocols. Industry tools which use FSMs to model computer systems include Simulink [35], IBM Rational Rhapsody [36] and Sparx Systems Enterprise Architect [37].

FSMs are commonly classified as two types that are very similar, Moore and Mealy machines, with the Mealy definition being more general. Mealy machines have a finite number of states and given a current state and an input, they transition to a new state and produce an output. A formal definition of a Mealy FSM is found in [38]:

**Definition 1.** A finite state machine *M* is a quintuple

$$M = (I, O, S, \delta, \lambda)$$

where *I*, *O* and *S* are finite non-empty sets of input symbols, output symbols and states, respectively.

$\delta: S \times I \to S$  is the state transition function and

$\lambda: S \times I \to O$  is the output function.

When the machine is in a state *s* in *S* and receives an input *a* from *I* it moves to the next state specified by  $\delta(s, a)$  and produces an output  $\lambda(s, a)$ .

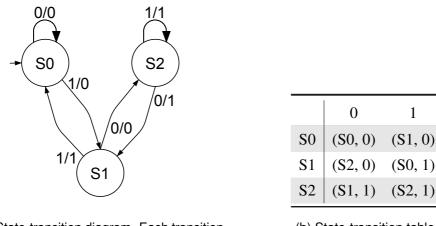

An example FSM is shown in Figure 2.5a as a state-transition diagram. The input to this FSM is a binary number and the output is the input divided by 3. Thus, the sets of input and output symbols *I* and *O* are both  $\{0,1\}$  and the set of states *S* is  $\{S0,S1,S2\}$ .

**Starting State** Generally, FSMs have a single initial state which they enter when they are reset. Throughout this thesis, this is referred to as the *starting state*. The starting state for the divide-by-3 FSM in Figure 2.5 is *S*0.

**Accepting State** Some FSMs may have one or more accepting states, indicating whether the received input sequence is accepted or not. Such FSMs may not produce outputs at each transition, but a single output once all input has been processed, indicating if the reached state is accepting or not.

(a) State-transition diagram. Each transition is labelled as *input/output*.

(b) State-transition table.

Figure 2.5: An example of a divide-by-3 FSM. The machine takes a binary number, as an input sequence of bit values, and produces the number divided by 3 as an output.

## 2.5.1 Complete and Partial FSMs

A *complete* FSM is one, in which every state has a transition for each input. These FSMs are also known as *deterministic* FSMs. In contrast, in a *partial* FSM, an input could have no transition for a given state, i.e. a partial FSM has missing transitions.

**Density** Chapters 6 and 7 refer to the *density* of a given FSM. It is calculated as the percentage of transitions present in the FSM out of the number of all possible transitions for that FSM, which is |S| \* |I|. Partial FSMs have densities that are less than 100%.

FSMs can be represented as state-transition tables, in which rows represent states and columns represent inputs from the input set. Each entry in the table is a tuple (next state, output), which encodes the transition of the FSM, corresponding to the respective state and input. In other words, the element for row *s* and column *a* of the matrix is the tuple ( $\delta(s,a), \lambda(s,a)$ ). A *sparse* transition table indicates that transitions are missing for a large number of state/input pairs. On the other hand, a *dense* table indicates that there is a transition for most state/input pairs.

Figure 2.5b shows the transition table for the divide-by-3 FSM. This is a complete FSM, which has a full transition table and a density of 100%.

### 2.5.2 Testing FSMs

FSM testing can refer to two distinct activities.

The first aims to confirm that a system implementation generated from an FSM model, manually or automatically, is behaviourally equivalent to the model. This is *not* the FSM testing activity that is the focus in this thesis, but it is related. In this activity, the FSM is used to generate suitable tests which, when executed on the implemented system, will confirm that the implementation conforms to requirements. It relies on the assumption that the FSM is an accurate model of the system requirements. This is the activity which is commonly referred to as *Finite State Machine Testing* in literature, covering problems like state identification, state verification and machine verification. There is extensive literature on these problems dating back to the 1950's [38, 39].

The second aims to check that an FSM model accurately captures the high level requirements. Its goal is to confirm that a system that is developed based on a model will deliver what is required of it. A practical approach to confirming the behaviour of FSM models, employed in industry, is the generation and execution of large test suites, which can be costly and time-consuming. This problem is the focus of Chapters 6 and 7 of this thesis. A test checking the behaviour of an FSM consists of an input sequence to the machine and an expected output sequence. Executing such a test involves applying the inputs in the sequence one by one, commencing at the starting state, transitioning through the states of the FSM, and recording the outputs associated with each transition. The test passes if the output sequence is the expected one and fails otherwise.

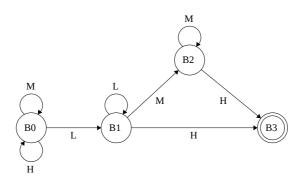

**Example: Digital Oscilloscope** The problem with time consuming FSM test runs was first brought to the author by an industrial partner, Keysight Technologies [40]. Keysight provide electronic measurement solutions to the wireless communications, aerospace and semiconductor industries. Their systems are modelled using FSMs that get tested extensively. They report that testing to validate their FSM models is part of the test cycles for test-driven development and there is tension between the need for test suites that achieve full coverage and the need for short test execution.

Figure 2.6: An FSM model of a digital oscilloscope from Keysight Technologies.

To illustrate this problem, consider an example designed by Keysight. Figure 2.6 shows an FSM, which is used to identify and trigger particular measurements of interest performed by a digital oscilloscope [41]. The inputs L, M and H correspond to Low, Medium and High frequencies and this particular FSM is designed to identify a rising edge in the digital signal. In order to ensure that the FSM identifies exactly the required type of digital pattern, the system engineers at Keysight perform testing on it. They execute input sequences and observe the output behaviour, checking both for false positives and false negatives.

While this is a simple example, the aforementioned test execution problem is encountered with large FSMs with thousands of states, depending on the input pattern they are designed to identify. Such FSMs require millions of tests to ensure that all parts of the FSM are tested adequately and provide confidence in its correctness. Executing all the tests can take arbitrarily long times, adding cost to the project and strain to the project schedule.

# 2.6 Summary

This chapter provides background information related to the problem and methodology presented in this thesis. Information on the software testing process demonstrates the problem of time-consuming test executions and the importance of solving it. Introduction to the GPU architecture, memory hierarchy and programming model is essential for the understanding of the main approach and performance optimisations in this thesis. Finally, the sections on embedded systems and FSMs introduce the application domains, to which the techniques proposed in this thesis are applied.

# **Chapter 3**

# **Related Work**

## 3.1 Introduction

The problems, solutions and applications examined in this thesis relate to five separate areas of research. The main problem belongs to the field of *accelerating software testing*. Section 3.2 reviews the existing work in this field, including traditional approaches and the use of parallel architectures. The proposed solution, execution of test cases in parallel on the GPU, falls within the broader area of *using GPUs for software testing*, which is reviewed in Section 3.3. This thesis applies the proposed solution to two types of systems, *embedded software* and *finite state machines*. Sections 3.4 and 3.5, respectively, provide summaries for the existing work on testing for both of them. Finally, the automated approach presented in Chapter 4 compliments existing research on *automated GPU code generation*, which is summarised in Section 3.6.

# 3.2 Accelerating Software Testing

Accelerating software testing is an important problem, which has received a lot of interest, examining both test generation and test execution. The related work in the context of this thesis is with respect to test execution.

## 3.2.1 Minimisation, Selection and Prioritisation

Optimising test execution is a long-standing problem and research in this area spans four decades. The objectives are reduced test execution costs in terms of both time and resources, without sacrificing effectiveness in terms of fault finding. Traditional approaches are primarily focused on manipulating the test suite and popular techniques are test suite minimisation, test case selection and test case prioritisation. Yoo and Harman [8] provide a comprehensive survey of these approaches.

- Test suite minimisation [42], also called test suite reduction, is the process of systematic removal of tests from a test suite, aiming to reach the minimum number of tests which satisfy some criteria, usually a measurement of code coverage. The goal is to optimise the test suite by removing tests that over time have become redundant with respect to the testing requirements for which they were generated. Finding the minimum test suite is an NP-hard problem and existing work has been focused on developing heuristics [43–45] and algorithms [46, 47] to guide this process.

- Test case selection [48] is a technique similar to test suite minimisation, but instead of focusing on a single version of the SUT, it aims to select a subset of tests for execution, covering the changes between two versions of the applications. In the context of regression testing, the goal is to avoid executing tests whose outcome will not have changed between the current and the previous versions of the program. Therefore, the selected set of tests will be different for each regression. Particular techniques for test case selection all aim to identify the test cases in the given test suite that cover the modifications in the program. Existing approaches are based on data-flow analysis [49–51] and graph-walking for control flow and control dependence graphs [52–55]. Test case selection techniques are surveyed by Biswas et al. [56], while Kazmi et al. [57] review recent empirical studies on their effectiveness in terms cost, coverage and fault finding, all of which are important objectives. In [58], Yoo and Harman formulate test case selection as a multi-objective problem and evaluate three algorithms. They allow software engineers to optimise test suites based on multiple objectives and observe trade-offs between them.

- Test case prioritisation [59] is a technique which reorders test cases based on some desirable criterion, with the aim of detecting faults as early during execution as possible. This is particularly useful in situations in which there are fixed time and resource budgets allocated for testing. Popular criteria used for test case prioritisation include code coverage [60–62], fault detection rates [63–66] and system requirements [67–69]. A systematic literature review on test case prioritisation criteria and techniques is provided by Khatibsyarbini et al. [70].

Recent work attempts to apply these techniques in real-world regression testing at scale. Elbaum et al. [71] report that traditional test selection and prioritisation approaches that rely on code coverage and instrumentation are too expensive for Google's large codebases. They propose two new cost-effective selection and prioritisation techniques, based on historical data of tests that were recently executed and revealed faults. Similarly, Herzig et al. [72] from Microsoft dismiss code coverage for test selection due to its runtime overhead, and present a cost-based test selection strategy based on historic test performance data. Machalica et al. [6] from Facebook also use historical testing data for test case selection, but in a novel way. They train a statistical model to select a subset of tests for a particular code change using basic machine learning techniques on data on previous code changes and test outcomes on those changes. All three papers report significant reductions in regression testing time and costs.

A major risk associated with test suite optimisation approaches is omitting the execution of tests which reveal faults in the SUT. Yoo and Harman [8] summarise the findings of four studies on the effect of test suite minimisation on fault finding. The studies provide contradictory results, with [73, 74] finding negligible reduction in fault finding, while [75, 76] show a considerable negative effect. Yu et al. [10] apply ten different test suite minimisation techniques to a set of eight programs and report that higher reduction in test suite size tends to negatively impact fault finding. A similar conclusion is reached by Heimdahl and George [77] for test suites form model-based test generation. Elbaum et al. [11] compare five different techniques for test case prioritisation over eight programs and conclude that the rate of fault detection after the application of test suite prioritisation varies considerably across different attributes of the SUT, test suites, and program modifications. In addition, Inozemtseva et al. [78] show that structural coverage of the code, one of the common criteria used for these approaches, does not have a strong correlation with test effectiveness when test suite size is controlled for, while a study by Namin and Andrews [79] concludes that both coverage and test suite size are important for fault finding. The results in these studies demonstrate the difficulty in guaranteeing that these approaches will not negatively impact fault finding for a given program and testing scenario. Therefore, when software correctness is of critical importance, executing the entire test suite would still be preferred. In these situations, parallel hardware can be leveraged to accelerate test execution without the need to modify the test suite. Furthermore, even in cases when minimisation, selection and/or prioritisation are successfully used, parallel test execution can still be utilised as a complimentary approach to further speed up testing.

## 3.2.2 Parallel Test Execution

Distributing test executions on parallel hardware infrastructure has become a widespread practice that has received attention both in industry and academia, using clusters of multiple machines to execute tests in parallel. Kushneryk and Barnett [80] use an auxiliary test environment, comprised of additional PCs, laptops and/or servers, to run test cases in parallel with the primary test environment. Misailovic et. al. [81] present a constraint-based algorithm that combines test generation and execution of structurally complex test inputs in parallel. They apply their approach to an application developed at Google, using 1024 machines from Google's infrastructure. Garg and Datta [9] combine test prioritisation with parallel test execution. They use a functional dependency graph to partition the test suites for web applications into prioritised test sets that can be distributed for execution on multiple machines. Gupta et al. [82] present a method for automatic machine configuration for parallel test execution, which targets not only large test suites, but also multiple software configurations.

The main drawback of these approaches is the costs associated with building, maintaining and operating parallel CPU clusters at a large scale [7]. This has led to the exploration of using cloud-based services as a way to reduce the costs associated with building dedicated testing infrastructure. Parveen and Tilley [83] explore this idea by taking into account the characteristics of the SUT and the types of testing performed on the application, stating that in certain situations cloud-computing "can aid in reducing the execution time of large test suites in a cost-effective manner". In [84], they propose a parallel test execution environment for cloud services using the MapReduce programming model [85] and Hadoop [86]. Yu et al. [87] present an elastic Test-as-a-Service platform to automatically cluster, schedule, and manage unit testing, including test generation, test execution and result reporting. More recently, Gambi et al. [88] present a framework for cloud unit testing, targeting Java unit tests, which automatically allocates computational resources and efficiently schedules test execution on them, including in the presence of test dependencies. Despite its advantages, cloud-based test execution might not be suitable for all projects, due to networking and bandwidth challenges, loss of autonomy and security, and potential lack of support for particular features or technologies, on which the SUT is dependent [83]. It could also still be prohibitively expensive for projects with limited budgets and large testing workloads. For these reasons, there is still a need for low-cost efficient test acceleration achievable on local infrastructure.

Another drawback of these approaches are the usability challenges associated with creating and maintaining a parallel test environment, which requires knowledge of testing frameworks and parallel technologies. A survey on test execution parallelisation for open-source projects by Candido et al. [12] found that only 15% of 110 project surveyed used parallel test execution. Among the teams who did not use it, the most common reasons cited are the extra work to organise testing, as well as lack of continuous integration services and unfamiliarity with the underlying technology.

Unlike CPU clusters, GPUs provide large scale parallelism at low cost, but they too pose significant challenges associated with ease of use (Section 1.2). The work in this thesis addresses this issue by presenting an automated approach to leverage GPU parallelism to accelerate test execution.

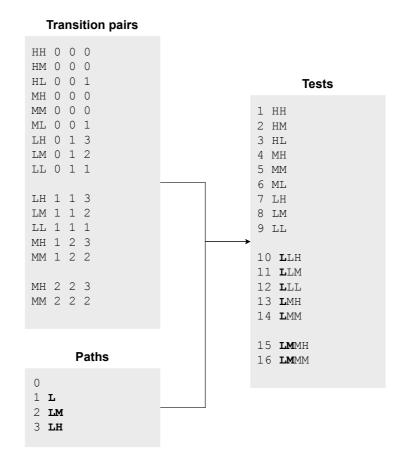

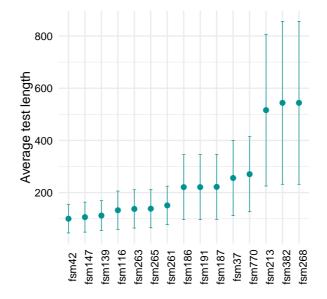

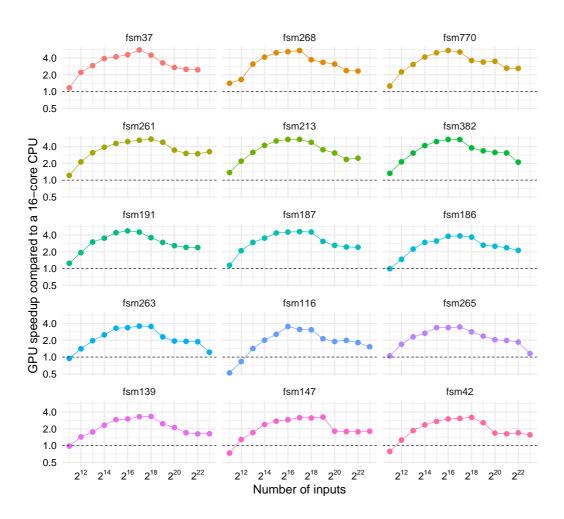

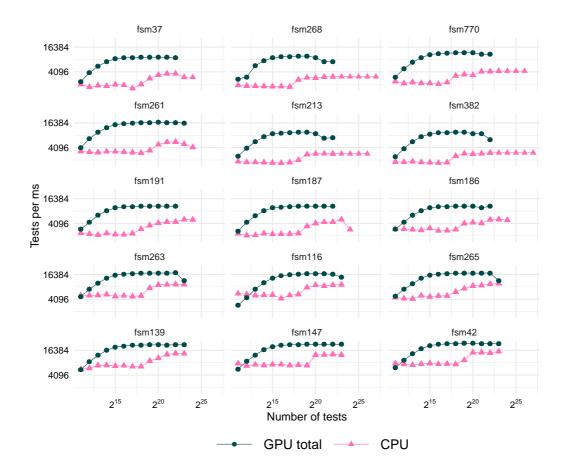

## 3.3 Using GPUs for Software Testing