# International Journal of Electronics and Electical Engineering

Volume 1 | Issue 2 Article 9

October 2012

## **Current Mirror Circuits with Improved Performance**

## Bajrang Bansal

Electronics & Communication Engineering Department Jind Institute of Engineering & Technology, Jind, India, bajrangbnsl@gmail.com

## Prabhat Ranjan

Electronics & Communication Engineering Department Jind Institute of Engineering & Technology, Jind, India, prabhattiet@gmail.com

## Himanshu Kaushik

Electronics & Communication Engineering Department Jind Institute of Engineering & Technology, Jind, India, Himkaushik342@yahoo.co.in

Follow this and additional works at: https://www.interscience.in/ijeee

Part of the Power and Energy Commons

## **Recommended Citation**

Bansal, Bajrang; Ranjan, Prabhat; and Kaushik, Himanshu (2012) "Current Mirror Circuits with Improved Performance," International Journal of Electronics and Electical Engineering: Vol. 1: Iss. 2, Article 9.

DOI: 10.47893/IJEEE.2012.1023

Available at: https://www.interscience.in/ijeee/vol1/iss2/9

This Article is brought to you for free and open access by the Interscience Journals at Interscience Research Network. It has been accepted for inclusion in International Journal of Electronics and Electical Engineering by an authorized editor of Interscience Research Network. For more information, please contact sritampatnaik@gmail.com.

## **Current Mirror Circuits with Improved Performance**

## <sup>1</sup>Bajrang Bansal, <sup>2</sup>Prabhat Ranjan, <sup>3</sup>Himanshu Kaushik

Electronics & Communication Engineering Department Jind Institute of Engineering & Technology Jind, India

Email: <sup>1</sup>bajrangbnsl@gmail.com, <sup>2</sup>prabhattiet@gmail.com, <sup>3</sup>Himkaushik342@yahoo.co.in

Abstract—Current mirrors are core structures for almost all analog mode circuits and are integral part of a signal processing elements like op amps. The performance of analog structures largely depends on their characteristics. In this paper we present some of the current mirror circuits and analyze their performances, so that one can choose a suitable current mirror for a particular application.

#### I. INTRODUCTION

The analog circuits are implemented in the form of standard building blocks, called analog signal processing (ASP) cells [1]. The ASP cells consist of several basic analog circuit structures and may have voltage mode and/or current mode circuit structures. In Current mode circuits (CMCs) input and output signals are currents. Current mirror (CM) is one such structure, which finds use in analog circuit structures. CMs may be used as active load as they offer high impedance. They may also be used as biasing structures as they provide better insensitivity to the variations in power supply and temperature [2].

In this article, some of the CMs with improved performances are presented so that one can choose an appropriate CM for specific applications.

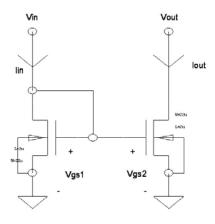

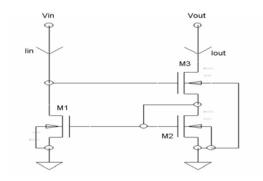

## II. BASIC CURRENT MIRROR

CM is a two terminal structure whose output current at any instant of time is independent of voltage applied across its output terminals (Fig. 1) and depends on the input current. It allows precise copying of the current with no sensitivity to variations in power supply and temperature. The ratio of  $i_{out}$  and  $i_{in}$  is given by the ratio of device dimensions that can be controlled with better

accuracy [3]. CM determines the characteristics of many analog circuits [4]. Following are the performance parameters of a current mirror.

Figure 1. Basic CM Structure

#### **Input-output resistance**

CM should have zero input and infinite output resistance so that the input voltage will not vary with the input currents and the output currents will not depend on the applied output voltage. Output resistance is very important parameter for a current mirror.

## **Output voltage swing**

A CM requires a minimum voltage at the output to ensure that the devices operate in saturation. This voltage is called the output compliance voltage. For a simple current mirror (Fig. 1) minimum voltage required is  $V_{ds2}(sat)$ . This output compliance voltage may be different for different topologies.

## Input linear range

The total input current must be in the range where both transistors (Ml and M2 in Fig. 1) operate saturations.

#### DC balance

The drain source voltage of the mirror transistors MI and M2 (Fig. 1) should be equal.

The error due to the mismatch in drain to source voltages is  $\lambda(V_{ds2}-V_{ds1})$ , where  $\lambda$  is the channel length modulation coefficient.

## **Device matching**

It requires perfect matching of the mirroring transistors Ml and M2 (Fig. 1) for accurate mirroring of the signal current. Current transfer ratio (CTR) is precisely set by the (W/L) ratios.

The study of various CM topologies is necessary so that the circuit designers can choose an appropriate CM for particular application.

## III. CLASSIFICATION OF CM

A CM may be a

- 1. Simple CM

- 2. Standard Cascode CM

- 3. High swing CMs

- 4. Improved Swing CMs

- 5. Wilson CMs

- 6. Regulated Cascode CMs

All CMs are useful and for selecting a particular CM, it requires an in depth knowledge of these CMs.

## A. Simple Current Mirror

Fig. 1 shows the basic structure for a current mirror. It uses the principle that if the gate source potentials of two identical MOS transistors are equal, the channel current should be equal. For a good current source, the MOSFETs should operate in saturation region.

For simple CM the minimum V<sub>in</sub> value is given as

$$\mathbf{v}_{\mathrm{in}} = \mathbf{v}_{\mathrm{t}} + \sqrt{\frac{2\mathbf{i}_{\mathrm{in}}}{\beta_{\mathrm{i}}}} \tag{1.1}$$

The output compliance voltage is given as

$$v_{out} = \sqrt{\frac{2i_{in}}{\beta_i}}$$

(1.2)

The output resistance is given as

$$\mathbf{r}_{\text{out}} = \mathbf{r}_{\text{ds2}} \tag{1.3}$$

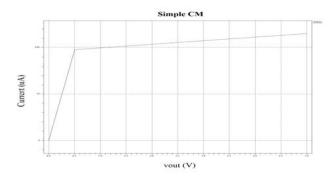

Output characteristic for this structure is shown in Fig. 2. It can be seen that the output current is not constant in saturation mode as it is varying with change in output voltage. This is because of its low output resistance ( $r_{ds2}$ ). This low output resistance is a major drawback of this CM. The ratio of mirrored ( $i_{out}$ ) to the input current  $i_{in}$  is [5]

$$\frac{\dot{\mathbf{i}}_{\text{out}}}{\dot{\mathbf{i}}_{\text{in}}} = \frac{\mathbf{W}_2 \mathbf{l}_1}{\mathbf{l}_2 \mathbf{W}_1} \tag{1.4}$$

Bigger size transistors achieve higher output resistance which is very much desired for a good current mirror. But

there will be higher output capacitance which degrades the frequency response of a CM.

Figure 2. Output characteristics for simple CM Standard Cascode CM

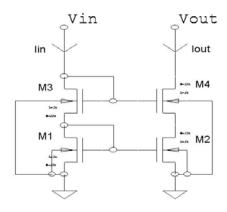

#### B. Standard Cascode Current Mirror

The small signal output resistance is a good measure of the perfection of the current mirror. Higher performance current mirrors will attempt to increase the value of r<sub>out</sub>. The approach used to increase the output resistance is to use cascode structure. Standard cascode CM shown in Fig. 3 [6] is a good choice for increasing output resistance.

Figure 3. Standard Cascode CM Structure

The minimum input voltage  $v_{\text{in}}$  for this structure is given as

$$v_{in} = 2v_t + 2\sqrt{\frac{2i_{in}}{\beta_i}}$$

(1.5)

This value is double of the input compliance voltage for a conventional CM

Output compliance voltage is given as

$$v_{\text{out}} = v_{\text{t}} + 2\sqrt{\frac{2i_{\text{in}}}{\beta_{\text{i}}}}$$

(1.6)

This is greater than the minimum voltage required for a conventional cascode, by an amount of  $v_t$ , threshold voltage of a transistor.

The output resistance is given as [3]

$$r_{\text{out}} = r_{\text{ds2}} + r_{\text{ds4}} + g_{\text{m4}} r_{\text{ds2}} r_{\text{ds4}} (1 + \eta_4)$$

(1.7)

This can be approximated as

$$r_{out} = g_{m4} r_{ds2} r_{ds4}$$

(1.8)

Which is greater than the output resistance of simple CM, by gain of a transistor ( $g_m r_{ds}$ )

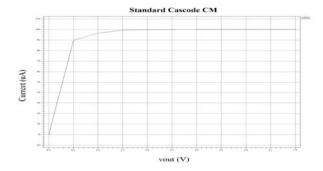

Output characteristic of this structure is shown in Fig. 4.

Figure 4. Output characteristics for Standard Cascode CM

As shown in Fig. 4, the output compliance voltage is near about 1.63V. Also in saturation mode output current is not varying with output voltage. This advantage is because of its higher output resistance. The disadvantage of this structure is its higher input and output compliance voltage.

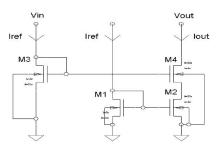

#### C. High Swing Cascode Current Mirror

The disadvantage of standard cascode current mirror is its higher input and output compliance voltage. This high swing cascode topology shown in Fig. 5 [3] is better alternate as it provides the same output resistance as of standard cascode but it provides low input and output compliance voltage in comparison to standard cascode structure.

Figure 5. High Swing Cascode CM Structure

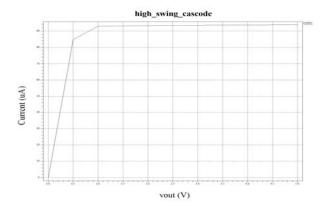

The output characteristic for this structure is shown in Fig. 6. As shown in figure, the output compliance voltage is near about 1.5V which is lower than the value for standard cascode CM. So this is a better topology than standard cascode CM.

Figure 6. Output characteristics for high swing Cascode CM

In Fig. 5 the W/L ratio of transistor M3 is chosen one fourth in respect to other transistors. That causes input compliance voltage as

$$v_{in} = v_t + 2\sqrt{\frac{2i_{ref}}{\beta_i}}$$

(1.9)

Then output compliance voltage becomes

$$v_{out} = 2\sqrt{\frac{2i_{ref}}{\beta_i}}$$

(1.10)

This is same as for conventional cascode structure.

The output resistance for this structure is same as in standard cascode structure. That is

$$r_{out} = g_{m4} r_{ds4} r_{ds2}$$

(1.11)

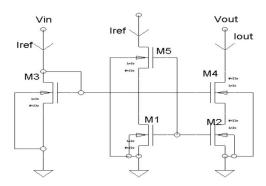

The problem with this structure is that the  $V_{ds}$  of M1 and M2 are not equal. So the current  $i_{out}$  will not be an accurate replica of  $i_{ref}$  due to channel length modulation. If exact mirroring of  $i_{out}$  is desired with  $i_{ref}$ , then a slight modification of Fig. 5 will minimize this problem. The required structure is shown in Fig. 7. An additional transistor M5 is added in series with M1 so as to make the drain voltages of M1 and M2 to be equal, thus removing any error due to channel length modulation.

Figure 7. Improved high swing Cascode CM

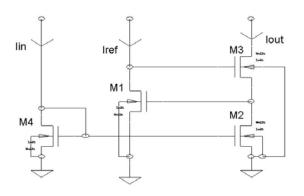

## D. Wilson Current Mirror

This is another type of current mirror. This circuit is an n-channel implementation of the well known Wilson current mirror [7].

Figure 8. Wilson CM

As shown in Fig. 8, the output resistance of the Wilson current mirror is increased through the use of negative current feedback [8]. This structure has large input and

output compliance voltage. The output resistance for this structure is given as

The output resistance is seen to be comparable with that of standard cascode current mirror.

The input compliance voltage is given as

$$v_{in} = 2v_t + \sqrt{\frac{2i_{out}}{\beta_2}} + \sqrt{\frac{2i_{out}}{\beta_3}}$$

(1.13)

The output compliance voltage is given as

$$v_{out} = v_t + \sqrt{\frac{2i_{out}}{\beta_2}} + \sqrt{\frac{2i_{out}}{\beta_3}}$$

(1.14)

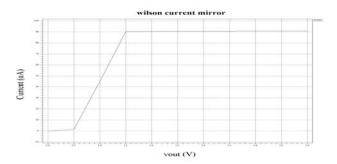

The output characteristic for this structure is shown in Fig. 9.

Figure 9. Output characteristics for Wilson CM

As shown in this Fig. 9, the output compliance voltage is approximated 1.63V. Also in saturation region its output current is not varying with output voltage just because of its higher output resistance. The advantage of Wilson CM is its higher output resistance. Its main drawback is the asymmetrical biasing, which causes large DC matching error. This can be removed by adding one transistor in series with transistor M1.

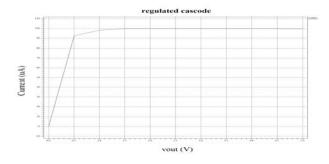

## E. Regulated Cascode Current Mirror

As explained earlier, the well desired property of good current mirror is its high output resistance. An improvement in Wilson CM can be made if somehow its output resistance is increased. This can be achieved by

using negative current feedback circuit. The resulted circuit is shown in Fig. 10 [9].

Figure 10. Regulated Cascode CM

The output compliance voltage for this structure is given as

$$v_{out} = \sqrt{\frac{2i_{out}}{\beta_2}} + \sqrt{\frac{2i_{out}}{\beta_3}}$$

(1.15)

The output resistance for this structure is given as  $r_{out} \cong r_{ds2}g_{m3}r_{ds3}g_{m1}r_{ds1}$  (1.16)

So this structure achieves an output resistance on the order of  $\ g_m^{\ 2} r_{ds}^{\ 3}$

The output characteristic of this structure is shown in Fig. 11.

Figure 11. Output characteristics for Regulated Cascode CM

As can be seen from this Fig. 11, output compliance voltage for this structure is 1.5V. Also in saturation mode, output current is constant as it should be ideally.

## IV. SIMULATION RESULTS

The circuits have been simulated using MCNC 1.25um CMOS process level 2 spice parameters. The purpose was to obtain higher output resistance and low output compliance voltage. The performance comparison of various CM structures is shown in table I.

TABLE I. COMPARISON OF VARIOUS CM STRUCTURES

| Character istics                    | Simpl<br>e CM | Standar<br>Cascodo<br>CM | 0          | Wilso<br>n CM | Regulate<br>Cascode<br>CM |

|-------------------------------------|---------------|--------------------------|------------|---------------|---------------------------|

| Input<br>Complianc<br>e<br>Voltage  | Low           | High                     | Mediu<br>m | High          | High                      |

| Output<br>Complianc<br>e<br>Voltage | Low           | High                     | Mediu<br>m | High          | High                      |

| Output<br>Resistance                | Low           | High                     | High       | High          | Highes<br>t               |

| Area (No. of Transistor s)          | 2             | 4                        | 4          | 3             | 4                         |

As output resistance is very important performance parameter of a CM, table II summarizes this parameter for different CM structures.

TABLE II. OUTPUT RESISTANCES OF VARIOUS CM

| Current Mirror        | Output Resistance (r <sub>out</sub> )                                                                                                                              |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Simple CM             | $r_{ds2}$                                                                                                                                                          |  |  |

| Standard Cascode CM   | $r_{\!_{ds2}}\!+\!r_{\!_{ds4}}\!+\!g_{\!_{m4}}r_{\!_{ds2}}r_{\!_{ds4}}(1\!+\!\eta_4)$                                                                              |  |  |

| High Swing Cascode CM | $g_{m4}r_{ds4}r_{ds2}$                                                                                                                                             |  |  |

| Wilson CM             | $r_{ds3} + r_{ds2} \left( \frac{1 + r_{ds3} g_{m3} (1 + \eta_3)}{+ g_{m2} r_{ds1} g_{m3} r_{ds3}} - \frac{1 + g_{m2} r_{ds2} r_{ds2}}{1 + g_{m2} r_{ds2}} \right)$ |  |  |

Regulated Cascode CM  $r_{ds2}g_{m3}r_{ds3}g_{m1}r_{ds1}$

#### V. CONCLUSION

In this article, various possible CM structures are presented along with their merits and demerits. Any one of them can be selected as per requirement. The most important performance parameters for a CM are its compliance voltages and output resistance. The most frequently used CMs have been considered for comparison of the performance parameters. They are simple CM, standard cascode CM, high swing CM, Wilson CM, Regulated cascode CM. From comparison of various parameters of these structures, it can be seen that Regulated cascode CM structure is best suited structure, as it provides medium input and output compliance voltage and very high output resistance.

#### REFERENCES

- [1] M. Ismail and T. Fiez, "Analog VLSI Signal and Information Processing," New York: McGraw-Hill 1994.

- [2] B. Razavi, "Design of Analog CMOS Integrated Circuits," New York: Tata McGraw-Hill 2002.

- [3] P. E. Allen and D. R. Holberg, "CMOS analog circuit design," New York: Oxford University Press, 2002.

- [4] S. S. Rajput and S. S. Jamuar, "A high performance current mirror for low voltage designs," Proc. APCCAS-2000/IEEE, Tianjin pp. 170-173, China, Dec 2000.

- [5] I. M. Filanovsky, "Current Mirrors with Limiting of Linear Dynamic Range," University of Alberta, Edmonton, Alberta, Canada, T6G 2El.

- [9] E. SACKINGER and W. GUGGENBUHL, "A versatile building block: the CMOS differential difference amplifier," IEEE J., 1987, SC-22, (2), pp. 287-294.

- [6] D.A. Johns and K. Martin, "Analog Integrated Circuit Design," John Wiley & Sons, Inc., New York, 1997.

- [7] G. R. Wilson, "A Monolithic Junction FET-npn Operational Amplifier," IEEE J. Solid-State Circuits, Vol. SC-3, No. 5, pp. 341-348, Dec. 1968.

- [8] Z. Wang, "Analytical determination of output resistance and DC matching errors in MOS current mirrors," IEE PROCEEDINGS, Vol. 137, Pt. G, No. 5, OCTOBER 1990.