Mississippi State University Scholars Junction

Theses and Dissertations

Theses and Dissertations

12-14-2001

## **Global Synchronization of Asynchronous Computing Systems**

**Richard Neil Barnes**

Follow this and additional works at: https://scholarsjunction.msstate.edu/td

#### **Recommended Citation**

Barnes, Richard Neil, "Global Synchronization of Asynchronous Computing Systems" (2001). *Theses and Dissertations*. 2425. https://scholarsjunction.msstate.edu/td/2425

This Graduate Thesis - Open Access is brought to you for free and open access by the Theses and Dissertations at Scholars Junction. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Scholars Junction. For more information, please contact scholcomm@msstate.libanswers.com.

### GLOBAL SYNCHRONIZATION OF ASYNCHRONOUS

### COMPUTING SYSTEMS

By

Richard Neil Barnes II

A Thesis Submitted to the Faculty of Mississippi State University in Partial Fulfillment of the Requirements for the Degree of Master of Science in Computer Engineering in the Department of Electrical and Computer Engineering

Mississippi State, Mississippi

December 2001

Copyright by

Richard Neil Barnes II

2001

### GLOBAL SYNCHRONIZATION OF ASYNCHRONOUS

### COMPUTING SYSTEMS

By

Richard Neil Barnes II

Approved:

James C. Harden Graduate Coordinator of the Department of Computer Engineering (Director of Thesis)

Donna S. Reese Professor of Computer Science (Committee Member) Nicholas H. Younan Professor of Electrical Engineering (Committee Member)

A. Wayne Bennett Dean of Engineering Name: Richard Neil Barnes II

Date of Degree: December 14, 2001

Institution: Mississippi State University

Major Field: Computer Engineering

Major Professor: Dr. James C. Harden

# Title of Study: GLOBAL SYNCHRONIZATION OF ASYNCHRONOUS COMPUTING SYSTEMS

Pages in Study: 93

Candidate for Degree of Master of Science

The MSU ERC UltraScope system consists of a distributed computing system, custom PCI cards, GPS receivers, and a re-radiation system. The UltraScope system allows precision timestamping of events in a distributed application on a system where the CPU and PCI clocks are phase-locked. The goal of this research is to expand the UltraScope system, using software routines and minimal hardware modifications, to allow precision timestamping of events on an asynchronous distributed system.

The timestamp process is similar to the Network Time Protocol (NTP) in that it uses a series of timestamps to improve precision. As expected, the precision is less accurate on an asynchronous system than on a synchronous system. Results show that the precision is improved using this sequence of timestamps, and the major error component is due to operating system delays. The errors associated with this timestamping process are characterized using a synchronous system as a baseline.

## ACKNOWLEDGMENTS

The author extends his sincere appreciation to the members of his graduate committee, Dr. Jim Harden, Dr. Donna Reese, and Dr. Nicholas Younan, for all the advice and help that they have provided me throughout my graduate studies.

The author would also like to acknowledge Dr. Donna Reese, Greg Henley, and See-kit Lam for their contributions towards the software, operating system considerations, and general debugging.

## TABLE OF CONTENTS

## Page

| ACKNOW    | LEDGN                                                                                                                   | IENTS                                                                                                                                                                             | ii               |

|-----------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| LIST OF T | ABLES                                                                                                                   |                                                                                                                                                                                   | v                |

| LIST OF F | FIGURES                                                                                                                 | 5                                                                                                                                                                                 | vi               |

| CHAPTER   | R                                                                                                                       |                                                                                                                                                                                   |                  |

| I.        | INTRO                                                                                                                   | DUCTION                                                                                                                                                                           | 1                |

|           | 1.2<br>1.3                                                                                                              | The UltraScope system<br>Timestamping on an asynchronous system<br>Error sources in the asynchronous timestamp process<br>Research scope                                          | 1<br>2<br>3<br>3 |

| II.       | LITERA                                                                                                                  | ATURE REVIEW                                                                                                                                                                      | 5                |

|           | 2.2<br>2.3<br>2.4<br>2.5<br>1<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 | Error sources<br>2.5.1 GPS error sources<br>2.5.2 Quartz Clock oscillator error sources<br>2.5.3 Clock synchronization error sources<br>2.5.4 Communication network error sources |                  |

| III.      |                                                                                                                         | Y OF OPERATION                                                                                                                                                                    | 17<br>17         |

|           | 3.2 S                                                                                                                   | Synchronous operation                                                                                                                                                             | 18<br>18<br>20   |

|           | -                                                                                                                       | Operating synchronous UltraScope on an asynchronous system                                                                                                                        |                  |

|        | 3.4<br>3.5                             | Modifications required for asynchronous operation3.4.1Hardware3.4.2Software3.4.3PCI transaction correctionOverview of error sources          | 23<br>24<br>25       |

|--------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| IV.    | RESU                                   | LTS                                                                                                                                          | 34                   |

|        | 4.1<br>4.2<br>4.3<br>4.4<br>4.5        | Test and verification procedure<br>PCI bus idle<br>PCI bus busy<br>PCI bus with arbitration<br>Error characterization                        | 36<br>38<br>40       |

| V.     | CONC                                   | LUSIONS                                                                                                                                      | 47                   |

|        | 5.1<br>5.2<br>5.3                      | Timestamp precision<br>Error sources and their contributions<br>Future Work                                                                  | 49                   |

| REFERE | NCES                                   |                                                                                                                                              | 54                   |

| APPEND | IX                                     |                                                                                                                                              |                      |

| А.     | TEST                                   | PLAN                                                                                                                                         | 56                   |

|        | A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6 | Re-radiation system<br>Physical indictors<br>GPS functionality<br>PAB functionality<br>System parameters<br>Data collection and analysis     | 57<br>58<br>58<br>59 |

| B.     | PAB L                                  | OGIC MODIFICATIONS                                                                                                                           | 63                   |

|        | B.1<br>B.2                             | Modifications to allow software access to the PAB counter<br>Full VHDL source code for the PAB registers                                     |                      |

| C.     | DATA                                   | COLLECTION SOFTWARE                                                                                                                          | 70                   |

|        | C.1<br>C.2<br>C.3                      | Full source code listing for <i>cpu_tlt</i><br>Full source code listing for <i>timestamp</i><br>Full source code listing for <i>time_seq</i> | 74                   |

| D.     | DATA                                   | ANALYSIS SOFTWARE                                                                                                                            | 88                   |

|        | D.1<br>D.2                             | Full source code listing for <i>time_analysis.m</i><br>Full source code listing for <i>pci_sim.m</i>                                         |                      |

## LIST OF TABLES

| TABLE                                                                 | Page |

|-----------------------------------------------------------------------|------|

| 3.1 Error sources and their contributions to the overall error        | 31   |

| 5.1 Each test case and the average precision of the timestamps        | 48   |

| 5.2 List of error sources and their contribution to the overall error | 50   |

## LIST OF FIGURES

| FIGURE                                                                      | Page |

|-----------------------------------------------------------------------------|------|

| 2.1 NTP timestamp sequence                                                  | 10   |

| 2.2 The sawtooth pattern present in the GPS 1PPS signal                     | 12   |

| 3.1 The hardware block diagram for computing the PPS"                       | 20   |

| 3.2 The sequence of timestamps required on an asynchronous system           | 25   |

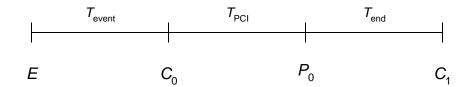

| 3.3 Regions of delays in a timestamp sequence                               | 26   |

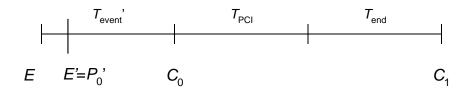

| 3.4 The timestamp sequence after correction                                 | 28   |

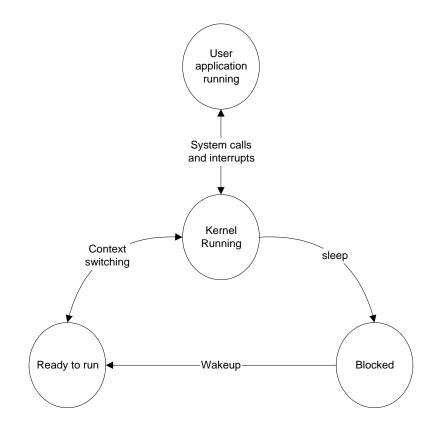

| 3.5 The process states and transitions possible when accessing the PCI bus  | 33   |

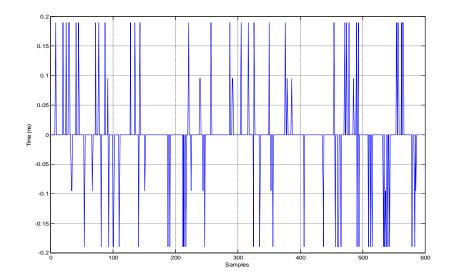

| 3.6 Measured error from using an approximation of the clock frequency ratio | 33   |

| 4.1 Timestamp data when the PCI bus is idle                                 | 37   |

| 4.2 Timestamp data when the PCI bus is busy                                 | 39   |

| 4.3 Timestamp data without arbitration                                      | 43   |

| 4.4 Timestamp data with bus arbitration                                     | 43   |

| 4.5 Distribution of error contributed by the operating system               | 45   |

| B.1 The modified PAB counter schematics                                     | 64   |

## CHAPTER I

## **INTRODUCTION**

Monitoring physically distributed computing systems require the ability to create precision timestamps based on events that occur during an application. Precise timestamps are used in a variety of applications including database systems, communications, distributed system performance evaluation, and parallel application debugging. There are a wide range of implementation schemes for precision timestamping that involve both hardware and software solutions. However, a hardware-only solution is usually expensive and may perturb the system when collecting timestamp data, while software-only solutions tend to have poor timestamp precision. A hybrid solution of low-cost hardware and software routines can provide high precision timestamps. The MSU ERC UltraScope is an example of such a hybrid system that allows precision timestamping of events in distributed and parallel applications [1].

### **1.1** The UltraScope system

The UltraScope system consists of a distributed computing system equipped with custom PCI boards and Global Positioning Satellite (GPS) receivers. Embedded in the parallel application are software probes that trigger timestamps for application events. The custom, PCI-bus-based Probe Acquisition Board (PAB) allows a software event to be correlated to Universal Coordinated Time (UTC) time. Using the GPS receiver's one-pulse-per-second (1PPS) signal allows the PAB board to resolve a timestamp into UTC time. GPS system timing is precise to within approximately ± 15 ns [2]. A high-precision link between the CPU and PAB timestamps is facilitated by PC-based hardware where the CPU and PCI clocks are synchronized with respect to each other. With the popularity of the Internet, techniques have been developed for time synchronization of physically separated computers. The Network Time Protocol (NTP) is a formal standard by which computers are time synchronized. By using similar techniques, the UltraScope system can be expanded to systems where the CPU and PCI clocks are unsynchronized.

#### **1.2** Timestamping on an asynchronous system

A limitation of the current implementation of the UltraScope system is the CPU and PCI clocks must be synchronous with respect to each other. Only a subset of computing systems, such as Intel PC's, currently has this characteristic. Furthermore, there is no guarantee designs will continue to be synchronous in the future. Software routines based on NTP can be used to estimate the system characteristics, such as the ratio of the CPU clock frequency to the PCI bus clock frequency and the time offset between the host processor and the PAB board. From these characteristics, the delays associated with accessing the PAB board, such as the PCI bus latency, can be corrected. When these errors are accounted for, the estimated timestamp will have a high correlation to UTC time. Naturally, there will be some error associated with the timestamps that is not present in the synchronous case.

#### **1.3** Error sources in the asynchronous timestamp process

Additional errors in the timestamping process are due to delays in creating the initial timestamp, the PCI bus latency, the operating system's activities, and translating the timestamp into UTC time. The system characteristics to be estimated include the ratio of the CPU clock frequency to the PCI bus clock frequency and the time offset between the times represented by the processor and the PAB board. Errors in these calculations translate into a loss of precision in the final timestamp value. By using the asynchronous timestamping methods described in Section 1.2 on a synchronous system, each of these errors can be characterized, which will allow the determination of the specific error contributions incurred by the asynchronous timestamping methods. Additionally, this procedure validates the correctness of the asynchronous methods.

### **1.4** Research scope

The goal of this research is to extend the UltraScope system using software routines and minimal hardware modifications to precisely generate and resolve timestamps to UTC time on asynchronous, distributed computing systems and to characterize any remaining sources of error. The approach taken is to modify the timestamping process so that it is similar to NTP. To timestamp an event, timestamps must be created both at the host processor and at the PAB board. The PAB hardware must be modified so that an accurate local timestamp can be created by the software. Software routines are needed to determine the system characteristics, perform the timestamping process, and to correct for the PCI bus delays that are a result of accessing the PAB board.

This thesis presents a review of previous research in the area of precision timestamping, the theory and design of the hardware modifications and software routines, the results of this research, and the conclusions made from these results.

## CHAPTER II

## LITERATURE REVIEW

The previous research in precision timestamping presented here covers several areas: applications of precision timestamping, timestamp ordering issues in distributed systems, methods of clock synchronization, accuracy of the GPS signals, and the error sources involved in timestamping.

### 2.1 Applications of precision timestamping

There are many different applications of precision timestamping from e-commerce to communications systems. For e-commerce systems, many issues, such as ownership of an item, monetary transactions, and various other legal issues would benefit from precise timestamps that correspond to a universal time [3]. If a client and server have two different times, it is possible that fraud or even theft of a product or service could occur [3].

Distributed databases also benefit from precision timestamps that correspond to a universal time. Transactions to the database can occur from several different clients at once. Without precise timestamps synchronized to a global timebase, the database would not know the correct order in which to commit the transactions [4]. Some databases also use the timestamps as a method of obtaining locks on the data so that it can be modified exclusively by a client.

Digital communications systems are another example of system that can use precision timestamping to obtain an estimate of the quality of service over the network. Communication networks can be operating over a large distance with a few or many clients. In some cases, the clients may be devices on the network that act as slaves such as on an interface bus or they may be computers attached to a wide area network. Precision timestamping allows for distributed communication between the clients which will allow it to operate as a large metasystem [1].

Distributed, parallel applications are difficult to debug. In addition, estimating the performance of the algorithm is problematic. Each processing node is running code with no synchronization to other processors except through explicit synchronization calls. Using small triggers embedded in the software that generate timestamps can create a trace of the events on a processing node. If these events are precisely synchronized to a global time, then the events on all the nodes can be merged into a single trace of events [5]. This merged event trace can then be used to debug errors in the code or to determine exactly how long a section of code required to execute.

#### 2.2 Timestamping

Timestamping is used to resolve the order of system events, even when the system is distributed or characterized by non-deterministic delays. A timestamp is generated by an event trigger and can provide an absolute or relative indication of the time at which the event occurred.

The timestamp for a sequence of events on a system can be chosen to indicate one of the following: time before any of the sequence of events, the time immediately before a specific event, the time immediately after a specific event, or the time after all events have occurred. The time that a timestamp represents is chosen by the application [4]. For example, timestamps can be used as concurrency controls to create locks in the application [4]. The synchronization of the time references is important. Having an unsynchronized time reference can cause the timestamps to appear to have been received in the reverse order from which they were generated [6].

Timestamps can also act as events that trigger other events in a system. For this type of event triggering, especially in a distributed system, it is important that the order of the timestamps is preserved across all communication. Using timestamps with a global time reference is an obvious way to generate events and messages that are suitable for event-based computing [7]. Using a global time reference may not always be feasible, and not every application requires global timestamping or high precision. Some applications may only need the timestamp to be resolved to a relative time.

#### 2.3 Clock synchronization

Clock synchronization is required where there are two or more clocks in the system that are generated from different sources. These clocks can be on the same local

system or physically distributed. Clock synchronization attempts to provide a way these two separate clocks can be deterministically related to each other. For clock oscillators, this can be a matter of a phase lock between the two oscillators. For a clock-generated timestamp based on a counter, synchronization adjusts the rate at which the counter increments to achieve synchronization.

#### 2.3.1 Types of algorithms for clock synchronization

Much research has been done in the area of clock synchronization. The two major types of synchronization systems are hardware algorithms and network algorithms [8]. Hardware algorithms require a dedicated set of communication links through which the clocks can be broadcast. This method is expensive, but the communication delays are known and deterministic in the dedicated network [8]. Network algorithms share the communication links with the rest of the system. This method is cheaper than the hardware methods, but it introduces uncertainties in the communication delays. This problem is usually solved by sending timestamp messages back and forth between the two clock sources. The downside of this technique is that these messages increase the load on the network [8].

#### 2.3.2 Probabilistic clock synchronization

Many of the network algorithms are probabilistic in nature. Unlike deterministic hardware solutions, these algorithms use timestamp messages to estimate the statistical properties of the communication delays and try to remove these delays from the system.

The primary statistics that are estimated are the roundtrip delay between the timestamp messages, the time offset between the clocks, and the amount of drift between the two clocks. Research has been conducted to find better estimates of these parameters and better ways to implement synchronization messages.

There are many different schemes for network clock synchronization. One probabilistic scheme uses wavelets. The wavelet-based approach is able to completely filter out any pattern-dependent jitter [9]. Another scheme is to continuously run the synchronization algorithm. This way the network load due to the synchronization is constant rather than bursty [8]. Other methods include the Time Transmission Protocol [10], the time protocol, and the Internet Control Message Protocol (ICMP) timestamp messages [11]. The most popular of all the clock synchronization protocols is NTP.

#### 2.3.3 NTP

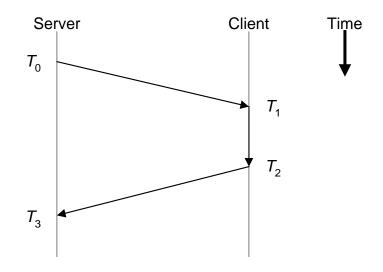

The NTP protocol is based on the time protocol and ICMP timestamp messages [11]. There are over 100,000 NTP servers and clients on the Internet [12]. NTP uses a series of timestamps as shown in Fig. 2.1 [13]. In the NTP protocol, a series of these timestamp exchanges are made between the client and server. The roundtrip delay, time offset between the clocks, relative clock drift, and the most accurate time server are determined. The results are passed through a clock filter and then used to update the local clock oscillator. The amount of error in the synchronization determines the length of the interval the algorithm waits before exchanging another series of timestamps [13]. NTP is able to synchronize clients to a time server over the Internet to within 10 ms [12].

Fig. 2.1 NTP timestamp sequence

#### 2.4 GPS

The GPS system consists of a constellation of 24 satellites orbiting the earth. Each satellite contains an onboard atomic clock that is used to create a signal that is broadcast to earth. The atomic clock is synchronized to UTC time [14]. The GPS receivers receive the signals broadcast by the satellites. The receiver uses these signals to compute its current position. The current UTC time can then be solved for using the positional equations contained in the receivers [14]. When the position of the receiver is accurately known, a more accurate UTC time can be computed. Until May 2, 2000, the government used a process called selective availability to intentionally degrade the performance of the civilian GPS receivers [2], making this time less accurate.

The GPS receiver used in the UltraScope system is the Motorola UT Oncore receiver. When selective availability was active, the precision of the 1PPS signal from this receiver was  $\pm$  50 ns (1-sigma) when the current position of the receiver was known [15]. Now that selective availability is disabled, the precision of the 1PPS signal has been measured to be  $\pm$  15 ns when the current position of the receiver is known [2]. For timing purposes, the GPS 1PPS signal has excellent long-term stability, but poor short-term stability.

#### 2.5 Error sources

There are many different error sources involved in clock synchronization and precision timestamping. In clock synchronization, there are errors inherent in the clock characterization, the synchronization of the clocks, the communications network, and the synchronization algorithms. In precision timestamping, the major sources of error are the generation of the timestamp and the communication network.

#### 2.5.1 GPS error sources

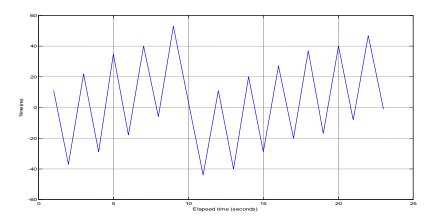

The major errors in the GPS system are the receiver error and the precision of the 1PPS signal. The receiver error consists of positional error, atmospheric error, multipath error, and local oscillator error. The positional error is due to not knowing exactly where the receiver is located. As mentioned earlier, the UTC time is determined by solving the positional equations in the receiver. If the position is not exactly known, there will be error introduced into the solution of the equations. This error is reduced by telling the receiver its precise location [14]. Atmospheric error is due to the change in the speed of the satellite signals when the signals penetrate the earth's atmosphere. The multipath error is due to the signal reflecting off surfaces and delaying its time of arrival at the receiver. Multipath error can also occur when both the GPS signal and a delayed version of that signal reach the receiver. If the reflected, delayed signal is strong enough, it could be interpreted by the receiver as the true signal rather than noise. Local oscillator error is due to the asynchronous relationship between the GPS signals and the local clock oscillator. The result of this error is a sawtooth pattern, shown in Fig. 2.2 [2]. The sawtooth pattern results from underestimating or overestimating the actual beginning of the 1PPS signal.

Fig. 2.2 The sawtooth pattern present in the GPS 1PPS signal

The precision of the 1PPS signal is within 300 ns when selective availability is active and the receiver is not told its current position. When the receiver has a known position and selective availability is active, the precision increases to  $\pm$  50 ns [14]. Measurements have been made using the Motorola UT Oncore receiver now that selective availability has been disabled. These measurements indicate that the precision of the 1PPS is now  $\pm$  15 ns when the receiver has a known position [2].

#### 2.5.2 Quartz Clock oscillator error sources

Quartz oscillators are commonly employed and in general have good short-term stability, but poor long-term stability. An oscillator's error comes from two major factors: aging of the crystal and temperature variations. A quartz crystal oscillator will typically drift up to 5 parts in  $10^8$  per week due to aging [2]. Crystals also experience temperature instability. The amount of instability caused by temperature varies by the type of crystal and the cut of the crystal. The temperature stability of a crystal is usually a cubic function of temperature that varies from  $\pm$  10 parts per million (ppm) to  $\pm$  100 ppm [2].

#### 2.5.3 Clock synchronization error sources

Clock synchronization errors are due to mismatch in the two clocks and the communications network. Clock synchronization has several parameters to describe the synchronized clocks: time offset, frequency offset, and relative clock drift. The time offset is due to the clocks starting at different instants in time. The frequency offset is

due to the difference in frequencies between the two clocks and determines the relative rate at which one clock increments with respect to the other clock. The relative clock drift is an indication of variation in clock synchronization over time and can be caused by not being able to correct the frequency offset between the two clocks due to temperature or crystal aging. The frequency offset and relative clock drift can be corrected by phase locking one clock oscillator to the other. The time offset can be corrected by adjusting the frequency of the clock oscillator until the time offset is reduced.

#### 2.5.4 Communication network error sources

The communication network provides additional errors when the synchronized clocks are physically distributed. The roundtrip delay, the possibility of receiving timestamp messages out-of-order, and network traffic can affect the synchronization process. In many synchronization techniques, the delay is assumed to be symmetric between the source and destination when computing the roundtrip delay. Checkpoints have to be inserted in to the synchronization algorithms to insure that the timestamps are operated on in order. Using out-of-order timestamps can cause erroneous results when computing the roundtrip delay, time offset, etc.

#### 2.5.5 Timestamp error sources

Timestamp errors are caused by the generation of the timestamp itself and the communication network. The error in generation of timestamps can be caused by delays in reading the timebase of the system or even in the software itself. Reading of the local

timebase can be delayed by the operating system and the low-level processor instructions needed to access it. An operating system manages many different processes including itself. Significant delays can occur if the allocated time for the process requesting the timestamp expires as it initiates the request of the timestamp. Smaller delays are also caused by the general overhead present in the operating system. Because of the speed of most processors compared to the memory system, a large delay can occur if the instructions to read the local timebase have to be loaded into cache. This delay can also be quite small if the instructions are already located in the instruction cache of the processor. The processor can also delay the reading of the timebase due to the out-of-order execution found in most of the modern processors. For the timestamp to be completely accurate when indicating the order of events, the processor's instruction pipeline should be flushed. The flushing of the pipeline causes a non-deterministic delay that depends on how many instructions were loaded into the pipeline ahead of the timestamp instruction. This delay can be reduced by not flushing the pipeline. However, there will be no way to guarantee the order of events in this case.

The magnitude of these errors is not the only important characteristic. The variability of the timestamp errors can cause problems as well. If an error source has a low variability, this error can be corrected by shifting the timestamp in time. The error is more difficult to correct when a high variability error source is present. The accuracy of the timestamp is reduced since the accuracy will vary by the same amount as the error sources.

In conclusion, high-precision timestamps have many different uses from database systems to communications systems. There are many different error sources in a timestamp including the creation of the timestamp and, in the case of NTP, transmitting a timestamp across a widely distributed network. By using technologies such as GPS and NTP, these errors can be reduced resulting in a more precise timestamp. A combination of hardware and software can yield even better precision timestamps at a relatively low cost compared to strictly hardware-based systems.

## CHAPTER III

## THEORY OF OPERATION

This chapter discusses the differences between synchronous and asynchronous computing systems. There are different requirements for timestamping on each system. These requirements are reflected in the hardware and software components of the UltraScope. This section covers the fundamental differences between these two types of computing systems, the hardware and software components of the UltraScope for each system, and an overview of the source of errors incurred on an asynchronous system.

#### **3.1** Synchronous and asynchronous computing systems

For the purpose of this work, a synchronous computing system is a system that has a fixed relationship between the clock signal for the processor and the clock signal for the PCI bus [1]. This fixed relationship is usually in the form of phase-locked signals. The PCI bus and the processor have different clock frequencies, but the ratio between the processor clock frequency and the PCI bus frequency is fixed and deterministic. Examples of synchronous systems include many of the current Intel-based PC's.

On an asynchronous system, the clock frequency ratio is not a deterministic value. This can be due to having two non-phase-locked clock signals or by having a method that maintains a phase-lock only periodically. Examples of asynchronous systems include many Sun Microsystem workstations and servers, such as the UltraSparc 10 workstation and the Enterprise 450 server.

#### **3.2** Synchronous operation

To create a timestamp, the synchronous UltraScope must establish a relationship between the event to be timestamped and the time at which that event occurred. By using GPS, the time of a timestamp can be expressed as UTC time, a precise global time reference suitable for use in widely distributed systems. The function of the PAB board is to create a relationship between the event and UTC time [1].

There are three components necessary to establish this correlation: the re-radiation system, the PAB hardware, and the software routines to timestamp an event. The re-radiation system allows the GPS receivers to receive the GPS transmissions without requiring direct line-of-sight with the GPS satellites. The PAB hardware correlates the software event to UTC time. The software routines are called by the distributed application to initiate the timestamping of an event.

#### 3.2.1 Hardware

The hardware components of the synchronous UltraScope system are the re-radiation system and the PCI-based PAB board. The PAB board hardware consists of a GPS receiver, a temperature sensor, an FPGA, and 512KB of onboard memory. The FPGA on the PAB board is divided into five functional blocks: PCI, GPS, Timecore, Time Lookup Table (TLT), and the Temperature block. The PCI and GPS blocks allow the PAB board to interact with the PCI bus and GPS receiver, respectively. The Timecore and the TLT blocks contain the functionality for the actual timestamping process. The Temperature block is used to improve the accuracy of the timestamps when the UltraScope is used on a synchronous system.

The majority of the Timecore is a free-running 60-bit counter called the PAB counter. The PAB counter is initialized to zero when the PCI bus reset is released. The PAB counter is clocked using the 33MHz PCI bus clock. The Timecore also contains a 60-bit register (PPS count) that is loaded using the 1PPS signal from the GPS receiver. At the rising edge of the 1PPS, the PAB counter is sampled and stored in this register. Since the PAB counter is clocked using the PCI bus clock, there is a direct relationship between events on the processor and the PAB counter itself.

The TLT provides a way to store the PPS counts over time. The TLT allows a PAB count to be correlated to a UTC time. When the TLT is enabled by the user application, the current PPS count and UTC time are stored in the PAB's onboard memory. On every rising edge of the 1PPS signal, a compressed version of the PPS count for that second is stored in the TLT. The TLT establishes the link between a PAB count and UTC time.

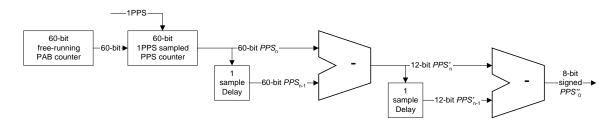

The TLT uses the second derivative of the PPS count to reduce the 60-bit PPS counts to 8-bit values. The first derivative of a PPS count is denoted with a single prime (*PPS'*); the second derivative uses a double prime (*PPS''*). When the TLT is started the current PPS count *PPS*<sub>0</sub>, its first derivative *PPS'*<sub>0</sub>, and the current UTC time,  $UTC_0$ , is

stored in a header in the PAB board's memory. At each second, the TLT computes and stores the second derivative of the PPS count using:

$$PPS'_{n} = PPS_{n} - PPS_{n-1} \tag{3-1}$$

$$PPS''_{n} = PPS'_{n} - PPS'_{n-1}$$

$$(3-2)$$

The value of  $PPS''_n$  is stored in the TLT. This process is shown as a block diagram in Fig. 3.1. The TLT also stores the current temperature at the time a new PPS count is generated. A similar compression method is used to store the temperature.

Fig. 3.1 The hardware block diagram for computing the PPS"

#### 3.2.2 Software

The timestamps are collected during the execution of the user application. On a post-mortem basis, the timestamps are converted to UTC times. The timestamping software consists of several steps. The first step collects the actual timestamp. This is done by reading the 64-bit performance monitoring counter on the host processor. The performance monitoring CPU counter increments using the processor clock, and it is initialized to zero when the CPU reset is released on bootup [16]. This 64-bit CPU counter value represents the time, with respect to the processor, at which an event

occurred. By only reading the CPU counter, the timestamp generation is a low overhead routine that causes little perturbation of the executing software [1].

The next step converts the CPU count,  $CNT_{CPU}$  to a corresponding PAB count,  $CNT_{PAB}$ . There are two parameters needed to convert the CPU count to the corresponding PAB count. The first parameter is clock frequency ratio (*R*) between the PCI clock and the processor clock. The other parameter is the time offset ( $CNT_{Offset}$ ) between the counters. Once these parameters are known, it is possible to convert a CPU count to a PAB count using:

$$CNT_{\text{PAB}} = \frac{(CNT_{\text{CPU}} + CNT_{\text{Offset}})}{R}$$

(3-3)

The final step is to convert the PAB count to the UTC time at which the event occurred. The first step in this process is to iterate through the TLT and reconstruct the PPS counts using the difference counts stored in the TLT. As the PPS counts are determined, the UTC time for each PPS count is also calculated and stored. The PAB count corresponding to the software event can now be correlated to UTC time. Through interpolation of the PPS counts, the PAB count of the event is converted to a UTC time and stored. The timestamps are now in their final form of UTC times and can be used for a variety of purposes.

### 3.3 Operating synchronous UltraScope on an asynchronous system

When using the synchronous version of the UltraScope on an asynchronous system, there are several problems. One problem is computing a highly accurate estimate

of the clock frequency ratio. Initially, this does not seem to be a problem. Time averaging estimates of the clock frequency ratio over a long period of time usually provides a highly accurate estimate. However, the counter values for both the CPU and PAB counters become very large as the system is running. Even a very small error in the clock ratio estimate can amount to seconds or hours of error depending on the length of time the computing system has be running. The error due to the clock frequency ratio is a linear function of time. This problem can be solved using a sufficient number of calibration cycles over a period of time. The calibration cycles can correct for this linear error.

However, an even more difficult problem deals with temperature variations. In a system where the PCI and CPU clocks are phase-locked, temperature variations will affect both clocks, but not the clock frequency ratio. In an asynchronous system, the temperature variations primarily affect the stability both of clocks and can affect the clock frequency ratio. Unless the temperature for both clocks can be controlled or monitored for correction the entire time the system is powered up, there is little that can be done to improve synchronization of the counters with each other. This prevents a precise relationship between the CPU count and the PAB count.

#### **3.4** Modifications required for asynchronous operation

On an asynchronous system, the deterministic relationship between the PCI clock and the CPU clock does not exist. To complicate matters, the clock frequencies for the PCI and CPU clock oscillators are temperature dependent. The temperature dependency between the PCI and CPU clocks causes the clock frequency ratio to vary over time. Without a precise estimate of the clock frequency ratio, the relationship between the CPU and PAB counters cannot be established. The traditional software method of synchronization, such as NTP, is to use a series of timestamps. These timestamps are collected at both the server (the host processor) and the client (the PAB board). The disadvantage to this method is the large amount of overhead involved in collecting a timestamp sequence.

The timestamp process is modified so that an event triggered series of timestamp measurements are made on both the processor and the PAB board. The timestamp sequence is then used to correct some of the errors incurred by accessing both the CPU counter and the PAB board. These modifications include changing the hardware to support accurate indicators that can be used as a timestamp and modifying the software to collect a timestamp sequence rather than a single timestamp measurement.

#### 3.4.1 Hardware

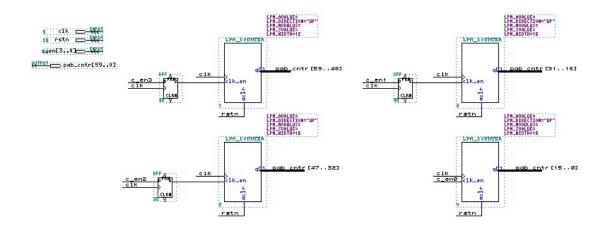

The PAB hardware must be modified so that precision timestamps may be obtained on an asynchronous system. Rather than creating more hardware for timestamp measurements, the existing 60-bit PAB counter is used. The modified timestamp process requires that the PAB count must be readable by the application software. For the synchronous UltraScope, the sampled PPS count is readable by software at offset 0x05 from the base address of the PCI board. The logic was changed so that the free-running PAB count is now available at offset 0x05 instead of the PPS count.

Since the free-running PAB count is now readable by application software, the 60-bit counter itself was modified to be more robust. Originally, the PAB counter was massively pipelined into 15 stages. This is changed so that the counter is pipelined into 4 stages. The reduction in pipelined stages reduces the latency required to read a PAB value. It also reduces the possibility of an error due to lower stages of the pipelined counter rolling over. If the PAB counter could be read in a single, atomic operation, this error would not be possible. A 32-bit PCI bus implementation is used for the PAB board. The PAB counter is 60-bits so it requires two accesses to the PCI bus to completely read the PAB counter. There is no hardware mechanism that prevents the first 32-bits from changing as the remainder of the counter is read. Bounds checking can be performed that will prevent an invalid count from being used in the timestamp calculations.

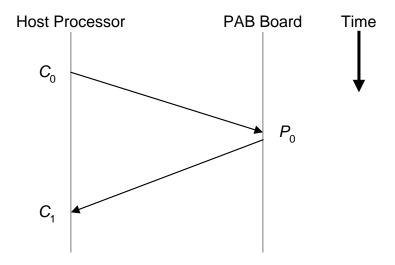

#### 3.4.2 Software

The software required for asynchronous operation has two major parts. The first part collects the timestamp. This step now involves a sequence of readings similar to NTP. The timestamp sequence used in the asynchronous case is shown in Fig. 3.2. A timestamp sequence is created by reading the CPU counter,  $C_0$ , then the free-running PAB counter,  $P_0$ , and then another CPU count,  $C_1$ . The two CPU counter readings are taken to allow for correction for PCI bus transaction delays. Unlike the synchronous case, there is no conversion needed to convert the timestamp into a PAB count. The PAB counter now represents the timestamp of an event rather than a CPU count.

Fig. 3.2 The sequence of timestamps required on an asynchronous system

The only conversion step necessary is to use the TLT to interpolate the UTC time given the PAB count of the timestamp. Because this timestamp uses the PAB count directly, the delay of the PCI bus transaction is contained inside the timestamp. By recording the CPU counts before and after reading the PAB counter, a correction can be applied to minimize the effect of the PCI bus transaction.

#### 3.4.3 PCI transaction correction

The method used to adjust the timestamp value  $P_0$  to account for the PCI bus delays depends on several assumptions. A timestamp sequence can be divided into three distinct regions. These regions are shown in Fig. 3.3. The actual event is designed by *E*.

Fig. 3.3 Regions of delays in a timestamp sequence

The first region,  $T_{event}$ , is the time it takes to read the first CPU count  $C_0$  after the actual event, E, occurs. This time is determined by the overheads of entering the timestamp generation routine, loading the instructions for the CPU counter into cache, and reading the first CPU count. The next region,  $T_{PCI}$ , is the time elapsed from  $C_0$  to  $P_0$ . This time is dominated by the PCI bus transaction delays. The final region,  $T_{end}$ , is the time elapsed from  $P_0$  to  $C_1$ . This time is composed of the time to read the final CPU count and the operating system delays.

Reading the CPU counter accesses a local resource, but reading the PAB counter requires a PCI bus transaction. Therefore, it is possible that  $T_{PCI}$  will be large compared with  $T_{event}$  and  $T_{end}$ . Since  $T_{event}$  and  $T_{end}$  contain similar delays, they will appear to be nearly equal as  $T_{PCI}$  grows relative to  $T_{event}$  and  $T_{end}$ . Therefore, the first assumption is to equate  $T_{event}$  with  $T_{end}$ . The time  $T_{event}$  contains the time required to enter the timestamp routine, load the required processor instructions into cache, and read the CPU counter,  $C_0$ . When reading the last CPU count,  $C_1$ , the time  $T_{end}$  includes the operating system overhead, reading the CPU counter, and returning from the timestamp routine. The delays in  $T_{\text{event}}$  and  $T_{\text{end}}$  are similar in both nature and magnitude. The next assumption is that the clock frequency ratio can be approximated by:

$$R \approx R_{\rm est} = \frac{C_1}{P_0} \tag{3-4}$$

Using (3-4), a PAB count can be converted to a CPU count if the ratio and the time offset,  $CNT_{Offset}$ , are known. When a system has been running for a sufficiently long time, the counter values for the PAB counts and CPU counts will be greater than the time offset by several orders of magnitude. When approximating the ratio in (3-4), the absence of the time offset results in a minimal difference between *R* and *R*<sub>est</sub>. This is illustrated in more detail in Section 3.5.

The correction for the PCI bus is given as follows:

$$T_{\text{event}} = T_{\text{end}}$$

$$\frac{C_0}{R} - E = \frac{C_1}{R} - P_0$$

$$E = P_0 - \frac{C_1 - C_0}{R}$$

$$R \approx R_{\text{est}} = \frac{C_1}{P_0}$$

$$E' = P_0 - \left(P_0 - P_0 \frac{C_0}{C_1}\right)$$

$$E' = P_0' = P_0 \frac{C_0}{C_1}$$

(3-6)

By using this estimation of the event timestamp, the corrected PAB count is being shifted in time so that it occurs before the PCI bus transaction, as shown in Fig. 3.4. Since both  $T_{\text{event}}$  and  $T_{\text{end}}$  incur the delay of reading the CPU counter, this delay is also corrected. The disadvantage to this correction is any delays that are a part of  $T_{\text{end}}$  and not a part of  $T_{\text{event}}$  will cause the corrected PAB count to be moved an additional amount of time. If  $T_{\text{end}}$  is greater than  $T_{\text{event}}$ , then the PAB count will be corrected so that it is now represents a time before the software event.

Fig. 3.4 The timestamp sequence after correction

To analyze the error resulting from shifting the PAB count too far or too little, let K be the PAB count at the time of the actual event, E, and use the approximation in (3-6) to attempt to estimate the event. The estimate of the event, E, is given by E'. Also, let the times  $T_{\text{event}}$ ,  $T_{\text{PCI}}$ , and  $T_{\text{end}}$  be in terms of CPU counts. This results in:

$$C_0 = RK + T_{\text{event}}$$

$$P_0 = \frac{RK + T_{\text{event}} + T_{\text{PCI}}}{R}$$

$$C_1 = RK + T_{\text{event}} + T_{\text{PCI}} + T_{\text{end}}$$

$$E' = P_0 \frac{C_0}{C_1} = \frac{RK + T_{\text{event}} + T_{\text{PCI}}}{R} \left( \frac{RK + T_{\text{event}}}{RK + T_{\text{event}} + T_{\text{PCI}} + T_{\text{end}}} \right)$$

$$E' = K \left( 1 + \frac{T_{\text{event}} + T_{\text{PCI}}}{RK} \right) \left( \frac{1 + \frac{T_{\text{event}}}{RK}}{1 + \frac{T_{\text{event}} + T_{\text{PCI}} + T_{\text{end}}}{RK}} \right)$$

Let the error be  $\varepsilon$  where  $\varepsilon = E' - E$

$$\varepsilon = K \left( 1 + \frac{T_{\text{event}}}{RK} + \frac{T_{\text{PCI}}}{RK} \right) \left( \frac{1 + \frac{T_{\text{event}}}{RK}}{\left( 1 + \frac{T_{\text{event}}}{RK} + \frac{T_{\text{PCI}}}{RK} + \frac{T_{\text{end}}}{RK} \right)} - K$$

Using Binomial expansion:  $(1+X)^{-1} = 1 - X + X^2 - X^3 + \dots, X^2 < 1$ or  $(1+X)^{-1} \approx 1 - X, X^2 << 1$ . This can be used since  $K >> T_{\text{event}}, T_{\text{PCI}}$ , or  $T_{\text{end}}$ .

$$\varepsilon = K \left( 1 + \frac{T_{\text{event}}}{RK} + \frac{T_{\text{PCI}}}{RK} + \frac{T_{\text{end}}}{RK} \right) \left( 1 - \frac{T_{\text{event}}}{RK} - \frac{T_{\text{PCI}}}{RK} - \frac{T_{\text{end}}}{RK} \right) - K$$

$$\varepsilon = K \left( 1 + \frac{T_{\text{event}}}{RK} - \frac{T_{\text{end}}}{RK} \right) - K$$

If  $T_{\text{event}} = T_{\text{end}}$  then

$$\varepsilon = K - K = 0$$

If  $T_{\text{end}} = T_{\text{event}} - \Delta$  then

$$\varepsilon = K \left( 1 + \frac{\Delta}{RK} \right) - K$$

$$\varepsilon = \frac{\Delta}{R}$$

(3-9)

(3-7)

(3-8)

Note that the error,  $\varepsilon$ , does not depend on  $T_{PCI}$ . The variations in the delays associated with  $T_{PCI}$  will have no effect on the error; only variation in  $T_{event}$  or  $T_{end}$  will cause a change in  $\varepsilon$ . As long as  $K >> T_{event}$ ,  $T_{PCI}$ , and  $T_{end}$ , the resultant error  $\varepsilon$  does not depend on K. Therefore, if  $T_{event} \neq T_{end}$ , then the difference between these two times is the amount of error that is added to the corrected PAB count,  $P_0$ '. This result is confirmed experimentally in Chapter 4.

## **3.5** Overview of error sources

With the asynchronous UltraScope system, there are several error sources in the timestamping process. When collecting the timestamp, there are delays due to reading the CPU counter, the PCI bus transaction, and operating system functions. Other error sources include the inaccuracies associated with the 1PPS signal and computing the approximation to the clock frequency ratio. Table 3.1 lists each error source, the general amount of error supplied to the timestamps, and indicates if that error can be reduced in software.

| Error Source                        | Amount of error<br>supplied                        | Can be reduced?     | Clock<br>frequency<br>dependent? |

|-------------------------------------|----------------------------------------------------|---------------------|----------------------------------|

| Reading the CPU counter             | 1 - 2 µs                                           | Yes                 | Yes                              |

| PCI bus transaction                 | 2 - 3 µs                                           | Yes                 | Yes                              |

| PCI bus arbitration                 | 1 - 2 $\mu$ s depending on the number of devices † | Yes                 | Yes                              |

| Operating system delays             | 0.5 - 3 μs depending on<br>the system load         | No <sup>*</sup>     | Yes                              |

| GPS 1PPS error                      | ± 15 ns                                            | Error is negligible | No                               |

| Clock frequency ratio approximation | <±1 ns                                             | Error is negligible | No                               |

Table 3.1 Error sources and their contributions to the overall error

<sup>\*</sup> Using an open-source operating system such as Linux, may allow better insight into these errors, and therefore allow the errors to be reduced.

<sup>†</sup> The PCI bus specification provides typical delays due to bus arbitration [17].

To read the CPU counter, the processor's pipeline must be flushed. If the pipeline is not flushed, the count returned may represent a time before the software event occurs or significantly after the event [16]. This uncertainty is due to the out-of-order execution capability that most modern processors utilize. Flushing the processor's pipeline removes this uncertainty; however, it adds a small amount of delay before the CPU counter can be read. The delay of flushing the pipeline and reading the CPU counter is incurred twice for every timestamp created.

The PCI bus transaction is a major source of error when creating a timestamp on an asynchronous system. A problem with a PCI bus transaction is the variability of the time required to complete a transaction. As the number of different transactions on the PCI bus increases, the arbitration of the PCI bus becomes a large factor in the PCI delays.

The delays incurred from the operating system are the most troublesome. The operating system can switch processes just before a timestamp is created or during the timestamping process. Additionally, when accessing the PCI bus, the operating system places the distributed application into a blocked state until the PCI bus transaction has completed [18]. When the PCI bus transaction has completed, the operating system must switch back to the distributed application. This context switching adds a delay before the second CPU counter value is read. A diagram of the relevant process states under Unix is shown in Fig. 3.5 [18]. Because the operating system underlies all of the software that is running on a system, these delays cannot be accurately measured nor characterized.

The errors due to the GPS signals and the approximation of the clock frequency ratio are miniscule in comparison to the other sources of error. The GPS 1PPS signal, without selective availability, has a variation of approximately  $\pm$  15 ns [2].

Each of these error sources will be discussed and characterized more specifically for several cases of system usage. The test cases used are for when 1) the PCI bus is nearly idle, 2) the PCI bus is busy but under normal usage, and 3) the PCI bus has several devices attempting to use the bus simultaneously.

Fig. 3.5 The process states and transitions possible when accessing the PCI bus

Fig. 3.6 Measured error from using an approximation of the clock frequency ratio

## CHAPTER IV

## RESULTS

This chapter discusses the methodology used for verification of the hardware and software modifications as well as collection and analysis of the timestamp data. Three major cases are investigated. The first case is when the PCI bus is idle during most of the application's runtime. The second case is when the PCI is busy but under a normal load, such as on a multi-user system. The last case is when the PCI bus is busy and device arbitration occurs. The error for each of these cases is characterized and analyzed.

## 4.1 Test and verification procedure

A series of tests and programs are run to determine the characteristics of a computing system. These tests are outlined in Appendix A. The tests can be divided into three categories: testing the hardware and software modifications to the PAB board, determining the system characteristics, and timestamp collection and analysis. All of these tests were performed on an Intel 233 MHz Pentium II PC. The test computer is a synchronous system.

Testing the PAB counter modifications requires two PAB boards. One board is installed running the synchronous design, and the other board contains the modified, asynchronous design. Over a period of several days, the counters on both PAB boards are read. The difference between the two PAB counters should be within one second of each other. Other functions, such as communications with the GPS receiver and the temperature sensor, are checked in case the hardware modifications caused other areas of the board to malfunction.

The characteristics of the computing system can be determined with the software listed in Appendix A. An important characteristic is whether a system is synchronous or not. When probing the processor clock signal and the PCI bus clock signal with an oscilloscope, a synchronous system will exhibit a phase lock between these two signals. In an asynchronous system, the phase between these two clocks will vary over time, possibly only on an intermittent basis. Such was the case for the Sun systems tested where the phase lock of the CPU and PCI clocks were allowed to slip periodically.

Most of the analysis of an asynchronous system is performed to validate the timestamp algorithm. From these tests, an estimate of the overall timestamp precision can be formed. A significant amount of error is due to the PCI bus transactions. The load of the PCI bus is varied so that the error, and its impact on timestamp precision, can be determined. Three cases of PCI bus loading are investigated. When the PCI bus is idle, there is a minimum of extraneous system activity, which allows the error to be characterized accurately. The load of the PCI bus is increased which better simulates the actual conditions on a multi-user system. The timestamp precision achieved in this case will be more representative of the actual achievable precision. As the load on the PCI bus increases, the probability that bus arbitration occurs increases as well. PCI bus arbitration adds a significant amount of time to a bus transaction. For this reason, these

arbitration delays will be simulated to investigate their affect on the precision of a timestamp.

#### 4.2 PCI bus idle

A common trend in distributed computing is the move to a cluster of computers instead of using a large multiprocessor machine. In a cluster environment, a user is assigned a number of nodes from the cluster. Except for the operating system and the queuing software, the user application has exclusive access to these nodes. Exclusive access to a group of nodes reduces the amount of traffic on the PCI bus. Most of the PCI bus activity would be caused by the PAB board, the network interface card, and a disk controller card. A single PAB board is used in the test PC with no applications running other than the test software.

Timestamp data is collected over both short and long periods of time. Recall from Fig. 3.3, a timestamp can be divided into three times:  $T_{\text{event}}$ ,  $T_{\text{PCI}}$ , and  $T_{\text{end}}$ . By using a synchronous system, all PAB counts can be converted to CPU counts, and therefore,  $T_{\text{PCI}}$  and  $T_{\text{end}}$  can be measured. The time of the actual event is unknown, so  $T_{\text{event}}$  cannot be directly measured. However, (3-8) and (3-9) use  $T_{\text{end}}$ , which can be measured, to estimate  $T_{\text{event}}$ .  $T_{\text{PCI}}$  and  $T_{\text{end}}$  are formed by:

$$T_{\rm PCI} = \frac{CNT_{\rm PAB_0} + CNT_{\rm Offset}}{R} - CNT_{\rm CPU_0}$$

(4-1)

$$T_{\rm end} = CNT_{\rm CPU_1} - \frac{CNT_{\rm PAB_0} + CNT_{\rm Offset}}{R}$$

(4-2)

Once the timestamp data is collected, the PAB count is shifted in time using (3-3). The corrected PAB count is converted into CPU counts so the data can be analyzed.

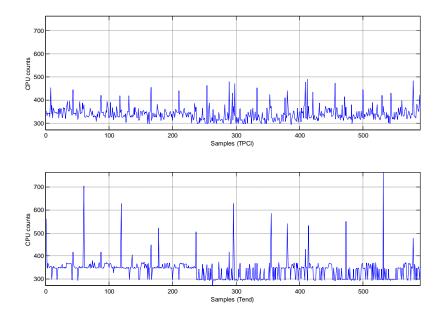

The two measurable times,  $T_{PCI}$  and  $T_{end}$ , are shown in Fig. 4.1. It is important to observe that the delays due to the PCI bus are similar in magnitude to the remaining delays. A strong motivation for correcting the PAB count was the thought that the PCI bus delays would be much worse than the remaining errors. The variation of the time for a bus transaction is not much more than the variations due to the operating system and reading the CPU counter. However, it can be seen in Fig. 4.1 that the PCI bus delays have no effect on  $T_{end}$ , which implies no effect on the timestamp precision. These results validate the approach taken with the instrumentation hardware and the software routines.

Fig. 4.1 Timestamp data when the PCI bus is idle

To create an estimate of the timestamp precision, the magnitude and variation of  $T_{end}$  must be examined. When the PCI bus is idle, the average delay for  $T_{end}$  is 300 to 350 CPU counts. The variation of this delay is ± 25 CPU counts. The amount of error contained in  $T_{end}$  is assumed to be the amount of error in the estimate of the time the event actually occurred. Therefore, the precision is limited by that error. For a distributed system consisting of a cluster of computers, the overall precision of a timestamp is limited to  $1.28 - 1.50 \ \mu s \pm 107 \ ns$ , when the processor clock frequency is 233 MHz. The precision is dependent on the clock frequency of the processor. The computing system is at the lowest possible activity, so this is the best case scenario for an asynchronous machine.

### 4.3 PCI bus busy

A situation where the PCI bus experiences moderate to frequent activity is when the distributed system is a multi-user system. In this case, the user does not have exclusive access to the processing nodes. Software other than the operating system may be running at all times. The amount of processing time and I/O time required by the running software will vary. This makes the timestamping process less accurate due to the increased level of activity on the computing system.

A second PAB board was installed into the test system. Both boards are PCI bus target devices with no bus mastering capability. A program that continuously accessed the second PAB board was started in the background. The background program was designed to continuously read a 48-byte block of the secondary PAB board's registers. In the foreground, the timestamp collection program was running and collecting timestamps on a regular basis using the primary PAB board.

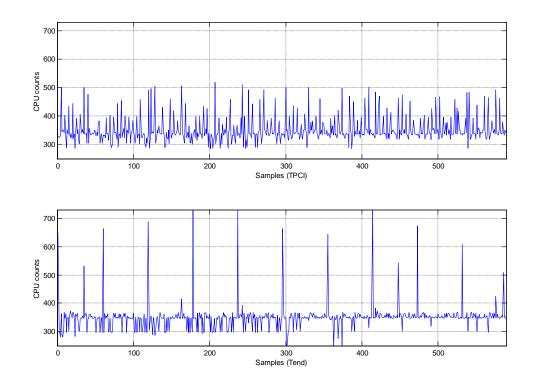

The procedure used to analyze the timestamps is the same procedure used when the PCI bus was idle. The results of the timestamp data are shown in Fig. 4.2. For this data, there is significantly more variation in the PCI bus delays than in the previous case. Similar to when the bus is idle, the PCI bus delays do not affect the estimate of when the event occurs.

Fig. 4.2 Timestamp data when the PCI bus is busy

The operating system has a more active role in determining the precision of the system. On a 233 MHz computer, it requires 220 CPU counts to read the CPU counter, assuming the instructions have already been loading into cache. There is some additional delay, approximately 75 CPU counts, that can only be caused by the operating system. As the operating system is managing multiple user applications, these delays are slightly worse than in the previous case. The large spikes that appear in  $T_{end}$  are likely to be caused by the operating system responding to the background application rather than the foreground test program.

The additional error from the operating system slightly degrades the timestamp precision when the PCI bus is heavily loaded. The average amount of error present in  $T_{end}$  yields a precision of 350 - 350 CPU counts, or 1.50 - 1.63 µs ± 107 ns on a 233 MHz Intel PC. Surprisingly, the variation of the precision is not any worse than when the PCI bus is idle.

### 4.4 PCI bus with arbitration

If multiple bus mastering devices use the PCI bus on a system, bus arbitration may occur. Bus arbitration does not require a heavily loaded bus. If at any time two or more devices request access to the bus, arbitration will occur. There are an assortment of arbitration schemes that can be used. Fixed priority, priority-based round-robin, and equal priority round-robin are just a few of the arbitration schemes that may be used. If the requesting PCI devices are bus masters, there can be several physical devices participating in the bus arbitration. If none of the devices are bus masters, the motherboard must handle the arbitration between all of the devices requesting the PCI bus. The PCI bus specification leaves the actual implementation details of the arbitration scheme up to the manufacturers. Currently, Intel uses a round-robin scheme in their PCI bridge chipsets [19]. Sun also implements a round-robin arbitration scheme for their systems [20].

The PAB board is a target-only device, so it is not capable of participating in bus arbitration. The Intel PC used in these tests did not contain any bus master PCI devices. To test the performance of the UltraScope with bus arbitration, a Matlab simulation was created. The PCI arbitration simulation adds bus arbitration delays to existing timestamp data.

The arbitration simulation requires several parameters that are used to define the delays associated with bus arbitration. These parameters determine the number of devices that are requesting the PCI bus when arbitration occurs and the amount of delay each requesting device adds to the PAB board's PCI bus transaction. If a device gains control of the PCI bus before the PAB board, the overhead of the signaling protocol and the bus transaction itself must be accounted for. Once a device is granted access to the PCI bus, the signaling protocol typically takes two PCI bus clock cycles [17]. The latency that is added by a single device's bus transaction during arbitration is dependent on a latency counter. The latency counter defines the maximum amount of time a master may hold the PCI bus during an arbitrated transaction. The value of this counter is configurable and determined by the manufacturer of the PCI device. A typical value for

the latency counter for a bus master is 22 PCI bus clock cycles [17]. The last parameter specifies the frequency at which bus arbitration occurs. For this simulation, a cluster of computers is assumed. Therefore, the PCI bus traffic will be light so bus arbitration will occur infrequently.

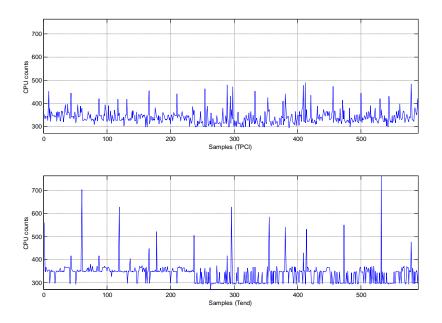

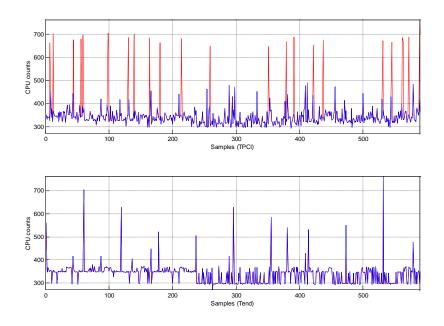

The timestamp data used in this simulation represents an idle PCI bus where infrequent arbitration occurs. To better visualize the effect arbitration has on a timestamp, Fig. 4.3 displays the timestamps without arbitration. Fig. 4.4 represents the timestamp data after the arbitration delays have been added. For the  $T_{PCI}$  measurements in Fig. 4.4, all of the measurements that have a magnitude greater than 500 CPU counts are due to the arbitration delays.

By examining Fig. 4.3 and Fig. 4.4, it can be seen that the only differences between timestamps with and without arbitration delays occur in  $T_{PCI}$ . None of the arbitration delay is present in the estimate of when the event occurs. Consequently, the performance of this timestamp algorithm is not affected by PCI bus arbitration. The precision of the timestamp data resulting from this simulation is the same as when the PCI bus is idle without arbitration, 1.28 - 1.50 µs.

Fig. 4.3 Timestamp data without arbitration

Fig. 4.4 Timestamp data with bus arbitration

### 4.5 Error characterization

Just as important as the overall precision, are the sources of error that affect the precision. In this section, the error sources will be characterized with respect to each of the three test cases. The error sources due to the timestamp process are reading the CPU counter and accessing the PCI bus to read the PAB counter. Other sources of error are from other executing applications. These are characterized by the operating system error and the PCI bus arbitration error.

Reading the CPU counter first requires the processor's pipeline to be flushed, and then the CPU counter can be read. The time required to flush the pipeline is dependent on the type and number of instructions that are currently executing on the processor. Measurements show flushing the pipeline takes on average 100 clock cycles. Then, it requires 220 clock cycles for the processor to read the CPU counter. This operation has been measured to increase up to 500 clock cycles if the instructions are not held in cache. This error is incurred at the beginning of a timestamp sequence and at the end of the sequence. When the PAB counter is adjusted, the estimate of the timestamped event is improved by 320 clock cycles, which is  $1.37 \,\mu$ s.

To read the PAB counter, a PCI bus transaction is initiated. If bus arbitration does not occur, the average error is  $2 - 3 \mu s$ . Bus arbitration adds an additional  $1 - 2 \mu s$  depending on the number of devices requesting the PCI bus. The distribution of the error due to the PCI bus is a Raleigh distribution, which is commonly used to model communications systems. Once the PAB counter is adjusted, the effect of the PCI bus error on a timestamp's precision is negligible.

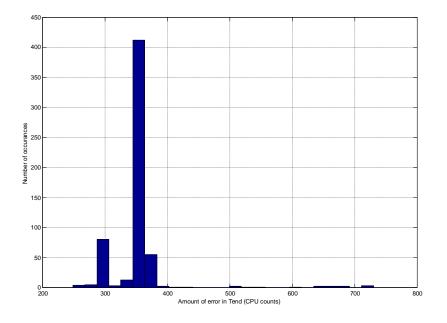

The most troublesome error source is the operating system. Depending on the system load, the operating system contributes  $1 - 3 \mu s$ . As the system load increases, the error supplied by the operating system is likely to increase as well. This error is worse than the PCI bus error because it cannot be better estimated or corrected without access to the inner workings of the operating system. The distribution of this error source can be characterized similar to the PCI bus error. Fig. 4.5 shows the empirical distribution of error that is contributed from the operating system. The empirical distribution is a histogram that reports the frequency of occurrence for a range of values. The distribution shown in Fig. 4.5, is similar to the distribution of the PCI bus errors, which is a Raleigh distribution.

Fig. 4.5 Distribution of error contributed by the operating system

The significant sources of error are the PCI bus transaction and the operating system delays. By correcting the PAB counter in a timestamp sequence, the PCI bus errors are removed as well as most of the errors due to reading the CPU counter. It is likely that some of the error due to the operating system is corrected by the overhead when entering the timestamp collection routine; however, this cannot be verified.

# CHAPTER V

## CONCLUSIONS

The goal of this work is to allow precision timestamping of events in distributed and parallel applications. The UltraScope instrumentation hardware and software allowed precision timestamps to be created on systems where the PCI bus clock and the processor clock were phase locked together. This research expands on this previous work to allow precision timestamping on computing systems that do not exhibit this characteristic.

Modifications to both the hardware and software components were required to achieve this goal. The timestamping process was modified so that an event driven series of timestamps is collected on both the host processor and the PAB board. A correction to the final timestamp value is created to account for the delays incurred by the PCI bus, such as bus arbitration and initiating and completing a bus transaction.

## 5.1 Timestamp precision

The overall precision and contributions of the error sources were investigated for three cases: the PCI bus is idle, the PCI bus is busy, and the PAB must arbitrate for access to the PCI bus. A distributed system that consists of a cluster of nodes allows a user to gain exclusive control over a group of nodes. The result is a nearly idle PCI bus and low system load. The PCI bus is being heavily used represents a parallel system that is shared among many simultaneous users. Finally, a simulation of PCI bus arbitration is used to verify the corrections applied to a timestamp can adjust for bus arbitration. Table 5.1 lists each case and the average precision of the timestamp data.

Table 5.1 Each test case and the average precision of the timestamps

| Test case                | Precision<br>(CPU counts) | Precision<br>(Time)                |

|--------------------------|---------------------------|------------------------------------|

| PCI bus idle             | $300 - 350 \pm 25$ counts | $1.28 - 1.50 \ \mu s \pm 107 \ ns$ |

| PCI bus busy             | $350 - 380 \pm 25$ counts | $1.50 - 1.63 \mu s \pm 107 ns$     |

| PCI bus with arbitration | $300 - 350 \pm 25$ counts | $1.28 - 1.50 \ \mu s \pm 107 \ ns$ |

When the PCI bus is idle, the overall timestamp precision was 300 to 350 CPU counts. This translates into  $1.28 - 1.50 \,\mu s$  on a 233 MHz Pentium II Intel computer. The precision suffered a variability of approximately  $\pm 107$  ns.

The major differences between a busy PCI bus and the idle case are the operating system delays and the variability of the PCI bus delays. The variability of the PCI bus delays had a negligible impact on the timestamp precision. The accuracy of these timestamps is  $1.50 - 1.63 \,\mu$ s with a variation of  $\pm 107$  ns. The increased operating system delays of a busy, multi-user system reduces the overall precision slightly.

The PCI bus arbitration simulation was designed to test the performance of the PCI bus correction given by:

$$P_0' = P_0 \frac{C_0}{C_1}$$

(5-1)

The PCI bus arbitration is treated as a longer than normal PCI bus transaction. The correction in (5-1) positioned the final timestamp so that it occurs before the PCI bus arbitration. Consequently, the precision obtained in this case is similar to the previous cases. The overall precision is  $1.28 - 1.50 \,\mu s$  with a variability of  $\pm 107 \, ns$ .

These three cases validated the use of (5-1) to accurately correct for the PCI bus delays. The experimental results shown in this work validate the mathematical justifications given in Chapter 3. These results confirm that using a series of timestamps rather than a single timestamp value can be used to increase the precision on an asynchronous distributed system, by accounting for the PCI bus transaction delays.

#### 5.2 Error sources and their contributions

Examination of the test results using a synchronous system allows the classification of the various errors that are present in the timestamps. The error sources and their contributions are listed in Table 5.2.

| Error source          | Final error supplied to a timestamp | Affects precision? | Clock frequency dependent? |

|-----------------------|-------------------------------------|--------------------|----------------------------|

| Reading the CPU       | < 1.20 µs                           | Yes                | Yes                        |

| counter               |                                     |                    |                            |

| PCI bus transaction   | ± 30 ns                             | No                 | Yes                        |

| PCI bus arbitration   | ± 30 ns                             | No                 | Yes                        |

| Operating system      | 0.5 - 3 μs                          | Yes                | Yes                        |

| delays                |                                     |                    |                            |

| GPS 1PPS error        | ± 15 ns †                           | No                 | No                         |

| Clock frequency ratio | ± 30 ns                             | No                 | No                         |

| approximation         |                                     |                    |                            |

| Timestamp correction  | ± 30 ns                             | No                 | No                         |

Table 5.2 List of error sources and their contribution to the overall error

<sup>†</sup> This is the measured GPS 1PPS error after Selective Availability was disabled [2].