Mississippi State University Scholars Junction

Theses and Dissertations

Theses and Dissertations

12-11-2009

## Partitioning And Interface Requirements Between System And Application Control For Power Electronic Converter Systems

Anil Kumar Kondabathini

Follow this and additional works at: https://scholarsjunction.msstate.edu/td

#### **Recommended Citation**

Kondabathini, Anil Kumar, "Partitioning And Interface Requirements Between System And Application Control For Power Electronic Converter Systems" (2009). *Theses and Dissertations*. 3455. https://scholarsjunction.msstate.edu/td/3455

This Dissertation - Open Access is brought to you for free and open access by the Theses and Dissertations at Scholars Junction. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Scholars Junction. For more information, please contact scholcomm@msstate.libanswers.com.

# PARTITIONING AND INTERFACE REQUIREMENTS BETWEEN SYSTEM AND APPLICATION CONTROL FOR POWER ELECTRONIC CONVERTER SYSTEMS

By

Anil Kumar Kondabathini

A Dissertation Submitted to the Faculty of Mississippi State University in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electrical Engineering in the Department of Electrical and Computer Engineering

Mississippi State, Mississippi

December 2009

Copyright by

Anil Kumar Kondabathini

2009

## PARTITIONING AND INTERFACE REQUIREMENTS BETWEEN SYSTEM AND

#### APPLICATION CONTROL FOR POWER ELECTRONIC

#### CONVERTER SYSTEMS

By

Anil Kumar Kondabathini

Approved:

Herbert L. Ginn III Associate Professor of Electrical and Computer Engineering (Director of Dissertation) Noel Schulz Professor of Electrical and Computer Engineering (Committee Member)

Randolph Follett Assistant Professor of Electrical and Computer Engineering (Committee Member) Anurag K. Srivastava Assistant Research Professor of Electrical and Computer Engineering (Committee Member)

Sarah A. Rajala Dean of Bagley College of Engineering James E. Fowler Professor and Graduate Program Director of Electrical and Computer Engineering (Graduate Coordinator) Name: Anil Kumar Kondabathini

Date of Degree: December 11, 2009

Institution: Mississippi State University

Major Field: Electrical and Computer Engineering

Major Professor: Dr. Herbert L. Ginn III

#### Title of Study: PARTITIONING AND INTERFACE REQUIREMENTS BETWEEN SYSTEM AND APPLICATION CONTROL FOR POWER ELECTRONIC CONVERTER SYSTEMS.

Pages in Study: 132

Candidate for Degree of Doctor of Philosophy

Applications of power electronics in power systems are growing very rapidly and changing the power system infrastructure in terms of operation speed and control. Even though applications of power electronics are wide spread, the cost and reliability of power electronics are the issues that could hinder their penetration in the utility and industrial systems. The demand for efficient and reliable converter controllers gave rise to modularized converter and controller design. The objective of this dissertation is to determine the appropriate partitioning and interface requirements between the system and application control layers for power electronic converters so that the minimum set of system layer to application layer control interfaces is compatible across all power electronic controllers.

Previous work, using the Open System Architecture (OSA) concept has shown that there is a set of common functions shared by different converters at the low-level control layers. It has also shown that, depending on the application, there is a variation in control functions in application/middle control layers. This functional variation makes it difficult to define system functionality of power converters at upper control layers and further complicates the investigation into the partition requirements of system to application control layer. However, by analyzing the current or voltage affected by a converter in terms of orthogonal components, where each component or group of components is associated with a power-converter application, and the amount of required DC bus energy storage, a common functionality can be observed at the application control layer. Therefore, by establishing common functionality in terms of affected current or voltage components, a flexibility of operation can be realized at upper control layers that will be a major contribution towards standardizing the open system architecture.

In order to a construct functional flexible power converter control architecture, the interface requirements to the system control layer and the partitioning between the system control layer and application control layer need to be explored. This will provide flexibility of system design methodology by reducing the number of constraints and enabling system designers to explore possible system architectures much more effectively.

## DEDICATION

I would like to dedicate this work to my wife and my family members.

#### ACKNOWLEDGMENTS

I would like to take this opportunity to express my deepest gratitude to my advisor Dr. Herbert L. Ginn III for his support, guidance, and encouragement throughout this research. I would also like to extend thanks to the other committee members Dr. Noel Schulz, Dr. Randolph Follett and Dr. Anurag Srivastava for serving on my committee to improve this work.

I would like to thank US Navy-Office of Naval Research (ONR) for providing the financial support.

I would also like to thank my parents, my brother and my friends for their support throughout my academic career without which I would not have dreamt about my PhD degree.

I would also like to thank my wife for her support and encouragement.

### TABLE OF CONTENTS

| DEDICATI                 | ION                                                                               | ii                                                 |

|--------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------|

| ACKNOW                   | LEDGMENTS                                                                         | iii                                                |

| LIST OF T.               | ABLES                                                                             | vii                                                |

| LIST OF F                | IGURES                                                                            | ix                                                 |

| CHAPTER                  |                                                                                   |                                                    |

| I. INT                   | RODUCTION                                                                         | 1                                                  |

| 1.1<br>1.2<br>1.3<br>1.4 | Topic Background<br>Objective of Dissertation<br>Approach<br>Dissertation Outline | 1<br>5<br>6<br>7                                   |

| II. PRI                  | NCIPLE OF CONTROL PARTITIONING                                                    | 8                                                  |

| 2.1<br>2.2               | Partition Criteria<br>Typical Control Architectures                               | 8<br>10                                            |

|                          | PLICATION CONTROL LAYER TO CONVERTER CONTROL<br>YER PARTITIONING                  | 14                                                 |

| 3.1<br>3.2               | <ul> <li>Partition Criteria</li></ul>                                             | 14<br>18<br>18<br>19<br>20<br>21<br>22<br>24<br>25 |

3.2.3 Active Rectifiers.....

Three-Phase VSC

28

30

|       |                                                                                                   | 30<br>33             |

|-------|---------------------------------------------------------------------------------------------------|----------------------|

| IV.   | SYSTEM CONTROL LAYER TO APPLICATION CONTROL LAYER                                                 | 35                   |

|       |                                                                                                   | 37                   |

|       |                                                                                                   | 37<br>41             |

|       | 1                                                                                                 | 48                   |

|       |                                                                                                   | 49                   |

|       |                                                                                                   | 51                   |

| V.    | PARTITION TEMPORAL REQUIREMENTS                                                                   | 53                   |

|       | 5.1 Partitioning Observations                                                                     | 53                   |

|       | 6                                                                                                 | 55                   |

|       | 5.2.1 STATCOM Control Partition Temporal Requirements                                             | 56                   |

|       | 1                                                                                                 | 59                   |

|       | 1                                                                                                 | 60                   |

|       | 1 1                                                                                               | 62                   |

|       | 1 1                                                                                               | 63<br>64             |

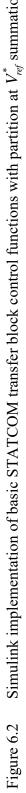

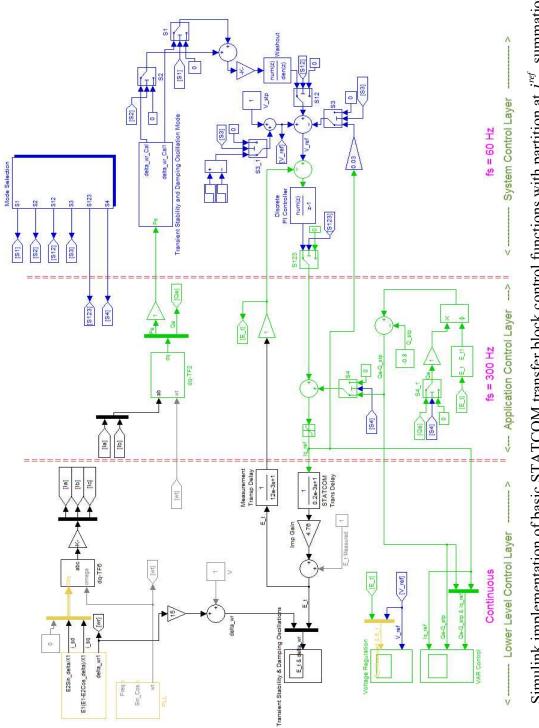

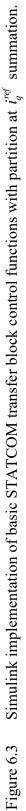

| VI.   | <ul><li>6.1 STATCOM Simulation Model and Results</li><li>6.1.2 Oscillation Damping Mode</li></ul> | 66<br>66<br>68<br>69 |

|       |                                                                                                   | 74                   |

|       |                                                                                                   | 75                   |

|       |                                                                                                   | 77                   |

|       |                                                                                                   | 82                   |

|       | 6.4 Vector Controlled Motor Drives                                                                | 85                   |

|       | 6.5 Summary                                                                                       | 89                   |

| VII.  | SYSTEM TO APPLICATION CONTROL LAYER INTERFACE<br>DEFINITION                                       | 90                   |

|       | 7.2 Communication Requirement for System to Application                                           | 90<br>93             |

| VIII. |                                                                                                   | 95                   |

|       |                                                                                                   |                      |

|       | 8.1 Future Work                                                                                   | 96                   |

| REFE | RENCES                                                     | 98  |

|------|------------------------------------------------------------|-----|

| APPE | NDIX                                                       |     |

| A.   | SHUNT CONNECTED CURRENT CONVERTER CONTROL<br>ARCHITECTURES | 104 |

| B.   | CAPACITOR SIZING CALCULATION                               | 113 |

| C.   | SIMULATION CASE STUDIES                                    | 123 |

### LIST OF TABLES

| TABLE |                                                                                                   | Page |

|-------|---------------------------------------------------------------------------------------------------|------|

| 2.1   | Some typical shunt connected current controller applications [8]                                  | 11   |

| 2.2   | Some typical series connected voltage controller applications                                     | 12   |

| 3.1   | Some typical shunt connected current controller applications with affected current components [8] | 17   |

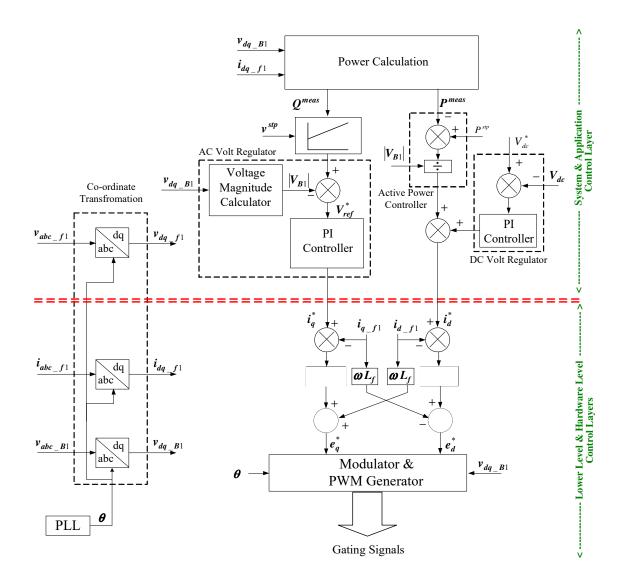

| 4.1   | Signal list for STATCOM applications – partition at $V_{ref}^*$ summation                         | 38   |

| 4.2   | Signal list for STATCOM applications – partition at $i_q^{ref}$ summation                         | 41   |

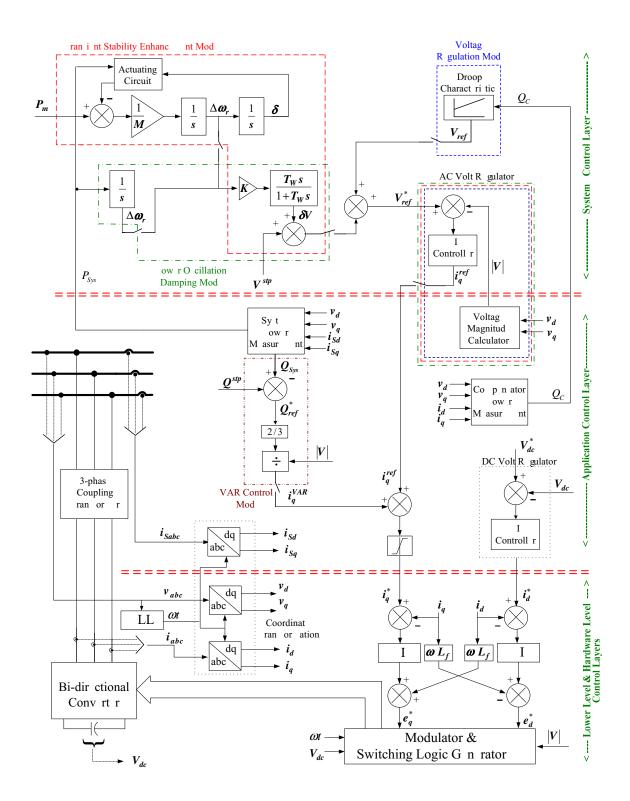

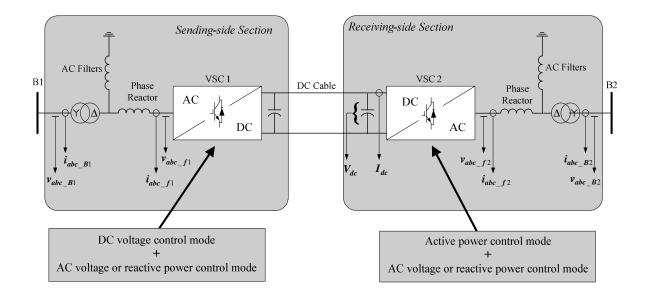

| 4.3   | Signal list for HVDC applications – partition at $V_{ref}^*$ summation                            | 45   |

| 4.4   | Signal list for HVDC applications – partition at $i_q^{ref}$ summation                            | 45   |

| 4.5   | Signal list for vector drive applications – partition at $T_{em}^*$ summation                     | 49   |

| 4.6   | Signal list for typical fixed-function active filter applications                                 | 52   |

| 5.1   | Summary for determining the bandwidth – partition at $V_{ref}^*$ summation                        | 58   |

| 5.2   | Summary for determining the bandwidth – partition at $i_q^{ref}$ summation.                       | 59   |

| 5.3   | Summary for determining the bandwidth requirement – partition at $V_{ref}^*$ summation            | 59   |

| 5.4   | Summary for determining the bandwidth requirement – partition at $i_q^{ref}$ summation            | 60   |

| 5.5   | Partitioning interface signals list with system and application layer sampling requirement        | 65   |

| 7.1 | System to application communication requirements        | 94  |

|-----|---------------------------------------------------------|-----|

| B.1 | Multi level inverter topologies characteristics         | 116 |

| B.2 | Summary: Multilevel inverter topologies characteristics | 116 |

| B.3 | Summary for required capacitance                        | 122 |

### LIST OF FIGURES

| FIGURE |                                                                                                                             | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------|------|

| 1.1    | Control architecture for a power electronic converter system [5]                                                            | 3    |

| 3.1    | Functional diagram of a converter with partitioned control architecture                                                     | 16   |

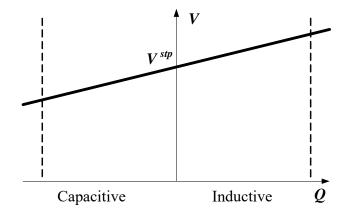

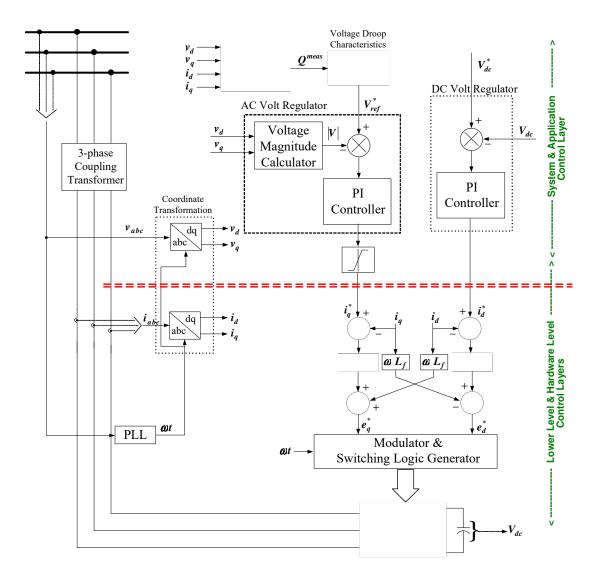

| 3.2    | Voltage set point with droop characteristic                                                                                 | 20   |

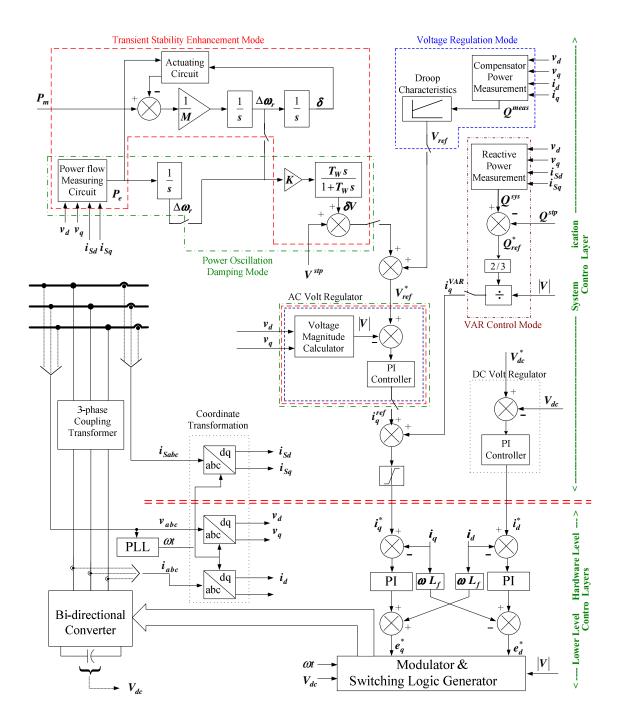

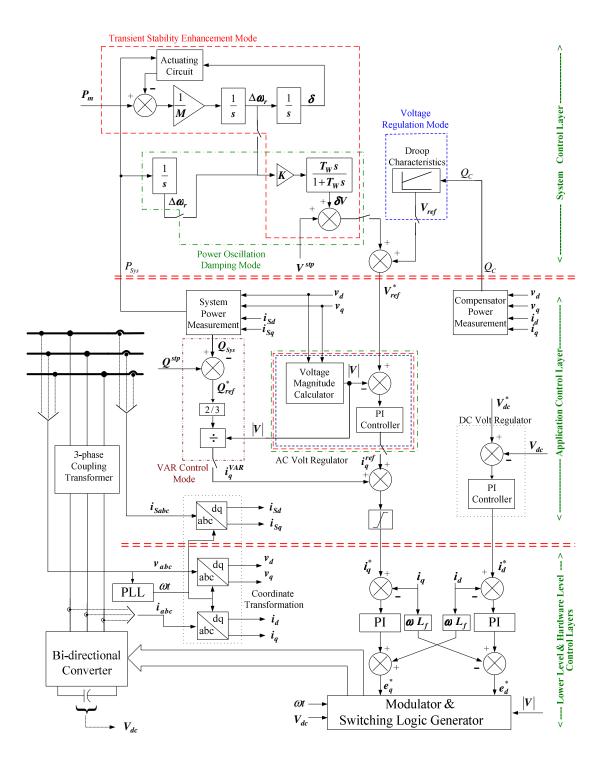

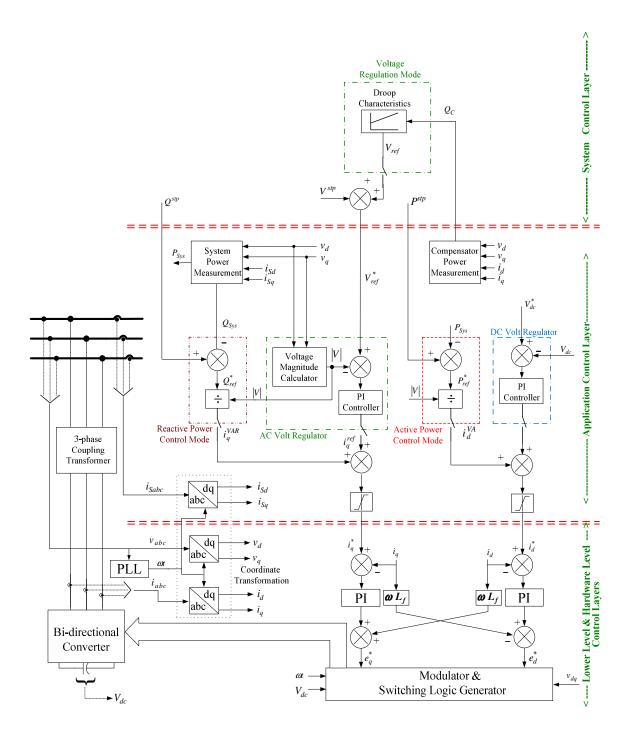

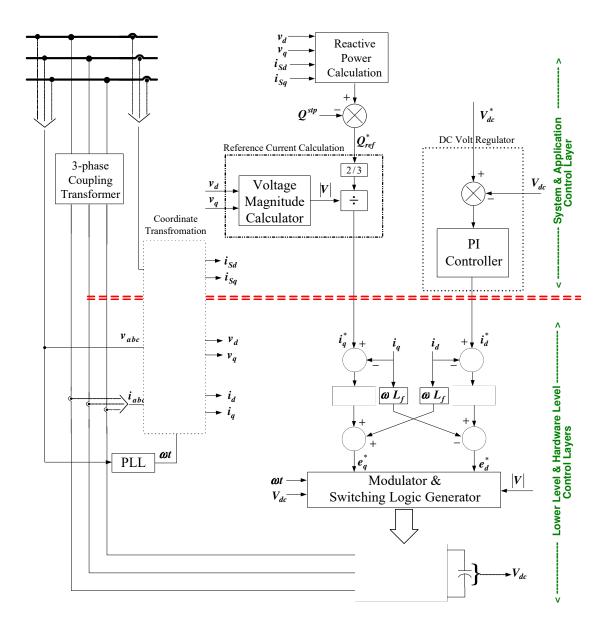

| 3.3    | Typical STATCOM control functions with division between lower functions and application plus system functions               | 23   |

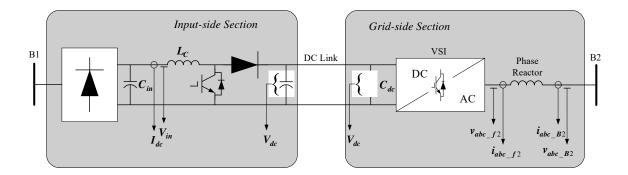

| 3.4    | Power system using DC-DC boost chopper                                                                                      | 26   |

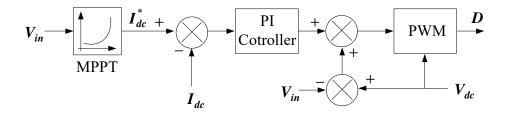

| 3.5    | Control diagram of boost chopper                                                                                            | 26   |

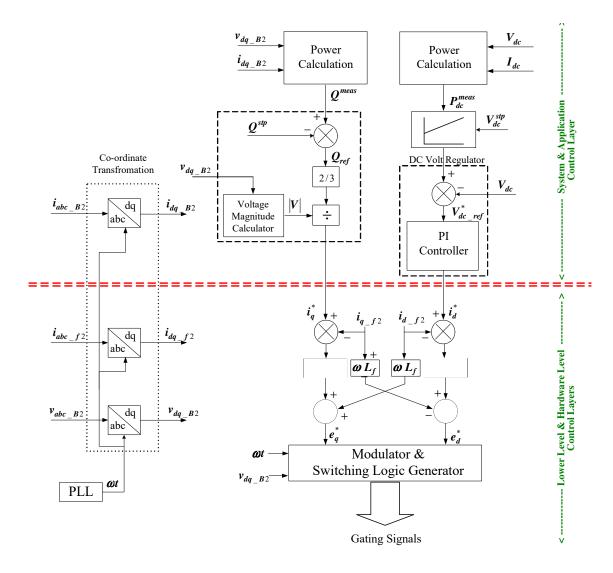

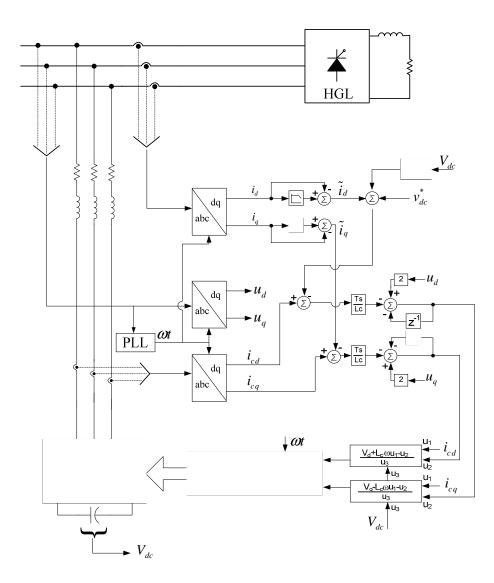

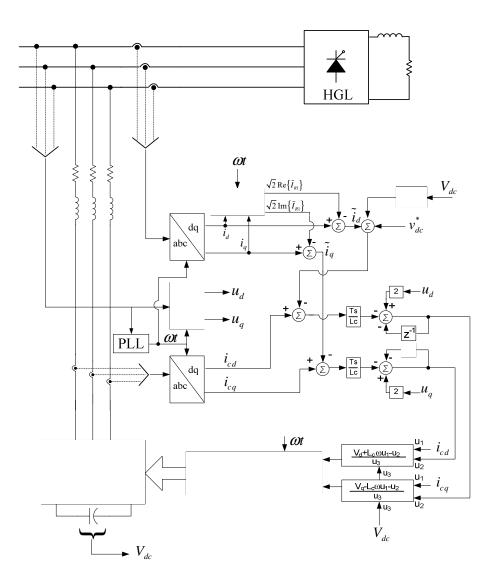

| 3.6    | Control structure of grid-side converter                                                                                    | 27   |

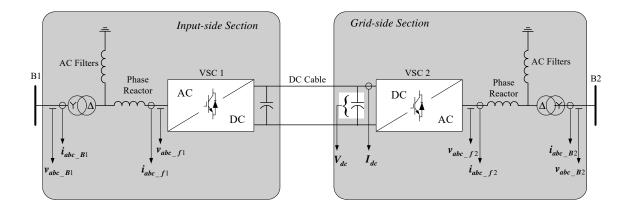

| 3.7    | Power system diagram for the HVDC Light transmission system                                                                 | 28   |

| 3.8    | Control structure of input-side converter                                                                                   | 29   |

| 3.9    | Control structure of an active rectifier                                                                                    | 31   |

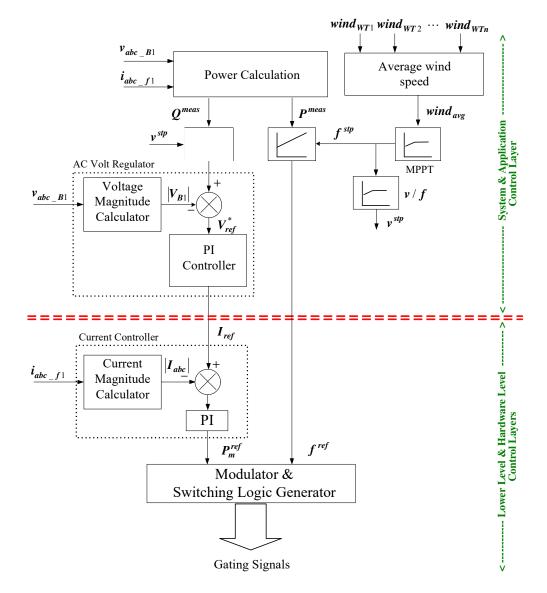

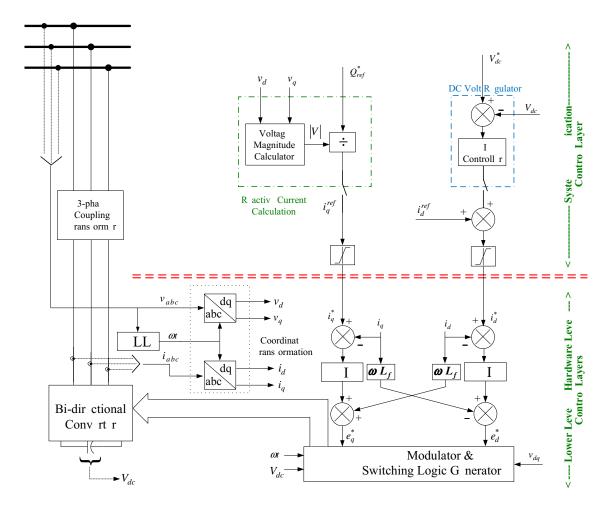

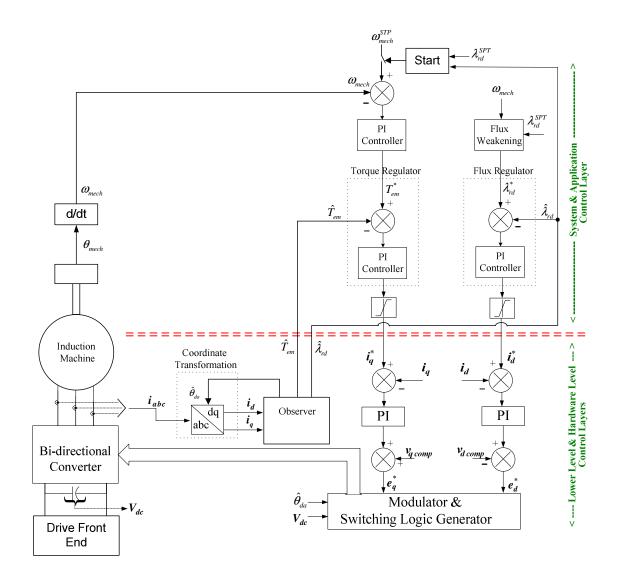

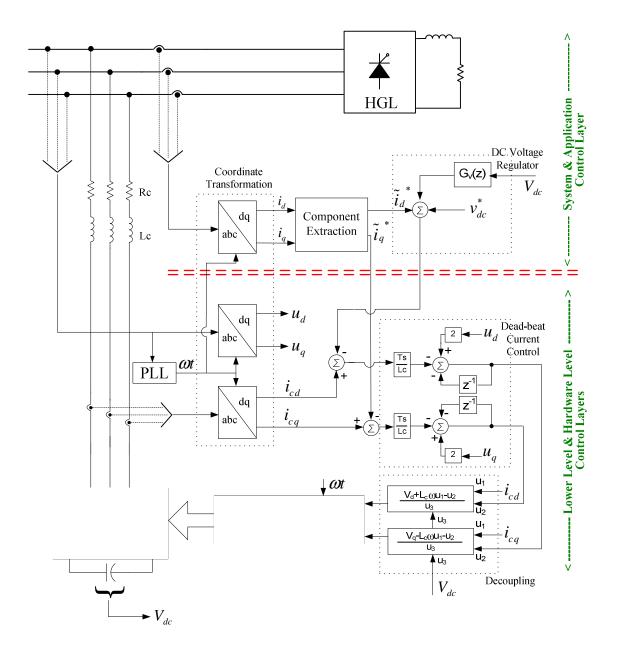

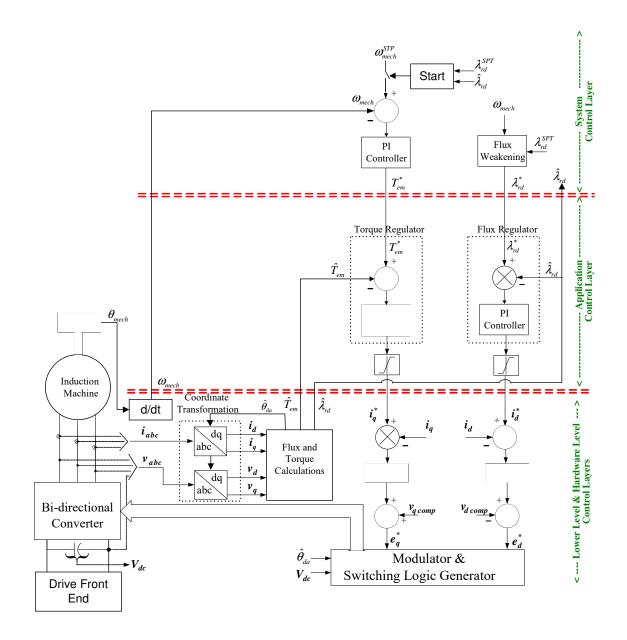

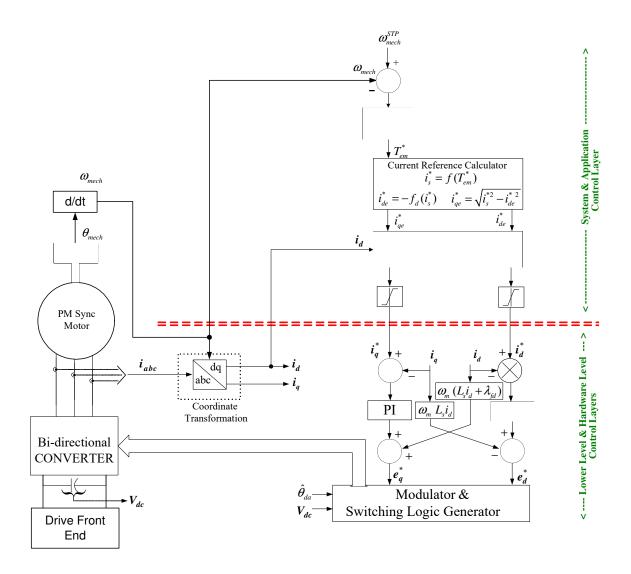

| 3.10   | Rotor flux orientation vector control induction motor drive                                                                 | 32   |

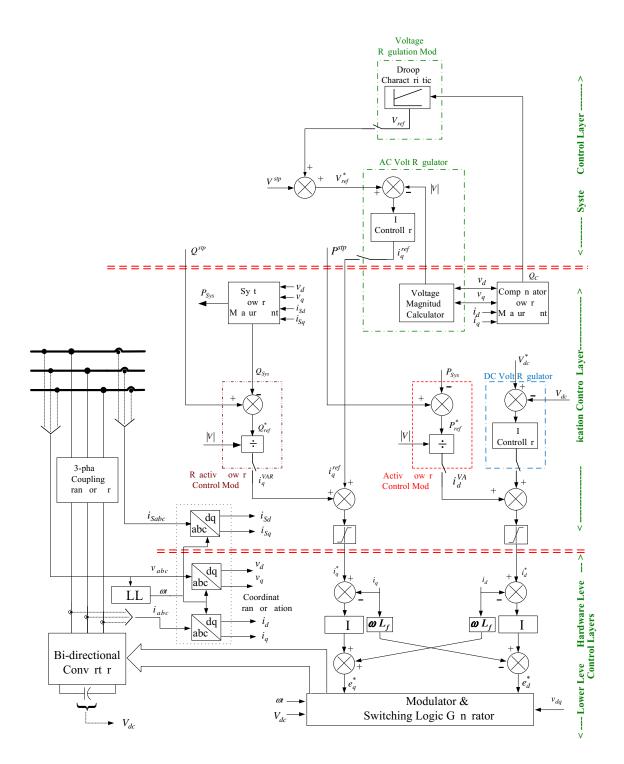

| 3.11   | Typical active compensator control functions with division between<br>lower functions and application plus system functions | 34   |

| 4.1    | Generalized STATCOM control structure with system to application control layer partition at $V_{ref}^*$                     | 39   |

| 4.2    | Generalized STATCOM control structure with system to application control layer partition at $i_q^{ref}$                     | 40   |

| 4.3 | Overall system control of the VDC-HVDC power transmission system                                                                                       | 42 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.4 | Control system of a grid connected converter                                                                                                           | 43 |

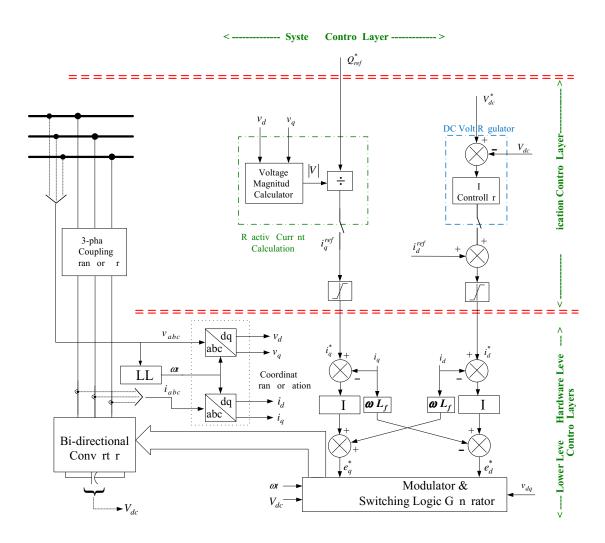

| 4.5 | HVDC control structure with system to application control layer partition at $V_{ref}^*$                                                               | 46 |

| 4.6 | HVDC control structure with system to application control layer partition at $i_q^{ref}$                                                               | 47 |

| 4.7 | Control structure of an active rectifier                                                                                                               | 48 |

| 4.8 | Rotor flux orientation vector control induction motor drive                                                                                            | 50 |

| 5.1 | The control block diagram of voltage loop                                                                                                              | 60 |

| 5.2 | Signal convention at the system to application partition interface                                                                                     | 64 |

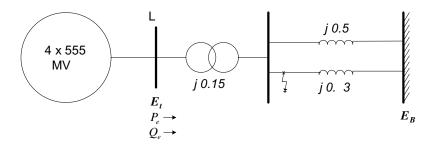

| 6.1 | Power system representation consisting of four 555 MVA, 24 kV, 60 Hz units                                                                             | 66 |

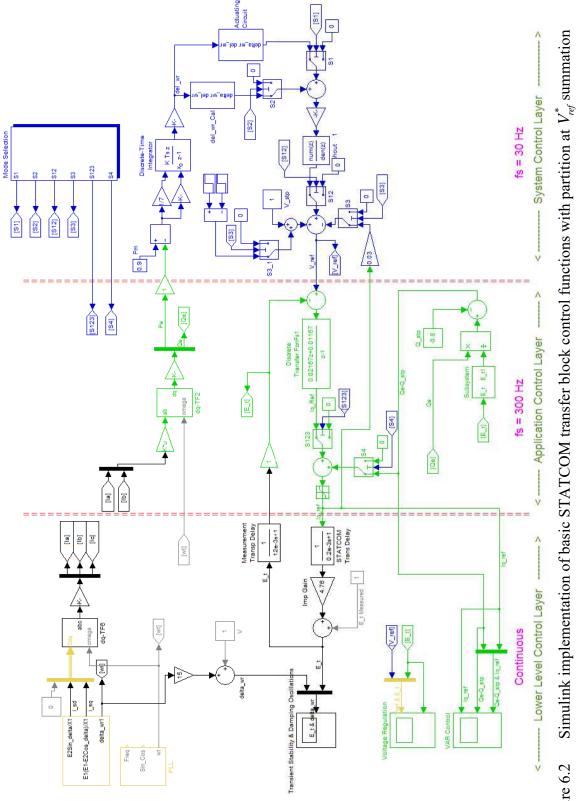

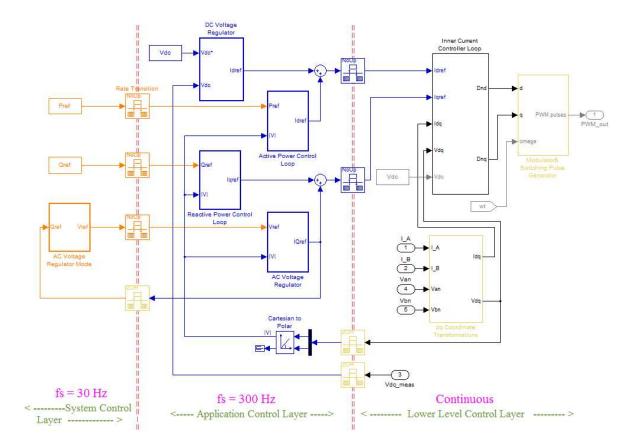

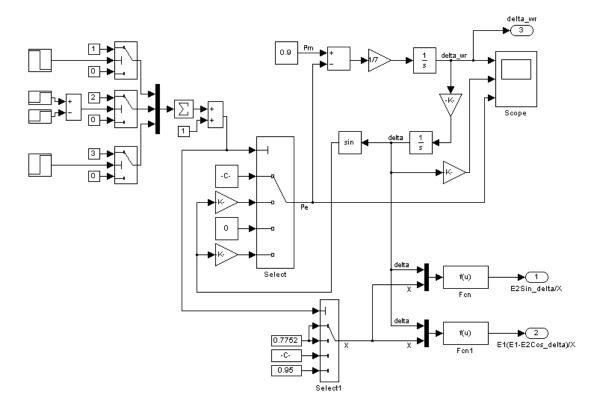

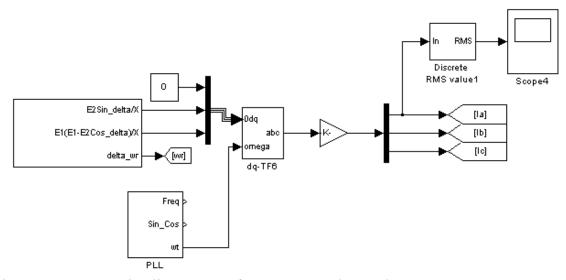

| 6.2 | Simulink implementation of basic STATCOM transfer block control functions with partition at $V_{ref}^*$ summation                                      | 70 |

| 6.3 | Simulink implementation of basic STATCOM transfer block control functions with partition at $i_q^{ref}$ summation                                      | 71 |

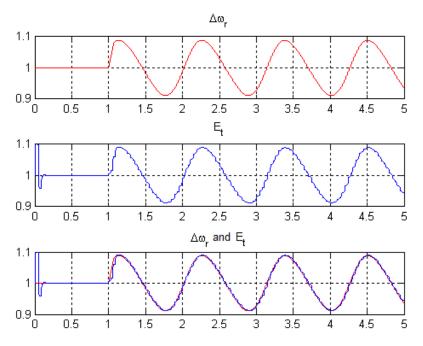

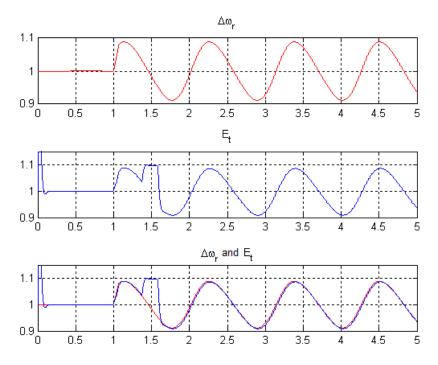

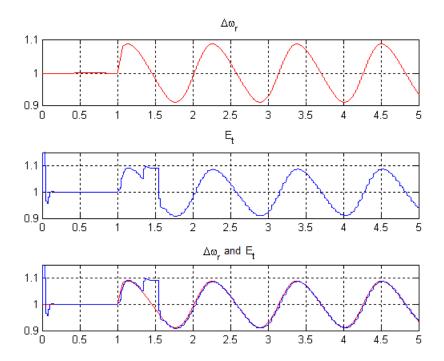

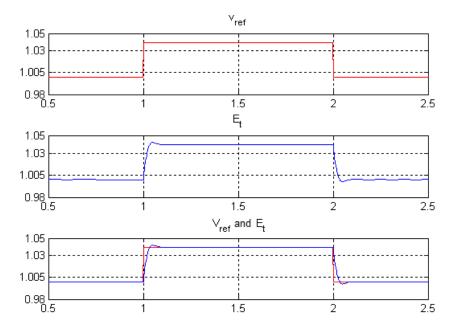

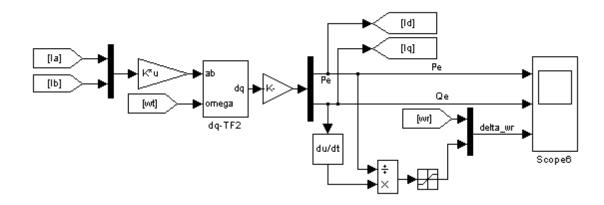

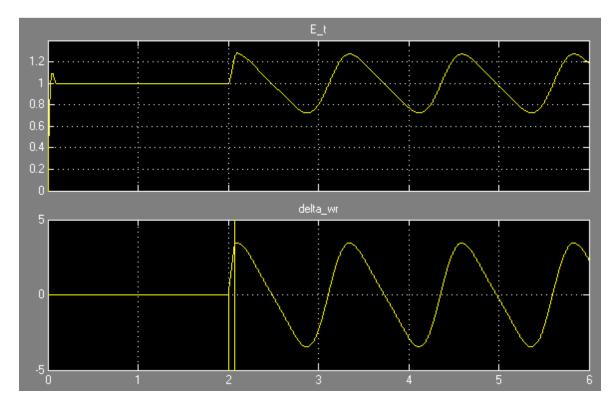

| 6.4 | Variation of terminal voltage (E <sub>t</sub> ) in proportion to the rotor angle variation in STATCOM oscillation damping mode - $V_{ref}^*$ partition | 72 |

| 6.5 | Variation of terminal voltage (E <sub>t</sub> ) in proportion to the rotor angle variation in STATCOM oscillation damping mode - $i_q^{ref}$ partition | 72 |

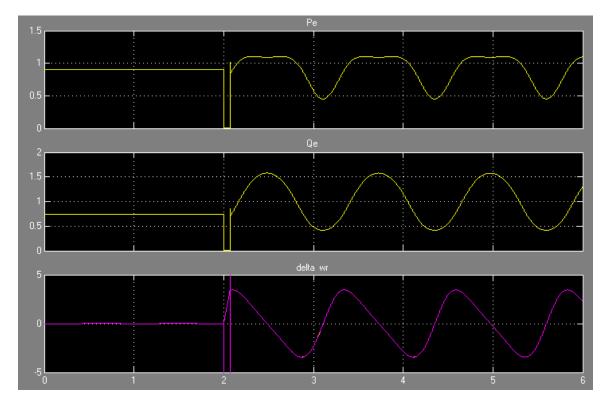

| 6.6 | Improvement of first swing stability limit with STACOM transient stability enhancement - $V_{ref}^*$ partition                                         | 73 |

| 6.7 | Improvement of first swing stability limit with STACOM transient stability enhancement - $i_q^{ref}$ partition                                         | 73 |

|     |                                                                                                                                                        |    |

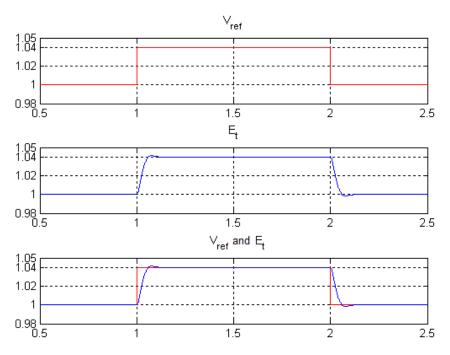

| 6.8  | Response of the STATCOM terminal voltage $E_t$ to a change in voltage reference value $V_{ref}$ while operating in voltage regulation mode - $V_{ref}^*$ |          |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

| 6.9  | partition                                                                                                                                                | 74<br>75 |  |

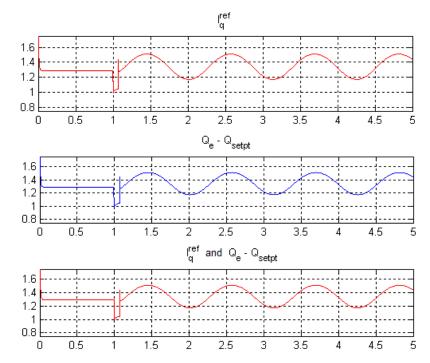

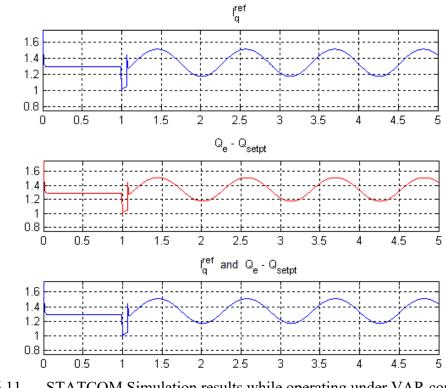

| 6.10 | STATCOM simulation results while operating under VAR control mode- $V_{ref}^*$ partition                                                                 | 76       |  |

| 6.11 | STATCOM simulation results while operating under VAR control mode - $i_q^{ref}$ partition                                                                | 76       |  |

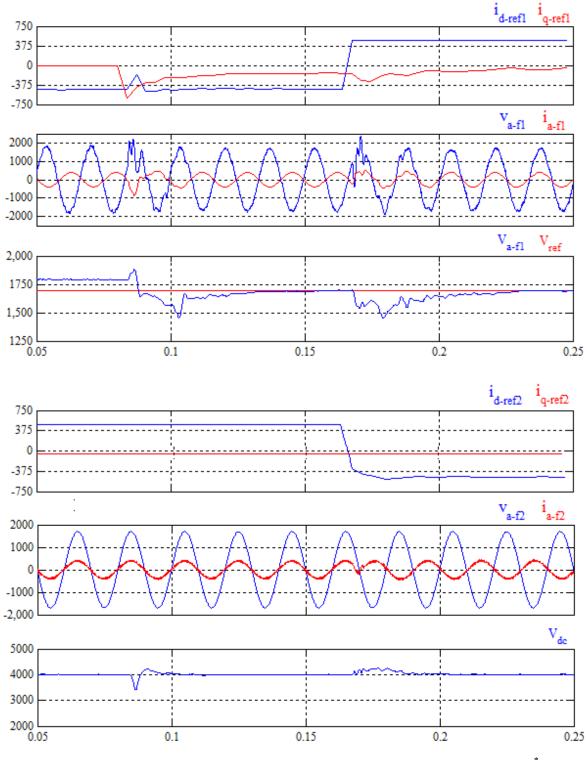

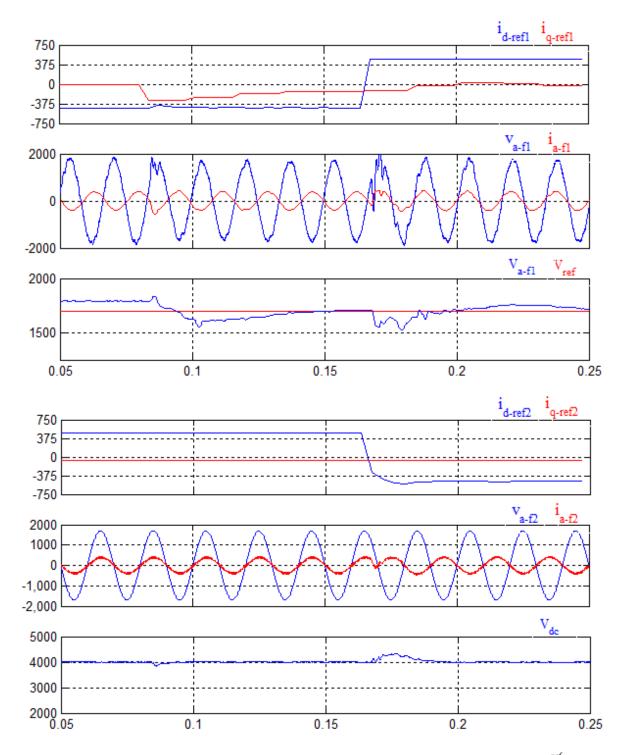

| 6.12 | MATLAB/Simulink simulation control structure for HVDC partitioning at $V_{ref}^{*}$                                                                      | 78       |  |

| 6.13 | MATLAB/Simulink simulation results for HVDC partitioning at $V_{ref}^*$                                                                                  | 79       |  |

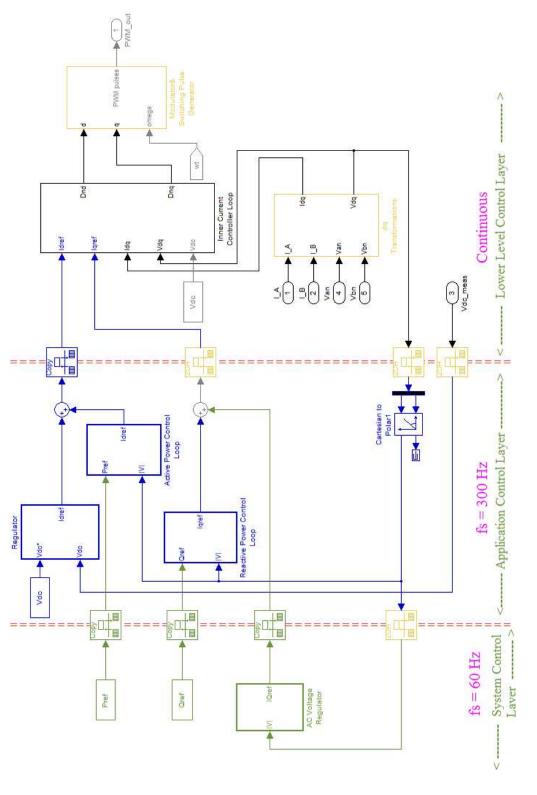

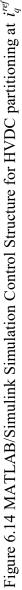

| 6.14 | Simulation control structure for HVDC partitioning at $i_q^{ref}$                                                                                        | 80       |  |

| 6.15 | MATLAB/Simulink simulation results for HVDC partitioning at $i_q^{ref}$                                                                                  | 81       |  |

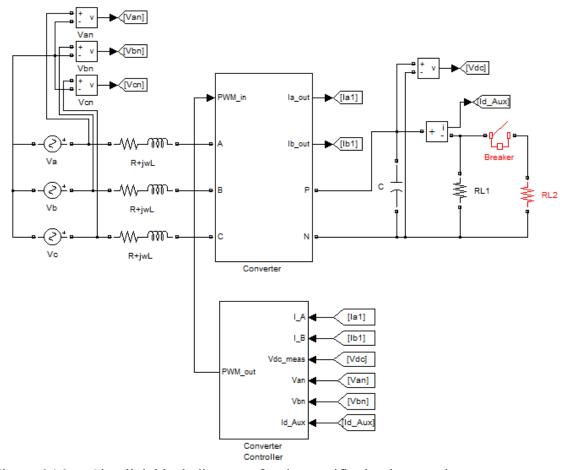

| 6.16 | Simulink block diagram of active rectifier implementation                                                                                                | 82       |  |

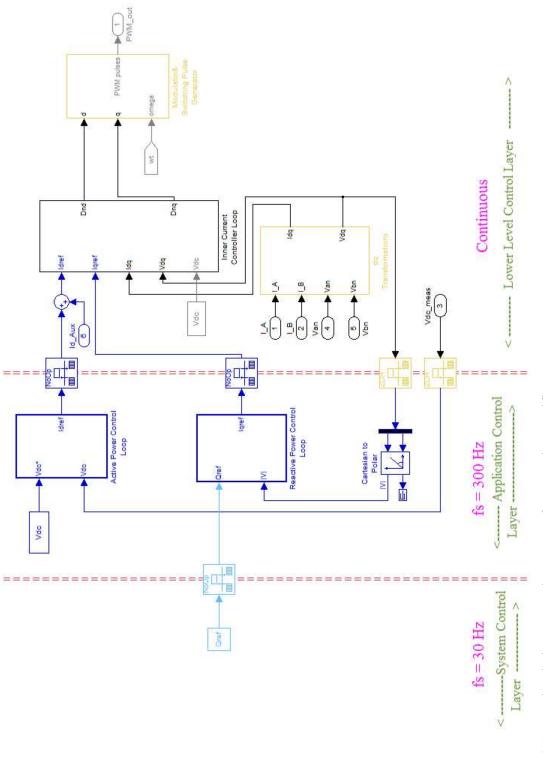

| 6.17 | Simulation control structure for an active rectifier                                                                                                     | 83       |  |

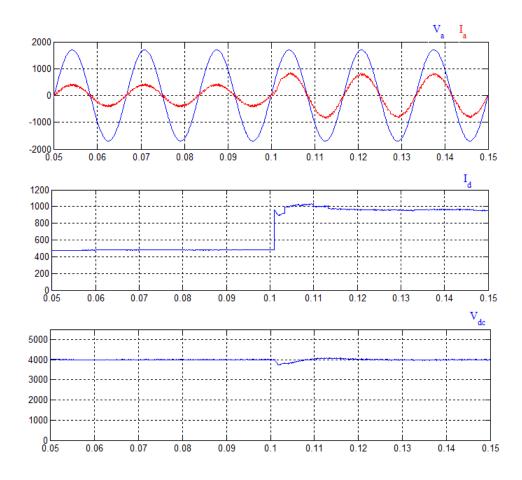

| 6.18 | MATLAB/Simulink simulation results for an active rectifier                                                                                               | 84       |  |

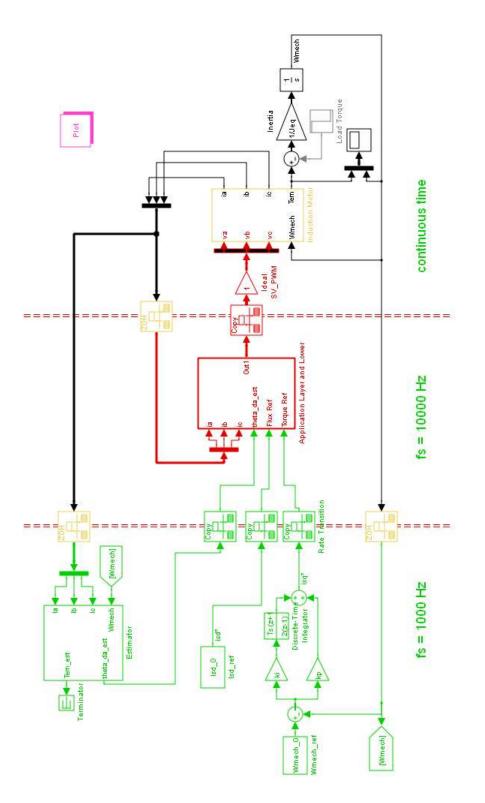

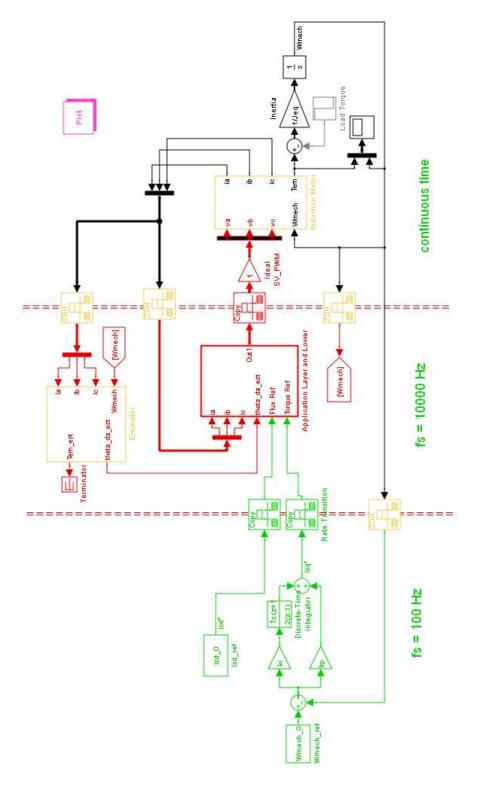

| 6.19 | Partitioned model of a vector controlled motor drive with estimation<br>in the system control layer                                                      | 86       |  |

| 6.20 | Partitioned model of a vector controlled motor drive with estimation below the system control layer                                                      | 87       |  |

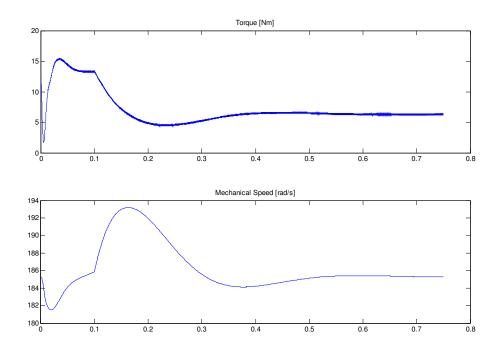

| 6.21 | Torque and speed for the partition and sampling times shown in Figure 6.19                                                                               | 88       |  |

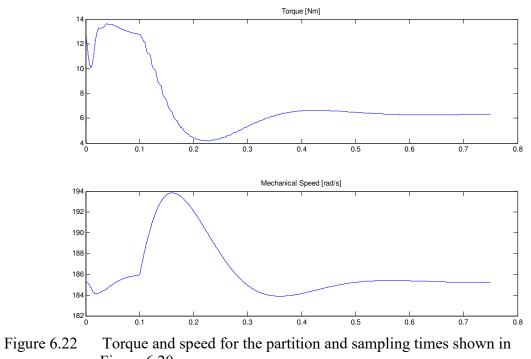

| 6.22 | Torque and speed for the partition and sampling times shown in Figure 6.20.                                                                              | 88       |  |

| 7.1 | Generalized grid connected converter control structure                                                                                                     | 91  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A.1 | STATCOM control structure for VAR control                                                                                                                  | 105 |

| A.2 | STATCOM control structure for voltage regulation                                                                                                           | 106 |

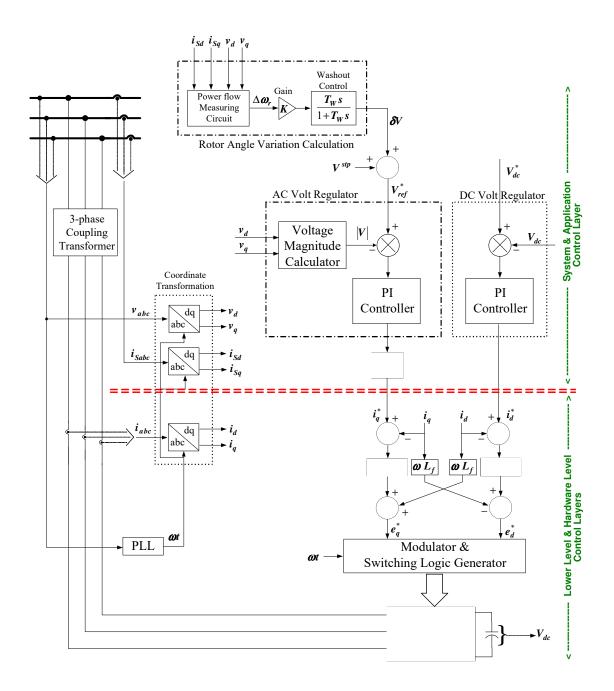

| A.3 | STATCOM control structure for power oscillation damping                                                                                                    | 107 |

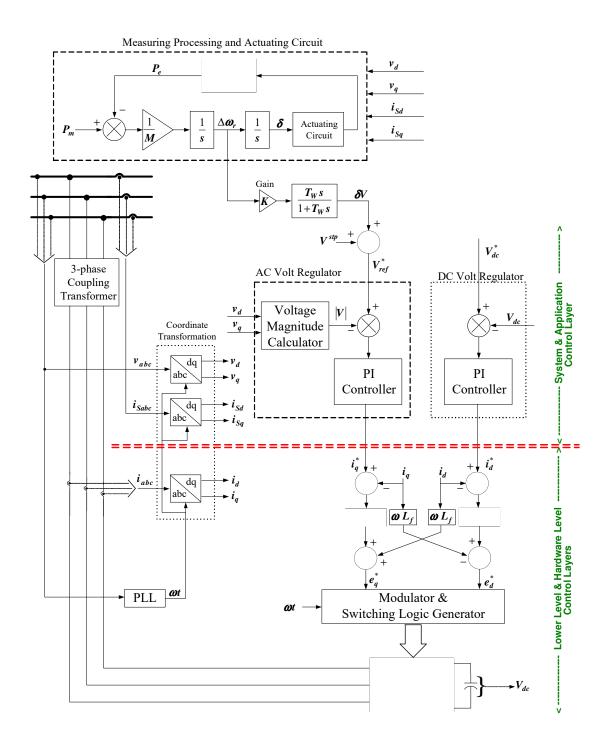

| A.4 | STATCOM control structure for transient stability enhancement                                                                                              | 108 |

| A.5 | Indirect vector control permanent magnet synchronous motor drive                                                                                           | 109 |

| A.6 | Active filter application using the digital IIR filter harmonic extraction method in the d-q reference frame                                               | 111 |

| A.7 | Active filter application using the frequency domain RDFT harmonic extraction method in the d-q reference frame                                            | 112 |

| C.1 | Simulink power system model for all three-system conditions:<br>a) prefault, b) during fault and c) postfault                                              | 124 |

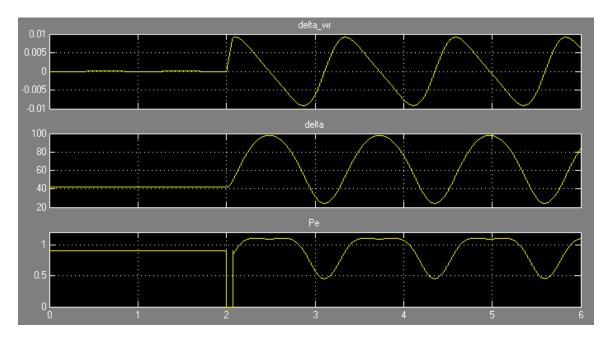

| C.2 | Rotor angle speed (delta_wr, $\Delta \omega_r$ ), rotor angle (delta, $\delta$ ),<br>and active power flow ( $P_e$ ) for clearing time of $t_c = 0.07$ sec | 125 |

| C.3 | Extracting line currents from current orthogonal components                                                                                                | 126 |

| C.4 | Obtaining rotor angular speed variation (delta_wr, $\Delta \omega_r$ )<br>from line currents                                                               | 127 |

| C.5 | Active power flow $(P_e)$ , reactive power flow $(Q_e)$ , variation in rotor angle speed (delta_wr, $\Delta \omega_r$ ) obtained from the formula          | 127 |

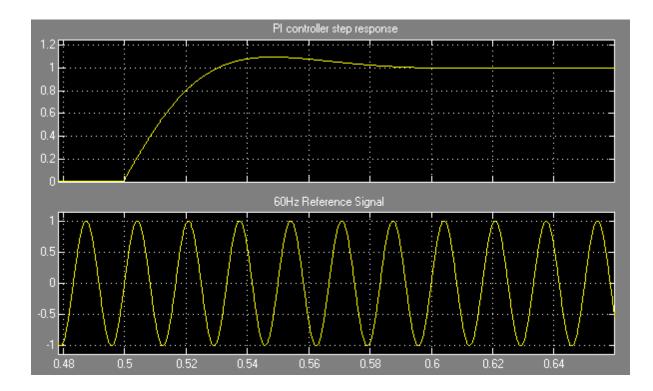

| C.6 | PI-controller unit step response for a desired settling time of 0.1 second                                                                                 | 128 |

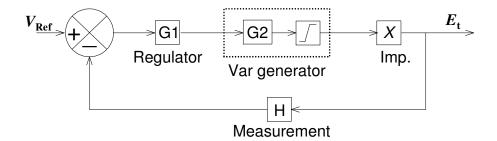

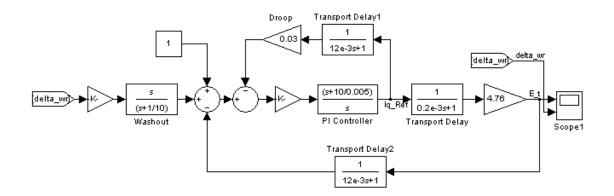

| C.7 | Basic transfer function block diagram of the STATCOM                                                                                                       | 129 |

| C.8 | MATLAB/Simulink implementation of basic transfer block diagram including an AC voltage regulator                                                           | 130 |

| C.9 | Variation in the terminal voltage (E_t, $E_t$ ) with variation<br>of rotor angular speed (delta_wr, $\Delta \omega_r$ )                                    | 130 |

#### CHAPTER I

#### INTRODUCTION

This chapter introduces the dissertation topic by giving a brief background on layered control architecture of three-phase power electronic converters used in utility and industrial applications. Also, it addresses the research problem by recognizing the issues in the power electronic business with regard to the control interfaces and current design practices.

#### **1.1 Topic Background**

Applications of power electronics in power systems are growing very rapidly and changing the power system infrastructure in terms of operation speed and control. The cost and reliability of the power electronics are the issues that could hinder the penetration of their applications in utility systems. Recognizing these issues while supporting high power density and high-speed operation for high power applications, the Power Electronics Building Block (PEBB) concept has been proposed [1]. In the construction of PEBB based modular systems, the characteristics of the interfaces between the control modules are of prime importance [1]-[2]. Presently power electronic systems especially in the medium and high-power range, employ custom control architectures and their control interfaces and control modules are also specific to the type and manufacturer [3]. This limits the system designer's choices when considering the power electronic converters for various power system applications. Thus, an open architecture power converter system with standardized modules and control interfaces was introduced that would allow system designers to explore the design space much more effectively [2]. This architectural openness would contribute to healthy industrial competitiveness and reduction of the recurring engineering costs.

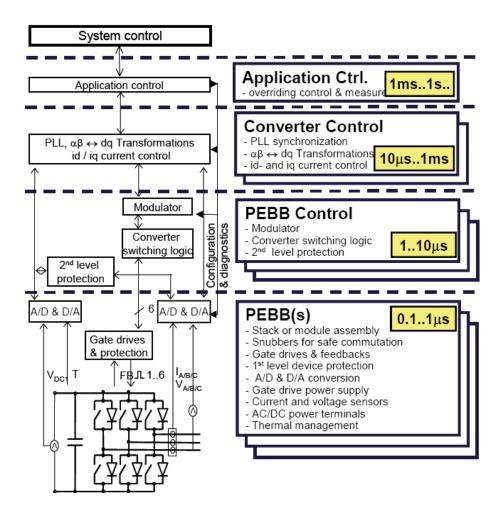

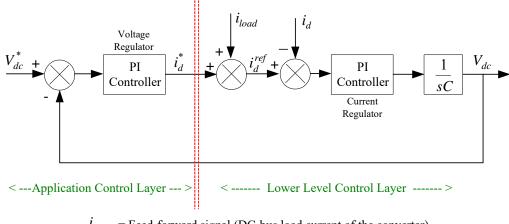

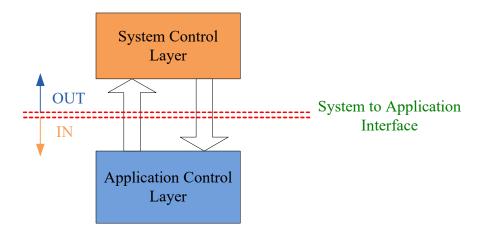

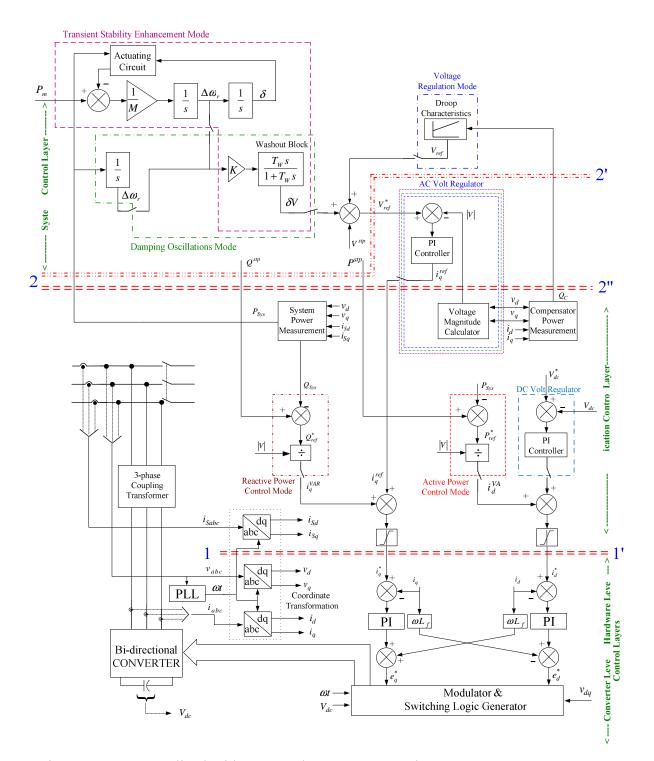

The concept of the PEBB as a basic building block in power conversion has been developed and analyzed for generic power electronics applications [1]. When control functions of many different power converter systems are investigated and evaluated, at the lower level control layers, a common control functionality emerges irrespective of the target application [2], [4]. Using the concept of system level layers, it is possible to define hierarchical control architectures for these systems. A block diagram of the layered control architecture of a power electronic converter system is shown in Figure 1.1. The control architecture is partitioned into several common control layers. A system control layer determines the overall mission of the system, application control layer dictates the operation of the overall mission of the system, converter control layer implements many of the common functions of converters, switching control layer handles modulation and pulse generation, and the hardware control layer manages all operations specific to the power hardware.

Figure 1.1 Control architecture for a power electronic converter system [5].

The control partitioning approach, based on functional and temporal distribution into system layers, is considered to be a basic step towards modularization [4]. Controller partitioning of power converter architecture alone is not sufficient and will not provide significant advancements in power electronics technology if partition interface standardization is not achieved in parallel. Finding common denominators for different power architectures and standardizing interfaces between layers could bring a new constructive approach to power electronics design and practice [6], [7]. In the literature [2], [4], an Open System hierarchical Architecture (OSA) is proposed, based on functional distribution, to standardize control architecture in power converter applications using the concept of hierarchical system layer partitioning. The objective of OSA is to standardize the PEBB based controller design through standardization of interface between layers from a set of common basic functions. OSA also suggests that the partition for a power converter system control involving multiple subsystems should have several levels or layers corresponding to a system control layer, an application control layer, and low-level control layers (converter/functional layer, switching layer, and the PEBB hardware control layer).

Some work in standardizing the control architecture [2] has presented the partitioning interface characteristics and requirements of low-level control layers by showing that the control functions are nearly uniform for all type of converters. It has also shown that there is a variation in control functions, in the application/middle control layer, depending on applications. This variation is because of the functional blocks corresponding to the reference signal generation having employed a different control reference frame according to the application. This does not allow the OSA to provide flexibility of operation at the upper or system and application control layers. In order to construct functional flexible power converter control architecture, the possible commonality in system and application control functions, along with the partitioning interface requirements between the system control layer and application control layer, need to be explored.

#### **1.2** Objective of Dissertation

As discussed in the topic background some example implementations [2] using the OSA concept showed that there is a set of common functions shared by different converters at the low-level control layer. It has also showed that there is a variation in control function, in the application/middle control layer, depending on application. This functional variation makes it difficult to define a common functionality of power converters at the upper control layers and further complicates the investigation into the partition requirements of the system to application control layer. However, by analyzing the current or voltage affected by a converter in terms of orthogonal components [8], where each component or group of components is associated with a power-converter application, and the amount of required DC bus energy storage, a common functionality can be observed at the application control layer that contributes to determining the partitioning requirements of the system to application control layer partition. Thus, by establishing common functionality in terms of affected current or voltage components, a flexibility of operation can be realized at upper control layers that will be a major contribution towards standardizing the open system architecture.

The goal of this research is to determine the appropriate partitioning and interface requirements between the system and application control layers for systems of power electronic converters so that the minimum set of system layer to application layer control interfaces is compatible across all power electronic controllers. This will provide flexibility of system design methodology by reducing the number of constraints and enabling system designers to explore possible system architectures much more effectively. The research plan consists of several aspects, including investigation into appropriate control layers, partitioning of their interfaces, finally the modeling and simulation in order to validate the suggested interface requirements.

#### 1.3 Approach

This research is mainly focused on three-phase power converters widely used in power system utility and industrial applications like Power Quality, Flexible AC Transmission Systems (FACTS), High Voltage DC Transmission (HVDC), Distributed Generation and Motor Drive applications, etc. Three-phase converter topologies consist of either Shunt Connected Current Controllers (ShCC), Series Connected Voltage Controllers, or a combination of the two [9], but shunt converters are more common. Therefore, the work will focus on shunt connected converter systems with an expectation that the approach can be extended to series connected converters. The working approach for the proposed research consists of three major tasks:

#### Task 1: Application Control Layer to Converter Control Layer Partitioning

Separating the application and system control functions from the lower level control functions so that the boundary location between the system and application control layers can be explored.

Task 2: System Control Layer to Application Control Layer Partition

Determining the effect of boundary location on the system to application control layer partition interface based on the following criteria: total number of interface signals, commonality of signals across the typical applications, and bandwidth requirements of the signals. Task 3: Modeling and Simulation

Validating system and application control layer partitioning interface requirements using simulations for several example applications.

#### **1.4** Dissertation Outline

The dissertation is organized as follows: Chapter II gives a background view on the principles of control partitioning in power electronic converter architectures. Chapter III presents a formulated criterion of application control layer to converter control layer partitioning for three phase power converters. Chapter IV presents system control layer to application control layer partitioning. This is based on developing generalized control architectures for several power converter applications. Chapter V explores partition and temporal requirements through various options and considerations in the partitioning of system control layer to application control layer. Chapter VI addresses modeling, and validation of partition requirements between the system control layer and application control layer interface using MATLAB/Simulink models. Chapter VII gives a definition for the system to application control layer interface so that it is compatible across all power electronic controllers. Chapter VIII includes the conclusions and future work.

#### CHAPTER II

#### PRINCIPLE OF CONTROL PARTITIONING

Chapter I introduced the concept of layered control architecture and mentioned that in the construction of modular power electronics converter systems, the characteristics of the interfaces between the modules are of prime importance. This chapter presents the criteria behind the partitioning of the system components into a hierarchical layered architecture.

#### 2.1 Partition Criteria

In the literature [6], [10], the general partitioning of control architecture was proposed for generic power electronics systems and is based on following criterion [2]:

- Functional distribution

- Temporal distribution: protection, switching frequency and modulation, time constants and control bandwidth.

- Technology distribution: physical nature of values and property of materials, and manufacturing process.

- Spatial distribution: power level and system requirements.

"All four criteria: functional, temporal, spatial, and technological criteria can be used for partitioning of the control functions. However, because technology distribution and spatial distribution are specific to particular implementations, functional and temporal distributions are considered to be the driving criteria. It is expected that both technology and spatial distributions may modify the distributions for particular implementations. Furthermore, in a majority of cases functional and temporal distributions will naturally occur at the same boundaries," [11]. Figure 1.1, shown in Section 1.1, is a typical voltage source power electronic converter application with a partition of the control system based on functional and temporal distribution.

In order to determine the locations of the control layer boundaries it is instrumental to categorize power electronic systems into one of three broad categories: Shunt Connected Current Controller, Series Connected Voltage Controllers, and Impedance Controllers [9]. The criteria for establishing the boundary locations for lower level control layers are listed as follows:

*Converter Control Layer*: The converter control layer implements many of the common functions of converters. It is responsible for maintaining such functions as synchronous timing (PLL), current and voltage filtering, measurements, and feedback control calculations. Thus, the functional control layer will have some common functions depending on the particular target applications. The primary application of this layer is the feedback control system, while the other components support the input and output requirements of the feedback control system.

Switching Control Layer: The switching control layer will contain many common functions irrespective of the final application. The functions include switching or modulation control, and pulse generation. The switching control layer and all lower layers enable the power electronics to behave as a PWM controller source. Here the PWM controlled source is defined as having its terminals directly at the power terminals of the power electronics hardware.

*Hardware Control Layer*: The hardware control layer manages everything specific to the power electronics, and it may exist as multiple modules depending on final power configurations. Gating, measurements, galvanic isolation, safe commutation and 1<sup>st</sup> level protection are functions of this layer and will be common for virtually any PEBB based application.

Determining the partition criteria for upper control layers, system control layer and application control layer, and their interface requirements are primary objectives of this dissertation and these will be discussed in detail in the remaining chapters.

#### 2.2 Typical Control Architectures

Two main types of power electronic converter systems used in power distribution and industrial applications are shunt connected current controllers (ShCC) and series connected voltage controllers (SeVC) [9]. Shunt connected current controllers can be grouped by applications [2], [8] where the bi-directional voltage source converter is the basic power electronic module. It is also the basic module for series connected voltage controllers. Table 2.1 lists some common shunt connected current controllers for distribution system applications and Table 2.2 lists some series connected voltage controllers, where HGL denotes a harmonic generation load.

The available amount of current for shunt connected devices depends on the voltage at the point of connection and the available voltage drop across series devices depends on the current in the system. Thus, they behave as controlled impedances. From

the standpoint of the system control there is no difference between the controlled impedance and the controlled voltage or current source, with the exception of their operating limits.

| Converter System<br>Description                | Function                                                                                                     | Simple One-line Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Active Filter                                  | Cancel harmonic currents by<br>injecting appropriate current into<br>the node                                | $ \begin{array}{c c} i & i_{L} \\ \downarrow i_{h} \\ \downarrow L_{c} \\ \downarrow \downarrow \downarrow \\ \downarrow \downarrow \downarrow \\ \downarrow \downarrow \downarrow \\ \downarrow \downarrow \downarrow \downarrow $                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Static Synchronous<br>Compensator<br>(STATCOM) | Provide desired reactive current for<br>VAR compensation, voltage<br>regulation and stability<br>enhancement |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Mini-HVDC<br>(HVDC Light)                      | Provide interconnection between<br>two AC nodes for active and<br>reactive power flow control                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Energy Storage System<br>Interface             | Provide active power for load<br>leveling or UPS function                                                    | $i  i_{L}  \text{Loads}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Active Front End for<br>Motor Drives           | Provide active and reactive power<br>for motor VSD                                                           | $ \begin{array}{c c} i & i_{L} \\  & \downarrow i_{a,r} \\  & \downarrow L_{c} \\  & \downarrow L_$ |

Table 2.1Some typical shunt connected current controller applications [8].

| Converter System<br>Description                 | Function                                                                                           | Simple One-line Diagram |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------|

| Series Active Filter                            | Cancel voltage harmonics by<br>adding a cancelling voltage drop<br>into the line                   |                         |

| Static Synchronous Series<br>Compensator (SSSC) | Provide desired voltage for VAR<br>compensation, voltage regulation<br>and stability enhancement   |                         |

| Inter line Power Flow<br>Controller (IPFC)      | Provide interconnection between<br>multiple AC nodes for active and<br>reactive power flow control |                         |

Table 2.2Some typical series connected voltage controller applications.

Although each of the applications in the three basic classes discussed in Table 2.1 and Table 2.2 have the same basic circuit structure within a class, each one is made unique and has fixed and limited application due to custom control architectures and interfaces that are tailored to the specific application. This does not provide the flexibility of operation at the upper or system and application control layers. In order to construct functional flexible power converter control architecture, the interface requirements to the system control layer and the partitioning between the system control layer and application control layer need to be explored. As mentioned above, both shunt and series connected converters are employed to implement different power electronic applications, but shunt converters are more common. Therefore, the rest of the work will focus on shunt connected converters with the expectation that the approach can be extended to series connected controllers.

#### CHAPTER III

## APPLICATION CONTROL LAYER TO CONVERTER CONTROL LAYER PARTITIONING

The criteria for establishing the boundary locations for lower level control layers were given in Chapter II. This chapter introduces a formulated criterion of application control layer to converter control layer partitioning for three phase power converters. The application and system control functions are then separated from the lower level control layers for each of the typical applications outlined in Table 2.1 of Chapter II.

#### **3.1** Partition Criteria

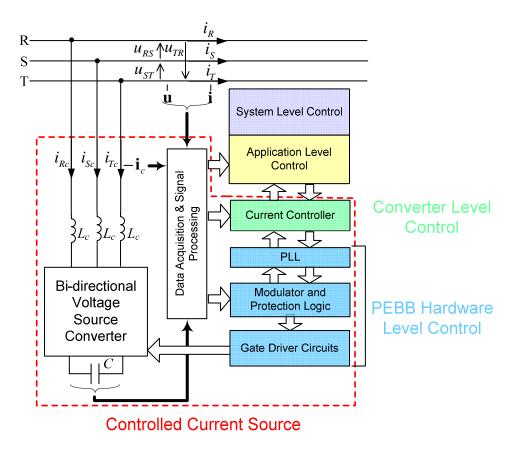

In power converter applications the shunt connected current controllers are used when particular components of the current are drawn from or injected into a system. The operating principle of ShCC is like a controlled current source where the application dictates the functionality of the control components that generate the reference current. Thus, the lower-level control layers with ShCC converter topology behave as a controlled current source. This will be selected as the criteria for the division of lower control layers from the application and system control layer. Figure 3.1 depicts a simplified ShCC with the control partitioned into four layers [8]. The converter layer and hardware layer controls enable the PEBB hardware to behave as a controlled current source, as depicted by the dashed line. All control layers that act to create high power current source using the PEBB hardware are considered as those control layers that are below the application and system layers. The application and system control functions will be separated from the lower control layers for all typical applications of converter topologies.

Similarly, the operating principle of the series connected voltage source converters is like a controlled voltage source. Thus, the lower-level control layers with SeVC converter topology behave as a controlled voltage source and those that enable it to behave as such are separated from the application and system control layers. Therefore, the same approach can be applied to the SeVC class of applications.

Some typical shunt connected current controller applications shown in Table 2.1 along with current components affected are summarized in Table 3.1, where each current orthogonal component or group of components associated with a ShCC application [8] were shown in column III of Table 3.1. Here, the components  $i_a$ ,  $i_r$ ,  $i_u$  are the active, reactive and unbalanced components of the current fundamental respectively,  $i_h$  is the current component that corresponds to harmonics present in the system and  $i_c$  is the overall converter current.

Figure 3.1 Functional diagram of a converter with partitioned control architecture.

| Converter System<br>Description                | Function                                                                                                        | Current<br>Components                                             | Simple One-line<br>Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Active Filter                                  | Cancel harmonic currents<br>by injecting appropriate<br>current into the node                                   | Affected<br>$i_c = i_h$ $i_c = i_h + i_r$ $i_c = i_h + i_r + i_u$ | $ \begin{array}{c c} i & i_{L} \\ \downarrow i_{h} \\ \downarrow L_{c} \\ \downarrow L_$ |

| Static Synchronous<br>Compensator<br>(STATCOM) | Provide desired reactive<br>current for VAR<br>compensation, voltage<br>regulation and stability<br>enhancement | $i_c = i_r$                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |