Mississippi State University Scholars Junction

Theses and Dissertations

Theses and Dissertations

8-17-2013

# Design Modifications and Platform Implementation Procedures for Supporting Dynamic Partial Reconfiguration of FPGA Applications

Sean Gabriel Owens

Follow this and additional works at: https://scholarsjunction.msstate.edu/td

#### **Recommended Citation**

Owens, Sean Gabriel, "Design Modifications and Platform Implementation Procedures for Supporting Dynamic Partial Reconfiguration of FPGA Applications" (2013). *Theses and Dissertations*. 1302. https://scholarsjunction.msstate.edu/td/1302

This Graduate Thesis - Open Access is brought to you for free and open access by the Theses and Dissertations at Scholars Junction. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Scholars Junction. For more information, please contact scholcomm@msstate.libanswers.com.

Design modifications and platform implementation procedures for supporting dynamic partial reconfiguration of FPGA applications

By

Sean Gabriel Owens

A Thesis

Submitted to the Faculty of Mississippi State University in Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical and Computer Engineering in the Department of Electrical and Computer Engineering

Mississippi State, Mississippi

August 2013

Copyright by

Sean Gabriel Owens

Design modifications and platform implementation procedures for supporting dynamic

# partial reconfiguration of FPGA applications

By

Sean Gabriel Owens

Approved:

Thomas H. Morris Assistant Professor Electrical and Computer Engineering (Director of Thesis) Yoginder S. Dandass Associate Professor Computer Science and Engineering (Committee Member)

Bryan A. Jones Associate Professor Electrical and Computer Engineering (Committee Member) James E. Fowler Professor Electrical and Computer Engineering (Graduate Program Director)

Jerome A. Gilbert Interim Dean of the Bagley College of Engineering

### Name: Sean Gabriel Owens

Date of Degree: August 17, 2013

Institution: Mississippi State University

Major Field: Electrical and Computer Engineering

Major Professor: Dr. Tommy Morris

Title of Study: Design modifications and platform implementation procedures for supporting dynamic partial reconfiguration of FPGA applications

Pages in Study: 141

Candidate for Degree of Master of Science

Dynamic partial reconfiguration of FPGAs allows systems to autonomously alter sections of their design during runtime based on the state of the system. This functionality provides size, weight, and power benefits that are useful in extreme environments such as space. Therefore, NASA has requested research into the feasibility of using a commercial off-the-shelf software flow to convert a static HDL design to support partial reconfiguration. This project presents an analysis of this conversion process using the Xilinx Partial Reconfiguration Flow to convert the static design for the ITU G.729 Voice Decoder. This paper explores the design modifications that must be made to allow for partial reconfiguration. Furthermore, an in-depth description of how to set up the hardware platform to support the HDL application is provided. Finally, timing and size data are presented and analyzed to empirically show the benefits and limitations of using dynamic partial reconfiguration.

# DEDICATION

This work is dedicated to my sister, Stephanie Lynn.

#### ACKNOWLEDGEMENTS

This material is based upon work supported by the National Science Foundation under Grant No. DGE-0947419 at Mississippi State University. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect the views of the National Science Foundation.

I would like to first thank the Mississippi Space Grant Consortium and National Science Foundation for funding the research that made this project possible. I would also like thank my family, Sherryl, John, Perryl, Jim, Evie, Jill, Justin, Dave, Matthew, and Michael for always supporting me throughout my childhood and my graduate school career. I also want thank my friends Hannah W., Hannah B., Kasey, Erin J., Erin A., and Leilani for always rooting for me. I want to especially thank Matt B. for being there for me when I needed help or to keep pushing me when I needed motivation. Finally I would like to thank the members of the CODEC team whose work was critical in being able to do this work: Zach, Troy, Mike, Parker, Nick, Cooper, Josh, David, Corey, Walter, Doug, Jeff, and Seth.

# TABLE OF CONTENTS

| DEDICA  | TION              |                                                                                                                                                                                                                                                        | ii                         |

|---------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| ACKNOV  | VLEDO             | GEMENTS                                                                                                                                                                                                                                                | iii                        |

| LIST OF | TABLE             | ES                                                                                                                                                                                                                                                     | vi                         |

| LIST OF | FIGUR             | ES                                                                                                                                                                                                                                                     | vii                        |

| LIST OF | ACRO              | NYMS                                                                                                                                                                                                                                                   | xi                         |

| CHAPTE  | R                 |                                                                                                                                                                                                                                                        |                            |

| I.      | INTR              | ODUCTION                                                                                                                                                                                                                                               | 1                          |

|         | 1.1<br>1.2<br>1.3 | Background<br>Motivation and Problem Statement<br>Previous Research and Significance of Work                                                                                                                                                           | 4                          |

| II.     | HDL               | DESIGN MODIFICATION                                                                                                                                                                                                                                    | 12                         |

|         |                   | Module Data Extraction<br>Reconfigurable Module Set Selection<br>Reconfigurable Module Port Set Selection and Abstraction<br>System Architecture Modification<br>4.1 Data Flow Architecture<br>4.2 External Signals<br>System Functionality Simulation | 17<br>21<br>27<br>27<br>30 |

| III.    |                   | AMIC PARTIAL RECONFIGURATION SYSTEM DESIGN<br>IMPLEMENTATION                                                                                                                                                                                           | 36                         |

|     | 3.1 Reconfigurable Module Unit Synthesis                       | 36 |

|-----|----------------------------------------------------------------|----|

|     | 3.2 Dynamic Partial Reconfiguration Hardware Platform          | 37 |

|     | 3.2.1 Platform Design and Synthesis                            | 37 |

|     | 3.2.2 Partial Reconfiguration Design and System Implementation | 39 |

|     | 3.3 Software Testing Platform                                  | 45 |

| IV. | RESULTS                                                        | 48 |

|        | 4.1 Design Size                                      |        |

|--------|------------------------------------------------------|--------|

|        | 4.1.1 Size Data                                      |        |

|        | 4.1.2 Size Analysis                                  |        |

|        | 4.2 Application Runtime                              |        |

|        | 4.2.1 Timing Data                                    |        |

|        | 4.2.2 Timing Analysis                                |        |

|        | 4.2.2.1 Test System Analysis                         |        |

|        | 4.2.2.2 Timing Analysis Extrapolation                |        |

|        | 4.2.2.3 PR Application Period                        |        |

| V.     | FUTURE WORK AND CONCLUSIONS                          |        |

|        | 5.1 Conclusions                                      |        |

|        | 5.2 Future Work                                      |        |

| REFERE | ENCES                                                | 61     |

| APPEND | DIX                                                  |        |

| А.     | G.729 DECODER TOP-LEVEL FSM                          |        |

| В.     | DYNAMIC PARTIAL RECONFIGURATION HARDWAF              | ₹E     |

|        | PLATFORM DEVELOPMENT TUTORIAL                        |        |

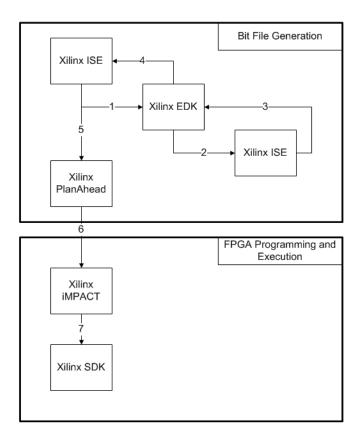

|        | B.1 File Structure                                   | 75     |

|        | B.2 ISE - Project Creation                           | 77     |

|        | B.3 XPS - System Design I                            |        |

|        | B.3.1 Base System Builder                            |        |

|        | B.3.2 Additional Peripheral Insertion (HWICAP)       |        |

|        | B.3.3 Create a Custom Peripheral                     |        |

|        | B.4 ISE - Custom Peripheral Modification             |        |

|        | B.5 XPS – System Design II                           |        |

|        | B.6 ISE - Project Synthesis                          |        |

|        | B.7 PlanAhead - Floorplanning and Bitfile Generation |        |

|        | B.7.1 Create a Project                               |        |

|        | B.7.2 Define a Reconfigurable Partition              |        |

|        | B.7.3 Floorplanning                                  |        |

|        | B.7.4 Design Implementation                          |        |

|        | B.7.5 Generate Bitstreams                            |        |

|        | B.8 XPS – Test Platform Initialization               |        |

|        | B.9 SDK – Test Platform Configuration                |        |

|        | B.10 iMPACT – FPGA Programming                       |        |

| C.     | DYNAMIC PARTIAL RECONFIGURATION DECODER              | SYSTEM |

|        | TESTING APPLICATION                                  |        |

# LIST OF TABLES

| 2.1 | ITU G.729 Decoder System Module Tree                      | 14 |

|-----|-----------------------------------------------------------|----|

| 2.2 | ITU G.729 Decoder Module Port Data                        | 16 |

| 2.3 | Port Abstraction Method Size Comparison                   | 27 |

| 3.4 | Reconfigurable Module Set Resource Requirements           | 42 |

| 4.1 | RM Resource Data                                          | 49 |

| 4.2 | Aggregated RM and Decoder Static Resource Requirements    | 50 |

| 4.3 | Static and Partial Reconfiguration Design Size Comparison | 50 |

| 4.4 | Timing Data for 1 Frame of Audio                          | 53 |

# LIST OF FIGURES

| 1.1  | ITU G.729 Operation Overview [25]                      | 3   |

|------|--------------------------------------------------------|-----|

| 1.2  | G.729 Decoder HDL Architecture                         | 4   |

| 1.3  | FPGA Configuration Memory                              | 5   |

| 1.4  | FPGA Partial Reconfiguration                           | 6   |

| 1.5  | DPR Testing Platform                                   | .11 |

| 2.1  | Port Abstraction – Superset Port Name Generalization   | .22 |

| 2.2  | Port Abstraction – Superset Port Set Selection         | .22 |

| 2.3  | Port Abstraction – Vector Port Set Selection           | .24 |

| 2.4  | Port Abstraction – Subset Port Set Selection           | .25 |

| 2.5  | Original Data Flow Architecture                        | .28 |

| 2.6  | Decoder Intermediate Data Flow Architecture            | .29 |

| 2.7  | Decoder Final Data Flow Architecture                   | .30 |

| 2.8  | Partial Reconfiguration Wait Time Without Optimization | .33 |

| 2.9  | Partial Reconfiguration Wait Time With Optimization    | .33 |

| 2.10 | Decoder Functional Simulation                          | .35 |

| 3.1  | DPR System Block Diagram                               | .38 |

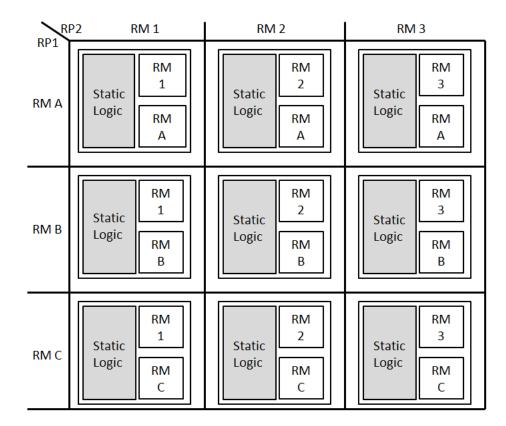

| 3.2  | FPGA Resource Structure                                | .41 |

| 3.3  | Design Configurations Example 1                        | .43 |

| 3.4  | Design Configurations Example 2                        | .44 |

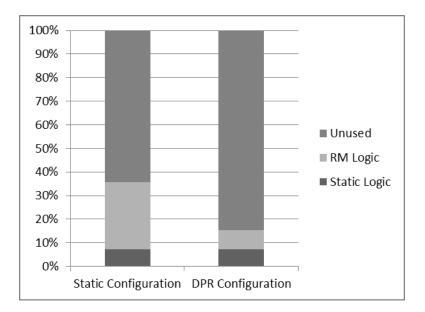

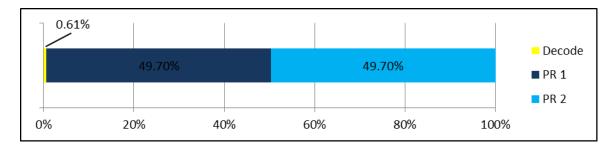

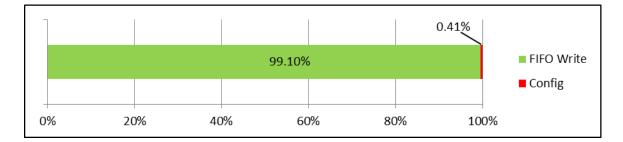

| 4.1  | FPGA Usage Comparison                                  | .51 |

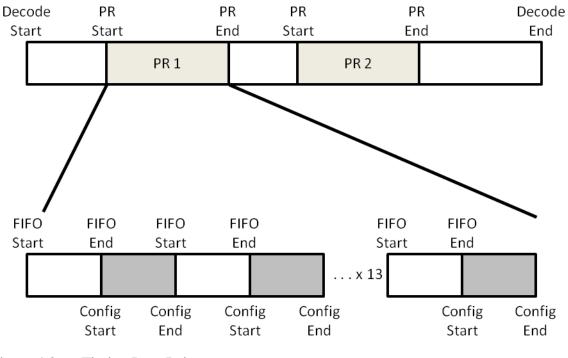

| 4.2  | Timing Data Points                                      | 2 |

|------|---------------------------------------------------------|---|

| 4.3  | Frame Decode Timeline                                   | 3 |

| 4.4  | Frame Decode Percent Contributions                      | 4 |

| 4.5  | PR Percent Contributions                                | 5 |

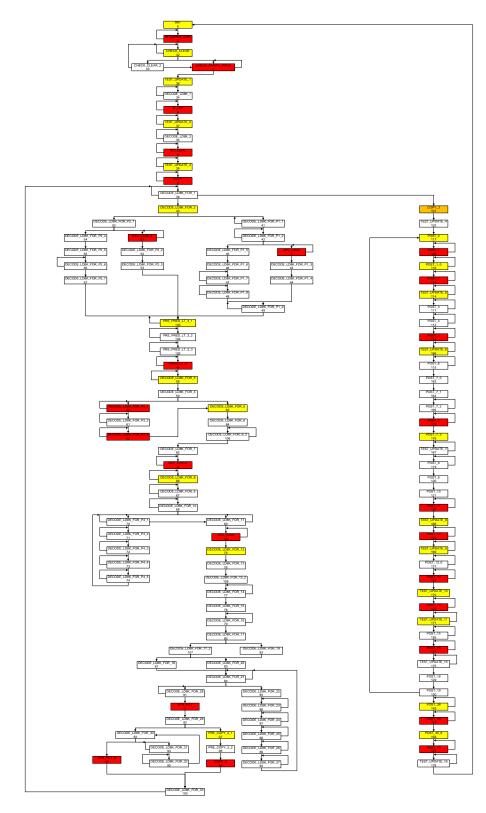

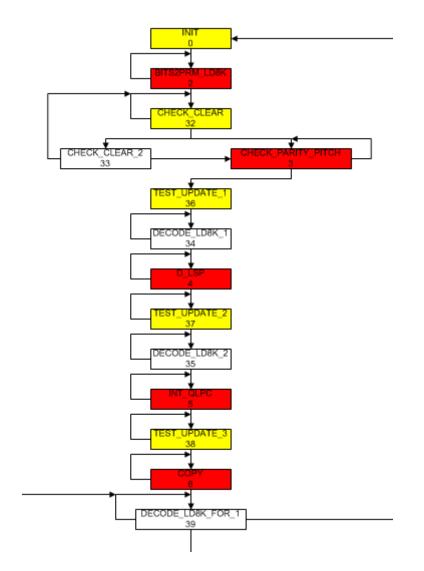

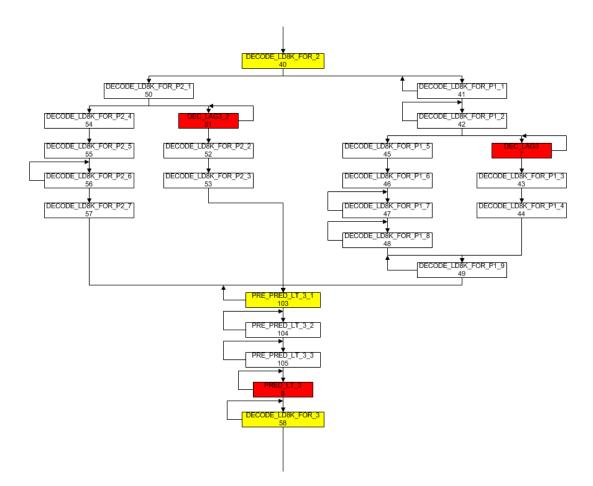

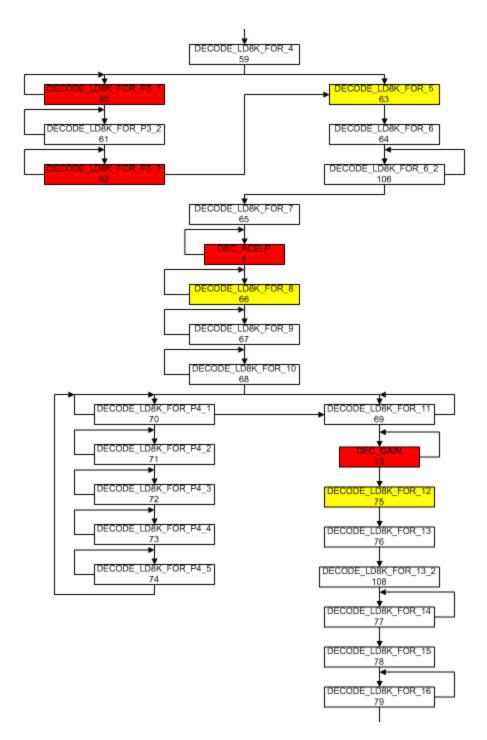

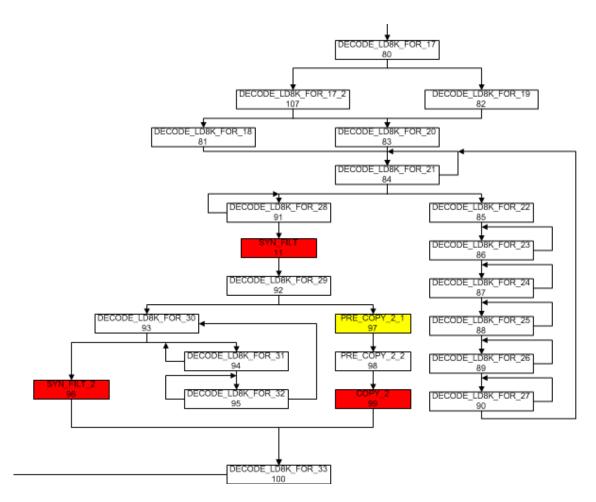

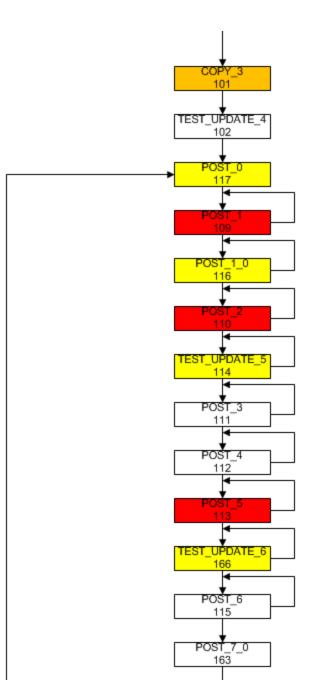

| A.1  | Decoder Control FSM Overview                            | 5 |

| A.2  | Decoder Control FSM Detailed Part 16                    | 6 |

| A.3  | Decoder Control FSM Detailed Part 26                    | 7 |

| A.4  | Decoder Control FSM Detailed Part 36                    | 8 |

| A.5  | Decoder Control FSM Detailed Part 46                    | 9 |

| A.6  | Decoder Control FSM Detailed Part 57                    | 0 |

| A.7  | Decoder Control FSM Detailed Part 67                    | 1 |

| A.8  | Decoder Control FSM Detailed Part 77                    | 2 |

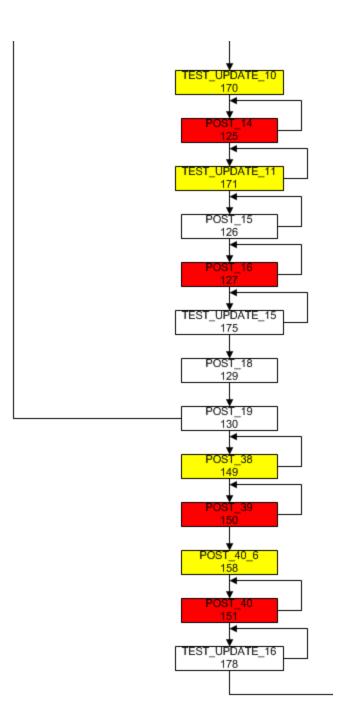

| B.1  | Dynamic Partial Reconfiguration Software Flow Overview7 | 5 |

| B.2  | DPR File Tree Structure                                 | 6 |

| B.3  | ISE Create New Project Window7                          | 8 |

| B.4  | ISE Project Settings Window7                            | 9 |

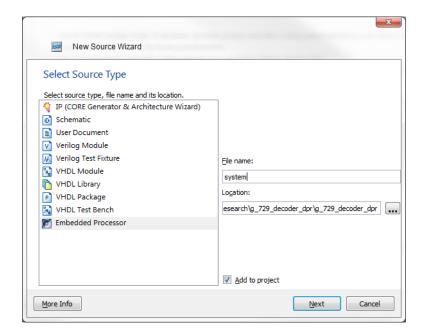

| B.5  | ISE Select Source Type Window8                          | 0 |

| B.6  | XPS Application Preferences Window8                     | 1 |

| B.7  | XPS BSB Board Selection Window8                         | 2 |

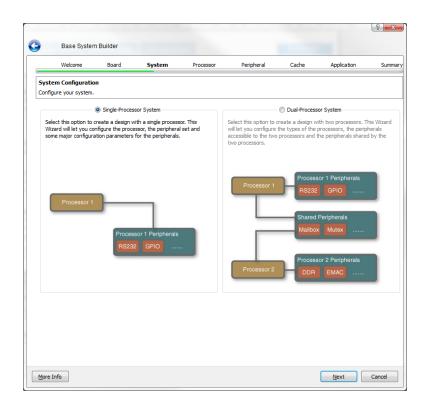

| B.8  | XPS BSB System Configuration Window                     | 3 |

| B.9  | XPS BSB Processor Configuration Window                  | 4 |

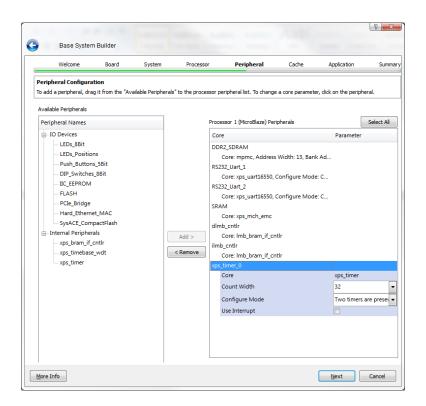

| B.10 | XPS BSB Peripheral Configuration Window8                | 5 |

| B.11 | XPS HWICAP Core Configuration Window                    | 6 |

| B.12 | XPS Create Peripheral Name and Version Window8          | 8 |

| B.13 | XPS Create Peripheral <i>IPIF Services</i> Window       | 9 |

| B.14 | XPS Create Peripheral User S/W Register Window                                      | 90   |

|------|-------------------------------------------------------------------------------------|------|

| B.15 | XPS Create Peripheral User Memory Space Window                                      | 90   |

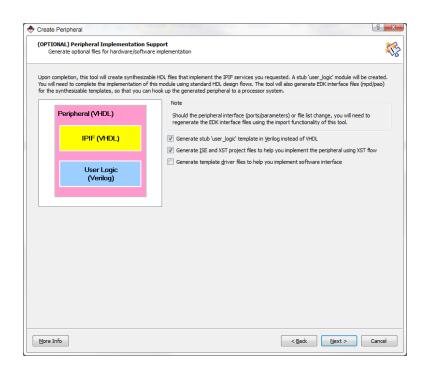

| B.16 | XPS Create Peripheral Peripheral Implementation Support Window                      | 91   |

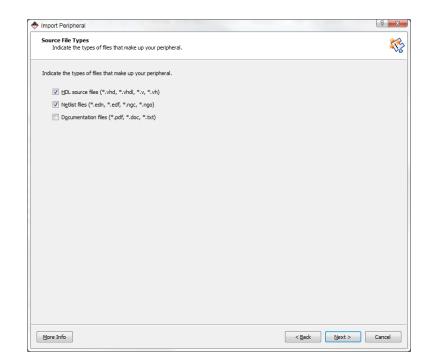

| B.17 | XPS Import Peripheral Peripheral Flow Window                                        | 93   |

| B.18 | XPS Import Peripheral Name and Version Window                                       | 94   |

| B.19 | XPS Import Peripheral Source File Types Window                                      | 95   |

| B.20 | XPS Import Peripheral HDL Source Files Window                                       | 96   |

| B.21 | XPS Import Peripheral Bus Interfaces Window                                         | 97   |

| B.22 | XPS Import Peripheral SPLB: Parameter Window                                        | 98   |

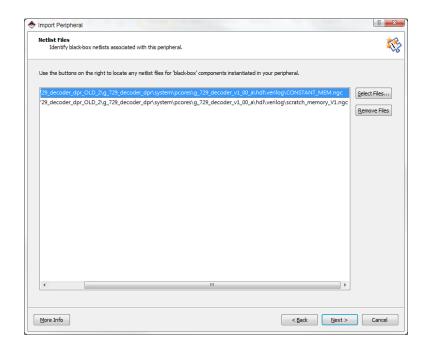

| B.23 | XPS Import Peripheral Netlist Files Window                                          | 99   |

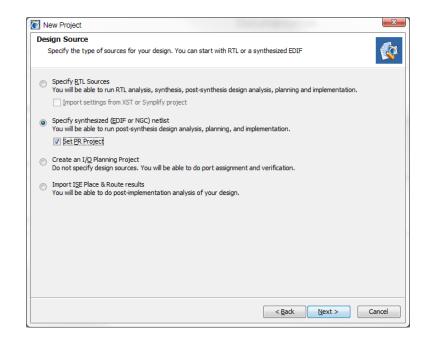

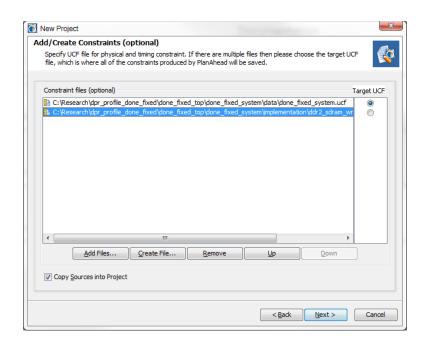

| B.24 | PlanAhead New Project Design Source Window                                          | .101 |

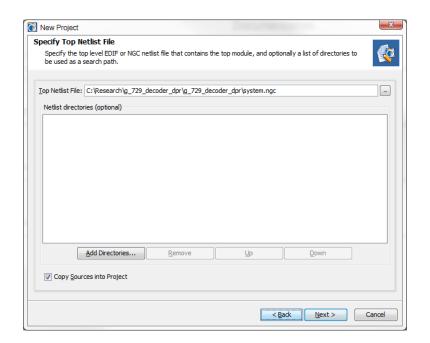

| B.25 | PlanAhead New Project Specify Top Netlist File Window                               | .102 |

| B.26 | PlanAhead New Project Add/Create Constraints Window                                 | .103 |

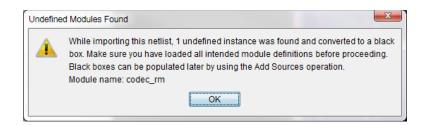

| B.27 | PlanAhead Undefined Instance Warning                                                | .104 |

| B.28 | PlanAhead Undefined Module in Netlist Tree                                          | .104 |

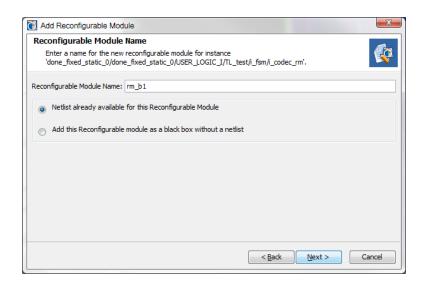

| B.29 | PlanAhead Add RM - RM Module Name Window                                            | .105 |

| B.30 | PlanAhead Add RM – Specify Top Netlist File Window                                  | .106 |

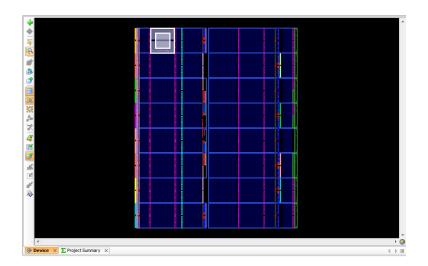

| B.31 | PlanAhead Reconfigurable Partition Pblock                                           | .107 |

| B.32 | PlanAhead Pblock Statistics Panel                                                   | .108 |

| B.33 | PlanAhead Create Multiple Runs – Choose Implementation Strategies<br>and RMs Window | .109 |

| B.34 | PlanAhead Create Multiple Runs – Specify Partition Window                           | .110 |

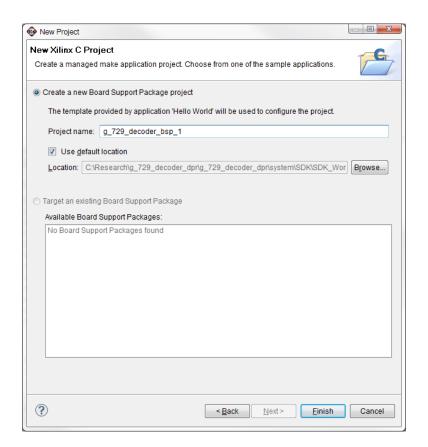

| B.35 | SDK New Project – Project Name and Template Window                                  | .112 |

| B.36 | SDK New Project – BSP Configuration Window                                          | .113 |

| B.37 | SDK BSP Configuration Window                                                        | .114 |

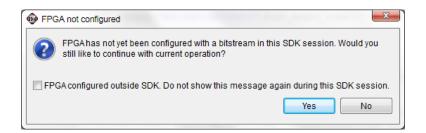

| B.38         | SDK FPGA Not Configured Warning                  | 114 |

|--------------|--------------------------------------------------|-----|

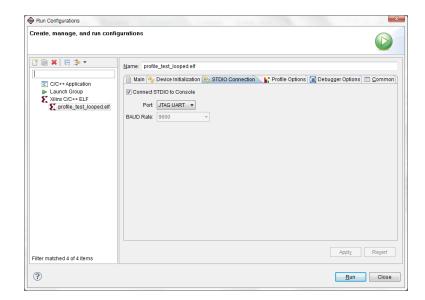

| B.39         | SDK Run Configurations - STDIO Connection Window | 115 |

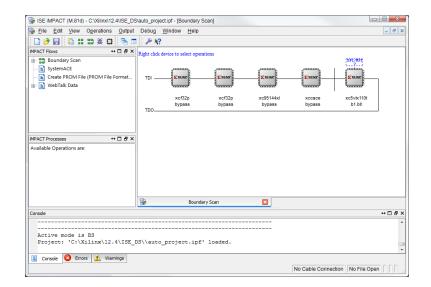

| B.40         | iMPACT Launch Window                             | 116 |

| <b>B.</b> 41 | iMPACT Device Chain                              | 117 |

# LIST OF ACRONYMS

| ASIC   | Application-Specific Integrated Circuit     |

|--------|---------------------------------------------|

| BSB    | Board Support Package                       |

| CLB    | Configurable Logic Block                    |

| CODEC  | Coder/Decoder                               |

| COTS   | Custom Over-The-Shelf                       |

| DMA    | Direct Memory Access                        |

| DPR    | Dynamic Partial Reconfiguration             |

| DSP    | Digital Signal Processor/Processing         |

| EDK    | Embedded Development Kit                    |

| FIFO   | First In, First Out                         |

| FPGA   | Field Programmable Gate Array               |

| FSM    | Finite State Machine                        |

| HWICAP | Hardware Internal Configuration Access Port |

| ICAP   | Internal Configuration Access Port          |

| IDE    | Integrated Development Environment          |

| IP     | Intellectual Property                       |

| ISE    | Integrated Software Environment             |

| MHz    | Megahertz                                   |

| PAR    | Place and Route                             |

- PLB Processor Local Bus

- PR Partial Reconfiguration

- RM Reconfigurable Module

- RP Reconfigurable Partition

- SDK Software Development Kit

- XPS Xilinx Platform Studio

#### CHAPTER I

#### INTRODUCTION

### 1.1 Background

Scientists are constantly exploring new and more extreme environments. As the complexity of the systems required to operate in these environments increases, new methods must be researched to provide sufficient and efficient computing power. Of these environments, space has become a major area of exploration over the last half century. Space exploration introduces new challenges not found on Earth. Due to the infeasibility of having access to hard line support systems such as power, life support, and communication lines, space vehicles must operate on a finite and limited supply of power in a finite and limited space. Therefore, it is imperative that the SWAP (size, weight, and power) principle be taken into account when developing applications for execution in space.

There are three main types of integrated circuits available for application solutions. The first is the Application-Specific Integrated Circuit (ASIC) that requires custom circuit design. The level of customization of these ICs can range from fully custom to standard cell or gate array designs. However, using ASICs trades high development cost and usage flexibility for better, "application specific" performance. On the other end of the spectrum is the general purpose IC. This group of ICs includes chips such as general purpose microprocessors, as well as general purpose digital signal

processors (DSPs) and some common logic configurations. This option reduces cost and performance by allowing for the use of generalized instructions and high performance mathematics circuits. The final category of ICs is field-programmable ICs. This group provides a compromise between the two previous options. It includes Field-Programmable Gate Arrays (FPGAs) which allow controllers to define a circuit for the chip and then change the circuit and reprogram the chip with the new design. As FPGAs have grown in size, become more powerful, and become more affordable, their ability to support customized hardware designs as well as provide the ultimate flexibility of being able to be reconfigured has led the platform to become a popular development option [1].

One area in particular that has been proposed by NASA is the use of FPGAs to maintain voice communication protocols. A project was funded through an ESMD Space Grant, Senior Design Project (ID: JSC4-36-SD), to develop an HDL implementation of the ITU G.729 Voice CODEC currently in use by the space program. This project was completed by four senior design teams at Mississippi State University. Detailed lists of the contributions from each team are given in their respective design reports [8]-[11].

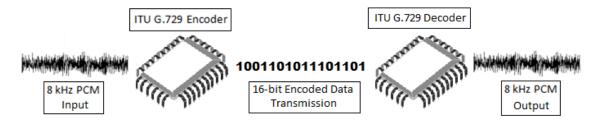

The G.729 is an audio compression system that produces highly-intelligible audio in low-bandwidth environments using a "conjugate-structure algebraic-code-excited linear prediction" algorithm at a rate of 8 kbits/s [23]. The CODEC operates in two stages, the encoding stage and the decoding stage, as shown in Figure 1.1. During the encoding stage, raw audio samples are streamed to the system. These samples are collected and grouped into frames that correspond to 10 ms of audio or 80 samples. The Encoder stage outputs 16-bit encoded bitstream that can then be transmitted to the destination system that houses the decoding stage. The Decoder accepts the bitstream in

groups of 80 32-bit sign-extended double-words, and outputs an 8 kHz PCM raw audio stream.

Figure 1.1 ITU G.729 Operation Overview [25]

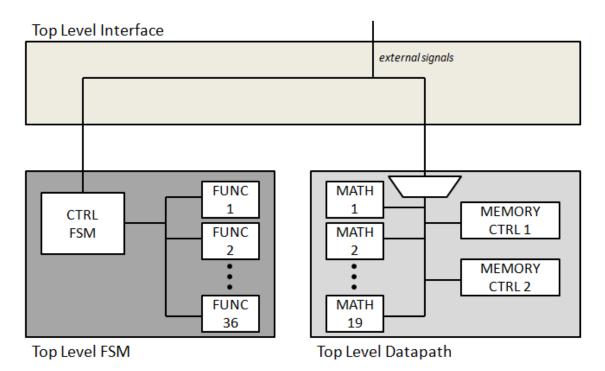

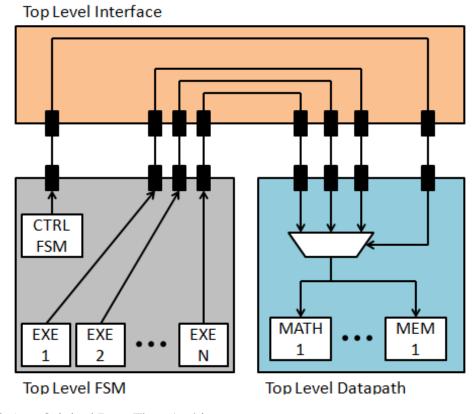

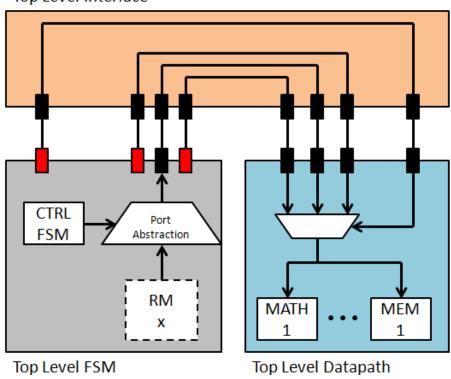

While understanding of the mathematical and digital signal processing theory for audio coding is needed to implement the two stages as demonstrated by Owens et al. in [8]-[11], it is beyond the scope of this project. However, an overview of the architecture and functionality of the HDL implementation is necessary for understanding the case study presented in this paper. Both the Encoder and Decoder stages use the same general architecture diagrammed in Figure 1.2. The system consists of three main blocks: the control block (Top Level FSM), the datapath block (Top Level Datapath), and the interconnect between the two and the interface to the external world (Top Level Interface). The Encoder/Decoder functions by performing a set of algorithms on the input data. For the Decoder, the set consists of 36 distinct functions. These functions are coded into individual Verilog modules and called sequentially by the control FSM. All of the algorithms use a shared set of math units and memory space that are located in the Datapath block. Therefore, a multiplexer bank is used in the Datapath to direct the signals from the currently executing function to the proper math modules and memory interfaces.

Figure 1.2 G.729 Decoder HDL Architecture

### **1.2** Motivation and Problem Statement

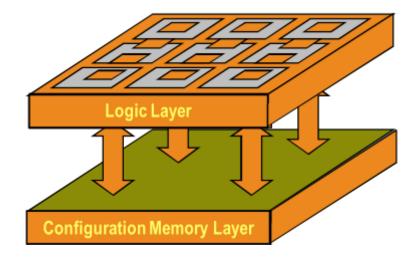

FPGAs were introduced in the late 1980's by Xilinx [4]. The chips were comprised of a set of distinct, configurable logic blocks (CLBs) that are connected by programmable switches. Initially, FPGAs could only be reconfigured on a whole chip basis. While this functionality did not lend itself to the in-application flexibility of later models, this ability still provided much more flexibility than static VLSI designs. The ability to partially reconfigure an FPGA first became available with the release of the Xilinx 6200 series [5]. Furthermore, the Xilinx Virtex-II allowed the partial reconfiguration of individual columns of the FPGA. However, as demonstrated by Sedcole et al. [6], this method of partial reconfiguration puts heavy constraints on routing. With Xilinx's release of the Virtex 4, the size of the reconfiguration frame was reduced to a height of only 16 configurable logic blocks (CLBs) which remedied the routing problems found in the Virtex II. This ability to access small portions of the chip is achieved through the use of a "Configuration Memory Layer" as shown in Figure 1.3.

Figure 1.3 FPGA Configuration Memory

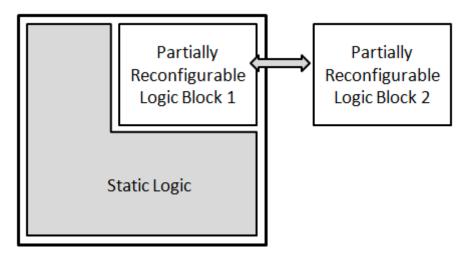

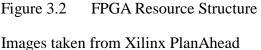

The development of techniques to allow for the partial reconfiguration of FPGAs has increased interest in using them as a platform for more diverse applications. A key feature of partial reconfiguration is that a subset of the logic programmed to an FPGA can be modified without affecting the operation of the rest of the logic on the chip [2]. This idea is illustrated in Figure 1.4 where the logic circuits defined for the *Logic Block 1* region can be replaced with the circuits defined in *Logic Block 2* without modifying or interrupting the execution of the circuits defined in the *Static Logic* region. For the rest of this report, the area of the FPGA designated to be reconfigured independently from the rest of the system will be referred to as the reconfigurable partition (RP). Furthermore, the set of circuit designs that can be interchanged with one another inside of a given

reconfigurable partition will be referred to as reconfigurable modules (RMs). These reconfigurable modules are defined by "partial bitfiles" that only give configuration information for the reconfigurable partition, as opposed to "full bitfiles" which define the configuration of the entire FPGA.

Figure 1.4 FPGA Partial Reconfiguration

The functionality of partial reconfiguration has led to the concept of Dynamic Partial Reconfiguration (DPR). Dynamic partial reconfiguration allows a system to autonomously reconfigure sections of its design based on the state of the system [3]. This allows partial reconfiguration to be utilized in real time during the operation of a system. There are two main options for configuring FPGAs: externally over a communications channel or internally using on-chip logic to modify the FPGA's logic. The external option can be useful for debugging purposes but is not sufficient to support dynamic partial reconfiguration designs. The second, internal option does support dynamic partial reconfiguration and for certain Xilinx chips utilizes a native hardware construct named the Internal Configuration Access Port (ICAP). The ICAP interfaces through a communication FIFO that transfers reconfiguration data from the partial bitfiles in system memory to the ICAP circuit.

There are many apparent benefits to using a dynamic partial reconfiguration design. The first is design size. If a design would normally require 5 resource units, but 4 of these units are mutually exclusive, a dynamic partial reconfiguration design would only require 2 resource units on the actual chip. A second apparent benefit is power saving. This savings is due to the reduction of onboard circuitry needed to support different applications simultaneously (e.g. a separate set of chips/interfaces solely for voice communication, life support, navigation, etc.). Testing the power savings by running partial reconfiguration as opposed to the standard circuitry is beyond the scope of this project.

The benefits of dynamic partial reconfiguration have led to the conclusion that partially reconfigurable systems would be useful in environments that have space and power constraints. Therefore, dynamic partial reconfiguration has been a major area of research for space applications. Osterloh et al. [7] provide an overview of the design considerations necessary to use an FPGA in space. However, their focus is on the physical hardware considerations and data integrity aspects of the system, rather than the software capabilities of using dynamic partial reconfiguration. Recently, further research was requested by NASA to answer the question, "Can a Commercial Over-The-Shelf (COTS) design flow be used to convert a statically configured system to use dynamic partial reconfiguration?"

## **1.3** Previous Research and Significance of Work

Several authors have presented research that answers different parts of this question. The first, by Manet et al. [12], provides an in-depth analysis of the use of dynamic partial reconfiguration in signal processing applications. The authors provide a method for improving on the ICAP design by writing their own custom configuration management system that utilizes direct memory access (DMA) and other optimization techniques. The authors conclude that while dynamic partial reconfiguration has potential for use in signal processing, custom hardware reconfiguration controllers must be created to support the small processing period required by signal processing applications. While the authors did provide conclusions on the shortcomings of the Xilinx software flow, some of these shortcomings are outdated and the authors did not provide a detailed assessment of the software flow's capabilities for use without the need for custom interface designs.

Another study utilizing partial reconfiguration for signal processing was performed by Claus et al. [13]. The authors used partial reconfiguration to insert and remove different "hardware accelerator engines" to support the varying needs of the different functions that are running on the chip. This design is opposite of the design presented in this project where the support modules are statically configured and the function logic is reconfigured. Furthermore, the ICAP control was also modified in this study to produce better throughput for partial reconfiguration.

Another research project, by McDonald [14], attempts to use partial reconfiguration for a "software-defined radio" utilizing Xilinx's work flow. In this case, the author chose to use partial reconfigure to swap between the encoder and decoder

based on the current needs of the system. While the author does provide timing information, no indication is made as to whether timing constraints were met. The solution provided was to allocate enough memory as a buffer to avoid any loss of data due to the latency of the system.

Another investigation into the use of DPR at a higher design level was presented by Bhandari et al. [15]. The main focus of this paper was to evaluate the benefits of using the dynamic partial reconfiguration to support multiple types of signal processing systems on the same chip. The conclusions made by the authors are observations of the apparent benefits of using dynamic partial reconfiguration over static designs. However, they do provide empirical timing information for the use of dynamic partial reconfiguration in real-time signal processing, but these results are for different CODECs than the ITU G.729 CODEC used by NASA and are for changing between CODECs rather than optimizing a single one.

Based on the information provided by Xilinx and the research presented above, it was hypothesized that Xilinx's dynamic partial reconfiguration flow was sufficient to provide a COTS solution for converting statically designed systems to take advantage of the benefits dynamic partial reconfiguration offers. The ITU G.729 Decoder HDL design created by Owens et al. was chosen as a test case to evaluate the conversion process.

In order to validate this hypothesis, three stages must be completed: modify the original HDL to support dynamic reconfiguration, create hardware and software testing platforms for the application, and test the system to verify functionality, measure size, and ensure it meets application timing constraints.

For the first stage, this project provides an evaluation of the process required to convert a statically configured HDL design into a dynamically, partially reconfigurable HDL design. This includes design requirements, such as port abstraction, as well as design considerations, such as the system architecture and reconfigurable module sets.

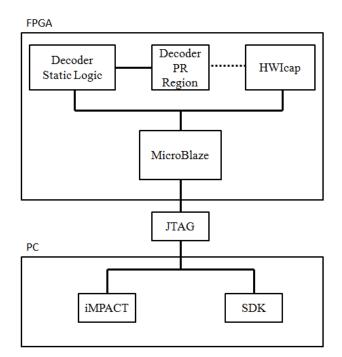

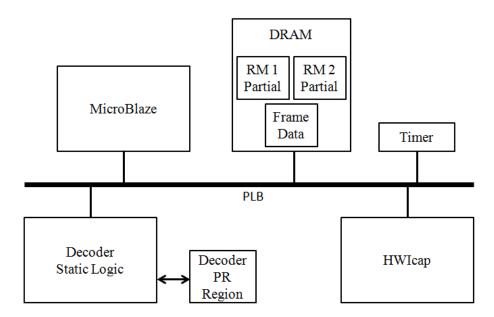

To address the second stage, this project presents a validation platform design, as summarized in Figure 1.5. The FPGA is externally programmed with the Xilinx iMPACT tool via the JTAG cable. The JTAG is also used as the communication bus between the Microblaze soft processor and the Xilinx SDK environment where debugging information is output. The Microblaze is connected to a system bus that communicates back and forth with the test application and the HWIcap, a standard interface to the ICAP provided by Xilinx. The HWIcap is the construct that reconfigures the Decoder PR Region, which is indicated by the dotted line. The Microblaze runs a software test program that starts the Decoder, performs timing analysis, and runs the dynamic partial reconfiguration procedure when necessary. The process for creation of the platform and the design considerations associated with it are expanded upon in section 3.1.

Figure 1.5 DPR Testing Platform

Finally, this project gives validation data for three aspects of the system. First, after the HDL design is modified to support dynamic partial reconfiguration, it must be tested to ensure that it still functions properly. The results of these tests and the procedures for doing so are presented in this paper. Second, although it is assumed that the size of a design will reduce when utilizing dynamic partial reconfiguration, an analysis of the actual resulting sizes is presented. This allows for an empirical conclusion as to the benefits of dynamic partial reconfiguration with respect to design size. Finally, although dynamic partial reconfiguration has many positive aspects, one property that is negatively affected is run time. Therefore, this paper presents timing data and analysis to determine if a system is capable of performing in its time constraints if it is using dynamic partial reconfiguration.

#### CHAPTER II

#### HDL DESIGN MODIFICATION

A key contribution of this project is the evaluation of the additional work in the design phase of the application development cycle necessary to produce a dynamically, partially reconfigurable system. This chapter addresses the modifications that must be made to a static design configuration as well as other aspects of the design that must be considered when developing a dynamic partial reconfiguration application. The five considerations presented below are: extracting module information for use in future design decisions, defining the set of reconfigurable modules, abstracting the port lists of reconfigurable modules, modifying the system architecture to support dynamic partial reconfiguration, and performing functional simulation to ensure the modified design produces the same results as the original.

### 2.1 Module Data Extraction

The first step in converting a static application to a dynamic partial reconfiguration application is to analyze the design and determine the set of functional blocks that can be implemented into independent modules. As is the case with the Decoder design, the application may already be separated into mutually exclusive modules. Once the set of modules is identified, information about each is extracted to provide an overview of the system that is necessary for consideration in future design decisions. This process was completed by hand; however some of the information extracted could have been gathered using custom parsing programs. The key characteristics to observe are: the system's module tree, each module's instantiation level, and a breakdown of each module's port list. Another data set that is included in the module data extraction is a breakdown of the FPGA resources needed by each module. However, this information can only be obtained after the reconfigurable module synthesis process described in section 3.1 is completed.

The system module tree is a hybrid graph that shows multiple dimensions of the application flow at the same time. Vertically, it shows the sequential order in which the Decoder modules execute. Horizontally, it shows the module hierarchy. The left most modules are the highest level or top level of module hierarchy. The right most modules are the lowest level of module hierarchy, and modules listed more than once in the vertical list are functions which are used more than once to compute the overall function. This information is useful for determining the reconfigurable module set described in the next section. The next important property is each module's instantiation level. This property is derived from the system module tree. A module's instantiation level is defined as the number of modules a signal must travel through to reach the highest hierarchy or "top" level. Module instantiation levels are vital for determining the reconfigurable module set and will be examined further in section 2.2. As stated, a breakdown of each module's port list is also included in the module extraction data. This data includes counts for every port width for inputs and outputs and is necessary for the port abstraction process described in section 2.3. Table 2.1 shows the system module tree for the Top Level FSM block of the Decoder. Each column corresponds to the different

module instantiation levels. All modules of a given level are instantiated by the first module encountered above it in the next highest level.

| 0            | 1                | 2               | 3             | 4                  | 5    |

|--------------|------------------|-----------------|---------------|--------------------|------|

|              |                  |                 |               |                    |      |

| Top_Level_FS |                  |                 |               |                    |      |

| M            |                  |                 |               |                    |      |

|              | bits2prm_ld8k    |                 |               |                    |      |

|              |                  | bin2int         |               |                    |      |

|              | CheckParityPi    |                 |               |                    |      |

|              | tch              |                 |               |                    |      |

|              | D_lsp            |                 |               |                    |      |

|              |                  | Lsp_iqua_cs     |               |                    |      |

|              |                  |                 | Lsp_get_quant |                    |      |

|              |                  |                 |               | Lsp_expand_1<br>_2 |      |

|              |                  |                 |               | Lsp_prev_co        |      |

|              |                  |                 |               | mpose              |      |

|              |                  |                 |               | Lsp_prev_upd       |      |

|              |                  |                 |               | ate                |      |

|              |                  |                 |               |                    | сору |

|              |                  |                 |               | Lsp_stability      |      |

|              |                  |                 | Lsp_prev_extr |                    |      |

|              |                  |                 | act           |                    |      |

|              |                  |                 | Lsp_prev_upd  |                    |      |

|              |                  |                 | ate           |                    |      |

|              |                  |                 | сору          |                    |      |

|              |                  | lsf_lsp2        |               |                    |      |

|              | int_qlpc         |                 |               |                    |      |

|              |                  | LSP_to_Az       | ant lon not   |                    |      |

|              | 2020             |                 | get_lsp_pol   |                    |      |

|              | copy<br>Dec_lag3 |                 |               |                    |      |

|              | Pred_lt_3        |                 |               |                    |      |

|              |                  |                 |               |                    |      |

|              | Random           | L_shr           |               |                    |      |

|              |                  | L_shi<br>L_add  |               |                    |      |

|              |                  | L_add<br>L_mult |               |                    |      |

|              | de_acelp         |                 |               |                    |      |

|              | Dec_gain         |                 |               |                    |      |

|              | Dec_gain         |                 |               |                    |      |

Table 2.1

ITU G.729 Decoder System Module Tree

| Table 2.1 ( | (continued) |

|-------------|-------------|

|-------------|-------------|

|              | Gain_update_ |           |  |

|--------------|--------------|-----------|--|

|              | erasure      |           |  |

|              | Gain_predict |           |  |

|              |              | Log2      |  |

|              |              | mpy_32_16 |  |

|              |              | Pow2      |  |

|              | Gain_update  |           |  |

|              |              | Log2      |  |

| syn_filt     |              |           |  |

| Weight_Az    |              |           |  |

| calc_st_filt |              |           |  |

|              | syn_filt     |           |  |

|              | calc_rc0_h   |           |  |

| filt_mu      |              |           |  |

| scale_st     |              |           |  |

| pst_ltp      |              |           |  |

|              | Search_Del   |           |  |

|              | сору         |           |  |

|              | Compute_Ltp  |           |  |

|              | _L           |           |  |

|              | select_ltp   |           |  |

|              | filt_plt     |           |  |

| post_process |              |           |  |

The Decoder design can be broken down into four different module categories: execution, utility, math, and memory. There are 36 execution modules corresponding to the 36 functions called sequentially to decode an audio frame. There are 3 utility functions that are used by the execution modules or run independently that are instantiated in the FSM block rather than the Datapath block. There are 19 distinct math operations that are broken into modules instantiated in the Datapath block. Finally, there are four memory blocks corresponding to two memory cores with a memory controller for each. The math and memory modules are shared by all of the execution and utility functions. This breakdown is shown in Table 2.2. Furthermore, the port data for all of the modules in the Decoder design are given in Table 2.2. The columns headings under Input and Output Port Counts correspond to the bit widths of the ports (i.e. 1, 4, 6, etc.).

|           |      |                     |    | Input Port Counts* |   |    |    |    |    |   | Output Port Counts* |    |    |             |  |

|-----------|------|---------------------|----|--------------------|---|----|----|----|----|---|---------------------|----|----|-------------|--|

| Туре      | Code | Module Name         | 1  | 4                  | 6 | 12 | 16 | 32 | 1  | 2 | 12                  | 16 | 32 | Total Ports |  |

| System    | t1   | Top_Level           | 19 | 0                  | 0 | 2  | 0  | 1  | 14 | 0 | 0                   | 0  | 1  | 3           |  |

|           | t2   | Top_Level_FSM       |    |                    |   |    |    |    |    |   |                     |    |    |             |  |

|           | t3   | Top_Level_Data_Path |    |                    |   |    |    |    |    |   |                     |    |    |             |  |

| Execution | b1   | bits2prm_ld8k       | 5  | 0                  | 0 | 0  | 2  | 2  | 4  | 0 | 3                   | 4  | 1  | 2           |  |

|           | b2   | bin2int             | 5  | 0                  | 0 | 0  | 4  | 1  | 3  | 0 | 1                   | 5  | 0  | 1           |  |

|           | b3   | CheckParityPitch    | 5  | 0                  | 0 | 0  | 2  | 1  | 4  | 0 | 2                   | 4  | 1  | 1           |  |

|           | b4   | D_lsp               | 14 | 0                  | 0 | 0  | 4  | 9  | 13 | 0 | 3                   | 16 | 9  | 6           |  |

|           | b5   | Lsp_iqua_cs         | 12 | 0                  | 0 | 3  | 3  | 8  | 11 | 0 | 3                   | 13 | 8  | 6           |  |

|           | b6   | Lsp_get_quant       | 10 | 0                  | 0 | 4  | 6  | 6  | 9  | 0 | 3                   | 10 | 6  | 5           |  |

|           | b7   | Lsp_expand_1_2      | 8  | 1                  | 0 | 1  | 3  | 3  | 7  | 0 | 2                   | 6  | 5  | 3           |  |

|           | b8   | Lsp_prev_compose    | 6  | 0                  | 0 | 5  | 1  | 4  | 5  | 0 | 3                   | 6  | 2  | 3           |  |

|           | b9   | Lsp_prev_update     | 6  | 0                  | 0 | 2  | 2  | 2  | 5  | 0 | 2                   | 4  | 3  | 2           |  |

|           | b10  | Lsp_stability       | 7  | 0                  | 0 | 1  | 2  | 3  | 6  | 0 | 2                   | 4  | 5  | 3           |  |

|           | b11  | Lsp_prev_extract    | 7  | 0                  | 0 | 5  | 1  | 5  | 6  | 0 | 3                   | 7  | 3  | 3           |  |

|           | b12  | lsf_lsp2            | 9  | 0                  | 0 | 2  | 4  | 4  | 8  | 0 | 3                   | 11 | 2  | 4           |  |

|           | b13  | int_qlpc            | 29 | 0                  | 0 | 0  | 11 | 13 | 17 | 0 | 3                   | 17 | 13 | 10          |  |

|           | b14  | LSP_to_Az           | 27 | 0                  | 0 | 2  | 10 | 12 | 16 | 0 | 2                   | 15 | 13 | g           |  |

|           | b15  | get_lsp_pol         | 29 | 0                  | 0 | 1  | 10 | 12 | 16 | 0 | 2                   | 15 | 13 | 9           |  |

|           | b16  | Dec_lag3            | 6  | 0                  | 0 | 0  | 5  | 1  | 5  | 0 | 2                   | 6  | 1  | 2           |  |

|           | b17  | Pred_It_3           | 8  | 0                  | 0 | 1  | 4  | 5  | 7  | 0 | 3                   | 6  | 5  | 3           |  |

|           | b18  | Random              | 3  | 0                  | 0 | 0  | 0  | 0  | 1  | 0 | 0                   | 1  | 0  |             |  |

|           | b19  | de_acelp            | 6  | 0                  | 0 | 0  | 3  | 1  | 5  | 0 | 2                   | 6  | 1  | 2           |  |

|           | b20  | Dec_gain            | 23 | 0                  | 0 | 0  | 5  | 9  | 14 | 0 | 3                   | 16 | 9  | 7           |  |

|           | b21  | Gain_update_erasure | 7  | 0                  | 0 | 0  | 2  | 3  | 6  | 0 | 2                   | 5  | 4  | 2           |  |

|           | b22  | Gain_predict        | 20 | 0                  | 0 | 0  | 4  | 7  | 11 | 0 | 3                   | 16 | 6  | 6           |  |

|           | b23  | Gain_update         | 16 | 0                  | 0 | 0  | 3  | 7  | 9  | 0 | 3                   | 10 | 6  | 5           |  |

|           | b24  | syn_filt            | 16 | 0                  | 1 | 4  | 2  | 5  | 9  | 0 | 2                   | 9  | 5  | 5           |  |

|           | b25  | Weight_Az           | 6  | 0                  | 0 | 3  | 1  | 3  | 5  | 0 | 2                   | 4  | 3  | 2           |  |

|           | b26  | Residu              | 9  | 0                  | 0 | 3  | 2  | 5  | 8  | 0 | 2                   | 9  | 5  | 4           |  |

|           | b27  | calc_st_filt        | 25 | 0                  | 0 | 6  | 8  | 11 | 17 | 0 | 2                   | 18 | 11 | g           |  |

|           | b28  | calc_rc0_h          | 14 | 0                  | 0 | 2  | 6  | 8  | 11 | 0 | 2                   | 9  | 8  | 6           |  |

|           | b29  | filt_mu             | 17 | 0                  | 0 | 3  | 7  | 10 | 15 | 0 | 2                   | 16 | 9  | 7           |  |

|           | b30  | scale_st            | 16 | 0                  | 0 | 3  | 8  | 8  | 14 | 0 | 2                   | 13 | 8  | 7           |  |

|           | b31  | pst_ltp             | 27 | 0                  | 0 | 2  | 17 | 15 | 20 | 0 | 3                   | 23 | 13 | 12          |  |

|           | b32  | Search_Del          | 23 | 0                  | 0 | 1  | 14 | 11 | 18 | 0 | 3                   | 28 | 10 | 10          |  |

|           | b33  | <br>Compute_Ltp_L   | 10 | 0                  | 0 | 2  | 6  | 5  | 9  | 0 | 3                   | 13 | 6  | 5           |  |

|           | b34  | select_ltp          | 16 | 0                  | 0 | 0  | 18 | 7  | 11 | 1 | 0                   | 16 | 6  | 7           |  |

|           | b35  |                     | 8  | 0                  | 0 | 0  | 6  | 4  | 7  | 0 | 2                   | 8  | 4  | 3           |  |

|           | b36  | post_process        | 15 | 0                  | 0 | 10 | 8  | 10 | 11 | 0 | 3                   | 13 | 8  | 7           |  |

Table 2.2ITU G.729 Decoder Module Port Data

| Utility | u1   | сору                       | 5  | 0 | 0 | 2 | 2 | 2 | 4 | 0 | 2 | 2 | З | 22 |

|---------|------|----------------------------|----|---|---|---|---|---|---|---|---|---|---|----|

|         | u2   | Log2                       | 8  | 0 | 0 | 0 | 2 | 5 | 6 | 0 | 1 | 8 | 4 | 34 |

|         | u3   | Pow2                       | 13 | 0 | 0 | 0 | 4 | 4 | 6 | 0 | 1 | 9 | 3 | 40 |

| Math    | m1   | add                        | 3  | 0 | 0 | 0 | 2 | 0 | 2 | 0 | 0 | 1 | 0 | 8  |

|         | m2   | L_add                      | 3  | 0 | 0 | 0 | 0 | 2 | 2 | 0 | 0 | 0 | 1 | 8  |

|         | m3   | sub                        | 3  | 0 | 0 | 0 | 2 | 0 | 2 | 0 | 0 | 1 | 0 | 8  |

|         | m4   | L_sub                      | 3  | 0 | 0 | 0 | 0 | 2 | 2 | 0 | 0 | 0 | 1 | 8  |

|         | m5   | mult                       | 4  | 0 | 0 | 0 | 2 | 0 | 2 | 0 | 0 | 1 | 0 | 9  |

|         | m6   | L_mult                     | 3  | 0 | 0 | 0 | 2 | 0 | 2 | 0 | 0 | 0 | 1 | 8  |

|         | m7   | shl                        | 3  | 0 | 0 | 0 | 2 | 0 | 2 | 0 | 0 | 1 | 0 | 8  |

|         | m8   | L_shl                      | 3  | 0 | 0 | 0 | 1 | 1 | 2 | 0 | 0 | 0 | 1 | 8  |

|         | m9   | shr                        | 3  | 0 | 0 | 0 | 2 | 0 | 2 | 0 | 0 | 1 | 0 | 8  |

|         | m10  | L_shr                      | 3  | 0 | 0 | 0 | 1 | 1 | 2 | 0 | 0 | 0 | 1 | 8  |

|         | m11  | norm_l                     | 3  | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 6  |

|         | m12  | norm_s                     | 3  | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 6  |

|         | m13  | L_abs                      | 3  | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 6  |

|         | m14  | L_negate                   | 3  | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 6  |

|         | m15  | L_mac                      | 3  | 0 | 0 | 0 | 2 | 1 | 2 | 0 | 0 | 0 | 1 | 9  |

|         | m16  | L_msu                      | 3  | 0 | 0 | 0 | 2 | 1 | 2 | 0 | 0 | 0 | 1 | 9  |

|         | m17  | mpy_32_16                  | 9  | 0 | 0 | 0 | 2 | 3 | 4 | 0 | 0 | 6 | 2 | 26 |

|         | m18  | Мру_32                     | 9  | 0 | 0 | 0 | 1 | 4 | 4 | 0 | 0 | 6 | 2 | 26 |

|         | m19  | div_s                      | 5  | 0 | 0 | 0 | 3 | 1 | 4 | 0 | 0 | 3 | 2 | 18 |

| Memory  | mem1 | Scratch_Memory_Controller  | 2  | 0 | 0 | 2 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 6  |

|         | mem2 | scratch_memory_V1          | 2  | 0 | 0 | 2 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 6  |

|         | mem3 | Constant_Memory_Controller | 2  | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 5  |

|         | mem4 | CONSTANT_MEM               | 2  | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 5  |

|         |      |                            |    |   |   |   |   |   |   |   |   |   |   |    |

Table 2.2 (continued)

\* The columns under the port count headings refer to the bitwidths of the different sized ports (i.e. 1-bit, 4-bit, 6-bit, etc.)

## 2.2 Reconfigurable Module Set Selection

The first dynamic partial reconfiguration design decision is choosing the set of modules to be included in the reconfigurable module set. The number of reconfigurable modules sets possible is bounded by *n*!, where *n* is the number of identified potential reconfigurable modules. This number increases very rapidly as the number of reconfigurable modules increases. Therefore, this section provides common schemes and practical constraints that will limit the number of set compositions.

To determine which modules are eligible for partial reconfiguration, all modules must be analyzed to decide if they execute sequentially or concurrently with other modules. Because sequentially executed modules only need to be present on the chip during their execution time, they are perfect candidates for partial reconfiguration. However, modules that run concurrently with other modules must be on the chip whenever the other modules are executed. Such is the case for the math and memory modules in the Decoder. While the modules are not used by every execution module, their use is often enough and their design size is small enough that the added complexity of including them in the reconfigurable module set would not be worth the benefits gained. This reduces the potential reconfigurable modules to the 36 execution and 3 utility modules.

The execution modules from Table 2.2 are each finite state machines which were derived by converting a C programming language functions to Verilog HDL. The execution modules perform complex mathematical operations using the shared math modules and read and store data from the share memory objects using the shared utility functions. The execution module hierarchy mirrors the original C program and represents the hierarchy found there. Instantiation of one module within another generally represents either a large function which was carved out as a separate subroutine or represents a function which was called multiple times in a loop. For the loop case the Verilog HDL version includes a finite state machine in the higher hierarchy level module which implements the loop and uses module to module hand shaking to wait for execution of the lower module's finite state machine. This organization had a large impact on the decision process when choosing which modules to dynamically reconfigure.

An obvious selection scheme would be to select every execution module for the reconfigurable set. However, many execution modules utilize multiple instantiation levels. All of the modules in a "multi-instantiation level" configuration can only be implemented in three ways. The first implementation would have all of the execution modules individually use the same reconfigurable partition regardless of the module's instantiation level in Table 2.1. Often leaf modules communicate through the higher level modules to the shared math modules. As such the leaf module requires the multiplexors or wires in the instantiating modules to be present. This creates a concurrency requirement between the leaf module and its instantiating module. This makes it impossible to treat each execution module as a separate member reconfigurable module set. In effect, this creates groupings of modules which must always be simultaneously present and reduces the size of the potential reconfigurable module set accordingly. A second option considered was to move the lower hierarchy modules' logic directly into the higher level modules. This option is possible but proved impractical due to the complexity of the logic that must be integrated into the higher level state machines of the altered execution modules. The final option is to define a separate reconfigurable partition, and thereby separate reconfigurable module sets, for each instantiation level. This is infeasible because it requires the instantiation of a reconfigurable partition inside of another reconfigurable partition, which is not supported by Xilinx's PlanAhead software. Therefore, it can be concluded that partially reconfiguring every module in a

"multi-instantiation level" design is impractical when using the standard Xilinx partial reconfiguration flow.

So, to avoid a reconfigurable module set that spans across instantiation levels, the reconfigurable module set was limited to modules from a single level of hierarchy. This scenario forces all of the sub-modules associated with a given reconfigurable module to dynamically added or removed from the FPGA simultaneously with the instantiating module. Consequently, the set of possible reconfigurable modules without modifying the original HDL structure is reduced to the set of modules in the first instantiation level. For the Decoder, this set consists of 18 modules.

One of the goals of this project is to measure the impact of dynamic partial reconfiguration on design size and runtime. For design size, data for the 18 reconfigurable module set chosen above can be obtained through the unit synthesis procedure described in section 3.1. However, it is unnecessary to use the entire set to obtain runtime data. This is because the reconfiguration time is dependent on the size of the reconfigurable partition rather than the size of the reconfigurable module set. Therefore, it is sufficient to select a small subset of the reconfigurable module set and extrapolate the runtime for the whole set based on the data observed from using the subset. Moreover, because the runtime is solely dependent on reconfigurable partition size, the results can be extrapolated to predict the impact of implementing any selection scheme. The subset chosen for the Decoder application consists of the first two modules in the first instantiation level: b1 (*bits2prm*) and b3 (*CheckParityPitch*) as shown in Table 2.1.

## 2.3 Reconfigurable Module Port Set Selection and Abstraction

One design modification that is required by Xilinx for dynamic partial reconfiguration systems is the port set selection and abstraction of all modules in the reconfigurable module set. That is, all reconfigurable modules associated with a single reconfigurable partition must have identical port lists [17]. As is the case with the Decoder, most HDL systems are designed in such a way that each modules port list is unique to the needs of that module. Therefore, it is necessary to modify the port lists of all of the reconfigurable modules. There are three steps to this process: generalizing the port names, selecting the port set, and abstracting the port list in the HDL design. Three methods of port naming and set selection are presented below.

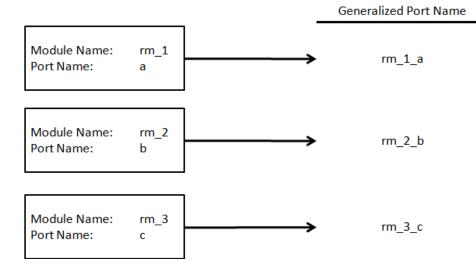

The first method is to create a "superset" of all of the ports for every reconfigurable module. This method has the benefit of being easy to implement but also has the largest port list. This can lead to the reconfigurable partition being "I/O Limited", where the size of the partition is bounded by the number of ports rather than the size of the logic contained. The first step, generalizing port names, for the superset method can be easily accomplished by adding a unique module identifier either as a prefix or suffix to all of the ports. This process is illustrated in Figure 2.1.

Figure 2.1 Port Abstraction – Superset Port Name Generalization

Once all of the names have been generalized, the port set can be selected. In this case, every port is selected for the superset as shown in Figure 2.2. In the figure, all three modules have the same three ports. However, using the superset method, every port is prefixed and added to the superset port list resulting in a nine port set.

| Individual Port Lists  |                 |   | Superset Port List         |

|------------------------|-----------------|---|----------------------------|

| Module Name:<br>Ports: | rm_1<br>a, b, c | > | rm_1_a<br>rm_1_b<br>rm_1_c |

| Module Name:<br>Ports: | rm_2<br>a, b, c |   | rm_2_a<br>rm_2_b<br>rm_2_c |

| Module Name:<br>Ports: | rm_3<br>a, b, c |   | rm_3_a<br>rm_3_b<br>rm_3_c |

Figure 2.2 Port Abstraction – Superset Port Set Selection

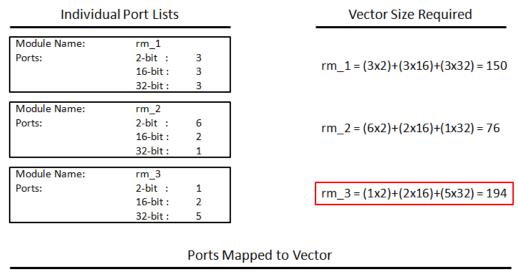

This unnecessary redundancy is addressed by the second approach to port set selection. The goal of the second approach is to minimize the number of ports by defining two vectors, one input and one output, that are sized to match the largest port list in the reconfigurable module set. Then, each module's ports can be mapped into the vectors. This approach has the benefit of removing the need for port name generalization and guaranteeing the minimum port list size. However, it does require more complex logic to implement than the "superset" approach. An illustration of the "vector" approach is shown in Figure 2.3. In this example, there are three modules with varying quantities of 2-bit, 16-bit, and 32-bit ports. The calculations on the right show how large a vector would need to be to support that module. Because  $rm_3$  requires the largest vector, it is chosen as the vector size for the reconfigurable module port list. Although not drawn to scale, the boxes at the bottom give a representation of how each module's port list could be mapped into the vector.

Figure 2.3 Port Abstraction – Vector Port Set Selection

A third approach, that bridges the gap between the two previous options, is to define a port set that is a common subset to all of the reconfigurable modules. To implement this "subset" approach, a different naming scheme must be used than the one used in the "superset" method. In this naming scheme, all ports are converted to a common naming convention that includes three properties: whether the port is an input or an output, the width of the port, and a unique number for that port given its type and size. For example, the third 8-bit input would have a generalized port name of the following form: *input\_8\_3*.

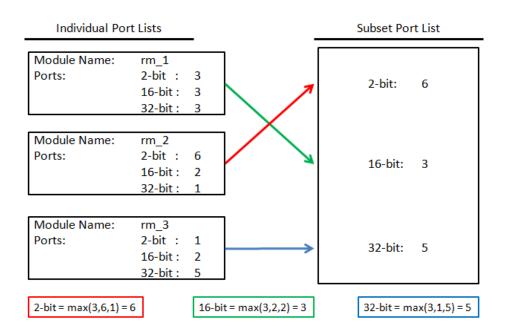

Using the module port data collected in Table 2.2, a minimum set can be created by taking the largest count for each port width and type. This procedure is illustrated in Figure 2.4. Using the same example modules from the "vector" approach, the arrows in this figure indicate which module is responsible for contributing the most ports for each width. For the 2-bit case, module  $rm_2$  is the contributing module because it requires 6, 2-bit ports, whereas  $rm_1$  and  $rm_3$  only require 3 and 1, respectively. The boxes at the bottom of the figure show the calculations for each of the port widths.

Figure 2.4 Port Abstraction – Subset Port Set Selection

This approach requires more effort to implement than both of the other methods but will result in a smaller port list than the "superset" method and a more legible design than the "vector" approach.

All of the selection schemes presented above modify the port lists for the reconfigurable modules; therefore, both require a port abstraction approach that will link the original unique port names to the new generalized port names without requiring the modification of any execution logic in the HDL design. It does, however, require

architecture modifications in both the instantiating module and the reconfigurable modules. In the reconfigurable modules, all abstracted ports can be tied to their respective signals with an assign statement. In the instantiating module, however, the abstraction process is more complicated. Any mutually exclusive output signals associated with a reconfigurable module can be linked to their respective abstracted port with an assign statement. For the rest of the signals, a multiplexer circuit is implemented to allow the system to determine what signal should be connected to what abstracted port based on which reconfigurable module is currently on the chip.

Because one of the main goals of this project is to evaluate the design size benefits associated with dynamic partial reconfiguration systems, "I/O Limiting" is a factor when choosing which option to implement. The "vector approach produces the greatest size reduction benefit possible. That is, using the approach, if the reconfigurable partition size can be reduced to the point that it is I/O limited, any further reduction in size would have to be the result of a reduction in the port list size. However, the port list size is already at its minimum, therefore reducing it would cause some reconfigurable module to not be supplied its required port counts. This creates a contradiction. The selection approach chosen for the Decoder conversion is the subset solution because of its reduced port list size and legibility. Based on the data in Table 2.2, Table 2.3 shows a comparison of the port lists created for the Decoder using all three methods. It is clear from this table that the vector method provides the best results while only sacrificing code legibility.

26

|  | Table 2.3 | Port Abstraction | Method Size | Comparison |

|--|-----------|------------------|-------------|------------|

|--|-----------|------------------|-------------|------------|

|                                 | Superset | Vector | Subset |

|---------------------------------|----------|--------|--------|

| Number of Ports Across Boundary | 976      | 2      | 139    |

| Number of Bits Across Boundary  | 12,614   | 1643   | 1849   |

### 2.4 System Architecture Modification

Although it is possible for a given application to be architected in a way that already supports dynamic partial reconfiguration, this section outlines modifications that were made to the Decoder application to illustrate the type of architecture necessary for dynamic partial reconfiguration.

## 2.4.1 Data Flow Architecture

The first modification to the architecture is the removal of data flow selection logic that is rendered unnecessary during the partial reconfiguration conversion process. In the static design configuration of an application, a multiplexer bank is used to select the proper set of signals to route from the execution modules to the shared modules based on which module is currently executing. This original organization is shown in Figure 2.5. As can be seen in the figure, every executable module sends every one of its output to the datapath block. Because the execution modules operate sequentially, only one set of the outputs will be active at a time resulting in a high percentage of the signals being inactive at any given time. Furthermore, because the execution modules are all attempting to access the same resources in the datapath block, many of the signals redundantly point to the same destination.

Figure 2.5 Original Data Flow Architecture

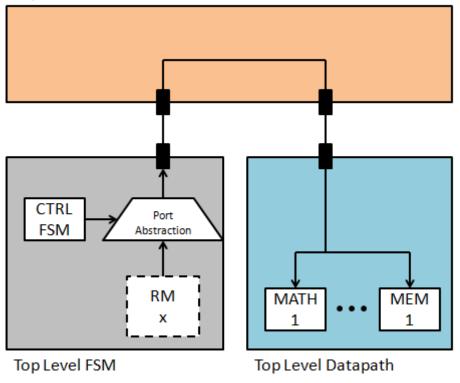

Although this design requires more inter-module communication than necessary, it functions properly. However, this design is not sufficient for a dynamic partial reconfiguration system. It is possible that all of the execution modules are designated as reconfigurable modules. In this case, only one of the executable module blocks will ever be on the chip at a time, producing only a single set of outputs. The adjustment for linking this set of outputs to the proper design signals is already managed by the port abstraction multiplexer described in the previous section. As a result, only a single set of signals connects the FSM block to the Datapath block. This makes the original shared module multiplexer useless because only a single input set will ever be driven resulting multiple floating inputs, as shown as red ports in Figure 2.6. Therefore, the multiplexer

bank in the datapath can be removed from the system architecture to reduce design complexity and size. The final system data flow architecture is shown in Figure 2.7.

Top Level Interface

Figure 2.6 Decoder Intermediate Data Flow Architecture

# **Top Level Interface**

Figure 2.7 Decoder Final Data Flow Architecture

# 2.4.2 External Signals

The second architecture modification required to convert the Decoder application was to revise the list of external signals from the Decoder and update their functionality. The modifications in this section are the only changes that affect the operation of the Decoder from its original version. However, the validation procedures presented in section 2.5 show a method for checking that the application will still function properly. There are three alterations made to the external signals of the Decoder: the removal of testbench signals, the extension of the completion state, and the addition of partial reconfiguration signals. The Decoder implementation provided by Duplantis et al. had many external signals that were used for application testbenching. These signals were used to pause execution at certain key points during the decoding process to allow the testbench to validate internal memory state. There signals are unnecessary now that the functionality of the Decoder's logic has been verified, so they have been removed to reduce the Decoder's design size. However, the pauses were created by states in the control logic that wait for an external signal to continue execution. To avoid modifying the control logic, a single continue signal is added to the external port list and permanently driven high. This allows the Decoder to "fall through" the pause states in the control logic.

Another modification to the external signals that, while not required to support dynamic partial reconfiguration, is necessary to interface with the Microblaze soft microprocessor is the extension of the completion state. In the original configuration, after the system completes the decoding process on one frame, a "done" state is entered for a single clock cycle that sets an external "done" signal high. After this clock cycle the system returns to the initial state and the "done" signal returns low. This single clock cycle is virtually impossible to detect by a polling trigger in the Microblaze's program, which is needed to serve the Decoder with the next set of frame data. Moreover, the timing operations performed in CHAPTER IV could only be completed if the Microblaze can detect when the Decoder has finished its operation on a frame. Therefore, the "done" signal was modified to remain at a high state while the Decoder is in its initial state and only be driven low when the start signal for the next frame is received.

The final modification to the external port list was the addition of two signals necessary to implement dynamic partial reconfiguration. These two signals are a load and

ready signal that allow the Decoder and Microblaze to communicate information about which reconfigurable module needs to be loaded and which is currently on the chip, respectively. Each signal is as wide as necessary to encode the number of reconfigurable modules in the reconfigurable module set. In the case of the Decoder, there are 24 reconfigurable modules; therefore, the load and ready signals are both five bits wide.

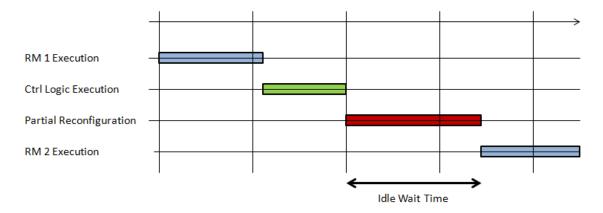

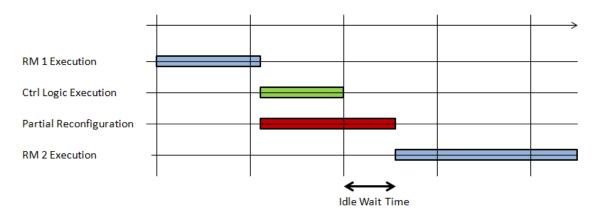

A key design decision for implementing dynamic partial reconfiguration is determining where in the control logic to signal the Microblaze to begin reconfiguring a new reconfigurable module. The simplest method would be to signal the Microblaze immediately before executing a reconfigurable module and then wait for the ready signal to report that the module has been loaded onto the FPGA to proceed with the execution of that module. However, simple analysis of the application flow can produce better results if the design has extra control logic in between the calls to the reconfigurable modules, as is the case with the Decoder. A system that calls functions sequentially gives the ability to determine which module will be needed next prior to execution. Therefore, it is possible to determine the earliest point in the application, after the previous reconfigurable module finishes executing, that a reconfigurable module can be guaranteed to be the next module to be executed. The control logic can signal the partial reconfiguration to begin at this point and continue executing while the partial reconfiguration process takes place in parallel. This method also requires that the application wait for the ready signal before each reconfigurable module is executed. This is necessary to guarantee that the partial reconfiguration process has completed before the application attempts to use the reconfigured logic. Figure 2.8 and Figure 2.9 show the theoretical difference in the

amount of time spent waiting on the partial reconfiguration process to complete. Note: these drawings are not to scale.

Figure 2.8 Partial Reconfiguration Wait Time Without Optimization

Figure 2.9 Partial Reconfiguration Wait Time With Optimization

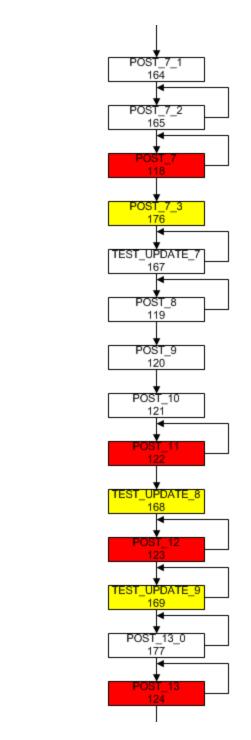

APPENDIX A gives a state diagram of the control logic for the Decoder and an illustration of which states (red) are executing reconfigurable modules and which states (yellow) are the optimized points where the Decoder signals the Microblaze to begin the partial reconfiguration process.

# 2.5 System Functionality Simulation

A vital component of the HDL application development cycle is operation validation. Although an application being converted to be partially, dynamically reconfigurable is assumed to have been functionally validated, the significant modifications to the system detailed in the previous sections require that the application be revalidated to ensure that the new design produces the same output as the original. However, standard verification methods for HDL designs cannot be used when testing a dynamic partial reconfiguration system. This is due to the fact that Xilinx tools are incapable of simulating partial reconfiguration [17]. Consequently, a customized test bench is presented in this section that allows for the testing of the functionality of the partial reconfiguration design. It should be noted that, while the HDL code tested by the presented method is not exactly the same as the code that is ultimately synthesized and implemented, the differences between the two do not affect the output of the system.