Florida International University FIU Digital Commons

**FIU Electronic Theses and Dissertations**

University Graduate School

11-12-2020

# Efficient, High Power Density, Modular Wide Band-gap Based Converters for Medium Voltage Application

Hadi Moradisizkoohi Florida International University, hmora041@fiu.edu

Follow this and additional works at: https://digitalcommons.fiu.edu/etd

Part of the Power and Energy Commons

### **Recommended Citation**

Moradisizkoohi, Hadi, "Efficient, High Power Density, Modular Wide Band-gap Based Converters for Medium Voltage Application" (2020). *FIU Electronic Theses and Dissertations*. 4554. https://digitalcommons.fiu.edu/etd/4554

This work is brought to you for free and open access by the University Graduate School at FIU Digital Commons. It has been accepted for inclusion in FIU Electronic Theses and Dissertations by an authorized administrator of FIU Digital Commons. For more information, please contact dcc@fiu.edu.

### FLORIDA INTERNATIONAL UNIVERSITY

Miami, Florida

# EFFICIENT, HIGH POWER DENSITY, MODULAR WIDE BAND-GAP BASED CONVERTERS FOR MEDIUM VOLTAGE APPLICATION

A dissertation submitted in partial fulfillment of the

requirements for the degree of

### DOCTOR OF PHILOSOPHY

in

### ELECTRICAL AND COMPUTER ENGINEERING

by

Hadi Moradisizkoohi

2020

To: Dean John Volakis College of Engineering and Computing

This dissertation, written by Hadi Moradisizkoohi, and entitled Efficient, High Power Density, Modular Wide Band-Gap Based Converters for Medium Voltage Application, having been approved in respect to style and intellectual contents, is referred to you for judgment.

We have read this dissertation and recommend that it be approved.

Sakhrat Khizroev

Mohammed Hadi

Raj Pulugurtha

Osama A. Mohammed, Major Professor

Date of Defense: November 12, 2020

The dissertation of Hadi Moradisizkoohi is approved.

Dean John Volakis College of Engineering and Computing

Andrés G. Gil Vice President for Research and Economic Development and Dean of the University Graduate School

Florida International University, 2020

© Copyright 2020 by Hadi Moradisizkoohi

All rights reserved.

## DEDICATION

This dissertation is dedicated to My Parents, who instilled in me the virtues of perseverance and commitment and relentlessly encouraged me to strive for excellence.

#### ACKNOWLEDGMENTS

This thesis would not have been possible without the inspiration and support of a number of wonderful individuals. First and foremost, I owe my deepest gratitude to my parents for their love and support throughout my life. Thank you both for giving me strength to reach for the stars and chase my dreams. My brother and sister deserve my wholehearted thanks as well.

I would like to thank my supervisor, Professor Osama Mohammed, for supervising me in this work, and for providing me with endless research ideas and technical support. He also provided me with financial support through a research assistantship in his research group working on his research projects and for some semesters as a teaching assistant at the Electrical and Computer Engineering Department at FIU. I would also like to thank Professor Mohammed for making me a part of the Energy System Research Laboratory (ESRL) and for the excellent research facilities made available for this project. I have gained a lot of skills and experience at ESRL with its first-class equipment needed to build and experimentally verify the results. This helped me complete my doctoral studies and enabled scholarly production resulting from this project. Also, as my doctoral research started to gain traction, Professor Mohammed provided me opportunities to grow within my professional career inside and outside the university and helped me build my own name in this field.

Furthermore, I would like to thank professors Sakhrat Khizroev, Mohammed Hadi, and Raj Pulugurtha for their insightful comments and suggestions to my dissertation.

v

Also, thanks to all my colleagues at ESRL, who created a professional and collaborative environment that helped me reach my research objectives. I also like to thank the Department of Electrical and Computer Engineering Staff who have helped me tremendously throughout my years of doctoral research.

### ABSTRACT OF THE DISSERTATION

# EFFICIENT, HIGH POWER DENSITY, MODULAR WIDE BAND-GAP BASED CONVERTERS FOR MEDIUM VOLTAGE APPLICATION

by

Hadi Moradisizkoohi

Florida International University, 2020

Miami, Florida, USA

Professor Osama A. Mohammed, Major Professor

Recent advances in semiconductor technology have accelerated developments in medium-voltage direct-current (MVDC) power system transmission and distribution. A DC-DC converter is widely considered to be the most important technology for future DC networks. Wide band-gap (WBG) power devices (i.e. Silicon Carbide (SiC) and Gallium Nitride (GaN) devices) have paved the way for improving the efficiency and power density of power converters by means of higher switching frequencies with lower conduction and switching losses compared to their Silicon (Si) counterparts. However, due to rapid variation of the voltage and current, di/dt and dv/dt, to fully utilize the advantages of the Wide-bandgap semiconductors, more focus is needed to design the printed circuit boards (PCB) in terms of minimizing the parasitic components, which impacts efficiency.

The aim of this dissertation is to study the technical challenges associated with the implementation of WBG devices and propose different power converter topologies for MVDC applications. Ship power system with MVDC distribution is attracting widespread interest due to higher reliability and reduced fuel consumption. Also, since the charging time is a barrier for adopting the electric vehicles, increasing the voltage level of the dc bus

to achieve the fast charging is considered to be the most important solution to address this concern. Moreover, raising the voltage level reduces the size and cost of cables in the car. Employing MVDC system in the power grid offers secure, flexible and efficient power flow.

It is shown that to reach optimal performance in terms of low package inductance and high slew rate of switches, designing a PCB with low common source inductance, power loop inductance, and gate-driver loop are essential. Compared with traditional power converters, the proposed circuits can reduce the voltage stress on switches and diodes, as well as the input current ripple. A lower voltage stress allows the designer to employ the switches and diodes with lower on-resistance  $R_{DS(ON)}$  and forward voltage drop, respectively. Consequently, more efficient power conversion system can be achieved. Moreover, the proposed converters offer a high voltage gain that helps the power switches with smaller duty-cycle, which leads to lower current and voltage stress across them. To verify the proposed concept and prove the correctness of the theoretical analysis, the laboratory prototype of the converters using WBG devices were implemented. The proposed converters can provide energy conversion with an efficiency of 97% feeding the nominal load, which is 2% more than the efficiency of the-state-of-the-art converters. Besides the efficiency, shrinking the current ripple leads to 50% size reduction of the input filter inductors.

## TABLE OF CONTENTS

| CHAPTER |                                                                                                                                                              | PAGE |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1       | Introduction 1.1 Background                                                                                                                                  |      |

|         | 1.2 Modular Power Electronics Converter                                                                                                                      | 6    |

|         | 1.3 Techniques to Improve the Efficiency                                                                                                                     | 12   |

|         | 1.4 Research Objectives                                                                                                                                      | 14   |

|         | 1.5 Original Contribution of This Thesis                                                                                                                     | 16   |

|         | 1.6 Dissertation Organization                                                                                                                                |      |

| 2       | A Bipolar DC-DC Converter with Wide Voltage-Gain Range for<br>Energy Storage Integration in Ship Power Systems<br>2.1 Introduction                           | 23   |

|         | 2.2 Proposed Isolated Bipolar Converter                                                                                                                      | 23   |

|         | 2.3 Operating Principles of the Proposed Circuit                                                                                                             | 24   |

|         | 2.4 Steady-State Analysis                                                                                                                                    | 28   |

|         | 2.5 Simulation Results                                                                                                                                       | 33   |

|         | 2.6 Conclusion                                                                                                                                               | 35   |

| 3       | A Family of Three-Port Three-Level Converter Based on<br>Asymmetrical Bidirectional Half-Bridge Topology for Fuel-Cell<br>Electric Vehicle Applications      |      |

|         | 3.2 Derivation Methodology of The TPTLC Topologies                                                                                                           | 37   |

|         | 3.3 Detailed Analysis and Design Consideration of the Stacked TPTLC                                                                                          | 42   |

|         | 3.4 Comparison of The Proposed Stacked TPTLC and Other Converters                                                                                            | 64   |

|         | 3.5 Loss Analysis and Experiment Verification                                                                                                                | 67   |

|         | 3.6 Conclusion                                                                                                                                               | 77   |

| 4       | Design and Implementation of a GaN-Based, Modular, PWM-<br>Controlled Quasi-Resonant, Bidirectional DC/DC Converter<br>Using GaN Switches for EV Application | 79   |

|         | 4.2 Proposed converter and its Operation Principle                                                                                                           | 19   |

|   | 4.3 Steady-State Analysis                                                                                                                                             | 87  |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | 4.4 Loss Analysis                                                                                                                                                     | 96  |

|   | 4.5 Comparison with the State-of-the-Art Converters                                                                                                                   | 99  |

|   | 4.6 Simulation and Experimental Results 1                                                                                                                             | .03 |

|   | 4.7 Conclusion 1                                                                                                                                                      | 17  |

| 5 | A Multilevel Bidirectional Buck-Boost Converter with<br>Distributed Voltage Stress Using eGaN HEMTs                                                                   |     |

|   | 5.2 Proposed converter and its Operation Modes                                                                                                                        |     |

|   | 5.3 Control Algorithm                                                                                                                                                 |     |

|   | 5.4 Design Specification                                                                                                                                              |     |

|   | 5.5 Simulation Results                                                                                                                                                |     |

|   | 5.6 Conclusion                                                                                                                                                        | 26  |

| 6 | A Voltage-Quadrupler Interleaved Bidirectional DC-DC<br>Converter with Intrinsic Equal Current Sharing Characteristic for<br>Electric Vehicle Applications            |     |

|   | 6.2 Structure and Operating Principles of the Proposed Converter 1                                                                                                    | 28  |

|   | 6.3 Steady-State Analysis of the Proposed Converter 1                                                                                                                 | 33  |

|   | 6.4 Design Considerations1                                                                                                                                            | 37  |

|   | 6.5 Performance Comparison1                                                                                                                                           | 40  |

|   | 6.6 Analysis of The Dynamic Performance 1                                                                                                                             | .43 |

|   | 6.7 Experimental Results1                                                                                                                                             | 45  |

|   | 6.8 Conclusion 1                                                                                                                                                      | 52  |

| 7 | Experimental Verification of a GaN-Based Double-Input Soft-<br>Switched DC/DC Converter for Hybrid Electric Vehicle<br>Applications with Hybrid Energy Storage System | 54  |

|   | 7.1 Introduction                                                                                                                                                      |     |

|   | 7.2 Proposed Double-Input Three-Level DC-DC Converter                                                                                                                 | 54  |

|   | 7.3 Operation Scenarios1                                                                                                                                              | 57  |

|   | 7.4 Design Considerations 1                                                                                                                                           |     |

|   | 7.5 Comparison of The Proposed Converter With Other<br>Converters                                                                                                     |     |

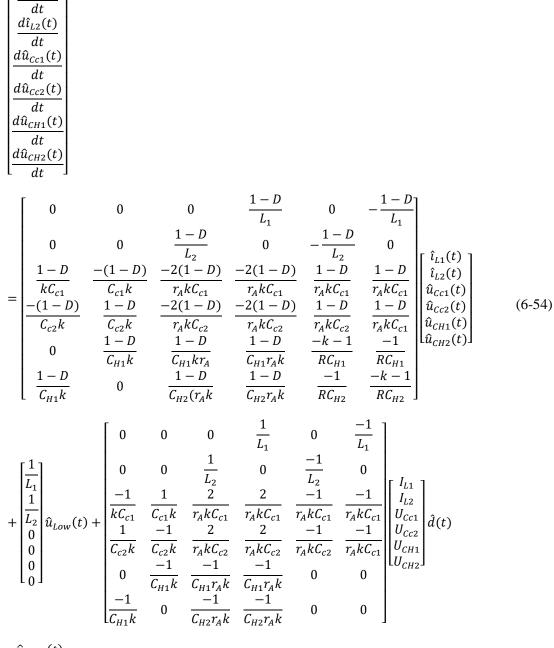

|   | 7.6 Dynamic Modeling and Control                                                                                                                                      |     |

|   |                                                                                                                                                                       | , , |

|    | 7.7 Power Management Algorithm                                                                                                                                    | . 178 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|    | 7.8 Experimental Results                                                                                                                                          | . 180 |

|    | 7.9 Conclusion                                                                                                                                                    | . 183 |

| 8  | PWM Plus Phase-Shift Modulated Three-Port Three-Level Soft-<br>Switching Converter Using GaN Switches for Photovoltaic<br>Applications                            |       |

|    | 8.2 Proposed STPTLC and Its Operation Analysis                                                                                                                    |       |

|    | 8.3 Experimental Results and Analysis                                                                                                                             |       |

|    | 8.4 Conclusion                                                                                                                                                    |       |

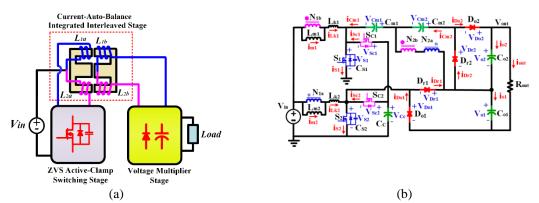

| 9  | An Integrated Interleaved Ultra High Step-Up DC-DC Converter<br>Using Dual Cross-Coupled Inductors With Built-in Input Current<br>Balancing for Electric Vehicles |       |

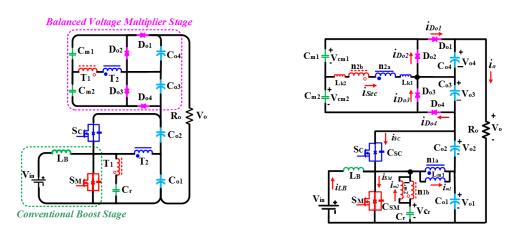

|    | 9.2 Proposed Integrated Interleaved Ultra High Step-Up DC-DC Converter with Dual Coupled-Inductors                                                                | . 225 |

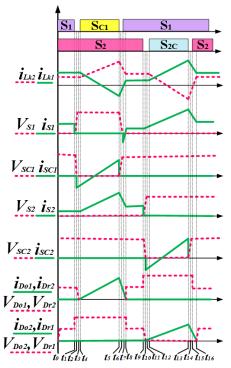

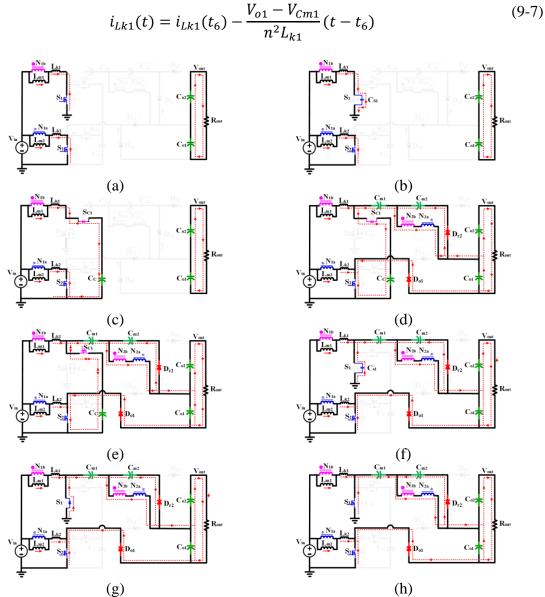

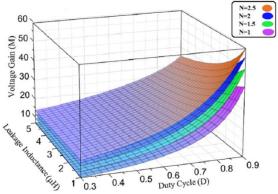

|    | 9.3 Steady-State Performance of the Proposed Converter                                                                                                            |       |

|    | 9.4 Comparison of The Proposed Converter and Other HSUCs                                                                                                          | . 241 |

|    | 9.5 Design Considerations                                                                                                                                         | . 245 |

|    | 9.6 Efficiency Analysis                                                                                                                                           |       |

|    | 9.7 Experimental Results                                                                                                                                          | . 249 |

|    | 9.8 Conclusion                                                                                                                                                    | . 255 |

| 10 | A Soft-Switched DC/DC Converter Using Integrated Dual Half-<br>Bridge with High Voltage Gain and Low Voltage Stress for DC<br>Microgrid Applications              |       |

|    | 10.2 Structure and Operating Principles of the Proposed Converter                                                                                                 | . 257 |

|    | 10.3 Loss Analysis of Proposed Converter                                                                                                                          | . 271 |

|    | 10.4 Design Considerations                                                                                                                                        | . 273 |

|    | 10.5 Simulation and Experimental Results                                                                                                                          | . 275 |

|    | 10.6 Conclusions                                                                                                                                                  |       |

| 11 | Family of Modular Single-Stage Quasi-Resonant Inverters                                                                                                           |       |

| 11.2 Examples of the existing inverters                                                | 284 |

|----------------------------------------------------------------------------------------|-----|

| 11.3 The proposed Family of MQRIs                                                      | 286 |

| 11.4 The Proposed Family of Single-Stage Quasi-Resonant<br>Inverters Design Directions | 287 |

| 11.5 Application Examples Using the Proposed MQRI                                      | 287 |

| 11.6 Advantages of The Proposed Single-Stage Quasi-Resonant<br>Inverter                | 289 |

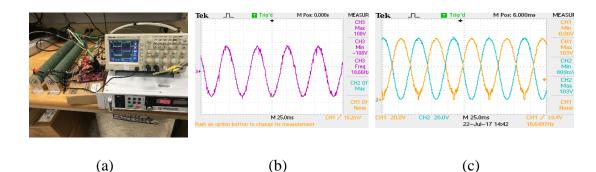

| 11.7 Experimental Results                                                              | 293 |

| 11.8 Conclusion                                                                        | 294 |

| Conclusions and Future Work                                                            | 296 |

| 12.2 Recommendations for Future Work                                                   | 299 |

| List of References                                                                     | 301 |

| VITA                                                                                   | 318 |

12

## LIST OF TABLES

| TABLE PAGE                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 1.1: Overview of different dc/dc converters for MVDC applications                                                                                                       |

| Table 3.1: Non-isolated three-port three-level DC/DC converters comprised of         ABHB modules                                                                             |

| Table 3.2: Partially-isolated three-port three-level DC/DC converters derived from ABHB modules                                                                               |

| Table 3.3: Current of inductor L <sub>B2</sub> for different values of duty cycle and phase-shift ratio.    57                                                                |

| Table 3.4: RMS Current of inductor L <sub>B2</sub> for different operating cases                                                                                              |

| Table 3.5: Comparison study between the proposed converter and other TPCs                                                                                                     |

| Table 3.6: Design specifications.    67                                                                                                                                       |

| Table 3.7: Loss equations for key components                                                                                                                                  |

| Table 4.1: RMS current, turn-off current, and maximum current of switches                                                                                                     |

| Table 4.2: Performance comparison ( $V_{BT}$ = 150 V, $V_{DC}$ = 600 V, $P_{out}$ = 1 kW, and $f_s$ = 100 kHz)                                                                |

| Table 4.3: Parameters of the prototype.    104                                                                                                                                |

| Table 4.4: RMS current of inductors and switches in case study II (battery voltage V <sub>BT</sub> =53 V, P <sub>out</sub> =1 kW, V <sub>DC</sub> =600 V, D=0.58, and S=4)109 |

| Table 4.5: RMS current of inductors and switches in case II (battery voltage V <sub>BT</sub> =120 V, P <sub>out</sub> =1 kW, V <sub>DC</sub> =600 V, D=0.63, and P=4)110      |

| Table 6.1: Loss equations for key components                                                                                                                                  |

| Table 6.2: Comparison Between the Proposed Converter and Other Bidirectional      Converters                                                                                  |

| Table 6.3: Experiment Parameters and Components    148                                                                                                                        |

| Table 7.1: Comparison study between the proposed converter and other converters 172                                                                                           |

| Table 7.2: Main Experimental Parameters of The Proposed Converter    172                                                                                                      |

| Table 8.1: The Current of inductor $L_{B2}$ for different values of D and $\theta$                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 8.2: The RMS Current of inductor $L_{B2}$ for different operating cases                                                                                                                                |

| Table 8.3: Comparison study between the proposed converter and other TPCs                                                                                                                                    |

| Table 8.4: Design specifications.    215                                                                                                                                                                     |

| Table 8.5: Loss equations for key components                                                                                                                                                                 |

| Table 9.1: Performance Comparison of the Proposed Converter and the Converter Cited in [21], [24], [28], and [29].       242                                                                                 |

| Table 9.2: Comparison of magnetic components size between the proposed converter and other converters. ( $P_{out}$ =1000 W, $V_{in}$ = 30 V, $V_{out}$ = 600 V, $f_s$ = 100 kHz, and $\Delta I_{in}$ = 10 %) |

| Table 9.3: Comparison of size of capacitors between the proposed converter and other converters. ( $P_{out}$ =1000 W, $V_{in}$ = 30 V, $V_{out}$ = 600 V, $f_s$ = 100 kHz, and $\Delta V$ = 10 %)            |

| Table 9.4: Parameters and Components of the Prototype                                                                                                                                                        |

| Table 10.1: Performance comparison among proposed converter and other converters.    270                                                                                                                     |

| Table 10.2: Parameters and components of implemented converter.    275                                                                                                                                       |

| Table 11.1: The laboratory setup specification    294                                                                                                                                                        |

## LIST OF FIGURES

| FIGURE          | PA                                                                                                                                                                                                                                            | GE   |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

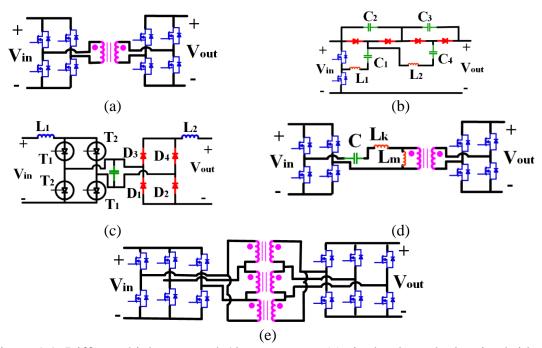

| bri<br>(c)      | fferent high step-up dc/dc converters. (a) single-phase dual active<br>idge (DAB1) converter. (b)Resonant switched-capacitor converter.<br>) Jovcic converter. (d) LLC converter. (e) three-phase dual active<br>idge (DAB3) converter.       | 4    |

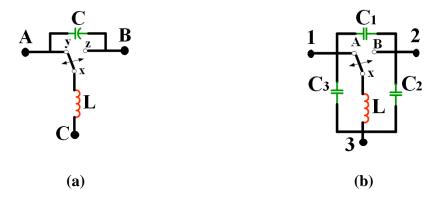

| •               | hematic of the canonical cell. (a) basic canonical cell. (b) advanced nonical cell.                                                                                                                                                           | 7    |

| Figure 1.3: Sch | hematic of a three level series-parallel switched capacitor converter                                                                                                                                                                         | 8    |

| Figure 1.4: Sch | hematic of a three-level flying capacitor converter                                                                                                                                                                                           | 9    |

| Figure 1.5: Sch | hematic of a modular three-level multilevel converter.                                                                                                                                                                                        | . 10 |

| Figure 1.6: Sch | hematic of a charge-pump converter                                                                                                                                                                                                            | . 11 |

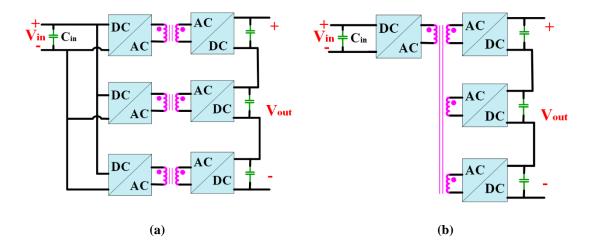

| •               | hematic of a cascaded converters. (a) series-parallel connected onverters. (b) Multi-winding transformer converter                                                                                                                            | 12   |

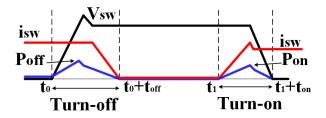

| Figure 1.8: Cu  | arrent, voltage, and power loss during hard-switching performance                                                                                                                                                                             | . 13 |

| Figure 1.9: Eq  | uivalent model of MOSFET                                                                                                                                                                                                                      | . 14 |

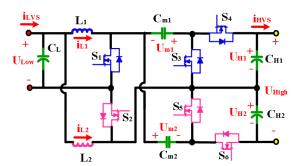

| 0               | oposed isolated converter and its equivalent circuit. (a) Circuit<br>agram of proposed isolated converter. (b) Equivalent circuit                                                                                                             | 24   |

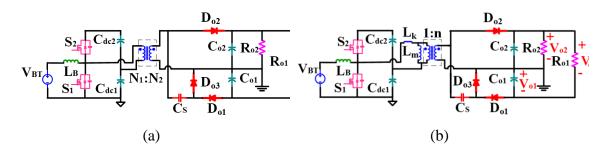

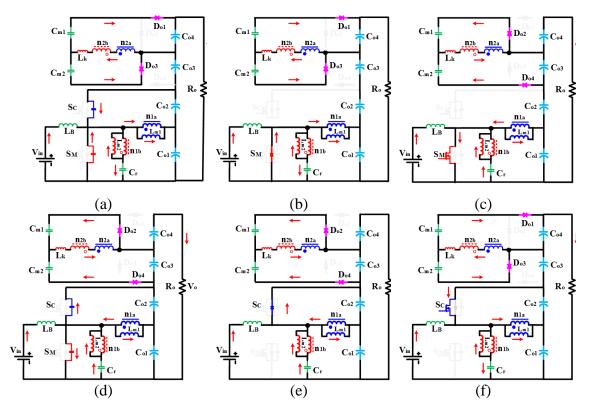

| 0 1             | peration intervals of the bipolar DC-DC converter. (a) Interval 1. (b)<br>terval 2. (c) Interval 3. (d) Interval 4. (e) Interval 5. (f) Interval 6                                                                                            | 25   |

| Figure 2.3: Ke  | ey waveforms                                                                                                                                                                                                                                  | . 26 |

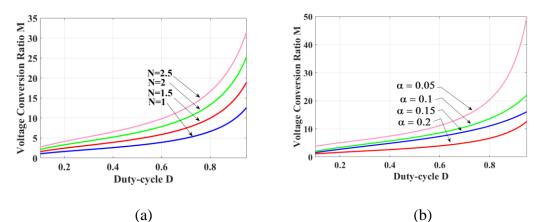

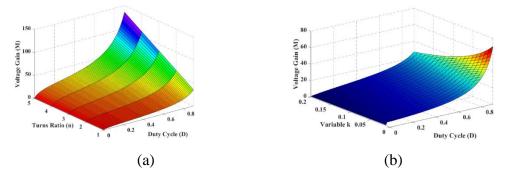

|                 | bltage gain as a function of turns-ratio and $\alpha$ . (a) Voltage gain under fferent turns-ratio ( $\alpha = 0.1$ ). (b) Voltage gain under different $\alpha$ (v=1)                                                                        | 30   |

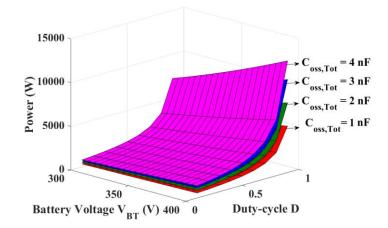

| •               | oft-switching condition of main switch $S_1$ under different output ower, battery voltage, and duty-cycle for various values of $C_{oss,Tot}$                                                                                                 | 31   |

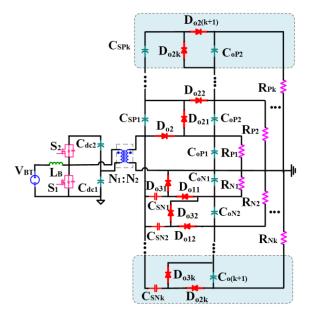

| Figure 2.6: Ext | tended version of the proposed isolated converter                                                                                                                                                                                             | . 33 |

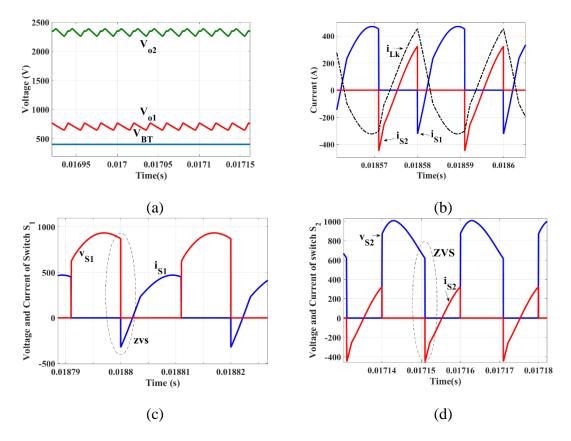

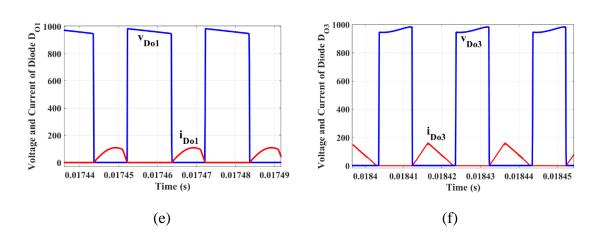

| V <sub>o</sub>  | mulation results. (a) battery voltage and output voltage levels $V_{o1}$ and $_{o2}$ . (b) Current of switches and the leakage inductor current $i_{Lk}$ . (c) bltage and current of switch $S_1$ . (d) voltage and current of switch $S_2$ . |      |

|             | (e) voltage and current of diode $D_{o1}$ . (f) voltage and current of diode $D_{o2}$                                                                                                                                                                                | 35 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

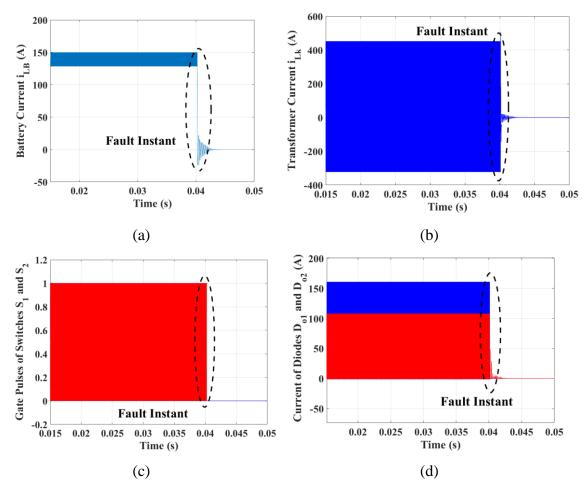

| Figure 2.8: | Simulation results when there is a pole to pole short circuit fault. (a) battery current $i_{LB}$ . (b) leakage inductor current $i_{Lk}$ . (c) current of switches $S_1$ and $S_2$ . (d) current of diodes $D_{o1}$ and $D_{o2}$                                    | 36 |

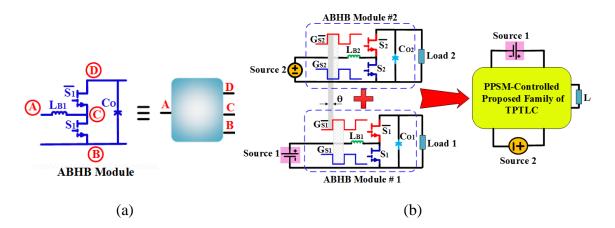

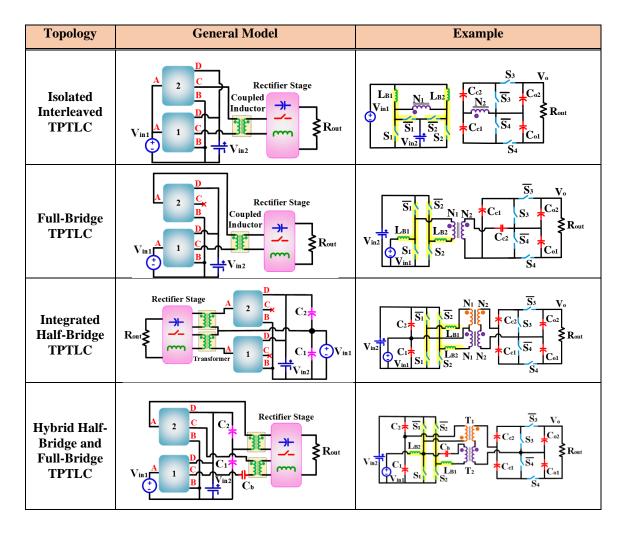

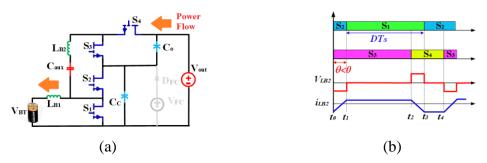

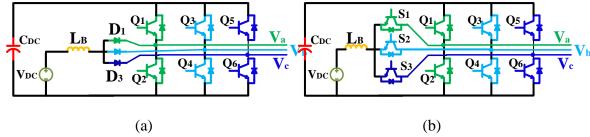

| Figure 3.1: | Topology derivation of the proposed family of three-port three-level DC/DC converters from ABHB modules: (a) Duty cycle controlled ABHB module. (b) PWM plus phase-shift modulated TPTLC composed of ABHB modules.                                                   | 39 |

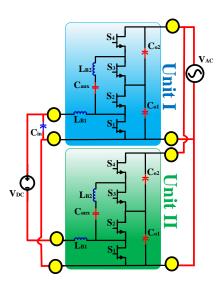

| Figure 3.2: | Proposed stacked TPTLC for FCEV applications                                                                                                                                                                                                                         | 14 |

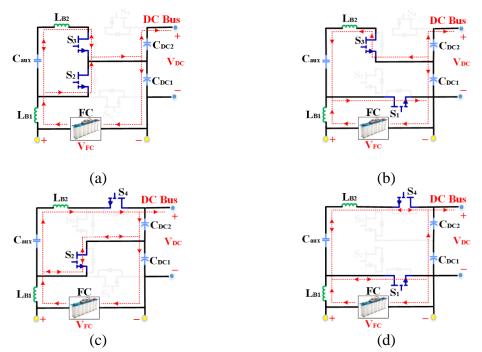

| Figure 3.3: | Equivalent circuits and key waveforms for scenario I. (a) Interval I. (b)<br>Interval II. (c) Interval III. (d) Interval IV. (e) Key waveforms                                                                                                                       | 18 |

| Figure 3.4: | Key waveforms                                                                                                                                                                                                                                                        | 18 |

| Figure 3.5: | The inductor current $i_{LB1}$ for scenarios I ( $P_{FC} < P_{out}$ ) and II ( $P_{FC} > P_{out}$ )                                                                                                                                                                  | 19 |

| Figure 3.6: | Equivalent circuit and key waveforms of converter in scenario III. (a)<br>Equivalent circuit. (b) Key waveforms                                                                                                                                                      | 19 |

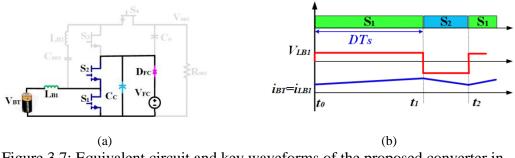

| Figure 3.7: | Equivalent circuit and key waveforms of the proposed converter in scenario IV. (a) Equivalent circuit. (b) key waveforms                                                                                                                                             | 50 |

| Figure 3.8: | Equivalent circuit of HVS of proposed stacked TPTLC                                                                                                                                                                                                                  | 51 |

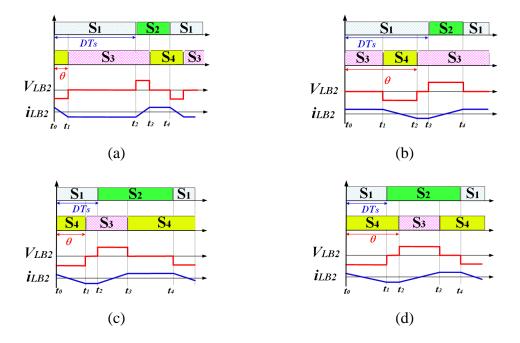

| Figure 3.9: | Different operation modes according to different values of duty-cycle<br>and phase shift ratio. (a) Case 1. (b) Case 2. (c) Case 3. (d) Case 4                                                                                                                       | 54 |

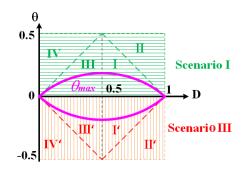

| Figure 3.10 | ): Operating cases for different values of phase shift ratio θ versus duty-<br>cycle D.                                                                                                                                                                              | 56 |

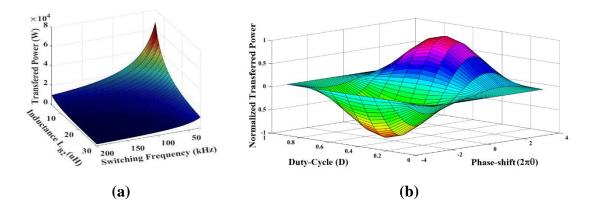

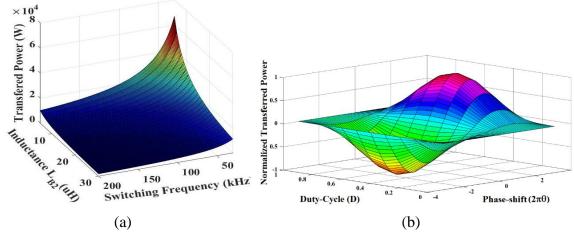

| Figure 3.11 | : Maximum power transferred and normalized transferred output power;<br>(a) Maximum power transferred as a function of switching frequency $f_s$<br>and inductance $L_{B2}$ . (b) Normalized power transferred versus different<br>phase-shift ratio and duty cycle. | 56 |

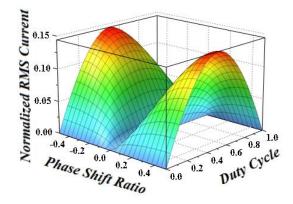

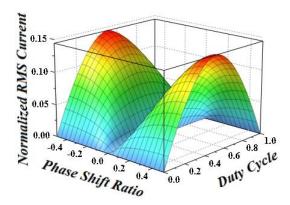

| Figure 3.12 | 2: Normalized RMS current versus different phase-shift ratio and duty cycle.                                                                                                                                                                                         | 58 |

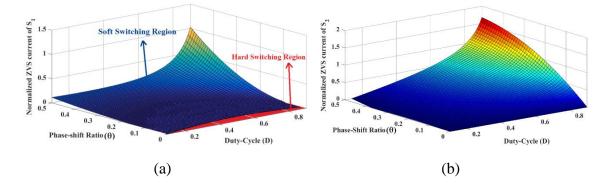

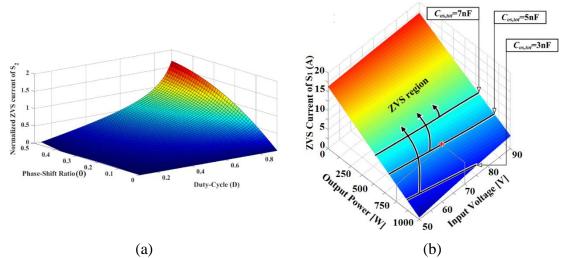

| Figure 3.13 | B: Normalized ZVS current of switches versus different phase-shift ratio<br>and duty cycle. (a) Switch S <sub>1</sub> . (b) Switch S <sub>2</sub>                                                                                                                    | 51 |

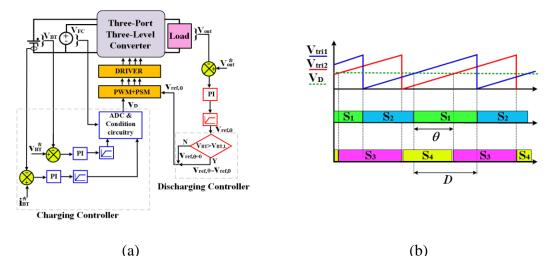

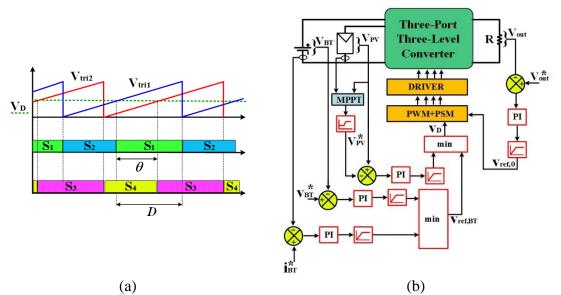

| Figure 3.14: Control scheme: (a) control block diagram of proposed converter, (b) modulation scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

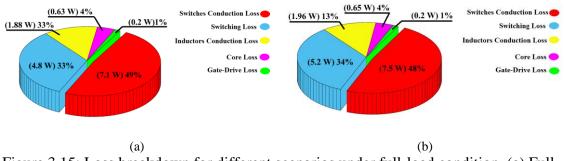

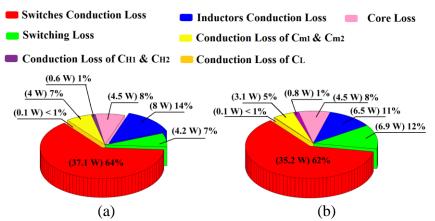

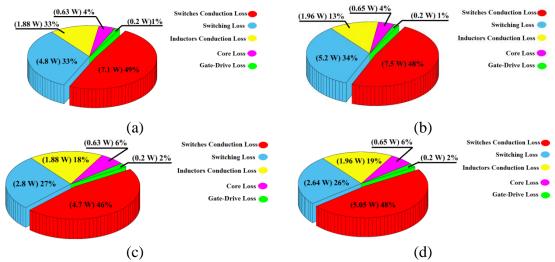

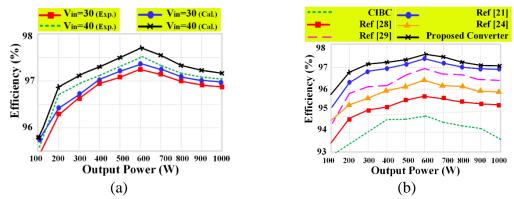

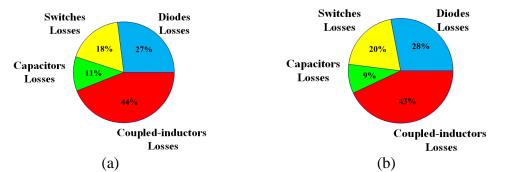

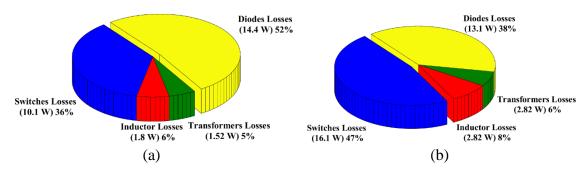

| Figure 3.15: Loss breakdown for different scenarios under full-load condition. (a)<br>Full-load $P_{out}=1$ kW, $V_{BT}=100$ V, $\theta=0.05$ and $D=0.53$ in scenario I. (b)<br>Full-load $P_{out}=1$ kW, $V_{BT}=100$ V, $\theta=-0.1$ and $D=0.53$ in scenario III                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

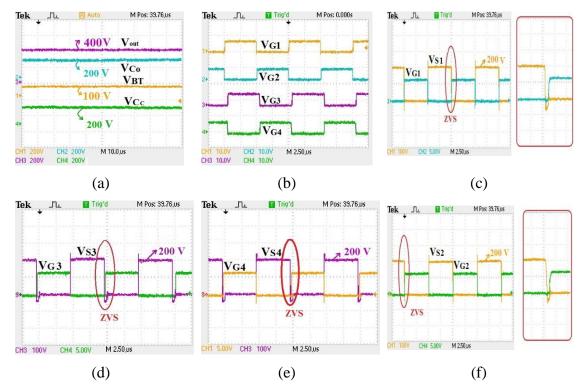

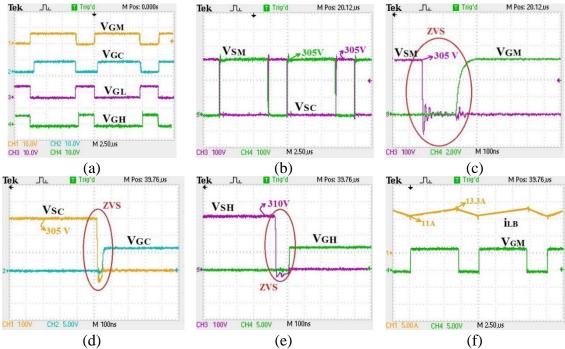

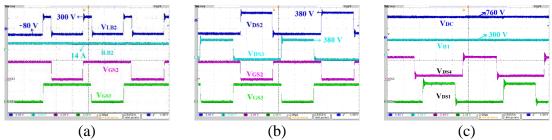

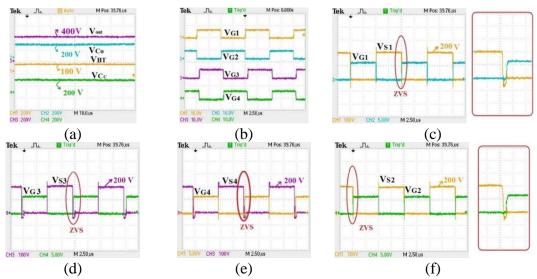

| Figure 3.16: Experimental results during scenario I at full-load condition when $V_{BT}$<br>= 100 V, $V_{out}$ = 400 V, $P_0$ = 1 kW, $\theta$ =0.05, and D=0.53. (a) Gate-<br>source voltage of switches. (b) drain-source voltage of switches S <sub>1</sub> and<br>S <sub>2</sub> (c) gate-source and drain-source voltage of switch S <sub>1</sub> . (d) gate-<br>source and drain-source voltage of switch S <sub>4</sub> . (e) gate-source and drain-<br>source voltage of switch S <sub>4</sub> . (f) gate-source voltage of switch S <sub>1</sub> and<br>inductor current i <sub>LB1</sub> and i <sub>LB1</sub>                                                                                                                                                                                                                                                                                                                                                         |

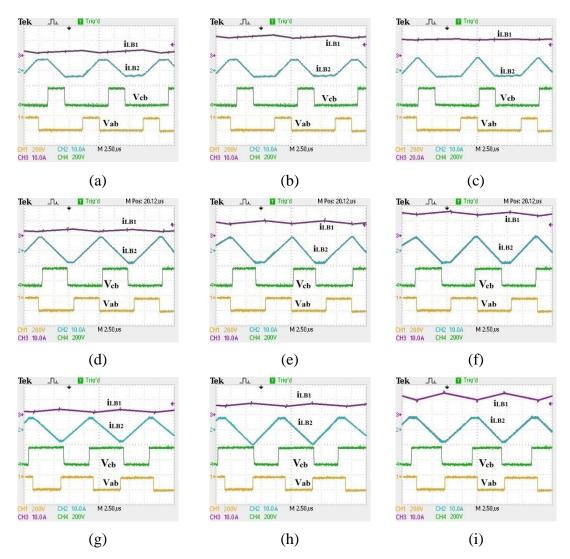

| Figure 3.17: Experimental results during scenario I for different battery voltage and output power $V_{FC} = 175.7 \text{ V}$ and $V_{out} = 400 \text{ V}$ . (a) $V_{BT} = 50 \text{ V}$ and $P_{out} = 100 \text{ W}$ . (b) $V_{BT} = 50 \text{ V}$ and $P_{out} = 500 \text{ W}$ (c) $V_{BT} = 50 \text{ V}$ and $P_{out} = 1000 \text{ W}$ . (d) $V_{BT} = 75 \text{ V}$ and $P_{out} = 100 \text{ W}$ . (e) $V_{BT} = 75 \text{ V}$ and $P_{out} = 500 \text{ W}$ . (f) $V_{BT} = 75 \text{ V}$ and $P_{out} = 1000 \text{ W}$ . (g) $V_{BT} = 100 \text{ V}$ and $P_{out} = 100 \text{ W}$ . (h) $V_{BT} = 100 \text{ V}$ and $P_{out} = 500 \text{ W}$ . (i) $V_{BT} = 100 \text{ V}$ and $P_{out} = 1000 \text{ W}$ . (j) $V_{BT} = 100 \text{ V}$ and $P_{out} = 1000 \text{ W}$ . (k) $V_{BT} = 100 \text{ V}$ and $P_{out} = 500 \text{ W}$ . (k) $V_{BT} = 100 \text{ V}$ and $P_{out} = 500 \text{ W}$ . (k) $V_{BT} = 100 \text{ V}$ and $P_{out} = 72 \text{ V}$ |

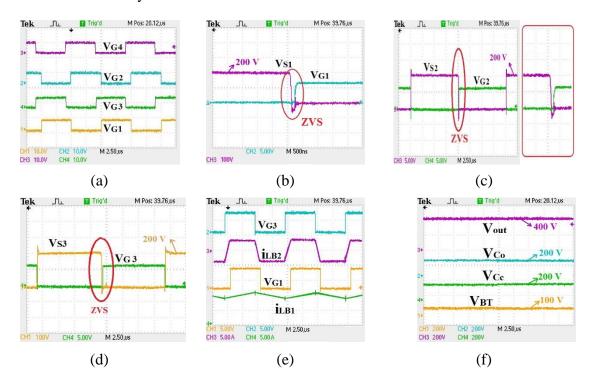

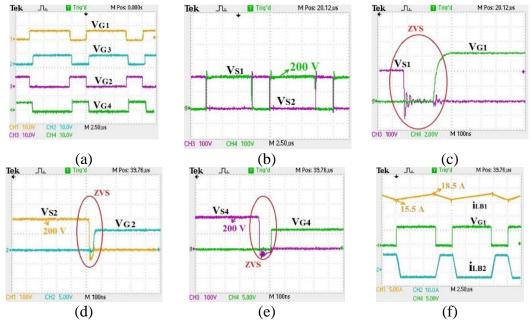

| Figure 3.18: Experimental results during scenario III at full load when D=0.53,<br>$\theta$ = -0.1, V <sub>BT</sub> = 100 V, V <sub>DC</sub> = 400 V, P <sub>0</sub> = 1000 W. (a) Gate pulse of<br>switches. (b) gate-source and drain-source voltage of switch S <sub>1</sub> . (c)<br>gate-source and drain-source voltage of switch S <sub>2</sub> . (d) gate-source and<br>drain-source voltage of switch S <sub>3</sub> . (e) gate-source of switches S <sub>1</sub> and S <sub>3</sub> ,<br>inductor current i <sub>LB1</sub> and i <sub>LB1</sub> . (f) Battery voltage, output voltage,<br>voltage across capacitors C <sub>01</sub> and C <sub>02</sub>                                                                                                                                                                                                                                                                                                               |

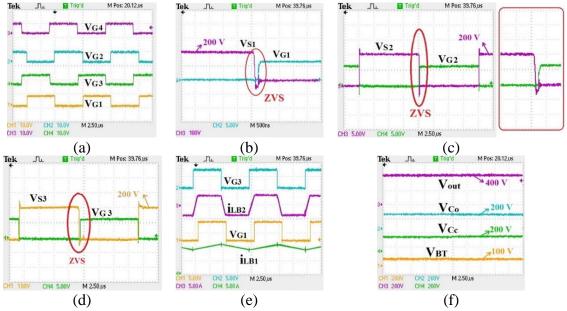

| Figure 3.19: Experimental results during scenario II and IV ( $V_{BT} = 70$ V, $V_{FC} = 175.7$ V, $P_O = 1000$ W, and D=0.6). (a) Gate-source voltage of switches. S <sub>1</sub> and S <sub>2</sub> and inductor current i <sub>LB1</sub> during Scenario II when $P_{FC}=1020$ W. (b) Battery voltage and gate-source voltage of switches S <sub>1</sub> and S <sub>3</sub> during scenario IV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <ul> <li>Figure 3.20: Experimental results under transition when Vout= 400 V and Pout= 1000 W. (a) Transition from scenario I to scenario III (VBT=100 V).</li> <li>(b) Transition from scenario III to scenario I (VBT=100 V). (c) Measured transient response characteristics during the stepped load change conditions. (VFC =175.8, PFC= 990 W, and VBT=50 V)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

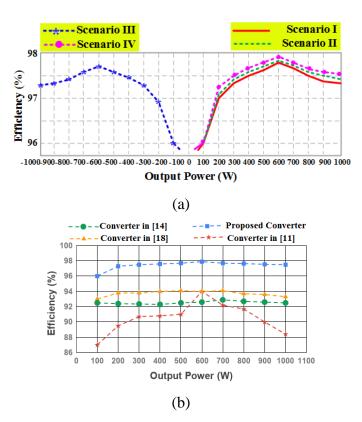

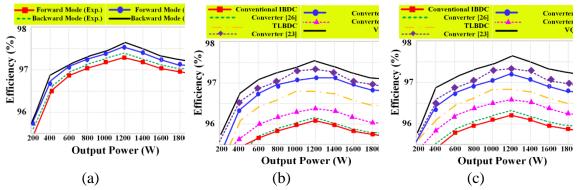

| Figure 3.21: Efficiency curves. (a) efficiency curves for different scenarios. (b)<br>Efficiency comparison between the proposed converter and other recent<br>TPCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

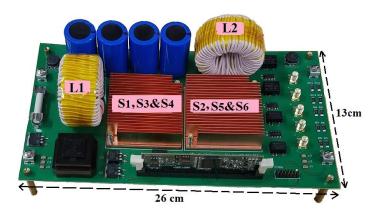

| Figure 3.22 | 2: Laboratory prototype of the Stacked TPTLC                                                                                                                                                                                                     | . 77 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

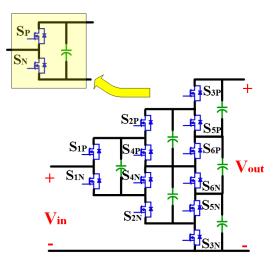

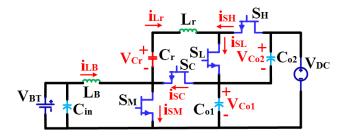

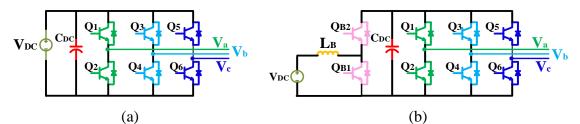

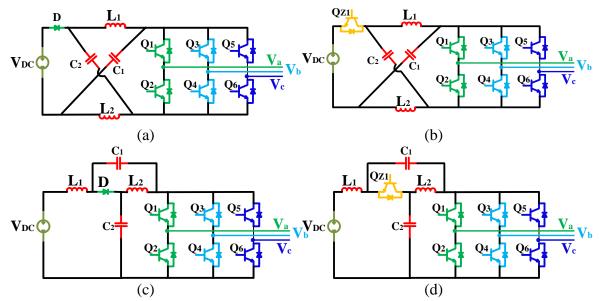

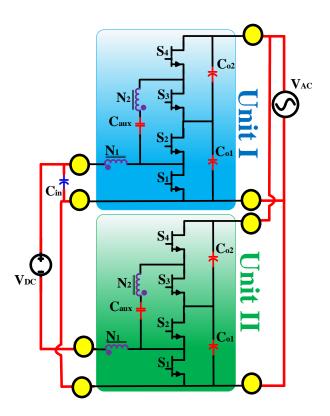

| Figure 4.1: | The single-phase version of proposed MQRB converter as a building block for multiphase MQRB converter.                                                                                                                                           | . 80 |

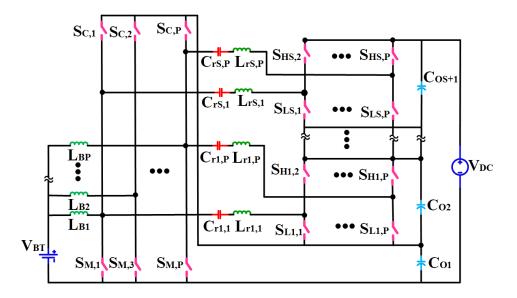

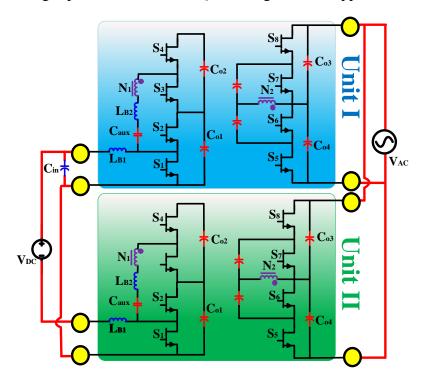

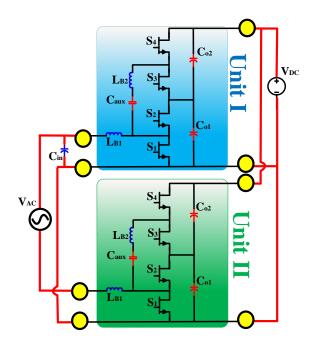

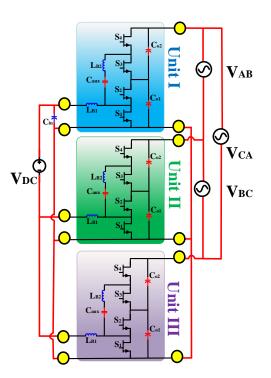

| Figure 4.2  | General configuration of the proposed MQRB converter for high-<br>voltage and high-power applications.                                                                                                                                           | . 81 |

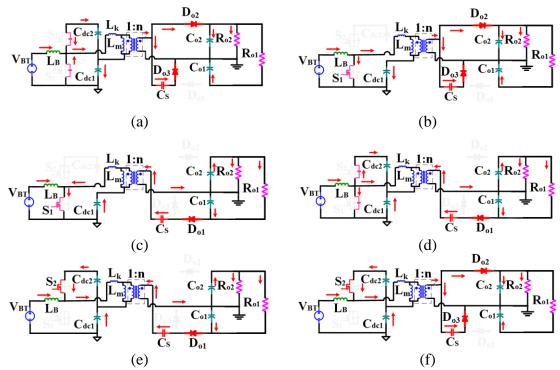

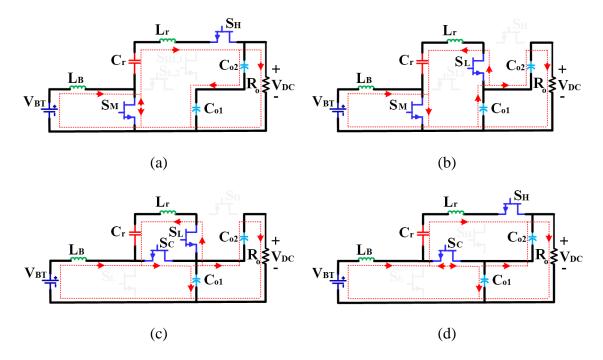

| Figure 4.3: | Different operation intervals during forward mode. (a) Interval 1; (b)<br>Interval 2; (c) Interval 3; (d) Interval 4                                                                                                                             | . 84 |

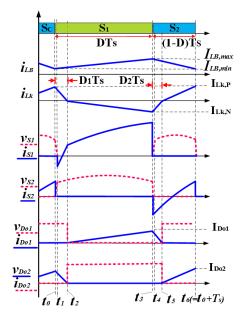

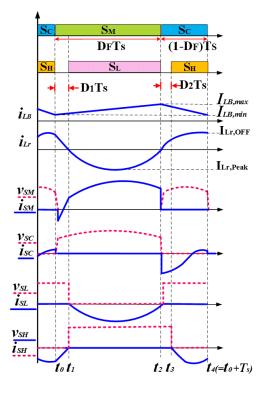

| Figure 4.4: | The key waveforms in forward mode                                                                                                                                                                                                                | . 85 |

| Figure 4.5: | Different operation intervals during backward mode. (a) Interval 1; (b)<br>Interval 2; (c) Interval 3; (d) Interval 4                                                                                                                            | . 86 |

| Figure 4.6: | The key waveforms in backward mode                                                                                                                                                                                                               | . 86 |

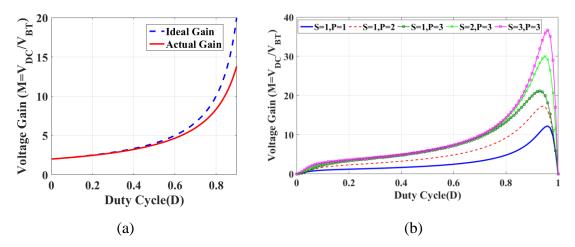

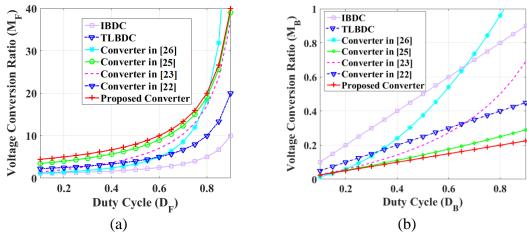

| Figure 4.7: | Voltage gain characteristics for different number of modules and duty-<br>cycle. (a) Voltage gain of single-phase MQRB. (b) Voltage gain of<br>MQRB.                                                                                             | . 89 |

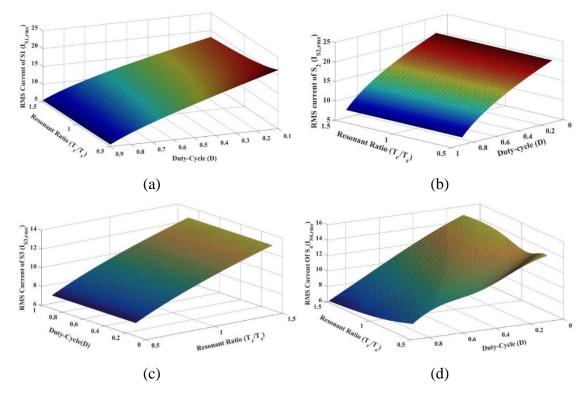

| Figure 4.8: | RMS current of switches for different duty-cycle (D) and resonant-ratio $(T_r/T_s)$ . (a) Switch S <sub>M</sub> . (b) Switch S <sub>C</sub> . (c) Switch S <sub>L</sub> . (d) Switch S <sub>H</sub>                                              | . 91 |

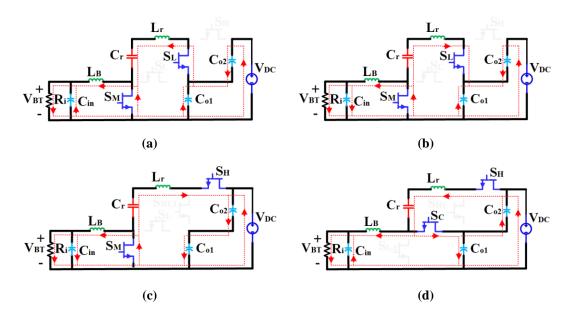

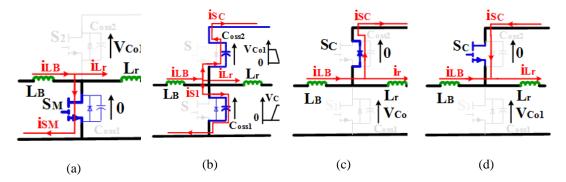

| Figure 4.9: | ZVS turn-on of switch $S_C$ . (a) Before turn-on instant. (b) Charging and discharging of output capacitor $C_{oss1}$ and $C_{oss2}$ . (d) Antiparallel diode freewheeling. (d) Flowing current in reverse direction.                            | . 92 |

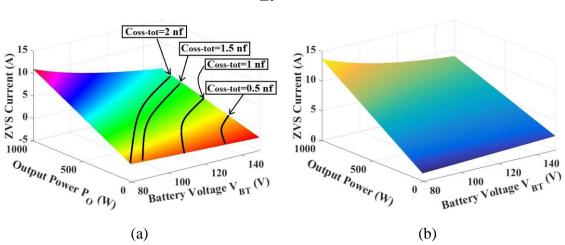

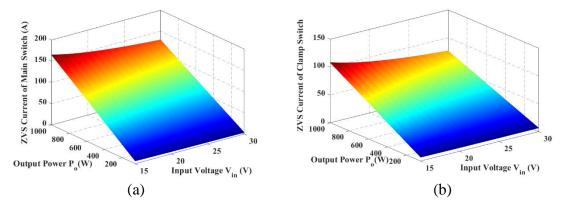

| Figure 4.10 | ): ZVS current for switches $S_M$ and $S_C$ . (a) switch $S_M$ . (b) switch $S_C$                                                                                                                                                                | . 94 |

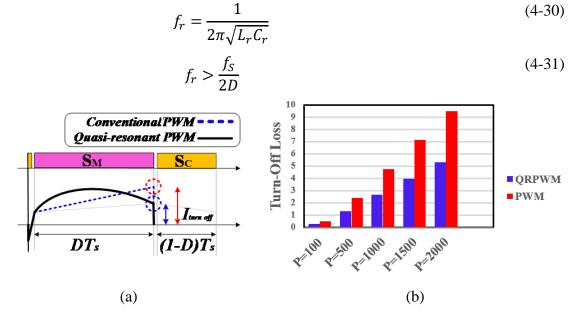

| Figure 4.11 | : QRPWM performance versus conventional PWM performance. (a)<br>Current waveform (b) Turn-off losses                                                                                                                                             | . 95 |

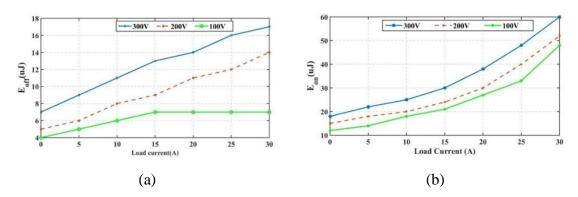

| Figure 4.12 | 2: Turn-on loss and the turn-off loss under different drain-source<br>voltages. (a) Turn-on loss under different drain-source voltages. (b)<br>Turn-off loss under different drain-source voltages.                                              | . 98 |

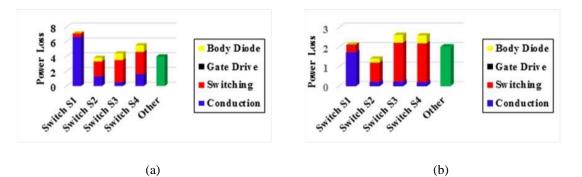

| Figure 4.13 | B: Loss breakdown under full load and half-load condition. (a) Full load.<br>(b) Half-load.                                                                                                                                                      | . 99 |

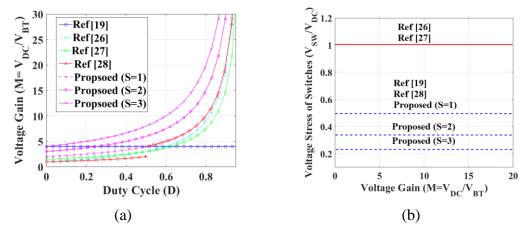

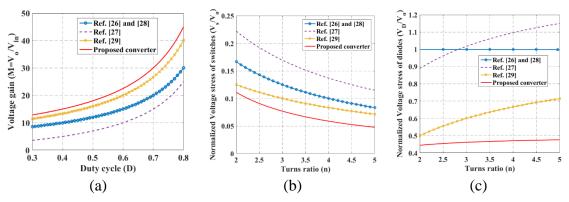

| Figure 4.14 | E: Performance comparisons regarding the voltage gain and voltage stress of switches. (a) voltage gain. (b) voltage stress of switches                                                                                                           | 101  |

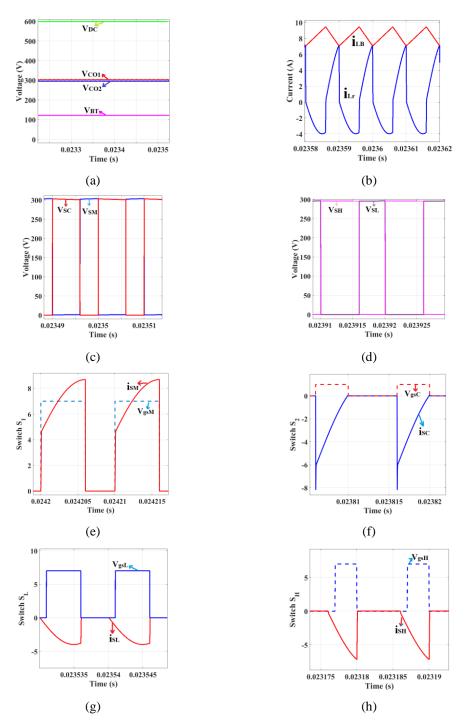

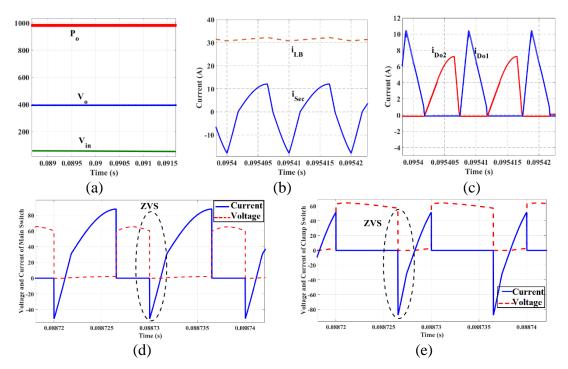

| Figure 4.15 | 5: Simulation results for case I (battery voltage $V_{BT}=122$ V, $P_{out}=1$ kW, $V_{DC}=600$ V, D=0.6, and P=S=1). (a) Voltage of battery, DC-link, and output capacitors. (b) Current of inductors $i_{LB}$ and $i_{L4}$ . (c) Voltage stress |      |

|             | of switches $S_M$ and $S_C$ . (d) Voltage stress of switches $S_L$ and $S_H$ . (e) gate-source voltage and current of main switch $S_M$ . (f) gate-source voltage and current of clamp switch $S_C$ . (g) gate-source voltage and current of switch $S_L$ . (h) gate-source voltage and current of switch $S_H$ 105                                                                                                                                                                                                                                     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

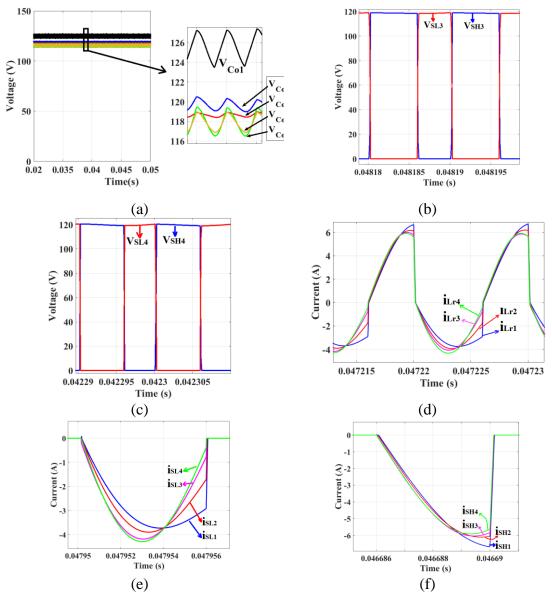

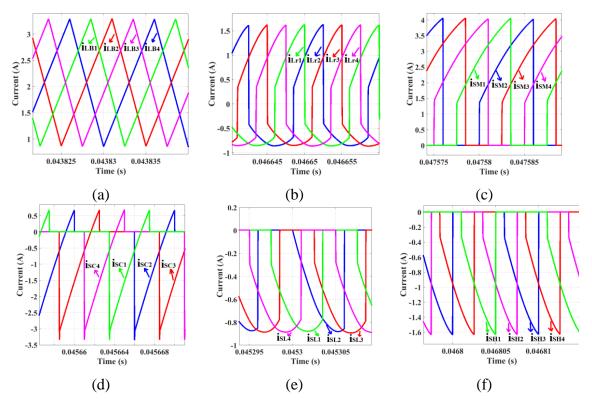

| Figure 4.16 | 5: Simulation results for case study II (battery voltage $V_{BT}=53$ V, $P_{out}=1$ kW, $V_{DC}=600$ V, D=0.58, and S=4). (a) Voltage of output capacitors $C_{o1}-C_{o5}$ . (b) Voltage stress of switch $S_{L3}$ and $S_{H3}$ . (c) Voltage stress of switch $S_{L4}$ and $S_{H4}$ . (d) Inductor current $i_{Lr1}$ - $i_{Lr4}$ . (e) Current of lower switches in each module $i_{SL1}$ - $i_{SL4}$ . (f) Current of upper switches in each module $i_{SH1}$ - $i_{SH4}$                                                                             |

| Figure 4.17 | 2: Simulation results for case study III (battery voltage $V_{BT}=120$ V,<br>$P_{out}=1$ kW, $V_{DC}=600$ V, $D=0.63$ , and $P=4$ ). (a) current of main switches<br>$i_{SM1}$ - $i_{SM4}$ . (b) current of clamp switches $i_{SC1}$ - $i_{SC4}$ . (d) Inductor current<br>$i_{Lr1}$ - $i_{Lr4}$ . (e) Current of lower switches in each module $i_{SL1}$ - $i_{SL4}$ . (f)<br>Current of upper switches in each module $i_{SH1}$ - $i_{SH4}$                                                                                                           |

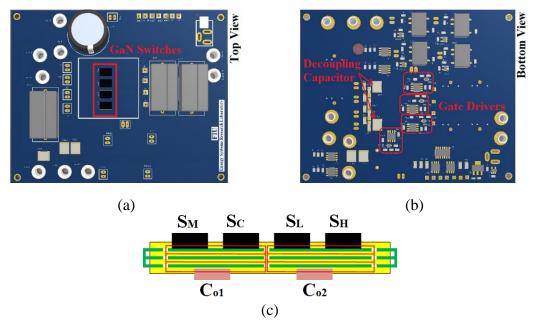

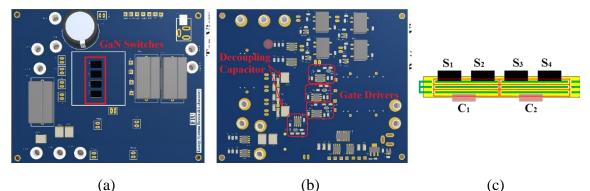

| Figure 4.18 | B: Layout of single-phase MQRB converter; (a) Top view. (b) Bottom view. (c) Side view                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

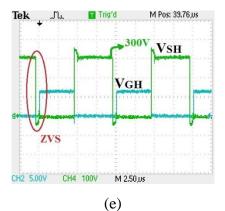

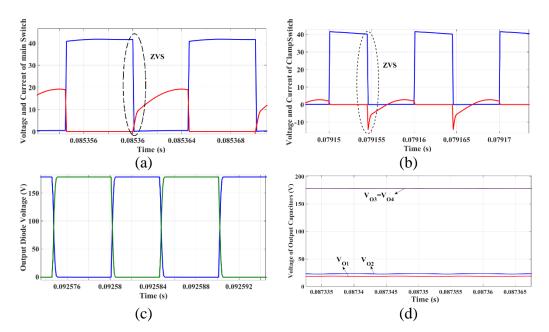

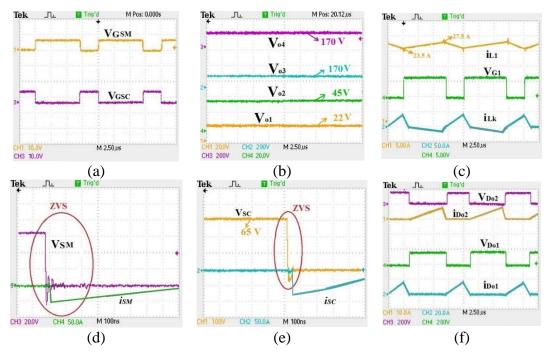

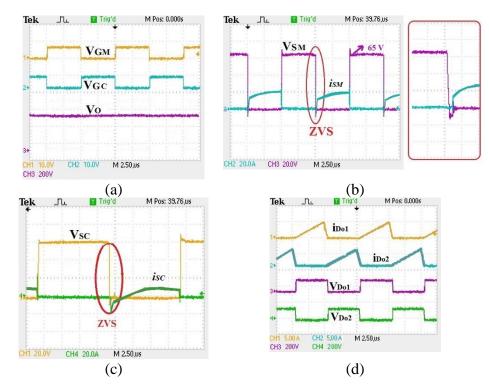

| Figure 4.19 | P: Experimental results of forward mode at full load condition when<br>$D=0.72$ ( $V_{BT} = 85$ V, $V_{DC} = 600$ V, $P_0 = 1$ kW). (a) Gate-source<br>voltage of switches. (b) Drain-source voltage of switches $S_M$ and $S_C$ (c)<br>Gate-source and drain-source voltage of switch $S_M$ . (d) Gate-source and<br>drain-source voltage of switch $S_C$ . (e) Gate-source and drain-source<br>voltage of switch $S_H$ . (f) Gate-source voltage of switch $S_M$ and inductor<br>current $i_{LB}$                                                     |

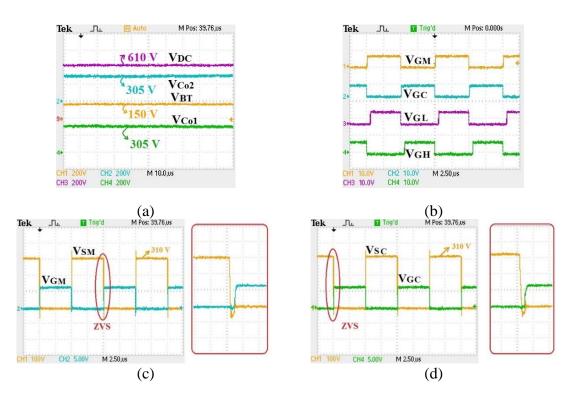

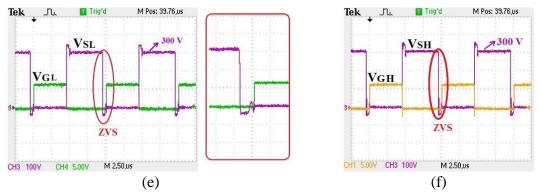

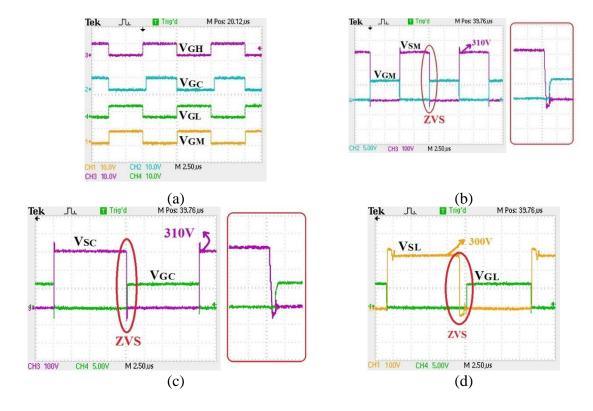

| Figure 4.20 | 2: Experimental results of forward mode at light load when D=0.5 ( $V_{BT}$ = 150 V, $V_{DC}$ = 600 V, $P_0$ = 100 W). (a) Battery voltage, High-side voltage, voltage across capacitors C <sub>01</sub> and C <sub>02</sub> . (b) Gate-source voltage of switches. (c) gate-source and drain-source voltage of switch S <sub>M</sub> . (d) gate-source and drain-source voltage of switch S <sub>C</sub> . (e) gate-source and drain-source voltage of switch S <sub>L</sub> . (f) gate-source and drain-source voltage of switch S <sub>H</sub> . 115 |

| Figure 4.21 | : Experimental results of backward mode at full load when D=0.5 ( $V_{BT}$ = 150 V, $V_{DC}$ = 600 V, $P_0$ = 1000 W). (a) Gate-source voltage of switches. (b) Gate-source and drain-source voltage of switch $S_M$ . (c) Gate-source and drain-source voltage of switch $S_C$ . (d) Gate-source and drain-source voltage of switch $S_L$ . (e) Gate-source and drain-source voltage of switch $S_H$ . (f) Thermal image of the converter                                                                                                              |

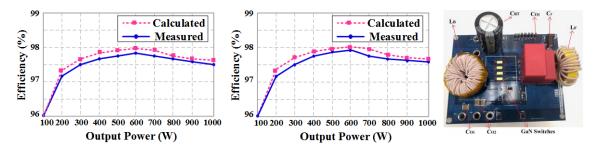

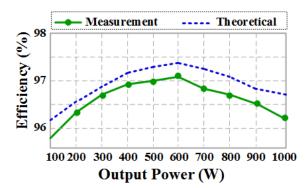

| Figure 4.22 | Efficiency curves and a photograph of the converter. (a) Calculated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

and measured efficiency in forward mode. (b) (a) Calculated and

|             | measured efficiency in backward mode. (c) A photograph of laboratory prototype.                                                                                                                                                                                                                                                                                                           | 117 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

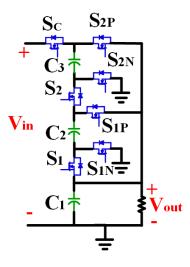

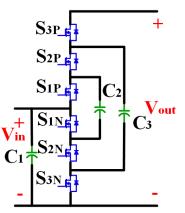

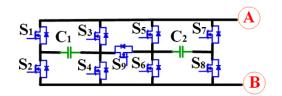

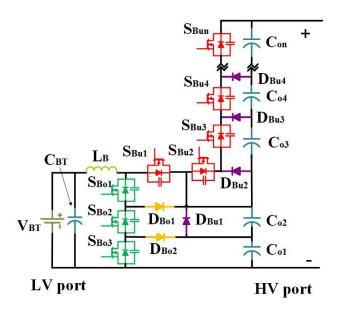

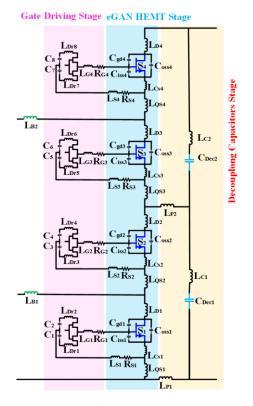

| Figure 5.1: | Circuit diagram of the Proposed Modular Converter                                                                                                                                                                                                                                                                                                                                         | 119 |

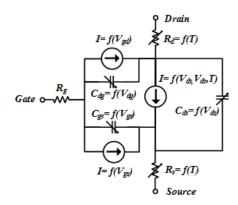

| Figure 5.2: | GanSys Model GS66508P PSpice equivalent model                                                                                                                                                                                                                                                                                                                                             | 119 |

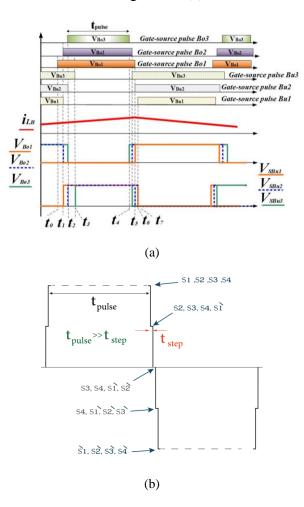

| Figure 5.3: | Steady-state waveforms. (a) the gate pulse sequence. (b) the switching sequence of the neutral point clamped leg                                                                                                                                                                                                                                                                          | 120 |

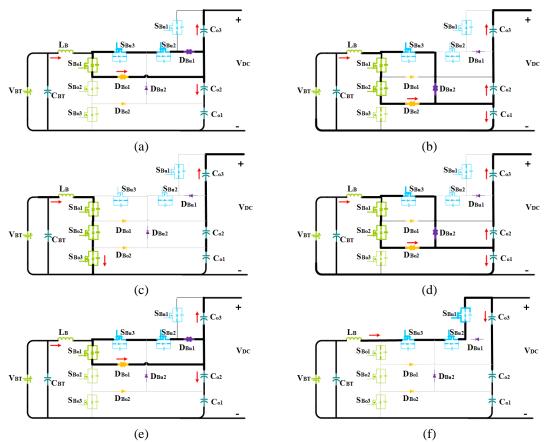

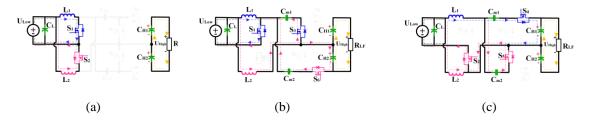

| Figure 5.4: | Boost Operation Modes. (a) mode1; (b) mode2; (c) mode 3 and (d) mode4; (e) mode 5; (f) mode 6.                                                                                                                                                                                                                                                                                            | 121 |

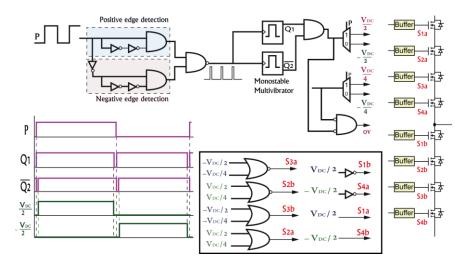

| Figure 5.5: | The proposed control scheme of the 5-level NPC leg                                                                                                                                                                                                                                                                                                                                        | 123 |

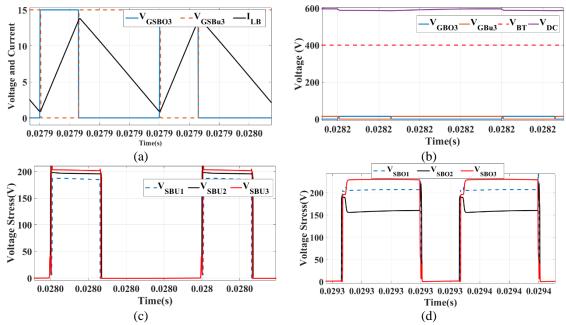

| Figure 5.6: | Simulation. (a) gate pulse of boost switch $S_{BO3}$ , buck switch $S_{Bu3}$ , and current of filter inductor $I_{LB}$ ; (b) gate pulse of boost switch $S_{BO3}$ , buck switch $S_{Bu3}$ , battery voltage and dc-link voltage; (c) voltage stress of buck switches $S_{Bu1}$ , $S_{Bu2}$ , and $S_{Bu3}$ ; (d) voltage stress of boost switches $S_{Bo1}$ , $S_{Bo2}$ , and $S_{Bo3}$ . | 126 |

| Figure 6.1: | The schematic of the proposed converter                                                                                                                                                                                                                                                                                                                                                   | 128 |

| Figure 6.2: | Equivalent circuit of the proposed converter in forward mode. (a)<br>Interval 1 and 3. (b) Intervals 2. (c) Interval 4                                                                                                                                                                                                                                                                    | 131 |

| Figure 6.3: | Key waveforms of the proposed converter. (a) forward mode. (b) backward mode.                                                                                                                                                                                                                                                                                                             | 132 |

| Figure 6.4: | Equivalent circuit of the proposed converter in backward mode. (a)<br>Interval 1 and 3. (b) Intervals 2. (c) Interval 4                                                                                                                                                                                                                                                                   | 133 |

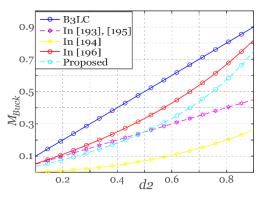

| Figure 6.5: | Comparison of the voltage conversion ratio. (a) Forward mode. (b)<br>Backward mode                                                                                                                                                                                                                                                                                                        | 142 |

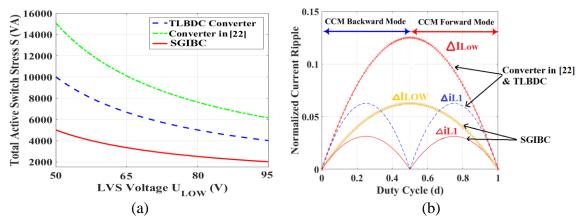

| Figure 6.6: | Comparison of the total switch stress S and normalized current ripple.<br>(a) Total switch stress S. (b) Current ripple                                                                                                                                                                                                                                                                   | 144 |

| Figure 6.7: | Voltage gain of the compared converters in the step-down mode versus the duty cycle.                                                                                                                                                                                                                                                                                                      | 144 |

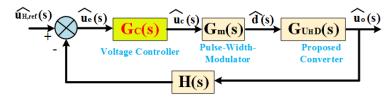

| Figure 6.8: | Voltage control strategy.                                                                                                                                                                                                                                                                                                                                                                 | 147 |

| Figure 6.9: | A photograph of laboratory prototype                                                                                                                                                                                                                                                                                                                                                      | 148 |

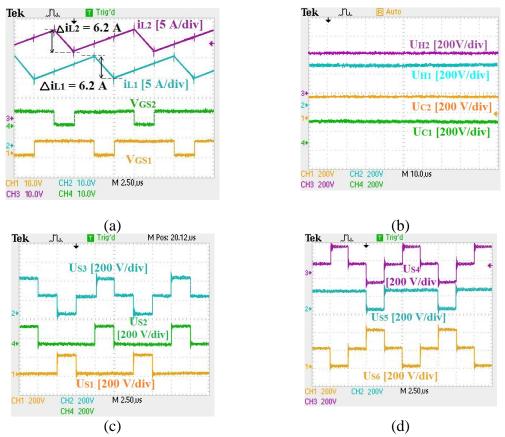

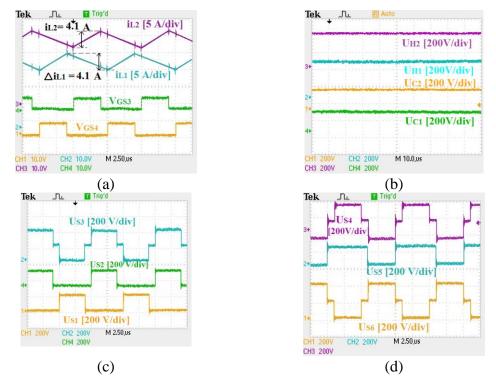

| Figure 6.10 | ): Experimental results for forward mode. (a) Gate-source voltage of switches $S_1$ and $S_2$ and Inductor currents. (b) Capacitor voltages. (c)                                                                                                                                                                                                                                          |     |

| -                                                                          | itches S <sub>1</sub> , S <sub>2</sub> , and S <sub>3</sub> . (d) Voltage stresses on                                                                                                                                                                           | 149 |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| switches $S_1$ and $S_2$ and Voltage stresses on switches                  | for backward mode. (a) Gate-source voltage of<br>Inductor currents. (b) Capacitor voltages. (c)<br>itches $S_1$ , $S_2$ , and $S_3$ . (d) Voltage stresses on                                                                                                   | 150 |

|                                                                            | distributions for the experiment. (a) forward ode.                                                                                                                                                                                                              | 152 |

| comparison of efficient                                                    | Experimental and calculated results. (b)<br>cy in forward mode. (c) comparison of efficiency                                                                                                                                                                    | 152 |

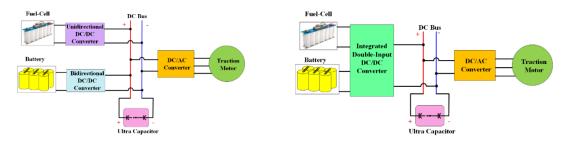

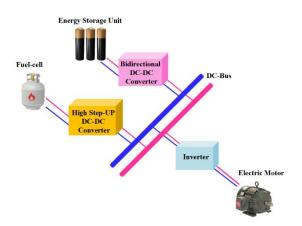

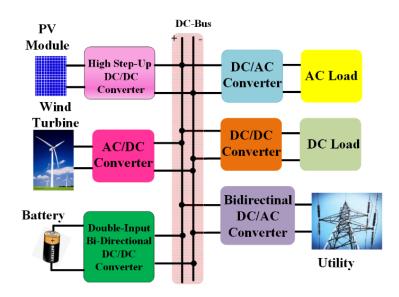

| (a) using separate conv                                                    | l-cell-powered EV with hybrid energy storage.<br>rerters. (b) Proposed integrated double-input                                                                                                                                                                  | 155 |

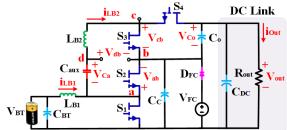

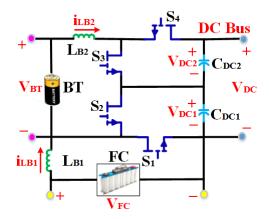

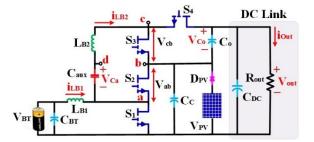

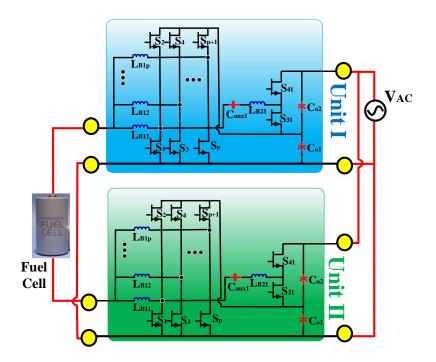

| Figure 7.2: Proposed three-level do                                        | ouble-input DC/DC converter.                                                                                                                                                                                                                                    | 156 |

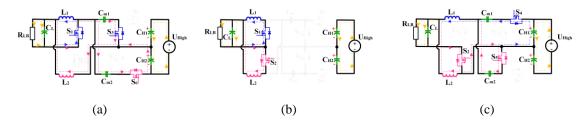

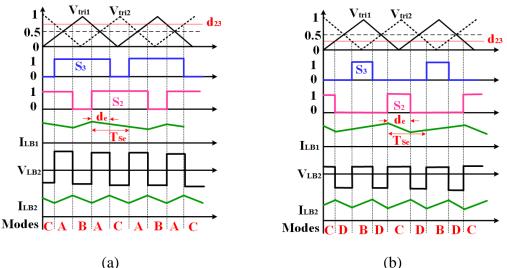

|                                                                            | es for forward operation. (a) $d_{23} > 0.5$ (b) $d_{23} <$                                                                                                                                                                                                     | 157 |

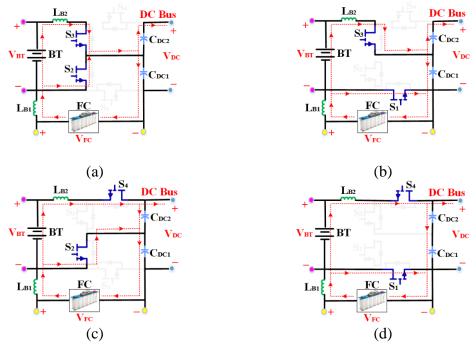

|                                                                            | scenario I. (a) State A. (b) State B. (c) State C.                                                                                                                                                                                                              | 158 |

|                                                                            | scenario II. (a) State A. (b) State B. (c) State C.                                                                                                                                                                                                             | 160 |

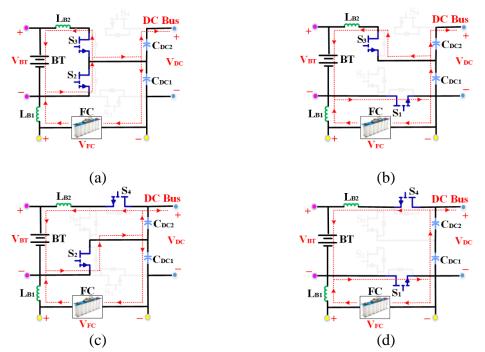

|                                                                            | g scenario III. (a) State A. (b) State B. (c) State                                                                                                                                                                                                             | 162 |

|                                                                            | scenario IV. (a) State A. (b) State B. (c) State C.                                                                                                                                                                                                             | 163 |

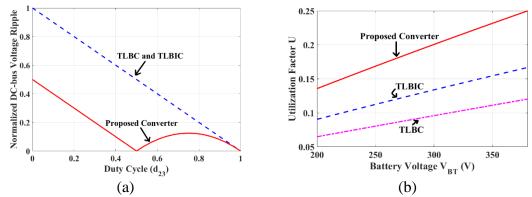

| converters ( $P_{UC} = 50$ ky                                              | Itage ripple and utilization factor for different<br>w, $f_s = 100$ kHz, and $V_{UC} = 760$ V). (a)<br>Itage ripple; (b) utilization factor                                                                                                                     | 165 |

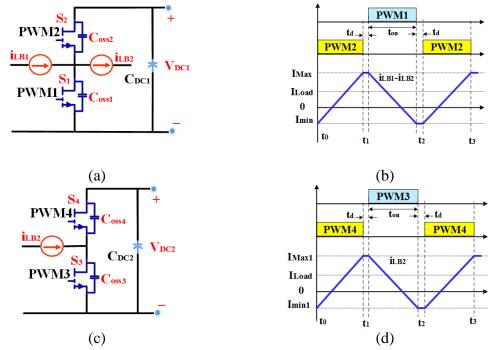

| module including swite $S_1$ and $S_2$ and inductor module including swite | oft-switching operation. (a) Equivalent circuit of<br>ches $S_1$ and $S_2$ . (b) Gate-source pulse of switches<br>currents $i_{LB1}$ and $i_{LB2}$ . (c) Equivalent circuit of<br>ches $S_3$ and $S_4$ . (d) Gate-source pulse of switches<br>current $i_{LB2}$ | 168 |

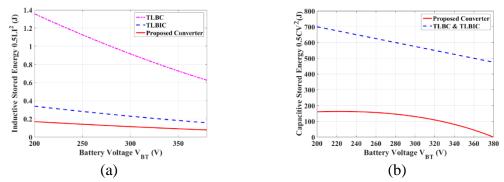

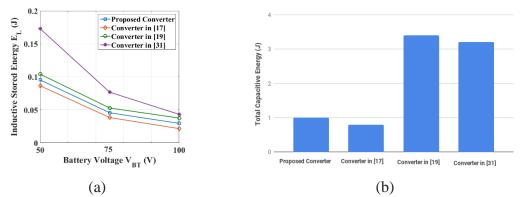

| Figure 7.10: Comparison of stored energy in the inductors and capacitors for<br>different converters ( $P_{UC} = 50$ kw, $f_s = 100$ kHz, and $V_{DC} = 760$ V). (a)<br>Inductive stored energy; (b) Capacitive stored energy                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

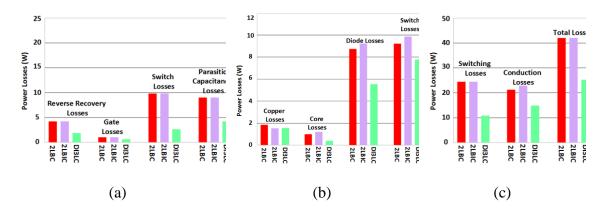

| Figure 7.11: Comparison of loss breakdown for the proposed converter versus 2LBC and 2LBIC. (a) Switching losses. (b) Conduction losses. (c) Total loss                                                                                                                                                                                                                                                                                                                                                                                                                   |

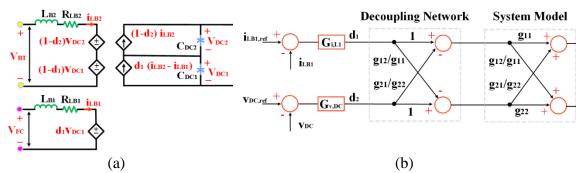

| Figure 7.12: Large signal model and decoupling network accompanied with closed-<br>loop compensators. (a) Large-signal average model of the proposed<br>converter; (b) Decoupling network and closed-loop compensators                                                                                                                                                                                                                                                                                                                                                    |

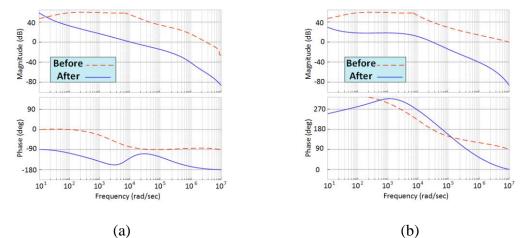

| Figure 7.13: Bode plots. (a) $i_{L1}(s) / d_1(s)$ . (b) $v_{DC}(s) / d_2(s)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

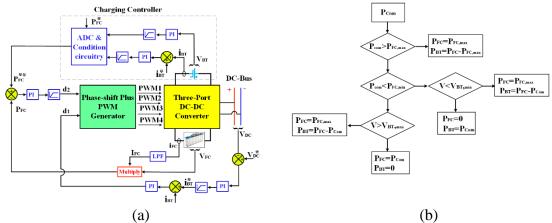

| Figure 7.14: The power management scheme and its flowchart. (a) The power management scheme. (b) flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

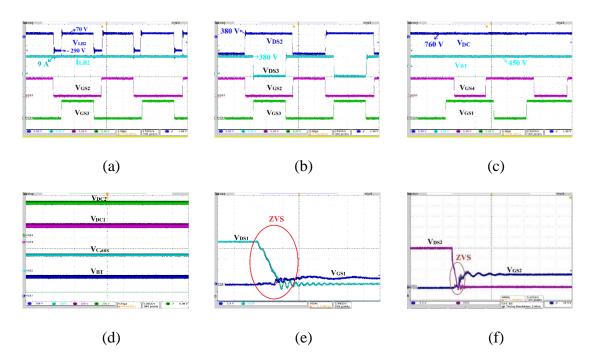

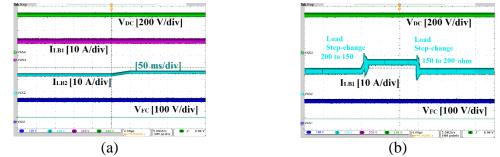

| Figure 7.15: Experimental results for scenario I ( $V_{BT} = 450$ V, $P_{DC} = 4$ kW and $V_{DC} = 760$ V). (a) Gate-source pulses of switches $S_2$ and $S_3$ , current and the voltage across inductor $L_{B2}$ . (b) Gate-source and drain-source voltage of switches $S_2$ and $S_3$ . (c) Gate-source voltage of switches $S_1$ and $S_4$ , DC-bus voltage, and battery voltage. (d) Voltage of capacitors $C_{DC1}$ , $C_{DC2}$ and $C_{aux}$ . (e) Gate-source and drain-source voltage of switch $S_1$ . (f) Gate-source and drain-source voltage of switch $S_2$ |

| Figure 7.16: Experimental results for scenario I ( $V_{BT} = 300 \text{ V}$ , $P_{UC} = 4 \text{ kW}$ and $V_{UC} = 760 \text{ V}$ ). (a) Gate-source pulse of switches $S_2$ and $S_3$ , current and the voltage across inductor $L_{B2}$ . (b) Gate-source and drain-source voltage of switches $S_2$ and $S_3$ . (c) Drain-source voltage of switches $S_1$ and $S_4$ , DC-bus voltage, and battery voltage                                                                                                                                                            |

| Figure 7.17: Experimental results for scenario IV ( $V_{BT} = 400$ V, $P_{UC} = 4$ kW and $V_{UC} = 760$ V). (a) Gate-source pulse of switches S <sub>2</sub> and S <sub>3</sub> , current and the voltage across inductor L <sub>B2</sub> . (b) Gate-source and drain-source voltage of switches S <sub>2</sub> and S <sub>3</sub> . (c) Gate-source voltage of switches S <sub>1</sub> and S <sub>4</sub> , DC-bus voltage, and battery voltage                                                                                                                         |

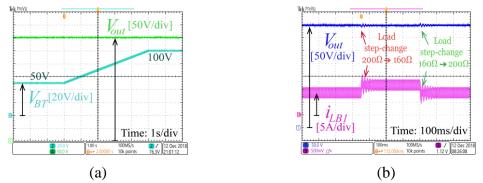

| <ul> <li>Figure 7.18: The experimental results of dynamic performance. (a) Transitioning from scenario I to scenario II. (b) Output voltage and inductor current when load step-change between 150 Ω and 200 Ω.</li> </ul>                                                                                                                                                                                                                                                                                                                                                |

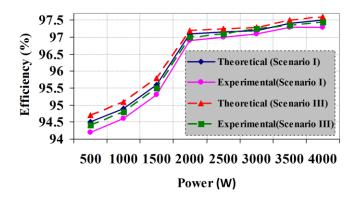

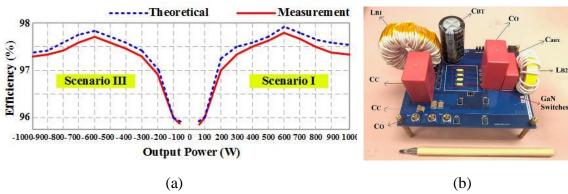

| Figure 7.19: The theoretical and experimental efficiency for different power P <sub>DC</sub> 183                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

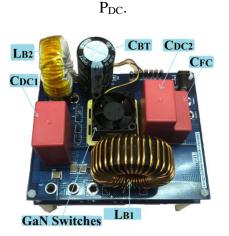

| Figure 7.20: Laboratory prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

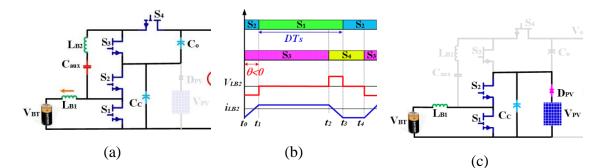

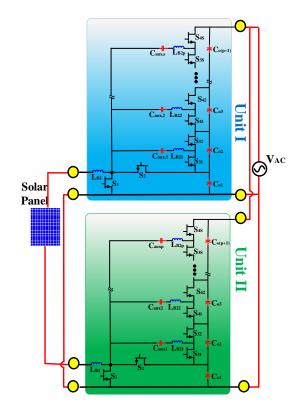

| Figure 8.1: Proposed STPTLC for hybrid BT/PV applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

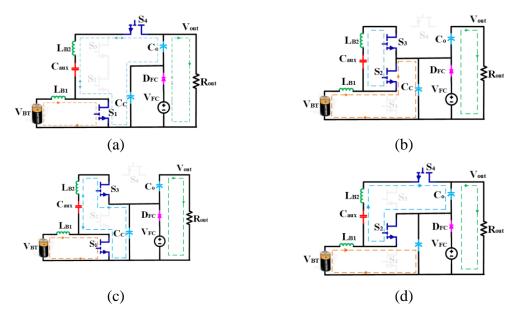

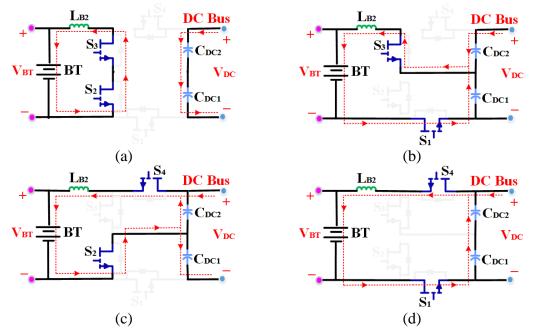

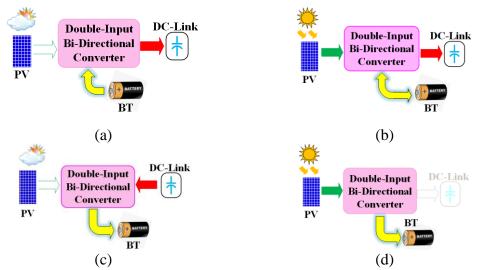

| Figure 8.2: | Different scenarios according to different condition of PV and load; (a)<br>Scenario I.(b) Scenario II.(c) Scenario III.(b) Scenario IV                                                                                                                        | 188 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

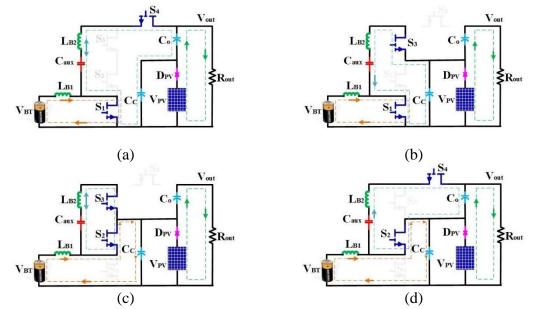

| Figure 8.3: | Operation modes and key waveforms for scenario I. (a) Mode I. (b)<br>Mode II. (c) Mode III. (d) Mode IV.                                                                                                                                                       | 189 |

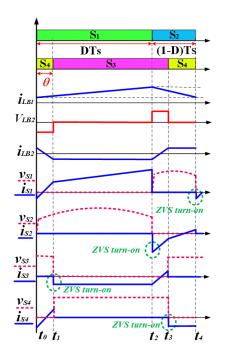

| Figure 8.4: | Key waveforms                                                                                                                                                                                                                                                  | 191 |

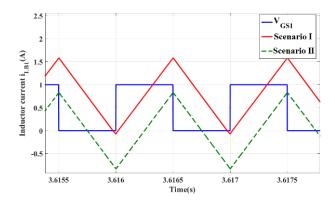

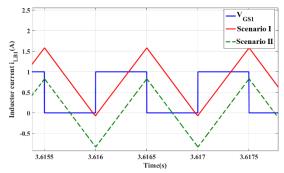

| Figure 8.5: | The inductor current for different scenarios I ( $P_{PV} < P_{out}$ ) and II ( $P_{PV} > P_{out}$ ).                                                                                                                                                           | 192 |

| Figure 8.6: | Equivalent circuit and key waveforms of converter in scenario III and IV. (a) Equivalent circuit in scenario III. (b) Key waveforms in scenario III. (c) Equivalent circuit in scenario IV                                                                     | 193 |

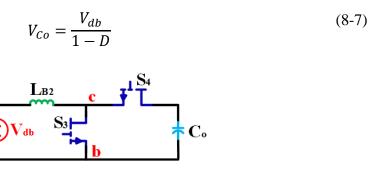

| Figure 8.7: | Equivalent circuit of HVP of proposed STPTLC                                                                                                                                                                                                                   | 194 |

| Figure 8.8: | Operating cases for different values of phase shift ratio $\theta$ versus duty-<br>cycle D.                                                                                                                                                                    | 195 |

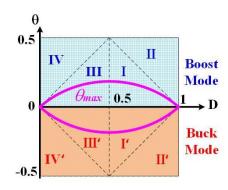

| Figure 8.9: | Different operation modes according to different values of duty-cycle and phase shift ratio $\theta$ . (a) Case 1. (b) Case 2. (c) Case 3. (d) Case 4                                                                                                          | 198 |

| Figure 8.10 | ): Maximum transferred power and normalized transferred power; (a)<br>Maximum transferred power as a function of switching frequency $f_s$<br>and inductance $L_{B2}$ . (b) Normalized transferred power versus different<br>phase-shift ratio and duty cycle. | 199 |

| Figure 8.11 | : Normalized RMS current versus different phase-shift ratio and duty cycle.                                                                                                                                                                                    | 202 |

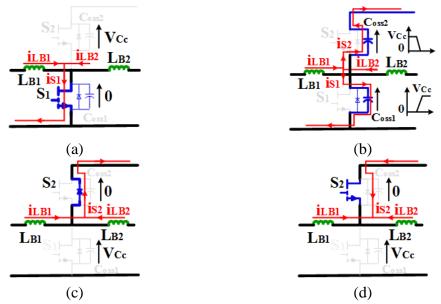

| Figure 8.12 | 2: ZVS turn-on of switch $S_2$ . (a) just before turn-on instant. (b) rapid<br>charging and discharging of output capacitor $C_{oss1}$ and $C_{oss2}$ . (d)<br>antiparallel diode freewheeling. (d) current polarity alternation                               | 203 |

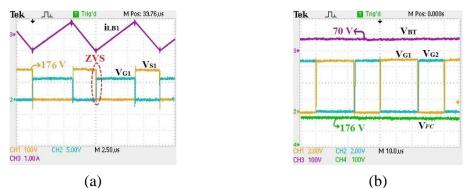

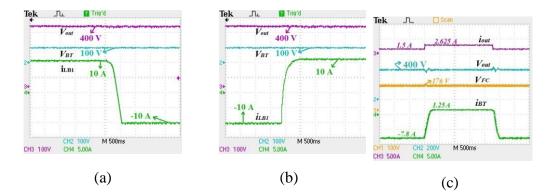

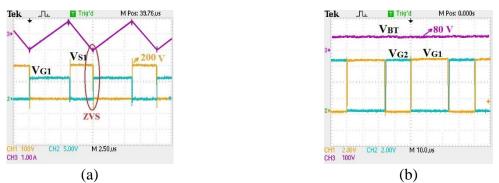

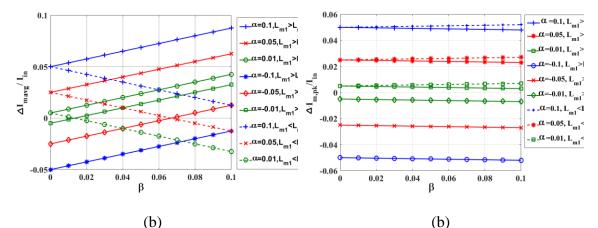

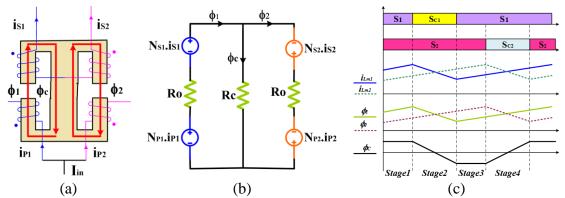

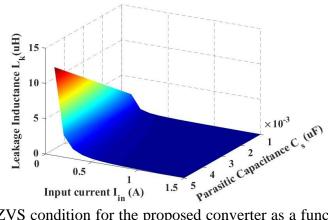

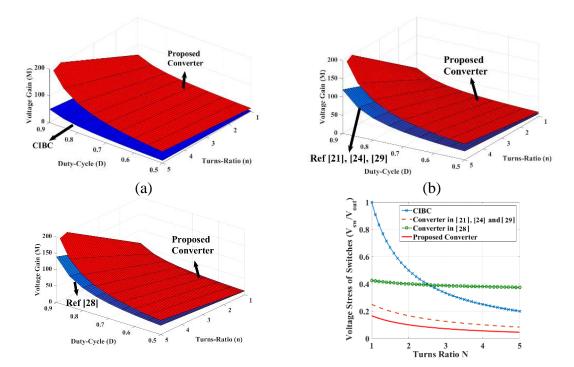

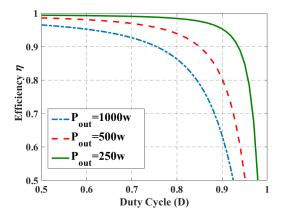

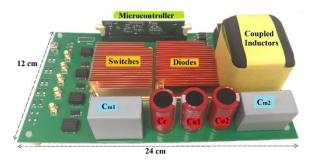

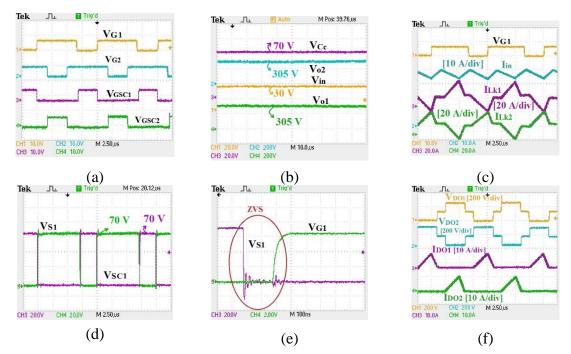

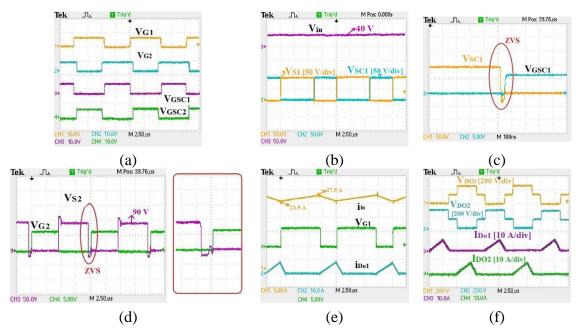

| Figure 8.13 | S: ZVS current of switches $S_1$ and $S_2$ . (a) Normalized ZVS current of<br>switch $S_2$ versus different phase-shift ratio and duty cycle. (b) ZVS<br>current of switch $S_1$ versus different battery voltage and output power                             | 205 |