© Universiti Tun Hussein Onn Malaysia Publisher's Office

IJIE

The International Journal of Integrated Engineering

Journal homepage: http://penerbit.uthm.edu.my/ojs/index.php/ijie ISSN: 2229-838X e-ISSN: 2600-7916

# **Optional CMOS based Monolithic Light Sensor for Detection of Light Intensity**

# Woon Yun Kean<sup>1</sup>, Warsuzarina Mat Jubadi<sup>2\*</sup>, Nabihah@Nornabihah Ahmad<sup>2</sup>

<sup>1</sup>eASIC Engineering team,

Intel Microelectronics (M) Sdn. Bhd. Bayan Lepas, 11900 Pulau Pinang, MALAYSIA

<sup>2</sup>Dept.of Electronics, Faculty of Electrical & Electronic Engineering, Universiti Tun Hussein Onn Malaysia, Batu Pahat 86400 Johor, MALAYSIA

\*Corresponding Author

DOI: https://doi.org/10.30880/ijie.2021.13.02.009 Received 9 June 2020; Accepted 1 December 2020; Available online 28 February 2021

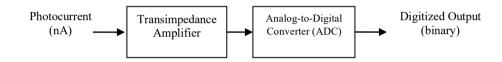

**Abstract:** Conventional light intensity sensing devices such as a light meter are big in size and incapable of outputting a digitized signal to a microprocessor for further control and actuation. Sensor transducers based on CMOS has therefore increased in popularity. Using CMOS technology, manufacturing costs and the power consumption can be reduced with smaller form factor. This paper presents a proposed design of light sensor for the detection of light intensity. The project utilizes Silterra's 130 nm CMOS architecture to create a low power and low space monolithic light sensor chip that is able to detect the intensity of light to assist in achieving the recommended levels of light intensity in domestic areas. The light intensity was simulated with a photocurrent and the photodiode operates optimally at a wavelength of 555 nm, the spectral sensitivity of the human eye and has good linearity. The light intensity detected is shown in illuminance (lux) and this project is capable to detect illuminance in the range of 0 to 200 lux with a resolution of 20 lux. The monolithic chip of the light intensity sensor comprises of the transimpedance amplifier which acts as a current to voltage converter and an ADC to convert the analog voltage into a digital reading. Hence, the output of the light intensity sensor is in binary representation. The total power consumption of the monolithic light intensity sensor is 1.88mW and the total size of the design is 0.01202 mm<sup>2</sup>.

Keywords: ADC, CMOS, light sensor, light intensity, monolithic

# 1. Introduction

Today, sensor and monitoring systems [1], [2] have seen rapid growth in demand as most current technology incorporates sensors into many different fields such as the automotive field [3], medical field [4], robotics [5], measuring instruments and much more. According to a report published in 'Global Markets and Technologies for Sensors' on July 2014, the global market of sensors are going to keep increasing and is expected to raise exponentially in the next decade [6]. With the reduction of size of most electronic devices going into the future, the demand for small sized, low cost and low power sensors has elevated as well and thus has become an attractive field of research, which is why the proposed design is based on the CMOS technology. CMOS circuits were invented in early 60s. Some twenty-five years later, CMOS technology has become the predominant technology in digital integrated circuits. This is essentially because area occupation, operating speed, energy efficiency and manufacturing costs have benefited and continue to benefit from the geometric downsizing that comes with every new generation of semiconductor manufacturing processes [7].

The intensity of light is an important issue in several fields and scenarios ranging from horticulture, light pollution study, robot navigation, automotive, medical appliances, and more. It is typically determined by using a light meter. The light meter, also known as the lux meter is used to measure the light intensity. As in normal meter, the lux value was obviously a displayed value, and hardly used for embedded application as well as for lighting monitoring considering its expensive price. This limits the lighting monitoring in certain critical field [8]. Conventional light intensity sensing de-vices such as the light meter are also big in size and incapable of outputting a digitized signal to a microprocessor for further control and actuation [8]. Sensor transducers based on CMOS has therefore increased in popularity [9], [10], [11]. CMOS technology was chosen because compared to conventional sensors, manufacturing costs and the power consumption can be reduced and manufactured in a smaller form factor. This project focuses on the design and simulation of a light sensor based on CMOS for the detection of light intensity in the Cadence EDA Tools. An analog front-end circuit consisting of the trans-impedance amplifier was combined with an Analog-to-Digital Converter (ADC) to produce a digital output signal so that it can be easily sent over a wide range of transmission media. A monolithic sensor chip is then developed which can detect the light intensity and response to a controller or computer. In a domestic environment, excessive light will cause a higher power consumption and expensive electrical bills; too little light will also cause problems such as difficulty of activity in that particular area requiring vision. Therefore, recommended light intensity levels of various areas are to be followed. Hence, this project is proposed so that a small size, a low cost, and low power sensor chip (less than 5mW) that helps in reaching the recommended light intensity levels in a domestic area can be realized.

#### 2. Design of Light Intensity Sensor

Today, sensor and monitoring Cadence EDA Tools is used for the design and simulation of the CMOS based light intensity sensor. The size of the CMOS transistors used to design the layout of the light intensity sensor is based on the 130 nm CMOS technology. The design process was divided into three phases, which are the specification identification, design, system, timing and logic Verification, and physical design phase. The block diagram of the light meter design is shown in Fig.1. The schematic of the transimpedance amplifier (TIA) and ADC is designed in the schematic editor of Cadence Virtuoso and the functionality of the light intensity sensor was tested by simulating the circuit using *spectre* analysis.

Fig. 1 - Block diagram of the CMOS based monolithic

The CMOS-based monolithic light intensity sensor is designed to detect the illuminance level of between 0 to 200 lux with a resolution of 20 lux. It is also designed to have low power consumption and low space occupancy. This is achieved by designing a custom 8-bit Flash ADC with a low number of comparators. The Flash ADC has high power consumption when more voltage comparators are being used; for example, a 3-bit Flash ADC would requires 23 comparators and the amount of comparators needed doubles every iteration. This would mean that an 8-bit ADC would require 2<sup>8</sup> (equivalent to 256) comparators which would have very high power consumption and space occupancy. Therefore, an ADC with a lower resolution is designed and this allows dramatically less voltage comparators to be used and a resolution of 20 is sufficient for domestic light level measurement to assist in reaching the recommended light levels.

## 2.1 Selection of Photodetector Circuit

Photodetector is used as a transducer in the light-to-voltage conversion in this research. There are various types of a photodetectors [12], [13], [14] which the most used types of light sensors are the photocell, photodiodes, photomultiplier, photoresistor, and photo-transistor as tabulated in Table 1. Photocells generally have a lower sensitivity than photodiodes and photo transistors. This is because photocells like LDR lack a PN-junction. Even when the light intensity is kept constant, the resistance may still vary significantly due to temperature changes, which makes them dependent on both light and temperature [11], [13]. This property makes them inaccurate and unsuitable for precise light intensity measurements. Other source of photo such as photocell is not suitable for our proposed design as it has very high latency (~30ms) and is inaccurate. Furthermore, it is affected by another external input which is temperature that could affect its accuracy. A photomultiplier is unsuitable in a CMOS based design, as it is fragile, hefty, and expensive. The phototransistor is slow, which makes it unsuitable for light intensity measuring purposes. In conclusion, the photodiode is the most suitable light to voltage converter that suits the needs of the proposed design.

| Types of<br>Photodetector | Latency<br>(Rise/fall) time | Power<br>Dissipation |  |  |

|---------------------------|-----------------------------|----------------------|--|--|

| Photocell                 | High                        | Low                  |  |  |

| [14]                      | 30ms                        | (90mW)               |  |  |

| Photodiode                | Low                         | Low                  |  |  |

| [15]                      | (3ns)                       | (100mW)              |  |  |

| Photomultiplier           | Very Low                    | Very High            |  |  |

| [16]                      | 1.6ns                       | (760mw)              |  |  |

| Phototransistor           | Medium                      | Low                  |  |  |

| [17]                      | (15µs)                      | (100mW)              |  |  |

Table 1 - Comparison of photodetectors

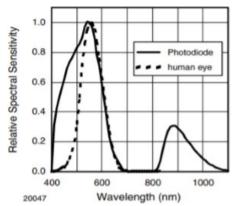

The photodiode used in the design was simulated using a current source. The photodiode chosen for this project is Vishay's TEMD5510FX01 [13]. It has an excellent linearity and operates in the wavelength between 430 nm to 610 nm; the closest to the human eye which can see light with wavelengths from 380 nm to 780nm, as shown in Fig.2. Furthermore, this photodiode operates optimally at the wavelength of 555 nm with the responsivity of  $1W/m^2$  (equivalent to 683 lux). An optimal photodiode at 555 nm allows the equivalent photocurrent to be simulated in Cadence.

Fig. 2 - Relative spectral sensitivity vs wavelength of the TEMD5510FX01 photodiode and the human eye [13]

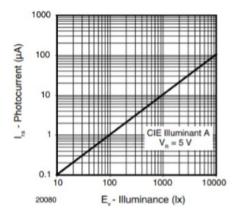

Fig. 3 shows that photocurrent and illuminance have a linear relationship where  $1\mu A$  of photocurrent equals to 100 lux of illuminance. For the design of the light intensity sensor, the range of the illuminance to be detected is from 0 to 200 lux which corresponds to a photocurrent input of 0 to 2  $\mu A$ . The light intensity sensor is designed to detect illuminance in the range of 0 to 200 lux and can be used to measure the light intensity of an area to ensure that it meets the recommended light levels.

Fig. 3 - Relationship between photocurrent and illuminance of TEMD5510FX01 [13]

#### 2.2 Transimpedance Amplifier Design

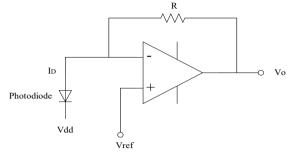

The transimpedance amplifier (TIA) which is use as the transducer in the light intensity sensor is commonly operate based on the current-to-voltage converter. It is an op-amp circuit which accepts an input current and generates an output voltage proportional to the input current. The gain of the current to voltage converter is denoted by R, which is also known as the sensitivity of the converter. The gain of the current to voltage converter can be varied by changing the value of R. Fig.4 shows the diagram of a transimpedance amplifier implemented in the circuit design.

Fig. 4 - Diagram of a transimpedance amplifier

#### 2.3 Types of Analog-to-Digital Converter

To convert the amplified analog input into a readable digital form, an analog to digital converter is utilized in the proposed project. An analog to digital converter is a device that converts analog signals obtained from an outside input, in this case light intensity into a digital format that is able to be read or further processed. It converts the continuous signal into a multi-level discrete signal without changing its important information. There are a wide variety of ADCs such as flash ADC, Sigma-Delta ADC, and Successive-Approximation ADC with different resolution, bandwidths, architectures and power requirements [18],[19]. Flash ADC, also known as a parallel ADCs are the fastest way to convert an analog signal to a digital signal. It is the simplest type of data converter and hence requires little time, which makes it suitable for large band. It utilizes  $2^N$  comparators which causes them to consume a lot of power and high cost [18], where *N* is the number of bit.

The successive-approximation ADC uses a single comparator over many cycles for conversion as opposed to the flash ADC which uses multiple comparators for a single cycle conversion. Successive-approximation-register (SAR) ADCs [20] are commonly used for medium to high resolution applications, ranging from 8 to 16 bits while having a low power consumption and small form factor [19]. The SAR ADC is very power efficient and power consumption can be further reduced at the cost of resolution. The sigma-delta ADC uses a very different approach compared to other types of ADCs. Sigma-delta ADC has high resolution and low cost [18]; which makes them attractive for applications where accuracy is important. The sigma-delta ADC consists of an integrator, comparator and a single bit DAC. The sigma-delta ADC is notable for its high resolution, low power consumption and high stability. However, it is very complex and due to oversampling, its speed is not as fast compared other types of ADC. The flash ADC is used in the light sensor design to digitize the light conversion reading due to its design simplicity and provide fastest conversion amongst other ADC circuit. The circuit development are presented in the following topic.

#### 3. Circuit Simulation Results with Cadence EDA

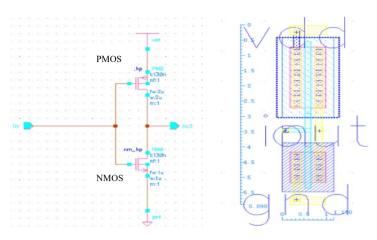

Using Cadence, the schematic of the components (inverter) are first designed in the form of transistor level diagram in a cell view, shown in Fig. 5(a). The transistor level diagram is then converted into symbols so that it is simpler to identify each components when everything is connected. The layout design of the circuit is the 2D top down view and shows in Fig. 5(b). There are rules to be followed for layout design. The layout design rules are used to translate a circuit design into actual geometry in silicon. All of the design will follow the layout design rules to ensure that there is no short circuit or errors. The layout design also allows us to determine the size of each individual design.

Fig. 5 - (a) Schematic diagram; (b) Layout of the inverter (1.170 µm x 5.890 µm)

#### 3. 1 Transimpedance Amplifier Design Simulation

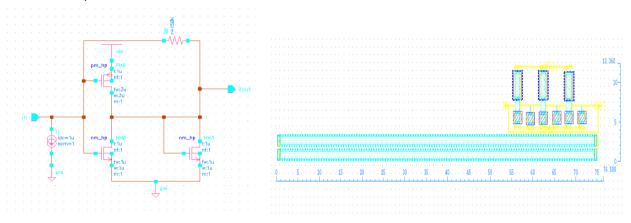

In the light intensity sensor, photodiode is used as the transducer. Since photodiodes generate a very low current and the next stages of processing mostly revolves around voltage, hence the current must be first converted into voltage. The TIA is able to convert photocurrent into voltage and amplify it to a higher value with a large transimpedance gain. The designed transimpedance amplifier consists of three stages of inverters cascaded with a feedback resistor from the output to the input. Fig.6(a) shows a single stage transimpedance amplifier based on an inverter. The W/L ratio of the PMOS and NMOS used in the design are 3:1, with the PMOS having  $3\mu/1\mu$  and NMOS having  $1\mu/1\mu$ , respectively. The single stage inverter based transimpedance amplifier mainly consists of an inverter, and an extra NMOS connected to the output to increase the bandwidth and decrease miller effect. A feedback resistor with a resistance of 150 k $\Omega$  is also connected from the output to the input. The current source circuit simulates the photocurrent from photodiode. Fig.6(b) shows the layout of the three-stage inverter-based transimpedance amplifier with area size of 76.500 x 12.360  $\mu$ m<sup>2</sup>.

Fig. 6 - (a) Schematic for single-stage; (b) Layout of three-stage inverter-based transimpedance amplifier

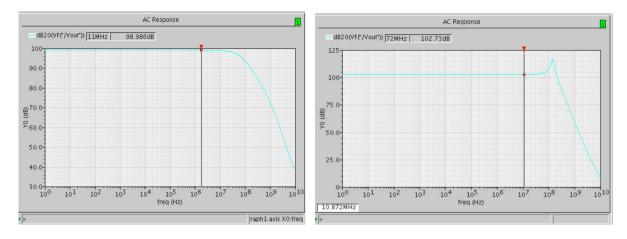

This single stage transimpedance amplifier operates on the supply voltage of 1.2 V. Each transistor in the single stage TIA is in the saturation region to perform amplifier function. The ac response of the single stage inverter based TIA is shown in Fig.7. The maximum gain achieved by the single stage inverter based transimpedance amplifier was 98.98 dB. The bandwidth of the single-stage inverter based TIA, where the gain remains constant at 98.98 dB is 11 MHz. This is acceptional bandwidth to be used for the sensor design. The three-stage inverter-based TIA is constructed by cascading three single stage TIA in series. Similar to the single-stage inverter-based TIA, the W/L ratio of each PMOS and NMOS are  $3\mu/1\mu$  and  $1\mu/1\mu$  respectively. All transistors are operating in the saturation region where  $V_{DS} > V_{GS}-V_T$  for the NMOS and  $V_{SD}> V_{SG}-|V_T|$  for the PMOS. This is to ensure that all the transistors are functioning well as an amplifier in the design. The output of the single TIA is connected to the input of the consecutive single stage TIA and forth. Based on the AC response curve in Fig. 7(b), it is observed to have a higher maximum gain at 102.73 dB and operates at a larger bandwidth compared to the single-stage inverter-based TIA.

The three-stage inverter-based TIA has a greater bandwidth of 72 MHz compared to the single-stage TIA. Despite of the improved gain and bandwidth achieved with multistage connection, the design need to compromise with overshoot at a higher frequency. Further increment in the gain (by adding stage level) might results in severe distortion which affected the time response.

Fig. 7 - (a) AC Response of single-stage inverter-based TIA; (b) AC Response of three-stage inverter-based transimpedance amplifier

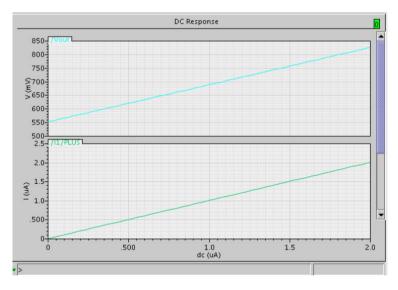

# 3.2. Current to Voltage Conversion of the Transimpedance Amplifier

The three-stage inverter-based TIA is designed to accept a photocurrent input of 0 to 2  $\mu$ A, which means it is able to sense light with intensity of 0 to 200 lux. By running a dc analysis in the analog design environment of *Spectre*, the output voltage of the corresponding photocurrent can be obtained. The functionality of the three-stage inverter-based TIA is verified based on the DC response curve obtained through DC analysis. When a DC sweep is performed from 0 to 2  $\mu$ A, a voltage of 551.44 mV to 822.14 mV are obtained as shown in Fig.8.

Fig. 8 - DC response of three-stage inverter-based TIA

These results were tabulated in Table 2 which each of the photocurrents values are corresponds to the light sensed (illuminance). The output voltage of the TIA will then be fed into the ADC for conversion to a digital signal so that the illuminance can be measured.

| Illuminance<br>(lux) | Photocurrent (µA) | Output voltage of<br>TIA (mV)<br>551.44 |  |  |

|----------------------|-------------------|-----------------------------------------|--|--|

| 0                    | 0                 |                                         |  |  |

| 20                   | 0.2               | 578.81                                  |  |  |

| 40                   | 0.4               | 606.30                                  |  |  |

| 60                   | 0.6               | 633.47                                  |  |  |

| 80                   | 0.8               | 660.60                                  |  |  |

| 100                  | 1.0               | 688.20                                  |  |  |

| 120                  | 1.2               | 715.19                                  |  |  |

| 140                  | 1.4               | 742.28                                  |  |  |

| 160                  | 1.6               | 769.91                                  |  |  |

| 180                  | 1.8               | 797.91                                  |  |  |

| 200                  | 2.0               | 825.18                                  |  |  |

Table 2 - Illuminance vs photocurrent with the corresponding output

# 3.3. Analog-to-Digital Circuit

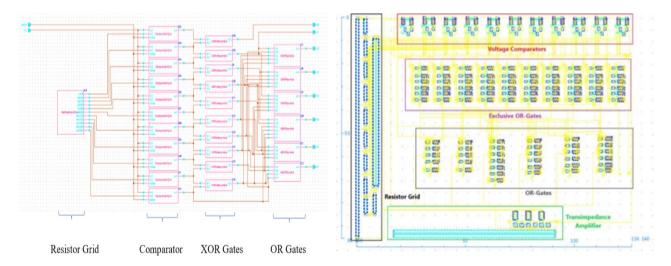

The flash ADC in the circuit is formed using a series of comparators where a reference voltage from a resistor grid is set for each comparators to be compared with the analog input voltage. The full ADC is created from the comparator, which accepts input from the output of the TIA and the reference voltage to determine the illuminance level by giving a HIGH output on the corresponding comparator. The schematic diagram of full ADC circuit is shown in Fig.9(a). The ADC designed is a custom 8-bit flash ADC with a binary resolution of 20 and is powered by a 1.2 V source voltage. The output of the comparators are then fed into the XOR gates to find the actual level of the illuminance by determining whether the illuminance is lower or higher than the detected illuminance. Finally, the OR gates are used to combine the outputs of the XOR gates into a binary output that is readable and measurable. The schematic design of ADC then used to obtain the layout. Fig. 9 (b) shows the full ADC layout with the dimension area of  $127.350 \times 94.580 \ \mu m^2$ .

Fig. 9 - (a) Schematic diagram of full ADC; (b) Layout of full ADC (127.350 µm x 94.580 µm)

The resistor grid block in Fig. 9 (a) provides the reference voltage which is compared with the analog input voltage. Each individual resistors in the grid are calculated based on the corresponding input voltages of the illuminance. The analog input voltage from the TIA has to be higher than the reference voltage. An interpolation of the analog input voltage of the TIA was done as an estimation of the reference voltage to be calculated. The calculation of the reference voltage is done using Equ. (1), similar to a voltage divider equation:

$$V_{ref} = \frac{R_a}{(R_a + R_b)} \times V_{in} \tag{1}$$

Where  $V_{ref}$  is the reference voltage,  $R_a$  is the total resistor value after the reference voltage,  $R_b$  is the total resistor value before the reference voltage and  $V_{in}$  is the voltage source/input of the resistor grid which is 1.2 V. The result

obtained from resistor grid block were then fed to the voltage comparator circuit. This block compares the analog input voltage with the reference voltage from the resistor grid.

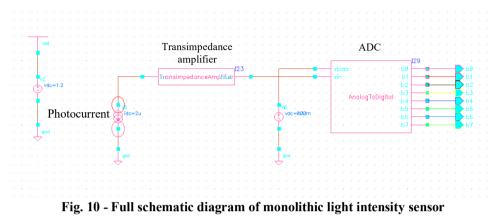

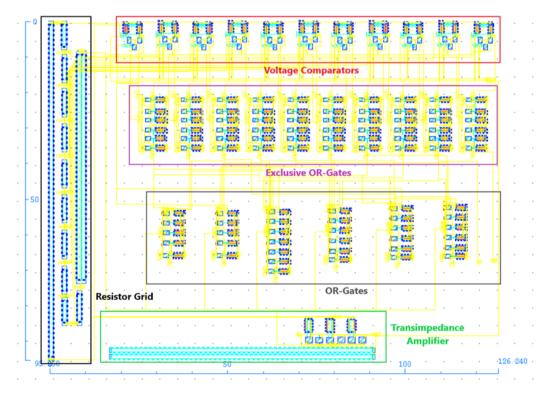

#### 3.4. Monolithic Light Intensity Sensor Circuit

The analog front end block of three-stage inverter-based transimpedance amplifier and ADC were integrated to function as full monolithic light intensity sensor. The light intensity sensor successfully shows the illuminance reading in a binary value. Fig. 10 and Fig.11 shows the schematic and layout diagram of the complete light intensity sensor. The total area for the monolithic light intensity sensor layout is  $126.240 \times 95.250 \mu m^2$ .

The total power consumption of the CMOS monolithic light intensity sensor is calculated through DC Analysis using spectre and was estimated about 1.88 mW. The static power consumption of the circuit can be calculated using equ. (2):

$$P_s = V_{CC} \times I_{CC} \tag{2}$$

Where  $V_{CC}$  is the supply voltage and  $I_{CC}$  is the current flow into the device.

Fig. 11 - Full layout of monolithic light intensity sensor (126.240 µm x 95.250 µm)

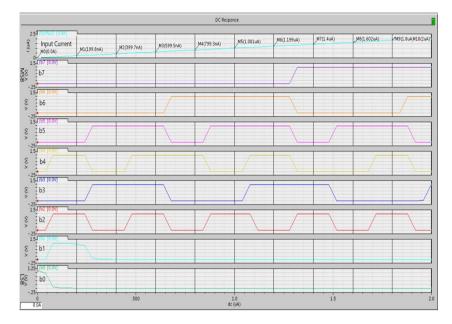

Fig.12 and Table 3 shows the result of the light intensity sensor under different levels of illuminance from 0 to 200 lux with a resolution of 20 lux. Each of these illuminance value were represented by eight bit binary number, where b0 is the Least Significant Bit (LSB) and b7 is the Most Significant Bit (MSB).

Fig. 12 - Sample of binary output of the monolithic light intensity sensor

| Illuminance<br>(lux) | Binary Output of Light Intensity sensor |    |    |    |    |    |    |    |

|----------------------|-----------------------------------------|----|----|----|----|----|----|----|

|                      | b7                                      | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| 0                    | 0                                       | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 20                   | 0                                       | 0  | 0  | 1  | 0  | 1  | 0  | 0  |

| 40                   | 0                                       | 0  | 1  | 0  | 1  | 0  | 0  | 0  |

| 60                   | 0                                       | 0  | 1  | 1  | 1  | 1  | 0  | 0  |

| 80                   | 0                                       | 1  | 0  | 1  | 0  | 0  | 0  | 0  |

| 100                  | 0                                       | 1  | 1  | 0  | 0  | 1  | 0  | 0  |

| 120                  | 0                                       | 1  | 1  | 1  | 1  | 0  | 0  | 0  |

| 140                  | 1                                       | 0  | 0  | 0  | 1  | 1  | 0  | 0  |

| 160                  | 1                                       | 0  | 1  | 0  | 0  | 0  | 0  | 0  |

| 180                  | 1                                       | 0  | 1  | 1  | 0  | 1  | 0  | 0  |

| 200                  | 1                                       | 1  | 0  | 0  | 1  | 0  | 0  | 0  |

Table 3 - Illuminance and the corresponding binary output of light intensity sensor

The illuminance reading of the sensor is translated by the binary output found from simulation. By designing a custom ADC with lower resolution it can be seen that a dramatically lower power consumption is achieved, albeit with less accuracy as a trade-off.

#### 4. Conclusion

In conclusion, the design of light intensity sensor is capable of detecting illuminance from 0 to 200 lux with a resolution of 20 lux is realized with a 130 nm CMOS architecture monolithic light sensor chip. The designed light intensity sensor is suitable to be used as an ambient light sensor for automatic light adjustment because the outputs illuminance in binary form. The monolithic light intensity sensor has a total power consumption of 1.88 mW and an area of 0.0120 mm<sup>2</sup>. The design has achieve the small chip area, low power consumption target, and the sensor design can measure the light intensity to help achieving the recommended light intensity levels of domestic areas. The CMOS monolithic light sensor chip can be made more accurate by increasing the resolution of the ADC. The resolution of the ADC can be increased by increasing the amount of voltage comparators for the extra reference voltages needed to show more measurable values at the cost of higher power consumption. The range of illuminance that is able to be detected

by the light intensity sensor can be increased by designing a different topology of TIA with adjustable gain using an NMOS as a feedback resistor.

# Acknowledgement

The authors would like to thanks Universiti Tun Hussein Onn Malaysia for the research facilities, TIER 1 Grant scheme no. H216 for and financial support.

# References

- [1] C.-T. Chiang (2014). Design of a CMOS monolithic digitized light detector with noise insensitivity for light monitoring applications. IEEE Sensor Journal, 14(8), 2537–2545

- [2] C. Chiang and Y. Hou (2016). A CMOS monolithic calibrated position-sensitive detector (PSD) for detecting light-spot position applications. IEEE International Conference on Mechatronics and Automation, 862-867

- [3] W. J. Fleming (2001). Overview of automotive sensors. IEEE Sensor Journal, 1(4), 296–308

- [4] G. Harsányi (2000). Sensors in Medicine. IEEE Sensor Journal, 171(12), 322-325

- [5] A. Song et.al (2015). Sensors for robotics 2015. Journal of Sensors, 2015

- [6] G. Markets (2016). Global Markets and Manufacturing. Global Papers, 7215

- [7] A. Kraš and D. Ph, (2006). CMOS Technology: Challenges for Future Development. Journal of Maritime Studies, 2, 97–104, 2006

- [8] A. H. Ismail et.al (2014). Development of a Webcam Based Lux Meter. IEEE Symp. Comput. Informatics, Isc. 2013, 70–74

- [9] James Janesick, Tom Elliott, James Andrews, John Tower (2017). Performance and design differences between PMOS and NMOS CMOS imagers. Proc. SPIE 10209, Image Sensing Technologies: Materials, Devices, Systems, and Applications IV, 102090Q

- [10] C. Chiang and J. Liou (2013). Design of A CMOS Intelligent Light Sensing Chip for Automatic Brightness Tuning Applications. IEEE Sensors Journal, 13, no. 12, 4955-4961

- [11] C. Bäumer et al. (2006). Design and Evaluation of a CMOS-Photosensor with In-Pixel Sigma-Delta Modulator for X-ray Computed Tomography. Proc. ESSCIRC, 432–435

- [12] W. H. Chen, H. B. Qin, Z. L. Feng (2011). Research and Design of Light Intensity Detection Circuit. 2011 International Conference on Electrical and Control Engineering. 4646-4648

- [13] Ambient Light Sensors. Available: http://www.vishay.com/docs/49670/\_pl0366.pdf [Accessed: 3 March 2019]

- [14] J. Nakamura, B. Pain, T. Nomoto, T. Nakamura, and E. R. Fossum (1997). On-Focal Plane Signal Processing For Current-Mode Active Pixel Sensors. IEEE Trans. Electron Devices, 44(10), 1747–1758

- [15] Bahram Nabet (2016). Photodetectors: Materials, Devices and Applications. Woodhead Publishing

- [16] M. H. U. Habib and N. McFarlane (2015). A perimeter gated single photon avalanche diode based silicon photomultiplier as optical detector. 2015 IEEE 58th International Midwest Symposium on Circuits and Systems (MWSCAS), pp. 1-4

- [17] Kevin M. Lynch, Nicholas Marchuk, Matthew L. Elwin (2016). Chapter 21 Sensors, Embedded Computing and Mechatronics with the PIC32, Newnes, 317-340

- [18] S. Bashir et. al. (2016). Analog-to-digital converters: A comparative study and performance analysis. 2016 International Conference on Computing, Communication and Automation (ICCCA), (pp. 999-1001)

- [19] Veepsa Bhatia et. al. (2010). Application Based Comparison of Different Analog to Digital Converter Architectures. International Journal of Engineering Science and Technology, 2(8), 3396-3404

- [20] P. Harpe (2016). Successive Approximation Analog-to-Digital Converters: Improving Power Efficiency and Conversion Speed. IEEE Solid-State Circuits Magazine, vol. 8 (4), 64-73