# Design of Low Power CMOS Bioamplifier in 250 nm and 90 nm Technology Node

## Wan Mohammad Ehsan Aiman Wan Jusoh\*, Chai Chooi Yee, Siti Hawa Ruslan and Mohd Jais Che Soh

Faculty of Electrical and Electronic Engineering Universiti Tun Hussein Onn Malaysia, Batu Pahat, Johor, Malaysia.

Abstract: The advancement of Complementary Metal Oxide Semiconductor (CMOS) technology has enabled a better design in bioamplifier for electroencephalography (EEG) and electrocardiogram (ECG) signals acquisition systems. Bioamplifier can be designed using two-stage CMOS operational transconductance amplifier (OTA). This paper presents the performance of CMOS bioamplifier which had been designed using two CMOS technology; one using 250 nm and the other in 90 nm technology. The 250 nm CMOS bioamplifier operates with  $\pm 2.5$  V voltage supply and has open loop gain of 82 dB and the common mode rejection ratio (CMRR) of 92 dB, meanwhile the 90 nm CMOS bioamplifier operates with  $\pm 1.2$  V voltage supply and has open loop gain of 73.03 dB. The power consumed by the OTA bioamplifier is 5.56 mW for the 250 nm amplifier and 15.53  $\mu$ W for the 90 nm amplifier.

Keywords: CMOS bioamplifier, biopotential signals, open loop gain, common mode rejection ratio, low-power OTA

## 1. Introduction

There are electrical signals that running through human body to control and enable the human system activities which can be referred as biopotential signals. One of the examples is the nervous system of human. The brain communicate with the body systems by receiving and transmitting the signal in the form of electricity where the electrical charge is jumping from cell to cell until it reaches its destination. The biopotential in human body are in millihertz which are too small for Analog-to-Digital Converter (ADC) digitalization. Hence, bioamplifier is needed in order to amplify the signal to be processed further for analyzing and monitoring purpose. In short, bioamplifier is a device used to collect and amplify the biopotential of the human body in order to monitor the physiology electrical activities.

The design of CMOS bioamplifier is mostly using the Operational Transconductance Amplifier (OTA) topology. For this approach, there are only transistors and capacitors involved in the design. Resistor is not preferable especially in the layout design since it will result in a larger layout area. A very low power consumption of amplifier is one of the key parameter that will be analyzed in this paper. There are few types of OTA design and every design has its pros and cons. Hamzah et al. reported a design and analysis of two-stage CMOS op-amp by using Silterra's 0.13 µm technology [1]. The two-stage op-amp consumed about 109.07 µW from 1.2 V voltage supply [1]. In 2012, Enamul Quadir et al. presented a design of bioamplifier with lowpower and low-noise characteristics for multielectrode neural recording which consumed 198.6 nW from 0.6 V voltage supply [2]. A CMOS bioamplifier for active

\**Corresponding author: ge170092@siswa.uthm.edu.my* 2017 UTHM Publisher. All right reserved. penerbit.uthm.edu.my/ojs/index.php/ijie

electrode with DC rejection reported in 2013 by Huang et al. [3]. The bioamplifier consumed 6.7  $\mu$ W from 1.8 V voltage supply [3]. Table 1 shows the summary of previous research of bioamplifier designs. In most of the designs, the main aim is to reduce the power consumption of the amplifier in order to increase the life-time of the battery used in the bioamplifier system.

Table 1 Summary of reported work.

|     | Year | Voltage<br>Supply<br>(V) | Gain<br>(dB) | Power<br>(W) | Topology   |

|-----|------|--------------------------|--------------|--------------|------------|

| [1] | 2014 | 1.2                      | 85.93        | 109.1µ       | Two-stage  |

| [2] | 2012 | 0.6                      | 24.94        | 198.6n       | Two-stage  |

| [3] | 2013 | 0.8                      | 39.5         | 6.7µ         | Telescopic |

| [4] | 2016 | 1.6                      | 34.13        | 0.264m       | Two-stage  |

| [5] | 2017 | 2.0                      | 84           | 38.02µ       | Two-stage  |

| [6] | 2014 | 1.0                      | 55.1         | 2.6µ         | Two-stage  |

| [7] | 2015 | 0.5                      | 88           | 80n          | Two-stage  |

The structure of this paper is as follows, Section II describes the design of bioamplifier in 250 nm and 90 nm together with design steps of the OTA bioamplifier. Section III gives the results and discussions of both

amplifiers. Finally, Section IV presents the conclusion of the paper.

## 2. Bioamplifier Design

The OTA bioamplifier starts with the identification of the input signal to the amplifier. Then, it continues with the calculation of the size of the transistors used for the amplifier in order to achieve a high gain and CMRR. After that, the amplifier is tested by running a few simulations. The results are analyzed and modifications to the transistor circuit and size are made if needed.

### 2.1 Circuit Topology

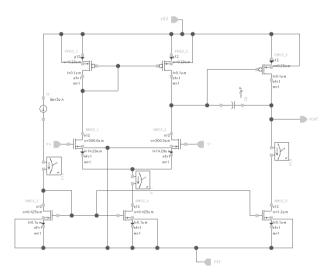

The circuit in Figure 1 is designed using Tanner S-Edit and Synopsys Schematic Editor-Custom Designer with CMOS technology 250 nm and 90 nm respectively. This circuit consists of 8 transistors. The NMOS\_1 and NMOS\_2 form the differential pair, and the PMOS\_1 and PMOS\_2 form the active load. PMOS\_3 and NMOS\_5 form a current mirror pair. The second stage consists of the common-source connected NMOS\_4 where NMOS\_3 provides the bias current for it. A compensation capacitor with capacitance of 5 pF is added in order to stabilize the amplifier circuit. The gain of the bioamplifier is defined by the size of the transistors. Hence, the right ratio of width over length (W/L) is vital in the design process.

Fig.1 Schematic circuit of the proposed 2 stage operational transcondutance amplifier (OTA).

## 2.2 Bioamplifier Design Specification and W/L Ratio of Transistors

The size for each transistor in Figure 1 is designed based on the specification in Table 2. Several steps must be followed in order to determine the transistor size. The steps are as follow:

Step 1: Decide the capacitance value for the compensation capacitor,  $C_C$ . The value of  $C_C$  must be larger than 2.2 pF.

Step 2: Determine the minimum value for tail current through NMOS\_4, I4. It is determined by equation (1).

$$I_4 = Slew Rate \times C_C \tag{1}$$

Table 2 Bioamplifier design specifications.

| Specification  | Value (250 nm         | Value (90 nm          |

|----------------|-----------------------|-----------------------|

| 1              | <b>Bioamplifier</b> ) | <b>Bioamplifier</b> ) |

| V-H            | 1 /                   | L /                   |

| Voltage Supply | $\pm 2.5$             | ±1.2                  |

| (V)            |                       |                       |

| Load           | 1                     | 1                     |

| Capacitor (CL) |                       |                       |

| ( <b>pF</b> )  |                       |                       |

| Open Loop      | >80                   | >40                   |

| Gain (dB)      |                       |                       |

| Slew Rate      | 10                    | 10                    |

| (V/us)         |                       |                       |

| Gain           | >10M                  | 10M                   |

| Bandwidth      |                       |                       |

| (GB)           |                       |                       |

| CMRR (dB)      | >60                   | >60                   |

| ICMR (V)       | >1.5                  | >1.5                  |

| Power          |                       |                       |

| Consumption    | <10m                  | <30µ                  |

| (W)            |                       | -                     |

Step 3: Calculate the size of PMOS\_1 and PMOS\_2 by using ICMR requirement as in equation (2).

$$S_{P1} = S_{P1} = \frac{W_{P1}}{L_{P1}}$$

$$= \frac{I_4}{K' [V_{DD} - V_{in(max)} - V_{TO3(max)} + V_{T1(min)}]^2}$$

(2)

Step 4: Determine the size for NMOS\_1 and NMOS\_2 from the desired gain bandwidth by using equation (3) and (4).

=

$$gm_1 = GB \times C_C \tag{3}$$

$$S_{N1} = S_{N2} = \frac{gm_1^2}{K_N' I_4} \tag{4}$$

Step 5: Calculate  $V_{DS4 (sat)}$  which is the minimum input voltage in order to determine the size for transistors NMOS\_3 and NMOS\_4 using equation (5) and (6).

$$V_{DS4(sat)} = V_{in(min)} - V_{SS} - \sqrt{\frac{I_4}{\beta_1}} - V_{T1(max)}$$

(5)

$$S_{N3} = S_{N4} = \frac{2I_4}{\kappa'_N [V_{DS(sat)}]^2}$$

(6)

Step 6: Determine the transconductance for PMOS\_3,  $gm_{P3}$  is determined before finding the size for PMOS\_3,  $S_{P3}$  using equation (7) and (8). It is assumed that  $V_{SG}$  of PMOS\_2 is equal  $V_{SG}$  of PMOS\_3.

$$gm_{P3} = 2.2gm_{N2}\frac{c_L}{c_C}$$

(7)

$$gm_{P3} = S_{P2} \frac{gm_{P3}}{gm_{P2}} \tag{8}$$

Step 7: Calculate the current through PMOS\_3,  $I_{P3}$  by using equation (9).

$$I_{P3} = \frac{gm_{P3}{}^2}{2K'_P S_{P3}} \tag{9}$$

Step8: Determine the size for NMOS\_5,  $S_{N5}$  to achieve the desired current ratios between  $I_{N4}$  and  $I_{P3}$  using equation (10).

$$S_{N5} = \frac{I_{P3}}{I_{N4}} S_{P3} \tag{10}$$

Table 3 summarizes all the dimension of the transistors in Figure 1 which have been calculated using equations (1) to (10). The W/L ratio of 250 nm bioamplifier is different from the 90 nm bioamplifier based on the specification in Table 2.

Table 3 Calculated size of transistors.

| Transistor        | W/L Ratio for<br>250 nm<br>Amplifier (um) | W/L ratio for 90<br>nm Amplifier<br>(um) |

|-------------------|-------------------------------------------|------------------------------------------|

| NMOS_1,           | 10/1                                      | 9/1                                      |

| NMOS_2<br>PMOS_1, | 25/1                                      | 39/1                                     |

| PMOS_2<br>NMOS_3, | 5/1                                       | 3/1                                      |

| NMOS_4<br>PMOS_3  | 157/1                                     | 480/1                                    |

| NMOS_5            | 13/1                                      | 18/1                                     |

However some modifications are done to the W/L ratio of the transistors. Modification on the size of transistors is based on references as stated in [8]. The sizes of input NMOS\_1 and NMOS\_2 transistor pair are increased tremendously in order to have an open loop gain as high as 80 dB. Table 4 shows the modified size of the transistors.

Table 4 Modified calculated size of transistor.

| Transistor        | W/L Ratio for<br>250 nm<br>Amplifier (um) | W/L ratio for 90<br>nm Amplifier<br>(um) |

|-------------------|-------------------------------------------|------------------------------------------|

| NMOS_1,<br>NMOS 2 | 151.2/7.2                                 | 300/14.29                                |

| PMOS_1,<br>PMOS_2 | 50.4/1.2                                  | 21/0.5                                   |

| NMOS_3,<br>NMOS_4 | 5.1/1.2                                   | 0.425/0.1                                |

| PMOS_3            | 302.4/1.2                                 | 75.6/0.3                                 |

| NMOS_5            | 14.4/1.2                                  | 1.2/0.1                                  |

#### 3. Simulation Results and Discussion

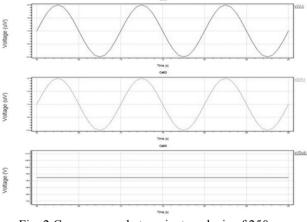

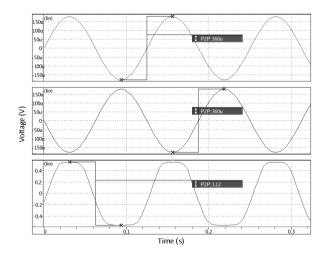

In transient analysis, a common mode and differential mode analysis are carried out to the bioamplifier. In the common mode analysis, both of the input sources are sinusoidal input and in phase with an amplitude of 360  $\mu$ V<sub>P-P</sub> and frequency of 8 Hz to imitate the waveforms of biopotential signals (EEG and ECG). Load capacitor with 10 pF capacitance is added at the output as a load capacitor.

When both the V+ and V- are in common mode, the waveform of the output, Vout for the 250 nm amplifier is a straight line, as shown in Fig. 2. On the other hand, for the 90 nm amplifier, the output waveform appear as a sinusoidal form as shown in Fig. 3. Both outputs are correct because in a common mode, the gain should be as small as possible and the ideal value is zero. In Fig. 2, the peak-to-peak voltage,  $V_{P-P}$  of the output is 100  $\mu$ V and for the Fig. 3, it is 250  $\mu$ V. Both the peak-to-peak output voltages are very small and can be considered zero. The result of the analysis shows that the amplifier being designed indeed functioning as it is supposed to be with a small  $V_{P-P}$  at the output.

Fig. 2 Common mode transient analysis of 250 nm bioamplifier.

Fig. 3 Common mode transient analysis of 90 nm bioamplifier.

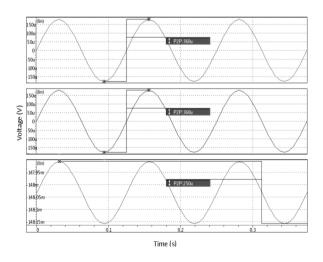

In the differential mode, both input to the amplifier are similar in magnitude which is 180  $\mu$ V<sub>P-P</sub> but different in phase by 180°. The simulation results are shown in Fig. 4 and Fig. 5 for the 250 nm bioamplifier and 90 nm respectively. Theoretically, the differential mode gain should be as high as possible, thus the output produced must be large. The 250 nm bioamplifier had an output of 4.11 V<sub>P-P</sub> and for the 90 nm amplifier it is 1.12 V<sub>P-P</sub>. However, the output for both amplifiers are slightly distorted due to the mismatch and non-ideal conditions of the transistors used. The output in Fig. 5 for the 90 nm amplifier is also clipped due to the limitation of the power supply at only 1.2 V<sub>P-P</sub>. This means the gain of the 90 nm amplifier must be reduced because it has achieved the saturation level.

Fig. 4 Differential mode transient analysis of 250 nm bioamplifier.

Fig. 5 Differential mode transient analysis of 90nm bioamplifier.

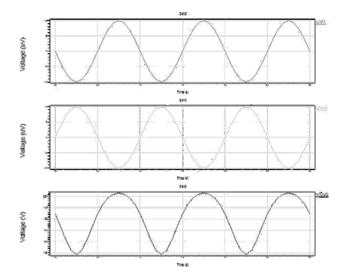

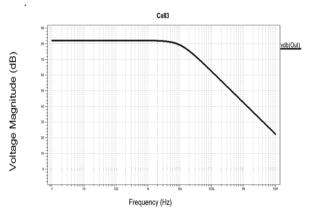

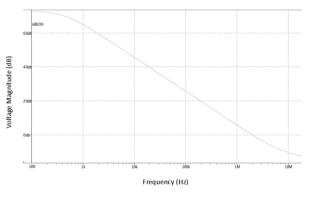

In the AC analysis, the gain of the amplifier versus the frequency is plotted. The analysis is done for the differential mode only because this is the gain needed. The results shown in Fig. 6 is for the 250 nm bioamplifier and

in Fig. 7 is for the 90 nm bioamplifier. The 250 nm amplifier produced a gain of 82 dB while the 90 nm amplifier produced a gain of 72.9 dB. Both gains are very high.

Fig. 6 Frequency response for 250 nm bioamplifier.

Fig. 7 Frequency response for 90 nm bioamplifier.

Common mode rejection ratio is a value that shows how good the amplifier in rejecting noise. The CMRR is obtained by calculation the common mode gain  $(A_c)$  and differential mode gain  $(A_d)$  by using equation (11) and (12). The CMRR is the ratio of  $A_d$  and  $A_c$  as shown in equation (13).

$$A_{C} = \frac{V_{O}}{0.5(V^{+}+V^{-})} \tag{11}$$

$$A_d = \frac{V_0}{(V^+ - V^-)}$$

(12)

$$CMRR(dB) = 20 \log_{10} \frac{A_C}{A_d}$$

(13)

Based on the result in Fig. 2 and Fig. 3, the common mode gain obtained is:

$$A_{C} = \frac{V_{O}}{0.5(V^{+} + V^{-})} = \frac{100 \ \mu V}{360 \ \mu V}$$

= 0.278 (250 nm amplifier)

$$A_{C} = \frac{V_{O}}{0.5(V^{+} + V^{-})} = \frac{250 \ \mu V}{360 \ \mu V}$$

= 0.694 (90 nm amplifier)

The differential mode is calculated based on the results shown in Fig. 4 and Fig. 5. The differential mode gain is:

$$\begin{split} A_{d} &= \frac{V_{O}}{(V^{+} - V^{-})} = \frac{4.1121 \, V}{360 \, \mu V} \\ &= 11422.5(250 \, nm \, amplifier) \end{split}$$

$$A_{d} = \frac{V_{0}}{(V^{+} - V^{-})} = \frac{1.12 V}{360 \mu V}$$

= 3111.11(90 nm amplifier)

By using equation (13), the CMRR of the designed amplifier can be calculated as:

$$CMRR(dB) = 20 \log_{10} \frac{A_c}{A_d} = 20 \log_{10} \frac{11422.5}{0.278}$$

$$= 92.3 \ dB(250 \ nm \ amplifier)$$

$$CMRR(dB) = 20 \log_{10} \frac{A_c}{A_d} = 20 \log_{10} \frac{3111.115}{0.694}$$

= 73.3 dB(90 nm amplifier)

The high CMRR obtained for both amplifiers show that the bioamplifier has a good noise rejection ratio. Hence it can be said the proposed bioamplifier circuit is functionally well in both 250 nm and 90 nm CMOS technologies.

#### 4. Power Consumption

Power consumption is the most important parameter in modern analog integrated circuit design. It will determine how long the battery life of a specific circuit especially if the circuit is for wearable application. As the biopotential acquisition system should be in portable size, it is essential for the bioamplifier to have low power consumption. Power consumption is calculated using equation (14).

$$P = (I_{first \ stage} + I_{second \ stage}) * V_{DD}$$

(14)

From simulations and calculations, the power consumption for the 250 nm and 90 nm bioamplifier are 5.59 mW and 15.31  $\mu$ W, respectively. When compared to the literature [1], [4], [5], the power consumed by 90 nm bioamplifier is lesser and this shows the 90 nm bioamplifier is better and besides that, it also consume less power when compared to 250 nm bioamplifier.

#### 5. Conclusion

The CMOS bioamplifier designed in this work is based on two-stage operational transconductance amplifier (OTA). The schematic design is done with 250 nm and 90 nm CMOS technology. The voltage supply for the 250 nm and 90 nm bioamplifier are  $\pm 2.5$  V and  $\pm 1.2$  V, respectively. The transient and AC analysis have been carried out. The two-stage 250 nm and 90 nm amplifiers produce open loop gain of 82 dB and 72.9 dB, and have a high CMRR of 92.3 dB and 73.03 dB, respectively. The power consumption of 250 nm amplifier is 5.59 mW while for 90 nm amplifier, it is  $15.53 \mu$ W.

Based on the comparison between both designed bioamplifier and existing bioamplifier from literature, it can be said that proposed design of 90 nm bioamplifier in this report achieved better performance in terms of power consumption, although the gain is slightly decreased when the voltage supply is reduced from 5 V to 1.2 V. The 90 nm bioamplifier with low-power and high CMRR characteristics is suitable to be implemented in detecting and analyzing biopotential signals.

#### References

- M. H. Hamzah, A. B. Jambek, and U. Hashim, "Design and analysis of a two-stage CMOS opamp using Silterra's 0.13 μm technology," *ISCAIE* 2014 - 2014 IEEE Symp. Comput. Appl. Ind. Electron., pp. 55–59, 2015.

- [2] M. S. Enamul Quadir, M. R. Haider, and Y. Massoud, "A low-power low-noise bioamplifier for multielectrode neural recording systems," *ISCAS 2012 2012 IEEE Int. Symp. Circuits Syst.*, pp. 2557–2560, 2012.

- [3] S. Huang, J. Zhang, and L. Wang, "A 6.7μW CMOS bioamplifier for active electrode with DC rejection," 2013 IEEE Biomed. Circuits Syst. Conf. BioCAS 2013, pp. 1–4, 2013.

- [4] S. Gaonkar and S. P.S., "Modeling, design and analysis of high CMRR two stage gate driven operational transconductance amplifier using 0.18 μm CMOS technology," 2016 3rd Int. Conf. Comput. Sustain. Glob. Dev., pp. 329–334, 2016.

- [5] C. L. Kavyashree, M. Hemambika, K. Dharani, A. V Naik, and M. P. Sunil, "Design and implementation of two stage CMOS operational amplifier using 90nm technology," in 2017 International Conference on Inventive Systems and Control (ICISC), 2017, pp. 1–4.

- [6] F. Moulahcene, N. E. Bouguechal, I. Benacer, and S. Hanfoug, "Design of CMOS two-stage operational amplifier for ECG monitoring system using 90nm technology," *Int. J. Bio-Science Bio-Technology*, vol. 6, no. 5, pp. 55–66, 2014.

- H. Veldandi and S. R. Ahamed, "A 0.5 V, 80-nW pseudo-differential two-stage OTA in 0.18??m CMOS technology," in 12th IEEE International Conference Electronics, Energy, Environment, Communication, Computer, Control: (E3-C3), INDICON 2015, 2016, pp. 2–6.

- [8] P. E. Allen and D. R. Holberg, CMOS Analog Circuit Design Second Edition. Oxford University Press, 2002.