## ABSTRACT

| Title of Dissertation:       | Composing and Decomposing OS Abstractions                                                   |

|------------------------------|---------------------------------------------------------------------------------------------|

|                              | James Benjamin Litton<br>Doctor of Philosophy, 2021                                         |

| Dissertation Co-directed by: | Professor Bobby Bhattacharjee<br>Professor Peter Druschel<br>Department of Computer Science |

Operating systems (OSes) provide a set of abstractions through which hardware resources are accessed. Abstractions that are closer to hardware offer the greatest opportunity for performance, whereas higher-level abstractions may sacrifice performance but are typically more portable and potentially more secure and robust. The abstractions chosen by OS designs impose a set of trade-offs that will not be well-suited for all applications.

In this dissertation, we argue the following thesis: Supporting novel hardware such as non-volatile RAM (NVRAM) and new abstractions like fine-grained isolation while maintaining efficiency, usability, and security goals, requires simultaneous access to both high-level OS abstractions and compatible access to their low-level decompositions. We support this thesis by offering two new abstractions, PTx and light-weight-contexts (lwCs), as well as the null-Kernel, a new OS architecture. PTx is a new high-level abstraction for persistence built on top of NVRAM, a new form of persistent byte addressable memory, whereas lwCs are a new OS abstraction that enables fine-grained intra-process isolation, snapshots and reference monitoring. Due to the efficiency requirements of both PTx and lwCs, both abstractions required access to low-level decompositions of higher-level abstractions, while interoperability requirements dictated that both low and high-level abstractions were exposed simultaneously. The null-Kernel is an OS architecture that enabled the simultaneous exposure of multiple abstractions for the same underlying hardware in a safe way, which, if adopted, would accelerate the development and deployment of abstractions such as PTx and lwCs.

## Composing and Decomposing OS Abstractions

by

James Benjamin Litton

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2021

Advisory Committee: Professor Bobby Bhattacharjee, Chair/Advisor Professor Peter Druschel, Chair/Advisor Professor Neil Spring Professor Dave Levin Professor Mark Shayman © Copyright by James Benjamin Litton 2021

#### Acknowledgments

The work in this dissertation was not a lone effort, but was instead aided by too many to mention explicitly. All the same, I would like to acknowledge the role a few individuals have played in this work and my life more broadly over this period.

First, I must thank the staff at the University of Maryland and the Max Planck Institute for Software Systems. To Brigitta, Claudia, Tom, Maria-Louise, Annika, and many others, thank you for your patience when dealing with my administrative incompetence and shepherding me through various bureaucratic and logistic obstacles that I ran into along the way.

I must also thank my advisors, Bobby Bhattacharjee and Peter Druschel. Bobby plucked me out of one of his courses and urged me to quit my inane job and start down this journey. All of this is his fault. It was a privilege to work with someone who understood where my mind was heading, even when I wasn't quite prepared to articulate it clearly. Peter, on the other hand, always offered a steady hand that kept my more fanciful ideas grounded and offered expert advice on framing and improving our work. Both contributed to my personal and professional development and this dissertation would not have been possible without their guidance. It has been an honor to be advised by both of them.

Beyond my advisors, there are a number of other researchers who helped me on this journey. Matthew Lentz often liked to give life advice (thankfully not all of it followed) and our frequent conversations about culinary pursuits and wine were a welcome distraction. Deepak Garg was a frequent collaborator who brought a different perspective to our work, which I appreciate. Dave Levin, who I collaborated on a paper with and had many discussions with, was ceaselessly and infectiously optimistic about our capabilities and is a fountain of good advice. Neil Spring, who was a leader in our group, contributed to the rigor of our group and always had an incisive, interesting and thoughtful perspective when discussing our work or the work of others. I benefited greatly from these varied perspectives and am grateful to have had the opportunity to learn from all of them.

Additionally, I would like to thank my advisors, Neil, Dave, and Mark Shayman, who all served on my committee and improved this dissertation.

I would also like to thank the following colleagues for their role as collaborators and friends. In alphabetical order: Paarijaat Aditya, Mohamed Alzayat, Theophilus Benson, Björn Brandenburg, Frank Cangialosi, Eslam Elnikety, Neal Gupta, Stephen Herwig, Mike Hicks, Pete Keleher, Zhihao Li, Andrew Miller, Alan Mislove, Aastha Mehta, Ramakrishna Padmanabhan, Richie Roberts, Roberta de Vita, Anjo Vahldiek-Oberwagner, and Liang Zhang.

Finally, most importantly, I'd like to thank my northern star, my wife Sarah. When Bobby suggested this path, she didn't hesitate and endorsed my pursuit of the Ph.D., and despite my occasional doubts, she remained my biggest cheerleader and defender. In more ways than I could ever articulate, she is the best thing in my life.

This dissertation was supported by the National Science Foundation (TWC 1314857, NeTS 1526635, and CNS 1840902), the European Research Council (ERC Synergy imPACT 610150), and the German Science Foundation (DFG CRC1223).

This dissertation involved collaborative efforts with the following people:

Chapter 3: My co-authors for PTx were Deepak Garg, Peter Druschel, and Bobby Bhattacharjee. We are appreciative of the feedback we received from from Isaac Sheff, Roberta de Viti, Mohamed Alzayat, and Matthew Lentz.

Chapter 4: My co-authors for Light-Weight Contexts [1] were Anjo Vahldiek-Oberwagner, Eslam Elnikety, Deepak Garg, Bobby Bhattacharjee, and Peter Druschel. We offer additional thanks to the following for their helpful feedback: Paarijaat Aditya, Björn Brandenburg, Mike Hicks, Pete Keleher, Matthew Lentz, Dave Levin, Neil Spring, anonymous reviewers, and KyoungSoo Park, who shepherded our conference submission.

Chapter 5: My co-authors for the Composing Abstractions using the null-Kernel [2] were Deepak Garg, Peter Druschel, and Bobby Bhattacharjee. We would like to thank the anonymous reviewers, Pete Keleher, Matt Lentz and Dave Levin.

# **Table of Contents**

| A  | ckno                            | wledge                                                                         | ements ii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----|---------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ta | able (                          | of Con                                                                         | tents v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Li | ist of                          | Table                                                                          | s vii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Li | ist of                          | Figur                                                                          | es viii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1  | <b>Int</b> r<br>1.1<br>1.2      | oduct<br>Thesis<br>Contr                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2  | <b>Bac</b><br>2.1<br>2.2<br>2.3 | <b>kgrou</b><br>Abstr<br>Decou                                                 | nd and Related Work10actions for NVRAM10upling Process Abstractions10ving OS Flexibility22                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3  | PT:<br>3.1<br>3.2<br>3.3        | Introd<br>PTx c<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7 | 24         luction       24         lesign       27         Requirements       27         PTx colors and operations       29         PTx Semantics       30         PTx storage       31         PTx primitives       32         Tracking Write Sets       39         Non-atomic NVRAM block writes       41         ation of PTx       42         Experimental setup       43         PTx versus PDMK       45         PTx on existing data structures       50         Multi-core scalability       52 |

|    | 3.4                             | $3.3.5 \\ 3.3.6$                                                               | Applications with persistent state       53         Persistent key-value store performance       57         usion       61                                                                                                                                                                                                                                                                                                                                                                               |

| 4        | Ligł         | nt-weight Contexts                                                                                                                                             | 63        |

|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|          | 4.1          | Introduction                                                                                                                                                   | 63        |

|          | 4.2          | lwC design                                                                                                                                                     | 66        |

|          |              | 4.2.1 Creating $lwCs$                                                                                                                                          | 67        |

|          |              | 4.2.2 Switching between $lwCs$                                                                                                                                 | 69        |

|          |              | 0                                                                                                                                                              | 69        |

|          |              | 4.2.4 Dynamic resource sharing                                                                                                                                 | 70        |

|          |              | 4.2.5 Access capabilities                                                                                                                                      | 71        |

|          |              | 4.2.6 System call interposition/emulation                                                                                                                      | 71        |

|          |              | 0 0                                                                                                                                                            | 72        |

|          |              | v                                                                                                                                                              | 73        |

|          |              | 4.2.9 $lwC$ isolation                                                                                                                                          | 73        |

|          |              | $4.2.10  lwC \text{ security } \ldots $ | 74        |

|          | 4.3          | 0 1                                                                                                                                                            | 76        |

|          | 4.4          | Evaluation of $lwCs$                                                                                                                                           | 83        |

|          |              | 4.4.1 $lwC$ switch                                                                                                                                             | 83        |

|          |              |                                                                                                                                                                | 84        |

|          |              | 4.4.3 Reference monitoring                                                                                                                                     | 85        |

|          |              | 4.4.4 Apache                                                                                                                                                   | 86        |

|          |              | 4.4.5 Nginx                                                                                                                                                    | 90        |

|          |              |                                                                                                                                                                | 95        |

|          |              |                                                                                                                                                                | 96        |

|          | 4.5          | Conclusion                                                                                                                                                     | 98        |

| <b>5</b> | The          | e null-Kernel                                                                                                                                                  | 99        |

| 0        | 5.1          |                                                                                                                                                                | <b>99</b> |

|          | $5.1 \\ 5.2$ | The null-Kernel                                                                                                                                                |           |

|          | 0.2          | 5.2.1 null-Kernel Capabilities                                                                                                                                 |           |

|          |              | 5.2.2 null-Kernel Structures                                                                                                                                   |           |

|          | 5.3          | null-Kernel in Practice                                                                                                                                        |           |

|          | 5.4          | NVRAM and the null-Kernel                                                                                                                                      |           |

|          | 5.5          | Isolation Abstractions and the null-Kernel                                                                                                                     |           |

|          | 5.6          | Conclusion                                                                                                                                                     |           |

|          | 0.0          |                                                                                                                                                                |           |

| 6        |              |                                                                                                                                                                | 23        |

|          | 6.1          | Future Work                                                                                                                                                    |           |

|          |              | 6.1.1 Extensions to PTx                                                                                                                                        |           |

|          |              | 6.1.2 Persistent $lwCs$                                                                                                                                        |           |

|          |              | 6.1.3 Implementing a null-Kernel                                                                                                                               |           |

|          | 6.2          | Concluding Thoughts                                                                                                                                            | 30        |

| Bi       | ibliog       | graphy 1                                                                                                                                                       | 32        |

## List of Tables

| 3.1 | Auxillary functions used in PTx                                                                                                               | 32 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Queries/second achieved with 1 second persistence for Redis, persist-                                                                         |    |

|     | ing its write-ahead log to disk, Redis-pmem, Redis using PTx as a                                                                             |    |

|     | backend, and a custom key value server using $PTx$ and the $C++$ hash                                                                         |    |

|     | table implementation. Lines is the source code lines changed relative                                                                         |    |

|     | to stock Redis.                                                                                                                               | 59 |

| 4.1 | API for interacting with $lwCs$ . Parameters in italics <i>new</i> , <i>caller</i> ,                                                          |    |

|     | are $lwC$ descriptors. Arguments args are passed during $lwC$ switches; resource-spec denotes resources (e.g. memory pages, file descriptors) |    |

|     | that can be shared or narrowed.                                                                                                               | 66 |

| 4.2 | Median switch time (in microseconds) and standard deviation over                                                                              | 00 |

|     | ten trials.                                                                                                                                   | 84 |

| 4.3 | Average requests per second over 60 seconds with 24 concurrent re-                                                                            |    |

|     | quests.                                                                                                                                       | 97 |

## List of Figures

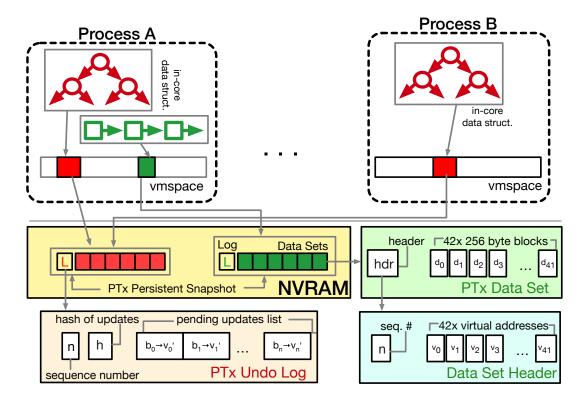

| 3.1  | Overview of PTx: Applications allocate persistent data structures using |    |

|------|-------------------------------------------------------------------------|----|

|      | "colored" parts of the heap. PTx tracks changes to the colored regions, |    |

|      | and atomically updates persistent copies in NVRAM upon commit. Details  |    |

|      | of the NVRAM structure and atomic update are described in the text      | 40 |

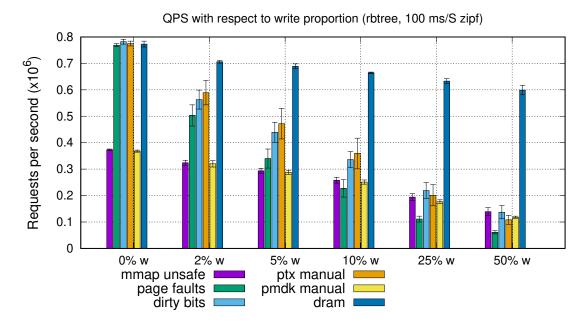

| 3.2  | Queries per second (in thousands) as a function of write frequency,     |    |

|      | with the PMDK provided red black tree implementation and Zipf           |    |

|      | distributed workload, commit every 100 ms                               | 46 |

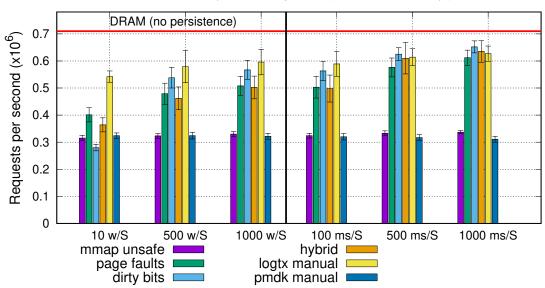

| 3.3  | Queries per second (in thousands) with the PMDK provided red black      |    |

|      | tree implementation and Zipf distributed workload with 2% clustered     |    |

|      | by writes per snapshot or milliseconds per snapshot                     | 48 |

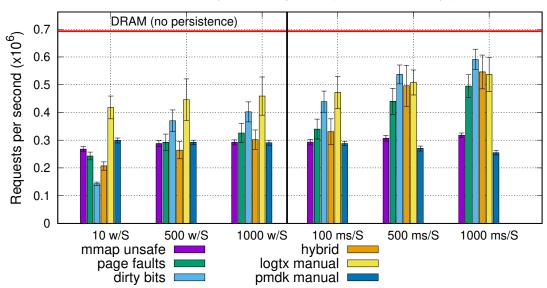

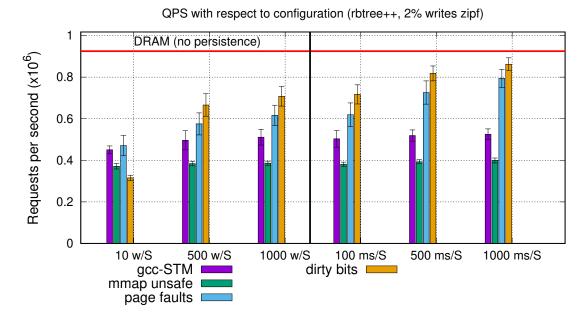

| 3.4  | Queries per second (in thousands) with the PMDK provided red black      |    |

|      | tree implementation and Zipf distributed workload with 5% clustered     |    |

|      | by writes per snapshot or milliseconds per snapshot                     | 49 |

| 3.5  | Queries per second with the C++ red-black tree implementation from      |    |

|      | a Zipf distributed workload with 2% writes.                             | 51 |

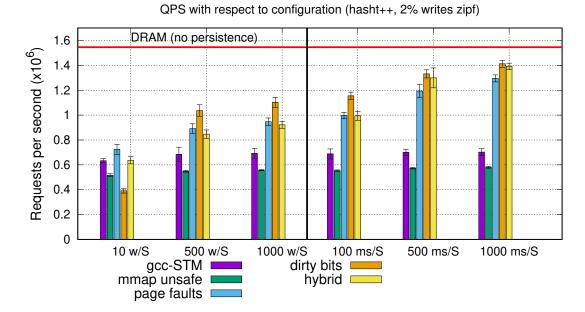

| 3.6  | Queries per second with the C++ hashtable implementation from a         |    |

|      | Zipf distributed workload with 2% writes.                               | 52 |

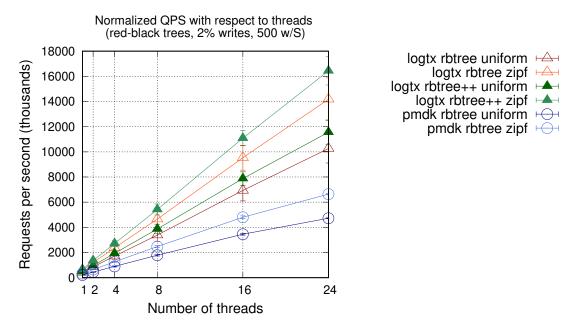

| 3.7  | Queries per second with the C++ and PMDK-provided red-black tree        |    |

|      | implementation, $2\%$ write workload, with 500 writes between commit    |    |

|      | calls                                                                   | 54 |

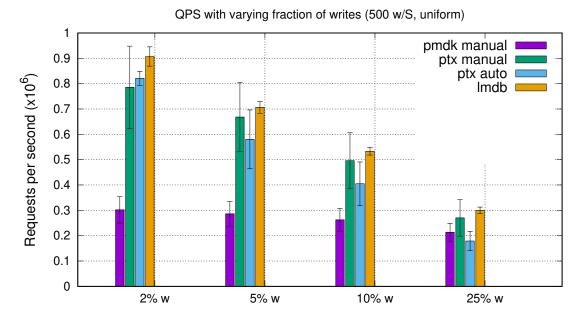

| 3.8  | Queries per second with 500 writes / commit from a uniformly dis-       |    |

|      | tributed workload varying write proportion.                             | 55 |

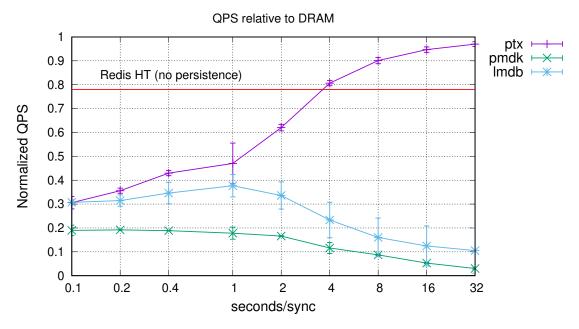

| 3.9  | Queries per second (relative to DRAM) with the C++ STL hashtable,       |    |

|      | dirty bits tracker with a 25% write workload generated from uniformly   |    |

|      | distribution keys. For comparison, we also include the throughput of    |    |

|      | PMDK and LMDB, both of which require manual annotation, and of          |    |

|      | the Redis hash table, <i>without</i> persistence                        | 57 |

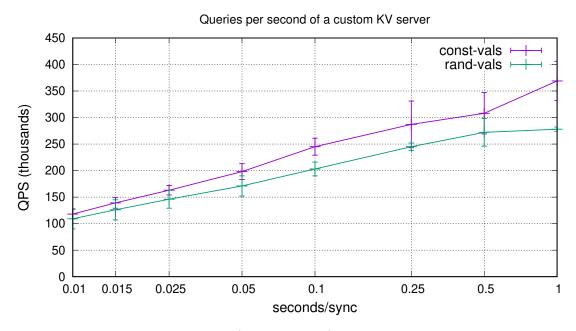

| 3.10 | Queries per second (in thousands) of our custom key-value server as     |    |

|      | a function of $\tt commit$ frequency and value distribution             | 60 |

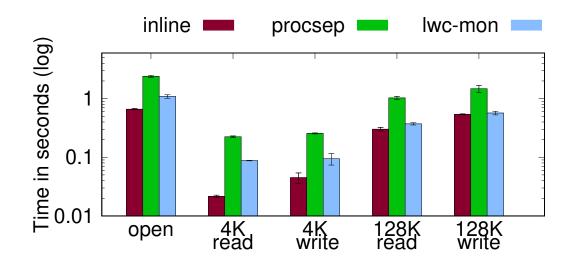

| 4.1  | Cost of 10,000 monitored system calls in seconds (log scale). Error     |    |

|      | bars show standard deviation                                            | 87 |

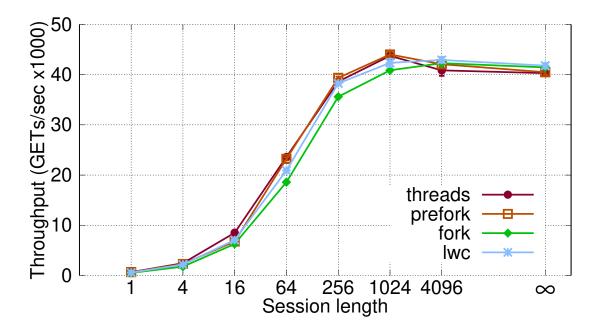

| 4.2 | Apache throughput in (GETs/sec) of 128 concurrent clients, 45 byte        |       |

|-----|---------------------------------------------------------------------------|-------|

|     | docs, over HTTP. Error bars show standard deviation, which was            |       |

|     | below $3.7\%$ .                                                           | . 88  |

| 4.3 | Apache throughput in (GETs/sec) of 128 concurrent clients, 45 byte        |       |

|     | docs, over HTTPS. Error bars show standard deviation, which was           |       |

|     | below 3.7%                                                                | . 89  |

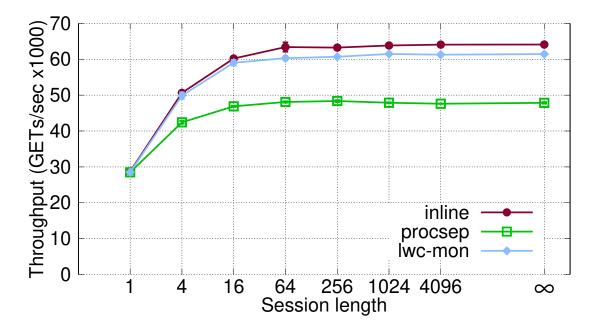

| 4.4 | Throughput of different Apache reference monitoring configurations        |       |

|     | in (GETs/sec) of 128 concurrent clients, 45 byte docs. Error bars         |       |

|     | show standard deviation, which was below 2%                               | . 91  |

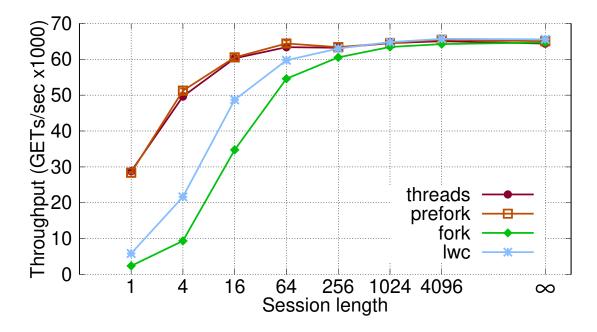

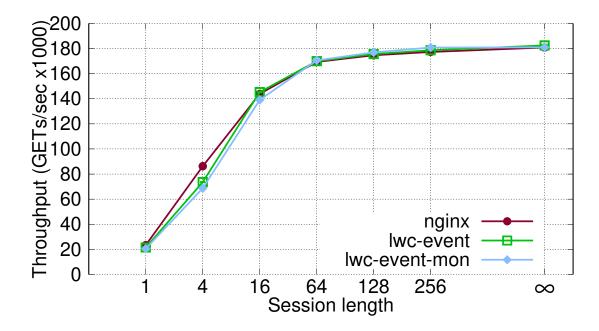

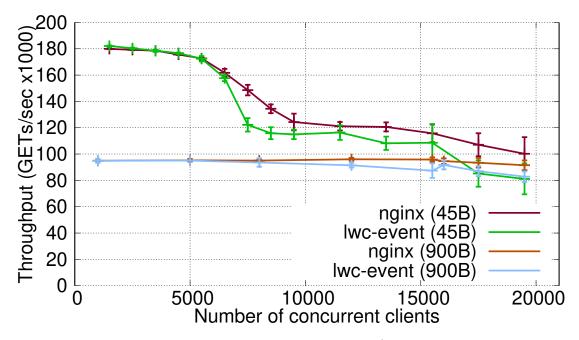

| 4.5 | Nginx throughput in GETs/sec for HTTP requests with 10 workers,           |       |

|     | 45B documents, 300 concurrent requests. Error bars show standard          |       |

|     | deviation, which was below 0.9%.                                          | . 92  |

| 4.6 | Nginx throughput in GETs/sec for HTTPS requests with 10 workers,          |       |

|     | 45B documents, 300 concurrent requests. Error bars show standard          |       |

|     | deviation, which was below 0.9%.                                          | . 93  |

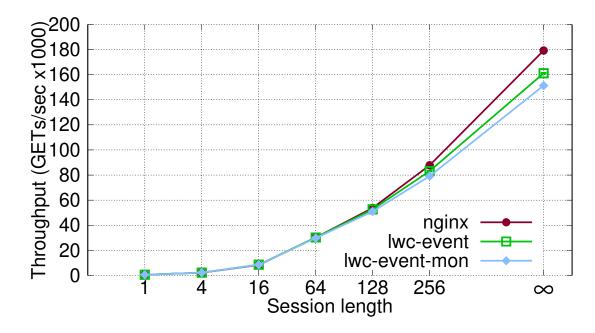

| 4.7 | Nginx cumulative throughput in GETs/sec with 10 workers, session          |       |

|     | length 256, 45B and 900B documents, increasing number of concur-          |       |

|     | rent clients. Error bars show standard deviation                          | . 94  |

|     |                                                                           |       |

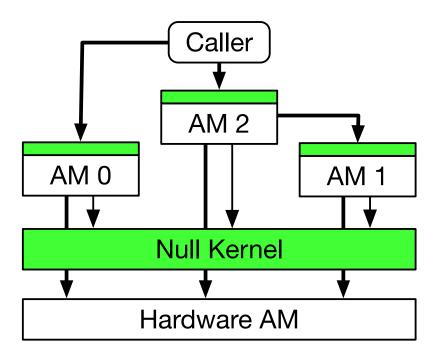

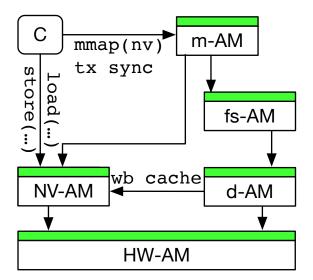

| 5.1 | An overview of the null-Kernel showing system components: the null-       |       |

|     | Kernel, abstract machines, and callers                                    | . 102 |

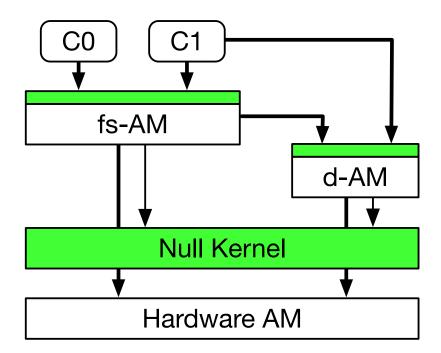

| 5.2 | A representation of a file system AM built on top of and exposing capa-   |       |

|     | bilities for a disk AM.                                                   | . 108 |

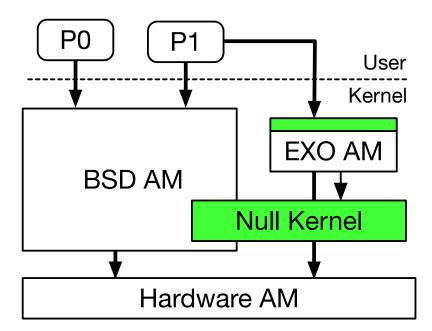

| 5.3 | Architecture for retrofitting the null-Kernel into a BSD system to expose |       |

|     | include safe exokernel like AM                                            | . 110 |

| 5.4 | Achieving direct access / layer bypass with a deconstructed linux         |       |

|     | null-Kernel                                                               | . 116 |

## Chapter 1: Introduction

An operating system (OS) provides a set of abstractions through which access to hardware resources may be granted or multiplexed (virtualized). The design of this set of abstractions is informed by performance, isolation/security, portability, and ease of use constraints. These constraints are often at tension with one another. For instance, maximizing performance, whether it be throughput or latency, and simultaneously maximizing security is difficult if not impossible. Security is typically provided by isolating actors on the system and their data from one another, yet crossing isolation boundaries has a performance cost, which implies an inherent trade-off between performance and security. Similarly, portability, the feature whereby programs can run with little to no modification on different hardware, OS versions, or even different OSes that maintain compatibility, is also at odds with performance and, in some cases, security. Each significant branch of OS architecture discussed below effectively chooses abstractions that impose different priority orderings of these constraints and impose these trade-offs on users. The question we ask is not which OS architecture offers the best abstractions, but rather whether an OS ought to be constrained to a fixed set of abstractions at all.

OSes are often designed to favor one constraint over others. An OS that fa-

vors performance above all else will offer abstractions that give direct or near-direct access to hardware. At the extreme, no OS (or just the hardware interface) is the best OS for performance. The abstractions offered in this case (i.e., the hardware interfaces) impose no overhead or unnecessary abstractions that may inhibit performance, but suffer from three drawbacks: they are non-portable, offer little isolation, and rarely provide a virtualized hardware interface to enable resource sharing. OSes that favor isolation and security will limit the amount of software that runs with elevated privileges and separate as many components as possible into separate domains that may only interact through some supervisory process. In addition to security, isolation may also be used to improve the robustness of the system: the effects of a fault may more easily be contained to the isolated domain, which simplifies recovery. Kernels that prioritize isolation may or may not be portable, but isolation cannot be achieved without some performance cost. Finally, OSes that favor portability necessarily have higher level abstractions, as their abstractions must remain constant as hardware evolves and thus, tend to be represented by high-level models for system resources. This implies both a performance cost, due to mismatches between the hardware and its higher-level abstraction, as well as a cost to security, since the need to maintain abstractions indefinitely hampers improvements in security that may result from improving abstractions to fix deficits or adapt to new hardware and application demands. Exokernels, microkernels, and the monolithic architectures exemplified by UNIX and its descendants tend to prioritize, respectively, performance, isolation, and portability. We discuss these kernels next.

The Exokernel [3] architecture prioritize performance over all other factors.

The interface exokernels provide is often non-portable and very closely matches the hardware, which as argued by Clark et. al [4], enables the widest possible set of application specific optimizations. All other design goals are sacrificed, with ease of use, portability, and isolation sacrificed unless layered with a set of libraries that define high-level abstractions, termed a "library OS," that applications rely on. At the limit, a library OS that prioritizes design goals other than performance will ultimately recapitulate design choices and trade-offs made by other kernel architectures.

Microkernels [5], on the other hand, preference isolation as the over-riding design principle. Liedtke explicitly argues that an abstraction should only be implemented within the kernel (i.e., have direct access to hardware) if the desired functionality cannot otherwise be achieved, leaving performance only as a secondary consideration [6]. Microkernels offer relatively high-level abstractions that are built as a set of userspace services that access hardware via interprocess communication (IPC) with a small privileged kernel. The isolation and high-level abstractions may hamper performance, but microkernels can be portable if the interface provided by the user space services is preserved. Note that user space services are analogous to library OSes, in that both are theoretically replaceable so long as portability is not a concern.

Monolithic kernels, best exemplified by the descendants of UNIX, favor portability. POSIX [7], a standardization of a common set of OS abstractions and basic utilities, specifies a set of abstractions supported by monolithic kernels that remain largely unchanged for over 25 years. These abstractions, which are meant to support a very broad set of hardware and application needs, tend to offer one-size-fits-all abstractions for hardware and applications. A cost of this portability is less flexibility in meeting new application demands that were not considered when the abstractions were standardized, as well as performance loss due to overhead from the OS abstractions that the applications must use. Monolithic kernels do make compromises to mitigate performance costs. They limit isolation, which they may do without affecting portability, which is a practice that leads to their name: almost the entirety of the kernel runs within a single monolithic address-space at increased privilege. Practical concerns do necessitate occasional violations of portability, such as neardirect access to new hardware through an exokernel like interface (e.g., an interface to an ASIC that accelerates machine learning calculations). These exceptions are ad-hoc and do not always interact well with the other abstractions offered by the OS

Each major OS architecture meets its design goals through a set of abstractions that reflect and impose onto applications the priorities of the OS. Applications that want to maximize performance may choose to run on an OS offering direct hardware access (e.g., an exokernel), whereas applications with strong security requirements might be best deployed on OS with stronger isolation (e.g., a microkernel).

New hardware and changing application requirements have given rise to applications with needs that cannot be met with any current OS architecture. Applications can subvert the restrictions of the OS while preserving compatibility, but traditionally this may only be done if the OS itself is modified. Our own work in developing new abstractions has suggested that the trade-off between constraints is not inherent and can be avoided, not by choosing a single ideal abstraction, but instead by simultaneously exposing multiple abstractions for each available resource.

### 1.1 Thesis

Supporting novel hardware such as NVRAM and new abstractions like fine-grained isolation while maintaining efficiency, usability, and security goals, requires simultaneous access to both high-level OS abstractions and compatible access to their low-level decompositions.

Next I will describe the terms in my thesis statement and discuss how they affect OS design.

While there is no precise definition of low-level and high-level abstractions, for the purpose of this dissertation we use low-level abstractions to refer to abstractions that are more similar to the hardware than a higher level abstraction. We consider direct hardware access as a low-level abstraction, and consider all high-level abstractions to be composed of one or more low-level abstractions. High-level abstractions are built on top of one or more low-level abstractions and typically provide greater ease of use, increased portability, or stronger isolation guarantees, but may sacrifice performance. A decomposition of a higher-level abstraction is then the set of all lower-level abstractions upon which the higher-level abstraction is built. Simultaneous access to both a high-level abstraction may be exposed, but each of the lowerlevel abstractions from which it is built should also be exposed and accessible to applications. In the context of the architectures we discussed above, we then describe exokernels as an OS with low-level abstractions and the monolithic kernels discussed above, on the other extreme, as an OS with high-level abstractions. Neither OS consistently exposes both high-level abstractions and their low-level decompositions. This implies that exokernels may be arbitrarily adaptable, but at the cost of usability due to significant implementation effort and loss of portability. Whereas the monolithic kernels and their high-level abstractions give us portability, but at the cost of efficiency that the end-to-end principle suggests is inherent with high-level abstractions. An OS that exported both low and high-level abstractions accommodates a wider set of applications, but care must be taken to do this safely.

The difficulty in exposing low and high-level abstractions simultaneously is one of interference. With few exceptions, all abstractions have a set of invariants that must be maintained for the abstraction to offer a useful contract with its callers. If multiple high-level abstractions are built on top of the same low-level abstraction (e.g., two separate file systems using the same block device) we need some mechanism to prevent interference between different high-level abstractions. A traditional OS achieves this by specifying how abstractions may be used a priori and requiring a supervisory process (i.e., the kernel) to enforce usage. A priori specifications cannot possibly meet the needs of all applications and must have embedded within them their own design trade-offs.

### **1.2** Contributions

As part of the work in evaluating the abstractions necessary to accommodate new hardware and changing application demands, we developed two new abstractions, PTx (Chapter 3) and Light-Weight Contexts (Chapter 4. We also introduced a new OS architecture, the null-Kernel (Chapter 5). Both PTx and Light-Weight Contexts (lwCs) were designed and implemented on production operating systems (FreeBSD and Linux respectively) and required access to traditional high-level OS abstractions, as well as access to non-traditional low-level abstractions to meet their performance goals. Building on our experiences in designing and implementing lwCsand PTx, we propose the null-Kernel architecture, which is an architecture that enables the simultaneous exposure of multiple abstractions for the same underlying resources in a safe way. Under the null-Kernel, the development of new abstractions such as lwCs and PTx would be accelerated, improving application performance and security. The dissertation is structured as follows:

#### Chapter 2: Background and Related Work

We contextualize PTx and lwCs in relation to other work that provides similar functionality. In addition to discussing the abstractions and capabilities of existing systems, we note if and when related work relies on or provides different lowerlevel OS abstractions than PTx and lwCs rely upon. We also discuss common OS architectures and kernel extension mechanisms and discuss the problems these systems are meant to solve and discuss the trade-offs inherent in each of these architectures.

#### Chapter 3: PTx

We describe PTx, which uses a new form of non-volatile memory (NVRAM) to efficiently persist in-core data structures to persistent media. We discuss the consistency and performance challenges one faces when using NVRAM, and how PTx solves these challenges. We evaluate PTx and show that it enables high performance persistence of standard C++ data structures that exceed the performance of data structures explicitly annotated for NVRAM. We also show that PTx can be used to provide persistence to Redis [8], a popular key-value server, with comparable overhead to custom solutions and minimal modification, or provide a compatible server with superior performance within 430 lines of source code.

#### Chapter 4: Light-weight Contexts

We describe Light-weight contexts, which decouples memory isolation, execution state, and privilege separation from within a process. lwCs can be used to provide snapshots, session isolation, reference monitoring, and protected compartments within a process. We evaluate lwCs with a series of micro-benchmarks and application scenarios and show that lwCs can provide enhanced security with low overhead or improve performance with its snapshot facility.

#### Chapter 5: The null-Kernel

PTx and lwCs both showed that existing OS abstractions were insufficient to deal with new hardware and increased security demands. We found that both systems could be implemented by exposing and then making use of lower-level abstractions, while portability concerns dictated that we preserve existing higher-level abstractions. To generalize the constraints that we observed while building these systems, we developed the null-Kernel, a model for describing existing OS architectures and suggest new OS paradigms to support the simultaneous exposure of low-level and high-level abstractions. We discuss how simultaneous exposure of abstractions provides new opportunities for improving performance and security and place PTx and lwCs in the null-Kernel context.

#### Chapter 6: Conclusion and Future Work

We conclude by revisiting the contributions of this work. We discuss future opportunities for improving PTx, both in terms of optimizations, as well as extensions to functionality. We also discuss combining PTx and lwCs to create a form of persistent lwC. Finally, we discuss the steps we have taken towards exposing lowerlevel abstractions within FreeBSD to userspace and thus, bring FreeBSD closer in line to a null-Kernel architecture.

## Chapter 2: Background and Related Work

In this chapter we discuss related work for persisting state to NVRAM, decoupling process primitives, such as isolation, and improving OS flexibility to hasten the development of new abstractions for differing application requirements and new hardware.

### 2.1 Abstractions for NVRAM

The price/performance characteristics of NVRAM make it an attractive new point in the storage hierarchy. Currently available NVRAM can be operated in one of two modes: *memory* and *direct*. In memory-mode, conventional DRAM is used as a cache for data stored in NVRAM, affording several TB of main memory at reasonable cost with performance close to DRAM for workloads with good locality. In this mode, NVRAM is used for its byte addressability and low cost per byte; the memory controller actively defeats persistence in this mode for security reasons, by encrypting data and destroying the keys during a system restart.

In direct mode, NVRAM appears directly in the system's physical address space and can be accessed with conventional load and store operations, albeit at reduced performance compared to DRAM. Note that in this mode, once a NVRAM page is mapped, loads and stores can be completed without OS intervention (i.e., without any abstraction overhead). Current commercially available NVRAM has higher latency (3.7x slower) and lower bandwidth when the bus is saturated (1/3 and 1/6 of DRAM read and write bandwidth respectively) [9].

Operating systems expose direct-mode NVRAM in one of two configurations. In the first configuration, the OS wraps NVRAM in a block device abstraction, which is then accessed through a filesystem interface. Applications access the data through the usual filesystem API, which has no bearing on the application other than increased performance. In the second configuration, which PTx relies on, the OS maps NVRAM directly into an application's address space through the mmap interface and applications modify persistent state through memory operations. This latter form is a lower-level interface, which allows for higher performance.

Directly-mapped NVRAM by itself, however, does not provide immediate nor atomic persistence. NVRAM accesses are subject to the same caching layers as DRAM. Writes to mapped NVRAM are not automatically flushed to NVRAM and thus, not persisted, until evicted from the CPU caches. A process may evict (and thus persist) cache lines as needed, or applications may explicitly push writes to NVRAM either via flush and fence instructions or via special instructions that bypass the cache. In either case, temporally proximate and spatially contiguous writes are combined by the hardware and written to NVRAM with an effective block size of 256 bytes. Regardless of the method chosen, persistence must be programmed carefully to ensure that the persisted structure is in a consistent state, and thus fault-tolerant, at all times, and that the NVRAM accesses are efficient. Failure to do so can lead to very subtle, hard-to-detect and hard-to-recover-from bugs.

While an application can use the lower level direct-mapped NVRAM directly to implement persistent data structures in principle, doing so is challenging both in terms of performance and correctness. The application needs to carefully manage data access locality and write amplification for performance, as well as use explicit barriers and cache flush instructions carefully throughout. Failure to use these instructions appropriately may result in inconsistent persistent states where the program fails in specific states, which is very difficult to debug. Our work will offer a higher-level abstraction that is different from the file system interface and reliant on access to lower-level abstractions.

In the rest of this section, we describe prior work on using NVRAM, both as a filesystem and for providing persistence. We also discuss existing solutions for persistence, and compare them to PTx.

**NVRAM file systems** Several file systems take advantage of the performance characteristics and byte addressability of NVRAM [10–12]. Just as file systems act as a namespace to provide a handle to disk resources, an NVRAM file system can be used to label NVRAM resources that can be mapped into the process address space. The file system interface is a familiar one for programmers seeking persistence, but it does impose overhead. At minimum, reading and writing to an NVRAM file require system calls that copy data from NVRAM to and from DRAM.

Both NOVA-Fortis [10] and PMFS [11] allow applications to map the NVRAM

data pages for a file directly into the application's address space. This feature, which the Linux EXT and XFS file systems also provide, is known as "direct-access," (DAX). DAX allows applications to modify file contents directly through CPU load and store directions, and as such grant lower-level access to the hardware. NVRAM file systems that do not support or are not DAX mapped support memory mapping like traditional file systems: with a buffer cache. The OS pages data onto DRAM from NVRAM on demand and writes all modified DRAM pages to NVRAM either opportunistically or when msync is called. Implementing persistent data structures through file system mappings shares the challenges described above. PTx, which offers an alternate high-level abstraction, relies on DAX mappings to read and write to NVRAM internally but does not expose the mappings directly to applications.

**NVRAM aware data structures** Many prior systems have provided persistence using bespoke NVRAM aware data structures [13], such as customized b+-trees [14, 15], radix trees [16], key value stores [17, 18], hash tables [19, 20], and write-ahead logging [21, 22]. PTx instead enables efficient persistence for legacy data structure implementations without annotation or modification to the data structure source code.

**Transactional Memory and Semantics** Transactional memory was introduced as a method of concurrency control. In this context, serializability and isolation between threads are key requirements, while durability is irrelevant because transactions are performed on volatile DRAM. Similarly, transactions for concurrency control tend to be short to enable fine-grained concurrency (e.g., add an item to a data structure).

More recently, transactional memory has been used as an abstraction for atomic updates to persistent memory, such as NVRAM. Here, atomicity with respect to failures is the key property: updates to persistent state must be applied in their entirely or not at all. Isolation between threads for concurrency control may or may not be provided. In this context, transactions tend to be larger as they may include updates to multiple data structures that must be applied atomically to maintain invariants application-wide, not just within a single data structure

Many persistent memory systems use a transaction abstraction [23–30] or an *atomic* keyword [31] to delineate state changes that must be persisted atomically. Some of these systems operate much like transactional memory systems for concurrency control, and provide concurrent consistency [23, 25, 27], whereas others [26, 28, 31], like PTx, expect applications to use external concurrency primitives for thread isolation within a process.

Transactional memory systems implement crash atomicity using logging. Systems that use undo logging [25–27] copy to-be-modified state to persistent memory before allowing modifications to occur. Applications then make modifications in place (i.e., directly in NVRAM) within a transaction. The undo log is only used to recover from a fault. Other systems use redo logging [31] and write updates to a redo log, to be applied to the main persistent store upon commit. Within a transaction, reads are redirected so that they read the proper values from the redo log. Pronto [32] wraps operations on data structures and asynchronously logs operations

and their arguments that may be replayed against the data structure API in the event of a failure.

Intel's persistent memory toolkit (PMDK) [26] provides a transactional interface that uses a combination of undo and redo logs to provide atomicity. Like PTx, PMDK does not provide isolation between threads, but unlike PTx, PMDK writes directly to NVRAM and requires programmer annotations to indicate the write set.

DudeTM [23] attempts to limit both the overhead caused by modifying NVRAM within a transaction, as well as the overhead incurred from the redo log indirection. Towards this end, DudeTM performs modifications on shadow DRAM pages and writes a redo log in volatile memory. As part of commit, the volatile redo log is flushed to NVRAM and subsequently, the persistent redo log is applied to the persistent data. PTx also makes all modifications to volatile shadow pages, but does not maintain an explicit redo or undo log. Instead, the PTx log structure enables writing a comparatively succinct undo log as a set of updates to the mapping between DRAM and NVRAM addresses.

Ni et al. [28] propose a design that also eliminates explicit undo logs, by atomically updating mapping information upon commit, but their approach relies on hardware modifications. Hu et al. [33] also use a log structure for data in NVRAM. New allocations are appended to the log and reads and writes are intercepted and redirected so that they act directly on the log. PTx does not require interception of reads and writes, and PTx's log does not require periodic cleaning due to fragmentation. Correia et al. [34] present a persistent transactional memory system based on universal constructions. Their work eliminates blocking transactions, but either requires code annotation or flushing all the memory where the data structure resides upon commit. This over-approximation of the write set is prohibitive for transactions over large data structures.

### 2.2 Decoupling Process Abstractions

Privacy-compromising exploits, such as Heartbleed [35], suggest that existing isolation abstractions, such as processes, either do not meet current isolation requirements, or do not meet them with sufficient expressiveness of performance. lwCs take the process abstraction, and decouples the isolation, scheduling, and privilege properties traditionally provided by a process and uses them to offer new abstractions that provides for strong, finer-grained isolation with minimal performance overhead, as well as snapshots and reference monitoring. Other systems also revisit lower-level aspects of the process abstraction and put them to new use, which we discuss now.

Wedge [36] provides privilege separation and isolation among *sthreads*, which are a new unit of encapsulation for an application. The program is split up into a series of sthreads, which by default share little to no state, and regions of computation gated by callgates. Each callgate is associated with an sthread, and whenever another sthread attempts to invoke a callgate (i.e., enter a protected region of computation), the caller thread is blocked and the sthread associated with the callgate is scheduled to execute the gated code, potentially while accessing protected state, and return a value back to the calling thread. Unlike lwCs, scheduling and isolation are still coupled in Wedge, but sthreads are a finer unit of isolation than a process and have a similar goal of protecting sensitive parts of a program's execution. lwCs are orthogonal to threads and therefore avoid the cost of scheduling when switching contexts. Moreover, lwCs can snapshot and resume an execution in any state, while a sthread can only revert to its initial state. Wedge provides a software analysis tool that helps refactor existing applications into multiple isolated compartments. lwCs could benefit from a such a tool as well.

Shreds [37] builds on architectural support for *memory domains* in ARM CPUs, a compiler toolchain, and kernel support to provide isolated compartments of code and data within a process. Like lwCs, shreds provide isolated contexts within a process. lwCs, however, are fully independent of threads, require no compiler support, and rely on page-based hardware protection only. lwCs also provide protection rings and snapshots, which shreds do not.

In SpaceJMP [38], address spaces are first-class objects separate from processes, which demonstrates broader utility for lower-level address space abstractions that are decoupled from the process. While both systems can switch address spaces within a process, SpaceJMP and lwCs provide different abstractions, capabilities, and are motivated by entirely different applications. SpaceJMP supports applications that wish to use memory larger than the available virtual address bits allow, wish to maintain pointer-based data structures beyond process lifetime, and share large memory objects among processes. A SpaceJMP context switch is not associated with a mandatory control transfer and, therefore, SpaceJMP does not support applications that require isolation or privilege separation within a process. lwCs, on the other hand, provide in-process isolated contexts, privilege separation, and snapshots. It should be noted, however, that the SpaceJMP address space abstraction is a low-level abstraction that is similar to the address space abstraction proposed in Section 5.5 for supporting new isolation abstractions in the null-Kernel, and in concert with other abstractions for managing control flow, could be used to provide isolation.

In Trellis [39], code annotations, a compiler, run time, and OS kernel module provide privilege separation within an application. The kernel and runtime ensure that functions can be called and data accessed only by code with the same or higher privilege level. lwCs provide privilege separation without language/compiler support, and can switch domains at lower cost. Moreover, lwCs additionally support snapshots.

Switching among lwCs is similar to migrating threads in Mach [40], where they were implemented to optimize local RPCs. Migration of threads across address spaces is also an element of the model described by Lindström et al. [41] and the COMPOSITE OS [42]. In single address space operating systems (SASOS) like Opal [43] and Mungi [44], all processes as well as persistent storage share a single large (64-bit) address space. Unlike lwCs, these systems do not provide privilege separation, isolation, or snapshots within a process.

Mondrian Memory Protection (MMP) [45] and Mondrix [46] use hardware extensions to provide protection at fine granularity within processes. The CHERI [47, 48] architecture, compiler, and operating system provides hybrid hardware-software object capabilities for fine-grained compartmentalization within a process. lwCsprovide in-process isolation at page granularity without specialized hardware or language support.

Resource containers [49] separate the unit of resource accounting from a process and account for all resources associated with an application activity, even if the activity requires processing in multiple processes and the kernel. Resource containers decompose task accounting from processes. lwCs are orthogonal to resource containers and as such, do not make use of accounting decomposition.

The Corey [50] OS provides fine-grained control over the sharing of memory regions and kernel resources among CPU cores to minimize contention. These lower-level abstractions are orthogonal to the capabilities of in-process isolation, privilege separation, and snapshots provided by lwCs.

Light-weight isolation, privilege separation, and snapshots can be provided also within a programming language. Functional languages like Scheme and ML provide closures through the primitive call/cc, which can be used to record a program state and revert to it later, and to implement co-routines. Typed object-oriented languages like C++ and Java provide *static* isolation and privilege separation through private and protected class fields but do not isolate objects of the same class from each other. *Dynamic* language-based protection, often implemented as object capabilities [51–53], provides fine-grained isolation and privilege separation but has considerable runtime overhead. lwCs instead provide in-process isolation, privilege separation, and snapshots at the OS level, independent of a programming language.

In low-level languages like C, isolation and privilege separation can be attained using binary rewriting and compiler-inserted checks as in CFI [54], CPI [55] and secure compilation [56]. All these techniques rely on dynamic checks that have runtime overhead. Techniques such as CPI and secure compilation rely on OS support for the isolation of a reference monitor, which *lwCs* can provide at low cost. ERIM [57] uses binary inspection in concert with Intel's memory protection keys to provide memory isolation between contexts with minimal overhead. While ERIM provides similar virtual memory isolation, it does not provide isolation for file tables or privilege.

Software fault isolation (SFI) [58] and NaCl [59] rely on static checking and instrumentation of binaries to isolate memory within applications running on unmodified operating systems. SFI and NaCl do not selectively protect system calls and file descriptors. lwCs instead allow fine-grained control over memory, file descriptors and other process credentials, and provide snapshots as part of an OS abstraction.

Process checkpoint facilities create a linearized snapshot of a process's state [60–63]. The snapshot can be stored persistently and subsequently used to reconstitute the process and resume its execution on the same or a different machine. Checkpoint facilities are used for fault-tolerance and load balancing. lwCs instead provide very fast in-memory snapshots of a process's state.

The Determinator OS [64] relies on a private workspace model for concurrency control, which enables deterministic execution on multi-core platforms. To support the model, Determinator provides *spaces*, in which programs mutate private copies of shared objects. Like lwCs, spaces provide isolated address spaces. Unlike a lwC, however, a space is tied to one thread, does not have access to I/O or shared memory, and can interact only with its parent and only in limited ways. Intel's Software Guard Extensions (SGX) [65] provide ISA support to isolate code and data in *enclaves* within a process. By mapping contexts to enclaves, SGX could be used to harden lwCs against a stronger threat model (untrusted OS) and to provide hardware attestation of contexts. However, enclaves have no access to OS services, so some lwC applications would need considerable re-architecting to run on SGX.

NOVA [66] provides protection domains (separate address spaces) and execution contexts (an abstraction similar to threads) in a micro hypervisor. NOVA's goal is to isolate VMMs and VMs from the core hypervisor, which is different from lwC's goal of providing isolation, privilege separation, and snapshots within processes.

Dune [67] provides a kernel module and API that export the Intel VT-x architectural virtualization support safely to Linux processes. This is akin to a form of layer bypassing supported by null-Kernel that allows low-level access to hardware, but this access is virtualized. The low-level interface granted is not a decomposition of abstractions used by higher-level abstractions, but is instead disjoint from the higher-level abstractions. Consequently, while privilege separation, reference monitors, and isolated compartments can be implemented within a process using Dune, these abstractions cannot be seamlessly integrated with the kernel's existing abstractions. lwCs, by contrast, instead provide a unified abstraction and API for these capabilities, and their implementation does not rely on virtualization hardware, the use of which could interfere with execution on a virtualized platform.

### 2.3 Improving OS Flexibility

VINO [68] and SPIN [69] offer mechanisms to safely extend monolithic kernels. Both systems require extensions to be written against a restricted, internal interface that maintains kernel invariants. These systems can be thought of as a limited instantiation of the hybrid system presented earlier, but access to the internal interface cannot be shared in a structured manner. This limits how extensions (AMs) relate:for instance, layer bypassing is not possible in either.

Microkernels [6] seL4 [70] and Barrelfish [71] export kernel objects to user space as capabilities. Capability types exported by the system are static. As a result, layer bypassing via delegated capabilities is not supported.

Exokernels [3] provide a minimal, non-portable hardware-like interface. Exokernel abstractions allow for the allocation and revocation of hardware resources in a manner similar to capability allocation, but unlike capabilities, these resources cannot be shared or reduced except by proxying through the resource owner.

EROS [72], derived from KeyKOS [73], is a stateless kernel that maps hardware into a set of capabilities. Applications use the operations permitted by these capabilities to construct higher level abstractions. EROS is equivalent to a specific instantiation of the null-Kernel that only exports a low level AM. HiStar [74] also exposes a limited set of kernel objects to user space, limiting access to those objects by tracking information flow.

The Cal timesharing system [75], Cambridge CAP computer [76] and Fluke [77] all allow an interface's operations to be implemented and over-ridden in a nested

manner that is similar to subclasses. This layering is constrained by capabilities. Unlike the null-Kernel, the interface for these interfaces is fixed.

## Chapter 3: PTx

In this chapter we discuss PTx, a new abstraction for efficiently persisting incore data structures to a new form of byte addressable and persistent non-volatile RAM (NVRAM).

## 3.1 Introduction

Non-volatile RAM (NVRAM) is a newly available memory technology that may have profound impact on both system hardware and software structure. The reason for this impending shift is that NVRAM has a cost/byte and speed between DRAM and Flash memory, is byte-addressable via unprivileged CPU instructions, and *persistent*. Thus NVRAM promises to combine the best features of DRAM (directly addresseable/memory mapped, performance) with those of disk/solid state memory (persistence, relatively low cost per byte).

We focus on the potential for NVRAM to enable persistent data structures. For example, an in-memory database could persist on NVRAM, obviating the need to save modified data on an external storage device for persistence. As a result, NVRAM has the potential to significantly reduce the cost of persisting state, enabling higher performance for a given granularity of transactions, or enabling more fine-grained transactions at a given level of performance.

There are two primary challenges when using NVRAM for persisting process state. First, performance: when saturated, NVRAM writes are ~6x slower than DRAM writes [9], which generally precludes using NVRAM as a direct replacement for DRAM. Instead, NVRAM is used as a backing store for DRAM and writes to NVRAM must be minimized for efficiency. Minimizing extraneous NVRAM writes is simple for some specific data structures, such as an append-only log. In general, however, it requires appropriate techniques for determining which parts of a process's state need to be persisted and which parts of that state were modified as part of a transaction. Performance also requires a design that minimizes NVRAM write amplification, i.e., modified data should have to be written only once per commit in the common case.

The second challenge is consistency: Processes may crash at any point in their execution, and even if all memory writes are saved, the restored state may not be consistent if the failure occurs when invariants on the application's state don't hold. For instance, an application-level transaction may involve modifications to multiple data structures that need to be performed atomically. Restored state must satisfy not only the individual data structures' invariants, but also invariants across the application state. Moreover, without additional information about the failed operation, it may be impossible to return to a consistent state without loss of information.

We introduce PTx, a userspace persistence library specialized for the perfor-

mance and atomicity needs to persist data structures to NVRAM. PTx enables programs to achieve failure atomicity for arbitrary code sequences simply by bracketing them with primitives to begin and end a transaction. No further annotation is required on code executing inside a transaction; in particular, existing unmodified data structure libraries can be invoked as part of a transaction, thus transparently persisting these data structures. While executing inside a transaction, the program can access data at DRAM speed. When ending the transactions, PTx persists the transaction atomically while minimizing the number of NVRAM writes required.

As discussed in Section 2.1, state-of-the-art, high-performance persistent data structures require manual annotation of individual memory writes, so that these changes can be written to persistent storage efficiently. We introduce several high performance automatic change trackers, which relieve the programmer from having to annotate source code to track changes. PTx trackers are akin to existing compilerbased mechanisms, such as those developed for Software Transactional Memory [78, 79], but provide much higher performance.

Because data accesses within a PTx transaction proceed at DRAM speed, existing data structures not designed for the reduced access speed of NVRAM may be used without penalty and subsequently persisted efficiently. Finally, PTx persists data in NVRAM using a data structure that supports non-destructive writes, avoiding unnecessary and costly NVRAM writes and the need for log cleaning/compaction. The combination of automatic, language independent write-set tracking, DRAM-speed data access within a transaction, and low NVRAM write amplification enables PTx to efficiently persist existing data structure implementations, without modifying their source code and even when transactions are large.

We experiment with persisting the standard C++ STL data structures [80]. With PTx automatic tracking, these structures can be made transparently persistent, and perform close to their native DRAM speeds. This allows PTx to match or exceed the query throughput of custom, hand optimized systems, such as LMDB, Redis, pmem-Redis, and previously developed NVRAM data structures, all of which require manual annotations to track changes.

This chapter is organized as follows: we provide a technical background on NVRAM and discuss related work in Section 2.1. The design of PTx, including its persistent data structures and algorithms is presented in Section 3.2. We discuss implementation specifics in Section 3.3. Section 3.3 contains a comprehensive evaluation of PTx and a comparison to several other persistence libraries and applications.

# 3.2 PTx design

#### 3.2.1 Requirements

PTx aims to enable persistent in-core data structures for *existing* systems and applications, without requiring extensive changes to code. An application should be able to link to the PTx library, map persistent memory objects into the application's address space using PTx's API, use the PTx memory allocator to allocate additional persistent memory dynamically. The programmer should be able to bracket sequences of operations on state that should be persisted atomically with transaction start and commit primitives as required. Any existing persistence mechanism within the application can be disabled. (Such a mechanism typically serializes and explicitly writes its persistent state to an external storage device, or invokes sync operations on memory-mapped files at appropriate points in its execution.) Due to the greater efficiency afforded by PTx and NVRAM, the application can benefit from increased performance, or persist its state more frequently. To realize this vision, PTx has the following design constraints:

**DRAM-speed data access:** Existing data structure implementations designed for DRAM may perform poorly on NVRAM. For instance, fine-grained writes get amplified to 256-byte block writes. Therefore, accesses within a transaction should be performed on DRAM.

Automatic write set tracking: Since existing data structure implementations don't explicitly state their write sets, we need to rely on automatic techniques to determine them. These techniques must reliably capture all modified state for correctness, without significantly over-approximating the write set.

Low write amplification: Applications are typically interested in persisting states that correspond to completed application-level transactions, not mutations of individual data structures. Therefore, transactional updates to persistent state are typically larger than memory transactions used for concurrency control. Efficiently supporting such transactions requires low amplification of NVRAM writes, i.e., modified data should be written only once per commit and at the 256 byte granularity of NVRAM.

### **3.2.2** PTx colors and operations

PTx supports multiple memory pools called *colors*. Each color is backed by an NVRAM file with separate access permissions. An application can map multiple colors for which it holds permissions into its address space. Each color has a separate dynamic memory allocator. PTx transactions operate on a single color, allowing applications to persist data of any one color atomically. Applications may also allocate memory in different colors and transact on them separately.

The PTx library exports four operations that each operate on a color c:  $ptx\_malloc (c)$  allocates persistent memory associated with a particular color.  $ptx\_begin$  (c) starts a transaction on a color,  $ptx\_commit (c)$  commits a transaction, and  $ptx\_restore (c)$  rolls back the color to the last committed state. Note that  $ptx\_restore$  (c) can be used at the start of a program execution to reinstate the last committed state of a color, or during execution to abort an uncommitted transaction on a color. We call the data of a given color persisted via a commit a *snapshot*. Later instantiations of the application or other applications may restore the latest snapshot of a given color into their address space by calling  $ptx\_restore()$ .

At runtime, PTx stores persistent data in main memory, which the application may read or write at DRAM speed. The "write set" represents the set of locations within a color that were modified within a transaction. PTx uses "trackers" to determine the write set, as described in Section 3.2.6. When the application invokes  $ptx\_commit()$ , the write set is written to NVRAM atomically.

At any time, the application, a later instantiation of the same application, or

a different application with appropriate permissions may restore the last committed state of a memory pool into its address space using  $ptx\_restore$  (c).

## 3.2.3 PTx Semantics

PTx transactions are committed atomically with respect to failures of applications and systems. From an application's perspective, a persistent memory pool ("color") is either updated entirely or not at all as part of a commit. Critically, this implies that as long as a memory pool's invariants hold at the time of a **commit** call, those invariants will hold after a system fault/recovery. An application may persist multiple data structures by allocating them using the same color, and different processes may simultaneously map the same color into their address spaces.<sup>1</sup>

PTx provides atomicity, durability, and consistency/isolation between processes (but not threads). The semantics provided by PTx are similar to ACID transactions at the level of processes. However, PTx transactions do not provide concurrency control among different threads of a process. Such synchronization normally occurs at a different granularity as PTx transactions and doesn't require atomic persistence. To synchronize among threads of the same process, an application must use a separate mechanism, such as locks or conventional transactional memory.

<sup>&</sup>lt;sup>1</sup>Our PTx prototype does not currently support concurrent mappings of a color by multiple processes.

### 3.2.4 PTx storage

Next we describe the storage components of PTx's design, namely the *data layer*, the *log*, and the *map*.

**PTx data layer:** The data layer stores persistent data and associated metadata in NVRAM. It must do so efficiently and maintain the ability to recover in the event of system failures. Towards this end, the store performs non-destructive data writes and minimizes write-amplification by allowing modified data to be written only once per transaction.

The data layer is organized as an array of fixed sized blocksets in NVRAM. Each blockset contains space for 41 data blocks of 256 bytes each, plus an additional 256 bytes for metadata. During a commit, PTx writes modified data into available data blocks in the data layer. The unit of allocation is a data block, although PTx seeks to allocate entire blocksets when possible. Note that the blocks of a data structure are typically stored non-contiguously in the data layer. Because NVRAM can sustain random block accesses with little or no performance degradation, there is no need for cleaning or compaction, which would create overhead and increase write amplification.

**PTx log:** A small, persistent circular log is used to support atomic transactions whose write set does not fit into a single blockset. The log holds metadata about a transaction during a commit; specifically, the transaction's sequence number, and the set of data blocks written as part of the transaction, followed by a hash. In case of a system failure before the hash is written, the information in the undo log is

used to free uncommitted data blocks in the data layer and add them to the free list.

**PTx map:** The map associates virtual addresses of data blocks in an application's address space with addresses in the data layer, where the last committed state of the block is stored. In the NVRAM, the map is distributed over the metadata blocks of the data layer. During execution, a copy of the map, organized as a range tree for efficiency, resides in main memory for efficiency. During a system restart, the in-memory range tree is reconstituted from metadata in the data layer.

**PTx free list:** The free list is an in-memory data structure that indicates which blocks in the data layer are free. Like the in-memory map, it is reconstituted during a system (re-)start from the data layer metadata.

## 3.2.5 PTx primitives

| Function                                                  | Description                               |

|-----------------------------------------------------------|-------------------------------------------|

| $BlockLocation \leftarrow getFreeBlock()$                 | returns free BlockLocation                |

| $\perp \leftarrow \text{freeBlock}(\text{BlockLocation})$ | sets BlockLocation to be empty            |

| $\perp \leftarrow copyToBlock(VAddr, BlockLocation)$      | copies Data from VAddr into BlockLocation |

| $\perp \leftarrow copyToVAddr(BlockLocation, VAddr)$      | copies Data from BlockLocation into VAddr |

| $\perp$ Object.persist()                                  | Flushes calling object to NVRAM           |

Table 3.1: Auxillary functions used in PTx

Next, we describe the PTx primitives. Basic data types and global structures are defined in Algorithm 1, auxiliary functions are defined in Table 3.1. Here, we assume that a write of an individual data block to the NVRAM (*Object.persist()* in Table 3.1) is atomic with respect to system failures. We discuss in Section 3.2.7