# FPAA BASED DESIGN AND IMPLEMENTATION OF SPROTT N CHAOTIC SYSTEM

### Serdar Çiçek

Nevşehir Hacı Bektaş Veli University, Vocational School of Hacıbektaş, Department of Electronic and Automation, Hacıbektaş, Nevşehir, Türkiye

serdarcicek@gmail.com; serdarcicek@nevsehir.edu.tr

#### Abstract

Nowadays, chaotic systems are used in various studies of different disciplines. Today, chaotic systems are used in various studies of different disciplines. In the literature, chaotic systems with various features have been introduced up to the present. In order to use these new chaotic systems in real-world engineering applications such as encryption, secure communication and authentication, they must be realized besides numerical simulations. In the literature, analog chaotic system implementations have been realized mainly with OPAMP devices. FPGAs and microcontrollers are used mostly in digital designs of chaotic systems. In this study, FPAA (Field Programmable Analog Array) based design and realization of Sprott N chaotic system was carried out. FPAA based design and numerical simulation results confirmed each other. As a result, it has been shown that the Sprott N chaotic system can be used based on FPAA in various engineering applications.

Keywords: Chaotic system, Sprott N chaotic system, FPAA

### 1. Introduction

Chaotic systems have been used in different disciplines since they were first noticed. Chaotic systems are especially used in areas such as secure communication [1, 2], encryption [3, 4], authentication [5, 6] and optimization [7, 8]. In addition, many chaotic, hyper chaotic and multi-scroll chaotic systems have been introduced in the literature. Some of these introduced systems have only been examined numerically and have not been realized. However, these chaotic systems must be designed as analog circuits or digital circuits (embedded system) in order to be used in real engineering applications. For this purpose, different designs and approaches are available for the realization of chaotic systems. OPAMP is generally used in analog circuit designs [9-11]. In digital designs, FPGA (Field Programmable Gate Array) [12, 13] and microcontroller [14, 15] usage is more.

Digital designs can be easily redesigned and programmed according to analog designs. But in digital designs, the system needs to be digitized. FPAA (Field Programmable Analog Array) is used when analog design of chaotic systems and easy reprogramming of the system is desired. FPAA is an embedded system product based on switched-capacitor technique. FPAA includes configurable analog blocks (CABs) to perform the desired analog operations. In the design software developed by the manufacturer, configurable analog modules (CAMs) for various functions are prepared and presented to the users. [16]. The use of FPAA in the realization of dynamical systems provides more efficient and small-scale designs [17]. There are studies in the literature on FPAA based realizations of various chaotic systems [16-23].

In 1994, Sprott introduced 19 new three-dimensional algebraically simple chaotic systems [24]. These chaotic systems are named from A to S. In this study, FPAA based design of Sprott N chaotic system is examined.

In this study, firstly numerical analysis results of Sprott N chaotic system were obtained. Afterwards, FPAA based design and implementation of Sprott N chaotic system was performed. The numerical analysis results of the Sprott N chaotic system and the FPAA based realization results confirmed each other.

# 2. Numerical Simulation of Sprott N Chaotic System

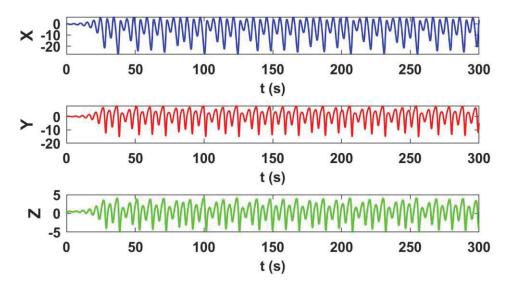

In this section, numerical results of Sprott N chaotic system were obtained in Matlab-Simulink program. The mathematical model of Sprott N chaotic system is given in Eq. 1. The system (1) contains a total of six terms. One of these terms is a nonlinear term and one is a fixed term. The outputs of the *x*, *y* and *z* state variables obtained as a result of numerical calculation in Matlab-Simulink program are given in Figure 1. The initial conditions of the system (1) were taken as  $(x_0 = 0, y_0 = 0, z_0 = 0)$ .

$$\dot{x} = -2y$$

$$\dot{y} = x + z^{2}$$

$$\dot{z} = 1 + y - 2z$$

(1)

#### 3. Scaling of Sprott N chaotic system

The operating voltage of the input/output pins of the FPAA is maximum  $\pm 3V$ . However, as shown in Figure 1, the state variable outputs of the system (1) are above  $\pm 3V$ . Therefore, the system must be scaled according to the FPAA input/output voltage values. Scale ratios are given in Eq. 2. In the scaled system, the new state variables names are given as *u*, *v* and *w*. Mathematical model of the scaled system obtained as a result of scale operation is given in Eq. 3.

$$u = \frac{x}{12}, \quad v = \frac{y}{9}, \quad w = \frac{z}{3}$$

$$\dot{u} = -1.5v$$

$$\dot{v} = 1.33u + w^{2}$$

$$\dot{w} = 0.33 + 3v - 2w$$

(2)

(3)

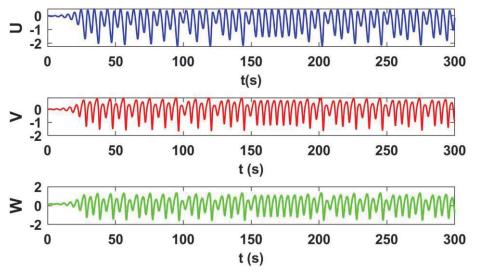

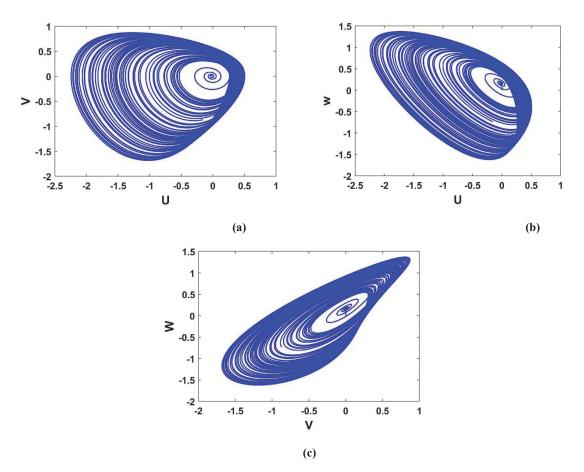

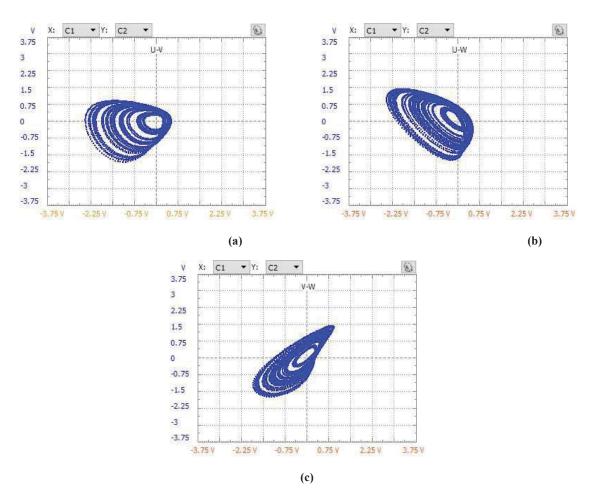

The outputs of the u, v and w state variables obtained as a result of numerical calculation in Matlab-Simulink program are given in Figure 2. As can be seen from the Figure 2, the outputs of the state variables of the scaled Sprott N chaotic system (3) has reached the voltage limits required for the FPAA device. The phase portraits of the scaled Sprott N chaotic system (3) are given in Figure 3.

Figure 2: Numerical calculation results of state variables of scaled Sprott N chaotic system (3) in Matlab-Simulink program

Figure 3: Phase portraits of scaled Sprott N chaotic system (3) in Matlab-Simulink program (a) u-v (b) u-w (c) v-w

# 4. FPAA Based Design and Implementation of Sprott N Chaotic System

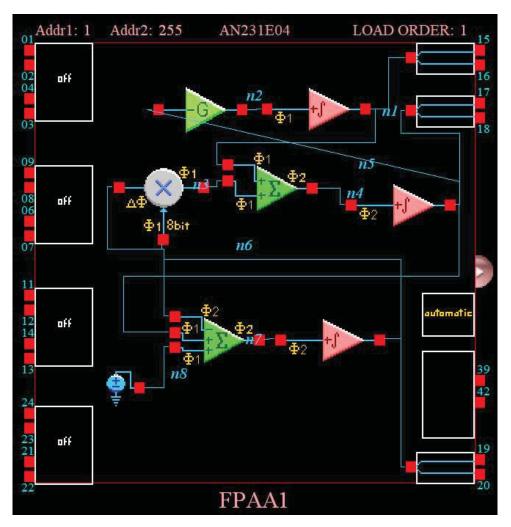

In this part of the study, FPAA based design and implementation of the scaled Sprott N chaotic system (3) is performed. In the design, the Quad Apex v2.0 FPAA development board of Anadigm was used. AnadigmDesigner2 program developed by Anadigm was used for FPAA design. Figure 4 shows the circuit of FPAA based design of the system (3). The parameter values of the CAMs used in the design are given in Figure 5.

Figure 4: FPAA design circuit of the system (3)

Sprott\_N.ad2 - AnadigmDesigner2

### **Configurable Analog Modules: FPAA1**

| Name                                     | Opti                                | ons                      | Parameters                           | Clocks                                    |

|------------------------------------------|-------------------------------------|--------------------------|--------------------------------------|-------------------------------------------|

| Integrator1<br>(Integrator v1.1.1)       | Polarity<br>Input Sampling<br>Phase | Non-inverting<br>Phase 1 | Integration Const.<br>[1/us] 0.00250 | ClockA 250 kHz (Chip<br>Clock 3)          |

|                                          | Compare<br>Control To               | No Reset                 |                                      |                                           |

| Anadigm<br>(Approved)                    |                                     |                          |                                      |                                           |

| GainInv1<br>(GainInv v1.0.1)             |                                     |                          | <b>Gain</b> 1.50                     | ClockA 250 kHz (Chip<br>Clock 3)          |

| -G-                                      |                                     |                          |                                      |                                           |

| Anadigm<br>(Approved)                    | 9050 p.c. (897)-66.0                |                          |                                      |                                           |

| SumDiff1<br>(SumDiff v1.0.1)             | Output Phase                        |                          | Gain 1 (UpperInput) 1.33             | ClockA 250 kHz (Chip<br>Clock 3)          |

| 1 (1) (1) (1) (1) (1) (1) (1) (1) (1) (1 |                                     | Non-inverting            | Gain 2 (LowerInput) 1.00             | CIUCK SJ                                  |

| - <u>Σ</u>                               |                                     | Non-inverting            |                                      |                                           |

| <b>91</b>                                | Input 3<br>Input 4                  | Off<br>Off               |                                      |                                           |

| Anadigm<br>(Approved)                    | Input 4                             | 0 <u>j</u> j             |                                      |                                           |

| Multiplier1<br>(Multiplier v1.0.2)       | Sample and<br>Hold                  | 0ff                      | Multiplication Factor 1.00           | ClockA 250 kHz (Chip<br>Clock 3)          |

| 41 Obr                                   |                                     |                          |                                      | ClockB <sup>4</sup> MHz (Chip<br>Clock 0) |

| Anadigm<br>(Approved)                    |                                     |                          |                                      |                                           |

| Integrator2                              | Polarity                            | Non-inverting            | Integration Const. 0.00250           | ClockA 250 kHz (Chip                      |

| (Integrator v1.1.1)                      | Input Sampling<br>Phase             | Phase 2                  | [1/us] 0.00220                       | Clock 3)                                  |

| ■ <sub>⊕2</sub> +J ■                     | Compare<br>Control To               | No Reset                 |                                      |                                           |

| Anadigm<br>(Approved)                    |                                     |                          |                                      |                                           |

| SumDiff2<br>(SumDiff v1.0.1)             | Output Phase                        | Phase 2                  | Gain 1 (UpperInput) 2.00             | ClockA 250 kHz (Chip                      |

| (SumDiff v1.0.1)                         | Input 1                             | Inverting                | Gain 2 (MiddleInput) 3.00            | Clock 3)                                  |

| Φ1 Φ2                                    | Input 2                             | Non-inverting            | Gain 3 (LowerInput) 0.165            |                                           |

| <b>•</b> 1                               | Input 3                             | Non-inverting            |                                      |                                           |

| Апаdigm<br>(Approved)                    | Input 4                             | Off                      |                                      |                                           |

| Integrator3                              | Polarity                            | Non-inverting            | Integration Const. 0.00250           | ClockA 250 kHz (Chip                      |

| (Integrator v1.1.1)                      | Input Sampling<br>Phase             | Phase 2                  | [1/us] 0.00250                       | Clock 3)                                  |

| ■ <sub>42</sub>                          | Compare<br>Control To               | No Reset                 |                                      |                                           |

| Anadigm<br>(Approved)                    |                                     |                          |                                      |                                           |

| Voltage1<br>(Voltage v1.0.1)             | Polarity                            | Positive (+2V)           |                                      |                                           |

| <b>.</b>                                 |                                     |                          |                                      |                                           |

| Anadigm<br>(Approved)                    |                                     |                          |                                      |                                           |

### Figure 5: The parameter values of the CAMs used in the FPAA design

FPAA outputs were examined by PC based oscilloscope. The oscilloscope outputs of the implemented FPAA based system (Figure 4) are given in Figure 6. When the numerical simulation results (Figure 3) and FPAA output results (Figure 6) are examined, it is seen that the phase portraits obtained are the same.

Figure 6: The oscilloscope outputs of the implemented FPAA based system (a) u-v (b) u-w (c) v-w

# 5. Results

In this study, FPAA based design and implementation of Sprott N chaotic system was performed. Since the output values of the state variables of the Sprott N chaotic system are outside the FPAA operating voltage range ( $\pm$ 3V), the system (1) was first scaled. With scaling operation, the outputs of the system (3) were matched to the FPAA operating voltage range ( $\pm$  3V). When the numerical simulation results (Figure-3) in Matlab program and FPAA based implementation results (Figure-6) were examined, it was seen that they confirmed each other. As a result, it has been shown that the design of the Sprott N chaotic system with FPAA can be used in various engineering applications. In addition, the FPAA can be easily redesigned so that the design can be updated more easily than designs using analogue elements such as OPAMP, multiplication IC, capacitor, resistor.

#### 6. References

[1] Varan, M., Yalçın, F. and Uyaroğlu, Y., "Synchronizations and secure communications applications of a third degree Malasoma system with chaotic flow", *Optik*, 127, 11086-11093, 2016.

[2] Elzaher, M.F.A., Shalaby, M., Kamal, Y. and Ramly, S.E., "Securing digital voice communication using non-autonomous modulated chaotic signal", *Journal of Information Security and Applications*, 34, 243-250, 2017.

[3] Liu, H., Zhang, Y., Kadir, A. and Xu, Y., "Image encryption using complex hyper chaotic system by injecting impulse into parameters", *Applied Mathematics and Computation*, 360, 83-93, 2019.

[4] Xingyuan, W., Junjian, Z. and Guanghui, C., "An image encryption algorithm based on ZigZag transform and LL compound chaotic system", *Optics and Laser Technology*, 119, 105581, 2019.

[5] Ni, R., Ruan, Q. and Zhao, Y., "Pinpoint authentication watermarking based on chaotic system", *Forensic Science International*, 179, 54-62, 2008.

[6] Lin, H.Y., "Improved chaotic maps-based password-authenticated key agreement using smart cards", *Communication in Nonlinear Science and Numerical Simulation*, 20, 482-488, 2015.

[7] Tang, M. and Xin, Y., "Energy efficient power allocation in cognitive radio network using coevolution chaotic particle swarm optimization", *Computer Networks*, 100, 1-11, 2016.

BILMES EN 2019 - ANKARA

[8] Pourmousa, N., Ebrahimi, S.M., Malekzadeh, M. and Alizadeh, M., "Parameter estimation of photovoltaic cells using improved Lozi map based chaotic optimization algorithm", *Solar Energy*, 180, 180-191, 2019.

[9] Qi, G., Chen, G., "Analysis and circuit implementation of a new 4D chaotic system", *Physics Letters A*, 352, 386-397, 2006.

[10] Liu, J., "A four-wing and double-wing 3D chaotic system based on sign function", Optik, 125, 7089-7095, 2014.

[11] Le, X., Sen, Z., Yicheng, Z. and Boquan, L., "Dynamics of a new composite four-scroll chaotic system", *Chinese Journal of Physics*, 56, 2381-2394, 2018.

[12] Azzaz, M.S., Tanougast, C., Sadoudi, S., Fellah, R. and Dandache, A., "A new auto-switched chaotic system and its FPGA implementation", *Communication in Nonlinear Science and Numerical Simulation*, 18, 1792-1804, 2013.

[13] Tuna, M., Alçın, M., Koyuncu, İ., Fidan, C.B. and Pehlivan, İ., "High speed FPGA-based chaotic oscillator design", *Microprocessors and Microsystems*, 66, 72-80, 2019.

[14] Chiu, R., Mora-Gonzalez, M. and Lopez-Mancilla, D., "Implementation of a chaotic oscillator into a simple microcontroller", *IERI Procedia*, 4, 247-252, 2013.

[15] Janakiraman, S., Thenmozhi, K., Rayappan, J.B.B and Amirtharajan, R., "Lightewight chaotic image encryption algorithm for real-time embedded system: implementation and analysis on 32-bit microcontroller", *Microprocessors and Microsystems*, 56, 1-12, 2018.

[16] Frasca, M., Fortuna, L. and Arena, P., "Implementation and synchronization of 3x3 grid scroll chaotic circuits with analog programmable devices", *Chaos*, 16, 013121, 2006.

[17] Kılıç, R. and Dalkıran, F.Y., "Reconfigurable implementations of Chua's circuit", *International Journal of Bifurcation and Chaos*, 19(4), 1339-1350, 2009.

[18] Kılıç, R. and Dalkıran, F.Y., "Programmable design and implementation of a chaotic system utilizing multiple nonlinear functions", *Turkish Journal of Electrical Engineering & Computer Sciences*, 18(4), 647-655, 2010.

[19] Arık, S. and Kılıç, R., "Reconfigurable hardware platform for experimental testing and verifying of memristor-based chaotic systems", *Journal of Circuits, Systems, and Computers*, 23(10), 1450145, 2014.

[20] Caponetto, R., Mauro, A.D., Fortuna, L. and Frasca, M., "Field programmable analog array to implement a programmable Chua's circuit", *International Journal of Bifurcation and Chaos*, 15(5), 1829-1836, 2005.

[21] Günay, E., Altun, K. and Ünal, C., "Anahtarlamalı Durum Kontrollü HSA Tabanlı Sprott C Kaos üretecinin FPGA ve FPAA Gerçekleştirimi", *International Conference on Artificial Intelligence and Data Processing (IDAP)*, 28-30 September, Malatya, Turkey, 2018.

[22] Günay, E. and Altun, K., "HSA tabanlı kaos üretecinin FPAA kullanılarak gerçekleştirilmesi", 25th Signal Processing and Communications Applications Conference (SIU), 15-18 May, Antalya, Turkey, 2017.

[23] Li, C., Thio, W.J.C., Sprott, J.C., Iu, H.H.C. and Xu, Y., "Constructing infinitely many attractors in a programmable chaotic circuit", *IEEE Access*, 6, 29003-29012, 2018.

[24] Sprott, J.C., "Some simple chaotic flows", *Physical Review E*, 50(2), 647-650, 1994.