# Development of Analogue circuits for the BETA ASIC HERD-FIT detector

A Master's Thesis Submitted to the Faculty of the Escola Tècnica d'Enginyeria de Telecomunicació de Barcelona Universitat Politècnica de Catalunya by

# AITOR IRAOLA ZAPIAIN

# In partial fulfilment of the requirements for the degree of MASTER IN TELECOMMUNICATION ENGINEERING

Advisor: Sergio Gómez Fernández, Xavier Aragones Cervera Barcelona, May 2021

<u>**Title of the thesis:</u>** Development of Analogue circuits for the BETA ASIC HERD-FIT detector</u>

Author: Aitor Iraola Zapiain

Advisor: Sergio Gómez Fernández, Xavier Aragones Cervera

# Abstract

The Electronics Instrumentation Service of the Insittute of Cosmos Science of the University of Barcelona (ICCUB-SiUB) is focused on developing ultrafast readout electronics for high-energy physics and medical imaging. In the framework of the HERD project (High Energy Cosmic-Radiation Detector) the group has developed the readout BETA-ASIC to push the limits of dark matter radiation research. Thus, the aim of this Master Thesis is to contribute to the ASIC design.

This project presents a low power comparator that will be used for detection triggering as well as internal path selecting of a multi gain system. The comparator has input rail-to-rail and hysteresis feedback. The power consumption is around  $60 \mu W$ , the gain is 76 *dB* and the hysteresis amplitude is about 5.75 *mV*. The single-photon *SNR* is around 10, the delay is 15 *ns* and jitter is below 100 *ps* for input energies higher than 10 pe (photoelectrons). These simulations prove the fulfilment the requirements for the ASIC, and a first prototype has already been sent to be manufactured in April.

# Acknowledgements

I would like to thank all my colleagues from ICCUB for all the support they have given to me and for sharing their scientific and technical knowledge. Special thanks to Sergio Gómez, for being my main advisor, to Anand Sanmukh, for his daily support at the lab, to Rafel Manera, for the layout course, and finally to David Gascón, for his guidance in analogue design.

Finally, I would like to thank Xavier Aragones for being the co-advisor of my Master Thesis.

# **Revision history and approval record**

| Revision | Date       | Purpose              |

|----------|------------|----------------------|

| 0        | 20/04/2021 | Document creation    |

| 1        | 03/05/2021 | Document revision I  |

| 2        | 17/05/2021 | Document revision II |

| 3        | 21/05/2021 | Document approval    |

| Written by: |                                                       | Reviewed and approved by: |                            |

|-------------|-------------------------------------------------------|---------------------------|----------------------------|

| Date        | 20/04/2021                                            | Date                      | 21/05/2021                 |

| Name        | Name Aitor Iraola Zapiain Name Xavier Arag<br>Cervera |                           | Xavier Aragones<br>Cervera |

| Position    | Project Author                                        | Position                  | Project Supervisor         |

# **Table of Contents**

| Abstract                                                 |    |  |  |  |

|----------------------------------------------------------|----|--|--|--|

| Acknowledgements4                                        |    |  |  |  |

| Revision history and approval record5                    |    |  |  |  |

| Table of Contents                                        | 6  |  |  |  |

| List of Figures                                          | 8  |  |  |  |

| List of Tables1                                          | 2  |  |  |  |

| 1. Introduction1                                         | 3  |  |  |  |

| 1.1. Challenge1                                          | 3  |  |  |  |

| 1.2. HERD Project1                                       | 4  |  |  |  |

| 1.2.1. HERD –ASIC (BETA)1                                | 6  |  |  |  |

| 1.3. Objective1                                          | 7  |  |  |  |

| 1.4. Gantt diagram1                                      | 9  |  |  |  |

| 2. Theoretical analysis of the comparator2               | 20 |  |  |  |

| 2.1. Fully differential amplifier with resistive load2   | 24 |  |  |  |

| 2.2. Rail-to-Rail Fully Differential Amplifier2          | 29 |  |  |  |

| 2.3. Hysteresis Comparator                               | 2  |  |  |  |

| 2.4. Output NOR gate                                     | 8  |  |  |  |

| 2.5. Current DAC                                         | 8  |  |  |  |

| 3. Methodology / project development                     | 0  |  |  |  |

| 3.1. Transistor level design of the comparator4          | 0  |  |  |  |

| 3.2. Transistor level design of the current DAC4         | 7  |  |  |  |

| 3.3. Analysis compared with ideal signal4                | .9 |  |  |  |

| 3.3.1. Transient analysis4                               | .9 |  |  |  |

| 3.3.2. DC analysis                                       | 0  |  |  |  |

| 3.3.3. AC analysis5                                      | 2  |  |  |  |

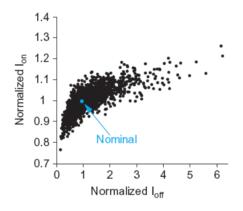

| 3.3.4. Process and Mismatch                              | 3  |  |  |  |

| 3.4. Analysis in real signal5                            | 5  |  |  |  |

| 3.5. Layout                                              |    |  |  |  |

| 3.6. Parasitics extraction and comparison with schematic |    |  |  |  |

| 3.7.   Comparator in the channel                         |    |  |  |  |

| 4. Results                                               |    |  |  |  |

| 4   | .1. Tr  | ansistor level design of the comparator  | 61  |

|-----|---------|------------------------------------------|-----|

| 4   | .2. Tr  | ansistor level design of the current DAC | 64  |

| 4   | .3. Co  | omparator compared with ideal signal     | 65  |

|     | 4.3.1.  | Transient analysis                       | 65  |

|     | 4.3.2.  | DC analysis                              | 69  |

|     | 4.3.3.  | AC analysis                              | 77  |

|     | 4.3.4.  | Process and Mismatch                     | 80  |

| 4   | .4. Co  | omparator in real signal                 | 87  |

|     | 4.4.1.  | SNR                                      |     |

|     | 4.4.2.  | Delay and Jitter                         | 90  |

| 4   | .5. Co  | omparator Layout                         | 94  |

| 4   | .6. Co  | omparator in extraction                  | 97  |

|     | 4.6.1.  | Standalone                               | 97  |

|     | 4.6.2.  | Real Signal                              | 98  |

| 4   | .7. Co  | omparator in Channel                     | 101 |

| 5.  | Conclu  | isions and future development            |     |

| 6.  | Bibliog | raphy                                    |     |

| Glo | ssary   |                                          | 108 |

# List of Figures

| Fig. 1<br>Station    | The HERD detector onboard the "Experiment module I" of the Chinese Space                                                                                                                                               |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 2               | Electrical model for SiPM (Figure taken from [3])15                                                                                                                                                                    |

| Fig. 3               | Avalanche and reset phase in the fired cells of the SiPM16                                                                                                                                                             |

| Fig. 4               | Block diagram of the BETA ASIC17                                                                                                                                                                                       |

| Fig. 5               | Gantt diagram19                                                                                                                                                                                                        |

| Fig. 6               | Block diagram with input and output signals20                                                                                                                                                                          |

| Fig. 7               | Comparator input signals mixed with noise21                                                                                                                                                                            |

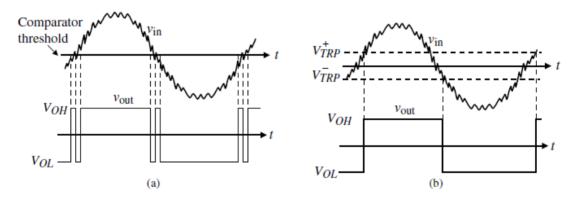

| Fig. 8               | Comparator input and output signals mixed with noise21                                                                                                                                                                 |

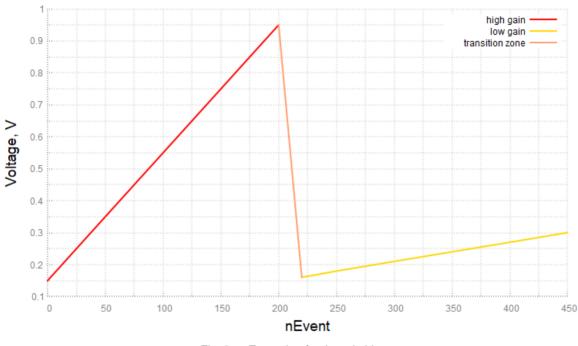

| Fig. 9               | Example of gain switching22                                                                                                                                                                                            |

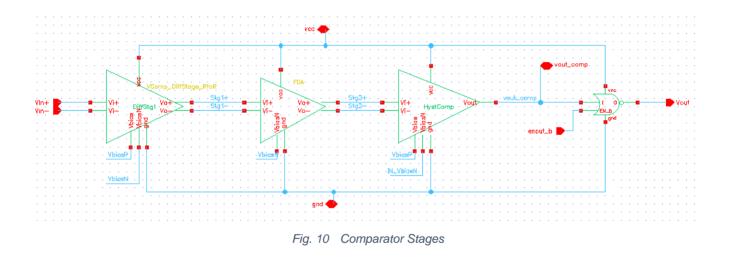

| Fig. 10              | Comparator Stages23                                                                                                                                                                                                    |

| Fig. 11              | Simple fully differential amplifier24                                                                                                                                                                                  |

|                      | (a) Response of MOS differential pair to very positive input, (b) response of ferential pair to very negative input, (c) qualitative plots of currents and voltages. rom B. Razavi, Fundamentals of Microelectronics ) |

| Fig. 13<br>Fundam    | Circuit behaving as amplifier or as comparator (Figure from B. Razavi,<br>entals of Microelectronics)                                                                                                                  |

| Fig. 14<br>Microele  | Basic fully differential amplifier (Figure from B. Razavi, Fundamentals of ctronics)                                                                                                                                   |

|                      | Variation of (a) drain currents, (b) the difference between drain currents, and ential output voltage as a function of input. (Figure from B. Razavi, Fundamentals electronics)                                        |

| Fig. 16<br>Aragoné   | small signal model of the FDA (Figure from slides of AACT subject, X. s)                                                                                                                                               |

| Fig. 17<br>Aragoné   | simplified half circuit FDA (Figure from slides of AACT subject, X. s)                                                                                                                                                 |

| Fig. 18<br>subject,  | Adding capacitances at output, for BW estimation. (Figure from slides of AACT X. Aragonés)                                                                                                                             |

| Fig. 19              | R2R FDA used in the first stage                                                                                                                                                                                        |

| Fig. 20<br>Design E  | Unequalized <i>gm</i> for differential pairs (Image taken from Willy Sanse, Analog Essentials)                                                                                                                         |

| Fig. 21              | Comparator transfer curve with hysteresis                                                                                                                                                                              |

| Fig. 22<br>input wh  | (a) Comparator response with noisy input. (b) Comparator response to a noisy en hysteresis is added                                                                                                                    |

| Fig. 23<br>of a high | Implementation of hysteresis using internal positive feedback in the input stage<br>-gain, open-loop amplifier                                                                                                         |

| Fig. 24<br><i>VTRP</i> +.<br>towards <i>VT</i> | <ul> <li>(a) Comparator of Fig. 23 where <i>vin</i> is very negative and increasing towards</li> <li>(b) Comparator of Fig. 23 where <i>vin</i> is very positive and decreasing</li> <li><i>TRP</i></li></ul> |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 25                                        | Complete comparator with internal hysteresis including an output stage36                                                                                                                                      |

| Fig. 26                                        | Hysteresis comparator                                                                                                                                                                                         |

| Fig. 27                                        | NOR gate                                                                                                                                                                                                      |

| Fig. 28                                        | Low voltage current mirror                                                                                                                                                                                    |

| Fig. 29                                        | Copy error due to VDS difference (Figure taken from MND course)                                                                                                                                               |

| Fig. 30                                        | transistor characterization testbench41                                                                                                                                                                       |

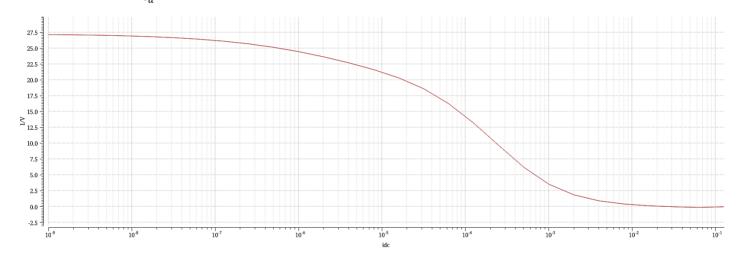

| Fig. 31                                        | <i>gmId</i> characteristic, from 1 <i>nA</i> to 10 <i>mA</i> 41                                                                                                                                               |

| Fig. 32                                        | VGS and VDS voltages for different transistor sizes                                                                                                                                                           |

| Fig. 33                                        | parameter values for 24 $\mu m$ width pMOS                                                                                                                                                                    |

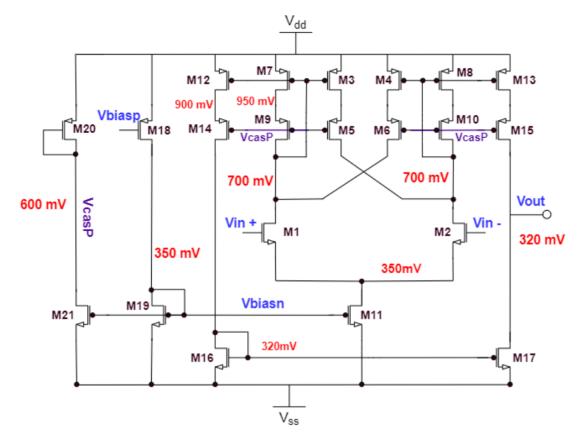

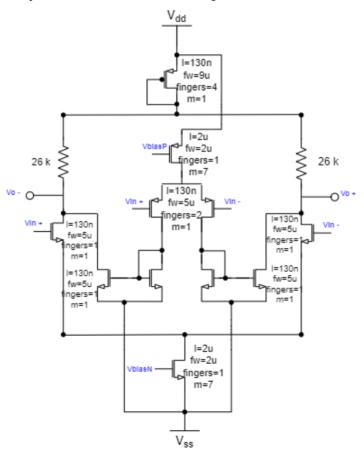

| Fig. 34                                        | 1 <sup>st</sup> stage design44                                                                                                                                                                                |

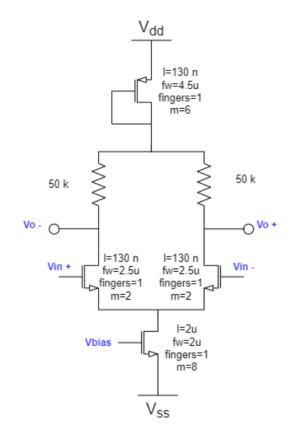

| Fig. 35                                        | 2 <sup>nd</sup> stage design45                                                                                                                                                                                |

| Fig. 36                                        | Hysteresis block design47                                                                                                                                                                                     |

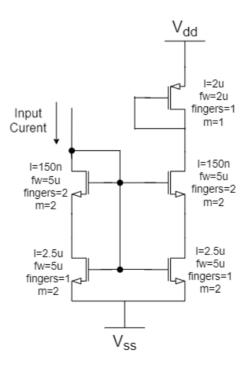

| Fig. 37                                        | DC node voltages current mirror48                                                                                                                                                                             |

| Fig. 38                                        | Transient analysis testbench                                                                                                                                                                                  |

| Fig. 39                                        | Delay measurement illustrated graphically50                                                                                                                                                                   |

| Fig. 40                                        | DC analysis testbench51                                                                                                                                                                                       |

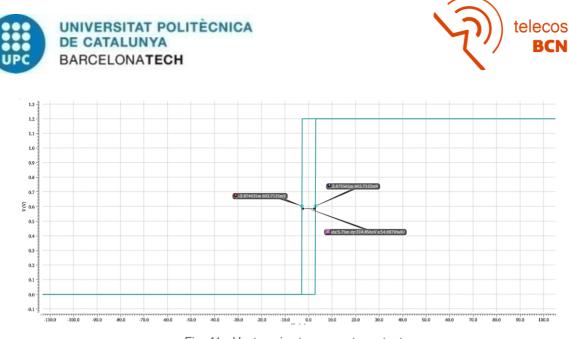

| Fig. 41                                        | Hysteresis at comparator output52                                                                                                                                                                             |

| Fig. 42                                        | Operating points in the hysteresis comparator block                                                                                                                                                           |

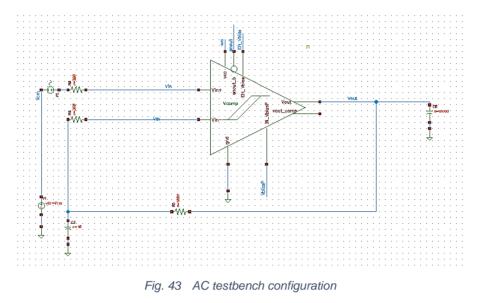

| Fig. 43                                        | AC testbench configuration                                                                                                                                                                                    |

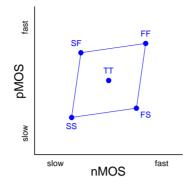

| Fig. 44                                        | Process corners                                                                                                                                                                                               |

| Fig. 45                                        | Monte Carlo simulation example                                                                                                                                                                                |

| Fig. 46                                        | Tuning DC operating points of the wide swing current mirror55                                                                                                                                                 |

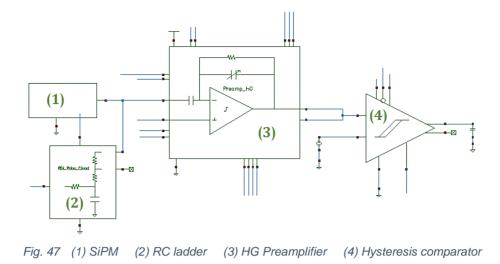

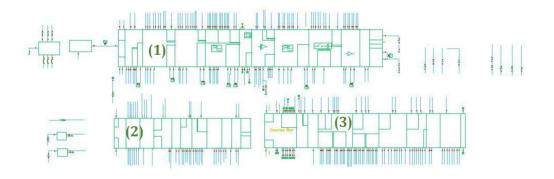

| Fig. 47<br>comparato                           | (1) SiPM (2) RC ladder (3) HG Preamplifier (4) Hysteresis<br>r                                                                                                                                                |

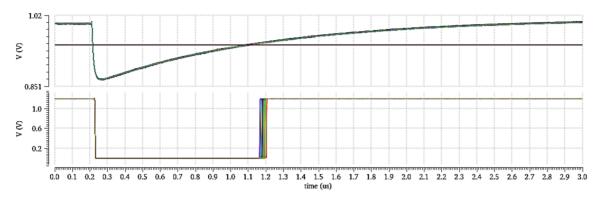

| Fig. 48                                        | Comparator input signals                                                                                                                                                                                      |

| Fig. 49                                        | Input and output of the comparator                                                                                                                                                                            |

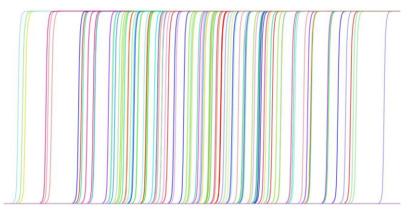

| Fig. 50                                        | Comparator switches in different moments each iteration                                                                                                                                                       |

| Fig. 51                                        | delay vs noise iteration                                                                                                                                                                                      |

| Fig. 52                                        | Threshold sweep for 1 photon signal and noise                                                                                                                                                                 |

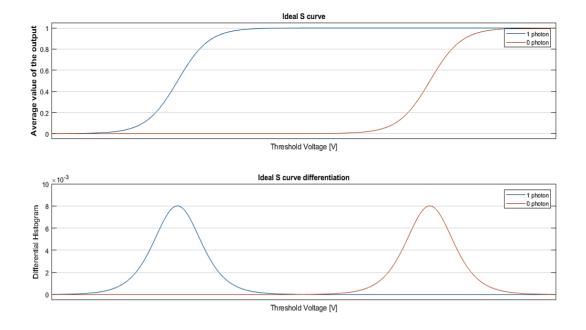

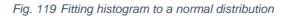

| Fig. 53                                        | S curves and differentiation                                                                                                                                                                                  |

| Fig. 54                                        | (1) Channel (2) Digital Control Block (3) Common Bias Block60                                                                                                                                                 |

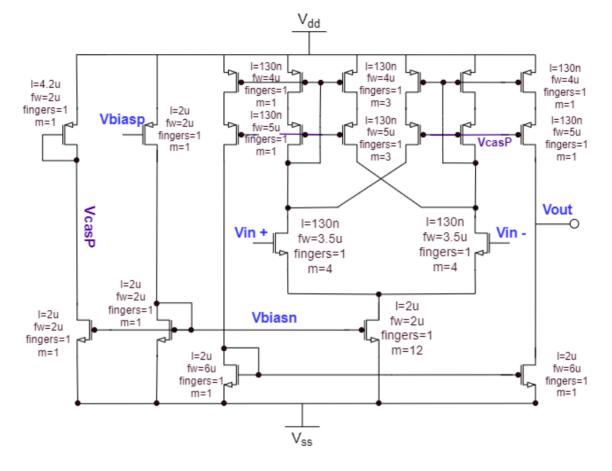

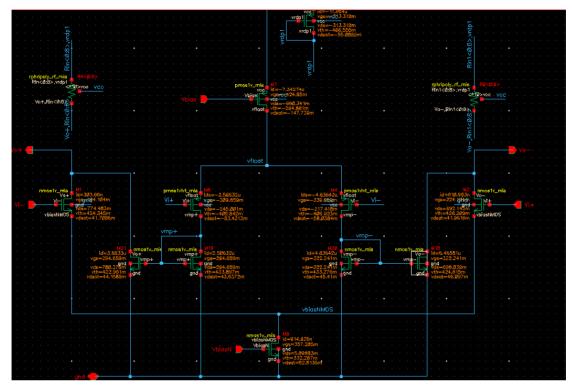

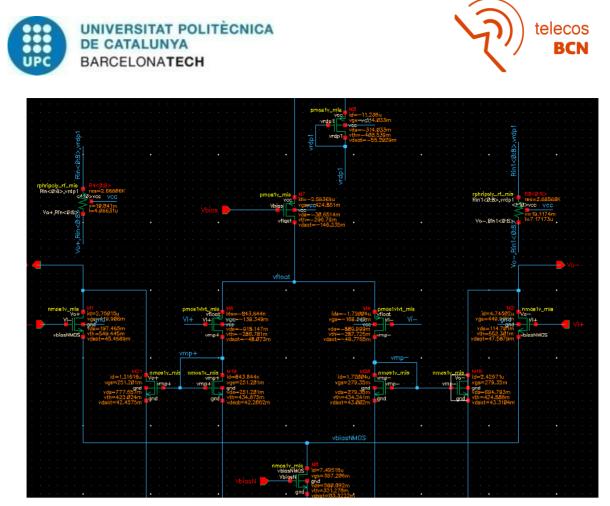

| Fig. 55                                        | 1 <sup>st</sup> stage definitive design61                                                                                                                                                                     |

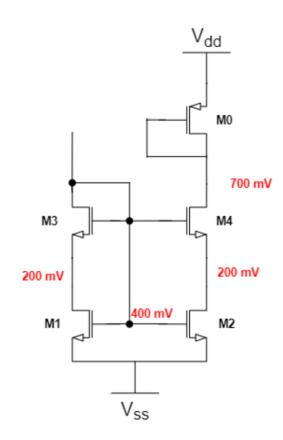

| Fig. 56 | 2 <sup>nd</sup> stage definitive design62                             |

|---------|-----------------------------------------------------------------------|

| Fig. 57 | Hysteresis comparator definitive design63                             |

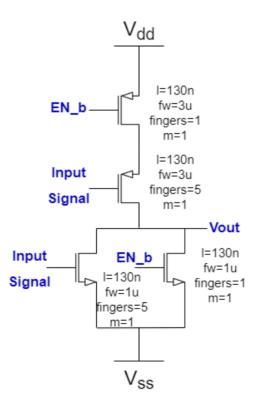

| Fig. 58 | NOR gate definitive design63                                          |

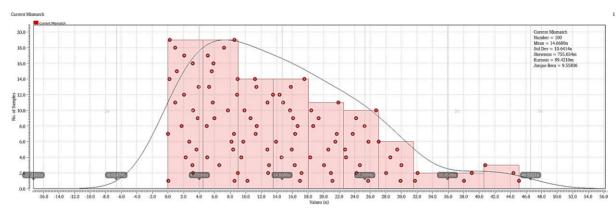

| Fig. 59 | Current mismatch statistics with Monte Carlo64                        |

| Fig. 60 | current mirror definitive values64                                    |

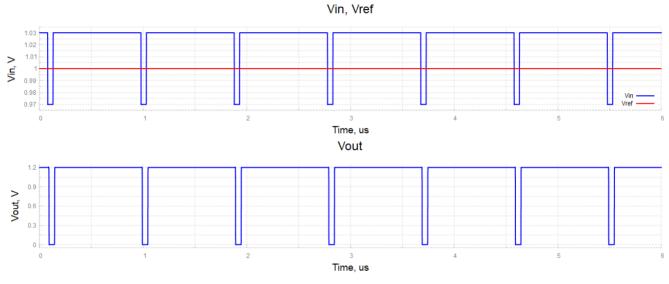

| Fig. 61 | Input, reference and output signals65                                 |

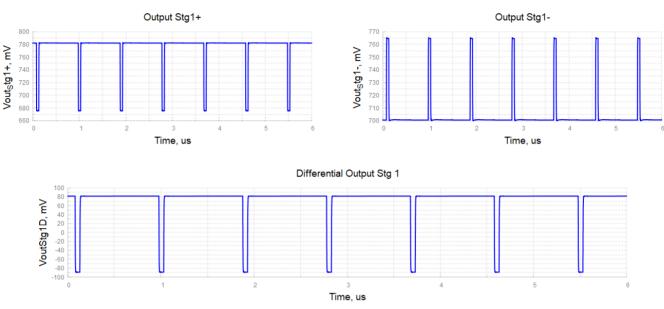

| Fig. 62 | Stage 2 differential signals66                                        |

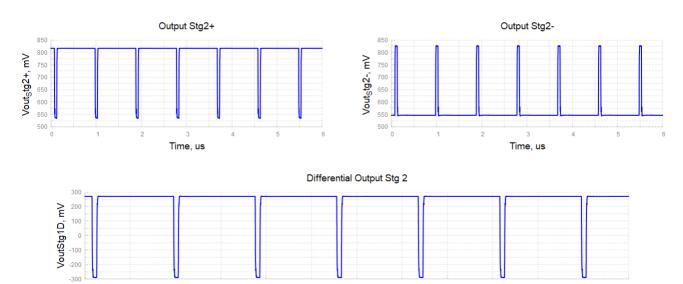

| Fig. 63 | Stage 1 diferential signals66                                         |

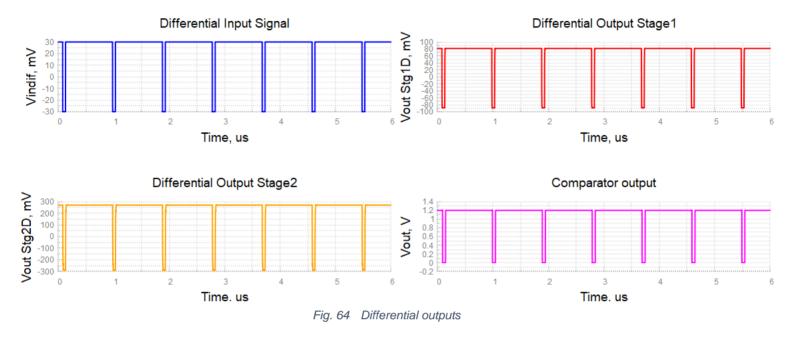

| Fig. 64 | Differential outputs67                                                |

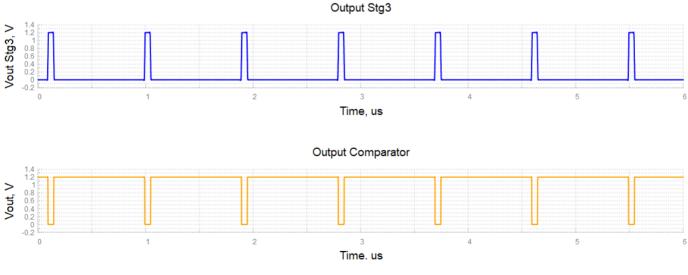

| Fig. 65 | Output signal restoring67                                             |

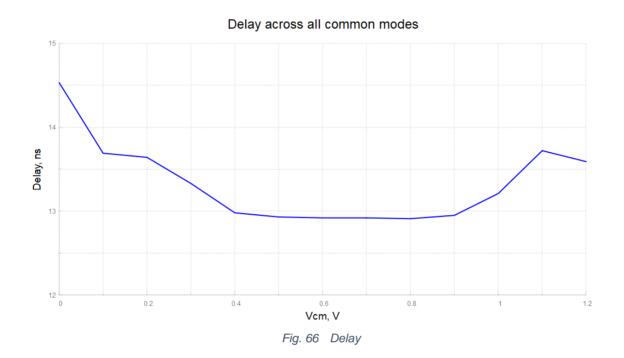

| Fig. 66 | Delay                                                                 |

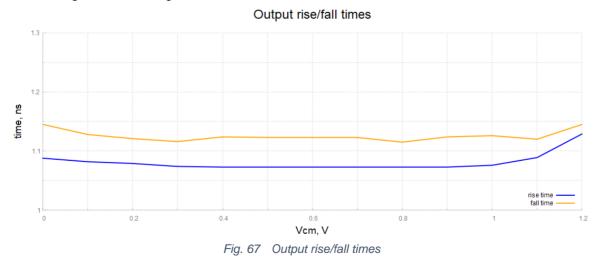

| Fig. 67 | Output rise/fall times68                                              |

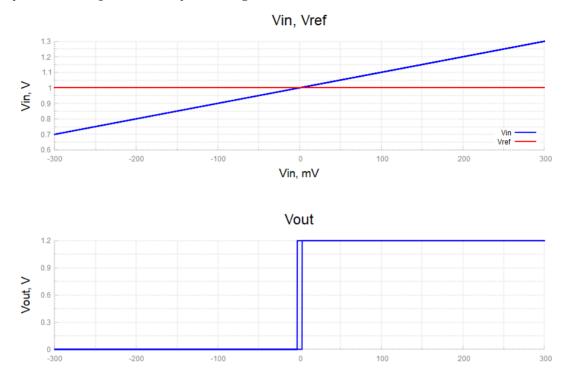

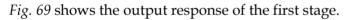

| Fig. 68 | DC input and output signals69                                         |

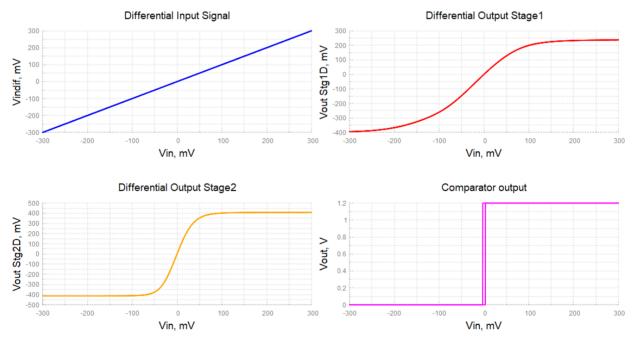

| Fig. 69 | Stage 1 differential signals at 1 V69                                 |

| Fig. 70 | Stage 1 output differential signals at 600 mV70                       |

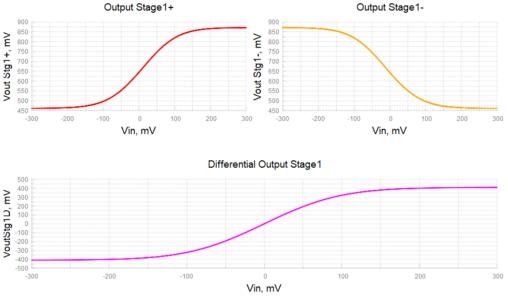

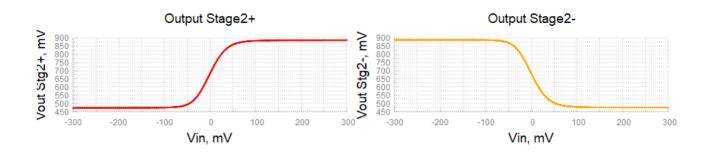

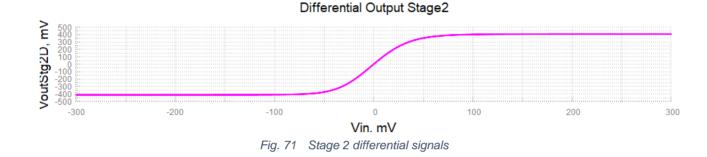

| Fig. 71 | Stage 2 differential signals71                                        |

| Fig. 72 | Output signals71                                                      |

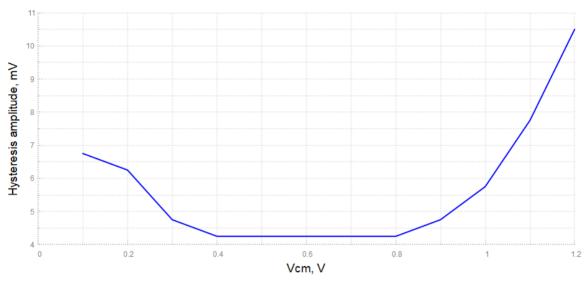

| Fig. 73 | Hysteresis amplitude72                                                |

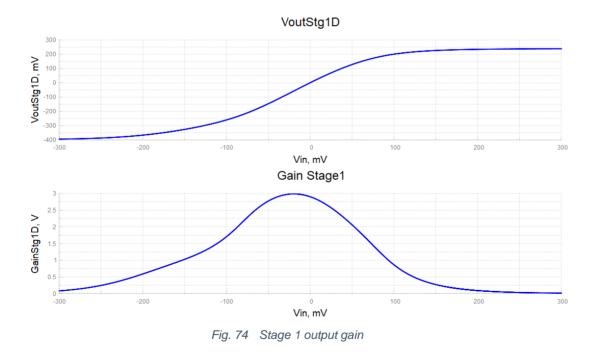

| Fig. 74 | Stage 1 output gain72                                                 |

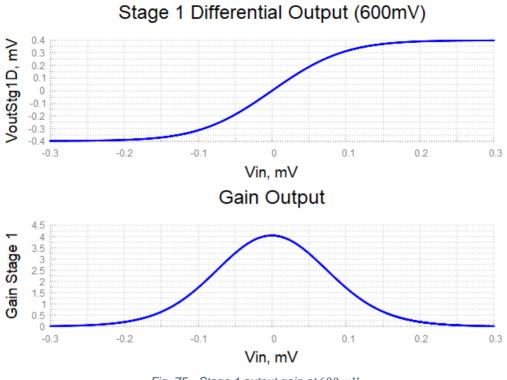

| Fig. 75 | Stage 1 output gain at 600 mV73                                       |

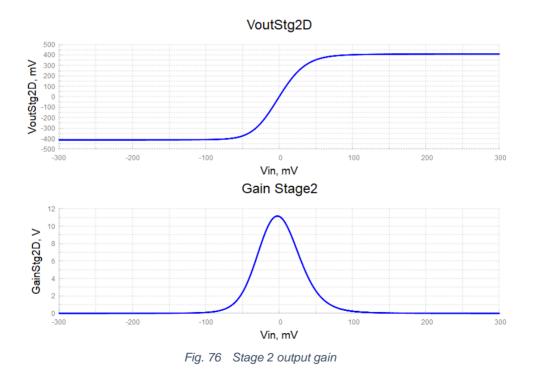

| Fig. 76 | Stage 2 output gain73                                                 |

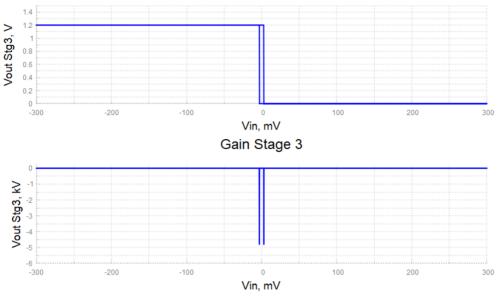

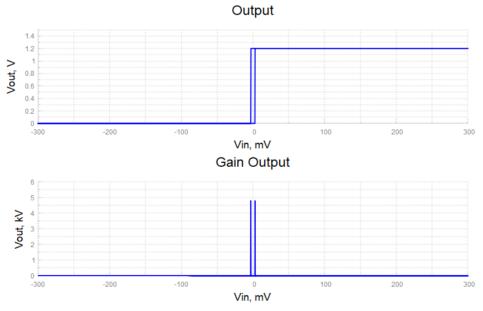

| Fig. 77 | Gain output stage 374                                                 |

| Fig. 78 | Gain output of the comparator (stage 4)74                             |

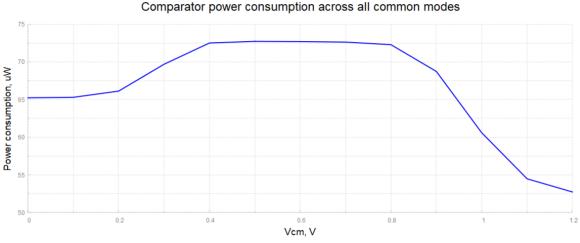

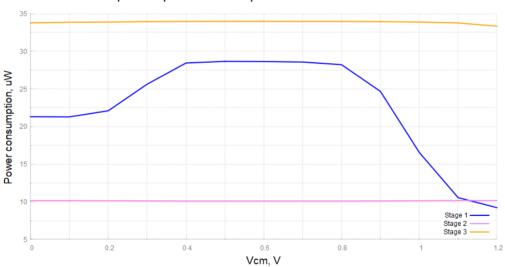

| Fig. 79 | Power consumption along the common mode75                             |

| Fig. 80 | Power consumption of each stage along all the common mode75           |

| Fig. 81 | Operating points 1 <sup>st</sup> stage at 200 mV common mode76        |

| Fig. 82 | Operating points 1 <sup>st</sup> stage at 1 V common mode77           |

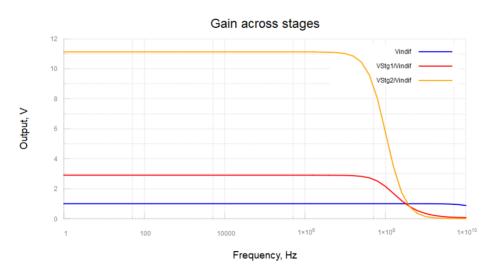

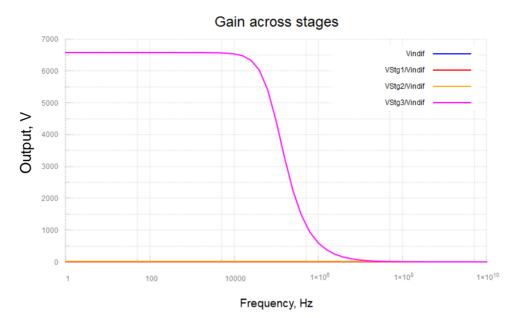

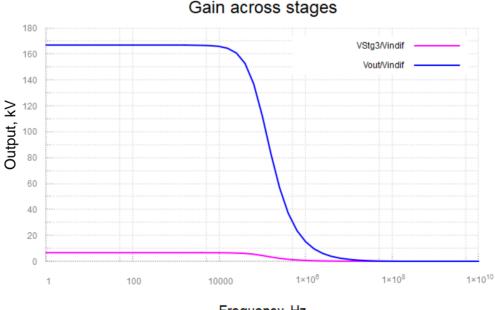

| Fig. 83 | Gain-bandwidth curves of input and intermediate AC signals77          |

| Fig. 84 | Comparison of third stage gain, with respect to the previous stages78 |

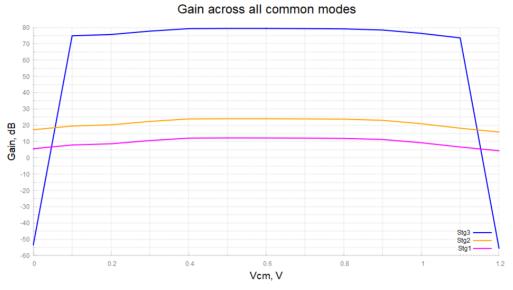

| Fig. 85 | Comparison of gain after the NAND gate with the hysteresis block78    |

| Fig. 86 | Gain in all common modes in dB79                                      |

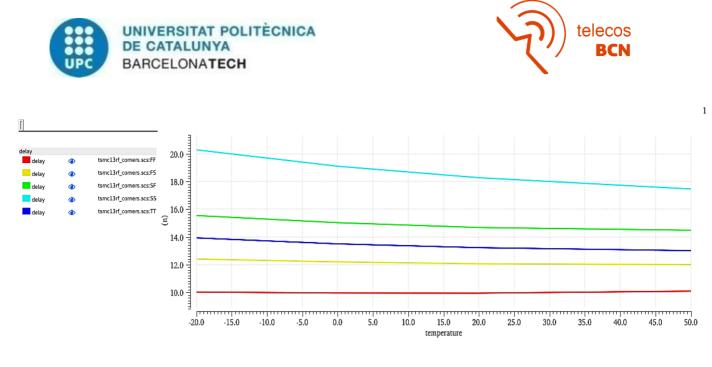

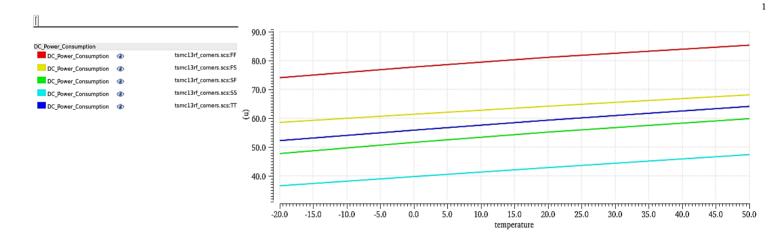

| Fig. 87 | Delay with corners81                                                  |

| Fig. 88 | DC power consumption with corners81                                   |

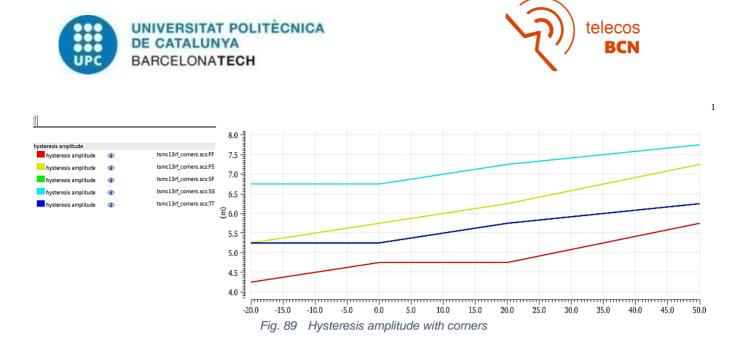

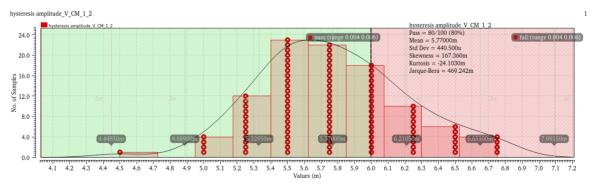

| Fig. 89 | Hysteresis amplitude with corners82                                   |

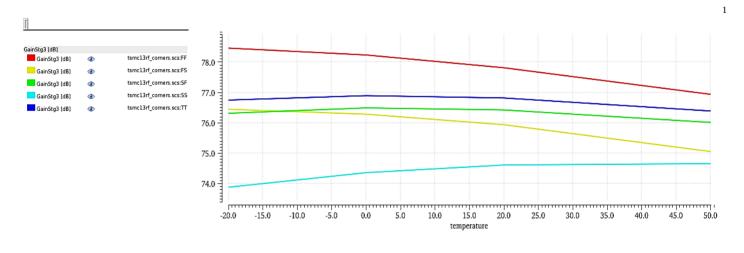

| Fig. 90              | Comparator gain with corners                                        | 32 |

|----------------------|---------------------------------------------------------------------|----|

| Fig. 91              | Operating points of hysteresis block at TT                          | 84 |

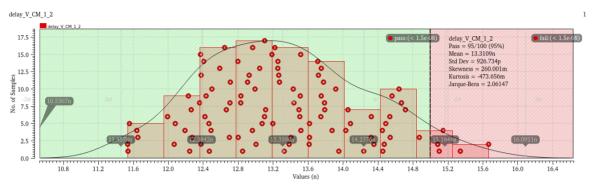

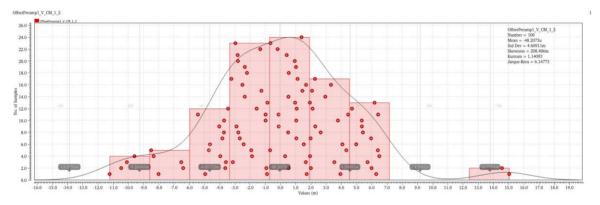

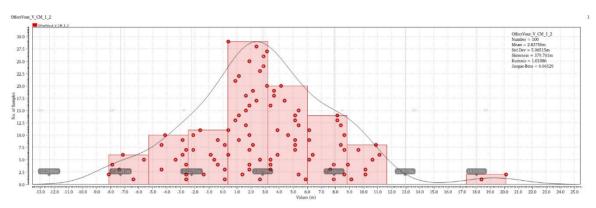

| Fig. 92              | Mismatch effect on delay                                            | 85 |

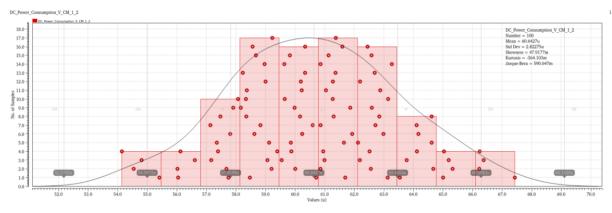

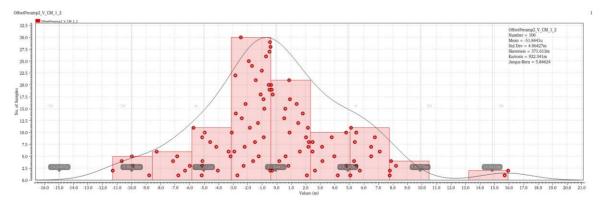

| Fig. 93              | Mismatch effect on power consumption                                | 85 |

| Fig. 94              | Mismatch effect on hysteresis amplitude                             | 85 |

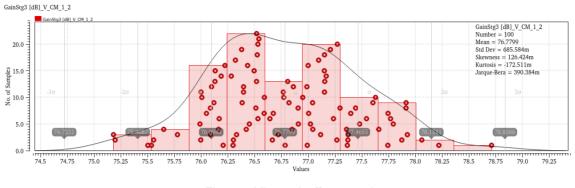

| Fig. 95              | Mismatch effect on gain                                             | 86 |

| Fig. 96              | Mismatch effect on R2R amplifier offset                             | 86 |

| Fig. 97              | Mismatch effect on 2 <sup>nd</sup> amplifier offset                 | 86 |

| Fig. 98              | Mismatch effect on comparator offset                                | 87 |

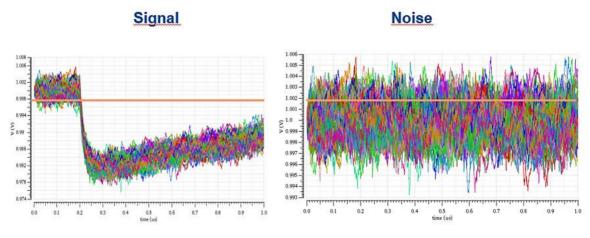

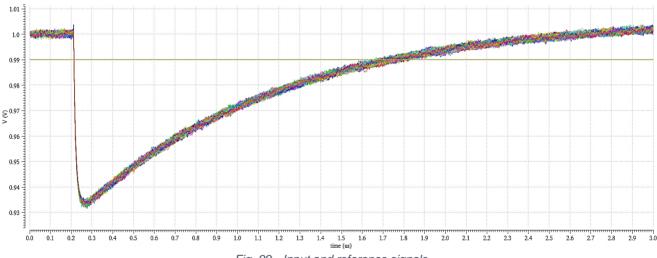

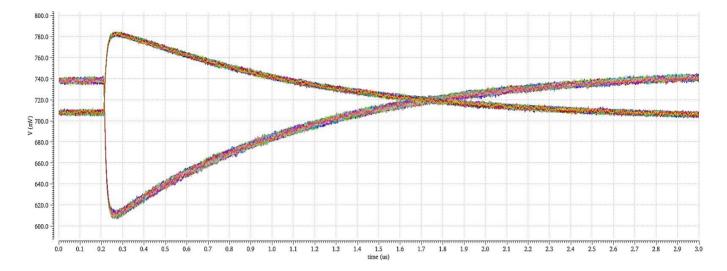

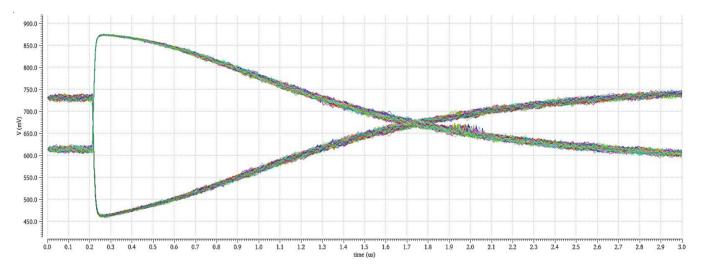

| Fig. 99              | Input and reference signals                                         | 87 |

| Fig. 100             | Stage 1 output differential signals                                 | 88 |

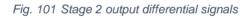

| Fig. 101             | Stage 2 output differential signals                                 | 88 |

| Fig. 102             | Comparator output signal                                            | 88 |

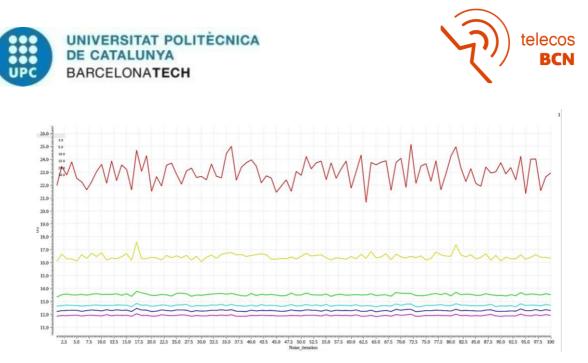

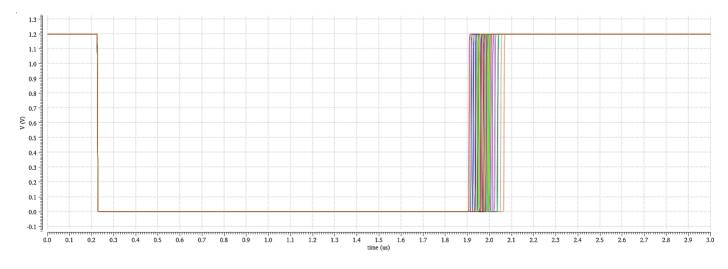

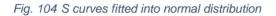

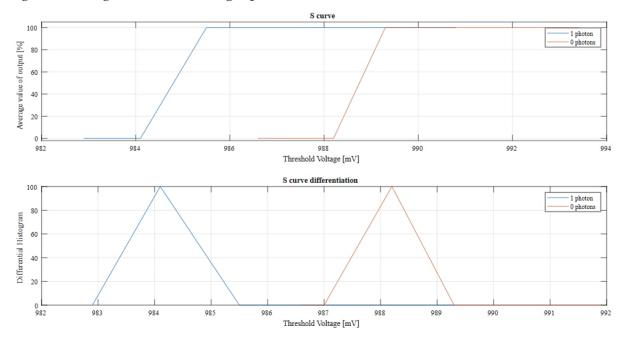

| Fig. 103             | S curves and differential histogram                                 | 89 |

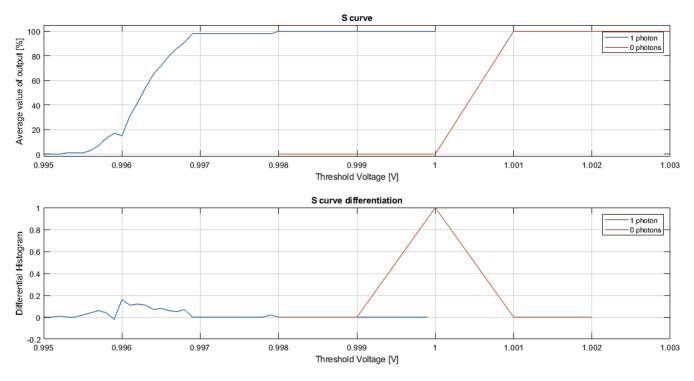

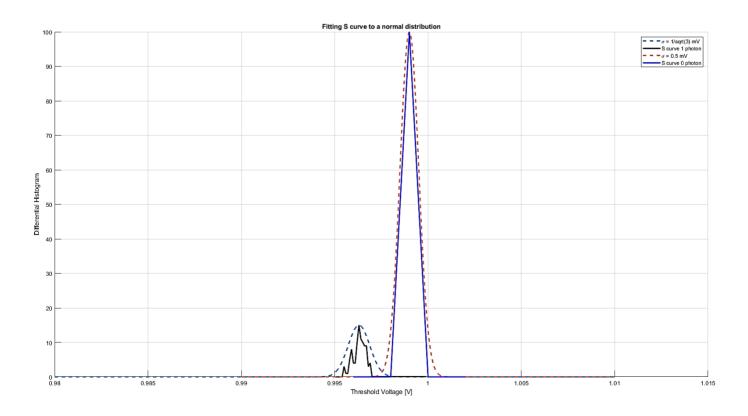

| Fig. 104             | S curves fitted into normal distribution                            | 90 |

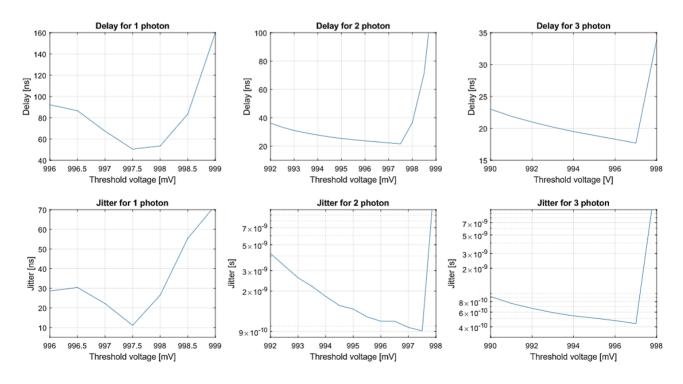

| Fig. 105             | Threshold scan for 1, 2 and 3 photons                               | 90 |

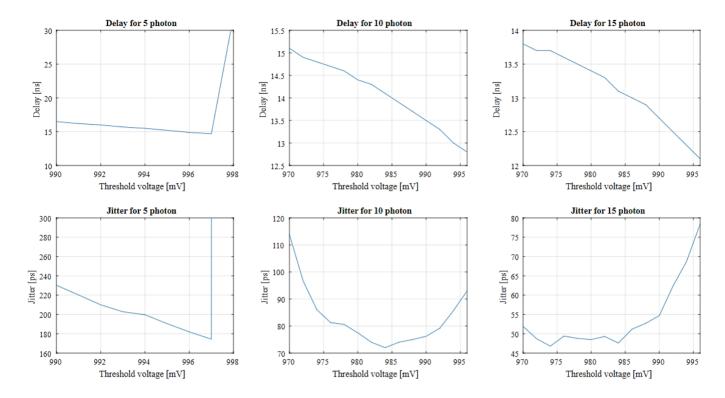

| Fig. 106             | Threshold scan for 5, 10 and 15 photons                             | 91 |

| Fig. 107             | Threshold scan for 20 and 30 photons                                | 91 |

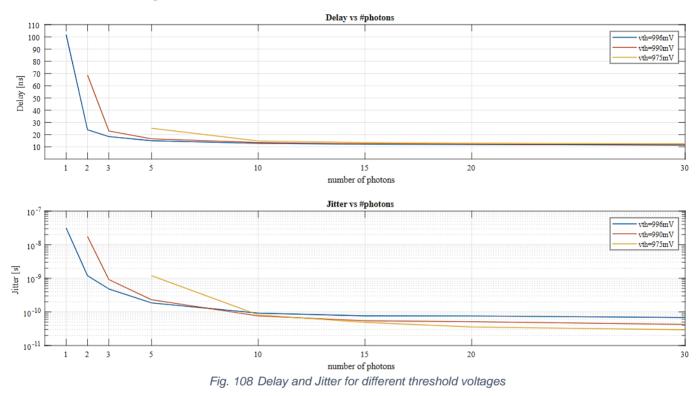

| Fig. 108             | Delay and Jitter for different threshold voltages                   | 92 |

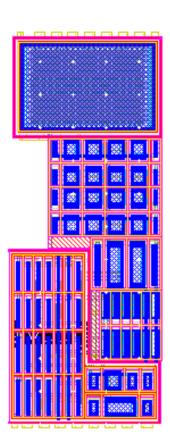

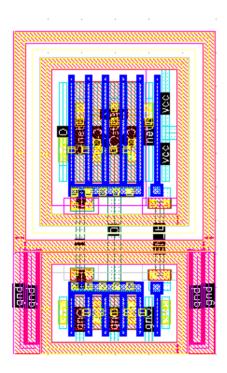

| Fig. 109             | First stage schematic                                               | 94 |

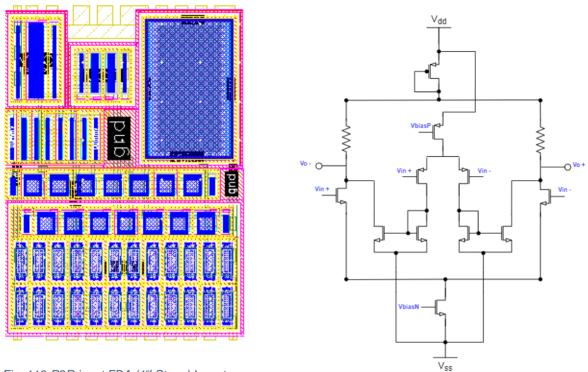

| Fig. 110             | R2R input FDA (1 <sup>st</sup> Stage) layout                        | 94 |

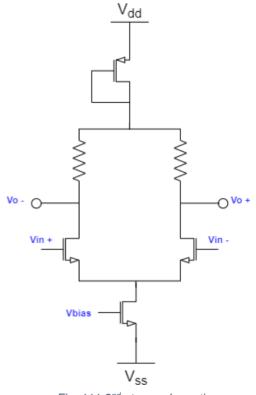

| Fig. 111             | 2 <sup>nd</sup> stage schematic                                     | 95 |

| Fig. 112             | FDA (2 <sup>nd</sup> Stage) layout                                  | 95 |

| Fig. 113             | hysteresis block schematic                                          | 96 |

| Fig. 114             | Hysteresis comparator layout                                        | 96 |

| Fig. 115             | NOR gate schematic                                                  | 96 |

| Fig. 116             | NOR gate layout                                                     | 96 |

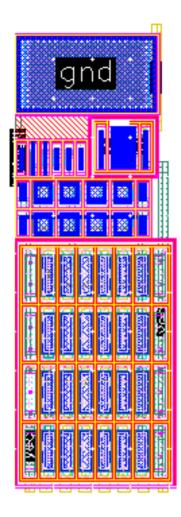

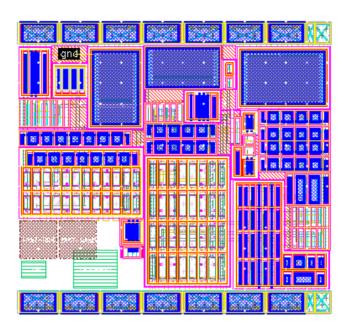

| Fig. 117             | Whole comparator layout                                             | 97 |

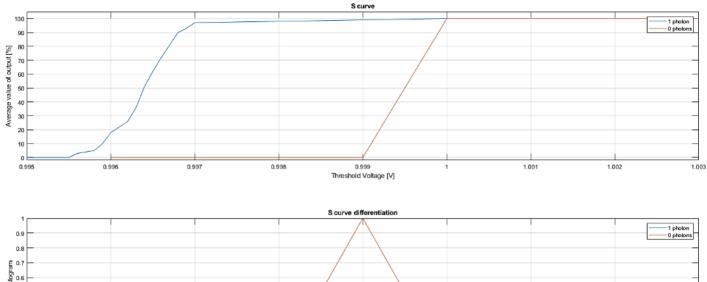

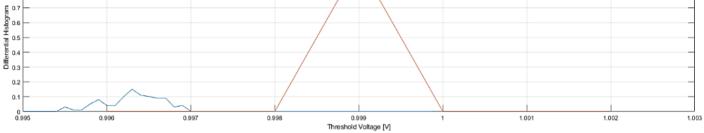

| Fig. 118 parasitics. | S curve and differential histogram of the comparator with extracted |    |

| Fig. 119             | Fitting histogram to a normal distribution                          | 99 |

| Fig. 120             | S curves in channel schematic10                                     | 01 |

| Fig. 121             | Fitting to a distribution in channel schematic10                    | 02 |

| Fig. 122             | Distribution fitting for channel in extraction10                    | 03 |

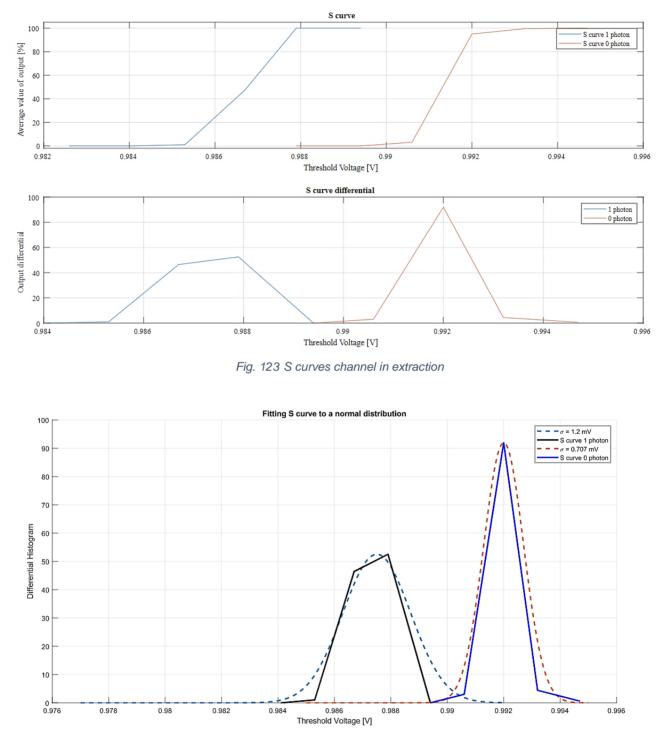

| Fig. 123             | S curves channel in extraction10                                    | 03 |

# **List of Tables**

| Table 1  | FIT ASIC specification                          | 17  |

|----------|-------------------------------------------------|-----|

| Table 2  | Comparator specifications                       | 18  |

| Table 3  | Comparator standalone results vs. initial specs | 80  |

| Table 4  | Summary of results for delay and jitter         | 93  |

| Table 5  | Comparison specs in schematic and extracted     | 98  |

| Table 6  | Jitter and delay for $vth = 975 mV$             | 100 |

| Table 7  | Jitter and delay for $vth = 990 mV$             | 100 |

| Table 8  | Jitter and delay for $vth = 996 mV$             | 101 |

| Table 9  | Delay and jitter in channel (Schematic)         | 102 |

| Table 10 | Jitter and delay for $vth = 975mV vth = 990mV$  | 104 |

| Table 11 | Jitter and delay with $vth = 996mV$             | 105 |

|          |                                                 |     |

# 1. <u>Introduction</u>

The aim of this thesis is to contribute to the development of analogue circuitry for a High Energy Cosmic-Radiation Detector (HERD), which is destinated to be one of the several space astronomy payloads onboard of the future China's Space Station (CSS). The scientific goals of HERD are to address fundamental key problems in physics: (1) to search for signatures of the annihilation/decay products of dark matter, (2) to measure precisely the energy spectra, composition of primary cosmic rays (from 30 *GeV* to 50 *PeV*) and (3) to provide wide field of view for monitoring of the high energy gamma-ray.

The HERD facility includes several detectors where the scintillating Fibre Tracker (FIT) is the baseline tracking system. ICC-UB is in charge of the design of the Front-End ASIC, referred to as BETA (fi**B**re track**E**r readou**T A**sic), which will be used for the Silicon Photo-Multiplier (SiPM) readout of the FIT. Recently, the BETA ASIC has also been chosen to generate the trigger signal for the plastic scintillator detector (PSD).

Besides the involvement of Chinese institutions, led by CSU and IHEP, several European institutes have expressed significant interest and provided scientific contribution to the project. They include researchers from Italy (Universities of Bari, Florence, Lecce, Pisa/Siena, Pavia, Perugia and Istituto Nazionale di Fisica Nucleare (INFN) and Gran Sasso Science Institute), Spain (CIEMAT Madrid) and Switzerland (University of Geneva and École Polytechnique Fédérale de Lausanne (EPFL)).

In this context, the core of the Master Thesis has been dedicated to the design of an *input Rail-to-Rail Hysteresis Comparator* for the BETA ASIC. Complementary to this, a *Current DAC* has also been designed for biasing the comparator. Finally, partial design of other biasing blocks has been done for the sake of further practice.

## 1.1. <u>Challenge</u>

After a century since the discovery of gamma rays, there is still long way from answering fundamental questions about their nature. Although, some large ground-based experiments (AUGER, IceCube and HESS/MAGIC) and space-borne missions (PAMELA, FERMI, AMS and DAMPE) have taken place, large systematic uncertainties were observed in indirect detection and unexpected features in the flux of cosmic ray electrons, protons and light ions have been observed recently in direct detection, which could indicate some missing pieces in the current cosmic ray acceleration and propagation models.

At present, there are very few individual flux measurements around the "knee" region ( $\sim 1 PeV$ ), but it is precisely in this region that interesting features in the total flux are being observed by ground-based experiments. Therefore, a new space instrument with  $\sim 10$  times larger acceptance compared to the current generation of missions is needed to measure precisely the spectrum and the elemental composition [1].

### 1.2. <u>HERD Project</u>

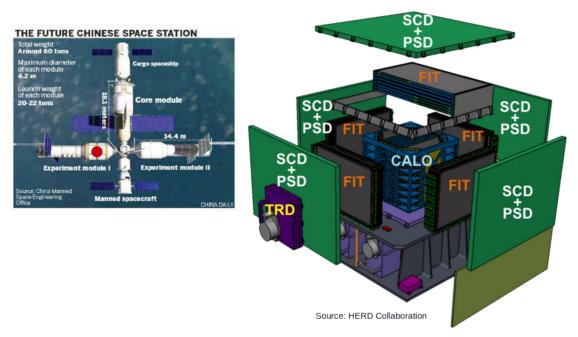

In the baseline design, HERD is composed of a deep 3-D cubic imaging calorimeter (CALO) made of LYSO crystals with an innovative design that ensures the same accuracy in the energy measurement and e/p separation for particles entering the detector from five out of the six sides. As *Fig.* 1 shows, on the top and on the four sides of the calorimeter, from outside to inside, there are a silicon charge detector (SCD) for the nuclei identification, a plastic scintillator detector (PSD) for veto and charge measurements and a scintillating fibre tracker (FIT). A Transition Radiation Detector (TRD), located on one of the lateral sides, is used for the energy calibration of TeV nuclei. The total weight of the HERD payload will be <3 tons, within a dimension envelope of  $\cong 2 \times 1.7 \times 1.2m^3$  (L x W x H) [1].

Fig. 1 The HERD detector onboard the "Experiment module I" of the Chinese Space Station

The sensor baseline solution is the use of Silicon Photomultiplier Arrays, that can stand the temperature, mechanical stress and radiation levels. The initial solution is based on the SciFi detector ones [2]. The already designed device has been redesigned to cope with the required dynamic range and number of cells for high energy signal measurement and needed energy resolution. Because of this, the current number cells used for SciFi detector (104) have been increased to around 1750 ( $15x15\mu m$  cell size) or 4000 ( $10x10 \mu m$  cell size).

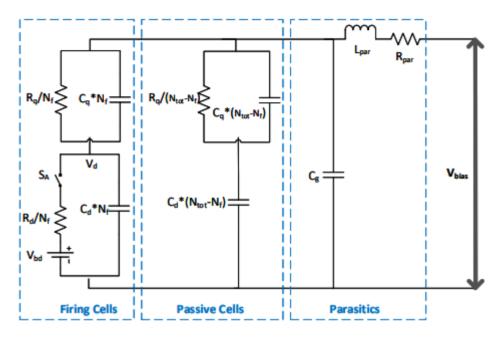

The SiPM can be electrically modelled as shown in *Fig.* 2. In this model we distinguish between two type of cells: firing cells, or cells that have been hit by a photon, and passive cells, cells that have not been hit and remain inactive. The single microcell is a single-photon avalanche photodiode (SPAD) that operates in Geiger mode and later quenched by an integrated resistor.

Fig. 2 Electrical model for SiPM (Figure taken from [3])

The electrical model of each cell, which is biased slightly above the breakdown voltage (over-voltage), includes the diode resistance  $R_d$  and capacitance  $C_d$ , the quenching resistance  $R_q$  and a small capacitance  $C_q$  and a switch  $S_A$  that closes the circuit when photons hit the sensor. Parasitic components are taken into account with  $L_{par}$ ,  $C_g$  and  $R_{par}$ .

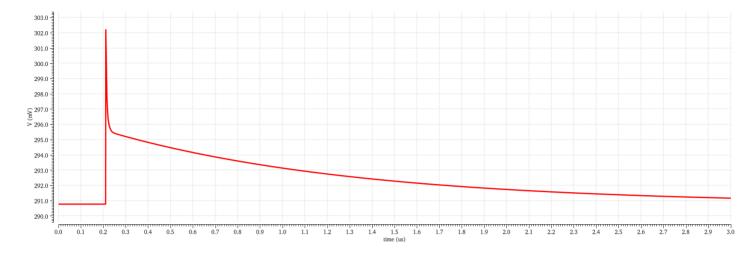

Initially,  $C_d$  is charged to SiPM bias voltage  $V_{bd}$ . When a photon hits a cell,  $S_A$  closes making the start of a breakdown event ( $N_f$  corresponds to the number of cells fired).  $C_d$  discharges through  $R_d$ , with a time constant  $R_d(C_d + C_q)$  (( $R_d \ll R_q$ )), and intermediate node voltage  $V_d$  decreases rapidly. At the same time, this generates a current that flows through the quenching resistor. This rapid current increase is the responsible for the fast rising edge of the readout current. As the quenching capacitor charges, the current flowing through the quenching resistor decreases, until it reaches a predefined threshold quenching current  $I_q$ and the bias of the SPAD is restored. This is modelled by opening the switch. This reset phase is determined by the discharging by two time constants: (1) when the avalanche is over,  $C_d$  is charged again to the biasing voltage  $V_{bd}$  with a fast time constant  $R_{load}C_{tot}^{1}$ . (2) During the recharging of the diode, the current through the quenching resistor starts decreasing exponentially with a slow time constant  $R_q(C_q + C_d)$ . The reset phase ends when  $V_D = V_{bias}$ . Fig. 3 illustrates the working principle of the SiPM [3].

<sup>&</sup>lt;sup>1</sup>  $C_{tot} = C_a + N_{tot}(C_d + C_a)$  and  $R_{load}$  is associated to the input impedance of the chip.

Fig. 3 Avalanche and reset phase in the fired cells of the SiPM

### 1.2.1. HERD -ASIC (BETA)

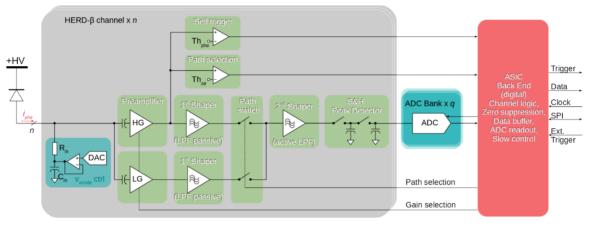

The main objective of the BETA ASIC is to perform the signal processing with very low power consumption, large dynamic range and a good signal to noise ratio (SNR) at the single photo-electron level. The 16-channel<sup>2</sup> ASIC is designed in a CMOS 130 nm technology with a total area of  $3.38 \times 1.96 \text{ }mm^2$ . It includes a trigger signal for the incoming photons and the measurement of charge captured by the SiPM, which is provided by a digitalized serial output. *Fig. 4* shows the block diagram of the chip's analogue Front-End.

The key parameter requirements are low power (**500**  $\mu$ *W*/*ch*), a high dynamic range of **12** *bits* (**676** *MIP* or **18748** *phe*), radiation hardness of at least **80** *Gray*<sup>3</sup> and *SNR* larger than **5** (linear) for operation. The chip must operate in a temperature range between  $-20 \ ^{\circ}C$  and  $50 \ ^{\circ}C$ . *Table 1* sums up the ASIC requirements.

This ASIC has been developed in TSMC **130** *nm* technology, a technology that is already qualified for higher radiation levels at CERN and it is used for the PACIFIC chip [4].

| Specification             | Target                            |

|---------------------------|-----------------------------------|

| Channels                  | 64                                |

| Input rate                | 1 kHz (max)                       |

| Power draw                | 0.5 mW/ch (1.2 V supply)          |

| Radiation Hardness        | 80 Gray                           |

| Dynamic Range             | 676 MIP (18748 phe) or 12<br>bits |

| Minimum detectable charge | 0.1 MIP (2 phe)                   |

<sup>&</sup>lt;sup>2</sup> The first prototype has 16 channels, and the final prototype will include 64 channels

<sup>&</sup>lt;sup>3</sup> It is defined as the absorption of one joule of radiation energy per kilogram of matter

| Slow control      | I2C                           |

|-------------------|-------------------------------|

| SNR for operation | > 5 (to set 3.5phe threshold) |

Table 1 FIT ASIC specification

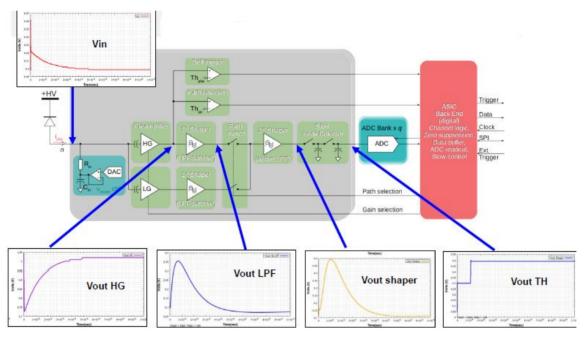

Fig. 4 Block diagram of the BETA ASIC

The Front-End architecture is based on a multi-gain system that reads the input current from each SiPM and converts it into voltage by means of a resistor divider circuit, one for each preamplifier. The output of the *High-Gain Amplifier* is used for triggering an incoming event and for selecting internally the gain path depending on the number of detected events. This multi-gain system intends to provide good amplification for low number of photons, as SNR is required for 1 photon. However, when hundreds of electrons are detected, the *High-Gain Amplifier* saturates the whole dynamic range available at the output. In order to prevent this, the *Low-Gain Amplifier* is selected by means of a path selection comparator.

The signal measurement is performed in several stages. A shaping stage is divided into an initial first-order LPF for each of the HG and LG preamplifiers. This LPF slows down the signal to give time to the digital circuitry to select between HG and LG signal paths by means of an analogue switch. The selected signal path is again filtered by a second-order LPF using a Sallen-Key topology. The peak amplitude is captured by a Track and Hold (T&H) circuit and the digitalization is made by means of a Wilkinson ADC.

## 1.3. <u>Objective</u>

The main objective of the thesis is to design a voltage comparator that will perform two different functionalities inside the chip: signal triggering and selection of the path to implement the multi-gain channel processing scheme. The target is to design a comparator

that can operate at different threshold levels along all dynamic range of the input signal. This is why a Rail-to-Rail input is required.

Due to the power source limitation of onboard electronic applications, the comparator power consumption will be limited to 50  $\mu$ *W*. The gain should be maximized for this power consumption.

Comparators are susceptible from small variations around the reference level due to the external and electronic noise. Thus, a hysteresis comparator has been proposed to provide robustness against noise variation. The hysteresis amplitude should be between 4 and  $6 \, mV$ .

The trigger comparator needs to be fast enough to follow the incoming events on the chip, so the desired delay will be around 15 *ns*. Also, the desired jitter is the minimum possible but, as it is a low power comparator, big jitter is inevitable at low energies. Even though, the target jitter below 100 *ps* at 10 events is fixed, which was required for the plastic scintillator detector. Finally, a single-photon *SNR* = 5 (*linear*) has been required.

The path selection comparator does not have particular constraints for the jitter, but it is important to select the gain path before the first shapers load the output. Although the delay is crucial for the correct performance of the ASIC, the comparator delay differ in one order of magnitude from the shaper delay (~250 *ns* in nominal configuration).

The specs are summarised in *Table 2*.

| Specification        | Target                       |

|----------------------|------------------------------|

| Power Supply         | $<50 \ \mu W$                |

| Gain                 | Maximise                     |

| Hysteresis amplitude | 4-6mV                        |

| Delay<br>Jitter      | < 15 ns<br>< 100 ps at 10 pe |

| SNR                  | 5 (linear)                   |

Table 2 Comparator specifications

Finally, the current DAC will be designed to provide the current bias of the comparator. This DAC will be configurable, leaving the option to modify the current consumption if needed. The initial target DC output current is  $1 \mu A$ .

#### 1.4. Gantt diagram

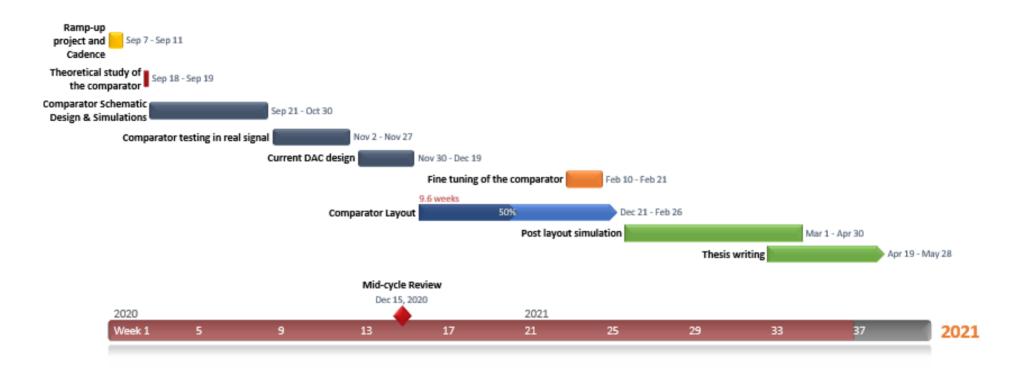

Fig. 5 shows the summary of the project main phases. It has taken around 9 months to complete it.

Fig. 5 Gantt diagram

# 2. <u>Theoretical analysis of the comparator</u>

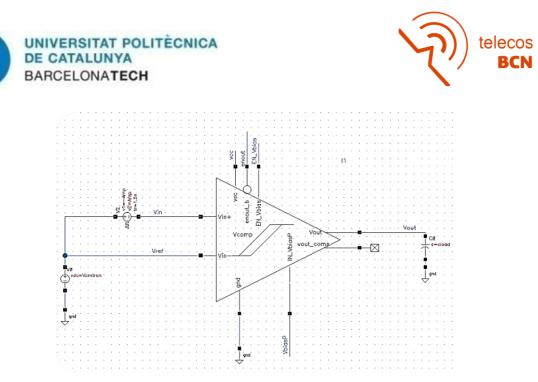

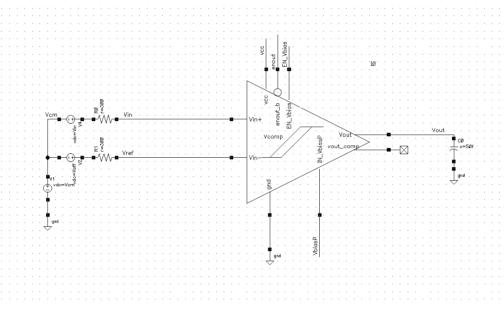

The Rail-to-Rail (R2R) Hysteresis Comparator is designed to perform a double functionality inside the chip: acting as a trigger comparator and selection of the path to implement the multi-gain channel processing scheme.

*Fig. 6* shows the signal waveforms expected after each block. The SiPM models the incoming photons in an exponential shaped signal, and the *High-Gain Amplifier* and *Low-Gain Amplifier* amplify, as well as invert, the signal according to their respective gains. The first low pass filter eliminates the high-frequency components, making the output signal slower. The comparators come into picture during the time the low-pass filter is shaping the signals.

Fig. 6 Block diagram with input and output signals

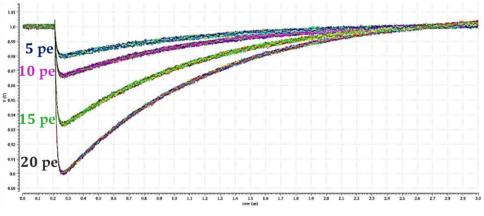

As it can be seen in *Fig. 6,* the input signal at the comparators is the one at the output of the *High-Gain Amplifier*. It is an inverted exponential pulse, which baseline (input DC level) is at 1 *V*. The amplitude at the output of the *High-Gain Amplifier* depends linearly on the number of photons, where the amplitude increases about 5 *mV* with each photon.

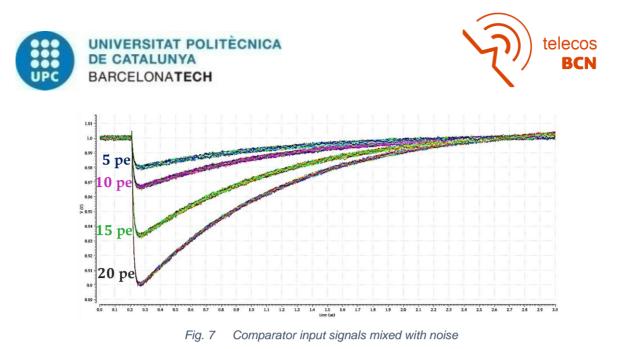

*Fig.* 7 shows the input signal at the comparator in case of different number of photons (or events).

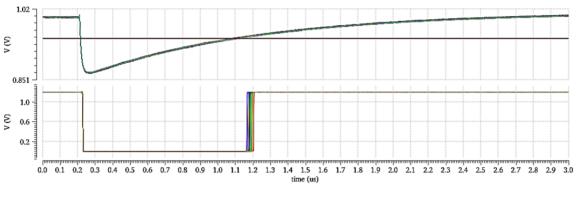

*Fig. 8* illustrates the principle of working of the comparator. The incoming signal is mixed with noise, which produces the timing variation in the output response. This time variations will be approached in the next chapter, when we study the noise in the comparator.

Fig. 8 Comparator input and output signals mixed with noise

Designing a single comparator means that it will need to work for very different input common mode voltages: the reference voltage of the trigger comparator will be near the DC level of the input signal whereas the reference of the path selection comparator will be very far.

The trigger comparator is responsible for sending a pulse to the digital backend when an event is detected. The threshold voltage level will be set according to the minimum number of events that can be detected. However, in order to prevent triggering due to Dark Count<sup>4</sup> a safety margin needs to be left. For the correct operation and synchronization among the rest of the blocks, this comparator has certain specifications that have been explained in the previous section.

On the other hand, the path switching comparator is responsible to switch from the *High Gain* path to the *Low-Gain* path when the input energy level is high enough. The reason for

<sup>&</sup>lt;sup>4</sup> Dark Count is an undesired effect of SiPMs, where spontaneous electron-hole pairs are generated due to the thermal noise. The frequency at which these e/h pairs appear is called *Dark Count Rate*.

this is that the the chip has a multi-gain system, where both paths amplify and shape the signal. The high gain is needed to detect low number of photons, but when higher energies are detected the *High-Gain Amplifier* saturates the whole dynamic range (power supply 1.2 V) available. At this time, the path switching comparator sends a command to the backend so that it chooses the signal coming from the *Low-Gain* path. Although this comparator is not as demanding as the trigger comparator, the time response is critical here, because it needs to switch before the low pass filter modifies the signal. *Fig. 9* illustrates an example of gain path switching. In this example the path should be switched when 200 events are detected.

Gain switching

Fig. 9 Example of gain switching

As the baseline of the incoming exponential signal will be 1 V, the threshold of the trigger comparator will be around 900 mV, while in the path selection comparator it will be around 100 mV. As the first one is the most demanding, the next sections will be devoted to its study.

The design of this comparator is entirely based on topologies used in other readout ASICs, such as FASTIC and HREFLXTOT. However, the design for HERD-BETA has been done at 130 *nm* node (TSMC), whereas FASTIC and HREFLXTOT have been manufactured at 65 *nm* (TSMC) and 180 *nm* (XFAB) [7] respectively. Another novelty is that low power requirements for the comparator (power supply 1.2 V), same as in FASTIC, while HREFLXTOT was fed with 1.8 V.

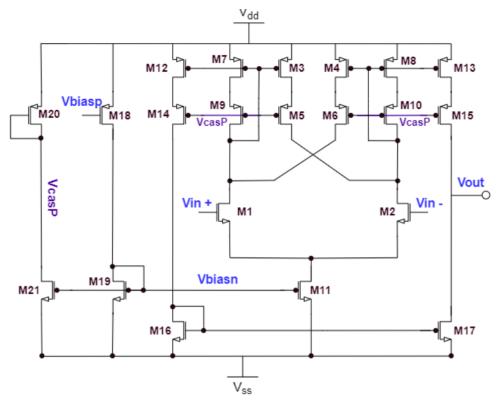

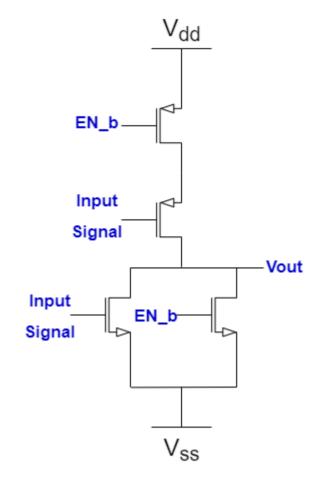

The comparator consists of four cascaded stages, including an enable bit buffer.

The first stage is a R2R input Fully Differential Amplifier (FDA) and the second stage is a basic FDA. The aim of the first two stages is to amplify the difference between the input signals, since the comparators work with high differential voltages. The reason we want

R2R input is that the baseline of the incoming signal is fixed at 1 V, and depending on the signal energy level, the input pulse may cover all the dynamic range. The second stage input does not need to be rail to rail, since the output of the first stage is not Rail-to-Rail and thus only a simple FDA with nMOS differential pair is used. Finally, the third stage is a hysteresis comparator, necessary to prevent the output oscillates due to the input signal fluctuations -mainly due to noise- around the threshold level. A NOR gate provides the possibility to set the output to zero and thus disable the comparator.

Fig. 10 shows the comparator is composed by 4 stages (from left to right):

- Rail to rail fully differential amplifier

- Classical fully differential amplifier

- Comparator with hysteresis

- Output NOR gate

For ease of convenience, the theoretical analysis will begin with the FDA, as the first stage is in practice an enhancement of it.

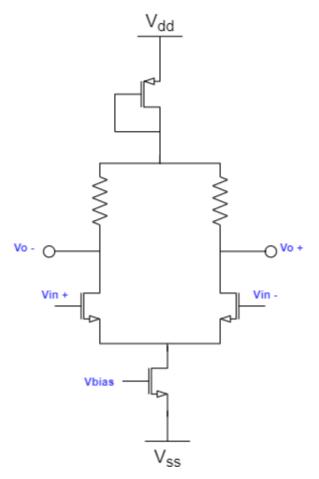

### 2.1. Fully differential amplifier with resistive load

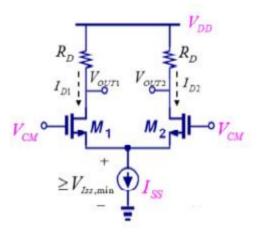

Fig. 11 Simple fully differential amplifier

### Working principle

The basic fully differential amplifier topology consists of a differential pair biased with a current source and loaded with resistors. In this case, the sources are biased with the current generated by the tail transistor, while the resistors convert the tail current into voltage producing a differential output voltage. The circuit is closed by a diode connected pMOS transistor, which helps to decrease the DC output voltage level. This is a method to ensure that next stage does not need input Rail-to-Rail. The initial circuit analysis does not include this diode, so in the end the general equation is modified to take into account the effects it may produce. The analysis carried out in this section is based on the subject *Advanced Analog Circuit Techniques* by Xavier Aragones.

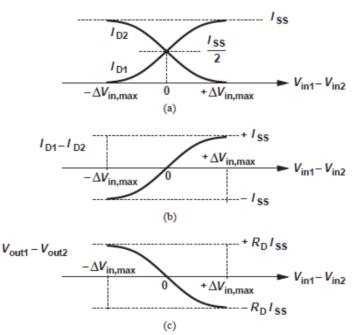

*Fig.* 12;*Error!* No se encuentra el origen de la referencia. sketches the output differential v oltage dependence on the differential input as a consequence of DC currents  $I_{D1}$  and  $I_{D2}$  above.

Fig. 12 (a) Response of MOS differential pair to very positive input, (b) response of MOS differential pair to very negative input, (c) qualitative plots of currents and voltages. (Figure from B. Razavi, Fundamentals of Microelectronics )

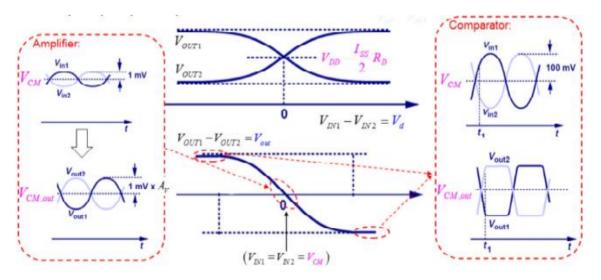

This circuit can operate in two different regimes. As small-signal amplifier or as a comparator. For amplification, the region of interest is the linear region of the amplifier output response, thus, small differential voltages. In case we want a comparator, this is, obtaining either a "large" or "small" signal depending on the input values, we should operate with large differential signals.

Fig. 13 Circuit behaving as amplifier or as comparator (Figure from B. Razavi, Fundamentals of Microelectronics)

#### DC analysis

For a linear operation, we need transistors M1 and M2 polarized in the saturation region, which limits the maximum common-mode input voltage, as shows *Fig.* 14:

Fig. 14 Basic fully differential amplifier (Figure from B. Razavi, Fundamentals of Microelectronics)

$$V_{DS} \ge V_{GS} - V_T$$

$$V_D \ge V_G - V_T$$

$$V_{CM} = V_G \le V_D + V_T$$

$$V_{CM} \le V_{DD} - \frac{I_{SS}}{2}R_D + V_T$$

We need to leave room for the signal, so:

$$V_{CM} + v_{in} \le V_{DD} - \left(\frac{I_{SS}}{2} + i_d\right) R_D + V_T$$

Where  $v_{in}$  and  $i_d$  are the positive value of the differential signal amplitude and differential current, respectively.

In our case, the diode connected transistor changes slightly the equation

1

$$V_{CM} + v_{in} \le V_{DD} - \left(\frac{I_{SS}}{2} + i_d\right) R_D + V_T - V_{DS_{sat,diode}}$$

The minimum common-mode voltage is set by the current source:

$$V_{CM} - V_{GS} \ge V_{I_{SS,min}}$$

$$V_{CM} \ge \sqrt{\frac{I_{SS}}{K}} + V_T + V_{I_{SS,min}}$$

Actually

$$V_{CM} - v_{in} \ge \sqrt{\frac{I_{SS}}{K}} + V_T + V_{I_{SS,min}}$$

The circuit thus behaves linearly for small values of  $\Delta V_{in}$  and becomes completely nonlinear for  $\Delta V_{in} \ge \Delta V_{in,max}$ . In other words,  $\Delta V_{in,max}$  serves as an absolute bound on the input signal levels that have any effect on the output.

Fig. 15 Variation of (a) drain currents, (b) the difference between drain currents, and (c) differential output voltage as a function of input. (Figure from B. Razavi, Fundamentals of Microelectronics)

#### AC analysis

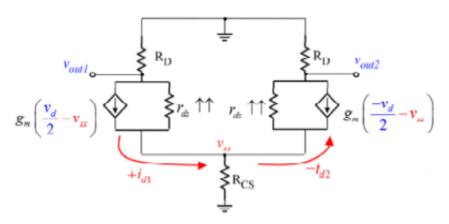

*Fig. 16* shows the small signal equivalent circuit, which can be simplified by observing that node VSS is a virtual ground. This simplification comes from the observation that as far as the differential variation  $V_d$  is small and circuit symmetry is preserved, the current variation in M1 will be fully absorbed by the current variation in M2.

Fig. 16 small signal model of the FDA (Figure from slides of AACT subject, X. Aragonés)

This observation greatly simplifies the analysis of the former small-signal equivalent, which now reduces to two independent sub circuits, that can be analysed separately.

Circuit analysis with virtual ground is straightforward.

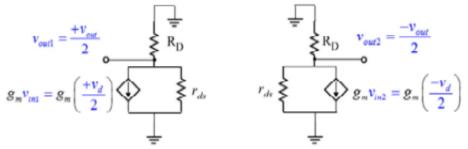

Fig. 17 simplified half circuit FDA (Figure from slides of AACT subject, X. Aragonés)

$$v_{out1} = -g_m \frac{v_d}{2} (r_{ds} || R_D)$$

$$v_{out2} = g_m \frac{v_d}{2} (r_{ds} || R_D)$$

$$A_{v_d} = \frac{v_{out1}}{v_d} = \frac{v_{out1} - v_{out2}}{v_d} = -g_m (r_{ds} || R_D) \cong -g_m R_D$$

The obtained result for the gain is the same as that of the single-ended differential amplifier, but the total  $I_{SS}$  is doubled now. Also, note the 180° phase inversion can be easily removed just by reversing the definition of the positive and negative output terminals, i.e.  $v_{out} = v_{out2} - v_{out1}$ .

Adding load capacitances  $C_L$  at the output nodes, BW can be estimated. Virtual node and half circuit analysis can still be used, as far as symmetry is preserved. Again, the same expression as in a single-ended common-source stage are obtained (*Fig. 18*).

Fig. 18 Adding capacitances at output, for BW estimation. (Figure from slides of AACT subject, X. Aragonés)

$$A_{v_d} = -g_m(R_D \mid\mid Z_{C_L} \mid\mid r_{ds}) = \frac{-g_m(R_D \mid\mid r_{ds})}{1 + j\omega(R_D \mid\mid r_{ds})C_L}$$

$$BW \cong |\omega_{pout}| = \frac{1}{(R_D \mid\mid r_{ds})C_L} \cong \frac{1}{R_D C_L}$$

Looking again back to *Fig. 11* the pMOS diode placed on top does not alter the expressions for the gain and the bandwidth, as the drain node could be considered as virtual ground. The only effect this diode will produce is to decrease the output DC voltage level of the amplifier.

#### 2.2. <u>Rail-to-Rail Fully Differential Amplifier</u>

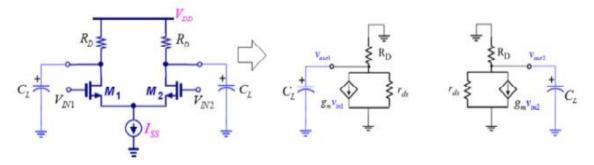

Fig. 19 R2R FDA used in the first stage

The architecture in *Fig. 19* is similar to previously analysed amplifier. The only difference is that a pMOS differential pair is added, and the amplified signal is copied by a simple

current mirror. The transistor above the differential pair acts as a current source. As already said, the diode connected transistor limits the voltage excursion at the output.

#### DC analysis

The common mode range that covers the nMOS pair has already been studied. For the pMOS differential pair a similar derivation can be made.

The minimum common mode that operates the pMOS pair is determined by the current mirror:

$$|V_{DS}| \le |V_{GS}| + |V_{TP}|$$

$$V_D \le V_G + |V_{TP}|$$

$$V_{CM} = V_G \ge V_D - |V_{TP}|$$

$$V_{CM} \ge V_{GS_{mirr}} - |V_{TP}|$$

We need to leave room for the signal, so:

$$V_{CM} - v_{in} \ge V_{GS_{mirr}} - |V_{TP}|$$

Where  $v_{in}$  is the positive value of the differential signal amplitude.

The maximum common-mode voltage is set by the pMOS tail transistor.

$$|V_{CM} + |V_{GS}| \le V_{DD} - V_{I_{SSP}}$$

Using the relation  $|V_{GS}| = \sqrt{\frac{I_{SSp}}{K_p}} + |V_{TP}|$

$$V_{CM} \le V_{DD} - V_{I_{SSp}} - \sqrt{\frac{I_{SSp}}{K_p}} - |V_{TP}|$$

Leaving room for the signal,

$$V_{CM} + v_{in} \le V_{DD} - V_{I_{SSp}} - \sqrt{\frac{I_{SSp}}{K_p}} - |V_{TP}|$$

In summary,

For pMOS:

$$V_{CM} - v_{in} \ge V_{GS_{mirr}} - |V_{TP}|$$

;  $V_{CM} + v_{in} \le V_{DD} - V_{I_{SSP}} - \sqrt{\frac{I_{SSP}}{K_p}} - |V_{TP}|$

For nMOS:

$$V_{CM} - v_{in} \ge \sqrt{\frac{I_{SS_n}}{K}} + V_{TN} + V_{I_{SS_n}}$$

;  $V_{CM} + v_{in} \le V_{DD} - \left(\frac{I_{SS_n}}{2} + i_d\right) R_D + V_{TN} - V_{DS_{sat,diode}}$

For the R2R Amplifier, the lower bound of the common mode is set by the pMOS pair and the upper bound is set by the nMOS pair.

### AC analysis

The AC analysis is also similar to the previous FDA. This time, however, we should add a parallel drain-to-source resistance corresponding to the transistor that copies the current flowing from pMOS branches. The drain-to-source resistance should be parallel-connected to nMOS differential pair  $r_{ds}$ . And the result of this, in parallel with  $R_D$  and diode resistance.

$$R_{out} = \left( r_{ds_{mirror}} || r_{ds_{diff}} \right) || R_D$$

To calculate the differential gain, we can use the expression for common-source configurations:  $g_m \cdot R_{out}$ . In this case, the transconductance is contributed by nMOS differential pair and its counterpart pMOS differential pair. Both transconductances are added, so that the overall transconductance is  $g_m = g_{m_n} + g_{m_p}$ .

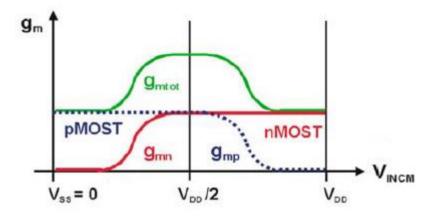

Fig. 20 Unequalized g<sub>m</sub> for differential pairs (Image taken from Willy Sanse, Analog Design Essentials)

*Fig.* 20 illustrates the fact that when a differential pair is off, their corresponding transconductance goes to zero, obviously. Now the overall transconductance of the circuit is no longer constant at the extreme common modes, which causes compensation problems<sup>5</sup>. This will make the transistor behave different in all the common modes. However, this is not critical for the design, as the comparator will work for fixed common mode voltages. Adding an equalization solution would make the power consumption increase and the benefit we would obtain is not that important.

<sup>&</sup>lt;sup>5</sup> Willy Sansen's book *Analog Design Essentials* proposes an ingenious solution to equalize the overall circuit transconductance. However, as it is not used in this topology, this part will be skipped.

Finally, the bandwidth of the R2R amplifier, in case we analyse it individually:

$$BW \cong \left| \omega_{pout} \right| = \frac{1}{R_{out}C_L} \cong \frac{1}{R_{out}C_L}$$

Although cascading amplifiers the voltage gain is multiplied, the bandwidth decreases.

### 2.3. <u>Hysteresis Comparator</u>

The hysteresis comparator is the core element of the comparator block, as it is responsible for detecting differences between incoming signals. This comparator is enhanced with hysteresis, which will provide robustness against variations caused by noise, ripple or other signal integrity faults. The following explanation is taken from Allen, and Holberg's book, *CMOS analog circuit design* [5].

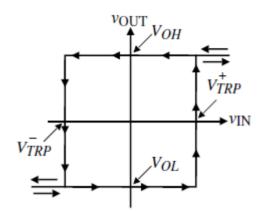

### Working principle: basics of hysteresis

One of the issues a comparator may face is the input signal fluctuations around the reference voltage level as a consequence of the noise. If the comparator is fast enough to follow the noise at the input, the output will show undesired glitches that do not correspond to the input signal change.. In this situation, hysteresis is needed in the comparator.

Hysteresis is the quality of the comparator in which the input threshold changes as a function of the input (or output) level. For instance, if the incoming signal surpasses the reference (threshold) level, and hence cause a transition at the output, the threshold voltage will be subsequently reduced or increased so that no transition happens unless the signal returns beyond this "new" threshold. This upper/lower reference levels are named *trip points*, which can be set by design. In practice, we could understand hysteresis as a guard zone around the threshold voltage that prevents the output from transitioning when the signal oscillates inside these guard zones.

This can be illustrated much more clearly with the diagram shown in *Fig. 21*. As the input starts negative and goes positive, the output does not change until it reaches the positive trip point,  $V_{TRP}^+$ . At this point, the effective trip point is moved to  $V_{TRP}^-$ , which means that the comparator will not switch state again until the input voltages decreases below this new trip point.

Fig. 21 Comparator transfer curve with hysteresis

The robustness of the hysteresis comparator is proved in *Fig.* 22, where glitches due to signal variations are eliminated.

Fig. 22 (a) Comparator response with noisy input. (b) Comparator response to a noisy input when hysteresis is added

Hysteresis can be implemented using various methods in a comparator, but all of them make use of positive feedback. The positive feedback can be introduced externally or internally. For convenience, only internal feedback will be analysed, since it is the topology that is implemented in the circuit we are interested in.

### Working principle: hysteresis comparator

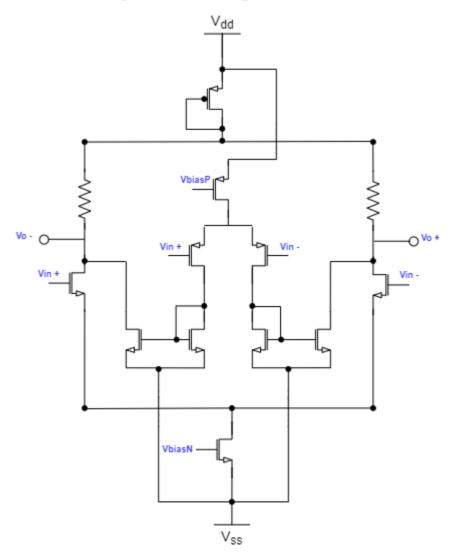

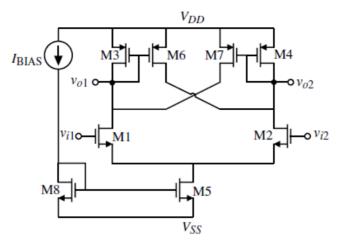

*Fig.* 23 shows the architecture of a comparator using internal feedback, where there are two paths of feedback. The first one, is current series feedback through the common source node of transistors M1 and M2, which is a negative feedback path. The second one, is the voltage shunt feedback through the gate-drain connections of transistors M6 and M7, which is a positive feedback path.

Fig. 23 Implementation of hysteresis using internal positive feedback in the input stage of a high-gain, openloop amplifier

The positive feedback factor needs to be higher than the negative feedback factor in order to have hysteresis, which is achieved by making the ratio  $\beta_6/\beta_3$  higher than one.

The following analysis shows the equations needed to associate the trip point values with transistor operating values and sizes.

Initially, we will assume that plus and minus supplies are used, and M1 is tied to ground and M2 has a variable voltage source. When the input of M2 is much less than zero, M1 is on and M2 is off. As M1 is on, M3 will also turn on. As M2 is off, there is no current flowing through M4, M7 neither M6. However, while M4 and M7 are off ( $v_{gs} = 0$ ), M6 is actually on ( $v_{gs} \sim v_{th}$ ). The reason why M6 is not giving current is because it is in deep ohmic region. Specifically, if  $i_{d_2} = i_{d_4} + i_{d_6}$ ,  $i_{d_6} = 0$  by force. The possibility is that M6 is in deep ohmic ( $v_{ds_6} = 0$ ).

As a consequence, all of the tail current  $i_5$  starts flowing from M1 and M3, so  $v_{02}$  is pulled high (remember  $v_{gs_4} = 0$ , or  $v_{ds_6} = 0$ ). The resulting circuit is shown in *Fig.* 24(*a*).

Fig. 24 (a) Comparator of Fig. 23 where  $v_{in}$  is very negative and increasing towards  $V_{TRP}^+$ . (b) Comparator of Fig. 23 where  $v_{in}$  is very positive and decreasing towards  $V_{TRP}^-$ .

When  $v_{in}$  starts to increase, some current starts flowing through M6, and some drain-tosource voltage will appear in M6. At this point M6 is still in ohmic, but its  $v_{ds_6}$  will be increasing towards saturation region, following the behaviour of  $I_D - V_{DS}$  curve. On the contrary, M4 will remain in deep subthreshold region until some charge starts accumulating in its gate. Indeed,  $v_{o2}$  starts decreasing slightly and the inflection point produces when M6 enters in saturation and copies the whole current of M3. Just beyond this point the comparator switches state.

To approximately calculate one of the trip points, the circuit must be analysed right at the point where  $i_2$  equals  $i_6$ . Mathematically this is:

$$i_{2} = i_{6} = \frac{(W/L)_{6}}{(W/L)_{3}}i_{3} = \frac{\beta_{6}}{\beta_{3}} \cdot i_{3} = \frac{\beta_{6}}{\beta_{3}} \cdot i_{1}$$

$$i_{SS} = i_{5} = i_{1} + i_{2} = \left(1 + \frac{\beta_{6}}{\beta_{3}}\right) \cdot i_{1}$$

This is,  $i_1$  is lower than  $\frac{i_{SS}}{2}$ . If we take  $\frac{\beta_6}{\beta_3} = 3$ ,  $i_1 = \frac{i_{SS}}{4}$  and  $i_2 = 3 \cdot \frac{i_{SS}}{4}$

Knowing the currents in both M1 and M2, it is easy to calculate their respective  $v_{GS}$  voltages. Since the gate of M1 is at ground, the difference in their gate–source voltages will yield the positive trip point as given below:

$$v_{GS1} = \left(\frac{2i_1}{\beta_1}\right)^{1/2} + V_{T1}$$

(1)

$$v_{GS2} = \left(\frac{2i_2}{\beta_2}\right)^{1/2} + V_{T2}$$

(2)

$$V_{TRP}^+ = v_{GS2} - v_{GS1}$$

Once the trip point is reached, the comparator changes state:  $v_{0_1}$  changes from low to high and  $v_{o_2}$  changes from high to low. During this short interval of time, the current in M1 decreases dramatically until there is no gate-to-source voltage in M1 nor M3 neither in M6. M6, however, continues in saturation during this time so, the current through M2, which was  $i_2 = i_6 + i_4$ , turns to be  $i_2 = i_4$ .

Finally, when  $v_{in}$  starts decreasing towards the threshold value, M7 will start conducting the same way M6 did previously, until it reaches saturation, when the comparator will switch state again, returning to the initial point.

The equivalent circuit in this state is shown in *Fig.* 24(*b*). To calculate the trip point, the following equations apply:

$$i_{7} = \frac{(W/L)_{7}}{(W/L)_{4}} i_{4}$$

$$i_{1} = i_{7}$$

$$i_{5} = i_{2} + i_{1} \qquad (i_{2} = i_{3})$$

i4)

Therefore,

$$i_4 = \frac{i_5}{1 + [(W/L)_7/(W/L)_4]} = i_2$$

$$i_1 = i_5 - i_2$$

Using Eqs. (1) and (2) to calculate  $v_{GS'}$  the trip point is

$$V_{TRP}^- = v_{GS2} - v_{GS1}$$

Note these equations do not take into account the effect of channel length modulation.

The differential stage described thus far is generally not useful alone and thus requires an output stage to achieve reasonable voltage swings and output resistance. There are a number of ways to implement an output stage for this type of input stage. One of these is given in *Fig.* 25. Differential-to-single-ended conversion is accomplished at the output and thus provides a Class AB type of driving capability.

Fig. 25 Complete comparator with internal hysteresis including an output stage

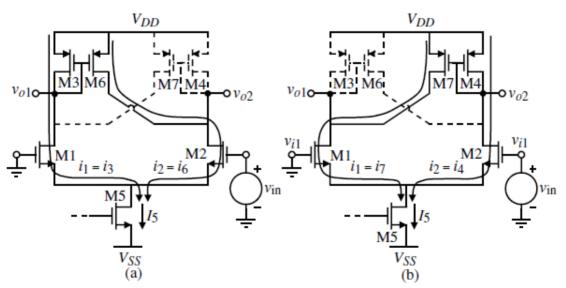

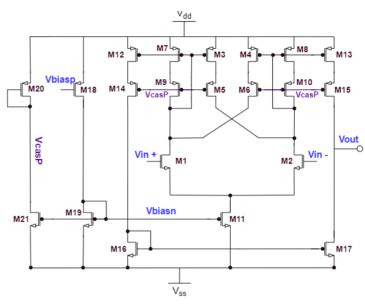

Fig. 26 illustrates the comparator actually being used in chip

Fig. 26 Hysteresis comparator

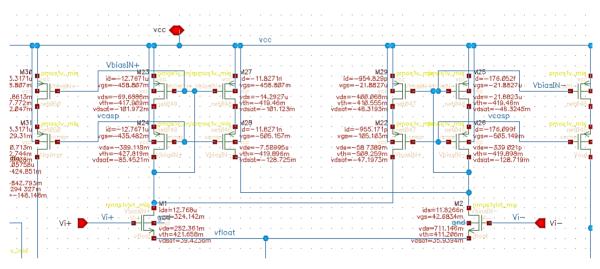

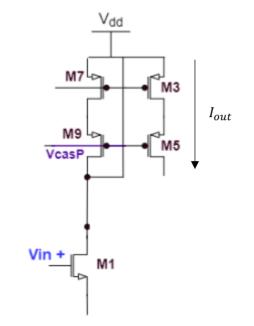

Indeed, our circuit uses a similar architecture, with some differences. One of the main differences is that it uses pMOS cascode transistors (M5, M9 and M6, M10) in the positive feedback path. The currents flowing through the voltage-shunt feedback transistors are copied to the first stage output by means of low-voltage current mirror configuration, which minimises the voltage necessary to keep the transistors in saturation and make it suitable for low power applications. First output differential signals are copied to the second stage. Finally, M16 copies the current to M17 with another current mirror, so that both differential signals are summed.

The circuit is biased externally through M18 and the input current is copied to tail transistor M11. The input current is also copied to M21 so that diode connected transistor M20 generates the biasing voltage for the cascode transistors current mirrors.

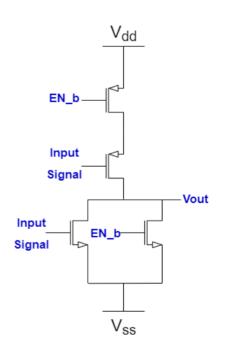

#### 2.4. <u>Output NOR gate</u>

Fig. 27 NOR gate

The NOR gate is a well-known logic gate that does not require further explanation. In our specific case it acts as a buffer that can be controlled with an enable (EN) bit. If EN = 1, the output is off and if EN = 0 the buffer will follow the input signal value, which will be high or low.

The load it will attack is very little, since the gate is connected to the digital backend. However, the signal path will add a considerable capacitance. A suitable sizing of the transistors that take into account the path load is required.

#### 2.5. <u>Current DAC</u>

As a complementary task, the design the current DAC is proposed. The current DAC consists of a digital-to-analogue converter that copies the current from a current reference. The digital-to-analogue converter gives an output current that corresponds to the bits selected externally. The generated current is copied through a current mirror and introduced in the comparator.

The digital-to-analogue converter is an IP block that has been already designed. It is a binary weighted 8 bit-DAC, which gives an output DC current of  $1 \mu A$ .

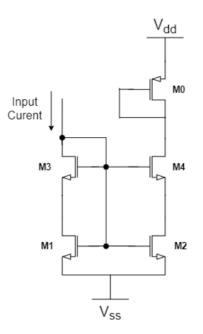

The current mirror that copies the current is a low-voltage cascode current mirror, which is shown in *Fig. 28*. However, in this topology the cascode transistors are biased directly at the same voltage as the drain.

Fig. 28 Low voltage current mirror

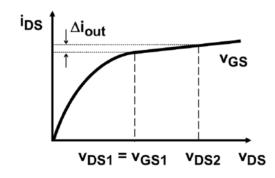

One of the limitations of simple current mirrors are the nonidealities due to  $V_{DS}$  difference between M1 and M2. *Fig.* 29 shows that  $I - V_{DS}$  curve is not actually constant due to channel length modulation. So, differences in  $V_{DS}$  introduce variations in the current copy.

Fig. 29 Copy error due to V<sub>DS</sub> difference (Figure taken from MND course)

The slope of the curve in saturation region is inversely dependent on the output resistance of the current mirror, i.e., the larger the output resistance the lower the slope will be and hence the copy error will be minimised. Therefore the cascode topology is introduced in the architecture.

Another requirement for current mirrors is that they need a minimum output voltage to operate. As we will see in next section, we will be operating in moderate inversion region, which makes it hard to calculate manually the operating points. Therefore, we will check the proper saturation of the current mirror in Section 4.2.

# 3. Methodology / project development

Following the discussion about the important aspects of the comparator, the comparator has been designed at transistor level. So, this section will be devoted to explaining the design procedure, and the followed criteria to choose the transistor dimensions. After this section, the rest of the chapter is dedicated to the simulations.

## 3.1. <u>Transistor level design of the comparator</u>

As we know, one of the most important challenges of this comparator is its low power consumption. As the power consumption is limited to  $50 \ \mu W$  and power supply is  $1.2 \ V$ , the total current consumption will be  $41.6 \ \mu A$ .

The core block of the comparator is the hysteresis comparator, so it seems reasonable to provide more current to this block. The next most important block would be the R2R Amplifier and finally the 2<sup>nd</sup> stage FDA. For an initial approximation, around half of the available current will be allocated to the hysteresis block, and the rest will be shared with the rest of the amplifiers:

$$I_{stg3} = 20 \ \mu A$$

$$I_{stg2} = 8 \ \mu A$$

$$I_{stg1} = 12 \ \mu A$$

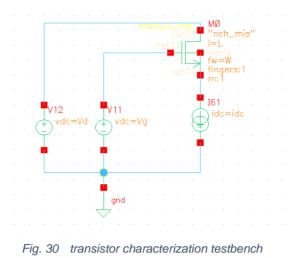

As the procedure to choose the transistor dimension, a current density sweep will be done, which is equivalent to analyse the transistor through the inversion regions. Concretely, a testbench will be generated where gate and drain voltages will be fixed. A DC current source will act as biasing current of the transistor. As we sweep this current value the source voltage will adapt to the current, and therefore we can extract the gate-to-source and drain-to-source voltages (and of course ensure the saturation of all transistors). These voltages will vary with transistor width and length. *Fig. 30* shows the testbench for the nMOS transistor characterization. The gate and drain voltages have been fixed to 1.2 *V*, and the width and length are variable. Also, an equivalent testbench is made for a pMOS transistor.

The first decision is to choose the region of inversion in which the transistor will operate. Plotting  $\frac{g_m}{I_d}$  for a wide bias current range, we can distinguish these regions of inversion.

Fig. 31  $\frac{g_m}{L}$  characteristic, from 1 nA to 10 mA

The weak inversion is the region where  $\frac{g_m}{I_d}$  is constant, strong inversion region is where  $\frac{g_m}{I_d}$  is minimum and the moderate inversion is the transitioning region. Clearly, the circuits in the comparator will operate in moderate inversion (~ 40  $\mu$ A).

The election of channel length is critical as well. In general, long channels are preferred where large impedances are needed, e.g. current mirrors. Short channels are more suitable if we care for switching speeds and low power designs. So, as a rule of thumb, the tail transistors will be long channel and the transistors where the signal travels will be short channel.

The width is also important: normally a bigger transistor has bigger transconductance, but it may switch slower as it includes more parasites.

For an initial design, the input DC voltages will be assumed at 0.6 V and the master current will be a current mirror with a large channel transistor for a good copy  $\left(\frac{W}{L}\right)_{mirror} = \frac{2 \ \mu m}{2 \ \mu m}$ .

The stages will be designed in order, so that the output voltages coincide with the following input voltages.

As the total current for the first stage is set to 12  $\mu A$ , and we are designing for 0.6 *V* common mode, each tail transistor will drive 6  $\mu A$ . Later, in simulations this ratio will probably be modified since we are interested in 1 *V* common mode. However, for an initial approximation we will set  $\left(\frac{W}{L}\right)_{M9} = \frac{12 \ \mu m}{2 \ \mu m}$  and  $\left(\frac{W}{L}\right)_{M10} = \frac{12 \ \mu m}{2 \ \mu m}$ .

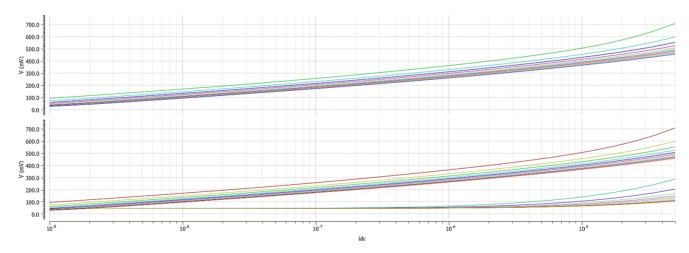

Looking into I-V curves in *Fig.* 32 and *Fig.* 32, we can look which is the needed  $V_{GS}$  and  $V_{DS}$  voltages to drive 12  $\mu$ A:  $V_{GS} = 400 \text{ mV}$ ,  $V_{DS} = 400 \text{ mV}$ ,  $V_{DSsat} = 142 \text{ mV}$  in case of pMOS.  $V_{GS} = 320 \text{ mV}$ ,  $V_{DS} = 320 \text{ mV}$ ,  $V_{DSsat} = 80 \text{ mV}$  in case of nMOS.

Each differential pair should drive 3  $\mu$ *A* and the transistors are sized according to this requirement. Besides, it is very convenient to maximise the transconductance, because the voltage gain depends directly on  $g_m$ . Finally, the transistor sizes are important, a big width will guarantee good  $g_m$  but will include many parasites as well. The length will be minimum since we want a fast comparator. Taking this into account  $W_{M1} = 6 \mu m$  seems a reasonable compromise, with  $g_{m,M1} = 70 \frac{\mu A}{V}$ .  $V_{GS} = 300 \text{ mV}$  and  $V_{DS} = 300 \text{ mV}$ , there is room for the differential pair polarization. For pMOS differential pair we can operate in a similar way.  $g_{m,M3} = 60 \frac{\mu A}{V}$

Fig. 32  $V_{GS}$  and  $V_{DS}$  voltages for different transistor sizes

Fig. 33 parameter values for 24 µm width pMOS

The other parameter that determines the gain is the output impedance of the amplifier, which is dominated by  $R_D$ . This should be a rather big resistance, but taking into account that too big transistors (> 50 k $\Omega$ ) may introduce distortion in the layout.

The mirror transistors will be designed with the same sizes as the differential pairs, with the risk that they can have an important  $V_{DS}$  mismatch, and hence a poor current copy. This voltage drop can be controlled with the resistor value. The resistor value will be quite large in order to compensate the small transconductance.

Finally, the pMOS diode will drive the whole  $12 \ \mu A$  and will limit the voltage excursion at the output. A drain-to-source voltage drop around  $330 \ mV$  will be chosen, so that the output does not reach the top rail. The initially chosen values will be the following:

$$\begin{pmatrix} \frac{W}{L} \\ \frac{W}{L} \end{pmatrix}_{M1} = \begin{pmatrix} \frac{W}{L} \\ \frac{W}{L} \end{pmatrix}_{M2} = \frac{6 \,\mu m}{130 \,nm}$$

$$\begin{pmatrix} \frac{W}{L} \\ \frac{W}{L} \end{pmatrix}_{M3} = \begin{pmatrix} \frac{W}{L} \\ \frac{W}{L} \\ \frac{W}{L} \end{pmatrix}_{M5} = \begin{pmatrix} \frac{W}{L} \\ \frac{W}{L} \\ \frac{W}{L} \\ \frac{W}{L} \end{pmatrix}_{M5} = \begin{pmatrix} \frac{W}{L} \\ \frac{W$$

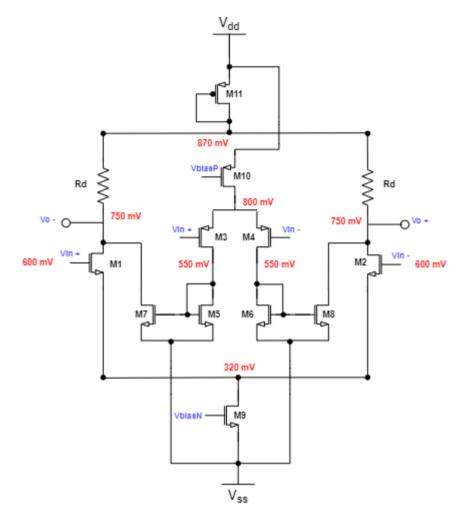

*Fig.* 34 shows the 1<sup>st</sup> stage circuit with approximate DC node voltages.

As studied in Section 2.1 the voltage gain is  $g_m R_D$ . The overall transconductance is the sum of  $g_{m,M1} + g_{m,M3} = g_m = 130 \frac{\mu A}{V}$ . The expected gain is  $A_v = 5.2$  (14.3 *dB*)

Fig. 34 1<sup>st</sup> stage design

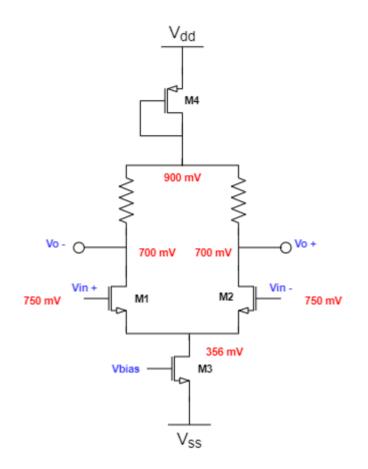

For the design of the second stage, we will follow the same considerations. The current that will drive the 2<sup>nd</sup> FDA is 8  $\mu$ A, which requires  $W_{M3} = 16 \,\mu m$  and  $L_{M3} = 2 \,\mu m$ . As we want a good transconductance with little parasitics, we choose  $W_{M1} = 5 \,\mu m$  with  $g_{M1} = 90 \,\mu A/V$ . The diode connected transistor is designed using the same criteria. Finally, the resistance will be maximised to provide proper gain. The chosen dimensions are:

$$\left(\frac{W}{L}\right)_{M1} = \left(\frac{W}{L}\right)_{M2} = \frac{5 \ \mu m}{130 \ nm}$$

$$\left(\frac{W}{L}\right)_{M3} = \frac{16 \ \mu m}{2 \ \mu m}$$

$$\left(\frac{W}{L}\right)_{M4} = \frac{10 \ \mu m}{130 \ nm}$$

$$R_D = 50 \ k\Omega$$

*Fig.* 35 shows the 2<sup>nd</sup> stage circuit with approximate DC node voltages.

The expected gain is  $A_v = 4.5 (13 \, dB)$

Fig. 35 2<sup>nd</sup> stage design

Following the 2<sup>nd</sup> stage, the hysteresis block is designed.

M18 will copy the current from the current reference and M19 replicates this current into the tail transistor. Also, the current will be replicated in M21, so that M20 can generate the necessary voltage to bias the cascodes in the current mirror. M18 and M19 will be identical to the mirror transistor in the master. M21 will also be the same size, as it is copying the current from the adjacent branch:  $\left(\frac{W}{L}\right)_{M18} = \left(\frac{W}{L}\right)_{M19} = \left(\frac{W}{L}\right)_{M21} = \frac{2 \ \mu m}{2 \ \mu m}$ .

The tail transistor needs to drive 20  $\mu$ *A* current, but output branches need to be taken into account as well. However, only one output branch will drive current each time the comparator switches state. Hence, the tail current will be allocated 10  $\mu$ *A*.  $W_{M11} = 20 \,\mu m$  and  $L_{M11} = 2 \,\mu m$ . The biasing branches would consume 1  $\mu$ *A* each but we will omit it.

The differential pair will provide the transconductance of the circuit. Again, only one of the pairs will drive the total tail current (the same way as the outputs). Considering the input capacitance of the pairs needs to be minimised:  $W_{M1} = 6 \ \mu m$  and  $L_{M1} = 130 \ nm$  with  $g_m = 216 \ \mu A/_V$ .

The voltage drop in the current mirrors that implement the positive feedback is around 500 *mV*. Assuming the drain-to-source voltage will be equally divided and they can not be too large because the speed of the comparator depends on how fast M3 and M5 enter in saturation, we choose  $W_{M7} = W_{M9} = 5 \,\mu m$ . Although they act like current mirrors, the speed is more important than an exact current copy. Hence, short transistor is used.  $V_{GS,M9}$  is around 350 *mV*, which means  $V_{casp} \approx 600 \, mV$ . Hence, we choose  $W_{M20} = 1 \,\mu m$  and  $L_{M20} = 2 \,\mu m$ , so that it has the required  $V_{DS}$  drop. Also, to provide hysteresis,  $\beta_3$  and  $\beta_5$  need to be higher than  $\beta_7$  and  $\beta_9$ , so as an initial value, we will double the widths and then calculate the resulting hysteresis with simulations. For a good current copy, M16 and M17 will be long channel.