Portland State University PDXScholar

**Dissertations and Theses**

**Dissertations and Theses**

3-1997

# Automatic Synthesis of VLSI Layout for CMOS Continuous-Time Filters

Wei Han Portland State University

Follow this and additional works at: https://pdxscholar.library.pdx.edu/open\_access\_etds

Part of the Electrical and Computer Engineering Commons Let us know how access to this document benefits you.

#### **Recommended Citation**

Han, Wei, "Automatic Synthesis of VLSI Layout for CMOS Continuous-Time Filters" (1997). *Dissertations and Theses.* Paper 5746. https://doi.org/10.15760/etd.7617

This Thesis is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. Please contact us if we can make this document more accessible: pdxscholar@pdx.edu.

# THESIS APPROVAL

The abstract and thesis of Wei Han for the Master of Science in Electrical and Computer Engineering were presented on January 6, 1997, and accepted by the thesis committee and the department.

| COMMITTEE APPROVALS: |                            |

|----------------------|----------------------------|

| D                    | r. W. Robert Daasch, Chair |

|                      |                            |

| D                    | or. Rolf Schaumann         |

| -                    |                            |

| D                    | Pr. Tom Schubert           |

|                      |                            |

Representative of the Office of graduate Studies

# DEPARTMENT APPROVAL:

by

Rolf Schaumann, Chair Department of Electrical Engineering

ACCEPTED FOR PORTLAND STATE UNIVERSITY BY THE LIBRARY

on 19 March 1997

#### ABSTRACT

AN ABSTRACT OF THE THESIS of Wei Han for the Master of Science in Electrical and Computer Engineering presented on January 6, 1997.

Title: Automatic Synthesis of VLSI layout for CMOS Continuous-Time Filters.

Automatic synthesis of digital VLSI layout has been available for many years. It has become a necessary part of the design industry as the window of time from conception to production shrinks with ever increasing competition. However, automatic synthesis of analog VLSI layout remains rare.

With digital circuits, there is often room for signal drift. In a digital circuit, a signal can drift within a range before hitting the threshold which triggers a change in logic state. The effect of parasitic capacitances for the most part, hinders the timing margins of the signal, but not its functionality. The logic functionality is protected by the inherent noise immunity of digital circuits.

With analog circuits, however, there is little room for signal drift. Parasitic directly influence signal integrity and the functionality of the circuit. The underlying problem, that the automatic VLSI layout programs face, is how to minimize this influence.

This thesis describes a software tool that was written to show that the minimization of parasitic influence is possible in the case of automatic layout of continuous-time filters using transconductance-capacitor methods.

# AUTOMATIC SYNTHESIS OF VLSI LAYOUT FOR CMOS CONTINUOUS-TIME FILTERS

by

Wei Han

.

A thesis submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE in ELECTRICAL AND COMPUTER ENGINEERING

> Portland State University 1997

#### ACKNOWLEDGMENTS

I would like to acknowledged the previous work done on this project by Martine Wedlake, Dr. W. Robert Daasch and David Lyle Robinson. They were the real pioneers in this tool. I was fortunate to be the one to inherit the work in progress. I wish to express my deepest gratitude to my advisor, Dr. Daasch, for his patience and perseverance on my behalf, his timely suggestions, and his properate guidance. I would also like to thank Dr. Schaumann for his help me to gain knowledge beyond the research area.

My sincere appreciation goes to the members of the committee, Dr. Schaumann and Dr. Schubert for their helpful comments and understanding. I am very grateful to David Chiang, Girish Chandrasekaran for their special contribution in build the standard cell library. The tremendous works they had done have provided me a lot of convenience in my thesis work. I also thank my co–researcher Jonathon W. Walker, all the help and encouragement he provided are great appreciated.

Finally, my mother and my sister deserve my special thanks for their devotion, support, understanding throughout this whole project. And I also thank my good friends for their love, encouragement and understanding. I will forever be indebted to them for all that they have done.

# **TABLE OF CONTENTS**

| LIST OF TABLES                     | viii |

|------------------------------------|------|

| LIST OF FIGURES                    | x    |

| CHAPTER                            |      |

| 1 INTRODUCTION                     | 1    |

| 1.1 MOTIVATION AND OBJECTIVE       | 1    |

| 1.2 THESIS OUTLINE                 | 2    |

| 2 BACKGROUND AND CONCEPT           | 4    |

| 2.1 ANALOG IC FILTERS              | 4    |

| 2.1.1 Types of Filters             | 4    |

| 2.1.2 CMOS Continuous–Time Filters | 7    |

| 2.2 FILTER REALIZATION             | 10   |

| 2.2.1 LC Ladder                    | 10   |

| 2.2.2 Normalization                | 11   |

| 2.2.3 Element Substitution         | 13   |

| 2.3 LAYOUT AUTOMATION              | 14   |

| 2.4 FILTER DESIGN AUTOMATION       | 16   |

| 3 OTACC                            | 18   |

| 3.1 CFL                            | 18   |

| 3.1.1 What is CFL ?                | 18   |

| 3.1.2 CFL Enhancement              | 20   |

| 3.2 BASIC STRUCTURE OF OTACC                         | 21 |

|------------------------------------------------------|----|

| 3.3 INPUT AND OUTPUT INTERFACE OF OTACC              | 22 |

| 3.3.1 FiltorX Interface                              | 22 |

| 3.3.2 Command Line and Options                       | 23 |

| 3.3.3 Technology File Scanning                       | 23 |

| 3.3.4 Error Message Coding                           | 24 |

| 3.4 SYMBOLIC LAYOUT AND TILE GENERATION              | 24 |

| 3.5 OPERATORS                                        | 28 |

| 3.5.1 Software Implementation and Circuit Synthesis  | 28 |

| 3.5.2 Data Communication                             | 31 |

| 3.6 FLOOR PLANNING                                   | 32 |

| 3.6.1 Series <i>LC</i> Block                         | 32 |

| 3.6.2 Shunt <i>LC</i> Block                          | 33 |

| 3.6.3 Folded Layout                                  | 34 |

| 3.6.4 Final Assembly                                 | 37 |

| 4 TESTING AND SIMULATION RESULTS                     | 39 |

| 4.1 Fourth–Order Elliptic LC Lowpass Filter          | 40 |

| 4.2 Eighth–Order Inverse Chebyshev LC Lowpass Filter | 47 |

| 4.3 Third–Order Bandpass Filter                      | 53 |

| 4.3 Summary                                          | 58 |

| 5 CONCLUSIONS                                        | 59 |

| 5.1 LIMITATION                                       | 60 |

v

|                                                                    | vi |

|--------------------------------------------------------------------|----|

| 5.2 FUTURE WORK                                                    | 61 |

| REFERENCES                                                         | 62 |

| APPENDIX A                                                         |    |

| CFL ROUTING FUNCTION ENHANCEMENT                                   | 64 |

| A.1 General Description                                            | 64 |

| A.2 Application                                                    | 65 |

| A.3 List of New Functions                                          | 67 |

| APPENDIX B                                                         |    |

| OTACC STACK ELEMENT STRUCTURE                                      | 68 |

| APPENDIX C                                                         |    |

| OTACC COMMAND OPTIONS                                              | 70 |

| APPENDIX D                                                         |    |

| TECHNOLOGY FILES FOR DIFFERENT OTAS                                | 71 |

| D.1 OTA I                                                          | 71 |

| D.2 OTA II                                                         | 72 |

| D.3 OTA III                                                        | 73 |

| APPENDIX E                                                         |    |

| RETURN CODES OF OTACC                                              | 75 |

| APPENDIX F                                                         |    |

| LAOUT OF DIFFERENT FILTERS                                         | 77 |

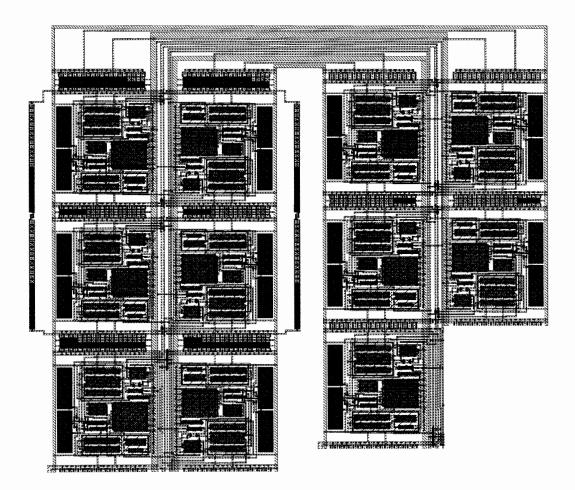

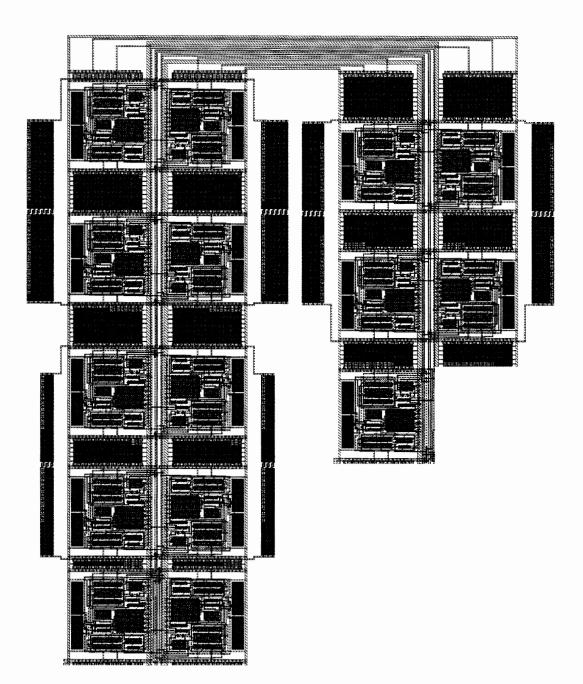

| F.1 Layout of Fourth-Order Elliptic LC Lowpass Filter Using OTA I. | 77 |

| F.2 Layout of Fourth-Order Elliptic LC Lowpass Filter Using OTA II | 78 |

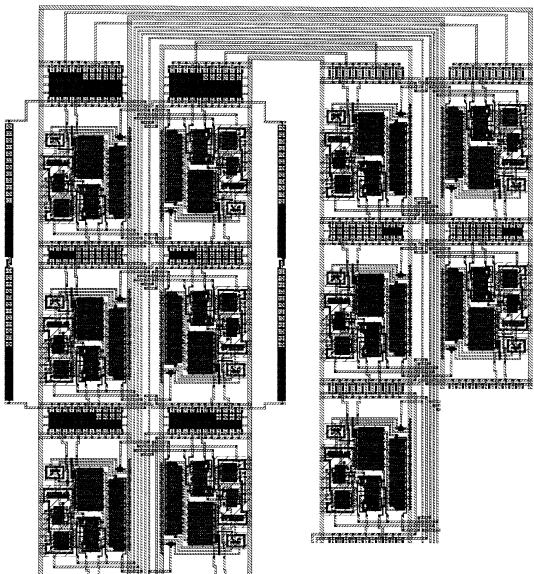

| F.3 | Layout of Fourth-Order Elliptic LC Lowpass Filter Using OTA III | 79 |

|-----|-----------------------------------------------------------------|----|

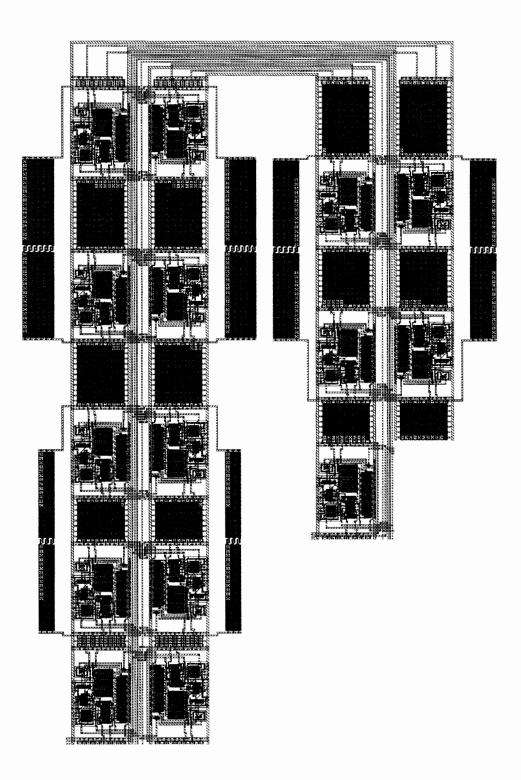

| F.4 | Layout of Eighth-Order Inverse Chebyshev Lowpass Filter Using   |    |

|     | OTA I                                                           | 80 |

| F.5 | Layout of Eighth–Order Inverse Chebyshev Lowpass Filter Using   |    |

|     | OTA II                                                          | 81 |

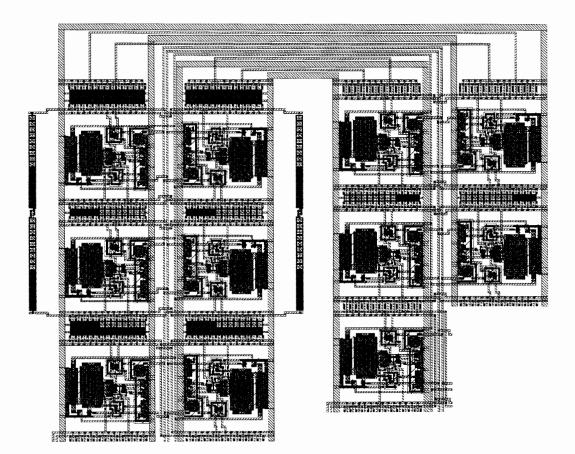

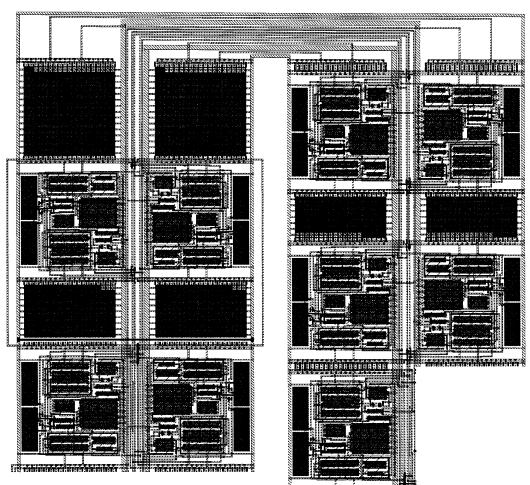

| F.6 | Layout of Third–Order Bandpass Filter Using OTA II              | 82 |

| F.7 | Layout of Third–Order Bandpass Filter Using OTA II              | 83 |

# LIST OF TABLES

| TABLEPAG |                                                                          |    |

|----------|--------------------------------------------------------------------------|----|

| 3.1      | Number of elements in OTACC stack structure                              | 21 |

| 3.2      | OTACC input from FiltorX                                                 | 23 |

| 3.3      | Route tiles for OTACC                                                    | 27 |

| 3.4      | Stack operators in OTACC                                                 | 28 |

| 4.1      | Filters be Realized with different OTAs                                  | 40 |

| 4.2      | Bias set up for different OTAs in filter realization and simulation      | 41 |

| 4.3      | Comparison among the Fourth-Order Lowpass Filters using different        |    |

|          | ОТА                                                                      | 43 |

| 4.4      | Approximate run time of AC analysis with 100 points per decade for the   |    |

|          | Forth–Order Lowpass Filter on SPARC 5 station                            | 46 |

| 4.5      | Geometric size of the layouts of the Forth-Order Lowpass Filters and the |    |

|          | OTAs                                                                     | 47 |

| 4.6      | Comparison among the Eighth-Order Lowpass Filters using different        |    |

|          | OTAs                                                                     | 52 |

| 4.7      | Approximate run time of AC analysis with 100 points per decade for the   |    |

|          | Eight–Order Lowpass Filter on SPARC 5 station                            | 52 |

| 4.8      | Geometric size of the layouts of the Eight-Order Lowpass Filters and the |    |

|          | OTAs                                                                     | 52 |

| 4.9      | Comparison among the Third-Order Bandpass Filters using different        |    |

|          | OTAs                                                                     | 56 |

| 4.10     | Approximate run time of AC analysis with 100 points per decade for the   |    |

|          | Third–Order Bandpass Filter on SPARC 5 station                           | 56 |

| 4.11 | 1 Geometric size of the layouts of the Third-Order Bandpass Filters and the |    |  |  |  |  |

|------|-----------------------------------------------------------------------------|----|--|--|--|--|

|      | OTAs 5                                                                      | 56 |  |  |  |  |

# **LIST OF FIGURES**

| FIG  | URE PAGE                                                           |

|------|--------------------------------------------------------------------|

| 2.1  | Lowpass filter characteristic                                      |

| 2.2  | Highpass filter characteristic                                     |

| 2.3  | Bandpass filter characteristic                                     |

| 2.4  | Band-rejection filter characteristic                               |

| 2.5  | Frequency response for a typical single pole OPAMP/OTA             |

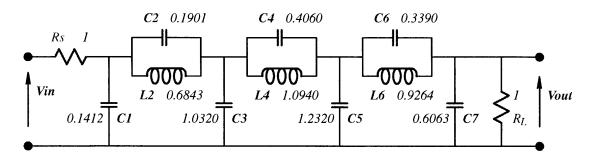

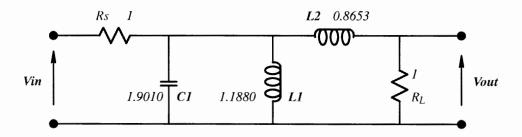

| 2.6  | Fourth–Order Elliptic LC Lowpass Ladder 10                         |

| 2.7  | Magnitude plot of Fourth–Order Elliptic LC Lowpass Ladder shown in |

|      | Figure 2.6 11                                                      |

| 2.8  | Normalized Fourth–Order Elliptic LC Lowpass Ladder 12              |

| 2.9  | Simulation for grounded resistor                                   |

| 2.10 | Simulation for grounded inductor                                   |

| 2.11 | Simulation for floating resistor                                   |

| 2.12 | Simulation for floating inductor                                   |

| 2.13 | Example requiring a route tile 16                                  |

| 2.14 | Diagram of automatic filter design cycle                           |

| 3.1  | Different layers on the top border of the SYMBOL 19                |

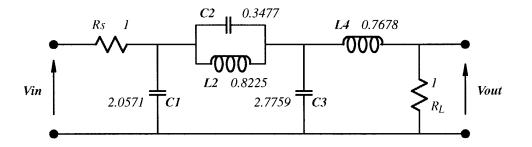

| 3.2  | Example of Fourth–Order Elliptic <i>LC</i> Lowpass Ladder          |

| 3.3  | An example of the tiles fitting together                           |

| 3.4  | Example for route tile generation                                  |

| 3.5  | Example for the synthesis of series <i>LC</i> block                |

| 3.6  | Capacitor array generation 31                                      |

| 3.7  | Basic building block of series <i>LC</i>                              | 33 |

|------|-----------------------------------------------------------------------|----|

| 3.8  | Basic building block of shunt <i>LC</i>                               | 34 |

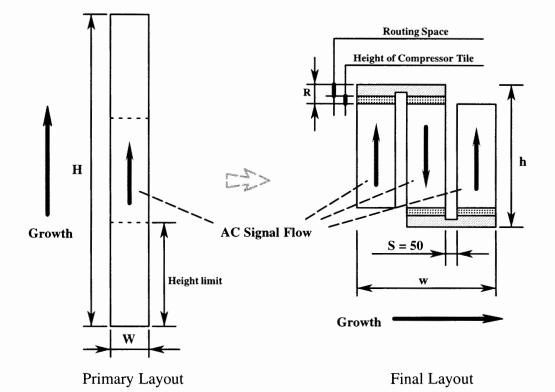

| 3.9  | Converting a linear growth filter to a zigzagged layout               | 35 |

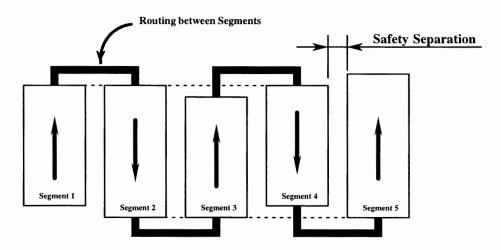

| 3.10 | Filter segments routed together.                                      | 37 |

| 3.11 | Routing wires between segments.                                       | 38 |

| 4.1  | Fourth-Order Elliptic Lowpass Filter.                                 | 41 |

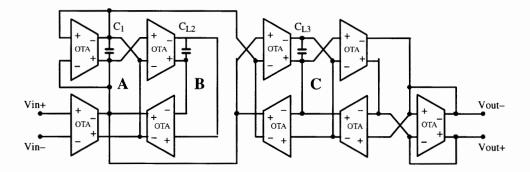

| 4.2  | Schematic diagram of $G_m - C$ Fourth-Order Lowpass Filter            | 41 |

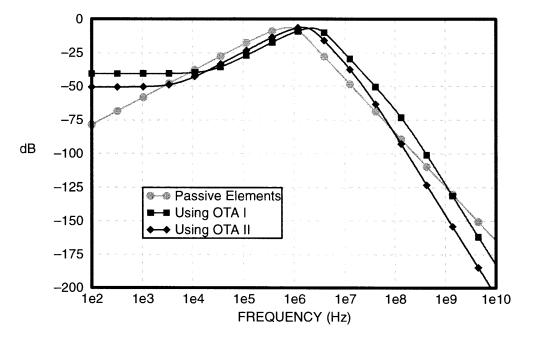

| 4.3  | Magnitude response of Fourth–Order Lowpass Filter using different     |    |

|      | OTAs                                                                  | 42 |

| 4.4  | Phase plot of Fourth-Order Lowpass Filters using different OTAs       | 42 |

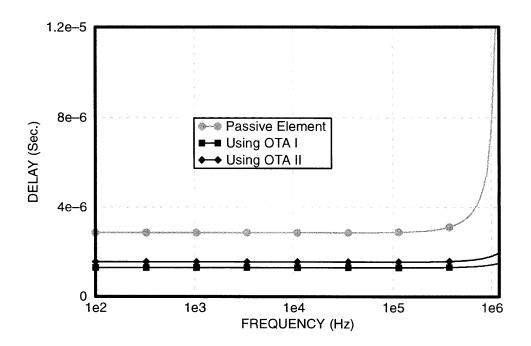

| 4.5  | Delay of Fourth–Order Lowpass Filters using different OTAs            | 43 |

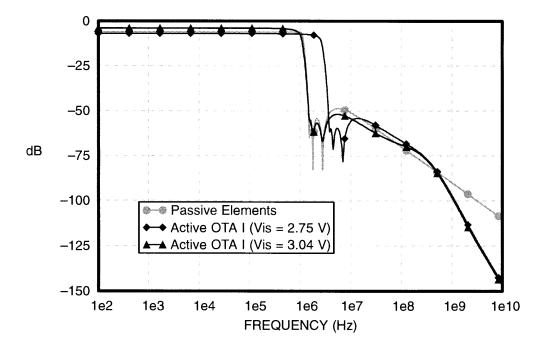

| 4.6  | Zero frequency tuning of Fourth-Order Lowpass Filter using OTA I      | 44 |

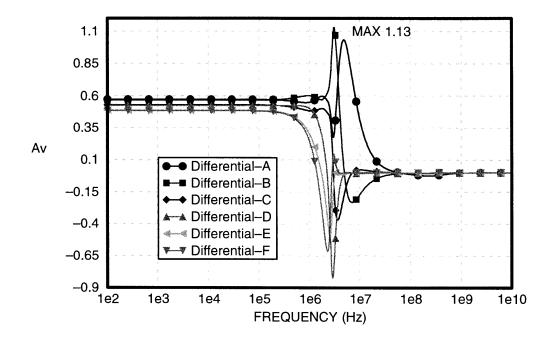

| 4.7  | Voltage gain to the internal nodes of the Fourth-Order Lowpass Filter |    |

|      | using OTA I                                                           | 45 |

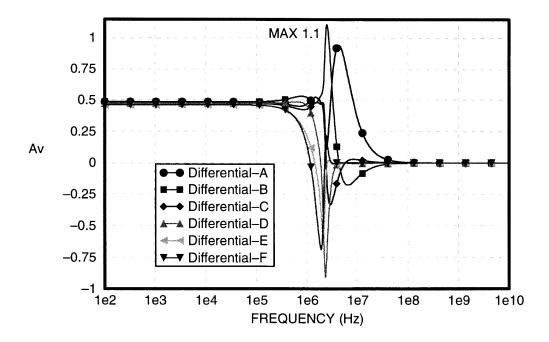

| 4.8  | Voltage gain to the internal nodes of the Fourth-Order Lowpass Filter |    |

|      | using OTA II                                                          | 45 |

| 4.9  | Voltage gain to the internal nodes of the Fourth-Order Lowpass Filter |    |

|      | using OTA III                                                         | 46 |

| 4.10 | Eighth-Order Inverse Chebyshev Lowpass Filter                         | 47 |

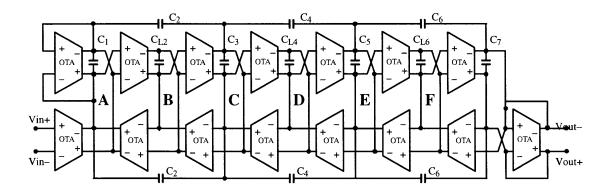

| 4.11 | Schematic diagram of $G_m - C$ Eighth–Order Lowpass Filter            | 48 |

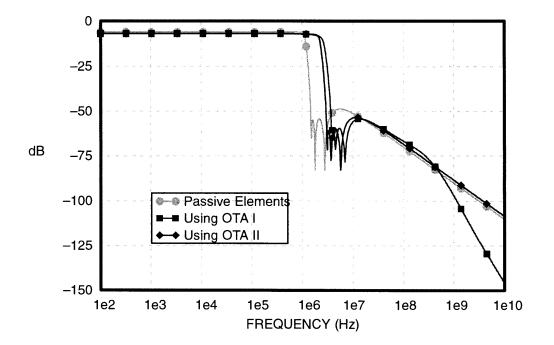

| 4.12 | Magnitude response of Eighth-Order Lowpass Filter using different     |    |

|      | OTAs                                                                  | 49 |

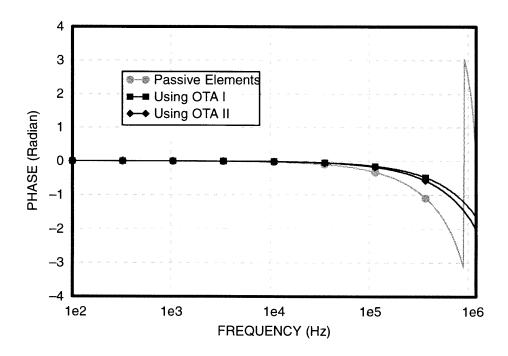

| 4.13 | Phase plot of Eighth-Order Lowpass Filters using different OTAs       | 49 |

| 4.14 | Delay of Eighth-Order Lowpass Filters using different OTAs 5               | 50 |

|------|----------------------------------------------------------------------------|----|

| 4.15 | Zero frequency tuning of Eighth–Order Lowpass Filter using OTA I           | 50 |

| 4.16 | Voltage gain to the internal nodes of the Eighth-Order Lowpass Filter      |    |

|      | using OTA I                                                                | 51 |

| 4.17 | Voltage gain to the internal nodes of the Eighth-Order Lowpass Filter      |    |

|      | using OTA II                                                               | 51 |

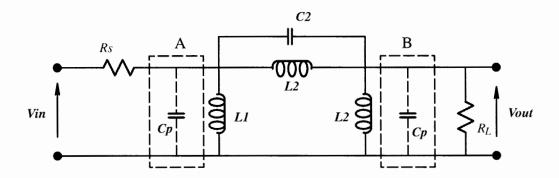

| 4.18 | Third–Order Bandpass Filter 5                                              | 53 |

| 4.19 | Schematic diagram of $G_m - C$ Third-Order Bandpass Filter                 | 53 |

| 4.20 | Magnitude response of Third-Order Bandpass Filter using different          |    |

|      | OTAs                                                                       | 54 |

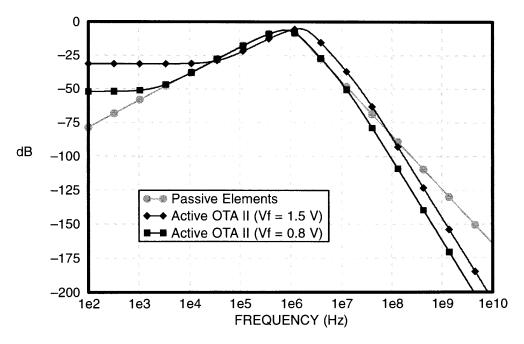

| 4.21 | Center frequency tuning of Third-Order Bandpass Filter using               |    |

|      | OTA II                                                                     | 54 |

| 4.22 | Voltage gain to the internal nodes of the Third-Order Bandpass Filter      |    |

|      | using OTA I                                                                | 55 |

| 4.23 | Voltage gain to the internal nodes of the Third-Order Bandpass Filter      |    |

|      | using OTA II                                                               | 55 |

| 4.24 | Equivalent circuit for a practical inductor simulated with OTAs            | 57 |

| 4.25 | Magnitude response of Third–Order Bandpass Filter with output              |    |

|      | impedance adjustment using OTA II                                          | 57 |

| 51   | Example for the influence of parasitic capacitance on floating nodes in th | ıе |

# **CHAPTER 1**

# **INTRODUCTION**

#### **1.1 MOTIVATION AND OBJECTIVE**

The process of computer software completing one or more IC design tasks is called design automation and exists in many varieties. Design automation software came about because of the demand to be more aggressive and competitive in a tight market. Increasing demands on engineering resources provoked research into productivity tools. The sometimes mundane task of layout was a prime candidate for automation. Initially, layout was accomplished by creating a text file of numerical coordinates describing plot locations for the mask layers. The first step towards improving layout efficiency was the introduction of graphical oriented layout tools such as MAGIC [10]. Furthermore, designers began to reuse the layout of some common circuit elements. Terminology would be evolved to fit the practice. "Full Custom Design" meant that everything was designed by hand using tools such as MAGIC. A good example of the Full Custom Design is the Zilog Z–80 microprocessor. One characteristic of Full Custom Design is that the overall layout of the chip shows very little regularity [7].

In contrast to Full Custom Design, the Intel Pentium microprocessor, which came about two decades later, uses the "Semi–Custom" methodology, where a library of standard cells was developed and reused wherever possible. Nowadays, with the advent of hardware description languages, standard cells can be automatically selected from a library and arranged by the computer following a digital designer's software instructions. However, currently the most mature design automation is only for digital circuits.

This thesis will discuss the area of analog IC design automation and describe a specialized analog layout tool, OTACC (Operational Transconductance Amplifier–Capacitance Compiler). This software tool is the focus of a research project in automating the layout of a CMOS continuous–time filter while minimizing the effects of parasitic capacitance and increasing the control of the shape (geometry) of the layout. Automating this part of the design cycle of these circuits simplifies the task of the designer and permits others to use the prior work of more experienced analog circuit designers.

OTACC initially was written by Martine Wedlake and Dr. W. Robert Daasch [4][5][6], and modified by David L. Robinson [7]. After receiving the initial prototype, this project added necessary features to both CFL and OTACC, so that the tool could be fully integrated into the filter design cycle. This involved CFL enhancement, changing the input and output interface of OTACC, expanding the functions so that OTACC has the capability to realize all necessary *LC* ladder components, expanding OTACC to accept both normalized and non–normalized *LC* ladder input, and adjusting the layout size to fit floor plan proportions. OTACC, beginning with its conceptual foundations, is described in the following chapters.

#### **1.2 THESIS OUTLINE**

This thesis is organized as follows:

Chapter 1 : General introduction.

Chapter 2 : An introduction of basic concept about continuous-time filters and design automation.

Chapter 3 : Description about the basic structure and some main functions of OTACC.

Chapter 4 : Software testing and result simulation. Several filters are realized with different OTAs by using OTACC, and their simulation results are discussed in detail.

Chapter 5 : Conclusions and future work.

# **CHAPTER 2**

# **BACKGROUND AND CONCEPT**

#### 2.1 ANALOG IC FILTERS

The trend of integrated circuits is to reduce the dimensions of the transistors and incorporate in a single chip as many building blocks as possible. In the design of high–performance electronic circuits, the application of analog filters is unavoidable. In telecommunication applications, for instance, active filters ranging from a few kiloHertz (kHz) up to several hundred MegaHertz (MHz) are required. Some other communication systems, such as radio and video frequency receivers, demand high–frequency and high–selectivity analog filters as well. There are also other considerable interests in many applications such as read–write channels in magnetic discs and antialiasing filters in digital signal processing systems [3].

#### 2.1.1 Types of Filters

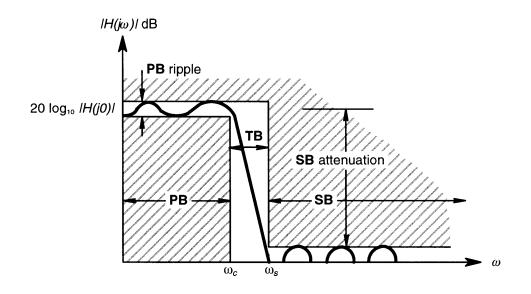

Generally, filters are electrical networks that can provide frequency–weighted transmission and can be typically categorized according to their filtering function. With the magnitude (gain, attenuation) as the primary characteristic, filters can be classified as lowpass, high pass, bandpass, or bandreject networks [1].

The function of the lowpass (LP) filter is to pass the low frequencies from DC to some desired cutoff frequency and to attenuate the high frequencies. This kind filter is

specified by its cutoff frequency  $\omega_c$ , stopband (**SB**) frequency  $\omega_s$ , DC gain, stopband attenuation, and passband (**PB**) ripple. The passband of the filter is defined as the frequency range  $0 \le \omega \le \omega_c$ , the stopband as the frequency range  $\omega \ge \omega_s$ , and the transition band (**TB**) as the frequency range  $\omega_c \le \omega \le \omega_s$ . These specifications are shown in Figure 2.1.

Figure 2.1 Lowpass filter characteristic [1].

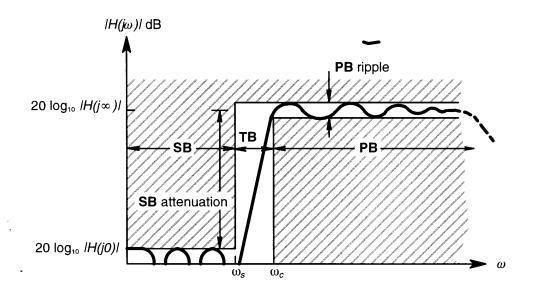

Opposite to the lowpass filter, the function of the highpass (**HP**) filter is to pass the high frequencies above the desired cutoff frequency  $\omega_c$  and to attenuate the low frequencies from DC to the specified stopband frequency  $\omega_s$ . The highpass filter is specified in the same manner as the lowpass filter. In principle, the passband of the highpass filter extends to  $\omega = \infty$ . In practice, however, it is limited in active filters by the finite bandwidth of the active devices and by parasitic capacitances. As a result, the gain of the highpass filter will eventually roll off at high frequencies, as illustrated in Figure 2.2.

Figure 2.2 Highpass filter characteristic [1].

Figure 2.3 Bandpass filter characteristic [1].

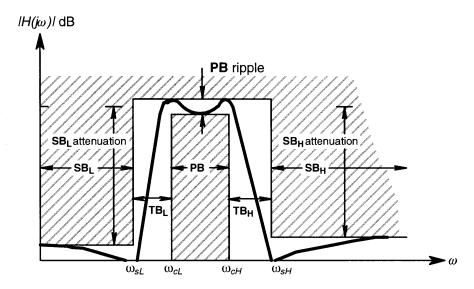

The function of the bandpass (**BP**) filter is to pass a finite band of frequencies while attenuating both lower and higher frequencies. This filter has both a lower stopband,  $SB_L$ , and an upper stopband,  $SB_H$ . Generally, as illustrated in Figure 2.3, the bandpass filter

may not be symmetrical, the attenuation in the lower and upper SBs may be different, and the upper and lower transition bands  $TB_L$  and  $TB_H$  may not be the same.

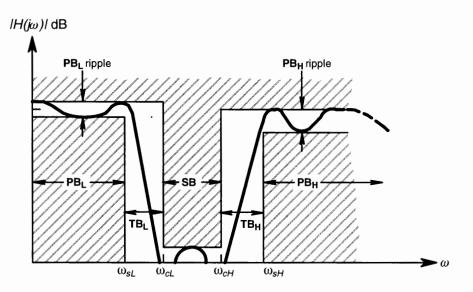

The function of the bandreject (**BR**) filter is to attenuate a finite band of frequencies while passing both lower and higher frequencies. As a result, this kind of filter has both lower and higher frequency passbands, **PB**<sub>L</sub> and **PB**<sub>H</sub>. The specification, which is similar to the bandpass filter, is shown in Figure 2.4. Just like the highpass filter, in reality the upper passband is limited due to the band–limited active devices and parasitics.

Figure 2.4 Band-rejection filter characteristic [1].

#### 2.1.2 CMOS Continuous–Time Filters

Typically, most of the important characteristics of the continuous-time filter are sensitive to the process parameter tolerances. Nowadays, the available technologies for integrated circuits are Complementary-Metal-Oxide-Semiconductor (CMOS), Bipolar, BICMOS (BIpolar-CMOS), Gallium-Arsenide, and devices based on other III-V substrate. Each one of these technologies has advantages and drawbacks. Actually, CMOS is the most popular technology due to its high circuit density, low cost and maturity. At this time, the commonly used techniques for the digital signal processing are implemented in CMOS technologies [3].

For the design of high–performance CMOS active filters, there are three main types of continuous–time filters, namely, RC active filters, MOSFET–C filters, and OTA based filters. The accuracy of the active RC filter is very limited. The MOSFET–C filters are basically active RC filters but with the resistors implemented by equivalent CMOS tunable resistors [26]. Due to the use of the resistors, buffered OPAMPs have to be employed. The limited frequency response of a two or more stage OPAMP reduces the application of the filters to low–frequency [3]. "Transconductance amplifiers appear to be the appropriate components because they are easy to implement in monolithic form, can be tuned electronically, and lead to intriguingly simple filter circuitry. Therefore, Operational Transconductance Amplifiers (OTAs) are likely to play an increasingly important role in analog filter design" [2]. The OTA is a functional circuit block that takes the input voltage and generates the output current with the relationship as:

$$I_{out} = g_m \cdot V_{in}$$

where  $V_{in}$  is the input voltage,  $I_{out}$  is the output current, and  $g_m$  is the transconductance value of OTA. It appears appropriate to take the OTA-based filter design strategy in our filter design automation tool.

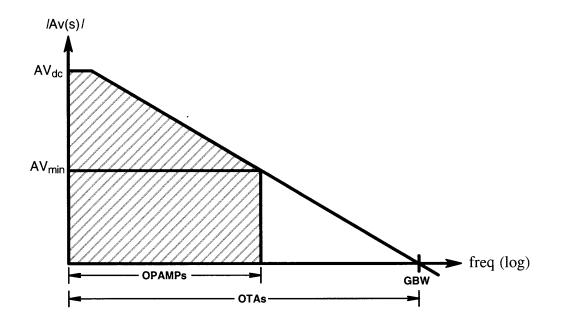

A minimum OPAMP gain, around 30 dB, is necessary for well behaved OPAMP based filters. Otherwise, the Gain–BandWidth (GBW) effect of the OPAMP degrades the performance of the system. For a single–pole OPAMP, this implies a useful frequency range of the order of GBW/30. This fact makes it extremely difficult to design high–fre-

quency OPAMP-based filters. Because the OTA-based integrators are implemented in open loop, the functional frequency range of these circuits is limited only by the OTA gain-bandwidth product [3].

The main topic of this research project is automating the layout of CMOS continuous-time filters. For the OTA based filters, the Operational Transconductance Amplifier-Capacitor (OTA-C) filters have already been reported with frequency ranges from a few kHz up to hundreds MHz. The basic building blocks of OTA-C filters are the Operational Transconductance Amplifier (OTA) and integrated capacitors. A major advantage of the OTA-based continuous-time filters is their extremely large frequency range [15][16][17][18]. Actually, OTA-based filters with resonant frequencies in the range of several hundred MHz have been reported [19][20]. A comparison of the useful frequency range for both OPAMP and OTA-based circuits is shown in Figure 2.5.

Figure 2.5 Frequency response for a typical single-pole OPAMP/OTA [3].

The **OTACC** (Operational Transconductance Amplifier–Capacitance Compiler), being the main topic of this thesis, focus on automating the design cycle of CMOS continuous–time filters by the simulation of *LC* ladder prototypes.

#### 2.2 FILTER REALIZATION

#### 2.2.1 LC Ladder

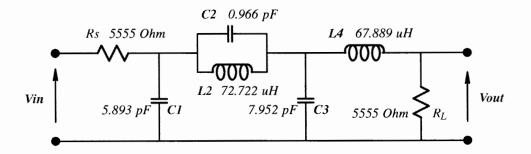

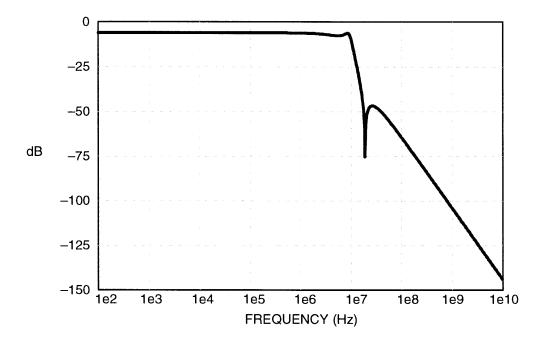

As an example, a fourth–order elliptic *LC* lowpass filter, with a 10MHz passband and nearly 50 dB of attenuation in the stopband, is shown in Figure 2.6. Its magnitude plot (simulated with ideal elements) is shown in Figure 2.7.

Figure 2.6 Fourth-Order Elliptic LC Lowpass Ladder.

The active *LC* ladder prototype is chosen for this project primarily in response to the filter design automation concerns [4]. For a desired transfer function, a filter is realized by the active simulation of an *LC* ladder topology derived from its input and output impedance. In addition, the *LC* ladder prototype was chosen because of its unique characteristic of low sensitivity to component variations and because a circuit capacitor is generally present at most of the circuit nodes in the original *LC* prototype. So the original value of the capacitance can be adjusted to include the value of the parasitic capacitance. That is:

$$C_{desired} = C_{circuit} + C_{parasitic}$$

If enough is known about the parasitics, we can combine the circuit capacitance with the parasitic capacitance associated with corresponding circuit node, and therefore, significantly limit the influence of the parasitic capacitance. The combination of the circuit capacitance with the parasitic capacitance will be referred to as *predistortion*.

Figure 2.7 Magnitude plot of Fourth–Order Elliptic *LC* Lowpass Ladder shown in Figure 2.6.

#### 2.2.2 Normalization

Like most electrical networks, the *LC* ladder is usually normalized with *Impedance–Level Normalization* and *Frequency Normalization*. Normalization causes no loss in generality and is performed only for simplicity in numerical computations, especially in hand calculations, because it can minimize the effects of round–off errors [1]. Frequency normalization is simply the frequency scaling by dividing the frequency variable by a conve-

niently chosen normalizing frequency  $\Omega_0$ . Similarly, impedance–level normalization is performed by dividing all impedances in the circuit by a normalizing resistance  $R_0$ . The normalized element values are, therefore,

$$R_n = \frac{R}{R_0} \qquad \qquad L_n = L \frac{\Omega_0}{R_0} \qquad \qquad C_n = C \Omega_0 R_0$$

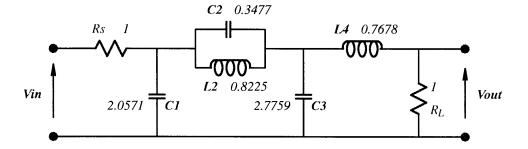

The schematic of the normalized *LC* ladder corresponding to Figure 2.6 is shown in Figure 2.8.

Figure 2.8 Normalized Fourth–Order Elliptic LC Lowpass Ladder.

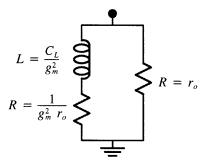

In our case, identical transconductance cells (with same  $g_m$  value), which converts the input voltage to output current, are used to realize the resistors and simulate inductors. So the actual denormalized physical parameters R, L, and C are,

$$R = \frac{1}{g_m} \qquad \qquad L = \frac{L_n}{g_m \Omega_0} \qquad \qquad C = C_n \frac{g_m}{\Omega_0}$$

Where the  $\Omega_0$  is the cutoff frequency of the filter. The *gm* parameter, which is necessary to calculate the circuit *R*, *L*, and *C* in OTACC, can be obtained from the technology file which is associated with the OTA standard cells in the library. The format and contents of the technology file used by OTACC is shown in Appendix D.

#### 2.2.3 Element Substitution

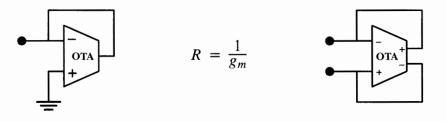

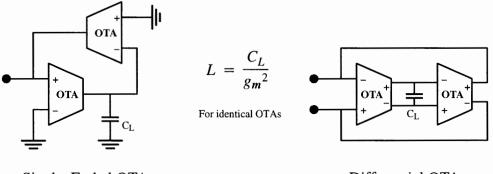

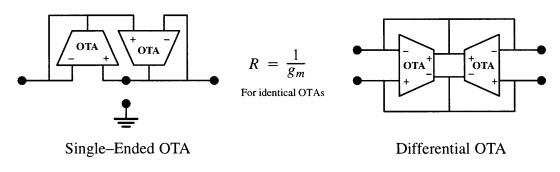

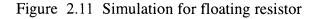

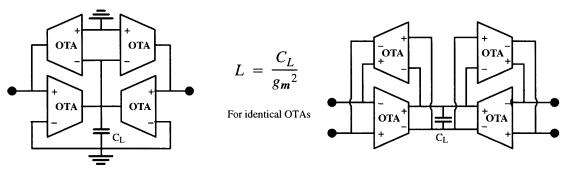

To achieve the integrated implementations of active filters, the R and L elements in the LC ladder must be replaced by active simulations with only OTAs and capacitors. These two elements are sufficient in general and lead to circuits that are easy to integrate in a typical IC process. The  $g_m$  simulation of the grounded resistor and grounded inductor are shown in Figure 2.9 and Figure 2.10.

Single-Ended OTA

Differential OTA

Figure 2.9 Simulation for grounded resistor

Single-Ended OTA

Differential OTA

Figure 2.10 Simulation for grounded inductor

When we need a floating resistor or a floating inductor instead, we must "lift the circuit off ground" and devise a method for the current to flow out of the second terminal. As shown in Figure 2.11 and Figure 2.12, extra OTAs are needed for simulating the floating resistor and floating inductor.

Single-Ended OTA

Differential OTA

Figure 2.12 Simulation for floating inductor

# **2.3 LAYOUT AUTOMATION**

There are a several methods to automate the layout process of digital and analog circuits. However, the way that parasitics, specifically parasitic capacitance and resistance, are handled is vital to the success of any analog design automation method.

The first method is polygon generation. In this method, nearly all the layout is generated by the software. Each transistor, for example, may be independently sized and routed to the next transistor for the entire design. This method has many variations that can be unforgiving in large analog subsystems. As the complexity of the system increases, the errors caused by parasitic capacitance and resistance begin to accumulate exponentially. However, there have been some successes with the automatic generation of small analog components [21][22][23] and digital systems [9][29].

The second method is module generation [22][24][25]. With this method, a library of basic building blocks containing modules such as logic devices, current mirrors, differential pairs, etc. is available. These modules are pre–assembled in such a way as to minimize internal and external layout problems. The methodology is general, but since the parasitic capacitances can still wreck havoc with analog configurations, considerable designer intervention is required for complex analog subsystems [24][25]. The work is ongoing with this method and may one day be the preferred methodology if the parasitic problem can be solved.

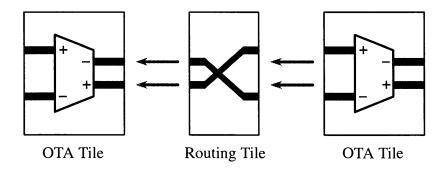

The third method is tiling. This takes the idea of modules a step further in that the modules (tiles) are more complex and are configured such that the signal routing may also be tiled. A library of pre–designed and characterized tiles are available as basic building blocks. Since routing is included in the tiles, the routing operation is static. Routing occurs simply by abutting two or more tiles together [6] as shown in Figure 2.13.

The disadvantage to this approach is library maintenance. If additional circuitry is added into the library, often a set of support tiles will need to be created also. For the digital logic application, there are no specialized routing tiles required. However for something more complex such as a tunable operational transconductance amplifier, the key element of the active filter in this thesis, additional support tiles are needed that match its layout. As an example shown in Figure 2.13, an additional route tile would be required

to support the OTA's layout to realize the multiplication by -1 using differential OTAs. So, not only would an additional tile need to be created, but this tile might need to be linked to a specific OTA in order to assure proper wire location.

Figure 2.13 Example requiring a route tile [7].

Tiling is the basic approach that OTACC will take. Although less general than module generation, it uses a standard cell library and predistortion to provide better accuracy that would otherwise be unattainable. This is a reasonable tradeoff in seeking for better analog automation tools. To reduce the number of tiles that are associated with each OTA, a polygon generation method is used in this project to generate some route tiles from a set of basic route tiles. This is really a hybrid of module, polygon generation, and tiling approach. Only the route tiles that really depend on the geometry character of the OTA have to be created when a new OTA cell is added to the library. The details of how the tool works and how to develop the support library will be covered in a later chapter.

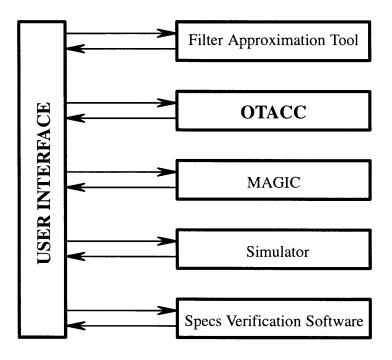

### 2.4 FILTER DESIGN AUTOMATION

Generally, there are four necessary procedures in the filter design cycle. They are filter approximation, layout, simulation, and verification. To automate the filter design cycle, user friendly interface is necessary to integrate the procedures to complete the filter design automation tool, as depicted in Figure 2.14.

Figure 2.14 Diagram of automatic filter design cycle.

In Figure 2.14, the user interface is a window based, graphical user interface. It is a separate project related to this research subject [28]. The filter approximation could be done by some filter approximation tool, such as FiltorX which is developed and distributed by Department of Electrical Engineering, University of Toronto [12]. The layout of the filter will be generated in MAGIC [10] format, and the circuit netlist can be extracted for simulation. The simulator could be some general purpose circuit simulation programs, such as SPICE. To complete the picture of the filter design automation, the verification software is a planned separate project.

# **CHAPTER 3**

### OTACC

OTACC is an automatic layout tool written in C intended to realize the design automation for the class of OTA–C continuous–time filters. It uses a set of library functions known as CFL library that interface to the MAGIC layout . It takes MAGIC cells as input and generates the layout output in MAGIC format. OTACC, beginning with its conceptual foundations, is described in the following sections.

### 3.1 CFL

#### 3.1.1 What is CFL?

CFL is a C function library to be used for the construction of VLSI circuit layouts. It is organized algebraically in that there is a data type called SYMBOL, a set of primitive operands of this type, and a set of operators that generate new SYMBOLs by forming combinations of existing SYMBOLs.

All inputs for the calculations required by the CFL operators are retrieved from the descriptions of the borders of the SYMBOLs. The information in the border descriptions includes the bounding box and lists of coordinates of the points where each kind of material in the SYMBOL makes contact with the bounding box, such as the example shown in Figure 3.1. When a border description is available for a particular SYMBOL, CFL will

not access the rest of the geometry of SYMBOL [11], which provides considerable performance gains.

Figure 3.1 Different layers on the top border of the SYMBOL.

The system generates a border description from the geometry whenever the need arises and saves library symbols on disk. In this way, modules that have a large number of rectangles may be accessed from the library without the need of reading all the files associated with their sub–modules. This capability allows CFL to assemble large blocks of circuitry extremely fast. Additionally, CFL also provides automatic hierarchy compression when symbols are written to disk so that only those symbols that represent meaningful layout need be saved [11].

With a complete set of placement and routing primitives, this tiling language is simple and flexible. The database is stored in the same format as the popular public domain VLSI CAD package, MAGIC [10], which has the capability to support large design layouts and includes an extractor that is used to create simulation netlist

#### 3.1.2 CFL Enhancement

To insure the widest variety of chip assembly options, CFL includes approximately 70 operators for juxtaposing, transforming, and replicating hierarchies of one or more symbols. Unfortunately, some of the original routing functions of CFL were not flexible enough to be used by our application. The major problems in the original CFL were:

- 1. Most routing functions could only place the routing wires with constant wire width.

- 2. Mask layers on the border could not be routed with a contact's original layers. For example, the METAL2 contact on the border of a symbol could not be routed with METAL1 or METAL2

Because of the limited routing functions within CFL, CFL routing facilities had to be modified. The new version of CFL is compatible with the old CFL–based layout program. That is, any C program that used the original CFL, can still use the new version CFL library without modification and with no differences in the final layout. The new features of the enhanced CFL are:

- 1. All routing functions have the ability to run the routing with the wire width of its original width at the border.

- 2. The border descriptor, as argument to some of the routers, has the capability to contain not only a given mask layer on the border, but also the contact layers related to it.

- 3. New user functions permit the user to exclude or include certain mask layers on the border from the border descriptor.

- 4. A new user function permits the user to switch the active layer of a point on the border. This means that CFL has the ability to complete the point-to-point routing with the layer that is associated with the source point instead of the destination point.

Features 2, 3 and 4 can be used only when the new format technology file, which contains important process oriented information, is supplied. Use of the new operators, without the new format technology file, will cause the program to exit with a warning that the new technology file is required.

More details about the enhanced CFL functions and their applications are listed in Appendix A.

# 3.2 BASIC STRUCTURE OF OTACC

The communication structure of the OTACC module is based on a stack. All operations obtain their input from the stack, and then push the results back onto the stack. Each stack element is a structure of pointers to layout symbols and miscellaneous information for communication between functions. A stack is preferred because to pass information back and forth between the routines, a large number of global variables would be required. Also, using a stack machine allows each tile to be read from the disk only once, with the tiles remaining in the memory for the duration of the whole layout procedure. This improves the efficiency of OTACC since multiple reads of the disk for each tile are avoided. An idea of the number of global variables that would have been required if a stack machine were not used can be obtained by viewing Table 3.1. For more detail about the stack structure definition please see Appendix B.

| OTACC<br>Stack Structure |                     | Туре о           | f Structure Ele | ements  |          |

|--------------------------|---------------------|------------------|-----------------|---------|----------|

|                          | SYMBOL<br>Structure | Integer<br>Array | Enumerator      | Integer | Floating |

| Number                   | 21                  | 2                | 3               | 8       | 10       |

Table 3.1 Number of elements in the OTACC stack structure.

#### **3.3 INPUT AND OUTPUT INTERFACE OF OTACC**

#### 3.3.1 FiltorX Interface

The filter design cycle consists of taking a filter specification and generating the transfer function, possibly using a classical methodology. Next, the transfer function is approximated with real circuit elements and finally implemented. The University of Toronto has created a design tool called FiltorX to assist in the approximation and realization process [12]. OTACC's grammar set was designed to be compatible with the output of FiltorX so that the two tools could be combined into one, allowing the approximation, realization, and implementation phase of the filter design cycle to be assisted or automated by the software.

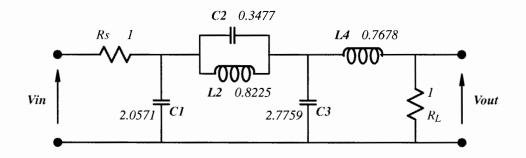

For a given transfer function, one possible output of FiltorX is in terms of the elements that make up an *LC* ladder filter. Reading the schematic showing in Figure 3.2 from left to right yields the FiltorX description shown in Table 3.2. Where the *filter\_name* will be the file name used for final layout of the filter.

By matching the input grammar of OTACC to the output of FiltorX, we create a link that is necessary to automate the most computationally intensive parts of the filter design cycle.

```

ladder filter_name (

seriesR 1.0;

shuntC 2.0571;

seriesLC 0.8225, 0.3477;

shuntC 2.7759;

seriesL 0.7678;

shuntG 1.0;

)

```

Table 3.2 OTACC input from FiltorX

#### 3.3.2 Command Line and Options

To increase the flexibility, several command line switches are supported by OTACC. The designer can control the geometry of the layout and easily update some of the required parameters to permit fine adjustments to be made during filter design. For example, most OTAs are designed with tuning nodes to adjust their transconductance value and the designer can predict the tuning effect on the transconductance by simply changing the transconductance value at the command line.

A list of command options for OTACC are outlined in Appendix C.

# 3.3.3 OTA-Technology File Scanning

OTACC caches all of the required technology parameters from the OTA-technology file that is associated with the OTA cells in the library. The tile file contains the important parameters of the OTA and important process parameters. The contents and format of the OTA-technology file are described in Appendix D. Currently, the only required parameters for executing OTACC, are the name of the OTA cell, transconductance value and cut off frequency of OTA, and parasitic capacitance values. The other parameters have been reserved for future development, and they can be omitted for current applications. Comment lines are allowed in the OTA-technology file to make it readable.

#### 3.3.4 Error Message Coding

To communicate with a top-level program such as a Graphic User Interface (GUI) or the designer, OTACC returns an encoded integer number for both normal exit and abnormal exit. For the non-fatal errors, a binary bitwise encoding method is used to encode the warning messages. This gives the designer or GUI a way to trace the program and a hint for debugging the problem when an error is detected during the OTACC execution.

The entire set of the error codes are defined in Appendix E.

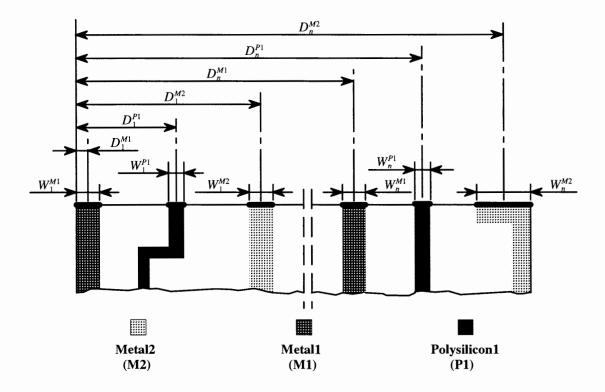

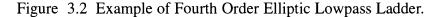

### 3.4 SYMBOLIC LAYOUT AND TILE GENERATION

As described in Chapter 2, OTACC uses a hybrid of module, polygon generation and tiling methodology. Generally, there are three types of tiles required:

- 1. Transconductance tile.

- 2. Unit capacitor tile.

- 3. A set of route tiles.

The route tiles act as an interface between the transconductance and an array of capacitor tiles. For a double polysilicon, double metal CMOS process, an example of how the three types of tiles fit together is shown in Figure 3.3.

Array of 8x2 Unit Capacitor Tiles

Figure 3.3 An example of the tiles fitting together.

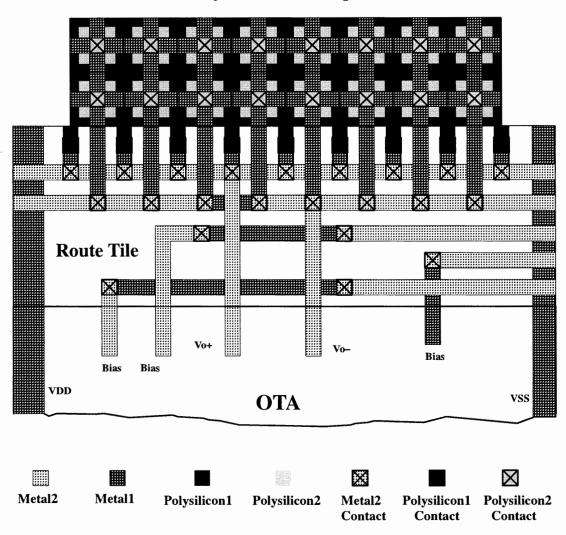

By "routing" the cells with pre-designed tiles, the desired amount of node capacitance can be predistorted according to the amount of parasitic capacitance as described in the OTA-technology file. This method of layout generation greatly reduces the unpredictable parasitic capacitance problem that plagues automatic synthesis of VLSI analog circuitry. The disadvantage of routing with tiles is that the synthesis software can be very specialized, and the standard cell library maintenance becomes more difficult. For the current version OTACC, fourteen route tiles are needed for *LC* ladder synthesis. i.e. beside the capacitor and OTA itself, fourteen route tiles need to be prepared for the filter synthesis.

Figure 3.4 Example for route tile generation.

To limit the difficulty of the library maintenance, a second version OTACC includes functions to generate some of the route tiles based upon a fixed set of tiles. Software examines the geometry characteristic of the existing tiles and then generates the desired route tile to guarantee they are perfectly matched for later assembly. An example of route tile generation, in which part of the compressor tile is generated from the existing capacitor comb, is shown in Figure 3.4. The compressor tile is important of the final assembly and will be fully described in Chapter 3.6.3.

The contents of the library for a specific OTA will include the MAGIC files of the OTA, unit capacitor tile, and 6 basic route tiles. All other necessary route tiles will be generated by the software automatically. The relationships between the different route tiles are shown in Table 3.3. Some basic route tiles need to be pre-designed, because they are dependent on the geometry of a specific OTA.

| Name       | Level      | Derived From    | Function in<br>OTACC | Application                       | Status   |

|------------|------------|-----------------|----------------------|-----------------------------------|----------|

| combinP    | Basic      | Pre-designed    |                      | In+ Comb for capacitor array      | Existing |

| combinN    | Basic      | Pre-designed    |                      | In- Comb for capacitor array      | Existing |

| comboutP   | Basic      | Pre-designed    |                      | Out+ Comb for capacitor array     | Existing |

| comboutN   | Basic      | Pre-designed    |                      | Out- Comb for capacitor array     | Existing |

| dcrib      | Basic      | Pre-designed    |                      | DC bias route tile                | Existing |

| ldrib      | Basic      | Pre-designed    |                      | Special DC bias route tile        | Existing |

| dcCenter   | Derivative | dcrib           | mkCframe             | Additional DC bias route tile     | Existing |

| dcEdge     | Derivative | unitC, comboutP | mkCframe             | DC signal connection stub         | Existing |

| zCenter    | Derivative | UnitC           | mkZCframe            | "zero" capacitor array route tile | Existing |

| zEdge      | Derivative | UnitC           | mkZCframe            | "zero" capacitor connection stub  | Existing |

| compressor | Derivative | dcrib, comboutP | mkcompressor         | Ac signal compressor tile         | New      |

| acisolator | Derivative | dcrib, comboutP | mkacisolator         | AC signal isolator tile           | New      |

| floatcombm | Derivative | dcrib, comboutP | mkfloatcomb          | Metal1 comb for float capacitors  | New      |

| floatcombp | Derivative | dcrib, comboutP | mkfloatcomb          | Poly1 comb for float capacitors   | New      |

Table 3.3 Route tiles for OTACC

To easily identify the route tiles and improve the maintenance of the library, all route tiles use the name of the OTA cell as the prefix of their name. For example, the MAGIC file name of the compressor tile for a transconductance cell named *OTAD* will be *OTAD.compressor.mag.*

#### 3.5 OPERATORS

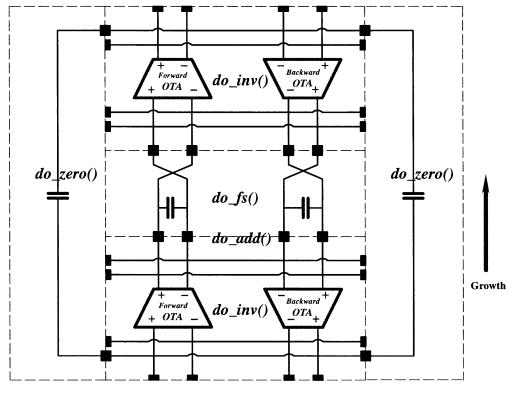

To build a filter, there are five main stack operators in OTACC to synthesis the *LC* ladder. They are:  $do_fs()$ ,  $do_zero()$ ,  $do_add()$ ,  $do_inv()$  and  $do_separation()$ . There are two additional stack operators,  $do_source()$  and  $do_load()$ , for the input source and the load resistor block of the *LC* ladder. All stack operators are stand alone, and are coordinated by the state of the program stack. For example, the  $do_add()$  operator checks for and then pops two elements from the stack, properly assembles them to get a larger component, and then the result is pushed back to stack. The order of the calls is dependent on the input data stream. Each of these operators are discussed in following paragraphs.

#### 3.5.1 Software Implementation and Circuit Synthesis

As shown in Table 3.4, each stack operator has a specific task to perform during *LC* ladder filter synthesis. Combining these operators with the filter descriptor, OTACC can realize an *LC* ladder filter of any order and transmission characteristics.

| Stack Operators   | Input                | Stack Operation | Stack Status           | Objective                            |

|-------------------|----------------------|-----------------|------------------------|--------------------------------------|

| do_inv()          | Nothing              | POP 1, PUSH 1   | Stack<br>Unchanged     | Add an Inversion                     |

| do_fs(double C)   | Capacitance<br>Value | POP 1, PUSH 2   | Stack<br>Increase by 1 | Capacitor Array                      |

| do_add()          | Nothing              | POP 2, PUSH 1   | Stack<br>Decrease by 1 | Addition<br>Operation                |

| do_zero(double C) | Capacitance<br>Value | POP 1, PUSH 2   | Stack<br>increase by 1 | Transmission Zero<br>Capacitor Array |

| do_separation()   | Nothing              | POP 1, PUSH 2   | Stack<br>increase by 1 | AC Signal Isolator                   |

| do_source()       | Nothing              | POP 1, PUSH 2   | Stack<br>increase by 1 | Source<br>Transformation             |

| do_load()         | Nothing              | POP 1, PUSH 2   | Stack<br>increase by 1 | Grounded Load<br>Resistor            |

Table 3.4 Stack operators in OTACC.

The stack element stores the tile symbols and miscellaneous information such as the parasitic capacitance values contributed by the OTA inputs and outputs, the route tiles and the capacitor tile. Other than modifying the stack, the stack operators have no output or return message when operating normally. Error messages are output when some error has occurred. For example, if a operator is used inappropriately or the stack is corrupted.

Figure 3.5 Example for the synthesis of series *LC* block.

An example for the synthesis of series *LC* block is shown in Figure 3.5. First the  $do_{inv}()$  operator puts a so-called forward OTA and backward OTA together, which is the core building block for the simulation of the inductance element as described in section 2.2.3. Next the  $do_{fs}()$  operator generates the capacitor array that is needed to simulate a specific value of inductance. Finally  $do_{add}()$  operator attaches the fragment onto the main structure of the layout. To complete a floating inductor, another OTA pair would be attached by the  $do_{inv}()$  operator. If a series capacitor array is needed, it would be gen-

erated by *do\_zero()* operator and stored in the stack with all the necessary information attached to the capacitor array for the final assembly.

Other elements are constructed by a similar combination of these operators. Generally, by using these operators, any functional block for the *LC* ladder filer could be constructed.

In the  $do\_fs()$  and  $do\_zero()$  operators, CFL utilities are used to construct the layout from OTA tiles, unit capacitor tiles, and route tiles. The parasitic capacitance of inputs and outputs of the OTA and the route tiles are known before the capacitor array is generated. For a desired capacitance, *C*, the number of capacitor tiles to be tiled for the circuit capacitor array is computed using:

$$N = \frac{C - \left(C_{I/O} + C_{route}\right)}{\left(C_{unit} + C_{unitP}\right)}$$

(3-1)

where N is the number of capacitor tiles required to make the circuit capacitor array.  $C_{I/O}$  is the sum of the OTA inputs and outputs parasitic capacitance.  $C_{route}$  is the parasitic capacitance of the route tiles.  $C_{unit}$  is the capacitance value of a single capacitor tile and  $C_{unitP}$  is the parasitic capacitance of a single capacitor tile.

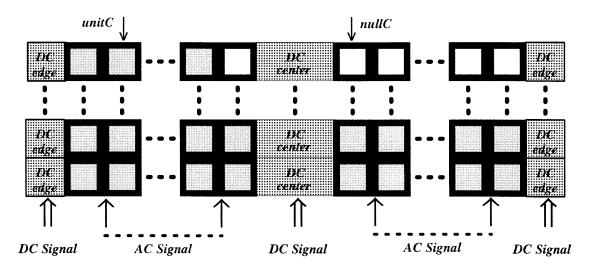

A capacitor array is constructed as a two dimensional array of the capacitor tiles, as shown in Figure 3.6. The number of capacitor tiles per row in the array is determined by the width of OTA cells and any required DC routing space. After the rows of unit capacitors are created, if the last row is incomplete, the remaining spaces are filled by "*nullC*" capacitor tiles as a place holders (i.e. insignificant contribution to the total capacitor array). One polarity of the power supply passes through the "*DC edge*" on each side. Another polarity of the power supply and the DC bias routing pass through the "*DC center*". Therefore the AC routing and the DC routing can be completed in single steps.

Figure 3.6 Capacitor array generation

If a series LC block is required in the filter, which is a key element for realizing a finite transmission zero in filter transfer function, the transmission zero capacitor array that is in parallel with the series L block is generated in the vertical direction. The number of the capacitor tiles per column in a transmission zero capacitor array is set by the height of OTA cells.

# 3.5.2 Data Communication

As noted earlier, the data communication in OTACC uses two stack operations: *push()* and *pop()*. The functions obtain their inputs from the stack element, and return their results to the stack.

Generally, the operators outlined will affect the stack, as shown in Table 3.4, in three ways.

- 1. Adding a new element on the top of the stack. The stack length is increased by 1.

- 2. Combine the first and second element's SYMBOLs. The stack length is decreased by 1.

3. Merge a new structure with the first element on the stack. The stack length is unchanged.

### **3.6 FLOOR PLANNING**

In its simplest form, the layout generated by OTACC grows in one direction along the "backbone" of OTA cells and AC, DC interconnection. The width of the backbone is set primarily by the sum of the widths of the transconductance cells and the DC channel route. The maximum width of the final filter includes the width of any transmission zero capacitor array attached to the side of the backbone. Although these capacitor arrays may vary in size, they typically do not exceed 150 microns each, or a total of 300 microns in a 2 micron technology.

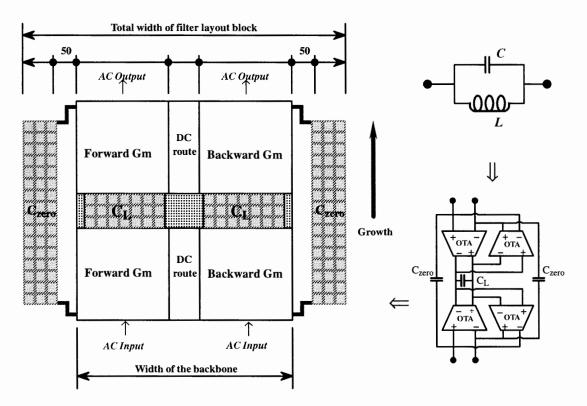

The basic building blocks of the filter layout consist of so–called forward transconductance, backward transconductance, and DC route tiles in the configuration shown in Figure 3.7 and Figure 3.8. The layout grows vertically because these meta–elements are stacked with capacitor arrays sandwiched in between.

#### 3.6.1 Series LC Block

As shown in Figure 3.7, the inductor L is simulated by four OTA cells and the capacitor array  $C_L$ . The transmission zero capacitor arrays are attached on both sides of the backbone for a fully balanced design (there is only signal transmission zero capacitor array on one side of the backbone for a single–ended design). The separation between the transmission zero capacitor array and the backbone has been verified to limit the cross–talk between the capacitor array and the backbone [9].

Figure 3.7 Basic building block of series LC.

For a series L branch, the  $C_{zero}$  capacitor array is not required. The rest of the structure is the same as the series LC branch.

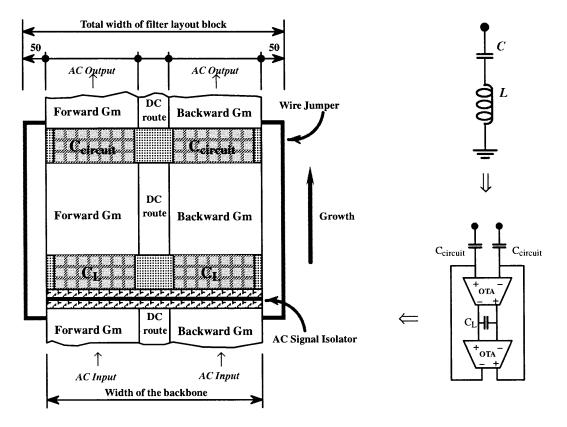

### 3.6.2 Shunt LC Block

As shown in Figure 3.8, all the components of the shunt *LC* branch remain within the backbone. Because of that, each shunt *L* branch must have a grounded end for the AC signal. An AC signal isolator is applied to reduce the cross–talk between the upper and lower block. The structure of the AC signal isolator also includes some vertical DC connection wires to carry the power and bias supply along the backbone, and a horizontal DC signal (AC ground) wire to isolate the AC signal. The AC signal along the backbone is

maintained by the wire jumpers which are generated automatically by OTACC on the sides of the backbone.

Figure 3.8 Basic building block of shunt LC.

For a shunt *L* branch, the series  $C_{circuit}$  capacitor arrays is not required. The rest of the structure is the same as the shunt *LC* branch.

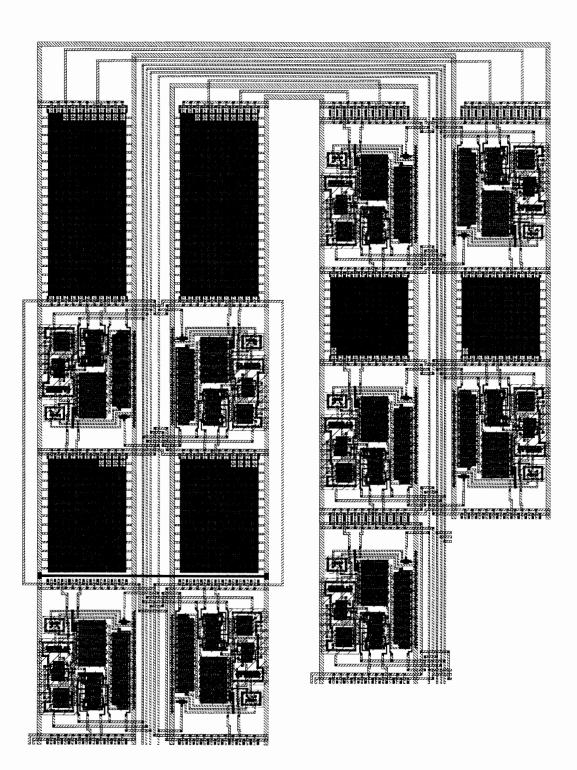

# 3.6.3 Folded Layout

Unfortunately, a tall, thin layout can be a large waste of silicon and difficult to fit into a larger design. It is generally desirable to have the layout to be roughly square, i.e., the width and height should grow at about the same rate. In order to utilize the space better, a height limit can be set by the designer to control the vertical growth of the layout to produce a zigzag layout. The single-line layout and zigzag layout are compared in Figure 3.9. As illustrated, each layout has approximately the same area.

Figure 3.9 Converting a linear growth filter to a zigzag layout.

Note that layout of an active filter IC may include one or more transmission zeros or shunt *LC* branches which are not shown in Figure 3.9. The arrows in the figure indicate the direction of growth and the flow of the AC signal path.

As shown in Figure 3.9, the filter must complete a U-turn in the AC signal path when the height limit is reached. The height limit is set by the user through the command line. If the user does not specify the height limit, the software will attempt to identify the best square layout. From Figure 3.9, for an ideal square, we have

h = w

where h and w are the height and width of the final layout. Equivalently we have

$$\frac{H + 2R(n-1)}{n} = nW + (n-1)S$$

(3-2)

where H and W are the height and width of the primary layout as shown in Figure 3.9. R is the sum of the routing space and the height of the so-called compressor tile. n is the number of segments that the primary layout will be divided into. S is the separation between the segments. Rearranging Equation (3–2) yields the quadratic equation.

$$(W+S)n^2 - (2R+S)n - (H-2R) = 0$$

Solving this quadratic equation for n, we get

$$n = \frac{(2R+S) + \sqrt{(2R+S)^2 + 4(W+S)(H-2R)}}{2(W+S)}$$

(3-3)

To solve *n* from Equation (3–3), two OTACC layouts are necessary. OTACC will generate a single–line layout first to determine the primary height (*H*) and primary width (*W*) of the layout, then the number of segments for the final layout is calculated. The height limit for the final layout is easily determined from:

$$h = \frac{H}{n}$$

If users specify a CIS style layout, i.e. input and output terminals on the same side of the layout, n is selected to be the nearest even number. If users specify a TRANS style layout, i.e. input and output terminals on opposite side of the layout, n is selected to be the nearest odd number.

The compressor tile is necessary to connect the two adjacent segments. The compressor tile combines the parallel signals into a single wire which is much more suitable for turning the filter's signal path to the opposite direction. A break for the U-turn occurs only at the boundary of capacitor array which contains many fingers of identical AC signals. If each of these AC signals were routed separately, a large routing area would be needed and a large unpredictable parasitic capacitance would be introduced.

The final rules for creating the zigzag structure are following:

- 1. When a filter's layout reaches the height limit, the capacitor fingers are "capped" with a compressor tile. The local routing for transmission zero and shunt inductor in this segment are completed and the next segment begins with another compressor tile.

- 2. An U-turn in the layout may only be made at the junction of a capacitor array. But it can not be turned at the junction of the capacitor array used in the simulation of the inductors to avoid additional AC signal routing.

- 3. The height of each segment may differ somewhat from the absolute height limit. The difference is always less than the height of the OTA cell used in the layout.

## 3.6.4 Final Assembly

After the software has processed the filter specification input and built the filter likely with more than one segment, final assembly begins. The segments of the filter are popped off the stack in order, and assembled with enough separation to reduce the AC signal cross-talk, as shown in Figure 3.10.

Figure 3.10 Filter segments routed together.

The height of each segment may vary slightly. To efficiently use the space, each segment is aligned with the current border of the previous segments instead of the border of the adjacent segment, as shown in Figure 3.10.

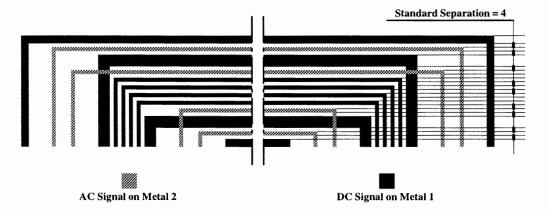

The AC signals between segments are routed with the layer metal 2 and the DC signals are routed with layer metal 1, as the example shown in Figure 3.11, To reduce the AC signal cross-talk as much as possible, all AC signals are separated by one or more DC signals.

Figure 3.11 Routing wires between segments.

After the final assembly, the labels for the input and output nodes of the filter are added onto the layout, and the final layout is stored as a MAGIC format file with the name that is specified in the *LC* ladder description file (the *filter\_name* in Table 3.2).

# **CHAPTER 4**

# **TESTING AND SIMULATION RESULTS**

Essentially, OTACC is the layout realization step in the filter design cycle. The previous step is the approximation step where the filter characteristics are converted into a set of element specifications that make up the filter. The step following the realization step is the verification step where the filter layout is simulated to verify that it meets the original specification. the OTACC input is the output of the approximation step, and the OTACC output is intended for verification/simulation.

To complete the verification using SPICE simulation, for example, the following procedures are required:

- 1. Generate the filter layout by running OTACC.

- 2. Extract the hierarchical circuit from the layout and generate the SPICE file.

- 3. Simulate the circuit by using SPICE.

- 4. Analyze the simulation results by comparing it with the original specification or the SPICE output of an ideal filter with same specification.

In order to fully automate the filter design and simulation process, a top-level design centering software may be utilized to control OTACC, Magic, Spice, and the comparison software. The user interface controls the data flow between the programs. This design centering software is the subject of another research project [27] [28].

More than twenty simulations were performed to verify the validity of the layout produced by OTACC. In most cases, the simulation results of the extracted filter layout meet the filter specifications. As examples, three different filters have been generated with different OTAs and simulated. The simulation results for each filter and OTA selection will be discussed in following sections.

|     | OTAs                  | FILTERs        |                |                 |  |  |

|-----|-----------------------|----------------|----------------|-----------------|--|--|

| No. | Developer             | Fourth-Order   | Eighth-Order   | Third–Order     |  |  |

|     |                       | Lowpass Filter | Lowpass Filter | Bandpass Filter |  |  |

| Ι   | Pan Wu                | Fully Verified | Fully Verified | Fully Verified  |  |  |

| II  | David Chiang          | Fully Verified | Fully Verified | Fully Verified  |  |  |

| III | Girish Chandrasekaran | Fully Verified | Failed         | Failed          |  |  |

Table 4.1 Filters be realized with different OTAs

The layouts of all filters listed in Table 4.1 are realized by running OTACC, and are simulated using U.C. Berkeley SPICE Version 3f4. The realization and simulation are executed on SPARC 5 work station using SunOS. The layouts of different filters are printed as a series of figures in Appendix F.

As shown in Table 4.1, OTA III failed to meet the specification in realizing an eighthorder lowpass filter and a third-order bandpass filter. OTACC generated the layout of the filter in one minute of wall-clock time or less. So the user can validate the filter design with certain OTAs in as little as ten minutes, and quickly fit the design with a suitable OTA.

#### 4.1 Fourth–Order Elliptic LC Lowpass Filter [1]

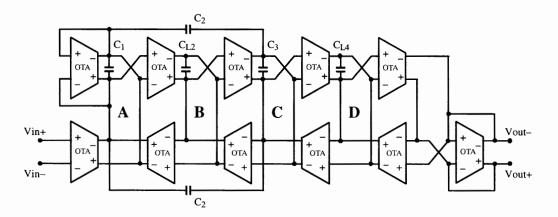

The schematic of a normalized fourth–order elliptic *LC* lowpass ladder is shown in Figure 4.1, and the schematic of the corresponding Transconductance–C realization using fully differential OTAs is shown in Figure 4.2.

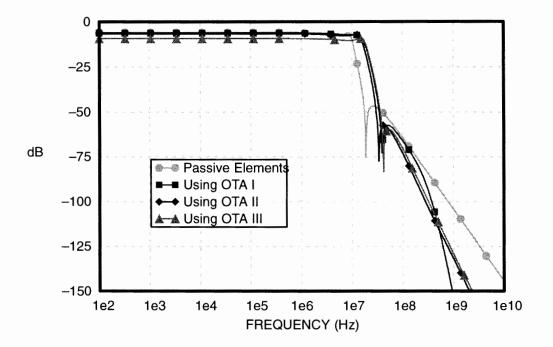

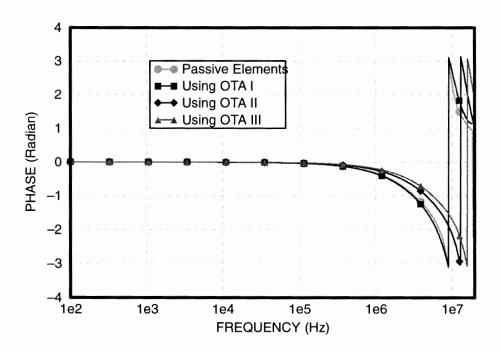

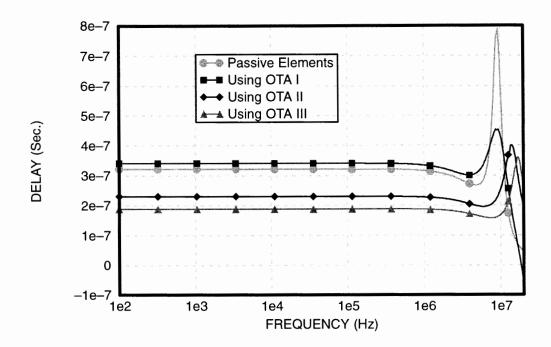

By using OTACC, three different versions of this design are generated using different OTA cells that are available in the current library. All SPICE simulations are based upon the circuit layout extraction. The magnitude responses of those filters are shown in Figure 4.3 and their phase and delay plots are shown in Figure 4.4 and Figure 4.5. The DC bias set points for the different OTAs are shown in Table 4.2. A comparison of the important characteristic of the filters is shown in Table 4.3. All parameters in this table are based on the simulation results and are not subject to adjustment or tuning.

Figure 4.1 Fourth–Order Elliptic Lowpass Filter.

Figure 4.2 Schematic diagram of  $G_m$ -C Fourth-Order Lowpass Filter.

| OTAs    | Power | DC Input | g <sub>m</sub> Control  | r <sub>o</sub> Control  | Misc.                                            | g <sub>m</sub> Value |

|---------|-------|----------|-------------------------|-------------------------|--------------------------------------------------|----------------------|

| OTAI    | ±5 V  | 0 V      | V <sub>is</sub> =2.75 V | V <sub>2</sub> =–2.68 V | V <sub>c</sub> =0 V ; V <sub>1</sub> =0 V        | 180 μS               |

| OTA II  | 5 V   | 2.5 V    | V <sub>f</sub> =1.5 V   | V <sub>q</sub> =2.1 V   | V <sub>bi</sub> =1.13 V ; V <sub>i1</sub> =2.5 V | 150 μS               |

| OTA III | 5 V   | 2.5 V    | V <sub>cf</sub> =1.03 V | V <sub>cq</sub> =2.65 V | V <sub>bias</sub> =1.2 V                         | 133 μS               |

Table 4.2 Bias set up for different OTAs in filter realization and simulation.

Figure 4.3 Magnitude response of Fourth–Order Lowpass Filter using different OTAs

Figure 4.4 Phase plot of Fourth–Order Lowpass Filters using different OTAs

Figure 4.5 Delay of Fourth–Order Lowpass Filters using different OTAs

| Fourth–Order<br>LP Filters | Cutoff<br>Frequency | Stopband<br>Frequency | Stopband<br>Attenuation | Passband<br>Ripple | Geometry:<br>WxH (um) | Linear Range<br>% of OTA |

|----------------------------|---------------------|-----------------------|-------------------------|--------------------|-----------------------|--------------------------|

| Specification              | 10 MHz              | 18 MHz                | 40.5 dB                 | 0 dB               |                       |                          |

| Using OTA I                | 17 MHz              | 39 MHz                | 50 dB                   | 0.9 dB             | 1482x1274             | 100%                     |

| Using OTA II               | 16 MHz              | 34 MHz                | 51 dB                   | 1 dB               | 1028x1126             | 100%                     |

| Using OTA III              | 17 MHz              | 41 MHz                | 48 dB                   | 1 dB               | 1150x927              | 100%                     |

Table 4.3 Comparison among the Fourth–Order Lowpass Filters using differentOTAs.

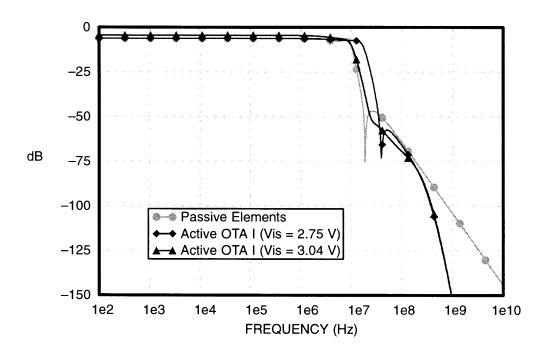

Due to the parasitic capacitance of the miscellaneous routing wires that can not be completely accounted by predistortion, non–linear variation of the input, output capacitance of OTAs, and the non–ideal character of the OTAs, the filter cutoff frequency varies from the desired frequency. This problem can be improved by more precisely filling the parameters in OTA technology file by the OTA cell designers. Fortunately, all the OTA cells in our library are designed with tuneable transconductance and this mechanism is proposed in the majority of designs in the literature. Therefore, the cutoff frequency of the filters can be adjusted to the desired frequency by tuning the  $g_m$  value of the OTAs. An example of the cutoff frequency tuning of the fourth–order elliptic lowpass filters is shown in Figure 4.6. Even though the notch is missing after the tuning of the transconductance value, the characteristics of the filter, such as stop band, pass band and transient band, are met by the tuned transconductance–C filter generated by OTACC.

Figure 4.6 Zero frequency tuning of Fourth-Order Lowpass Filter using OTA I.

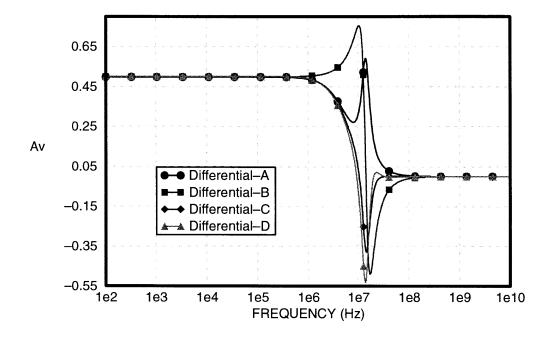

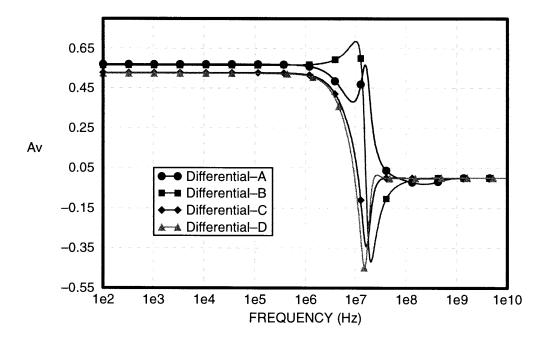

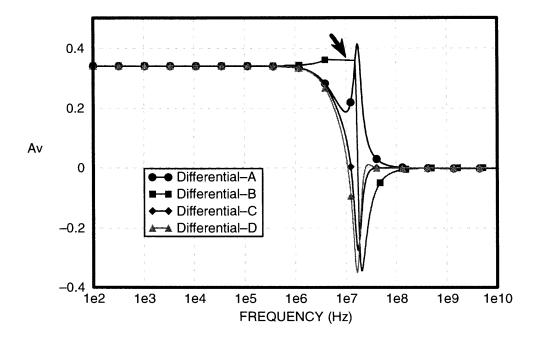

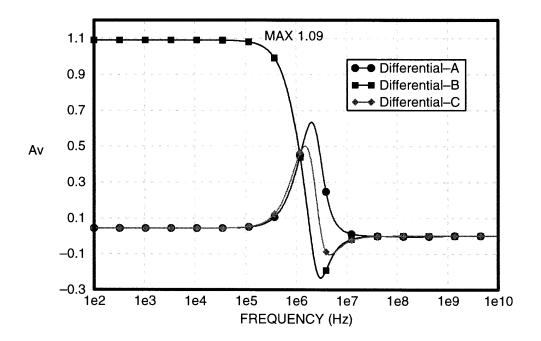

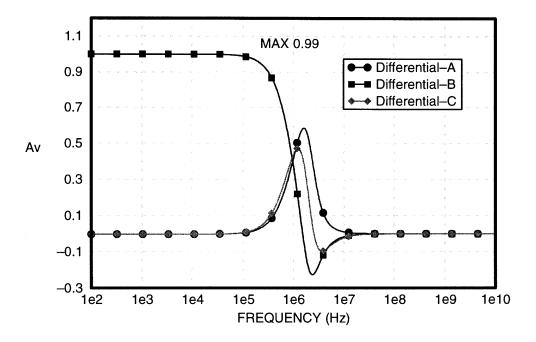

To further evaluate the performance of the filters and estimate the linear range of the overall filters, the voltage gains to each internal node of those filters at 200 mV AC input signal are plotted and shown in Figure 4.7, Figure 4.8, and Figure 4.9. The node names referred in those plots are corresponding to the names shown in Figure 4.2. From these plots, it can be seen that the voltage gain at each internal node is less than 1. Therefore the OTAs in the filters have their full dynamic range available.

Figure 4.7 Voltage gain to the internal nodes of the Fourth–Order Lowpass Filter using OTA I.

Figure 4.8 Voltage gain to the internal nodes of the Fourth–Order Lowpass Filter using OTA II.

Figure 4.9 Voltage gain to the internal nodes of the Fourth–Order Lowpass Filter using OTA III.

By using OTACC, the layout of those filters were generated in one minute (wallclock time) or less. The approximate wall–clock time for each step of the layout generation and simulation are shown in Table 4.4. If the user does not specify the height or width limit of the layout, OTACC will generate a layout that is roughly square. The geometric size of the layouts for the forth–order lowpass filter with different OTAs are shown in Table 4.5.

| Fourth-Order    | Processing Time (Sec) |            |           |         |       |  |  |

|-----------------|-----------------------|------------|-----------|---------|-------|--|--|

| Lowpass Filters | OTACC                 | Extraction | Ext2spice | Editing | Spice |  |  |

| Using OTA I     | 5                     | 10         | 2         | 1       | 60    |  |  |

| Using OTA II    | 5                     | 8          | 2         | 1       | 53    |  |  |

| Using OTA III   | 5                     | 7          | 2         | 1       | 35    |  |  |

Table 4.4 Approximate run time of AC analysis with 100 points per decade for the<br/>Fourth–Order Lowpass Filter on a SPARC 5 station

| Fourth–Order<br>Lowpass Filters | Size of     | Filters    | Size of OTAs |            |  |

|---------------------------------|-------------|------------|--------------|------------|--|

|                                 | Height (µm) | Width (µm) | Height (µm)  | Width (µm) |  |

| Using OTA I                     | 1274        | 1482       | 267          | 296        |  |

| Using OTA II                    | 1126        | 1028       | 206          | 180        |  |

| Using OTA III                   | 927         | 1150       | 154          | 213        |  |

Table 4.5 Geometric Size of the Layouts of the Forth–Order Lowpass Filters and the OTAs

From the test results for the Forth–Order Lowpass Filters shown above, it demonstrate that OTACC can realize the filter layout correctly and efficiently. From Figure 4.9, we can also find out that the filter using OTA III is in critical condition for normal operation. From Table 4.4 it can be concluded that the user can quickly optimize an OTA based filter design with OTACC.

# 4.2 Eighth–Order Inverse Chebyshev LC Lowpass Filter [1]

The schematic of the normalized eighth–order inverse Chebyshev *LC* lowpass ladder is shown in Figure 4.10. The schematic of the corresponding transconductance–C realization with fully differential OTAs is shown in Figure 4.11.

Figure 4.10 Eighth-Order Inverse Chebyshev Lowpass Filter.

Figure 4.11 Schematic diagram of  $G_m$ -C Eighth-Order Inverse Chebyshev Lowpass Filter.

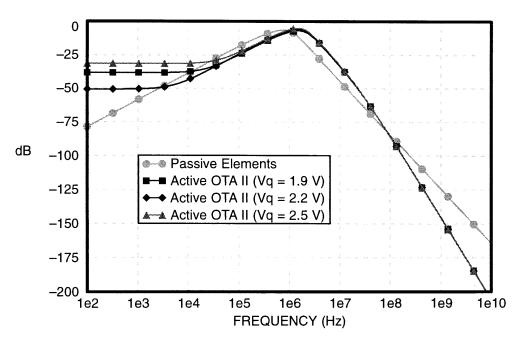

For the eighth–order inverse Chebyshev lowpass filter, OTA I and OTA II are chosen as examples. To examine the generality of OTACC, the same procedures as were used in the fourth–order lowpass filter, were used to test the eighth–order inverse Chebyshev lowpass filters. The bias set point for OTA I and OTA II are the same as shown in Table 4.2. The magnitude response for the two filters is shown in Figure 4.12. The phase and delay plots are shown in Figure 4.13 and Figure 4.14 respectively. The comparison of some important parameters of those filters is shown in Table 4.6. Because of the same reason in testing the Forth–Order Lowpass Filter, the filter cutoff frequency varies from the desired frequency. An example of the cutoff frequency tuning of the eighth–order lowpass filters is shown in Figure 4.15. The voltage gains to each internal node of those filters are plotted and shown in Figure 4.16, and Figure 4.17. The approximate wall–clock time for each step of the layout generation and simulation are shown in Table 4.7. The geometry size of the layouts for the eight–order lowpass filter with different OTAs are shown in Table 4.8.

Figure 4.12 Magnitude response of Eighth–Order Lowpass Filter using different OTAs

Figure 4.13 Phase plot of Eighth–Order Lowpass Filter using different OTAs

Figure 4.14 Delay of Eighth–Order Lowpass Filter using different OTAs

Figure 4.15 Zero frequency tuning of Eighth–Order Lowpass Filter using OTA I.

Figure 4.16 Voltage gain to the internal nodes of the Eighth–Order Lowpass Filter using OTA I.

Figure 4.17 Voltage gain to the internal nodes of the Eighth–Order Lowpass Filter using OTA II.

| Eighth–Order<br>LP Filters | Cutoff<br>Frequency | Stopband<br>Frequency | Stopband<br>Attenuation | Passband<br>Ripple | Geometry:<br>WxH (um) | Linearity:<br>% of OTA |

|----------------------------|---------------------|-----------------------|-------------------------|--------------------|-----------------------|------------------------|