Contents lists available at ScienceDirect

## Solid State Electronics

journal homepage: www.elsevier.com/locate/sse

# Performance and reliability in back-gated CVD-grown MoS<sub>2</sub> devices

Carlos Marquez<sup>a, c,\*</sup>, Norberto Salazar<sup>a</sup>, Farzan Gity<sup>b</sup>, Jose C. Galdon<sup>a</sup>, Carlos Navarro<sup>a</sup>, Ray Duffy<sup>b</sup>, Paul Hurley<sup>b</sup>, Francisco Gamiz<sup>a</sup>

<sup>a</sup> Nanoelectronics Group, Department of Electronics, CITIC-University of Granada, Granada 18071, Spain

<sup>b</sup> Nanoelectronic Materials and Devices Group, Tyndall National Institute, University College Cork, Cork T12 R5CP, Ireland

<sup>c</sup> Semiconductor Device Group, Departament of Electronic Engineering, ISOM-Polytechnic University of Madrid, Madrid 28040, Spain

#### ARTICLE INFO

Handling Editor: Bogdan Cretu

Keywords: Transition metal dichalcogenide Molybdenum disulfide MoS<sub>2</sub> Two-dimensional materials More than Moore Reliability Low-frequency noise

#### ABSTRACT

In this work, the electrical performance and reliability of as-synthesized CVD-grown  $MoS_2$  transistors directly grown on  $SiO_2/Si$  substrate without any transfer process have been evaluated. Transfer and output characteristics, current hysteresis, capacitance-voltage and low-frequency noise signatures have been characterized revealing the huge influence of surface and oxide defects and the disturbance due to the fluctuations of the carrier number on the back-gated transistor response.

## 1. Introduction

Since the discovery and isolation of graphene has been awarded with The Nobel Prize in Physics [1,2], two-dimensional (2D) materials have received an outstanding attention from various fields, especially in electronic, optics and photonic applications [3–5]. These 2D materials have demonstrated an optimal electrostatic control of the channel thanks to their reduced thickness with potentially better immunity to short channel effects than the planar silicon counterparts [6]. However, despite the exceptional properties of graphene [7], the absence of a band gap limits its application in digital electronics. As alternative, the transition metal dichalcogenides (TMDs) have taken advantage of the reduced thickness with a non zero-bandgap to preserve interesting properties in electronic applications [8]. Advantages in terms of higher ON/OFF ratios, reduced power consumption, lower current leakage and shorter switching delay are expected according to the International Roadmap for Devices and Systems (IRDS) guideline [9]. Inside the TMDs family, molybdenum disulfide (MoS<sub>2</sub>) has emerged as a prominent candidate to advance in the progressive scaling of the semiconductor industry. MoS<sub>2</sub> presents indirect to direct bandgap transition as the film thickness is reduced from multilayer to monolayer due to quantum confinement. Moreover, a band gap in the range of 1.2-1.8 eV [10], makes it suitable for near-infrared absorption and emission applications in optoelectronics. However, in general terms, the fabrication and processing of these materials to be integrated in ultimate electronic devices is still a bottleneck. Costly fabrication methods and non-optimized integration with industrially standardized insulators and materials result in device performances which rarely accomplish the promising theoretical properties. On the one hand, the advance on the synthesis method is crucial. Despite fundamental physics and devices on 2D TMDs have relied on the exfoliation method [11,12], wafer-scale deposition of films with well-controlled properties is mandatory in semiconductor industry. In this regard, vapor deposition techniques (CVD) [13,14], metal-organic CVD (MOCVD) [10] or plasma enhanced chemical vapor deposition (PECVD) [15,16] are being extensively explored due to their potential for high scalability. Withal, precise film deposition with wellcontrolled properties and thicknesses is still a challenge. On the other hand, despite the advances on the device reliability when using these materials [17-19], defects and impurities (grain boundaries, corrugation, sulfur vacancies, oxygen or moisture incorporation and oxide ions) still play an important role on the actual drop in performance of the fabricated transistors (Schottky barriers and current hysteresis). To advance in this aspect, in our previous work, we addressed the scalable fabrication of back-gated MoS2 devices following a chemical vapor deposition (CVD) synthesis, without any film transfer, and a standard CMOS photolitography and etching processing [20]. The transient

https://doi.org/10.1016/j.sse.2021.108173

Received 7 December 2020; Received in revised form 11 June 2021; Accepted 16 June 2021 Available online 19 August 2021 0038-1101/© 2021 The Author(s). Published by Elsevier Ltd. This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-ad/4.0/).

<sup>\*</sup> Corresponding author at: Nanoelectronics Group, Department of Electronics, CITIC-University of Granada, Granada 18071, Spain. *E-mail address:* carlosmg@ugr.es (C. Marquez).

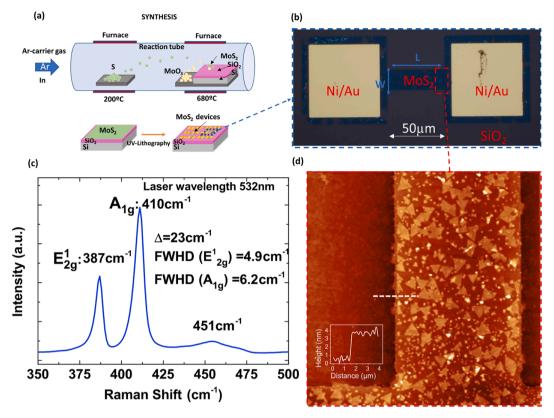

**Fig. 1.** a) Scheme of the synthesis (top) and lithography (bottom) processes. b) Optical image of a fabricated 50  $\mu$ m-length device. MoS<sub>2</sub> appears as a blue layer. c) Raman characterization of the synthesized MoS<sub>2</sub> layer carried out using 532 nm-wavelength laser. d) Atomic force microscopy a MoS<sub>2</sub> device. Inset: topography profile corresponding to the dashed line.

response of the conformed Schottky barrier devices were analyzed. In this work, we extended this study to evaluate the performance and the reliability implications of these fabricated transistors. Importantly, these devices have not been passivated or encapsulated in order to address the investigation on the inherit properties of the interfaces and the assynthesized material. Moreover, this kind of study is mandatory to determine the potential of these devices as sensors or detectors, where direct interaction of the target with the surface of the bare material could be required. Regrettably, the absence of encapsulation, passivation layers or the characterization under ambient conditions make that variability due to disturbing mechanisms (defect, adsorbates, oxide traps ...) could be comparable with the effect of dimension scaling (L or W) in the electrical parameters. This is the reason why despite having devices with different footprints, this study is more focused on determining the possible origin and implications of these disturbing mechanisms than on the optimization of the devices in terms of channel length or width.

### 2. Experimental and measurement setup

The direct synthesis of large-area  $MoS_2$  films on an n-type silicon substrate (1  $\times$  10<sup>15</sup> cm<sup>-3</sup>) covered by a 100 nm-thick SiO<sub>2</sub> layer was accomplished via CVD through sulfurization of molybdenum trioxide (MoO<sub>3</sub>) at a maximum temperature of 680 °C [20]. This process was carried out in a two-temperature-zone furnace as Fig. 1.a (top) indicates. Later, optical photolithography was employed to define the source and drain patterns, a scheme is shown in Fig. 1.a (bottom) summarizing the process: electron beam evaporation was used to deposit the Ni/Au electrodes. The thicknesses of Ni and Au were 20 nm and 200 nm, respectively. A lift-off process was carried out to complete contact fabrication of the back-gated MoS<sub>2</sub> FET. Then, a dry etching of the MoS<sub>2</sub> material outside the channel between S/D contacts was performed. The hard mask employed during the photolithography process allowed the fabrication of devices with a range of different channel lengths and widths as the optical microscope characterization shows (Fig. 1.b). The observed pads correspond to drain and source contacts. To improve the conductivity and reduce the contact resistance, the metal pads (Ni/Au) are deposited directly on the MoS<sub>2</sub>, i.e, there is a MoS<sub>2</sub> layer underneath the deposited contacts increasing the contact area. Regarding the layer thickness, the structural analysis was carried out by Raman spectroscopy (Jasco NRS-5100) and atomic force microscopy (NTMDT NTEGRA). The static DC characteristics were acquired using a Keithley SCS 4200 and an Agilent B1500 systems. The low-frequency noise characterization was carried out using a low-noise-current amplifier connected to a software-based spectrum analyzer [21].

## 3. Results and discussion

## 3.1. Structural characterization

Fig. 1.c shows the Raman characterization of the MoS<sub>2</sub> film exhibiting the two Raman characteristic bands at 387 ( $E_{2g}^1$ ) and 410 cm<sup>-1</sup> ( $A_g^1$ ) with a shift between peaks ( $\Delta$ ) around 23 cm<sup>-1</sup>. These results are consistent with the presence of thin MoS<sub>2</sub> layers [22]. The additional peak observed at 451 cm<sup>-1</sup> is usually attributed to disorders or partial oxidation on the MoS<sub>2</sub> sample [23]. This fact could suggest the presence of dislocation or impurities on the MoS<sub>2</sub> layer. In this case, due to the absence of any passivation on the samples, these disorders may be caused by the interaction with the ambient, with the SiO<sub>2</sub> interface or be intrinsic to the material growth. Fig. 1.d shows the result of the atomic force microscopy characterization. Channel conformed by coalescence of triangle flakes of MoS<sub>2</sub> can be inferred. As the topography profile shows in the inset of Fig. 1.d, this device presents a 4 nm-thick MoS<sub>2</sub> channel approximately. Under similar synthesis conditions, samples

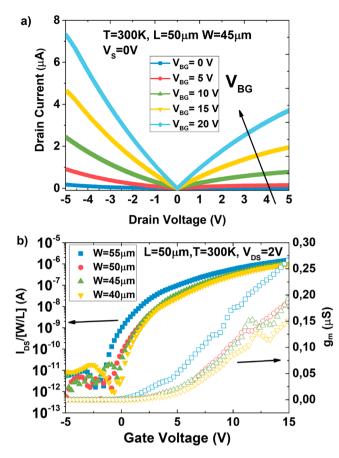

**Fig. 2.** a) Output characteristic for different back-gate biases. b) Normalized transfer characteristic for different device widths and the correspondent transconductace. Asymmetrical behavior in a) and absence of hole current in b) are attributed to back-to-back Schottky barriers. The Schottky barriers are modulated with the back-gate bias.

with down to 1.5 nm-thick MoS<sub>2</sub> channels have been achieved [20].

## 3.2. Electrical performance

The output characteristic ( $I_D$ - $V_D$ ) of a 50  $\mu$ m-length and 45  $\mu$ m-width device is depicted in Fig. 2.a. Different back-gate biases ( $V_{BG}$ ) reveal the modulation of the channel resistance with the applied voltage. The non-symmetrical and non-linear nature of these curves indicates the formation of back-to-back Schottky diodes in the metal–semiconductor interfaces [17,20].

Fig. 2.b shows the normalized transfer characteristic  $(I_D - V_{BG})$ , in logarithmic scale, for devices with different channel width. Despite the work function of the selected metals (Ni/Au) would facilitate the ambipolar behavior (both electron and hole currents), the curve presents only electron current characteristic. This absence of hole current demonstrates the Schottky barrier formation which blocks these carriers. This Schottky barrier is usually attributed to Fermi level pinning at the metal-semiconductor interface [24]. An extensive study of the Schottky barrier formation and how the current is modeled by the thermo-ionic emission in these devices can be found in [20]. The ON/OFF current ratio for these devices is around 10<sup>6</sup>. The transconductance is depicted in the right axis in Fig. 2.b. The curves present a monotonic increasing behaviour with a lack of saturation in the drain current. This result could be explained considering that the source-drain current is not only modelled by the carrier density in the channel but also by the Schottky diodes (metal-semiconductor junctions) whose barrier height depends on the applied gate bias as demonstrated in [20]. Due to the singular behavior of our devices with this monotonic increase in the

**Fig. 3.** a) Field effect mobility for two different gate lengths as a function of the channel width. b) Total resistance as a function of the channel dimension ratio (L/W). In dashed line the regression curve for the extraction of the sheet and contact resistances. Gate overdrive voltage,  $V_{OV} = 10$  V and low lateral voltage  $V_D = 0.1$  V.

transconductance, the mobility will present an increase with the gate voltage where field effect mobility ( $\mu_{FE}$ ) can be calculated following the expression:

$$\mu_{FE} = \frac{1}{C_{ox}} \frac{L}{W} \frac{dI_{DS}}{dV_{GS}} \frac{1}{V_{DS}}$$

(1)

where  $C_{ox} = \epsilon_{ox}/t_{ox}$  is the capacitance per unit area of the SiO<sub>2</sub> gate oxide dielectric, *L* and *W* are the channel length and width, respectively. Fig. 3.a shows the case for a gate overdrive voltage ( $V_{OV}=V_G-V_T$ ),  $V_{OV} =$ 10 V, and devices of two channel lengths and different channel widths. A smooth decrease in the mobility is presumable reducing the device dimensions, probably due to the higher influence of border effects and traps in smaller channels. The highest mobility observed in our characterized devices corresponds to  $\mu = 2.2 \text{ cm}^2 V^{-1} \text{s}^{-1}$ . This mobility results are around one order of magnitude lower than the reported in other studies after annealing or passivisation processes [25,26]. This effect could indicate that mobility is also limited by process residuals, surface roughness and other defects specially presented in these non-passivated devices.

Regarding the semiconductor conductance and contact resistance, Fig. 3.b depicts the total resistance measured as a function of the physical dimension ratio (L/W) of the devices. Through these results the sheet resistance, conductance and contact resistance can be extracted. Considering the total resistance should follow the expression:  $R = (L/W)\rho_S + 2R_C$  where  $\rho_S = \rho/t$  being  $\rho$  the material resistivity, t the thickness and Rc the corresponding contact resistance. Please note that this evaluation method could underestimate the value of mobility, contact and channel resistances. However this extraction could present a reasonable approach in absence of TLM structures [27] or when more accurate methods such as Y-function based method [28] cannot be applied due to the contact resistance dependence with gate voltage. From the experimental extrapolation (dashed curve in Fig. 3.b) the results are  $\rho \approx 1.3 \ \Omega.cm$  and the contact resistance  $R_C \approx 0.15 \ M\Omega$  ( $t \approx 4$ nm  $V_{OV} = 10 \ V$  and  $V_{DS} = 0.1 \ V$ ).

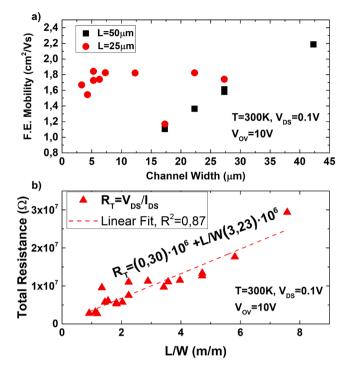

Fig. 4. Transfer characteristic of a back-gated transistor for different drain voltages in a double voltage sweep. L = 50  $\mu$ m, W = 45  $\mu$ m.

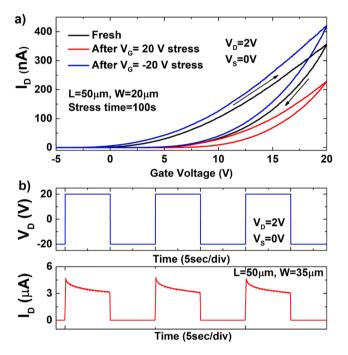

**Fig. 5.** a) Transfer characteristic for a device at fresh conditions (blue), after a gate pulse of 20 V for 100 s (red) and after a gate pulse of -20 V for 100 s (blue). Drain current response of a device (bottom) to successive positive (stress) and reverse (recover) back gate pulses (top). L =  $50\mu$ m, W =  $35\mu$ . (For interpretation of the references to color in this figure legend, the reader is referred to the web version of this article.)

The relative low mobility and the high contact resistance, together with the Fermi-level pinning causing the Schottky barriers at the contact-MoS<sub>2</sub> junction, may have their origin in defects, traps and impurities but not exclusively in these phenomena. To further analyze these issues and the implications of defects in the reliability of the devices, Fig. 4 depicts the transfer characteristic of a 10  $\mu$ m-length and 60  $\mu$ m-width device in a double gate voltage sweep characterization for different drain biases.

The current hysteresis for different drain voltages shown in Fig. 4 suggests the presence of traps at the  $MoS_2/SiO_2$  interface, surface or in the oxide. Although in our previous work we demonstrated that an anticlockwise behavior (for thicker devices) may suggest initial transient response of the device which needs an initial time to form the inversion

Fig. 6. a) Capacitance–voltage (C-V) characteristics for two frequencies and b) Conductance-voltage (G-V) characteristic. Room temperature for a L = 25  $\mu m$  and W = 25  $\mu m$  back-gated device.

layer [20], in this case the clockwise behavior (marked with the arrows) points to trapping and detrapping carrier phenomena and mobile ions in the oxide or at interface as main mechanism [29,18,30,31]. A charge density change during the characterization induces a shift (increase) in the threshold voltage, therefore the channel resistance is higher (lower current level) in the backward voltage swept. When a forward gate bias is applied, the traps whose energy levels are below the Fermi level are filled by electrons with different characteristic times. The trapped electrons and the shift of mobile ions contribute to the increase of negative charge and therefore, increase the threshold voltage. To determine if this threshold voltage shift is permanent, the transfer characteristic of a device is characterized before and after applying positive and negative back gate pulses, Fig. 5.a. As Fig. 5.a shows, this threshold voltage shift can be totally inverted with a recovery pulse. A more complete perspective of these effects can be acquired measuring the device response while the stress/recovery gate voltage pulses are applied, Fig. 5.b. Please note that the on-operation of the device happens only for the positive gate bias. In this on-the-fly characterization both previous effects are observed: i) there is a current decay as a function of the time while a positive voltage pulse is applied, which induces the hysteresis at double sweep characterizations (Figs. 4 and 5.a); and ii) the initial current level is recovered after the negative pulse ( $V_G$ =-20 V), repeating the same response in successive stress periods. The origin of defects and ions which induce these characteristic response on the devices could be associated with both extrinsic (diffused water molecules and the chemisorption of oxygen and intrinsic defect at the interface due to oxygen and sulfur vacancies [32,18,29], or even defects due to a nonpassivated surface bonds of the  $MoS_2$  [33].

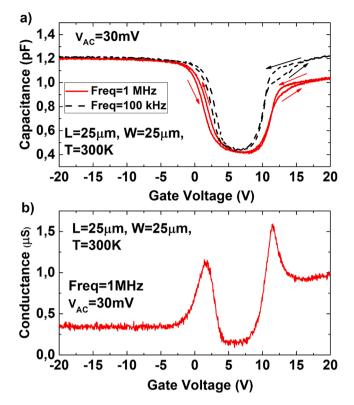

More information regarding the type of defects can be determined through capacitance–voltage (C-V) characterization. The measurement is carried out directly on the fabricated MOSFET devices (Si/SiO<sub>2</sub>/MoS<sub>2</sub>), where the force and low biases are applied at the Si substrate and at the drain contact, respectively. Fig. 6.a shows the C-V characteristic of

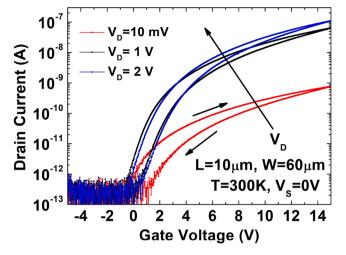

**Fig. 7.** a) Spectral density of the noise for a L = 25  $\mu$ m and W = 30  $\mu$ m device for different gate biases. V<sub>G</sub> from 2.5 V to 5 V with 0.5 V step. b) Normalized spectral noise density of the current as a function of the frequency for different device dimensions. W from 30  $\mu$ m to 60  $\mu$ m with 5  $\mu$ m step. V<sub>S</sub> = 0 V, T = 300 K.

a 25  $\mu$ m-length and 25  $\mu$ m-width device. Two frequencies (f = 100 kHz and f = 1 MHz) are recorded both for double voltage sweep measurements. The structure presents a clear accumulation channel, a depletion region and a inversion channel corresponding to the electron carriers (positive voltages at the back gate). Note that the measured maximum capacitance ( $C_{ox} = 1.24$  pF) agrees with the theoretical oxide capacitance value (Cox) for a 100 nm-thick SiO2 oxide and the area of the contact. Regarding the influence of traps in the device behavior, this device presents frequency dispersion in the inversion region, usually attributed to border traps [34]. A shift in the flat-band and threshold voltage is also inferred from the C-V characteristic. This shift depending on the signal frequency is attributed to the interface traps [34,19]. In accordance with this suggestion is the presence of conductance  $(G_n)$ peaks shown in Fig. 6.b, which marks the activity of mid-gap traps representing the losses due to the exchange of carriers with the interface traps [35,36,34].

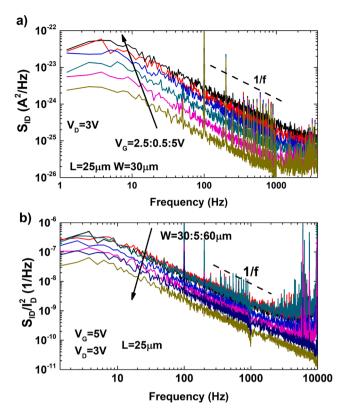

Additionally to C-V and I-V characteristics, low-frequency noise characterization may shed light on the traps and defect origin. Fig. 7.a depicts the spectrum of the current noise for different gate biases. The spectral signature presents an unambiguous 1-decade/1-decade characteristic associated with the flicker (1/f) noise contribution [37–39]. Flicker noise is usually caused by imperfections of the fabrication process and material defects appearing mostly at low frequencies. In transistors, the trend was described by McWhorther [37], who attributed the source of 1/f noise to slow oxide traps, ruled by the carrier tunneling between the inversion channel and slow oxide traps located at the Si-SiO<sub>2</sub> interface. The result is a carrier number fluctuation during the device operation. As previous C-V and Raman characterizations indicate, in our devices, the carrier trapping phenomena could take place both at the semiconductor surface due to the non-passivated characteristic and in the oxide traps located close to the MoS<sub>2</sub>/SiO<sub>2</sub> interface.

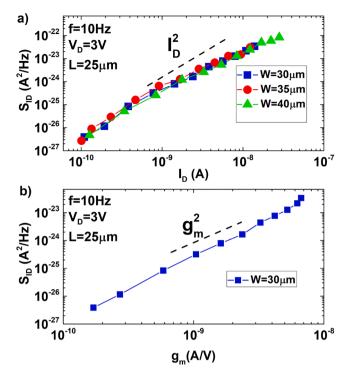

**Fig. 8.** Current noise spectral densities as a function of a) drain current and b) transconductance for different front-gate biases at f = 10Hz. Different channel widths are characterized in a) for devices with 25  $\mu$ m channel length. V<sub>S</sub> = 0 V, T = 300 K.

For the sake of comparison, normalized spectral noise density is shown in Fig. 7.b for devices with different physical dimensions. Narrower devices present higher noise levels in normalized spectrum representation. This increase is expected with device scaling (voltage flat band noise level scales with the factor 1/WL) and the possible contribution of high series and contact resistances to the total noise spectrum [40,41,39].

Additionally, Fig. 8.a shows the noise power spectral density as a function of the drain current. Curves follow a quadratic trend with the drain current,  $S_{ID}(f) \propto I_D^2$ . Fig. 8.b shows how the noise power spectral density also follows a quadratic trend with the transconductance ( $g_m$ ) corroborating that the low frequency noise is a trap-related (carrier number fluctuations) and not a mobility related ( $S_{ID} \propto I_D$ ) effect [42].

## 4. Conclusion

In this work, the performance and reliability of MoS<sub>2</sub> transistors have been studied. Back-gated transistors fabricated following a scalable chemical vapor deposition synthesis have demonstrated high current ratios and considerable contact resistance. The electrical characterization reveals the Schottky barrier formation suppressing the hole current due to Fermi level pinning. This pinning is probably caused by imperfections and defects. The reliability study demonstrates that defects also produce current hysteresis. Capacitance–voltage characterization shows frequency dispersion indicating the presence of both interface and border traps in the devices. Finally, the devices present a flicker noise characteristic which points to trapping/de-trapping phenomena influenced by the back-gate bias. These trapping phenomena induces a carrier number fluctuation which has more impact in narrower devices.

### **Declaration of Competing Interest**

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

#### Acknowledgment

This project has received funding from the European Union's Horizon 2020 research and innovation programme under the Marie Skłodowska-Curie grant agreement No 895322, from the Spanish Government under Juan de la Cierva Formacion Grant No. FJC2018-038264-I. The Spanish Program (TEC2017-89800-R), ASCENT (EU Horizon 2020 GRANT 654384) and Science Foundation Ireland: INVEST (SFI-15/IA/3131) and AMBER (12/RC/2278-P2) are also thanked for financial support. Funding for open access charge: Universidad de Granada / CBUA.

#### References

- [1] Novoselov KS, Jiang D, Schedin F, Booth TJ, Khotkevich VV, Morozov SV, Geim AK. Two-dimensional atomic crystals. Proc Nat Acad Sci 2005;102(30): 10451-3. https://doi.org/10.1073/pnas.0502848102.

- [2] Novoselov KS, Geim AK, Morozov SV, Jiang D, Zhang Y, Dubonos SV, Grigorieva IV, Firsov AA. Electric field effect in atomically thin carbon films.

- Science 2004;306(5696):666–9. https://doi.org/10.1126/science.1102896. [3] Novoselov KS, Falko VI, Colombo L, Gellert PR, Schwab MG, Kim K. A roadmap for graphene. Nature 2012;490(7419):192-200. https://doi.org/10.1038/ ature11458

- [4] Ferrari AC, Bonaccorso F, Fal'ko V, Novoselov KS, Roche S, Bøggild P, et al., Science and technology roadmap for graphene, related two-dimensional crystals, and hybrid systems. Nanoscale 2015;7(11):4598-4810. doi:10.1039/ C4NR01600A

- [5] Han J, Wang J. Photodetectors based on two-dimensional materials and organic thin-film heterojunctions. Chin Phys B 2019;28(1):017103. https://doi.org. 10.1088/1674-1056/28/1/017103

- [6] Chhowalla M, Jena D, Zhang H. Two-dimensional semiconductors for transistors. Nat Rev Mater 1(16052). doi:10.1038/natrevmats.2016.52.

- Geim AK, Novoselov KS. The rise of graphene, Nat Mater 2007;6(3):183-191. doi: [7] 10.1038/nmat1849.

- Alam K, Lake RK. Monolayer MoS2 transistors beyond the technology road map. [8] IEEE Trans Electron Devices 2012;59(12):3250-4. https://doi.org/10.1109 FED.2012.2218283

- [9] IRDS, International roadmap for devices and systems: beyond CMOS (2017).

- [10] Cwik S, Mitoraj D, Mendoza Reyes O, Rogalla D, Peeters D, Kim J, et al., Direct growth of MoS2 and WS2 layers by metal organic chemical vapor deposition. Adv Mater Interf doi:10.1002/admi.201800140.

- [11] Radisavljevic B, Radenovic A, Brivio J, Giacometti V, Kis A. Single-layer MoS2 transistors. Nat Nanotechnol 6 (March). doi:10.1038/nnano.2010.279.

- Molina-Sanchez A, Wirtz L. Phonons in single-layer and few-layer MoS2 and WS2. [12] Phys Rev B doi:10.1103/PhysRevB.84.155413.

- [13] Liu KK, Zhang W, Lee YH, Lin YC, Chang MT, Su CY, et al., Growth of large-area and highly crystalline  $MoS_2$  thin layers on insulating substrates. Nano Lett. doi: 10.1021/nl2043612.

- [14] Van Der Zande AM, Huang PY, Chenet DA, Berkelbach TC, You Y, Lee GH, et al., Grains and grain boundaries in highly crystalline monolayer molybdenum disulphide. Nat Mater doi:10.1038/nmat3633.

- Kim H, Ahn C, Arabale G, Lee C, Kim T. Synthesis of MoS2 Atomic Layer using [15] PECVD, ECS Trans doi:10.1149/05808.0047ecst.

- [16] Kaindl R, Bayer BC, Resel R, Müller T, Skakalova V, Habler G, et al., Growth, structure and stability of sputter-deposited MoS2 thin films. Beilstein J Nanotechnol doi:10.3762/bjnano.8.113.

- [17] Di Bartolomeo A, Grillo A, Urban F, Iemmo L, Giubileo F, Luongo G, Amato G, Croin L, Sun L, Liang S-J, Ang LK. Asymmetric Schottky contacts in bilayer MoS2 field effect transistors. Adv Funct Mater 2018;28(28):1800657. https://doi.org/ 10.1002/adfm.20180065

- [18] Illarionov YY, Rzepa G, Waltl M, Knobloch T, Grill A, Furchi MM, Mueller T, Grasser T. The role of charge trapping in MoS<sub>2</sub>/SiO<sub>2</sub> and MoS<sub>2</sub>/hBN field-effect transistors. 2D Mater 2016;3(3):035004. https://doi.org/10.1088/2053-1583/3/ 3/035004

- [19] Zhao P, Azcatl A, Gomeniuk YY, Bolshakov P, Schmidt M, McDonnell SJ, Hinkle CL, Hurley PK, Wallace RM, Young CD. Probing Interface Defects in Top-Gated MoS2 Transistors with Impedance Spectroscopy. ACS Appl Mater Interf 2017;9(28):24348-56. https://doi.org/10.1021/acsami.7b06

- [20] Marquez C, Salazar N, Gity F, Navarro C, Mirabelli G, Galdon JC, et al., Investigating the transient response of Schottky barrier back-gated MoS2 transistors. 2D Mater doi:10.1088/2053-1583/ab7628.

- [21] Chroboczek J. Automatic, wafer-level, low frequency noise measurements for the interface slow trap density evaluation. In: International conference on microelectronic test structures, 2003, IEEE, 2003, pp. 95-98. doi:10.1109/ ICMTS.2003.1197409.

- [22] Li H, Zhang Q, Yap CCR, Tay BK, Edwin THT, Olivier A, Baillargeat D. From bulk to monolayer MoS2: Evolution of raman scattering. Adv Funct Mater 2012;22(7): 1385-90. https://doi.org/10.1002/adfm.201102111.

- [23] Mignuzzi S, Pollard AJ, Bonini N, Brennan B, Gilmore IS, Pimenta MA, Richards D, Roy D. Effect of disorder on Raman scattering of single-layer MoS2. Phys Rev B 2015;91(19):195411. https://doi.org/10.1103/PhysRevB.91.195411

- [24] Das S, Chen HY, Penumatcha AV, Appenzeller J. High performance multilayer MoS2 transistors with scandium contacts. Nano Lett 2013;13(1):100-5. https://doi. org/10.1021/nl303583v.

- [25] Smithe KK, Suryavanshi SV, Muñoz Rojo M, Tedjarati AD, Pop E. Low variability in synthetic monolayer MoS2 devices. ACS Nano 2017;11(8):8456-8463. doi: 10.1021/acsnano.7b04100.

- [26] Illarionov YY, Smithe KKH, Waltl M, Knobloch T, Pop E, Grasser T. Improved hysteresis and reliability of MoS2 transistors with high-quality CVD Ggrowth and Al2O3 encapsulation. IEEE Electr Device Lett 2017;38(12):1763-6. https://doi.org/ 10.1109/LED.2017.2768602

- [27] Mitta SB, Choi MS, Nipane A, Ali F, Kim C, Teherani JT, Hone J, et al., Electrical characterization of 2D materials-based field-effect transistors. 2D Mater 8(1). doi: 10.1088/2053-1583/abc187.

- [28] Pacheco-Sanchez A, Jiménez D. Accuracy of Y-function methods for parameters extraction of two-dimensional FETs across different technologies. Electron Lett 2020;56(18):942-5. https://doi.org/10.1049/el.2020.1502.

- [29] Late DJ, Liu B, Matte HSSR, Dravid VP, Rao CNR. Hysteresis in single-layer MoS2 field effect transistors. ACS Nano 2012;6(6):5635-41. https://doi.org/10.1021/ nn301572c.

- [30] Di Bartolomeo A, Genovese L, Foller T, Giubileo F, Luongo G, Croin L, Liang S-J, Ang LK, Schleberger M. Electrical transport and persistent photoconductivity in monolayer MoS2 phototransistors. Nanotechnology 2017;28(21):214002. https:// doi.org/10.1088/1361-6528/aa6d98.

- [31] Di Bartolomeo A, Genovese L, Giubileo F, Iemmo L, Luongo G, Foller T, Schleberger M. Hysteresis in the transfer characteristics of MoS2 transistors. 2D Mater 2017;5(1):015014. https://doi.org/10.1088/2053-1583/aa91a7

- [32] Qiu H, Pan L, Yao Z, Li J, Shi Y, Wang X. Electrical characterization of back-gated bi-layer MoS<sub>2</sub> field-effect transistors and the effect of ambient on their performances. Appl Phys Lett 2012;100(12):123104. https://doi.org/10.1063/ .3696045.

- [33] Shu J, Wu G, Guo Y, Liu B, Wei X, Chen Q. The intrinsic origin of hysteresis in MoS2field effect transistors. Nanoscale 2016;8(5):3049-56. https://doi.org/ 10.1039/c5nr07336g

- [34] Zhao P, Padovani A, Bolshakov P, Khosravi A, Larcher L, Hinkle PKHCL, Wallace RM, Young CD, Understanding the Impact of Annealing on Interface and Border Traps in the Cr/HfO2/Al2O3/MoS2 System. ACS Appl Electr Mater 2019. https://doi.org/10.1021/acsaelm.8b00103. acsaelm.8b00103.

- [35] Xia P, Feng X, Ng RJ, Wang S, Chi D, Li C, He Z, Liu X, Ang K-W. Impact and origin of interface states in MOS capacitor with monolayer MoS2 and HfO2 high-k dielectric. Sci Rep 2017;7(1):40669. https://doi.org/10.1038/srep

- [36] Hurley PK, O'Connor É, Djara V, Monaghan S, Povey IM, Long RD, Sheehan B, Lin J, McIntyre PC, Brennan B, Wallace RM, Pemble ME, Cherkaoui K. The characterization and passivation of fixed oxide charges and interface states in the Al<sub>2</sub>O<sub>3</sub>/InGaAs MOS system. IEEE Trans Device Mater Reliab 2013;13(4):429-43. https://doi.org/10.1109/TDMR.2013.2282216.

- [37] McWhorter AL. 1/f noise and germanium surface properties, semiconductor surface Physics 1957

- [38] Hooge F, 1/f noise, Physica B+C 1976;83(1):14-23. doi:10.1016/0378-4363(76) 90089-9.

- [39] Balestra F, Ghibaudo G, Jomaah J. Modeling of low-frequency noise in advanced CMOS devices. Int J.Numer Model Electron Netw Devices Fields 2015;28(6): 613-27. https://doi.org/10.1002/jnm.2052.

- Li X, Vandamme L. An explanation of noise in LDD MOSFETs from the ohmic [40] region to saturation. Solid-State Electron 1993;36(11):1515-21. https://doi.org/ 10 1016/0038-1101(93)90022-L

- Contaret T, Romanjek K, Boutchacha T, Ghibaudo G, Bøeuf F. Low frequency noise [41] characterization and modelling in ultrathin oxide MOSFETs. Solid-State Electron 2006;50(1):63-8. https://doi.org/10.1016/j.sse.2005.10.035. Jomaah J, Balestra F, Ghibaudo G. Low frequency noise in advanced Si bulk and

- [42] SOI MOSFETs. J Telecommun Inf Technol 2005;1(1):24-32.

Carlos Marquez received the M.Sc. degree in telecommunication engineering, the M.S. degree in electrical engineering, and the Ph.D. degree in electronics from the University of Granada, Granada, Spain, in 2012, 2014, and 2017, respectively. Since 2013 he is with the Nanoelectronics Group in the Department of Electronics at University of Granada, Spain. His research interests include electrical characterization of semiconductor devices, MOSFET front-end-of the line (FEOL) reliability, onetransistor dynamic-random-access memory cells (1T-DRAM)

and two dimensional (2D) materials. Dr. Carlos Marquez is author or co-author of 22 peerreviewed indexed journal articles, 5 book chapters, 2 patents and 20 conference contributions (some invited).

He has been collaborating as post-doc with different groups through international funded projects, 20 months at Tyndall National Institute (Ireland) and 6 months at Polytechnical Madrid University (Spain). Since the end of 2020 he leads a Marie Curie Global postdoctoral fellowship (895322-TRAPS-2D) to advance in the fabrication and reliability of MoS<sub>2</sub> and other 2D electronic devices. This project is carried out between National Chiao Tung University, in Taiwan and University of Granada, in Spain.