${\bf MSc\ Thesis}$   ${\bf Master's\ Programme\ in\ Computer\ Science}$

# Modelling a Distributed Data Acquisition System

John Lång

June 7, 2021

FACULTY OF SCIENCE

UNIVERSITY OF HELSINKI

# Supervisor(s)

Prof. Keijo Heljanko

# Examiner(s)

Prof. Keijo Heljanko,

Ph.D. Jarno Alanko

## Contact information

P. O. Box 68 (Pietari Kalmin katu 5)

00014 University of Helsinki, Finland

Email address: info@cs.helsinki.fi

URL: http://www.cs.helsinki.fi/

#### HELSINGIN YLIOPISTO — HELSINGFORS UNIVERSITET — UNIVERSITY OF HELSINKI

| Tiedekunta — Fakultet — Faculty     |                   | Koulutusohjelma — U | tbildningsprogram — Study programme     |

|-------------------------------------|-------------------|---------------------|-----------------------------------------|

| Faculty of Science                  |                   | Master's Program    | mme in Computer Science                 |

| Tekijä — Författare — Author        |                   |                     |                                         |

| John Lång                           |                   |                     |                                         |

| Työn nimi — Arbetets titel — Title  |                   |                     |                                         |

| Modelling a Distributed Data Acq    | uisition System   |                     |                                         |

| Ohjaajat — Handledare — Supervisors |                   |                     |                                         |

| Prof. Keijo Heljanko                |                   |                     |                                         |

| Työn laji — Arbetets art — Level    | Aika — Datum — Mo | onth and year       | Sivumäärä — Sidoantal — Number of pages |

| MSc Thesis                          | June 7, 2021      |                     | 72 pages, 3-page appendix               |

Tiivistelmä — Referat — Abstract

This thesis discusses the formal modelling and verification of certain non-real-time aspects of correctness of a mission-critical distributed software system known as the ALICE Data Point Service (ADAPOS). The domain of this distributed system is data acquisition from a particle detector control system in experimental high energy particle physics research. ADAPOS is part of the upgrade effort of A Large Ion Collider Experiment (ALICE) at the European Organisation for Nuclear Research (CERN), near Geneva in France/Switzerland, for the third run of the Large Hadron Collider (LHC). ADAPOS is based on the publicly available ALICE Data Point Processing (ADAPRO) C++14 framework and works within the free and open source GNU/Linux ecosystem.

The model checker SPIN was chosen for modelling and verifying ADAPOS. The model focuses on the general specification of ADAPOS. It includes ADAPOS processes, a load generator process, and rudimentary interpretations for the network protocols used between the processes. For experimenting with different interpretations of the underlying network protocols and also for coping with the state space explosion problem, eight variants of the model were developed and studied. Nine Linear Temporal Logic (LTL) properties were defined for all those variants.

Large numbers of states were covered during model checking even though the model turned out to have a reachable state space too large to fully exhaust. No counter-examples were found to safety properties. A significant amount of evidence hinting that ADAPOS seems to be safe, was obtained. Liveness properties and implementation-level verification among other possible research directions remain open.

### ACM Computing Classification System (CCS)

Theory of computation  $\to$  Logic  $\to$  Verification by model checking Computer systems organisation  $\to$  Architectures  $\to$  Client-server architectures

Avainsanat — Nyckelord — Keywords

distributed systems, control systems, data acquisition, formal verification, model checking, case study

Säilytyspaikka — Förvaringsställe — Where deposited

Helsinki University Library

Muita tietoja — Övriga uppgifter — Additional information

Algorithms study track

# Contents

| 1 | Intr             | oduction                                             | 1             |

|---|------------------|------------------------------------------------------|---------------|

| 2 | <b>Bac</b> l 2.1 | kground The $O^2$ Project                            | <b>3</b><br>3 |

|   | 2.2              | ALICE Data Point Service                             | 4             |

|   | 2.3              | Requirements of ADAPOS                               | 6             |

|   | 2.4              | What Makes Testing Insufficient for ADAPOS?          | 9             |

|   | 2.5              | Why Formal Methods?                                  | 11            |

|   | 2.6              | Why Model Checking in Particular?                    | 12            |

| 3 | Enu              | merative LTL Model Checking                          | <b>15</b>     |

|   | 3.1              | Finite State Machines                                | 16            |

|   | 3.2              | Linear Temporal Logic                                | 21            |

|   | 3.3              | Enumerative Model Checking                           | 23            |

|   | 3.4              | State Space Explosion                                | 25            |

| 4 | The              | Model of ADAPOS                                      | 30            |

|   | 4.1              | Processes in the Model                               | 33            |

|   | 4.2              | Differences Between the Model and the Implementation | 34            |

|   | 4.3              | The Base Variant                                     | 37            |

|   | 4.4              | Input Counters Variant                               | 43            |

|   | 4.5              | Direct Input Variant                                 | 43            |

|   | 4.6              | Direct Input Counters Variant                        | 44            |

|   | 4.7              | Structured Input Variant                             | 44            |

|   | 4.8              | Structured Input and Output Variant                  | 46            |

|   | 4.9              | Input Channels Variant                               | 47            |

|   | 4.10             | Input and Output Channels Variant                    | 48            |

|   | 4.11             | Spin to LATeX Converter                              | 48            |

| 5 | The              | Specification of ADAPOS                              | <b>50</b>     |

|   | 5.1              | Sanity                                               | 50            |

|   | 5.2              | Safety                                               | 51            |

|   | 5.3              | Disjointness                                         | 52            |

|   | 5.4              | Checksums                                            | 52            |

|   | 5.5              | Causality                                            | 52            |

|   | 5.6              | Monotonicity                                         | 53            |

|   | 5.7              | Combined Effect of the Safety Properties             | 54            |

| 6 | Resi             | ults                                                 | <b>56</b>     |

| 7            | Disc  | cussion                                 | 60 |

|--------------|-------|-----------------------------------------|----|

|              | 7.1   | Lessons Learned                         | 60 |

|              | 7.2   | Experiences with Tools and Technologies | 60 |

|              | 7.3   | Related Work                            | 61 |

|              | 7.4   | Conclusion                              | 62 |

|              | 7.5   | Future Prospects                        | 63 |

|              | 7.6   | Acknowledgements                        | 64 |

| Re           | efere | nces                                    | 64 |

| $\mathbf{A}$ | Der   | ivation for Sanity in the Default Mode  | i  |

|              |       |                                         |    |

# 1 Introduction

A particle detector known as a Large Ion Collider Experiment (ALICE)<sup>1</sup> is one of the eight experiments of the Large Hadron Collider (LHC)<sup>2</sup> at European Organisation for Nuclear Research (CERN)<sup>3</sup> near Geneva in Switzerland and France. ALICE specializes in measuring properties of quark-gluon-plasma, an extremely hot and dense form of matter, produced in so-called heavy ion collisions involving two lead ions or a lead ion and a proton, accelerated to ultra-relativistic speeds. This research is important for building an understanding of the conditions of the early universe, just moments after the Big Bang.

Apart from the exciting prospects in physics and cosmology, the LHC experiments, including ALICE, also present formidable challenges to engineers and computer scientists. In terms of number of subsystems and experts of different fields involved, the complexity of LHC experiments is comparable to spaceship construction. According to [1, Table 4.1], the expected rate of raw physics data produced by the detectors of ALICE during the third run (RUN3) of LHC that starts in 2021<sup>4</sup> is more than a terabyte per second. Compared to the situation during the second run, the amount of physics data obtained in ALICE is going to grow hundred-fold.

In order to cope with the increase in data throughput, the data delivery architecture of ALICE from detectors all the way to the LHC Grid computing cloud needs to be upgraded. *ALICE Data Point Service* [48] (ADAPOS) is a distributed system that is part of this upgrade effort. It moves a subset of the data produced by subdetectors of ALICE towards the LHC Grid computing cloud for particle track reconstruction and physics analysis. The article [48, p. 482] lists five requirements for ADAPOS:

- 1. It must not lose or corrupt data;

- 2. it must preserve the ordering of data elements;

- 3. its throughput and latency must be as predictable as possible;

- 4. it must be stable and responsive; and

- 5. its processes must have redundant instances for maximising availability and making maintenance easier.

Originally, unit and integration tests were used for finding defects in ADAPOS implementation. Testing alone is insufficient for demonstrating the correctness of a system such as ADAPOS. The great Edsger Dijkstra has famously said [10, p. 21]:

<sup>1</sup>https://home.cern/science/experiments/alice

<sup>&</sup>lt;sup>2</sup>https://home.cern/science/accelerators/large-hadron-collider

<sup>3</sup>https://home.cern/

<sup>4</sup>https://lhc-commissioning.web.cern.ch/schedule/LHC-long-term.htm

"Testing shows the presence, not the absence of bugs."

The heart of the problem is that ADAPOS is a distributed system made of concurrently executing multi-threaded processes running on separate machines connected by network. There are simply too many possible scenarios to capture into hand-written test cases. The cppunit<sup>5</sup> test framework used for developing ADAPOS does not control scheduling of threads. When threads access shared memory, there can be data races that have different outcomes depending on scheduling. Unpredictable resolution of data races may translate into flaky test cases which sometimes succeed and sometimes fail. Reproducing rare system behaviours with flaky tests can be hard.

A portion of software systems are critical in some sense. According to [31, Table 2], a system is *mission-critical* if a failure

"[m]ay lead to an inability to complete the overall system or project objectives; e.g., loss of critical infrastructure or data."

The failure of ADAPOS could ruin the analysis of physics data collected from the subdetectors, making ALICE effectively a 10,000-tonne paperweight with huge electricity consumption. Thus, ADAPOS qualifies as a mission-critical system. Furthermore, stopping expensive experiments for patching ADAPOS is not on the table. These factors justify investing more than the usual amount of effort into verification and validation of ADAPOS.

The shortcomings in testing and the importance of getting ADAPOS work right led the author of this thesis to consider formal verification. Based on the good experiences obtained with a related system [49], model checking was chosen as the method for performing the current study. Simply put, model checking [2, 17, 38, 58] is the process of building a mathematical model of the system under verification and algorithmically checking if the model satisfies a specification written in formal logic.

The goal of this study is to demonstrate the correctness of ADAPOS with respect to the properties refined from the five requirements above. There are three levels of scope which contribute to the overall correctness of ADAPOS:

- 1. The part of the underlying C++ software framework that may run persistently;

- 2. The individual component processes of ADAPOS; and

- 3. ADAPOS as a distributed system.

Level 1. has been mostly verified [49]. The focus of the current work is on levels 3. Level 2 had to be left out as future work. Chapter 2 provides more context and motivation. Chapter 3 introduces the theory behind the methods used. Chapter 4 describes the abstract model that was developed. Chapter 5 presents the specification of the model. Chapter 6 summarises the results. Finally, Chapter 7 closes this thesis with discussion.

<sup>&</sup>lt;sup>5</sup>https://sourceforge.net/projects/cppunit/

# 2 Background

As mentioned above, for verifying that ADAPOS meets its requirements, a formal verification technique known as model checking was chosen for this study. The model checker chosen for model checking the abstract specification of ADAPOS was SPIN [34]. Another model checker, DIVINE [4] was tried for model checking the C++ implementation of ADAPOS. Implementation-level modelling had to be dropped due to technical issues with DIVINE and for keeping the scope of this work suitable for a master's thesis. This chapter provides background and motivation for the research question and the method chosen for answering it.

# 2.1 The $O^2$ Project

Until the third run of LHC, data from ALICE was processed in two stages. Online processing decides which measurements need to be preserved for further analysis and which measurements can be discarded as noise or otherwise uninteresting data. Offline processing reconstructs particle tracks from the data filtered online and compares them with predictions made by theoretical models. The  $O^2$  project, whose name refers to the conjunction of offline and online, aims to combine these two currently separate stages of processing into one real-time computation pipeline.

The ALICE experiment produces data relevant to  $O^2$  in two categories: physics data and conditions data. *Physics data* includes the readings from the numerous subdetectors of ALICE, e.g., gas detectors, silicon detectors, or scintillating crystals. Physics data forms the vast majority of the data produced by volume. The ALICE *Data Acquisition* (DAQ) system is responsible for collecting physics data and delivering it to Grid.

Conditions data, on the other hand, is data on the subdetectors themselves and their supporting infrastructure. Conditions data records the ambient conditions of ALICE. For example, the output voltages of power sources or gas temperature or pressure readings in gas detectors fall into this category.

Conditions data are crucial for maintaining optimal operating conditions for detectors. For example, too high input voltage can break the very delicate and expensive silicon detectors. For many of the devices, there are no commercially available replacements. The task of the ALICE *Detector Control System* (DCS) [14, 15] is to maximise the duration of optimal working conditions for physics detectors by using conditions data and possible commands from human operators.

Some of the physics calculations involved in particle track reconstruction are sensitive to ambient conditions. Thus, conditions data has a second role in providing correcting coefficients to the physics calculations. DCS and DAQ are designed to be two independent systems separated by a firewall, so DAQ cannot directly acquire conditions data from DCS.

#### 2.2 ALICE Data Point Service

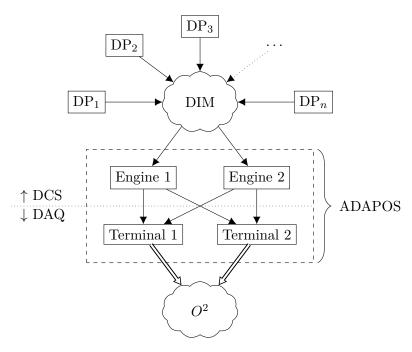

ADAPOS contributes to the  $O^2$  project. The purpose of ADAPOS is to transmit conditions data from DCS to DAQ. It succeeds an application known as Amanda which is part of the ALICE offline Shuttle [68] system. Figure 1 gives an overview of ADAPOS.

Figure 1: A simplified presentation of ADAPOS deployment.

The conditions data in ALICE DCS consists of data points. A *data point* represents the state of (a channel in) a hardware device, or some other logical or aggregated piece of information. There is separation of concerns between the DCS and the DAQ subsystems. The *service* delivering data points has been split into two types of processes accordingly: Engines operating on DCS servers and Terminals running on the DAQ side.

All data are replicated between two redundant copies of Engines and Terminals in order to increase the availability of the service. Engines and Terminals maintain indexed data structures known as *Full Buffer Images* (FBIs). An FBI represents a snapshot of the state of all data points published through ADAPOS. The number of data points is fixed; if it changes, then ADAPOS has to be reconfigured and restarted.

Data points are published to ADAPOS using the *Distributed Information Management* (DIM) [25] protocol, following a publisher-subscriber pattern with a service broker known as a DIM DNS server. DIM is developed and

maintained at CERN and is freely available<sup>6</sup>. Another protocol, called  $0 MQ^7$ , is used for transmitting data points between Engines and Terminals and also between Terminals and DAQ readout software.

In Figure 1, The bold arrow between Terminals and  $O^2$  emphasises the fact that the FBIs are sent as discrete messages of dozen or so megabytes in size. By contrast, other arrows denote continuous event-based data streams containing only changes to individual data points that arrive as they are measured. DP stands for a data point.

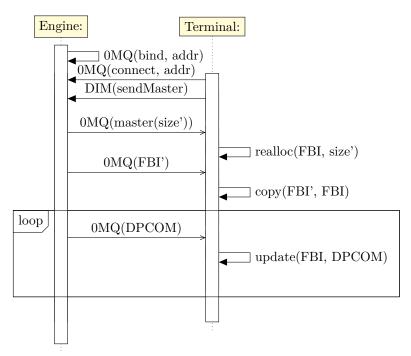

During the start-up of ADAPOS, Engine queries the DIM DNS server which returns the addresses of the servers publishing the data points. After that, Engine establishes a direct connection with the relevant servers. Figure 2 presents the interaction between an Engine and a Terminal after Engine has started.

**Figure 2:** A UML sequence diagram showing the key events in the communication between a Terminal and an Engine.

After the start-up phase, whenever the state of a data point changes, the new value is transmitted to Engine. Engine then sends a fixed-size binary record known as a *Data Point Composite Object* (DPCOM) to Terminal over a 0MQ socket.<sup>8</sup> A DPCOM contains the value of a single data point along

<sup>6</sup>http://dim.web.cern.ch/

<sup>&</sup>lt;sup>7</sup>https://zeromq.org/

<sup>&</sup>lt;sup>8</sup>See Chapter 4 of the ADAPRO manual for the classes used in ADAPOS at https://gitlab.com/jllang/adapro/-/jobs/artifacts/5.0.0/download?job=manual

with the name of the device or channel it represents and other metadata such as the type of the data point, a timestamp, and bit flags.

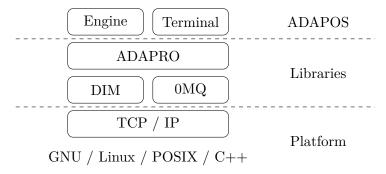

ADAPOS applications have been implemented on top of the open source C++ software framework, the ALICE Data Point Processing Framework (ADAPRO)<sup>9</sup>. Inspired partly by the SMI++ [23]<sup>10</sup> framework used in control systems at CERN, ADAPRO follows a state machine model which has been formally verified for certain safety and liveness properties [49]. The C++ implementation of the state machine mechanism was also partially verified in the same study. Figure 3 presents the technological ecosystem supporting ADAPOS.

Figure 3: The technological ecosystem which ADAPOS inhabits.

#### 2.3 Requirements of ADAPOS

This chapter discusses the specification of ADAPOS using the English language. The specification will be formalised in Chapter 5. The properties investigated in this thesis were developed from earlier requirements [48, p. 482] and discussed above in Chapter 1. Unfortunately, due to known theorems [21, 27] it is impossible to complete all of these goal to be listed below perfectly in the same system. ADAPOS aims to find a sensible compromise. The main properties investigated in this thesis are listed below.

- 1. Atomicity: ADAPOS must never produce output containing partial or incomplete data points.

- 2. Disjointness: ADAPOS must never mix updates to separate data points. Specifically, all data points must be stored in non-overlapping locations.

<sup>9</sup>https://gitlab.com/jllang/adapro

<sup>10</sup>https://smi.web.cern.ch/

<sup>&</sup>lt;sup>11</sup>See also the manual of ADAPOS Engine at https://gitlab.com/jllang/adapos-engine/-/jobs/713674023/artifacts/download

- 3. Causality: ADAPOS must never produce output values that it did not receive as input.

- 4. *Monotonicity*: ADAPOS must never change the order of updates to data points.

- 5. Availability: There should always be an Engine-Terminal pair available that is able to deliver up-to-date data points.

A software system may have *safety* [2, p. 109] and *liveness* [2, p. 119] properties. According to Leslie Lamport, safety properties state that "something will not happen" [44, p. 125] while liveness properties state that "something must happen" [44, p. 125]. Safety and liveness properties can also be distinguished by how they are refuted.

Safety properties are those properties that have counter-examples of finite length. Type safety (e.g., that variables declared having type int can never have string type values) and absence of division by zero, illegal memory accesses, or deadlocks are examples of safety properties. A stack trace that is printed when a Java program halts abnormally due to an unhandled NullPointerException, is a counter-example to the safety property asserting that the program never dereferences the null reference.

Liveness properties have counter-examples that are infinitely long. Depending on the property, a counter-example may never satisfy it or satisfy it at most finitely many times. Halting is a commonly needed liveness property. A counter-example to halting is an infinite, i.e. never-ending execution. Not all programs are meant to halt, though. In fact, ADAPOS processes should only halt in case of a scheduled maintenance. Livelocks are also typical liveness violations.

Properties 1-4 are safety properties. A natural desirable safety property would be that ADAPOS must never alter the data it transmits. This is related to the concept of data independence introduced by Pierre Wolper [67]. Considering the modelling and verification effort involved, and the use case at CERN, properties 1-4 together give reasonable guarantees for ADAPOS.

ADAPOS can be used for transmitting arbitrary binary data without type information. It would be hard to define and verify safety properties stronger than properties 1-4 in the general case. Furthermore, these four properties allow dropping or duplicating data points, which gives the implementation some slack when the network is highly congested or some data points are updated infrequently.

In addition to the safety properties, it is important to ensure the *availability* of ADAPOS, which is a liveness property. Availability means that at any given moment of time, there is at least one Engine-Terminal pair able to deliver conditions data to  $O^2$ . As mentioned earlier, maximising availability is the reason why ADAPOS has redundant copies of the Engine and Terminal processes.

There are interesting properties that had to be excluded from this study. Updates to certain data points may arrive scarcely. It is all the more important that they get through. The property that all updates eventually arrive at  $O^2$  would be reliability.

Ensuring reliability would require storing updates in a buffer that could theoretically grow without a bound. If ADAPOS processes ran out of their finite amount of memory, they would cease operation, violating availability. An unbounded memory requirement would also preclude certain formal verification methods, including model checking. Furthermore, arbitrarily long buffers would also introduce unbounded latency. Trade-offs between conflicting requirements are inevitable.

ADAPOS processes use a bounded amount of memory to avoid running out of resources or introducing unnecessary latency. In the previous study [48, p. 484], no evidence of packet loss was found. Considering the effort invested in simulating ADAPOS under maximum load, and the fact that no event losses have ever been observed, it can be argued that packet loss is unlikely to occur under foreseeable operating conditions. As mentioned in the previous study [48, p. 485],

"[t]he maximum level of performance with the test setup [of ADAPOS] was found to be around 400 kHz, which is two orders of magnitude better than the current requirements."

400 kHz means 400,000 data points per second.

Still, with the current design of ADAPOS, dropping updates under force majeure conditions cannot be ruled out theoretically. It is generally impossible to guarantee availability and atomic consistency (a strong form of reliability) in the same distributed system [27, p. 53]. ADAPOS prefers availability over reliability.

An important property is that if ADAPOS drops updates, it must do it without introducing biases to the conditions data. This property, *neutrality* means that no particular set of data points can be favoured over others by the architecture of ADAPOS. Neutrality would be very expensive to verify using model checking, because neutrality requires strong fairness assumptions for every data point separately.

A liveness property that was considered and even formalised, was called *synchrony*. This property asserts that every once in a while, all Terminal processes must have the same data points in their FBIs. However, this property was considered too demanding to be guaranteed in all possible situations, so it was dropped.

Another notion of synchrony, or *consensus* more precisely, is about deciding which Engine-Terminal pair serves as the active route for transmitting the conditions data and making sure that all processes involved agree on the decision. For a distributed system featuring replicated processes, it is

important to be able establish a consensus on the roles of each process. There are distributed consensus algorithms such as Paxos [46] and Raft [53].

An arrangement to use the distributed file system ETCD<sup>12</sup> to keep track on the active Engine-Terminal pair was considered. In principle, all of conditions data could be handled in a message passing system such as Apache Kafka<sup>13</sup>, which would also take care of consensus problems. Such a huge design change would be too late at this point considering the schedule of RUN3. The evidence on the more than satisfactory performance [48] of ADAPOS also argues against such a redesign, as all the hard work on testing and measuring (in addition to designing and implementing) the system would need to be redone.

It was decided to keep all Engines and Terminals always active and agnostic about processes outside ADAPOS accessing conditions data. In a way, this design decision moved the consensus problem to  $O^2$ . Now the recipient of the data streams has to decide which Terminal to connect to and there are no guarantees that all Terminals have the same data.

The last property to mention is that conditions data should be up-to-date in the sense that ADAPOS adds a bounded amount of latency to data point updates passing through it. This is related to the requirement 3 listed in Chapter 1. This requirement has been taken into account in the C++ implementation. Real-time properties such as bounded latency are out of the scope of this thesis, however. The model checker UPPAAL<sup>14</sup>, has been used for verifying real-time systems, e.g., in nuclear power domain [43].

Preliminary latency measurements were made during the early simulations [48], but they were considered to be too early for publication at that point, as details of the design and deployment of ADAPOS would change. Latency was not considered to be a critical concern of the design of ADAPOS. Much of the conditions data arriving at ADAPOS Engine is already relatively old and ADAPOS usually adds only milliseconds or so to the overall latency. For example, some power supply devices read out their channel voltages twice per minute. Furthermore, ALICE DCS applies smoothing to the conditions data [15, Section III]. The distance between devices and ADAPOS Engine (or Terminal) in terms of the number of different machines involved in transport and processing is quite long.

## 2.4 What Makes Testing Insufficient for ADAPOS?

The usual approach to verifying the correctness of a piece of software is to write tests to see how the system reacts to a handful of possible inputs. In this paradigm, it is typically the interactions between the software system and its environment or tests, as well as the feedback from the clients or

<sup>12</sup>https://etcd.io/

<sup>13</sup>https://kafka.apache.org/

$<sup>^{14}</sup>$ https://www.it.uu.se/research/group/darts/uppaal/examples.shtml

end-users, that define what correctness means. ADAPRO and ADAPOS originally relied on tests and hundreds of hours of simulations [48]. This work was certainly valuable but it did not remove all reasonable doubts on the correctness of the specification and design of ADAPOS.

The main difficulty in testing ADAPRO and ADAPOS were the complex concurrent behaviours arising from interactions between threads or processes. Concurrency-related defects were hard to anticipate in the informal design process and to reproduce with tests. Chapters 5 and 6 of the article [49] discuss four defects that were found in the formal verification of ADAPRO. Model checkers were able to quickly uncover these issues whereas hundreds of hours of testing and simulation had failed to do so.

Generally speaking, there are too many behaviours to test individually for achieving complete or even relatively high coverage. Exhaustive testing of a concurrent system takes double exponential amount of work with respect to the number of parallel processes, as noted by Petr Ročkai in his dissertation [59, Footnote 1 on p. 10]. Exhaustive testing is thus challenging.

One consideration in choosing verification methods is the level of risks involved in the project. Wikipedia lists cautionary tales on what may happen if verification is not done carefully enough<sup>15</sup>. The sheer number of software defects with catastrophic consequences in the past provides motivation for investing effort into preventing future incidents.

The failure of ADAPOS would mean that either  $O^2$  gets no conditions data at all, or the data is stale or incorrect. This in turn would hinder the particle track reconstruction process. If the physics data cannot be analysed accurately, then there is no point in running an expensive physics experiment. Even though it is a small system, ADAPOS is a link in a chain of critical software components of the ALICE experiment. The ADAPOS project aims not to be the weakest link in that chain.

From a business point of view, as conjectured by Gerard Holzmann [35, p. 81], the problems most likely to be exposed by testing may not be those that pose the greatest risk. One study goes even further to note that testing can even miss "simple, obvious faults than one may expect" [41, p. 217]. ADAPOS qualifies as a mission-critical system with economically high stakes. This motivates the search for high-risk defects in addition to the easily testable ones.

If testing cannot be carried out exhaustively, then the question is how to direct the testing effort in a way that maximises the chance of finding bugs. Methods such as Whitebox fuzzing [29], directed automated random testing [28], symbolic execution [11], and concolic testing [63] aim to increase test coverage by automatically generating inputs to tests. Regardless, earlier positive experiences with model checking [49] made the author of this thesis choose model checking over these advanced forms of testing.

<sup>&</sup>lt;sup>15</sup>https://en.wikipedia.org/wiki/List\_of\_software\_bugs

#### 2.5 Why Formal Methods?

Formal methods focus on demonstrating (or finding counter-evidence against) the correctness of a piece of software by employing mathematical techniques. The range of techniques under the umbrella of formal methods is quite extensive. It is thus hard to give a precise definition for the term. Christel Baier and Joost-Pieter Katoen characterise formal methods as "the applied mathematics for modeling and analyzing [Information and Communication Technology] systems" [2, p. 7].

Testing, static analysis, model checking, and theorem proving form a continuous spectrum of methods, each one choosing different trade-offs between exhaustiveness, precision, speed of execution and ease of use. At least a part or an aspect of the system under verification must be unambiguously defined in mathematical terms in order to apply formal methods. That formal definition can sometimes be generated or extracted programmatically. The formal specification of ADAPOS was written by hand, because it was easier to do that way.

There are numerous case studies and success stories on using formal methods in software development [22]. A seminar report<sup>16</sup> written by the author of this thesis lists a few reported uses of model checking for verifying real life systems and elaborates three of them in detail. In addition to the ADAPRO case [49], some interesting examples from the past decade or so include the Address Resolution Protocol [9], slats and flaps control unit of an aircraft [13], attitude and orbit control system of a satellite [24], the control system of another LHC experiment, the Compact Muon Solenoid control system [37], a stepwise shutdown system and uninterruptible power supply control software in nuclear power domain [43], a compiler for a subset of the C programming language [47], an operating system microkernel [41], just to name a few.

The first chapter in the book by Baier and Katoen [2] mentions some real-life examples of software defects exposed with model checking. The website of the Spin<sup>17</sup> model checker lists important use cases of the tool. There is another list of Spin case studies online. Other model checking and formal verification tools often list case studies and other research articles on their own websites. <sup>19</sup>

Apart from technical arguments, economical considerations often support formal methods, too. Gerard Holzmann [35] and John Fitzgerald et al. [22] provide business-oriented argumentation on why formal methods are worth using. Jonathan Bowen and Michael Hinchey discuss some com-

$<sup>^{16}</sup> https://www.cs.helsinki.fi/u/jllang/Three_Examples_on_the_Real_Life_Applications_of_Model_Checking.pdf$

<sup>17</sup>https://spinroot.com/spin/success.html

<sup>18</sup>http://www.imm.dtu.dk/~albl/promela.html

$<sup>^{19}\</sup>mathrm{E.g.}, \, \mathrm{https://ti.arc.nasa.gov/tech/rse/publications/vnv/\#model}$

mon preconceptions and provide general guidelines on the use of formal methods [8].

The rise of specialised companies relying on formal methods, such as Coverity [7] (which was acquired by Synopsys in 2014), Galois [55] and IOHK [40], hint that there might be a rising trend on the adoption of formal methods in the software industry. Large established companies such as Amazon [51], Microsoft [3], and former Lucent [12] (which was later acquired by Nokia) are also known for using formal methods to their profit. In the computer hardware industry, AMD [60], Centaur [30] and Intel [39] for example, have successfully deployed formal verification in their processes.

The case studies and companies mentioned above are just select few examples. More thorough overview on different flavours of formal verification and their industrial adoption is worthy of a survey article or a thesis in its own right. At any rate, the there is a growing corpus of literature demonstrating that formal methods are not merely an academic exercise that can be easily dismissed. There are industrial segments relying on formal methods.

### 2.6 Why Model Checking in Particular?

ADAPOS is a distributed system made of reactive components. Apart from possible bugfixes and design changes necessitated by the findings made during the verification, ADAPOS is more or less complete, for the time being. Since the source code already exists, a correct-by-construction approach (e.g., by constructing the system using a framework like Verdi [66] or directly with an interactive proof assistant [57] like how the CompCert C compiler [47] was made) is no longer attractive. Neither is a refinement approach such as the one taken in the seL4 case [41].

According to Edmund Clarke et al. [17, p. 4], model checking in general has three advantages:

- Ideally, model checking can be fully automated without need for verification experts in software development teams.

- Model checking can be applied at different stages and abstraction levels

of software development processes, from abstract designs to concrete

program code.

- Model checking is particularly suitable for analysing concurrent systems.

Baier and Katoen [2, p. 14-16] list eight other strong points of model checking:

- It is suitable to many applications such as embedded systems, software engineering, and hardware design.

- It supports partial verification; individual properties can be checked without having to supply a complete specification at once.

- It is not sensitive to the probability of an error occurring; this contrasts

model checking with testing and simulation which usually find only

the most easily exposed errors.

- It provides diagnostic information in case a property violation is detected which is useful for debugging.

- It is a potential "push-button" technology requiring neither a high degree of user interaction or high level of expertise.

- It enjoys an increasing interest by industry; many hardware manufacturers run their own verification labs and offer model checking-related jobs, there are also commercial model checkers available these days.

- It integrates well with current development processes; it does not have a steep learning curve, and empirical studies indicate that it may shorten the development times.

- It has a sound mathematical foundation based on the theory of graph algorithms, data structures, and logic.

All of the pros of model checking mentioned above are relevant for the work discussed in this thesis. That said, experience with the models studied in this thesis and in the previous article [49] have taught that especially the promises of a "push-button" technique can be a bit on the optimistic side. It can take weeks or months of work to have the model in a state where this metaphorical button can be finally pressed. Baier and Katoen [2, pp. 115–116] also list eight weaknesses of model checking:

- It is mainly suited to control-intensive applications; it is weaker on data-intensive applications that may have even infinite data domains.

- It depends on decision procedures; there are infinite-state systems and data types that require semi-decidable or even undecidable logics.

- It verifies a model of a system, and not the system itself; the results obtained are only as good as the model, so complementary techniques such as testing might still be needed.

- It checks only the properties suggested by the user; the validity of properties not checked remains open.

- It suffers from the state explosion problem (which will be discussed in Chapter 3.4); even the most advanced state space reduction techniques may not be able to make a model fit into a computer's memory.

- It requires a certain amount of expertise for finding the best abstractions for representing the system with a small model and stating the specification using mathematical logic.

- It may not deliver correct results if the model checker has a software defect, though parts of advanced model checking algorithms have been formally demonstrated to be correct using theorem provers.

- It does not work for generalisations: systems with an arbitrary number of components, i.e. parametrised systems, cannot be model checked; however, model checking may help to find hypotheses to be proved in a parametrised setting.

Based on personal experience, the author of this thesis would like to add to the list of shortcomings above that interpreting the counter-examples given by a model checker is not always easy. Clarke et al. [17, pp. 4-5] characterise three of the complementary methods with their pros and cons:

- Testing: There is a wide range of technologies for testing software, such as the familiar unit testing with hand-written inputs. Testing is generally the fastest and easiest software verification method to deploy. Due to its dynamic nature, testing can detect a wide range of errors, many of which are hard to find with purely static techniques. However, the weakness of testing is typically low coverage of state spaces, making it more suitable for debugging than verification. Advanced testing techniques, some of which were mentioned above at the end of Chapter 2.4, try to alleviate this shortcoming.

- Abstract interpretation: Though somewhat similar to model checking in some respects, abstract interpretation usually focuses more on speed while sacrificing some of its accuracy in exchange.<sup>20</sup>

- Theorem proving [57]: The disadvantage of this method is that it can be very time-consuming to the software developers, even more than model checking.

The above three families of methods are quite large and varied. Abstract interpretation itself is a general technique that can be used in many different settings, including model checking and theorem proving. All in all, based on the empirical observations and the more general reasoning above, it was decided that model checking would be a good method for carrying out the research in this thesis.

$<sup>^{20}\</sup>mathrm{Clarke}$  et al. might be referring to the use of abstract interpretation in  $static\ analysis$  [52, Ch. 4].

# 3 Enumerative LTL Model Checking

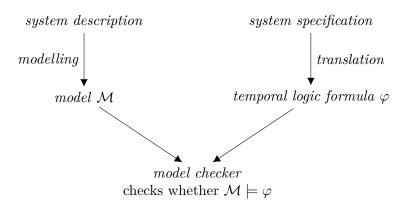

Model checking [2, 16, 38, 59] is based on the idea of representing the system under verification as a mathematical model and its properties as logical formulae. The problem of deciding whether or not a system meets its specification becomes the problem of deciding if its model satisfies the formulae. A model checker implements a decision procedure for this satisfaction problem. Figure 4 presents the general idea of model checking schematically.

Figure 4: Outline of model checking. Adapted from [17, p. 3].

There are multiple approaches to model checking. As Clarke et al. [17, p. 5] put it,

"... model checking is characterised less by purity of method than by the goal of debugging and analyzing dynamical systems that exist in the real world and can be modeled as state-transition systems."

Enumerative model checking [36] [38, Ch. 2] represents the model along with its properties explicitly as a finite state transition system. The satisfaction problem is solved by computing all the reachable states of the system and checking if they satisfy the property under investigation thus performing a proof by exhaustion. The model checkers DIVINE and Spin used for the research work discussed in this thesis are enumerative.

Instead of relying on brute strength, industrial grade enumerative model checkers use optimisation techniques to reduce the search space. These techniques include partial order reduction [54] and bitstate hashing [33] used in Spin, as well as  $\tau$ -reduction [5] used in DIVINE. Optimisation techniques for model checking are outside the scope of this thesis, however, and will not be discussed further.

Even though model checkers are automated tools, understanding their internal mechanisms and general theory helps building models that can be optimised well by the model checkers. There are many formalisms for representing finite-state systems such as (labelled) transition systems [2, p. 20] [54, p. 174], program graphs [2, p. 32] Kripke structures [17, p. 6] [42, p. 141], simple programs [38, Ch. 1.1], and various types of automata [26, p. 6] [36, p. 156] [42, p. 108] [61, Ch. 1]. These formalisms are all similar in spirit and differ only in specifics. There are likewise many different systems of formal logic used for specifying properties.

#### 3.1 Finite State Machines

A Finite State Machine (FSM) [36, p. 156], also known as Finite (State) Automaton [42, p. 108] [61, pp. 51, 53],  $(\Sigma, S, \iota, \delta, F)$  has

- a finite non-empty set  $\Sigma$  of symbols known as the *alphabet* (or label set or set of actions),

- a finite non-empty set S of states,

- an initial state  $\iota \in S$  [36, p. 156] (which could equivalently defined to be a set of initial states [42, p. 108]),

- transition relation  $\delta \subseteq S \times \Sigma \times S$ , and

- a set  $F \subseteq S$  of final (or accepting) states.

Following the convention of [2, p. 20], this text uses  $s \xrightarrow{\alpha} s'$  to denote the proposition  $(s, \alpha, s') \in \delta$ .

A program or a model written in textual programming or modelling language source code can be converted into an FSM. The following naïve conversion was inspired by the operational semantics of NanoPromela [2, Ch. 2.2.5] and the transition system semantics of channel systems [2, Ch. 2.2.4] but simplified (omitting channels and guards) and adapted for FSMs. More rigorous semantics for modelling languages such as PROMELA [50] can be quite complex.

- The alphabet will be the set of all statements in the code.

- The states will be tuples  $(\ell, \mathbf{v})$  containing the location  $\ell$  of the current statement of code and the values  $\mathbf{v} = v_0, v_1, \ldots, v_n$  of all the respective variables  $x_0, x_1, \ldots, x_n$  occurring in the code. A special location halt can be used to mark those states for which there are no more statements left to execute.

- The initial state will point to the first statement and have suitable values (e.g., zeros) in all variables.

- There will be a transition  $(\ell, \mathbf{v}) \xrightarrow{\alpha} (\ell', \mathbf{v}')$  if and only if

- 1.  $\ell$  is the location of the statement  $\alpha$ ;

- 2.  $\ell'$  is the location arrived after executing  $\alpha$  (usually the next line, but in case of control structures and goto statements it can be a different location); and

- 3. executing  $\alpha$  changes the values  $\mathbf{v}$  into the values  $\mathbf{v}'$ .

- All states can be made accepting. The reason for this choice will become clear later.

The conversion above tacitly assumes that the language of the code has well-defined operational semantics. Typically, this state-machine approach works best for imperative programs. For purely functional programs, other verification methods such as using the type system of the programming language to enforce safety invariants in a propositions-as-types [65] style and using equational reasoning might be better options.

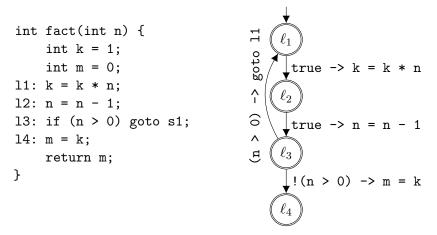

Consider the lines labelled as  $\ell_1$  to  $\ell_4$  in the C language subroutine fact shown in figure 5. The code uses a goto statement to create repetition instead of a loop in order to make it easier to establish the connection between fact and its flowchart-style FSM representation. In C,  $\mathbf{v} = \mathbf{e}$  means that the value of expression  $\mathbf{e}$  will be stored in the memory location named by variable  $\mathbf{v}$ . Such assignments are often denoted as  $v \leftarrow e$  or v := e in pseudocode. This must not be confused with a (Boolean-valued) assertion of equality, denoted as  $\mathbf{x} == \mathbf{y}$  in C or x = y in mathematics. The notation  $b \rightarrow \alpha$  on the FSM means that when (if ever) the Boolean-valued guard b is true, then the FSM can execute the statement  $\alpha$  in order to perform a state transition.

**Figure 5:** A subroutine in C (on the left) and an FSM (on the right) representing the control logic of the body of that subroutine after the initialization of the variables n, k, and m.

The interpretation of fact here as an FSM is intuitive rather than formal. It is somewhat imprecise. Firstly, the complications involved in calling and returning from subroutines are ignored. That is justified in this case, because

this is not an interprocedural analysis [52, Ch. 2.5]. Instead, the FSM represents the logic that takes place inside the subroutine body. Secondly, the FSM only considers the locations of the statements of fact and not the values of the variables n, k, and m.

If the variables n, k, and m are taken into account, then the conversion outlined above yields an FSM with 3n + 1 successive states without loops. Figure 6 demonstrates this when n = 3 initially. The reason for why all states are chained one after the other is that fact is deterministic: At any given state, executing a single statement can only result in a single successor state. Because a state also includes the current location, there can be at most one statement to execute.

**Figure 6:** A more accurate FSM representation of fact that models states as quadruples  $(\ell, n, k, m)$ .

Each choice of n leads into a different FSM, so fact describes an infinite family of systems. Model checking that all finite-state models of an infinite family fulfil a property is equivalent to solving the halting problem for an infinite-state system, cf. a Turing machine. The halting problem of Turing machines is undecidable. However, there are also infinite-state systems such as well-structured transition systems [20] that allow decidable state space enumerations. For model checking properties of ADAPOS, the models have been made finite-state by fixing free parameters during compilation.

An execution (of an FSM) is an alternating sequence

$$s_0\alpha_1s_1\alpha_2s_2\alpha_3\dots$$

of states  $s_i \in S$  and actions  $\alpha_i \in \Sigma$  such that  $s_i \xrightarrow{\alpha_{i+1}} s_{i+1}$  for every  $i \in \mathbb{N}$ . A finite execution is a sequence

$$s_0\alpha_1s_1\alpha_2s_2\alpha_3\ldots\alpha_ns_n$$

that is an initial segment of an execution.

An FSM accepts a finite path  $\alpha_1\alpha_2...\alpha_n$  (called *string* in this context) if and only if there is a finite execution  $s_0\alpha_1s_1\alpha_2...\alpha_ns_n$  such that  $s_0 = \iota$ , the initial state, and  $s_n \in F$ . A Büchi automaton is similar to an FSM, except it accepts an infinite string  $\alpha_1\alpha_2...$  if and only if there is an (infinite) execution  $s_0\alpha_1s_1\alpha_2...$  starting from  $s_0 = \iota$  that contains infinitely many occurrences of one or more states in F.

The handshake product [2, p. 48]  $\mathcal{M}_1 || \mathcal{M}_2$  of FSMs  $\mathcal{M}_1$  and  $\mathcal{M}_2$ , with  $\mathcal{M}_i = (\Sigma_i, S_i, \iota_i, \delta_i, F_i)$  for  $i \in \{1, 2\}$ , is an FSM  $(\Sigma, S, s_0, \delta, F)$  such that

- $\Sigma = \Sigma_1 \cup \Sigma_2$ ;

- $S = S_1 \times S_2$ ;

- $\iota = (\iota_1, \iota_2);$

- $\delta$  is defined with three rules:

$$\frac{\alpha_1 \not\in H, (s_1, \alpha_1, s_1') \in \delta_1}{((s_1, s_2), \alpha_1, (s_1', s_2)) \in \delta}(I_1) \qquad \frac{\alpha_2 \not\in H, (s_2, \alpha_2, s_2') \in \delta_2}{((s_1, s_2), \alpha_2, (s_1, s_2')) \in \delta}(I_2)$$

$$\frac{\alpha \in H, (s_1, \alpha, s_1') \in \delta_1, \text{ and } (s_2, \alpha, s_2') \in \delta_2}{((s_1, s_2), \alpha, (s_1', s_2')) \in \delta} (HS)$$

where  $H \subseteq \Sigma_1 \cap \Sigma_2$  is the set of handshake actions; and finally

•

$$F = F_1 \times F_2$$

.

The rules  $I_1$  and  $I_2$  express interleaving while the rule HS expresses handshaking. For a non-handshake action, one of the two component FSMs performs a transition while the other component FSM does nothing. If both component FSMs can perform a transition, then the handshake product automaton chooses non-deterministically one of them to perform a transition while the other one does nothing. When the two component FSMs can perform a transition with the same handshake action, then they perform that transition simultaneously. The difference between interleaving and handshaking is analogous to the difference between time sharing and parallel execution.

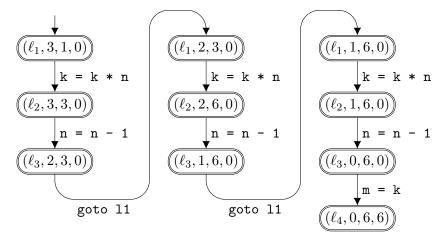

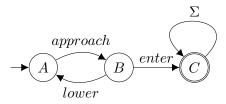

A railroad crossing system [2, pp. 50 - 52] is an example of a handshake product of three transition systems:

- 1. A *train*, which is initially far away from the crossing. It is safe to cross the railroad until the train gets near the crossing.

- 2. A gate, which needs to be lowered before the train reaches the crossing in order to prevent accidents. The gate can be opened again after the train has left the crossing.

3. A *controller* that receives information about trains that are about to enter the crossing. The controller must send the signal to raise or lower the gate when appropriate.

A natural correctness property for the railroad crossing system is that whenever the train is in the crossing, the gate must be down.

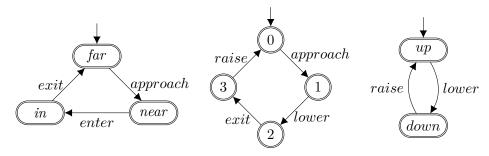

Figure 7 represents the three component systems as FSMs. Figure 8 shows the handshake product of the train, the gate, and the controller with handshake actions *approach*, *exit*, *lower*, and *raise*. The system a design flaw: The train might enter the crossing while the gate is still up. This unwanted behaviour will be exposed momentarily using an enumerative model checking algorithm.

Figure 7: The components FSMs of the railroad crossing system. The components are, from left to right: Train, controller, and gate.

Figure 8: The handshake product of the railroad crossing system. Dashed arrows denote transitions by interleaving (the Int rule) while other arrows denote handshake transitions (by the HS rule).

The Synchronous product [61, p. 61] [36, p. 159] [2, pp. 73 – 75]  $\mathcal{M}_1 \times \mathcal{M}_2$  of FSMs  $\mathcal{M}_1$  and  $\mathcal{M}_2$  is a special case of  $\mathcal{M}_1 || \mathcal{M}_2$  where  $\mathcal{M}_1$  and  $\mathcal{M}_2$  share the same alphabet  $\Sigma$  and every transition uses the rule HS with  $H = \Sigma$ . Simply put,  $\mathcal{M}_1 \times \mathcal{M}_2$  can only perform a transition when both  $\mathcal{M}_1$  and  $\mathcal{M}_2$  can. The FSMs  $\mathcal{M}_1$  and  $\mathcal{M}_2$  in  $\mathcal{M}_1 \times \mathcal{M}_2$  perform their transitions simultaneously, or in lock-step.

### 3.2 Linear Temporal Logic

Linear Temporal Logic (LTL) is a formal language used for specifying properties. Though known longer among logicians, LTL was introduced into computer science by Amir Pnueli in 1977 [56]. LTL expresses ordering of events [2, p. 226] (e.g., "the sun rises before it sets"), rather than real-time assertions (e.g., "the monitor shuts down after five minutes of inactivity") or claims about calendar events (e.g., "31 December is the New Year's Eve"). The syntax of LTL formulae over a set A of atomic propositions [2, p. 227] in BNF is:

```

\langle formula \rangle \quad ::= \quad \text{`true'} \\ | \quad \langle atomic \ proposition \rangle \\ | \quad \text{`('} \ \langle formula \rangle \ \text{`,'} \ \langle formula \rangle \ \text{`)'} \\ | \quad \text{`¬'} \ \langle formula \rangle \\ | \quad \text{`('} \ \langle formula \rangle \ \text{`U'} \ \langle formula \rangle \ \text{`)'} \\ | \quad \text{`('} \ \langle formula \rangle \ \text{`U'} \ \langle formula \rangle \ \text{`)'}

```

In model checking, atomic propositions often establish constraints over values of variables (e.g., x < 10) or locations of processes (e.g., "process A is at critical section"). This means that atomic propositions express properties of states. The constant true stands for a proposition that holds for every state.

The meta-variables  $\varphi$  and  $\psi$  will henceforth refer to arbitrary LTL formulae. Intuitively,  $\bigcirc \varphi$  asserts that  $\varphi$  will hold after a single abstract discrete moment of time. (More precisely,  $\bigcirc \varphi$  asserts that  $\varphi$  holds for the next state in every possible execution that continues from the current state.) The formulae  $\bigcirc \varphi$  and  $\neg \bigcirc \neg \varphi$  are equivalent. A formula of the form  $\varphi$  U  $\psi$  asserts that eventually  $\psi$  must hold and that  $\varphi$  holds perpetually until  $\psi$  becomes true.

Just like in classical propositional logic, the connectives false,  $\vee$ ,  $\rightarrow$ ,  $\leftrightarrow$  can be derived from  $\wedge$  and  $\neg$ . There are other commonly used LTL operators, such as  $\square$ ,  $\diamondsuit$ , W, and R among others that can be derived from U using propositional logic. The derivations are given below:

Intuitively,  $\Box \varphi$  asserts that  $\varphi$  holds always while  $\Diamond \varphi$  asserts that  $\varphi$  eventually holds at least once. The combinations  $\Box \Diamond \varphi$  and  $\Diamond \Box \varphi$  assert that  $\varphi$  holds infinitely often and  $\varphi$  holds eventually forever, respectively.

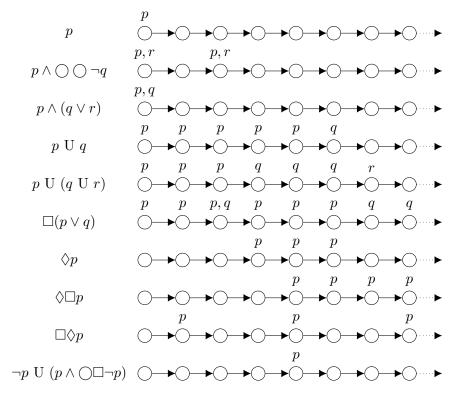

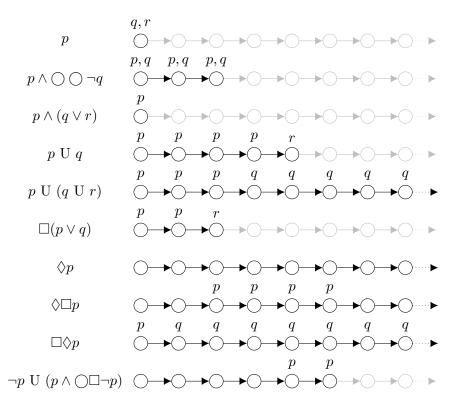

Figure 9 presents ten examples of LTL formulae along with one of their infinitely many satisfying executions in an unspecified model with respect to arbitrary atomic propositions p, q, and r. Figure 10 presents counterexamples to the same formulae.

Figure 9: Intuitive semantics of some LTL formulae.

A Kripke structure [17, p. 6] (S, R, L) over a set A of atomic propositions has a set of states S, a relation  $R \subseteq S \times S$ , and a labelling function  $L : S \to 2^A$  that assigns each state a set of propositions that the state satisfies. Kripke structures are similar to automata, except that instead of having labels on transitions (i.e. actions), they have labels on states. A path on a Kripke structure is a sequence  $s_0s_1s_2...$  such that  $(s_i, s_{i+1}) \in R$  for every  $i \in \mathbb{N}$ .

The relation  $\pi \models \varphi$  (" $\pi$  satisfies  $\varphi$ ") between (an infinite) path  $\pi$  in a Kripke structure and an LTL formula  $\varphi$  is defined inductively [2, p. 231] [17, p. 8] [42, p. 141]). Denote the path  $\pi$  with the first i states removed as  $\pi^i$ . Let  $\pi = s_0 s_1 s_2 ...$  and define

```

\begin{array}{lll} \pi \models \mathtt{true}; \\ \pi \models p & \mathrm{iff} & p \in L(s_0); \\ \pi \models \varphi \wedge \psi & \mathrm{iff} & \pi \models \varphi \text{ and } \pi \models \psi; \\ \pi \models \neg \varphi & \mathrm{iff} & \pi \not\models \varphi; \\ \pi \models \bigcirc \varphi & \mathrm{iff} & \pi^1 \models \varphi; \mathrm{and} \\ \pi \models \varphi \cup \psi & \mathrm{iff} & \pi^j \models \psi \text{ for some } j \geq 0 \text{ and } \pi^i \models \varphi, \forall i, 0 \leq i < j. \end{array}

```

Now enumerative model checking can be defined rigorously.

**Figure 10:** LTL formulae and their corresponding counter-examples. For safety properties, violations can be demonstrated in finitely many steps. The executions drawn in gray continue after the states where property violations have been established.

## 3.3 Enumerative Model Checking

An LTL formula can be converted into a Büchi automaton algorithmically [26] [42, Ch. 4.6.1]. Gerard Holzmann lists four steps for formalising the model checking problem [36, p. 159]:

1. Convert the negation  $\neg \varphi$  of the LTL property  $\varphi$  into the Büchi automaton  $\mathcal{B}_{\neg \varphi}$ .

- 2. Compute the handshake product  $\mathcal{A} = \mathcal{A}_1 || \mathcal{A}_2 || \dots || \mathcal{A}_n^{21}$  of the automata  $\mathcal{A}_i$  representing the concurrent processes in the model.  $F_i = S_i$  for each component automaton  $\mathcal{A}_i$ .

- 3. Compute the synchronous product  $C = A \times \mathcal{B}_{\neg \varphi}$ . Note that A is an FSM and  $\mathcal{B}_{\neg \varphi}$  is a Büchi automaton, but in this case the product can be computed as a synchronous product of FSMs. The resulting automaton will be a Büchi automaton.

- 4. See if  $\mathcal{C}$  has accepting executions.

Because all states in  $\mathcal{A}$  are accepting, it is  $\mathcal{B}_{\neg\varphi}$  alone that determines whether or not a given execution qualifies as a counter-example. There are depth-first and breadth-first algorithms for enumerative model checking [36].

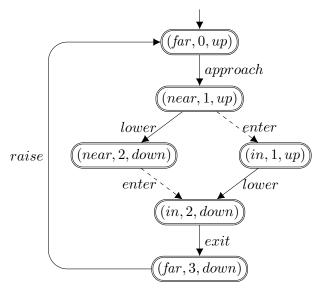

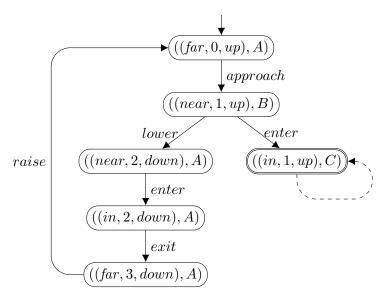

Consider the railroad crossing system again. A natural safety requirement for the system is that the gate must be always down when the train is approaching, i.e.  $\square$  ("train is in"  $\rightarrow$  "gate is down"). Figure 11 represents a Büchi automaton that accepts those executions where the train enters the crossing while the gate is still open. Figure 12 shows the synchronous product of the railway crossing system and this Büchi automaton. It has a reachable strongly connected component [42, p. 110] starting from the state ((in, 1, up), C) with accepting only states. Any execution visiting this state is a counter-example to the safety requirement.

Figure 11: The Büchi automaton accepting executions where the train moves into the crossing while the gate is still up. The label  $\Sigma$  is a wildcard matching all five actions.

There are also other ways of performing model checking. In *symbolic model checking*, the state space of the model is represented in a more abstract way often by grouping states in sets instead of enumerating them individually. Examples of these more abstract state set representation techniques include *Binary Decision Diagrams* (BDD), *Boolean Satisfiability* (SAT) and *Satisfiability Modulo Theories* (SMT). There is a survey focusing on symbolic model checking techniques for LTL properties [58]. Another survey [38] explains many more model checking techniques. Recent books [2, 16] likewise cover many areas of model checking.

$<sup>^{21}</sup>$ Actually, Holzmann uses *interleaving product* which is similar to the handshake product, but without handshake actions H and only the (Int) rule for the transition relation

**Figure 12:** The synchronous product of the FSMs presented in Figures 8 and 11. The dashed arrow means the state ((in, 1, up), C) is the initial state of a strongly connected component (shaped like the automaton in Figure 8) made entirely of accepting states.

### 3.4 State Space Explosion

All of the steps 1-4 of the enumerative model checking procedure in Chapter 3.3 can be performed on the fly. If a counter-example exists, then it usually suffices to expand only the part of the state-space covered by that counter-example. However, in worst case, and despite the optimisations mentioned briefly above, enumerative model checking can be computationally extremely expensive. Theorem 2 in [17, p. 13] expresses that:

"There is an LTL model-checking algorithm whose running time depends linearly on the size of the Kripke structure and exponentially on the length of the LTL formula."

Furthermore, it is known that the enumerative LTL model checking problem is PSPACE-complete [42, p. 147]. As [17, p. 13] and [42, p. 147] point out, in practice the bottleneck is usually the size of the FSM and not the size of the LTL formulae. The extremely fast growth of the number of states of a model as a function of the length of the model's formal description is known as the *state-space explosion* (or just state explosion) problem. There is a survey on state explosion problem [64].

Baier and Katoen [2] Denote Var as the set of all variables of a process, Loc as the set of possible program counter values, and dom(x) as the set of values that variable x may take, i.e. the domain of x. Thus, the number of

states in the program graph is [2, p. 75]

$$|S| = |Loc| \cdot \prod_{x \in Var} |dom(x)|, \tag{1}$$

where |X| denotes the cardinality (i.e. the number of elements) of the set X. Under the translation outlined in Chapter 3.1, the Equation (1) gives the number of states of the FSM representation of the process.

Without loss of generality, the domain of program counter values and the domains of variables may be assumed to be sets of bit strings. Thus, the equation (1) may be estimated as

$$|S| \le 2^k \cdot \left(\prod_{0 < i \le |Var|} 2^m\right),\tag{2}$$

where k is the number of bits needed for representing the domain of program counter values and m is the number of bits needed for representing the variable with the largest domain. If there are n variables, then (2) becomes

$$|S| \le 2^{kmn}. (3)$$

If there are p such processes, then the upper bound becomes

$$|S| \le 2^{pkmn}. (4)$$

For a system with heterogeneous processes, the upper bound can be estimated in terms of the process with largest state space and assuming that all processes are copies of the largest process. Thus, the state space potentially grows exponentially in at least four different variables.

Not all states in a model are necessarily reachable, though. In general, establishing the number of reachable states is a much more difficult task than estimating the upper bound for the number of all states. Determining the reachable states requires either deep knowledge in the details of the particular model under investigation or a large amount of computation for enumerating the reachable portion of the state space.

Consider the following C code fragment.

On an abstract level, the fragment above could be modelled as a (deterministic) finite state automaton or as a Kripke structure, as shown in Figure 13. The transitions of the finite state machine are labelled according to the labelling in the C code, while the states of the Kripke structure are labelled with the values of the variables x and y. The state  $s_0$  is the state after the initialization of the variables x and y in the first line of the C code fragment.  $s_1$  is the state after transition  $t_0$  and before the transition  $t_1$ , which takes the process back in state  $s_0$ .

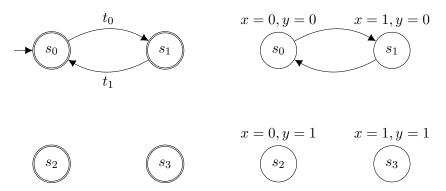

**Figure 13:** A finite state machine (on the left) and a Kripke structure (on the right) representing the C code fragment.

Notice that the transition  $t_2$  from  $s_0$  to  $s_2$  has been omitted from the diagrams, because it is never *enabled*: The condition of the if-else control structure can never be false, so the line labelled with t2 is *dead code*. Also, there is no code at all which could move the process to or from the state  $s_3$ . Hence, the states  $s_2$  and  $s_3$  are *unreachable*. Therefore, the size of the reachable state space for the Kripke structure is two, even though the whole state space has size four, assuming that the variables x and y are stored as single bits.

More realistically, all variables of type int might take one or more words of memory, e.g., 32 or 64 bits. If x and y would be stored as 32-bit integers, then there would be  $2^{32+32}$  potential combinations of their values. Furthermore, even though the code conceptually has only three transitions, the actual number of control points in the C code is eight. This makes the total number of states  $8*2^{64}$  as per equation (1). Fortunately, enumerative model checkers only allocate memory for the states they can reach, so the states for C code example above would be easy to enumerate.

The C code example also shows that a program having finitely many states does not need to terminate. This makes model checking suitable for verifying properties of *reactive systems*. Reactive systems in real life include control systems (including the ALICE [14] and CMS [37] DCSs), operating systems, and server processes. In fact, for many reactive systems, including ADAPOS, termination considered as a violation. By contrast,

many deductive verification [57] techniques that rely on theorem proving hinge on proofs of termination.

Another source for state space explosion is branching. The following complete Promela model is an extreme example of branching:

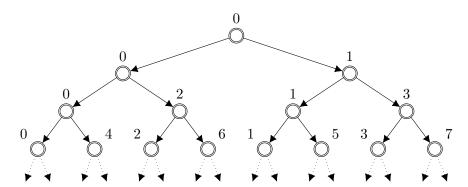

This PROMELA model essentially represents a random number generator that produces a random byte by eight consecutive coin flips. The bytes x and i are implicitly initialized to zeros. Inside the deterministic for-loop, there is a non-deterministic if-statement with two then-branches which either sets the ith bit of the byte x to 1 or leaves x unchanged. Both cases will be investigated by the model checker SPIN. After the loop has been executed, x may have any value, depending on the choices made during the loop. According to the verifier executable generated by the SPIN model checker, this model has 1024 reachable states. Figure 14 illustrates the shape of this model's state space.

**Figure 14:** The state space of the PROMELA model unrolled for the first three steps of the for-loop. The states are labelled according to the value of the variable x (omitting the 'x =' part of the propositions). Names for the states have been omitted, too.

To summarize the state-space explosion problem from a practical perspective, a model for a reactive system needs to try to minimize

- the number of processes;

- the number of statements;

- the amount of non-determinism;

- the number of variables;

- the size of the domains of the variables;

- the number and size of arrays and channels;

- the number of possible interleavings of statements belonging to concurrent processes;

- the number of auxiliary variables used for formulating the properties;

and

- lengths of the LTL formulae and the sizes of their corresponding Büchi automata.

The model should not have any unnecessary sources for complexity, because model size tends to be the bottleneck of model checking. Even though the number of reachable states is often many orders of magnitude lower than the number of all states, it is still often a very large quantity.

In the previous study [49], two model checkers were used for verifying properties of ADAPRO on both design and implementation level. The plan was originally to follow a similar approach in the current study. Implementation level C++ models were drafted for Engines and Terminals as individual processes with a simulated non-deterministic environment. These models were meant to be checked using the model checker DIVINE [4].

The complexity of the modelling task necessitated narrowing the focus to design level only, to make the work fit a master's thesis. Based on earlier good experiences [49], the model checker Spin [34] was chosen for building and verifying the model of ADAPRO discussed in this thesis.

# 4 The Model of ADAPOS

Now that the necessary background information for ADAPOS has been discussed, the following chapters will dive in to the technical substance. ADAPOS is a tailor-made system designed to serve a specific purpose on a specific environment operated by specialists over the limited duration of the third run of LHC. The model will be explained operationally on a moderately high level of detail. The general idea of the model will be presented first. After that, the eight variants refining certain details of the general specification will be introduced.

An abstract model of asynchronously operating ADAPOS Engines and Terminals was built with Prometa <sup>22</sup> for two reasons. Firstly, the model serves as an abstract specification document, focusing on the essential structures and phenomena and leaving out irrelevant details. Building a model is a great way to learn new insights about the domain of an application. Secondly, the C++ implementation-level models for Engine and Terminal that were initially planned had huge state spaces. Composing the C++ models together and verifying them would have been technically and computationally quite a challenge. The C++ models had to be dropped eventually.

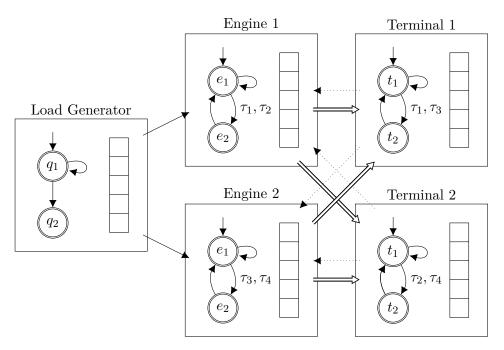

The Promela model is summarised in Figure 15. There are three types of concurrently operating processes, a Load Generator (LG), Engines, and Terminals. All processes loosely follow FSM-like logic and have their own copies of the FBI, represented as vertically aligned arrays in Figure 15. As Figure 15 suggests, all FBIs have exactly the same size. Data points are represented as bytes. For data connections, regular arrows denote single data point transmissions while bold arrows denote single data point or FBI transmissions depending on Engine state. Dotted arrows denote control connections for requesting FBI transmissions.

The model has four compile-time constants:

- Service count determines the number of data points per FBI.

- Engine count determines the number of Engines.

- Terminal count determines the number of Terminals.

- Event count determines how many updates to data points LG produces.

The states of FSMs shown in Figure 15 are high-level abstractions like the FSMs shown in Figures 5, 7, and 8 in Chapter 3.1, and also Figures 11, 12, and 13 in Chapter 3.4. The states of the FSMs of Engines and Terminals in Figure 15 are called *protocol states*. Protocol states should not not be confused with ADAPRO states which are omitted from this model.<sup>23</sup>

$<sup>^{22} \</sup>mbox{Version 6.10}$  of the model is archived at https://doi.org/10.5281/zenodo.4767686  $^{23} \mbox{See}$  Section 3.2 in the manual of ADAPRO.

**Figure 15:** A schematic view on the abstract model of ADAPOS with five data points per FBI, a Load Generator, two Engines, and two Terminals. The handshake actions  $\tau_i$  are used for synchronisation.

Protocol states could be considered to be substates of the ADAPRO state RUNNING, though this is a slightly inaccurate simplification.

The model makes the following assumptions on publish-subscribe network connections with DIM [25] and  $0 MQ^{24,25}$  protocols:

- Message contents are never altered.

- Messages between two processes are not duplicated in transit.

- Those messages between two processes that are received arrive in the order they were sent.

- When there is a message in transit between two processes and the sender attempts to transmit another message, then one of these messages will be dropped. DIM drops the old message and 0MQ drops the new one.

- Messages to n recipients are transmitted over n one-to-one connections which may drop messages independently.

- Engines may disconnect from Terminals for unspecified reasons.

$<sup>\</sup>overline{^{24}\text{TCP}}$  is assumed to be the underlying transport protocol.

<sup>&</sup>lt;sup>25</sup>https://rfc.zeromq.org/spec/29/

The data connections from LG to Engines and Engines to Terminals interpret the publish-subscribe patterns of DIM and 0MQ respectively. The control connections from Terminals to Engines represent DIM command calls that are assumed to never fail or be delayed.

The large state space of the base PROMELA model and the fact that there are multiple interpretations on how DIM and 0MQ connections could be modelled led to the creation of several variants of the model. Variants are maintained in separate branches in the Git version control system used in the modelling project. The variants differ by their interpretations of *input* (LG to Engines) and/or *output* (Engines to Terminals) connections.

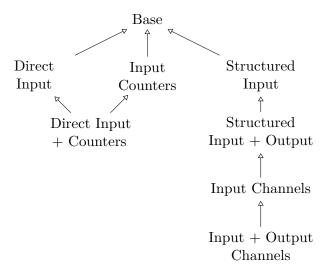

Figure 16 illustrates refinement relations between the variants of the model. In object-oriented terms, the arrows point from inheriting variants to the more general ones. This hierarchy is only conceptual and it is not reflected in the Prometa code in any way.

Figure 16: The variants of the Promela model of ADAPOS.

Chapters 4.3-4.10 sketch a simplified overview on these variants using Python-style pseudocode instead of Promela. A book [6] provides a hands-on introduction to the Promela modelling language and the Spin model checker. For the sake of conciseness, certain details on the variants have been omitted from this presentation, including

- details of the FSMs shown in Figure 15;

- FBI transfers between Engines and Terminals; and

- details on how Terminals keep track on the freshness, the current value, and the previous value of a data point in their FBIs.

General discussion on the roles and logic of the different process types of the model is appropriate before introducing the variants, though.

#### 4.1 Processes in the Model

LG and Engines are agnostic about other processes receiving their outputs. They act as publishers sending the same data to any number of subscribers. It is possible that a message will be received by some subscribers while it is dropped for others. Neither of these two process types ever block when sending messages. Both process types follow the same general logic regardless of the number of connected subscribers.

LG simulates the DIM services producing input to ADAPOS. By default, LG generates distinct updates until the number of updates generated exceed the event count. At this point, LG halts. LG also has an alternative cyclic mode in which it never halts, and keeps cycling through three constant values per data point. The event count parameter has no effect when LG is compiled to run in cyclic mode.

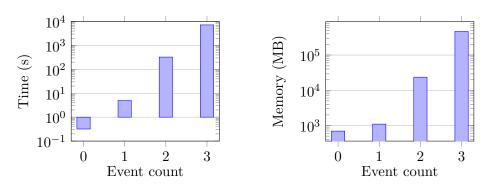

Consider the FSMs of Engines and Terminals shown in Figure 15. In the PROMELA code, the states  $e_1$  and  $t_1$  are both named as SEND\_SINGLE. The states  $e_2$  and  $t_2$  share the name SEND\_FBI. The meaning of these protocol states is that during  $e_1$  and  $t_1$  the processes expect the messages to be single data points, while state  $e_2$  and  $t_2$  the processes expect the next message to be an FBI.