Copyright by Miguel Francisco Gandara 2021 The Dissertation Committee for Miguel Francisco Gandara certifies that this is the approved version of the following dissertation:

# Utilizing Digital Design Techniques and Circuits To Improve Energy and Design Efficiency of Analog and Mixed-Signal Circuits

Committee:

Zhigang (David) Pan, Supervisor

Nan Sun, Co-Supervisor

Eric Soenen

Ranjit Gharpurey

Michael Orshansky

# Utilizing Digital Design Techniques and Circuits To Improve Energy and Design Efficiency of Analog and Mixed-Signal Circuits

by

Miguel Francisco Gandara

#### DISSERTATION

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN May 2021

Dedicated to my wife Disha. "Way before I found my sound, she kept my feet on the ground."

## Acknowledgments

I would like to start by thanking my PhD supervisor, Dr. Nan Sun. I had never seriously considered a PhD before I began working with Dr. Sun during my Master's studies, and without his encouragement I likely never would have pursued that degree. Thankfully, throughout our journey together he remained just as positive and encouraging, and I am deeply thankful for the opportunity to learn from him. I also want to express my deepest gratitude to Dr. David Z. Pan for taking on the role of supervisor late in my PhD journey and helping me to get across the finish line. My sincere thanks to the rest of my committee members, Dr. Michael Orshansky, Dr. Ranjit Gharpurey, and Dr. Eric Soenen, for offering their time and advice during my degree pursuit.

During my professional career, I have been blessed with a number of managers that saw the potential in me, and were absolutely crucial to my growth and success. Ron Strong first encouraged me to pursue graduate studies, Billy Dennie allowed me flexibility to work part-time to focus on my studies, Dr. Eric Soenen and Dr. Martin Kinyua gave me a great first analog design job, and Dr. Tamer Ali and Dr. Ramy Awad pushed me to complete my studies and worked with me to help me to do so. I owe them all for the academic and professional success I have had thus far.

The Sun Research Group is full of smart, passionate, and kind people. I

want to especially thank my colleague and friend Abhishek Mukherjee, for his support through all the ups and downs of the PhD journey. Our regular trips the various eateries of Austin were a great source of stress relief during the long hours of tapeouts. I also want to thank the colleagues that I collaborated with on my two tapeouts and the other projects covered in my dissertation - Dr. Wenjuan Guo, Paridhi Gulati, Ahmet Budak, Dr. Sungjin Hong, Dr. Xiyuan Tang, Yunyi Wang, Dr. Long Chen, Dr. Yeonam Yoon, Dr. Shaolan Li, and Anoosh Michael. Without your crucial assistance during these projects, I could not have possibly have completed this work and you helped to improve the quality of my research. Many thanks to the other members of the Sun Research Group that made the PhD pursuit more enjoyable, Dr. Jeonggoo Song, Dr. Yanlong Zhang, Dr. Wenda Zhao, Dr. Linxiao Shen, Dr. Yi Zhong, Wei Shi, Xiangxing Yang, and Dr. Chen-Kai Hsu. Andrew Kieschnick, the CERC administrator, was always quick to respond to any issue and provided invaluable support on the EDA tools and Linux environment.

Last but certainly not least, I would like to thank my family. My parents, Miguel Gandara and Kathryn Lueders; step-parents, Jeremy Horne and Lydia Persaud; and in-laws, Haresh and Maya Sampat, have been a constant source of love and support throughout this journey. They helped to give me strength during many troubled times in my life. My parents instilled in me the strong work ethic and were some of my first mentors in engineering. Jeremy, Lydia, and the Sampats have always treated me like a son and supported me unconditionally. My siblings Julia, Liam, and Emma have been my biggest cheerleaders and a reliable stress relief valve. Finally I want to thank the person that's taken every step of this journey with me, my wonderful wife Disha. Her partnership has enabled me to achieve beyond what I thought possible, and I am thankful every day that she is in my life.

## Utilizing Digital Design Techniques and Circuits To Improve Energy and Design Efficiency of Analog and Mixed-Signal Circuits

Miguel Francisco Gandara, Ph.D. The University of Texas at Austin, 2021

#### Supervisors: Zhigang (David) Pan Nan Sun

Technology scaling has long driven large growth in the electronics market. With each successive technology generation, digital circuits become more power and area efficient. The large performance increases realized for digital circuits due to digital scaling have not translated to similar performance improvements for analog circuits. First, noise-limited analog circuits are not capable of leveraging the reduced parasitics of advanced processes, since capacitor sizes are generally set by noise requirements. Second, analog circuit performance is closely tied to the achievable device intrinsic gain, which degrades as process sizes shrink. Reduced supply voltages further exacerbate this issue, as the achievable gain per stage is limited by the number of devices that can be stacked while maintaining all devices in saturation. Finally, process variation increases with decreased feature sizes, so analog circuits have deal with increased mismatch and wider variations in threshold voltages, increasing the time required to design a circuit that is robust across process, voltage, and temperature (PVT) variation. This work seeks to address the limitations of analog circuits in advanced technologies by leveraging digital techniques and digital-like circuits that offer improved scalability. The first half of this dissertation investigates replacing the traditional closed-loop residue amplifier in a pipeline analog-to-digital converter (ADC) with an open loop dynamic amplifier. Previous works incorporating dynamic amplifiers have struggled to achieve large gains and have suffered from offset mismatch between the comparator and amplifier, which will only get worse in more advanced technologies. We propose the usage of a residue amplifier that combines an integration stage, to ensure low noise operation, with a positive feedback stage, to ensure high gain and high speed operation. By utilizing this topology, the proposed amplifier was the first dynamic amplifier to achieve a high gain of 32. Additionally, the proposed amplifier can reuse existing comparator hardware in the ADC, removing all offset mismatch between comparator and amplifier. Digital calibration techniques were applied to ensure a constant gain across PVT. The next part of this dissertation tries to overcome the scaling challenges for noiselimited ADCs with band-limited input signals. By leveraging digital filtering techniques to generate a prediction of the band-limited signal, the conversion can be limited to a range that is a fraction of the total ADC input range, allowing for significant decreases in reference and comparator power consumption. This work extends previous works by enabling accurate predictions for any band-limited signal characteristic. Previous works only focused on accurate predictions for low-activity signals. Finally, the large compute power enabled

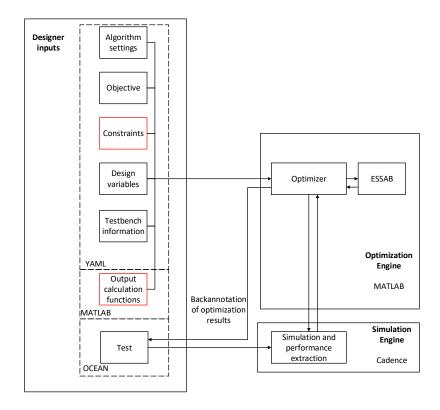

by modern technology scaling is leveraged to improve the design efficiency of analog circuits. A new automated circuit sizing tool is proposed that can achieve better performance than manual designs done by experts in a much shorter amount of time. All of these techniques help to alleviate the power and design efficiency limitations caused by technology scaling.

# Table of Contents

| Acknowledgments |       |                                                                                                                                   | $\mathbf{v}$  |

|-----------------|-------|-----------------------------------------------------------------------------------------------------------------------------------|---------------|

| Abstra          | act   |                                                                                                                                   | viii          |

| List of         | Table | es                                                                                                                                | xiii          |

| List of         | Figu  | res                                                                                                                               | xiv           |

| Chapt           |       | Introduction                                                                                                                      | 1             |

| 1.1             | Pipel | ine ADC Operation                                                                                                                 | 6             |

|                 | 1.1.1 | Residue Amplification                                                                                                             | 11            |

| 1.2             | SAR   | Operation                                                                                                                         | 14            |

| Chapt           | er 2. | Pipelined SAR ADC Reusing the Comparator a Residue Amplifier                                                                      | 15            |

| 2.1             | Intro | duction                                                                                                                           | 17            |

| 2.2             | Resid | lue Amplification Using a StrongARM Latch                                                                                         | 19            |

|                 | 2.2.1 | Basic Operation                                                                                                                   | 19            |

|                 | 2.2.2 | Noise                                                                                                                             | 23            |

|                 | 2.2.3 | Linearity                                                                                                                         | 30            |

| 2.3             | Pipel | ine ADC Architecture                                                                                                              | 32            |

| 2.4             | -     | urement Results                                                                                                                   | 36            |

| Chapt           | er 3. | A 172dB-FoM Pipelined SAR ADC Using a Regenerative Amplifier with Self-Timed Gain Control and Mixed-Signal Background Calibration | n-<br>d<br>40 |

| 3.1             | Intro | duction                                                                                                                           | 40            |

| 3.2             | Prope | osed Self-Timed Gain Control                                                                                                      | 44            |

| 3.3             | Prop  | osed Mixed-Signal Calibration                                                                                                     | 50            |

| 3.4             | Prop  | osed Pipelined SAR ADC Architecture                                                                                               | 52            |

| 3.5             | Meas  | urement Results                                                                                                                   | 54            |

| Chapter 4.   |            | Digital Filtering Techniques to Reduce SAR AD                                    |           |

|--------------|------------|----------------------------------------------------------------------------------|-----------|

| 4.4          | <b>T</b> , | Dynamic Energy                                                                   | <b>59</b> |

| 4.1          |            | luction                                                                          | 59        |

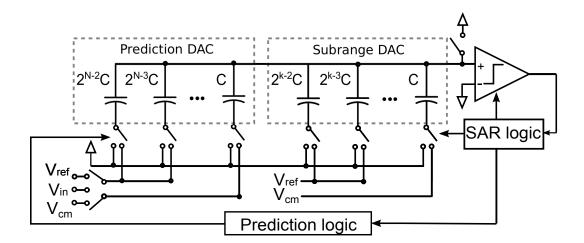

| 4.2          |            | ction Engine Theory of Operation                                                 | 62        |

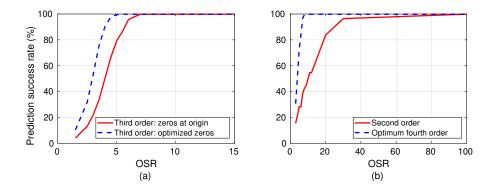

| 4.3          | Prope      | osed SAR ADC Architecture                                                        | 70        |

|              | 4.3.1      | Capacitive DAC                                                                   | 71        |

|              | 4.3.2      | Subranging Operation                                                             | 72        |

|              | 4.3.3      | Error Detection/Recovery                                                         | 74        |

| 4.4          | Imple      | mentation and Simulation Results                                                 | 75        |

|              | 4.4.1      | $Prediction \ filter \ implementation  . \ . \ . \ . \ . \ . \ . \ . \ . \ .$    | 75        |

|              | 4.4.2      | ADC implementation and simulation results                                        | 77        |

| Chart        | F          | Lungaring Design Efficiency Through the Use                                      | - C       |

| Chapte       | er 5.      | Improving Design Efficiency Through the Use of<br>Automated Circuit Sizing Tools | 80        |

| 5.1          | Prope      | osed analog IC sizing tool                                                       | 83        |

| 5.2          | Autor      | nated sizing test cases                                                          | 86        |

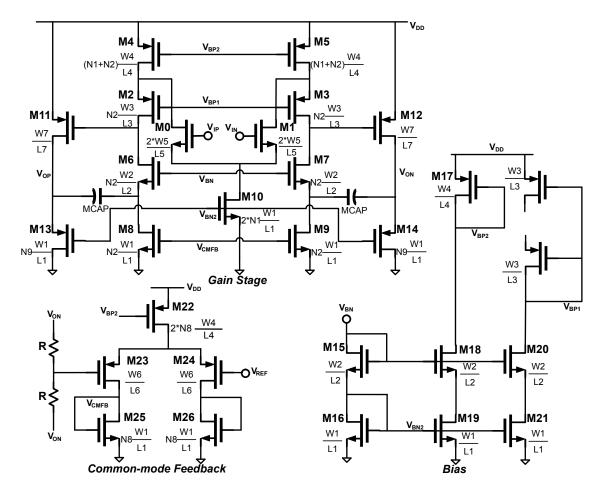

|              | 5.2.1      | MDAC utilizing a folded-cascode OTA                                              | 87        |

|              |            | 5.2.1.1 Designer considerations                                                  | 88        |

|              |            | 5.2.1.2 Optimization results                                                     | 90        |

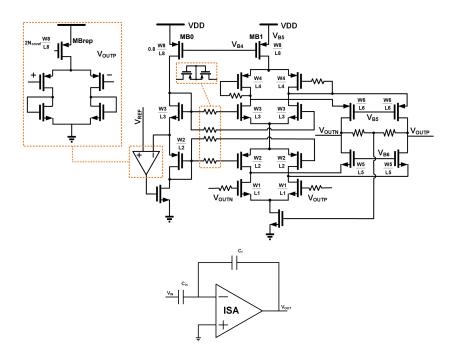

|              | 5.2.2      | Inverter stacking amplifier                                                      | 91        |

|              |            | 5.2.2.1 Designer considerations                                                  | 94        |

|              |            | 5.2.2.2 Optimization results                                                     | 95        |

|              | 5.2.3      | Distributed input VCO                                                            | 96        |

|              |            | 5.2.3.1 Designer considerations                                                  | 98        |

|              |            | 5.2.3.2 Optimization results                                                     | 98        |

| 5.3          | Concl      | usion                                                                            | 100       |

| Chapter 6.   |            | Conclusion                                                                       | 101       |

| Bibliography |            |                                                                                  |           |

# List of Tables

| Performance comparison between comparator and amplifier operating modes.    | 36            |

|-----------------------------------------------------------------------------|---------------|

| Performance Comparison                                                      | 39            |

| Performance Comparison                                                      | 58            |

| Zero placement for minimum prediction error                                 | 65            |

| Power comparison for the proposed prediction ADC and a tra-<br>ditional ADC | 79            |

| Design parameters and their ranges for the folded-cascode OTA               | 89            |

| A typical design obtained by ESSAB (folded-cascode)                         | 91            |

| Performance values of a typical design obtained by ESSAB (folded-cascode)   | 91            |

| Statistical results for different algorithms (folded-cascode)               | 92            |

| Design parameters and their ranges for ISA                                  | 92            |

| A typical design obtained by ESSAB (ISA)                                    | 95            |

| Performance values of a typical design obtained by ESSAB (ISA)              | 96            |

| Statistical results for different algorithms (ISA)                          | 97            |

| Design parameters and their ranges for VCO (VCO)                            | 98            |

| A typical design obtained by ESSAB (VCO)                                    | 99            |

| Performance values of a typical design obtained by ESSAB (VCO)              | 99            |

| Statistical results for different algorithms (VCO)                          | 100           |

|                                                                             | erating modes |

# List of Figures

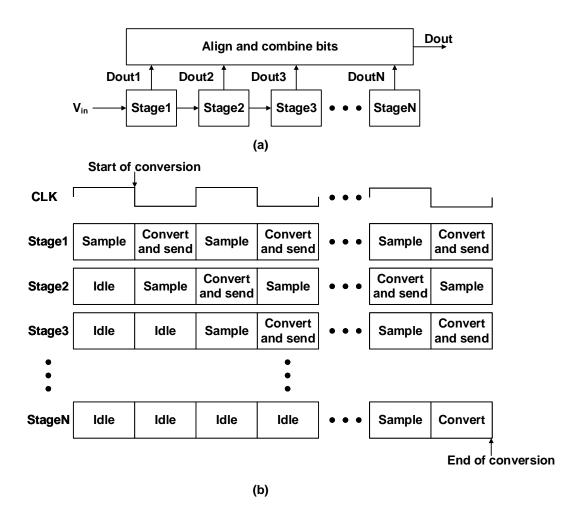

| 1.1  | Conceptual (a) block diagram and (b) timing diagram of a pipeline ADC                                                                                  | 8  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Example two-stage pipelined ADC                                                                                                                        | 9  |

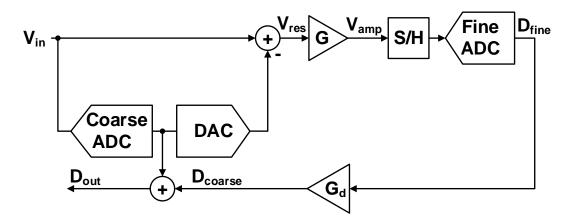

| 1.3  | Voltage transfer curve at residue amplifier (a) input (b) output                                                                                       | 10 |

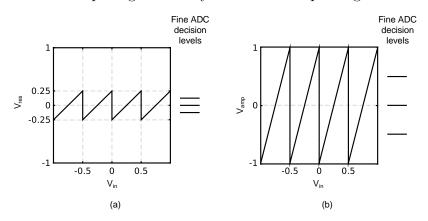

| 1.4  | Example MDAC                                                                                                                                           | 11 |

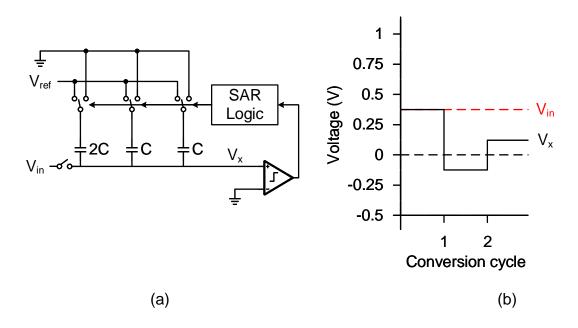

| 1.5  | (a) Example 2-bit SAR ADC (b) SAR ADC voltage waveforms                                                                                                | 15 |

| 2.1  | Proposed amplifier schematic.                                                                                                                          | 20 |

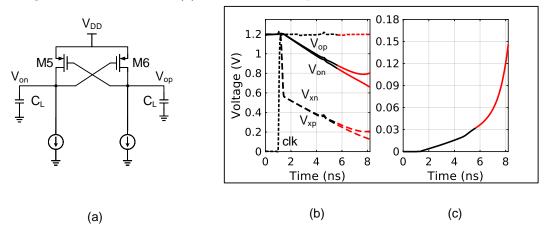

| 2.2  | <ul><li>(a) Amplifier equivalent schematic during internal integration</li><li>(b) Single-ended waveforms (c) Differential output waveform .</li></ul> | 20 |

| 2.3  | <ul><li>(a) Amplifier equivalent schematic during output integration</li><li>(b) Single-ended waveforms (c) Differential output waveform .</li></ul>   | 21 |

| 2.4  | (a) Amplifier equivalent schematic during regeneration (b) Single-<br>ended waveforms (c) Differential output waveform                                 | 21 |

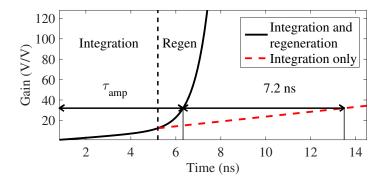

| 2.5  | Simulated amplifier gain (with extrapolated integration curve)                                                                                         | 23 |

| 2.6  | (a) Common-source amplifier with RC load half-circuit (b) Noise model                                                                                  | 24 |

| 2.7  | Noise model for proposed amplifier with integration and regen-<br>eration phases                                                                       | 26 |

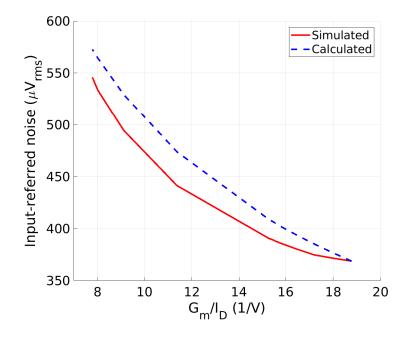

| 2.8  | Proposed amplifier input-referred noise vs. $G_m/I_D$                                                                                                  | 27 |

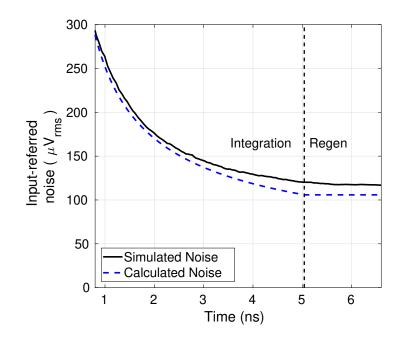

| 2.9  | Comparison between calculated and simulated input referred noise for the proposed amplifier                                                            | 28 |

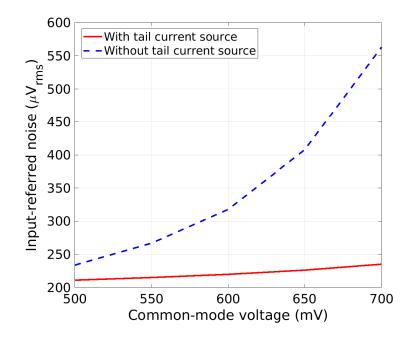

| 2.10 | Noise variation across common-mode                                                                                                                     | 29 |

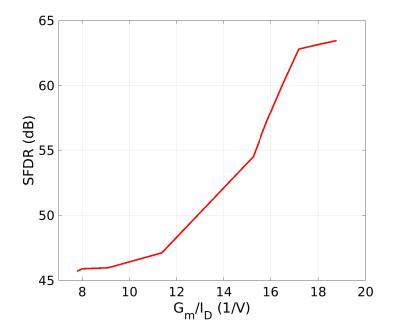

| 2.11 | Proposed amplifier SFDR vs. $G_m/I_D$                                                                                                                  | 31 |

| 2.12 | Proposed amplifier SFDR vs. input swing                                                                                                                | 32 |

| 2.13 | Proposed pipeline ADC architecture and timing diagram                                                                                                  | 32 |

| 2.14 | (a) Common mode variation across ADC conversion steps (b)<br>Offset mismatch across ADC conversion steps                                               | 34 |

| 2.15 | Amplifier offset vs. comparator offset and correlation coefficient<br>for a 10000 point Monte Carlo simulation                                         | 35 |

| 2.16 | ADC (a) die photo and (b) layout.                                                                   | 37 |

|------|-----------------------------------------------------------------------------------------------------|----|

| 2.17 | Measured ADC output spectra with 32768 points                                                       | 37 |

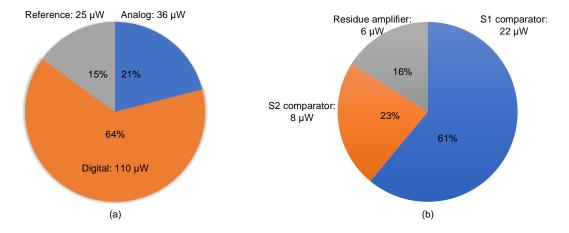

| 2.18 | (a) Measured power breakdown (b) Analog and delay line power breakdown                              | 38 |

| 2.19 | Measured SNDR and SFDR vs. (a) input frequency and (b) input amplitude                              | 38 |

| 3.1  | Block diagram of a regenerative amplifier in Ch. 2                                                  | 41 |

| 3.2  | Pipelined ADC with (a) digital gain calibration (b) mixed-signal gain calibration                   | 44 |

| 3.3  | Transient output voltages of the proposed amplifier                                                 | 45 |

| 3.4  | SNR vs jitter for continuous time sampling and positive feedback-<br>based amplification            | 46 |

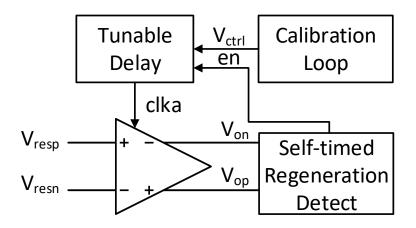

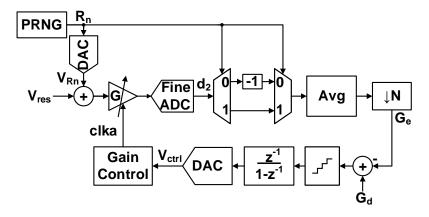

| 3.5  | Proposed gain control system                                                                        | 47 |

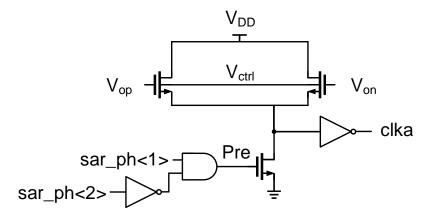

| 3.6  | Proposed self-timed gain control block                                                              | 47 |

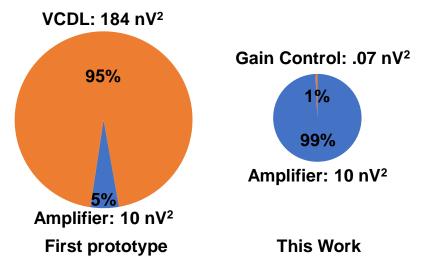

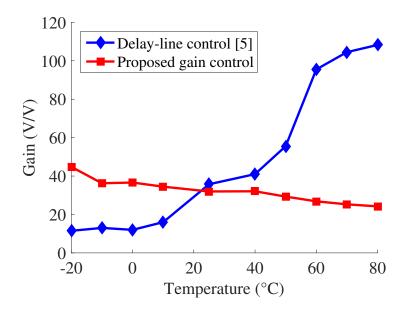

| 3.7  | Amplifier noise comparison between first prototype and second prototype                             | 49 |

| 3.8  | Measured amplifier gain vs. temperature                                                             | 49 |

| 3.9  | Proposed mixed-signal calibration loop                                                              | 50 |

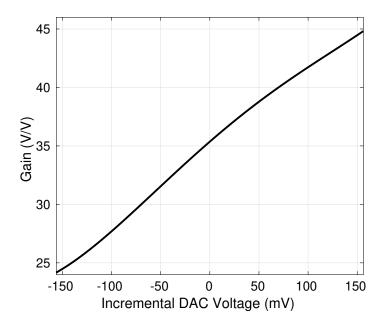

| 3.10 | Measured gain vs DAC tuning voltage                                                                 | 51 |

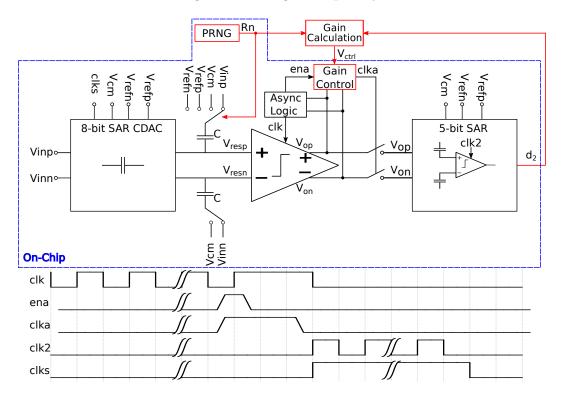

| 3.11 | Proposed pipeline ADC architecture and timing diagram                                               | 53 |

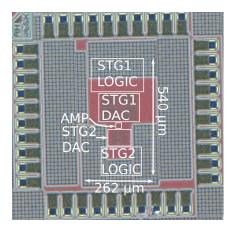

| 3.12 | ADC die photo                                                                                       | 54 |

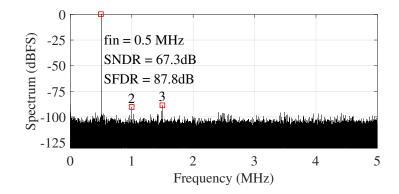

| 3.13 | Measured ADC output spectra with 32768 points                                                       | 56 |

| 3.14 | Measured SNDR and SFDR vs. (a) input frequency and (b) input amplitude.                             | 56 |

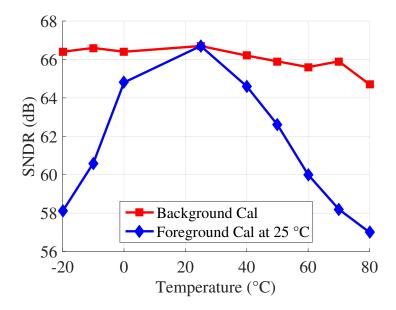

| 3.15 | Measured SNDR vs. temperature                                                                       | 57 |

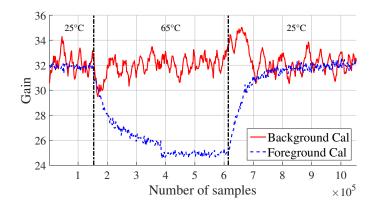

| 3.16 | SNDR over time with transient steps from 25°C to 65°C to 25° C                                      | 57 |

| 3.17 | (a) Measured power breakdown (b) Analog and delay line power breakdown                              | 58 |

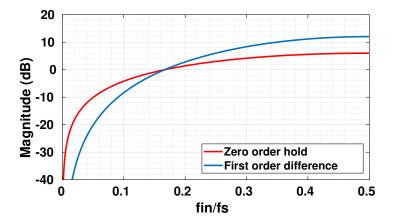

| 4.1  | Prediction error frequency response for zero-order hold and first order difference estimators       | 63 |

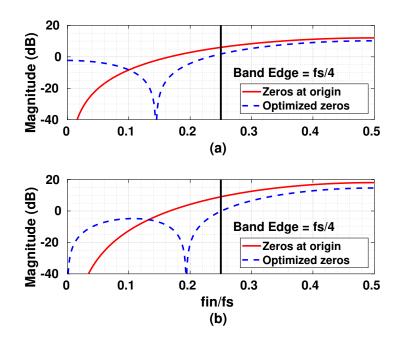

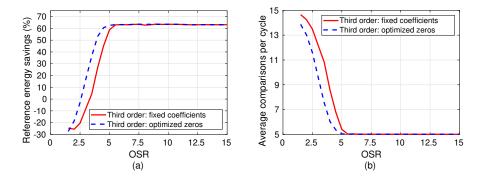

| 4.2  | Frequency response for (a) second, and (b) third-order predic-<br>tion filters                      | 64 |

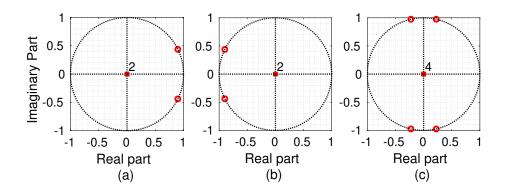

| 4.3  | (a) Example second-order low-pass filter and its (b) high-pass<br>and (c) band-pass transformations | 66 |

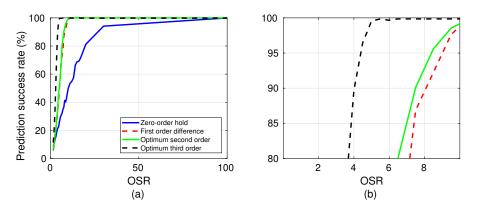

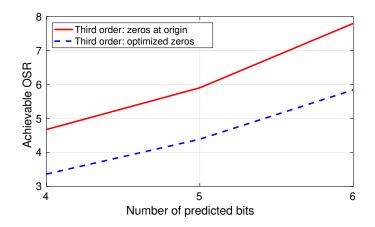

| 4.4  | (a) Success rate vs OSR for various filter orders (b) Zoomed in view                                                                     | 67 |

|------|------------------------------------------------------------------------------------------------------------------------------------------|----|

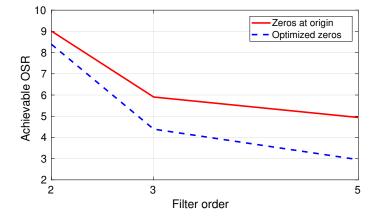

| 4.5  | Achievable OSR vs filter order                                                                                                           | 68 |

| 4.6  | Achievable OSR vs number of predicted bits for third-order filters                                                                       | 69 |

| 4.7  | Success rate vs. OSR for (a) high pass and (b) band pass pre-<br>diction filters                                                         | 70 |

| 4.8  | Schematic of capacitive DAC for an $N$ -bit ADC with $k$ -bit sub-ranging                                                                | 71 |

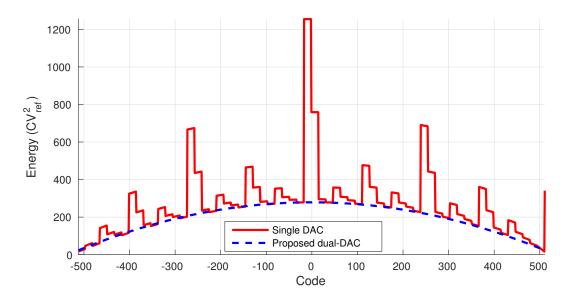

| 4.9  | Reference energy as a function of input code with a perfect initial guess. Single DAC [25] and the proposed dual-DAC approach are shown. | 72 |

| 4.10 | Comparison between dynamic and static filter bandwidth vs $\operatorname{OSR}$                                                           | 76 |

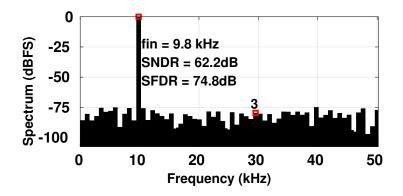

| 4.11 | Simulated ADC output spectra with 256 points                                                                                             | 78 |

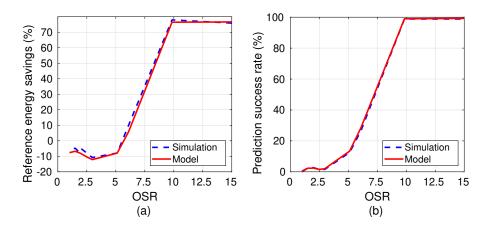

| 4.12 | Simulated and modeled (a) success rate and (b) reference energy savings vs OSR                                                           | 78 |

| 5.1  | Architecture of the proposed automatic sizing tool [29]                                                                                  | 84 |

| 5.2  | Schematic of the folded-cascode OTA                                                                                                      | 88 |

| 5.3  | Schematic of the ISA                                                                                                                     | 93 |

| 5.4  | Schematic of VCO                                                                                                                         | 97 |

## Chapter 1

## Introduction

Technology scaling has enabled increased functional integration into modern Systems on Chip (SOCs). Digital processors now commonly integrated mixed-signal functionality for sensing and communication. While technology scaling has significant benefits for digital circuits, reducing both the power and area with each new technology generation, analog circuits do not obtain the same benefits. First, for medium and high precision designs, the power consumption is set by the noise requirements, which will not scale with technology. Further, designing high precision signal processing elements becomes more difficult as technology scales. Traditional high precision signal processing is done by applying negative feedback to ensure constant performance across process, voltage, and temperature (PVT) variation. These techniques require amplifiers with large gain in order to ensure adequate loop gain to maintain high precision in the negative feedback loop. Device intrinsic gains generally reduce as the device size shrinks, which limits the achievable gain from a singlestage amplifier. Furthermore, reduced supply voltages in advanced processes also limit the amount of cascoding that can be performed while maintaining an adequate output swing. Both of these limitations imply more gain stages are needed in order to achieve the necessary amplifier gain to support closedloop operation. These extra gain stages increase power consumption as well as mismatch and noise. Our work seeks to address the scaling limitations of noise-limited designs and the challenges of designing high precision op amps for analog signal processing by leveraging digital techniques and more scalingfriendly amplification topologies.

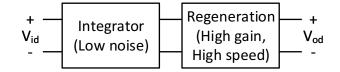

Pipeline analog-to-digital converters (ADCs) are an attractive option for medium resolution (12-16 bits) and medium to high speeds (tens of Ms/sto hundred of Ms/s). By splitting up a single high resolution conversion into multiple pipelined lower-resolution conversions, the pipeline ADC can achieve high sampling rates with only a linear increase in hardware complexity. The main design challenge associated with modern pipeline ADCs is their requirement for precise gain between stages to ensure adequate dynamic range for each pipeline sub-ADC. As mentioned above, precision gain is typically implemented using closed-loop approaches with large amplifier gain requirements. Previous work [17, 11] has sought to reduce the amplifier gain requirements by utilizing open-loop amplifiers, reducing the gain requirement to match the desired interstage gain in the pipeline ADC. In order to further reduce the residue amplifier power consumption, dynamic amplifiers using integration have been utilized. These amplifiers do not require any static power consumption, greatly improving their power efficiency. Integrator-based amplifiers suffer from two main limitations; the achievable gain is limited and the offset mismatch between the comparator and amplifier requires either large device sizes or additional hardware for offset calibration. Even in integrator-based designs that utilize special techniques to increase the achievable gain [24, 15], the maximum achievable gain is limited to approximately 16. Our work seeks to increase the achievable gain for dynamic amplifiers by cascading an integrator stage, to achieve moderate gain and sufficient signal-to-noise ratio (SNR), with a positive feedback stage, to achieve high gain and high speed. A prototype 12-bit pipelined ADC sampling at 10 Ms/s was fabricated in 130 nm CMOS technology to prove the feasibility of our residue amplification approach. To the authors' best knowledge, this is the first pipeline ADC to utilize positive feedback in the residue amplifier, and it is the first dynamic amplifier capable of achieving a gain of 32. Our proposed residue amplifier also offers a simple method to ensure there is no offset mismatch between the residue amplifier and the sub-ADC comparator. The strongARM latch that is used as a comparator in many ADC designs already performs this cascaded integrator and positive feedback operation. By stopping the comparator operation before its outputs have fully resolved to supply and ground, the comparator can be utilized as an analog amplifier. Sharing the strongARM latch between the residue amplifier and the sub-ADC comparator ensures no offset mismatch is present. Chapter 2 discusses the proposed residue amplifier and the proposed pipeline ADC architecture in more detail.

Despite the impressive advantages of our proposed residue amplifier, our first prototype suffered from two key limitations that limited the achievable performance and robustness. First, unlike traditional closed-loop amplifiers, our proposed residue amplifier's outputs are not fully settled at the end of the amplification operation. Since the outputs are still changing when the amplifier output is sampled, the output is sensitive to any jitter in the amplifier's timing control. When utilizing positive feedback, this sensitivity is increased even further, since the amplifier output increases exponentially with time. The jitter present in the timing control loop of our first prototype limited the ADC's ENOB to 10.3 bits. Second, the amplifier gain varies across PVT variation, a key disadvantage compared to closed-loop approaches. This sensitivity is increased by the usage of positive feedback. In order to address the jitter and gain variation, a simple timing control loop is proposed. The timing control is simple and adds minimal jitter to the timing loop. The proposed timing loop also automatically adjusts the amplification time for changing integration time, thus significantly reducing the gain variation across PVT. Finally, the timing control offers a simple control knob to further adjust the amplification time; by sensing the gain in the digital domain and adjusting the amplification time for constant gain, the loop can be closed in the digital domain, which allows for high loop gains without the implementation complexity of analog closed-loop solutions. The proposed timing control loop reduces both the jitter-induced noise and power consumption of the timing loop from the first prototype. The usage of a mixed-signal calibration loop also removes the need for a fractional divider running at the sampling rate, which can be a large source of power consumption for low-power ADCs. A second prototype was fabricated in 130 nm CMOS, and measurement results showed a 4 dB improvement in SNDR, as well as stable performance across a 100°C temperature range. Both performance improvements were enabled by the enhanced timing control loop with mixed-signal background calibration. Chapter 3 discusses the implementation of our proposed gain control and mixed-signal background calibration loop as well as the measured prototype performance.

Successive Approximation Register (SAR) ADCs are increasingly used in advanced processes due to their highly digital nature. For medium resolution ADCs that are noise-limited, however, the power consumption in the comparator and the capacitive digital-to-analog converter (CDAC) do not scale as well as the digital control. This is because the capacitance associated with each of these blocks must be sized large enough to ensure adequate SNR. As supply voltages reduce in advanced processes, the available input voltage swing also decreases, placing even more stringent noise requirements on the CDAC and comparator. Chapter 4 discusses the usage of digital filtering techniques to reduce the comparator and CDAC power when the input signal is bandlimited. By applying some knowledge of the input characteristics, a prediction filter can be designed to apply an initial guess to the SAR CDAC and reduce the required conversion range. Our work extends previous work by enabling prediction filtering for any band-limited input signal. Previous works have only focused on accurate predictions for low-activity signals. The theoretical results of this chapter are supported by modeling and simulation results of a 10-bit, 100 kS/s SAR ADC.

Chapter 5 seeks to improve the design efficiency of analog circuit designers by leveraging the large compute power enabled by technology scaling. A new circuit sizing tool is proposed that can achieve performance comparable to that of state-of-the-art designs in a fraction of the time required for manual design. Especially in advanced processes, optimizing the circuit sizing can be a tedious and time consuming process. By automating the sizing process, designers can focus on more interesting architectural and system-level design problems.

This dissertation is organized as follows. The rest of this chapter focuses on the fundamental concepts that are used throughout the rest of this dissertation. Sec. 1.1 covers the theory of operation of pipeline ADCs. Sec. 1.2 covers the theory of operation of SAR ADCs. Chapter 2 and 3 cover the proposed residue amplification technique for pipelined ADCS, as well as the proposed gain control and mixed-signal background calibration loop that ensures constant gain across PVT. Chapter 4 discusses the proposed digital prediction technique that allows for accurate prediction of any band-limited signal. Chapter 5 presents a new automated circuit sizing tool and some example case studies leveraging the new tool and a new optimization algorithm developed by another PhD student. Chapter 6 concludes the dissertation.

## 1.1 Pipeline ADC Operation

This section begins with an introduction to the operation of a simple pipeline ADC. After the introduction, the operation of the Multiplying DAC (MDAC), an important block in pipeline ADC design, is presented in detail. This section concludes with a discussion of redundancy, a commonly used

method in pipeline ADC designs for reducing the offset requirements of the sub-ADC comparators. Figure 1.1 shows an example block and timing diagram for a pipelined ADC. By splitting up an M-bit conversion into N stages, the maximum conversion speed can be increased to the conversion speed of a single sub-ADC. Additionally, increasing the resolution requires only a linear increase in hardware complexity. This is in contrast to flash and SAR ADCs, where an increase in resolution requires an exponential increase in hardware complexity. Each sub-ADC operates in two phases. In the first phase, the sampled residue voltage from the preceding stage is sampled for further processing. In the next phase, the sub-ADC performs its conversion, generates a residue voltage, and sends that residue to the succeeding stage for further quantization. An additional digital block collects all the outputs from the sub-ADCs, scales them appropriately, and combines the individual outputs into a single M-bit output. For further detail on the conversion and residue generation process, Figure 1.2 illustrates a general two stage pipelined ADC. After the first stage samples the input voltage during its first phase, the first stage moves into the conversion and residue generation phase. During this phase, the coarse ADC performs an *n*-bit conversion of the input. During this phase, the *n*-bit sub-ADC converts the input voltage into a digital code,  $D_{coarse}$ . An *n*-bit digitalto-analog converter (DAC) then transforms  $D_{\mathit{coarse}}$  to an analog voltage. The analog output from the *n*-bit DAC is then subtracted from the input voltage, producing an error residue voltage,  $V_{res}$ . The residue voltage is bounded by:

$$-\frac{V_{ref}}{2^n} \le V_{res} \le \frac{V_{ref}}{2^n} \tag{1.1}$$

Figure 1.1: Conceptual (a) block diagram and (b) timing diagram of a pipeline ADC

where  $V_{ref}$  is the reference voltage of the ADC that sets the maximum full-scale range of the ADC. The residue voltage is then amplified with a gain of G. This amplifier is used to reduce the precision requirements of the downstream ADC. The precision requirements on the *m*-bit fine ADC without an amplification stage would be m + n bits. For an *M*-bit ADC, the least significant bit (LSB)

Figure 1.2: Example two-stage pipelined ADC

size,  $\Delta$  is given by:

$$\Delta = \frac{V_{FS}}{2^M} \tag{1.2}$$

where  $V_{FS}$  is the full-scale voltage of the ADC. Without amplification,  $V_{FS}$  of the second stage is given by Equation 1.1. Using this value in Equ. 1.2 gives a second-stage size,  $\Delta_2$ , of:

$$\Delta_2 = \frac{V_{FS}}{2^{n+m}} \tag{1.3}$$

which is equivalent to an m + n bit ADC. With an amplification stage gain of  $G = 2^{B}$ ,  $\Delta$  becomes:

$$\Delta_2 = \frac{V_{FS}}{2^{n+m-B}} \tag{1.4}$$

which reduces the precision requirement to m+n-B bits. Since the full-scale voltage of the second stage is generally equivalent to the full-scale voltage of the first stage, the amplification factor G sets the effective resolution of the input to the second stage. Fig. 1.3 further illustrates the required fine ADC decision levels with and without residue amplification. Fig. 1.3(a) shows the

voltage transfer curve at the output of the coarse ADC, assuming a coarse ADC resolution of 2 bits. Without residue amplification, the fine ADC decision levels need to be spaced closely to cover the reduced input range. With residue amplification, the voltage transfer curve becomes 1.3(b), with the fine ADC decision level spacing relaxed by the residue amplifier gain. In traditional

Figure 1.3: Voltage transfer curve at residue amplifier (a) input (b) output

designs, the subtraction and amplification stages are implemented as a single switched capacitor device, the MDAC. Section 1.1.1 discusses the residue amplification operation in more depth. The second stage is sampling the output from the MDAC while the first stage is in its amplify/hold phase. At the end of the second stage sampling phase, the sampled voltage is quantized by an *m*-bit ADC, producing  $D_{fine}$ .  $D_{fine}$  is then passed through a digital gain stage with ideal  $G_d = G$  and combined with the coarse ADC output to produce the final (m+B) bit digital output,  $D_{out}$ . Although this example is only for two stages, this idea could be expanded to any number of arbitrary stages by adding an MDAC with its own amplify/hold phase to the second stage and replicating more stages. A high resolution ADC can be constructed from a series of low resolution ADCs by partitioning the conversion in this manner. For a pipeline with i stages, a latency of i - 1 cycles is introduced, but the cycle time is only limited by the longest stage conversion time.

#### 1.1.1 Residue Amplification

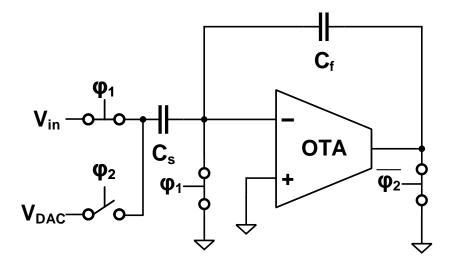

Figure 1.4 shows the first stage from Figure 1.2 with an n of one. The sum and gain stages are replaced with an ideal MDAC model. This particular MDAC topology is known as a non-fliparound architecture. A single-ended model is shown for simplicity. At the heart of the MDAC is an operational

Figure 1.4: Example MDAC

transconductance amplifier. For the purposes of this example, the OTA gain is assumed to be infinite, so that the voltage difference between the two OTA input terminals is zero. When the amplifier gain is less than infinity, static gain error is added to the MDAC output. For this reason, the closed-loop MDAC topology generally requires open-loop amplifier gains much larger than the desired closed loop gain.  $\phi_1$  and  $\phi_2$  are non-overlapping clock signals.  $\phi_1$  corresponds to the sample/conversion stage and  $\phi_2$  corresponds to the amplify/hold stage of the pipeline ADC.  $C_s$  is the sampling capacitors and  $C_f$  is the feedback capacitor. For the purposes of this example,  $C_s$  has a value of 2C and  $C_f$  has a value of C. When  $\phi_1$  is active, the input voltage,  $V_{in}$ , is sampled onto the sampling capacitors. The expression for the charge at node X at the end of  $\phi_1$ ,  $Q_{x,\phi_1}$  is:

$$Q_{x,\phi_1} = -2CV_{in} \tag{1.5}$$

At the end of  $\phi_1$ , the sub-ADC performs its conversion and connects the bottom plate of  $C_s$  to  $\pm \frac{V_{ref}}{2}$ . When  $\phi_2$  is active, the charge at node X,  $Q_{x,\phi_2}$ is:

$$Q_{x,\phi_2} = \begin{cases} -CV_{res,o} - CV_{ref} & \text{if } V_{in} > 0\\ -CV_{res,o} + CV_{ref} & \text{if } V_{in} \le 0 \end{cases}$$

(1.6)

where  $V_{res,o}$  is the amplified residue voltage. From charge conservation,  $Q_{x,\phi_1}$ and  $Q_{x,\phi_2}$  must be equal. Setting these quantities equal to each other and solving for  $V_{res,o}$  yields:

$$V_{res,o} = \begin{cases} 2V_{in} - V_{ref} = 2(V_{in} - \frac{V_{ref}}{2}) & \text{if } V_{in} > 0\\ 2V_{in} + V_{ref} = 2(V_{in} + \frac{V_{ref}}{2}) & \text{if } V_{in} \le 0 \end{cases}$$

(1.7)

Putting Equation 1.7 in terms of G and  $V_{res}$  from Figure 1.2, the voltage at the input of the m bit ADC is:

$$V_{res,o} = 2(V_{in} \pm \frac{V_{ref}}{2}) = GV_{res} = \frac{C_s}{C_f} V_{res}$$

(1.8)

From Equ. 1.8, the gain is set by the ratio of  $C_s$  to  $C_f$ . Passive components generally match each other well, so the MDAC has a well-defined gain that should be stable across PVT, assuming the OTA provides sufficient loop gain to minimize the static error at its inputs. Redundancy is a technique often used in pipeline ADCs to relax comparator offset requirements. To illustrate this, Figure 1.4 will be used. From Equations 1.1 and 1.7, the bound for the amplified residue output is:

$$|V_{res,o}| \le V_{ref} \tag{1.9}$$

From this equation, it can be seen that  $V_{res,o}$  is bound by the full-scale input range of the next stage ADC. Comparator offsets affect the decision levels of the sub-ADC, causing some residue voltages to exceed Equation 1.1. This will then cause  $V_{res,o}$  to exceed the input range of the next stage ADC. The use of redundancy increases the resolution in the stage sub-ADC without increasing the interstage MDAC gain. In this case, the effective stage resolution remains the same, but the maximum sub-ADC decision error decreases, thus allowing some additional headroom for comparator offsets. Most pipelined designs opt for either 1 bit or 1/2 bit redundancy. Adding an additional bit to the stage ADC in Figure 1.4 reduces the maximum input residue voltage by a factor of two, so the bound of  $V_{res,o}$  becomes:

$$|V_{res,o}| \le \frac{V_{ref}}{2} \tag{1.10}$$

With 1 bit redundancy, the MDAC can accommodate comparator offsets of up to 1/2 LSB without overloading the next stage ADC.

#### **1.2 SAR Operation**

SAR ADCs use a binary search algorithm to successively approximate the input voltage by comparing the input sampled voltage,  $V_{in}$  to a DAC output voltage,  $V_{DAC}$ . In many cases, the DAC is implemented using a capacitive charge redistribution method. Fig. 1.5 illustrates a two bit capacitive charge redistribution SAR ADC. A single-ended version of this design is shown for simplicity. In Fig. 1.5, the capacitor of size 2C is known as the most significant bit (MSB) capacitor and the first C is known as the least significant bit (LSB) capacitor. The second capacitor of size C is known as a dummy LSB capacitor. The signals  $d_1$  and  $d_0$  correspond to the digital outputs from the first and second conversion steps, respectively. The digital outputs are obtained from the output of the comparator. From the figure, the total capacitance of this ADC is 4C. A general expression for the total capacitance of an N bit SAR ADC with a unit capacitance of C is:

$$C_T = 2^N \cdot C \tag{1.11}$$

Equ. 1.11 shows that an increase in ADC resolution of 1 bit requires doubling the sampling capacitance. To perform a conversion, the ADC first samples the input. During this phase, the top plates of all capacitors are connected to  $V_{in}$  and the bottom plates are connected to  $V_{ref}$ . In the first conversion phase shown in Fig. 1.5(b), the 2C capacitor is switched from  $V_{ref}$  to 0, causing a change in voltage at  $V_x$  of  $0.5V_{ref}$ . The voltage at  $V_x$  is then compared to 0. For the case of Fig. 1.5, the sampled input voltage is less than  $0.5V_{ref}$ ,

Figure 1.5: (a) Example 2-bit SAR ADC (b) SAR ADC voltage waveforms so the comparator output will be 0. Since the comparator output is 0, the 2C capacitor will be reconnected to  $V_{ref}$  and the conversion will proceed by changing the C capacitor from  $V_{ref}$  to 0, causing a change on  $V_x$  of  $0.25V_{ref}$ . The comparator then fires to compare the  $V_x$  to 0. Each conversion proceeds in this manner until all bits are resolved. For an N bit ADC, N conversion steps are required to obtain the final digital output. This serialization of the conversion limits the achievable speed of this ADC topology. From Fig. 1.5, the SAR ADC only requires a CDAC, a comparator, and digital logic. Most of these blocks are digital or digital-like in nature, so they take advantage of the area, speed, and power benefits of technology scaling. As mentioned earlier, this fact does not hold as well for higher resolution ADCs, where the comparator and CDAC noise limit the overall performance. In this case, pipeline SAR

ADCs are an attractive option because they reduce the accuracy requirements of the SAR ADC to the sub-ADC resolution. This allows for large reductions in CDAC area and power, as well as large reductions in comparator power for noise-limited designs. The trade-off is the required residue amplification stage, which now sets most of the important performance parameters for the pipeline SAR ADC.

## Chapter 2

## Pipelined SAR ADC Reusing the Comparator as Residue Amplifier

#### 2.1 Introduction

Successive approximation register (SAR) analog-to-digital converters (ADCs) are very popular for medium resolution (8-10 bits) applications because of their mostly digital architecture and high power efficiency. For higher resolution at high speeds, pipelining becomes an attractive option to limit the capacitive digital-to-analog converter (CDAC) size and reduce the number of serial conversions per conversion cycle. The main drawback to this approach is the requirement of residue amplification between each stage. Traditional closed-loop residue amplifiers require large open-loop gains which are difficult to achieve in advanced processes. Moreover, these amplifiers consume static power, which limits the power efficiency when compared to a standard singlestage SAR architecture.

Many recent works have proposed alternatives to traditional closed-loop residue amplifiers. One option is to perform open-loop residue amplification, which greatly reduces the required amplifier gain at the cost of increased nonlinearity. This approach can require complex digital calibration [17] or lin-

earization techniques [32] and still consumes static power. Other recent works have proposed using dynamic amplifiers, or integrators, for residue amplification [27, 15, 24, 11]. Integrator-based amplifiers are attractive because they achieve high power efficiency for a given input-referred noise. One drawback of integrator-based amplifiers is that the maximum achievable gain is limited by transistor  $g_m/I_D$  and the voltage supply. Recent works have attempted to overcome this issue [24, 15], but the gain is either still limited [24], or additional gain requires increased timing complexity [15]. Another challenging issue for most residue amplifier architectures is the mismatch between comparator and amplifier offsets. Offset mismatch both increases the amplifier's input swing, increasing non-linearity, and can cause overranging in later stage ADCs. These effects are especially harmful in dynamic-amplifier based pipelined SAR ADCs because 1) the linearity of dynamic amplifiers is generally much more sensitive to input swing than closed-loop amplifiers and 2) the first-stage resolution is generally high in order to maintain the SAR's power efficiency and limit the amplifier input swing, thus reducing the LSB size and the effectiveness of gain redundancy. In general, either large devices or offset calibration techniques must be used in order to meet the offset matching requirements.

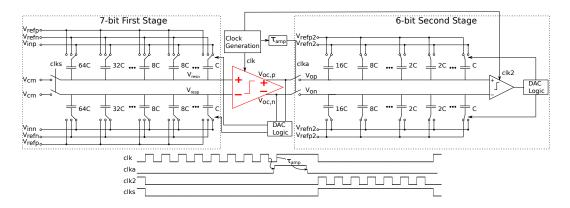

In this paper, we propose a novel pipelined SAR architecture, shown in Fig. 2.13. It addresses the aforementioned drawbacks of other dynamic amplifiers without adding any hardware complexity to the traditional SAR architecture by *reusing the first-stage comparator, a strongARM latch, as a residue amplifier.* This architecture maintains the noise filtering of an integrator as in [24], while adding a high-speed positive feedback gain phase. The achievable maximum gain is only limited by the ratio of supply voltage to input swing and the required second-stage linearity. The gain control only requires a simple tunable delay line. Since the amplifier and comparator are the same block, no calibration for offset mismatch needs to be done to limit input swing or prevent overranging. By properly partitioning the pipeline stages, the first-stage residue can be kept small enough that the amplifier does not require any non-linearity calibration.<sup>1</sup>

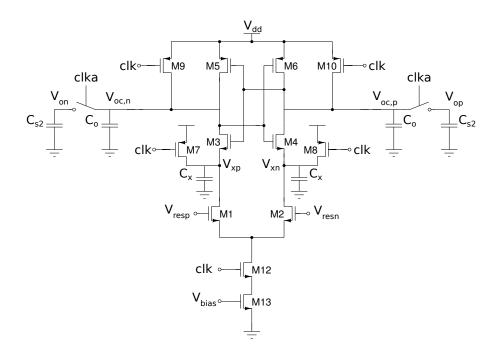

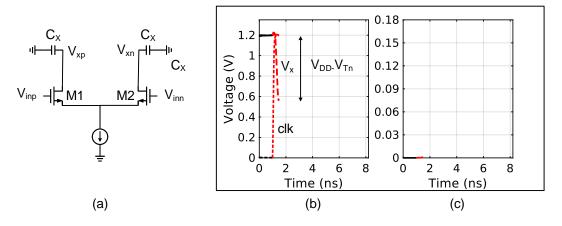

# 2.2 Residue Amplification Using a StrongARM Latch2.2.1 Basic Operation

The schematic of the proposed residue amplifier is shown in Fig. 2.1. The latch is very similar to that in [28], with an added current bias to improve the common-mode rejection of the amplifier. When the *clka* signal is low, the second stage SAR capacitance is disconnected from the amplifier and the amplifier behaves as a normal comparator. When *clka* is high, the amplifier transfers the residue to the second stage SAR with a gain that is proportional to the time *clka* is kept high,  $\tau_{amp}$ . The proposed amplifier operates in four phases: reset, internal integration, output integration, and regeneration. During the reset phase, *clk* is low and all comparator voltages,  $V_{op}$ ,  $V_{on}$ ,  $V_{xp}$ , and

<sup>&</sup>lt;sup>1</sup>This chapter is a partial reprint of the publication: Miguel Gandara, Wenjuan Guo, Xiyuan Tang, Long Chen, Yeonam Yoon, and Nan Sun, "A Pipelined SAR ADC Reusing the Comparator as Residue Amplifier," in *IEEE Custom Integrated Circuits Conference (CICC)*, 2017. I was the primary investigator and designer on this published work.

Figure 2.1: Proposed amplifier schematic.

Figure 2.2: (a) Amplifier equivalent schematic during internal integration (b) Single-ended waveforms (c) Differential output waveform

$V_{xn}$  are pulled to  $V_{DD}$ . Internal integration starts when clk switches from 0 to 1. Fig. 2.2 shows the equivalent circuit during internal integration and the

Figure 2.3: (a) Amplifier equivalent schematic during output integration (b) Single-ended waveforms (c) Differential output waveform

Figure 2.4: (a) Amplifier equivalent schematic during regeneration (b) Singleended waveforms (c) Differential output waveform

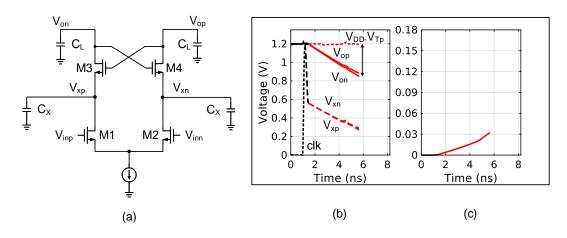

transient waveforms for the comparator voltages. During the internal integration phase, the differential current through M1 and M2 is integrated on the capacitance at nodes  $V_{xp}/V_{xn}$ ,  $C_x$ . Once the  $V_x$  node voltages decrease enough to turn on transistors M3/4, the output integration phase begins. Fig. 2.3 shows the equivalent circuit and transient waveforms during this phase. The differential current from the input pair is integrated onto the output load  $C_L$ , the parallel combination of the second-stage DAC capacitance,  $C_{s2}$ , and the comparator parasitic capacitance,  $C_o$ . M3 and M4 act as cascodes during this phase, with the  $V_{xp}/V_{xn}$  nodes following the  $V_{op}/V_{on}$  nodes to maintain adequate overdrive voltage to buffer the input pair current. Output integration continues until the voltage at nodes  $V_{op}/V_{on}$  drops below the threshold voltage of PMOS transistors M5/6, at which point the regeneration phase begins. The capacitance at the output nodes is generally much larger than the internal capacitance at the  $V_x$  nodes, so this phase is usually much longer than internal integration and most integration gain is achieved during this phase. At the end output integration, the integration gain  $G_{int}$  will be [3]

$$G_{int} \approx \left(\frac{g_m}{I_D}\right)_{1,2} \left\{ V_{T5,6} + \frac{C_X}{C_{s2} + C_o} \left(V_{T5,6} + V_{T3,4}\right) \right\}$$

(2.1)

Fig. 2.4 shows the equivalent circuit and transient waveforms during regeneration. Once the PMOS devices turn on, the amplifier acts as a positive feedback latch until clk is deasserted. At the end of the regeneration phase, the total amplifier gain, G is

$$G \approx G_{int} \cdot e^{T_{regen}/\tau} \tag{2.2}$$

where  $T_{regen}$  is the total regeneration time and  $\tau$  is the regeneration time constant, given by

$$\tau \approx \frac{C_{s2} + C_o}{g_{m5,6}} \tag{2.3}$$

Fig. 2.5 shows the amplifier gain as a function of time. An extrapolated version of the integration gain is shown as well to highlight the speed advantage of

the positive feedback stage. For a gain of 32, adding positive feedback to the amplifier increases the speed by more than two times.

Figure 2.5: Simulated amplifier gain (with extrapolated integration curve)

#### 2.2.2 Noise

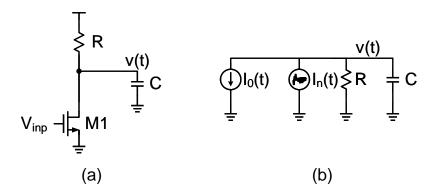

Most amplifier noise analysis relies on the assumption that all node voltages are in a steady state and their RMS noise does not change with time. For dynamic circuits, this assumption does not hold, as the RMS noise and gain are both a function of time. In order to calculate the noise for dynamic circuits, expressions utilizing stochastic differential equations must be used [6]. In order to calculate the amplifier noise during the integration and regeneration stages, the time-domain noise of a common-source amplifier with RC load during settling can first be calculated. Fig 2.6 shows the half-circuit of a differential common-source amplifier and its noise model.  $I_0(t)$  represents the transconductance of M1 and  $I_n(t)$  represents the combined noise current of M1 and the resistor R. The single-sided noise current power spectral density

Figure 2.6: (a) Common-source amplifier with RC load half-circuit (b) Noise model

(PSD) of  $I_n$  is

$$\overline{I_n^2} = 2kT(\frac{1}{R} + \gamma g_m) \tag{2.4}$$

where  $\gamma$  is the transistor white noise factor and  $g_m$  is the transconductance of M1. The differential equation for the voltage at node v(t) is

$$C\frac{dV}{dt} = -\frac{V}{R} + I_0(t) + I_n(t)$$

(2.5)

v(t) will have both a signal and noise component, expressed as

$$v(t) = S(t) + N(t)$$

(2.6)

By separating the signal and noise components and rearranging terms, the noise component is the stochastic differential equation

$$dN = -\frac{N}{RC} + \frac{I_n(t)}{C}dt$$

(2.7)

This is a form of the Langevin equation. By using the general solution of the Langevin equation, the noise power during settling can be calculated as

$$E(v^{2}(t)) = exp\left(\frac{-2t}{RC} \cdot E(v_{0}^{2})\right) + \frac{kT(1+\gamma g_{m}R)}{C} \cdot \left(1 - exp\left(\frac{-2t}{RC}\right)\right) \quad (2.8)$$

where  $E(v_0^2)$  is the initial noise voltage at v(t). If C is completely reset at the beginning of settling, which will be the case for the proposed amplifier, the initial noise will be

$$E(v_0^2) = \frac{kT}{C} \tag{2.9}$$

For complete settling, t >> RC, and Equ. 2.8 reduces to

$$E(v_t^2) = \frac{kT(1 + \gamma g_m R)}{C}$$

(2.10)

This result matches the noise calculated from traditional PSD-based noise analysis for completely settled circuits. Integration can be treated as a special case of Fig. 2.6 with  $R = \infty$  and Equ. 2.8 reduces to

$$E(v_t^2) = \frac{kT}{C} + \frac{2kT\gamma g_m}{C^2} \cdot t$$

=  $\frac{kT}{C} \cdot (1 + \gamma G_{int})$  (2.11)

and the input-referred integration noise is

$$\overline{v_{in}^2} = \frac{kT}{C} \cdot \left(\frac{1}{G_{int}^2} + \frac{\gamma}{G_{int}}\right)$$

(2.12)

This equation shows that the input-referred noise improves with larger integration gain. The regeneration case is also a special case of Fig. 2.6 with  $R = -1/g_m$ . Plugging in  $-1/g_m$  for R and calculating the input-referred noise during regeneration yields

$$\overline{v_{in}^2} = \frac{kT\gamma}{C} + v_0^2 \tag{2.13}$$

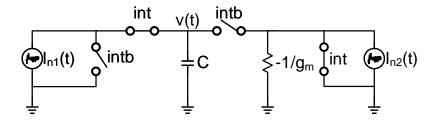

In the regeneration case, both the signal and noise power scale by  $G_{regen}^2$  so the input-referred noise does not depend on gain. The noise models during integration and regeneration are combined in Fig. 2.7 to model the noise of the proposed amplifier that combines integration and regeneration. Initially, the switches connected to *int* are closed, and the noise from the input differential pair is integrated onto C. At the end of integration, the *int* switches open and the *int* switches close and regeneration begins. Equ. 2.11 gives the noise at the end of the integration phase. To calculate the noise at the end of regeneration,  $v_0^2$  is set to the noise at the end of the integration phase and the total input-referred noise will be

$$\overline{v_{in}^2} = \frac{kT}{C} \cdot \left(\frac{1+\gamma}{G_{int}^2} + \frac{\gamma}{G_{int}}\right)$$

(2.14)

For sufficiently large integrator gain, the additional noise penalty incurred from the regeneration stage should be small, allowing for a large increase in amplification speed without a large loss in SNR.

Figure 2.7: Noise model for proposed amplifier with integration and regeneration phases

The proposed amplifier was simulated across operating conditions in order to validate the accuracy of the noise model. In Fig. 2.8, the input pair's  $G_m/I_D$  was swept and its noise was measured. Since integration gain is linearly proportional to  $G_m/I_D$ , the noise should reduce by the square root of  $G_m/I_D$ . The dashed blue line shows extrapolated noise calculations based on this relationship and the noise value for the maximum  $G_m/I_D$ . The simulation results generally track the calculation, and the maximum error is less than 10%. The

Figure 2.8: Proposed amplifier input-referred noise vs.  $G_m/I_D$

time-domain behavior of the amplifier's noise was also characterized. Fig. 2.9 shows the calculated and simulated input-referred noise across amplification time. Noise is calculated by using transient operating points and the loading conditions of the simulated amplifier to obtain the necessary terms in Equ. 2.14. During integration, the input-referred noise decreases proportional to  $\sqrt{t}$  and once regeneration begins the input-referred noise becomes constant, matching the expected behavior.

By adding a tail current source, the sensitivity of the amplifier's noise to

Figure 2.9: Comparison between calculated and simulated input referred noise for the proposed amplifier

its input common-mode is greatly reduced. The addition of the current source helps to stabilize the input pair's  $G_m/I_D$  across the input common-mode, maintaining a relatively constant integration gain and therefore a relatively constant input-referred noise. Fig. 2.10 plots the amplifier noise with and without the tail current source. Without the tail current source, the noise varies by more than two times across a 200 mV input common-mode range. Adding the current source reduces that variation to approximately 20% over the same input-common mode range. In high speed systems, the ADC is typically driven by a low-impedance source follower. The output voltage of the source follower can vary along with its threshold voltage, which can easily vary by 200 mV across process and temperature, so the proposed amplifier's addition of a tail current source can greatly reduce the noise penalty across input common-mode range.

Figure 2.10: Noise variation across common-mode

One key advantage of this amplifier topology is that its operation can easily be tuned for noise and speed requirements. In the integration phase, input-referred noise is inversely proportional to integration time, which is controlled by the bias current and load capacitance [24]. In the regeneration phase, input-referred noise is inversely proportional to load capacitance and is attenuated by the integration gain. For low speed and low noise designs, the integration time can be maximized by reducing the bias current. For highspeed designs with less stringent noise requirements, the bias current can be increased to minimize integration time. Whenever possible, the load capacitance should be minimized so that the regeneration phase can be as fast as possible while still meeting noise requirements. For a given integration time, the input pair's  $g_m/I_D$  should be large so that the noise contribution from the regeneration phase is minimized. By carefully controlling bias current and load capacitance, this topology can be used across a wide range of noise and speed requirements.

#### 2.2.3 Linearity

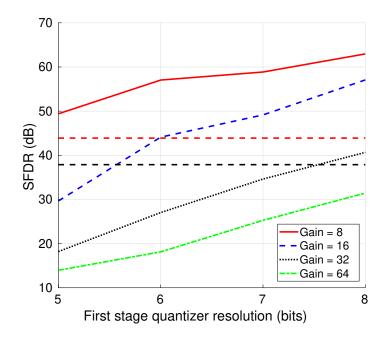

The final major consideration for this amplifier topology is its linearity. In general, the integration phase should be more linear than the regeneration phase, since its gain changes linearly with  $g_m$ , whereas the regeneration gain changes exponentially with changes in  $g_m$ . By maximizing the integrator gain, and therefore the input pair's  $G_m/I_D$ , the linearity should also be maximized. Fig. 2.11 plots the simulated typical corner SFDR across input pair  $G_m/I_D$ for the proposed amplifier. The general trend is that larger integration gain results in better linearity, which matches expectation. Another system-level consideration for the amplifier linearity is the first-stage quantizer resolution. Larger first-stage quantizer resolution results in a smaller input swing at the amplifier input, which results in improved amplifier linearity. Larger first-stage quantizer resolutions also generally imply lower speed, since extra conversions are required, so the first-stage quantizer resolution should be set to ensure linearity targets are met without unnecessarily slowing down the conversion speed. Fig. 2.12 plots the worst case SFDR for various first stage quantizer

Figure 2.11: Proposed amplifier SFDR vs.  $G_m/I_D$

resolutions and gains from 8 to 64. The dashed horizontal lines represent 6-bit and 7-bit linearity for the black and red lines, respectively. This plot shows that a gain of 64 will not have sufficient linearity for most pipeline designs. The gain of 16 can easily achieve 7-bit linearity with a moderate first-stage resolution of 6 bits. The amplifier can also feasibly achieve a gain of 32, but it requires a first-stage resolution of 8 bits for reasonable linearity. With a well-designed integrator stage, the proposed amplifier can achieve reasonable linearity with only a moderate first-stage resolution.

Figure 2.12: Proposed amplifier SFDR vs. input swing 2.3 Pipeline ADC Architecture

Figure 2.13: Proposed pipeline ADC architecture and timing diagram.

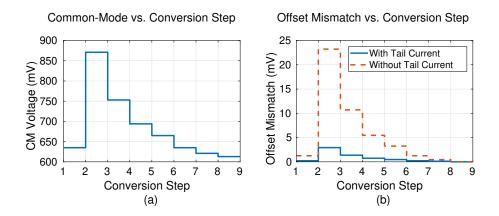

The proposed amplifier from Section 2.2 was integrated into the 12-bit, 10 MS/s two-stage SAR-based pipelined ADC shown in Fig. 2.13. The firststage resolution of 7 bits was chosen to reduce the amplifier input swing and eliminate the need for gain non-linearity calibration. Both SAR sub-ADCs use the bidirectional single-sided switching technique from [2] in order to minimize reference energy and reduce the required DAC capacitance. Redundant capacitors are added to overcome the common-mode voltage shifts that occur while using the bidirectional switching scheme. The redundant capacitors ensure the critical conversion cycle will happen after the common-mode voltage shifts become small. By doing this, the offset matching between the comparator operation and amplifier operation is maintained. The amount of required redundancy is significantly reduced by the tail current source in the proposed amplifier. Fig. 2.14(a) shows the common-mode variation across conversion step for the bidirectional switching scheme. Fig. 2.14(b) shows the 1-sigma offset mismatch caused by the common-mode variation for the proposed amplifier with and without the tail current source. Adding the tail current source reduces the maximum offset-mismatch from 23 mV to 3 mV, a reduction of more than 7 times. A voltage-controlled delay line (VCDL) is used to control the amplification time and its delay is tuned to a gain of 32.

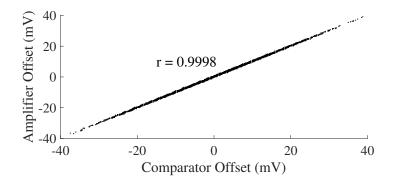

Sharing the amplifier and comparator has many benefits. First, no additional amplifier hardware is needed to enable residue amplification, reducing the system hardware complexity. Second, no calibration for offset mismatch needs to be done and the comparator input pair can be sized only to meet noise requirements without regard for offset. With standard residue amplifiers, a mismatch between the amplifier and comparator offsets will cause an

Figure 2.14: (a) Common mode variation across ADC conversion steps (b) Offset mismatch across ADC conversion steps

increase in the input swing seen by the amplifier. This increased output swing is especially harmful for dynamic open-loop amplifiers, where non-linearity is usually very sensitive to input swing. In the proposed amplifier topology, the offset seen during comparator operation and amplifier operation are the same, so even a very large offset will have no effect on the ADC functionality. To illustrate this point, Figure 2.15 shows the offset in comparator and amplifier mode from a 10000 run Monte Carlo simulation, showing that the offsets in both modes are almost perfectly correlated. Finally, since the amplifier sees the much larger second-stage DAC capacitance in amplification phase, the noise and speed can be optimized separately for comparator and amplifier operating modes by changing the ratio of comparator parasitic capacitance to second-stage DAC capacitance. Table 2.1 shows a comparison of important performance parameters for the proposed amplifier when it is in comparator and amplifier operation. When in comparator mode, the noise is only required to match the first-stage resolution, so the comparator can work in a high speed, high noise mode. Once the second stage DAC capacitance is connected, the amplifier works in a lower speed, lower noise mode. Additionally, Table 2.1 shows that from an energy perspective, the amplifier operation is approximately equivalent to firing the comparator an extra two times, highlighting the power efficiency of the proposed amplification method. Sharing the amplifier and comparator reduces hardware complexity, eliminates offset calibration, and still enables separate optimization between comparator and amplifier operating modes.

Figure 2.15: Amplifier offset vs. comparator offset and correlation coefficient for a 10000 point Monte Carlo simulation

|                                      | Comparator | Amplifier |

|--------------------------------------|------------|-----------|

|                                      | mode       | mode      |

| Input-Referred Noise $(\mu V_{rms})$ | 344        | 101       |

| Integration Time (ns)                | 0.98       | 5.2       |

| Regeneration Time Constant (ns)      | 0.19       | 1.8       |

| Offset $(mV_{rms})$                  | 10.67      | 10.71     |

| Energy per Operation (fJ)            | 86         | 148       |

Table 2.1: Performance comparison between comparator and amplifier operating modes.

#### 2.4 Measurement Results

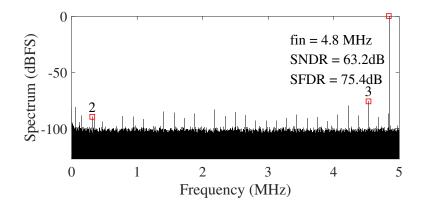

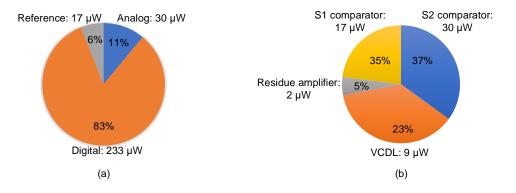

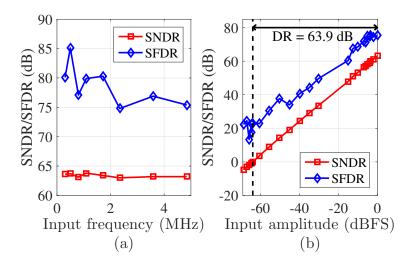

The ADC described in Section 2.3 was fabricated in 130 nm CMOS technology. Fig. 2.16 shows the die photo and layout of the chip. Capacitor mismatch was calibrated in the foreground with a single input. For this proof of concept, the VCDL delay was calibrated to achieve the desired gain in the foreground with a single input, but this work could easily be extended to place the delay-line in an interstage gain background calibration loop to ensure robustness against process, voltage, and temperature (PVT) variation. Fig. 2.17 shows the measured output spectrum with a Nyquist input. The measured SNDR and SFDR at Nyquist was 63.2 dB and 75.4 dB, respectively, leading to a 10.2-bit ENOB. The ENOB was mostly limited by the jitter of the voltage controlled delay line. The total measured power was 280  $\mu$ W, of which 83% was digital power. Fig. 2.19 shows the SNDR/SFDR across input frequency and input amplitude. The dynamic range of the ADC was measured to be 63.9 dB. These numbers translate to a Schreier FoM of 166.4

dB. As this work is mainly a proof of concept, much optimization is possible to further improve the performance. Additionally, this architecture uses only scaling-friendly components and consumes only dynamic power. Fabricating this design in a more advanced process than 130 nm would provide significant performance benefits. Table 2.2 shows that this prototype achieves the largest interstage gain among other state of the art dynamic amplifier works.

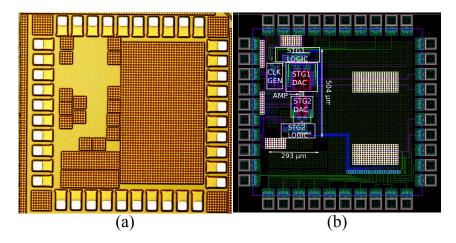

Figure 2.16: ADC (a) die photo and (b) layout.

Figure 2.17: Measured ADC output spectra with 32768 points.

Figure 2.18: (a) Measured power breakdown (b) Analog and delay line power breakdown

Figure 2.19: Measured SNDR and SFDR vs. (a) input frequency and (b) input amplitude.

| Table | 2.2. | Performance | e Comparison |  |

|-------|------|-------------|--------------|--|

| Table | 2.2. | 1 CHOIMANCO | Comparison   |  |

|                         | [24]     | [27]     | [23]      | [11]     | This work |

|-------------------------|----------|----------|-----------|----------|-----------|

| Process (nm)            | 28       | 40       | 65        | 90       | 130       |

| Architecture            | Pipe SAR | Pipe SAR | Pipe SAR  | Pipeline | Pipe SAR  |

| Res. Amp                | Dynamic  | Dynamic  | Static    | Dynamic  | Dynamic   |

| Architecture            |          |          | open-loop |          |           |

| Interstage Gain         | 16       | 4        | 16        | 3        | 32        |

| Supply Voltage (V)      | 1.0/1.8  | 1.1      | 1.0/1.2   | 0.5/0.55 | 1.2       |

| Sampling Rate (MS/s)    | 80       | 250      | 160       | 160      | 10        |

| SNDR (Nyq) (dB)         | 66       | 56       | 66.2      | 38       | 63.2      |

| ENOB (bit)              | 10.7     | 9.0      | 10.7      | 6.0      | 10.2      |

| Power (mW)              | 1.5      | 1.7      | 11.1      | 2.43     | 0.28      |

| HF Walden FoM (fJ/step) | 11.5     | 13.2     | 41.6      | 234.0    | 23.7      |

| HF Schreier FoM (dB)    | 170.3    | 164.7    | 164.8     | 143.2    | 166.4     |

## Chapter 3

# A 172dB-FoM Pipelined SAR ADC Using a Regenerative Amplifier with Self-Timed Gain Control and Mixed-Signal Background Calibration

#### 3.1 Introduction

With technology scaling, open-loop dynamic integrators have become an attractive choice for residue amplifiers of pipelined SAR ADCs [24, 27, 15, 11]. A dynamic integrator has two key merits. First, it consumes only dynamic power (no static power), and thus, is much more power efficient than a traditional closed-loop amplifier. Second, it has low noise; in fact, it can be proved that an integrator achieves the lowest noise for a given power budget. Despite these merits, it brings challenges: 1) its maximum achievable gain is limited by the power supply voltage and the transistor  $g_m/I_D$ , and is typically less than 10; 2) it requires accurate offset calibration to match the offset of the integrator with the SAR comparator [27, 15, 24]. Offset mismatch increases the amplifier input swing and can cause significant linearity degradation for a dynamic integrator, as its linearity is much more sensitive to the input swing than a closed-loop amplifier; 3) its gain is linearly proportional to the integration time, resulting in a strict trade-off between the amplifier gain and speed. To address these issues, the authors proposed in Ch. 2 to reuse the strongARM latch comparator in the SAR as a dynamic amplifier, thus removing the need for any offset calibration between the SAR comparator and the residue amplifier. It also naturally combines a front-end integrator, to achieve high noise efficiency, with a backend regenerative positive feedback stage, to attain high gain at high speed with negligible noise penalty as shown in Fig. 3.1.

Figure 3.1: Block diagram of a regenerative amplifier in Ch. 2.

Furthermore, this architecture automatically realizes load switching to dynamically adjust the comparator noise and power. When it operates as the SAR comparator, the load is small inverter buffers that drive the SAR logic, and thus, is low power but high noise. When it acts as a residue amplifier, the load is a much larger second-stage SAR input capacitor, and thus, its input referred noise is reduced, which ensures an overall high ADC SNR.

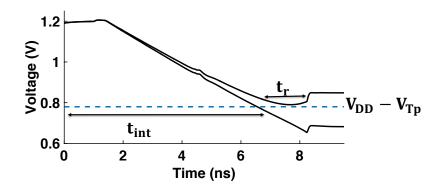

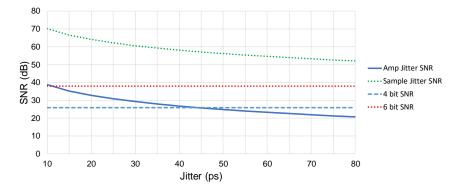

Nevertheless, there are two critical challenges of dynamic amplifiers that the work of Ch. 2 has not addressed: 1) the amplifier gain depends on time, and thus, it requires an accurate and low jitter clock to control the amplification time, but the clock generation is nontrivial and can be power consuming; 2) the amplifier gain, relying on  $g_m$  and time, is sensitive to PVT variation. The clock requirement is especially stringent for amplifiers utilizing regeneration Ch. 2, as the gain increases exponentially with time instead of linearly. In Ch. 2, a voltage-controlled delay line (VCDL) was used to control the gain, but its high jitter caused large gain variations, resulting in ADC SNR degradation. Moreover, the VCDL delay did not track the amplifier gain across PVT variation. Digital background calibration can be used to sense the analog gain variation and adjust the digital gain to match it [24]. This technique improves ADC SNDR, but it does not address the root cause of the problem: the amplifier gain still varies with PVT. Amplifier gain variation causes several issues. First, extra redundancy has to be added to ensure that the largest possible gain under PVT variation does not overload the second pipelined stage. Second, when the amplifier gain drops, the noise contribution from the later pipelined stages increases, causing SNR degradation that cannot be mitigated by digital calibration. Third, the digital gain is no longer a power of 2, requiring a tunable fractional multiplier that increases power and design complexity. Besides digital background calibration, other techniques to tackle gain PVT variation use interpolation [11] or replica [8], but these techniques often require power that is comparable to the power of the dynamic amplifier.

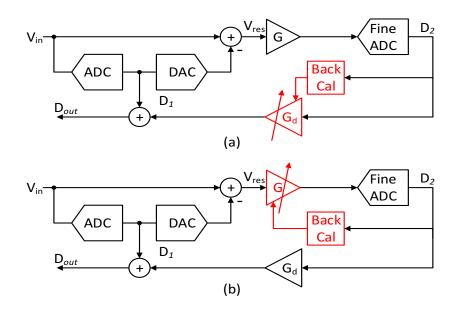

This work introduces a low-power self-timed gain control block that provides enhanced robustness to PVT variation. The gain control block is combined with a mixed-signal background calibration loop. Fig. 3.2(a) shows the ADC block diagram with the classic gain calibration, where the digital gain is tuned to match a *varying* analog gain. By contrast, Fig. 3.2(b) shows the proposed scheme, where the analog gain is tuned to match a *constant* digital gain. This scheme takes advantage of the unique feature of dynamic amplifiers, that the gain can be adjusted simply by changing the amplification time. This removes the need for extra redundancy to account for increased gain across PVT, and ensures that the analog gain is always large enough to suppress the second stage non-idealities. Additionally, it does not require a fractional digital multiplier running at the ADC sampling rate, as the analog gain can be maintained to be a power of 2 and the digital scaling can be accomplished with a simple bit shift. A prototype in 130nm CMOS validates the proposed techniques and achieves a 4 times power efficiency increase compared to Ch. 2.

This chapter is organized as follows. Sec. 3.2 describes the proposed gain control block. Sec. 3.3 discusses the proposed mixed-signal calibration. Sec. 3.4 describes the pipelined SAR ADC architecture with self-timed gain control and mixed-signal calibration. Sec. 3.5 shows the measured results.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>This chapter is a partial reprint of the publication: Miguel Gandara, Paridhi Gulati, and Nan Sun, "A 172dB-FoM Pipelined SAR ADC Using a Regenerative Amplifier with Self-Timed Gain Control and Mixed-Signal Background Calibration," in *IEEE Asian Solid-State Circuits Conference (A-SSCC)*, 2017. I was the primary investigator and designer on this published work.

Figure 3.2: Pipelined ADC with (a) digital gain calibration (b) mixed-signal gain calibration

#### 3.2 Proposed Self-Timed Gain Control