Copyright by Ching-Pei Lin 2021 The Dissertation Committee for Ching-Pei Lin certifies that this is the approved version of the following dissertation:

# Mitigating Bank Conflicts in Main Memory via Selective Data Duplication and Migration

Committee:

Yale Patt, Supervisor

Derek Chiou

Mattan Erez

Emmett Witchel

Chris Wilkerson

# Mitigating Bank Conflicts in Main Memory via Selective Data Duplication and Migration

by

Ching-Pei Lin

### DISSERTATION

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN May 2021

## Acknowledgments

There are many people to thank.

First and foremost, my family. My father, who has been a bedrock in my life through all the ups and downs. My brother, with whom there are so many things that only he can understand. My stepmom, who has been nothing but loving and nurturing ever since she joined our family. My late mother and grandparents, who all shaped me into who I am today. All my aunts, uncles, and cousins, with whom I have shared so many joyous and sad moments.

Next, I wish to thank all HPS members with whom I overlapped.

Jose, for his encyclopedic knowledge of all things computer-related and always calm demeanor. Khubaib, for many great conversations, and a very memorable reunion at Derek's house. Veynu, for always beating me in squash, and for teaching me about GPUs. Carlos, for many social outings, squash matches, heartfelt advice, and an incredible lunch atop Google Manhattan. Rustam, for many dinners together, and for being the first to show me what research really entails.

Milad, for always being helpful, insightful and confident. Faruk, for your astute intuitions, and for countless priceless moments throughout the years. Stephen, for daily conversations and explanations on just about every topic conceivable, and for teaching each other how to do research. Siavash, for co-inventing an entire genre of humor with me, for educating me on machine learning and C++, and for letting me vent to you. Ali, for putting up with my nonsense, and for being someone I can talk DRAM with within the group. Aniket, for taking part in the heroic push to get Scarab working with 64 bit executables right after joining the group. Chester, for taking on the mantle of 460N TAing guru.

Thank you to the other architecture students that I overlapped with: Nick, Haishan, Esha, Sangkug, Yongkee, Majid, Wenqi, Austin, Chirag, Dan, Tian, Alex, Sabine, Mochamad, Kishore, and Kamyar. I always felt a special fellowship among us.

Thank you to the many amazing friends I have met since coming to Austin. There are too many to name, but I will try: Bill, Sharon, Joe, Janet, Vincent, Wei-Jin, Hudson, Joanne, Vera, Clemens, Dara, Dominique, Leah, Yina, Weiyi, Henry, Fiona, Ben, Hope, and Jordy. Thank you for many wonderful moments.

Thank you to all my friends from Canada for still keeping in touch: Fraser, Mark, Derek, Tereza, Robyn, Julia, Josh, Jonny, Will, Leanne, Allison, Ken, Michael, Ivan, Yatin, Heidi, Yifan, Marguerite, James, Aric, and Matt. Special thanks to the Thurns, the Hills, the Browns, the deBruyns, and the Tardibuonos for always treating me like family. And a special note to Yatin: who would have thought back in 2006 that we would both end up doing PhDs in computer architecture? Thank you for being such a great friend all these years, and I look forward to visiting you in Ann Arbor!

Thank you to Rob Chappell, Philip Emma, Hillery Hunter, Doug Carmean, and Mike Shebanow for making my summer internships happen. I learned so much on those internships.

Thank you to all the members of my committee, whose feedback helped strengthen this dissertation. I especially wish to thank Mattan and Derek for helping out in the aftermath of Winter Storm Uri.

Finally, none of this would have been possible without the support and encouragement of my advisor, Dr. Yale Patt. Thank you for teaching me the importance of sound fundamentals and effective communication, and for being incredibly patient with me the entire PhD.

# Mitigating Bank Conflicts in Main Memory via Selective Data Duplication and Migration

by

Ching-Pei Lin, Ph.D. The University of Texas at Austin, 2021

SUPERVISOR: Yale Patt

Main memory is organized as a hierarchy of banks, rows, and columns. Only data from a single row can be accessed from each bank at any given time. Switching between different rows of the same bank requires serializing long latency operations to the bank. Consequently, memory performance suffers on bank conflicts when concurrent requests access different rows of the same bank.

Many prior solutions to the bank conflict problem required modifications to the memory device and/or the memory access protocol. Such modifications create hurdles for adoption due to the commodity nature of the memory business. Instead, I propose two new runtime solutions that work with unmodified memory devices and access protocols. The first, Duplicon Cache, duplicates select data to multiple banks, allowing duplicated data to be sourced from either the original bank or the alternate bank, whichever is more lightly loaded. The second, Continuous Row Compaction, identifies data that are frequently accessed together, then migrates them to non-conflicting rows across different banks.

To limit the data transfer overhead from data duplication and migration, only select data are duplicated/migrated. The key is to identify large working sets of the running applications that remain stable over very long time intervals, and slowly duplicate/migrate them over time, amortizing the cost of duplication/migration. In effect, the set of duplicated/migrated data form a cache within main memory that captures large stable working sets of the application.

# Table of Contents

| Acknow  | wledg  | ments                                                                                | iv  |

|---------|--------|--------------------------------------------------------------------------------------|-----|

| Abstra  | ct     |                                                                                      | vii |

| List of | Table  | es                                                                                   | xiv |

| List of | Figur  | es                                                                                   | xv  |

| Chapte  | er 1.  | Introduction                                                                         | 1   |

| 1.1     | The F  | Problem                                                                              | 1   |

| 1.2     | What   | Has Been Done                                                                        | 1   |

| 1.3     | Contr  | ibution                                                                              | 2   |

| 1.4     | Thesis | s Statement                                                                          | 5   |

| 1.5     | Disser | tation Organization                                                                  | 5   |

| Chapte  | er 2.  | Background and Motivation                                                            | 6   |

| 2.1     | DRAM   | M Organization and Operations                                                        | 7   |

|         | 2.1.1  | Channel Bandwidth                                                                    | 7   |

|         | 2.1.2  | Rank, Bank Group, and Bank Level Parallelism                                         | 9   |

|         | 2.1.3  | Row Buffer Locality and Bank Conflicts                                               | 11  |

|         | 2.1.4  | Memory Timing                                                                        | 13  |

|         | 2.1.5  | Memory Scheduling and<br>Duplicon Cache Motivating Example                           | 17  |

|         | 2.1.6  | Physical-to-DRAM Address Mapping and<br>Continuous Row Compaction Motivating Example | 20  |

|         | 2.1.7  | The Alternative: Tweaking the DRAM Device                                            | 27  |

|         |        | 2.1.7.1 Drawbacks of Modifying DRAM                                                  | 29  |

| Chapt | er 3. | Main Memory Caches                                                 | 31 |

|-------|-------|--------------------------------------------------------------------|----|

| 3.1   | Tag a | nd Data Store                                                      | 31 |

| 3.2   | Data  | Store                                                              | 33 |

|       | 3.2.1 | Reserving Physical Memory for Cache Data Store                     | 33 |

| 3.3   | Tag S | Store                                                              | 35 |

|       | 3.3.1 | Serial vs. Parallel Tag and Data Accesses                          | 35 |

|       | 3.3.2 | Line Size and Sectoring                                            | 35 |

| 3.4   | Mitig | ating Cache Data Transfer Overhead                                 | 38 |

|       | 3.4.1 | Device Modifications to Support<br>High Bandwidth Internal Copying | 40 |

|       | 3.4.2 | Infrequent Replacements and Resulting Challenges                   | 41 |

|       | 3.4.3 | Using Less Bandwidth Per Replacement                               | 42 |

|       |       | 3.4.3.1 Lazy vs. Eager Copying                                     | 42 |

|       |       | 3.4.3.2 Write-Through vs. Writeback Cache                          | 46 |

|       |       | 3.4.3.3 Tracking Dirty Bits                                        | 48 |

|       | 3.4.4 | Limiting Replacement Frequency                                     | 49 |

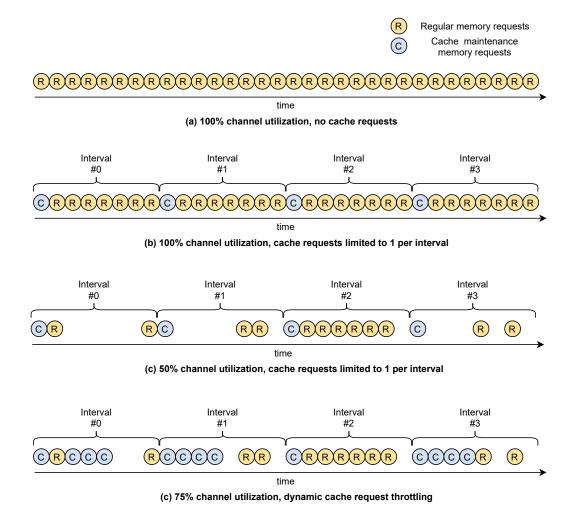

|       |       | 3.4.4.1 Explicit Copying Throttling                                | 49 |

|       |       | 3.4.4.2 Implicit Usefulness Tracking                               | 56 |

|       | 3.4.5 | Choosing the Right Data To Cache                                   | 57 |

|       |       | 3.4.5.1 Access Frequency $\ldots$ $\ldots$ $\ldots$ $\ldots$       | 59 |

|       |       | 3.4.5.2 Access Cost/Benefit $\ldots \ldots \ldots \ldots \ldots$   | 59 |

|       |       | $3.4.5.3$ Criticality $\ldots$                                     | 60 |

|       |       | 3.4.5.4 Temporal Correlation                                       | 60 |

| 3.5   | Coher | rence                                                              | 61 |

| 3.6   | Sumn  | nary                                                               | 61 |

| Chapt | er 4. | Duplicon Cache                                                     | 63 |

| _     |       | ziew                                                               | 63 |

| 4.2   |       | ration                                                             | 65 |

| 4.3   |       | enge (I):                                                          | 00 |

| 2.0   |       | nizing Tag Store Overhead                                          | 69 |

|       | 4.3.1 | Set-Associativity                                                  | 69 |

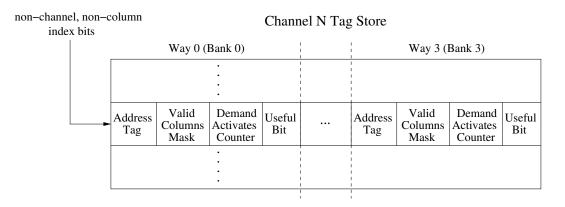

|       | 4.3.2 | The Tag Store                                                      | 72 |

| 4.4   |       | enge (II):<br>ifying the Most Suitable Data for Duplication                 | 74  |

|-------|-------|-----------------------------------------------------------------------------|-----|

|       |       | Demand Activates Filtering                                                  | 75  |

| 4.5   |       | enge (III):                                                                 | 10  |

| 4.0   |       | nizing Data Movement Overhead                                               | 75  |

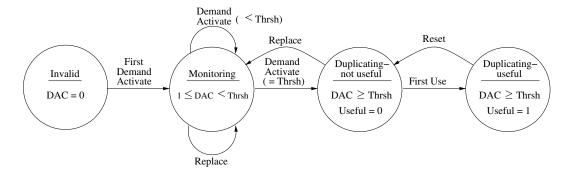

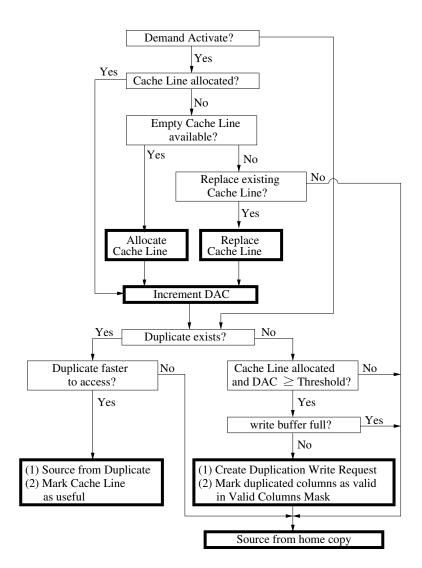

|       | 4.5.1 | Usefulness Tracking                                                         | 76  |

|       | 4.5.2 | Probabilistic Replacement                                                   | 77  |

| 4.6   |       | enge (IV):<br>ring Data Coherence and Correctness                           | 79  |

| 4.7   | Evalu | ation                                                                       | 81  |

|       | 4.7.1 | Methodology                                                                 | 81  |

|       | 4.7.2 | Performance                                                                 | 84  |

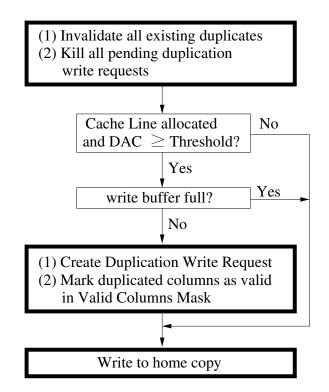

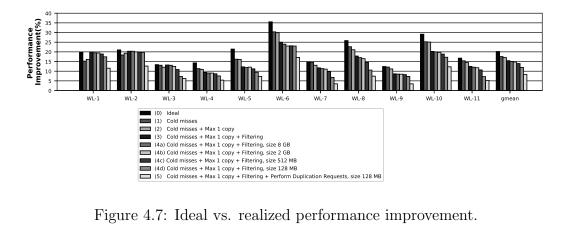

|       |       | 4.7.2.1 Ideal vs. Realized Performance                                      | 84  |

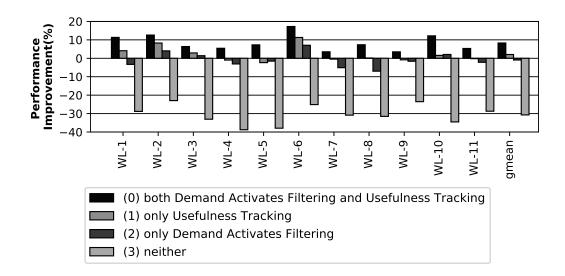

|       |       | 4.7.2.2 Effectiveness of Demand Activates Filtering and Usefulness Tracking | 87  |

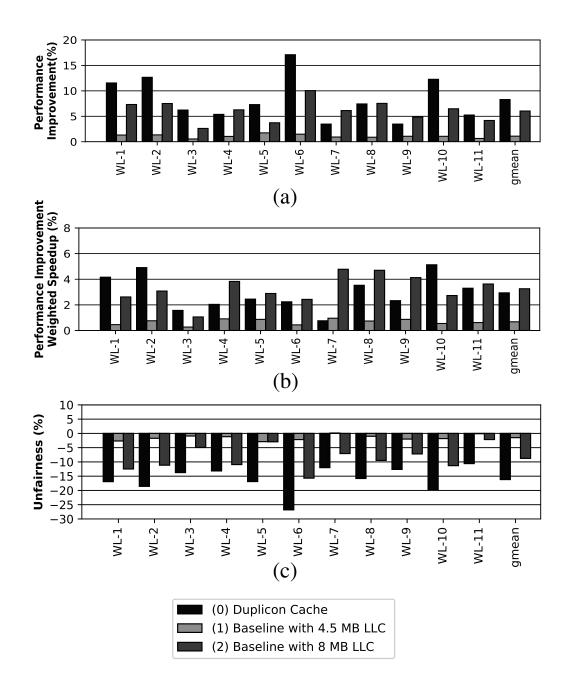

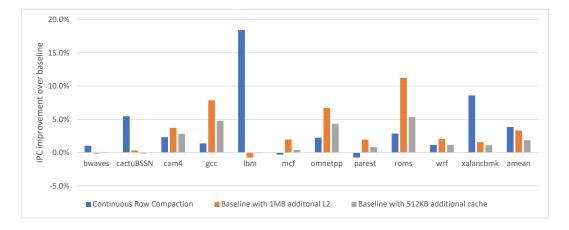

|       |       | 4.7.2.3 Comparison to Area-Equivalent Baseline                              | 89  |

|       |       | 4.7.2.4 Effect on Request Latency                                           | 91  |

|       |       | 4.7.2.5 8-Core Performance                                                  | 93  |

|       | 4.7.3 | Area                                                                        | 95  |

|       | 4.7.4 | Power/Energy                                                                | 96  |

| Chapt | er 5. | Continuous Row Compaction                                                   | 98  |

| 5.1   |       |                                                                             | 98  |

| 5.2   |       | ration                                                                      | 100 |

| 5.3   | Chall | enge (I):<br>nizing Data Movement Overhead                                  | 105 |

|       | 5.3.1 | Explicit Copying Throttling                                                 | 105 |

| 5.4   |       | enge (II):<br>ifying the Most Suitable Data for Duplication                 | 107 |

|       |       | Candidate Sequence Identification                                           | 107 |

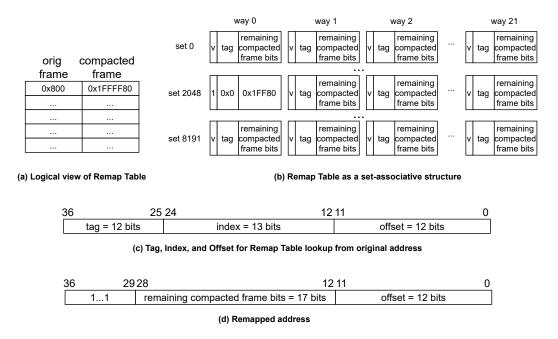

| 5.5   | Chall | enge (III):<br>nizing Tag Store Overhead                                    | 113 |

|       |       | Remap Table Organization                                                    | 113 |

| 5.6   | Chall | enge (IV):<br>ring Data Coherence and Correctness                           | 116 |

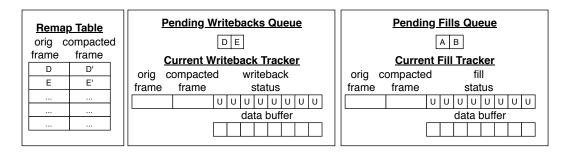

|        | 5.6.1  | Tracking | g partially written back/filled frames                                  | 116 |

|--------|--------|----------|-------------------------------------------------------------------------|-----|

| 5.7    | Evalu  | ation    |                                                                         | 125 |

|        | 5.7.1  | Benchm   | arks                                                                    | 125 |

|        | 5.7.2  | Baseline | e Configuration                                                         | 126 |

|        | 5.7.3  | Warmuj   | p Methodology                                                           | 126 |

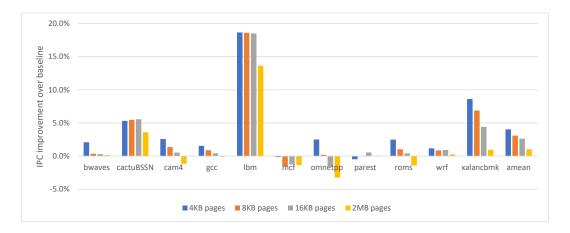

|        | 5.7.4  | Modelli  | ng Virtual-to-Physical Address Translation                              | 128 |

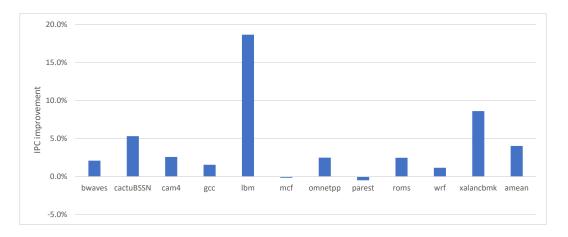

|        | 5.7.5  | Single ( | Core Performance                                                        | 129 |

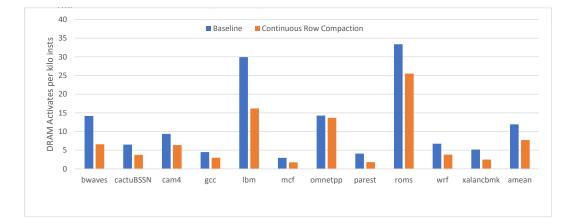

|        |        | 5.7.5.1  | Row Buffer Hit Rate                                                     | 130 |

|        |        | 5.7.5.2  | Effect on On-Chip L2 Evictions                                          | 131 |

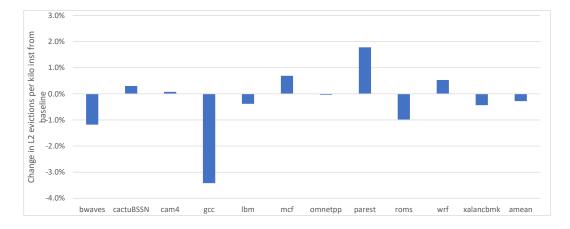

|        |        | 5.7.5.3  | Compaction Overhead $\ldots \ldots \ldots \ldots \ldots \ldots$         | 132 |

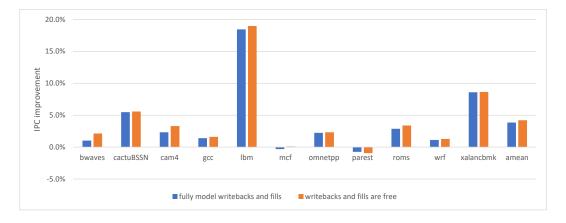

|        |        | 5.7.5.4  | Huge Pages and Consecutive Frames                                       | 134 |

|        |        | 5.7.5.5  | Prefetching                                                             | 136 |

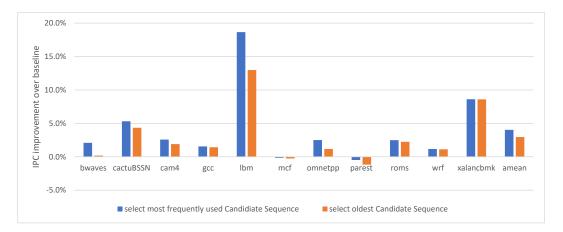

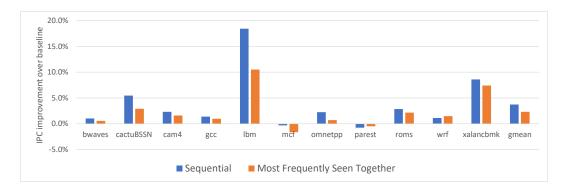

|        |        | 5.7.5.6  | Different Candidate Sequence Identification and<br>Selection Algorithms | 138 |

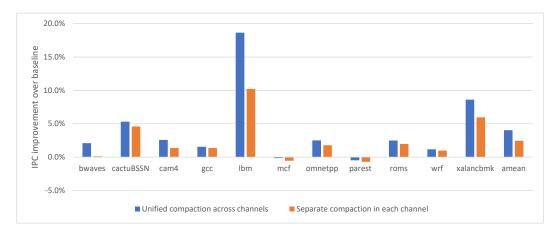

|        |        | 5.7.5.7  | Unified vs. Distributed Compaction Across Chan-<br>nels                 | 142 |

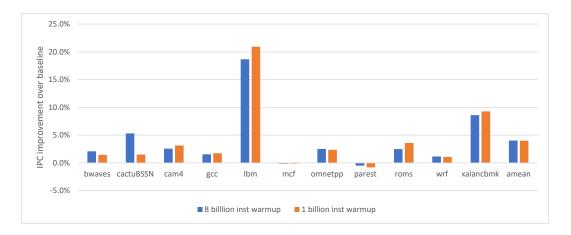

|        |        | 5.7.5.8  | Warmup Length                                                           | 144 |

|        |        | 5.7.5.9  | DRAM Reserved Storage Overhead                                          | 145 |

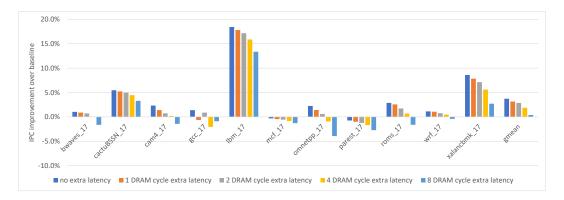

|        |        | 5.7.5.10 | Remap Table Latency                                                     | 148 |

|        | 5.7.6  | 4-core F | Performance                                                             | 149 |

|        |        | 5.7.6.1  | Benchmark Selection                                                     | 149 |

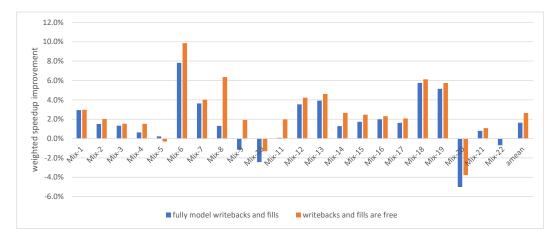

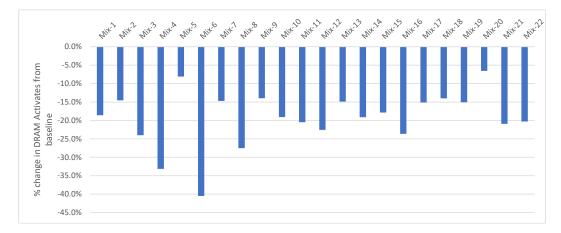

|        |        | 5.7.6.2  | Compaction Overhead                                                     | 150 |

|        |        | 5.7.6.3  | Row Buffer Hit Rate                                                     | 152 |

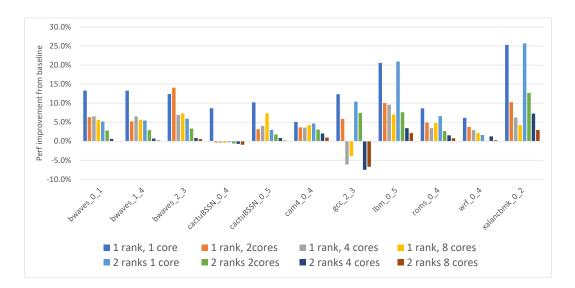

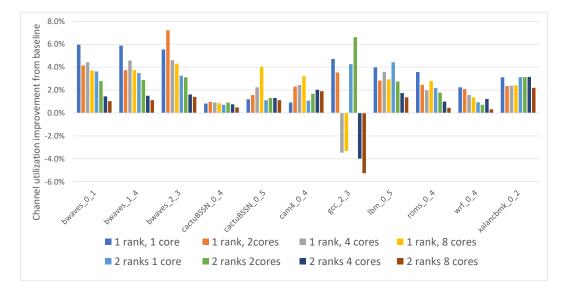

|        | 5.7.7  | Effect o | f Varying Bank and Core Counts                                          | 153 |

|        | 5.7.8  | Area     |                                                                         | 155 |

| Chapte | er 6.  | Relate   | d Work                                                                  | 158 |

| 6.1    | Cachi  | ng using | Performance-Optimized DRAM                                              | 158 |

| 6.2    | Cachi  | ng using | Tweaked Cost-Optimized DRAM                                             | 158 |

| 6.3    | Cachi  | ng using | Unmodified Cost-Optimized DRAM                                          | 160 |

|        | 6.3.1  |          | ag DRAM Latency using<br>fied Cost-Optimized DRAM                       | 161 |

| 6.4    | Fast 1 |          | ry Copying                                                              | 162 |

| 6.5    | Partitioning Memory Resources                                                                              | 162               |

|--------|------------------------------------------------------------------------------------------------------------|-------------------|

| 6.6    | Subrank and Subarray Parallelism                                                                           | 163               |

| 6.7    | Memory Scheduling and Throttling                                                                           | 164               |

| 6.8    | Data Blocking                                                                                              | 165               |

| 6.9    | Memory Compaction                                                                                          | 165               |

| 6.10   | Temporal Prefetching $\ldots \ldots \ldots$ | 166               |

|        |                                                                                                            |                   |

| Chapte | er 7. Conclusion                                                                                           | 167               |

| -      | e <b>r 7. Conclusion</b><br>Summary                                                                        |                   |

| 7.1    |                                                                                                            | 167               |

| 7.1    | Summary                                                                                                    | 167<br>168        |

| 7.1    | Summary         Future Work                                                                                | 167<br>168<br>168 |

# List of Tables

| 2.1 | DRAM timing constraints for DDR4-3200 22-22-22 memory  | 14  |

|-----|--------------------------------------------------------|-----|

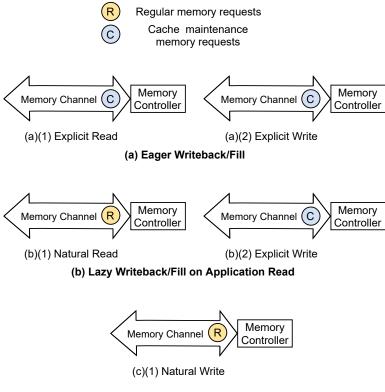

| 3.1 | Eager vs. lazy writeback/fill characteristics          | 46  |

| 3.2 | Duplicon Cache vs. Continuous Row Compaction           | 62  |

| 4.1 | Baseline Configuration                                 | 83  |

| 4.2 | Evaluated multi-programmed workloads                   | 83  |

| 4.3 | 8-core mixes                                           | 94  |

| 5.1 | Eleven most memory intensive SPECrate 2017 benchmarks. | 126 |

| 5.2 | Evaluated configuration.                               | 127 |

| 5.3 | 4-core mixes                                           | 150 |

| 5.4 | Memory and Continuous Row Compaction configuration for |     |

|     | area calculation                                       | 156 |

| 5.5 | Required data structures and cost                      | 156 |

# List of Figures

| 2.1 | DRAM hierarchical organization.                                                                                                                                                                                                                                   | 7  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Back-to-back read latency for row hits and conflicts                                                                                                                                                                                                              | 15 |

| 2.3 | Baseline FR-FCFS vs. improved Duplicon Schedule                                                                                                                                                                                                                   | 18 |

| 2.4 | Physical-to-DRAM address mappings                                                                                                                                                                                                                                 | 22 |

| 2.5 | Compacting Arrays C and D into the Compacted Region                                                                                                                                                                                                               | 25 |

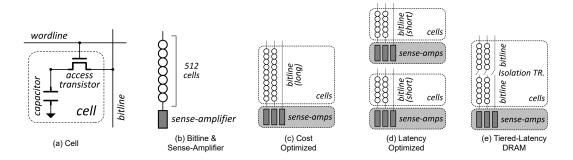

| 2.6 | Tweaking the DRAM device to shorten the bitlines. (from [29])                                                                                                                                                                                                     | 27 |

| 3.1 | Tag and Data Store.                                                                                                                                                                                                                                               | 32 |

| 3.2 | Reserving the top $2^k$ bytes of an $2^m$ physical address space                                                                                                                                                                                                  | 34 |

| 3.3 | Sectored Caches                                                                                                                                                                                                                                                   | 37 |

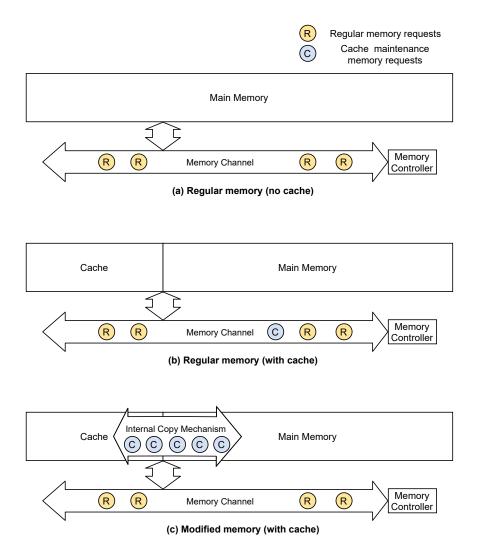

| 3.4 | Handling extra data traffic from main memory cache fills and writebacks.                                                                                                                                                                                          | 39 |

| 3.5 | Eager vs. Lazy writebacks/fills.                                                                                                                                                                                                                                  | 44 |

| 3.6 | Duplicon Cache as a Write-Through Cache.                                                                                                                                                                                                                          | 47 |

| 3.7 | Explicit throttling of cache fills and writebacks.                                                                                                                                                                                                                | 50 |

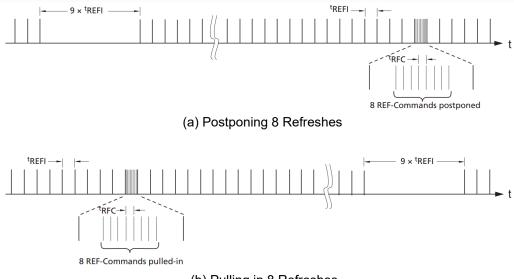

| 3.8 | Postponing and pulling in Refreshes(from [38])                                                                                                                                                                                                                    | 55 |

| 3.9 | Caching for very long time intervals with infrequent fills                                                                                                                                                                                                        | 58 |

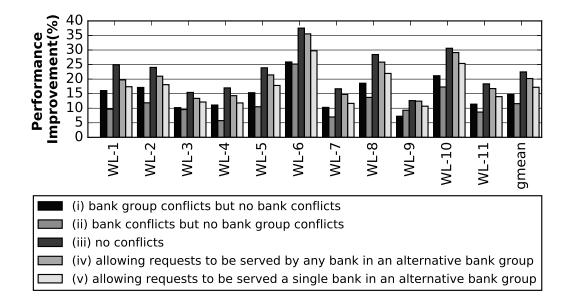

| 4.1 | Performance improvement when bank and/or bank group con-<br>flicts are removed or mitigated.                                                                                                                                                                      | 67 |

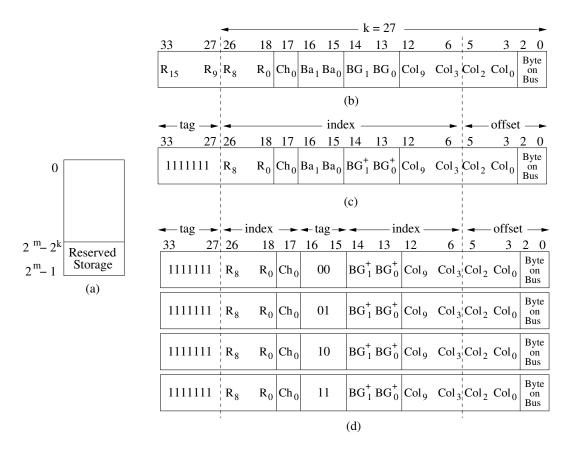

| 4.2 | (a) reserving a region in physical memory for duplicates, (b) the original physical address, (c) single duplication destination way in a direct-mapped Duplicon Cache (d) set of possible duplication destination ways in a 4-way set-associative Duplicon Cache. | 70 |

| 4.3 | Duplicon Cache tag store.                                                                                                                                                                                                                                         | 73 |

| 4.4 | Cache line state diagram.                                                                                                                                                                                                                                         | 78 |

| 4.5 | Flowchart for read.                                                                                                                                                                                                                                               | 80 |

| 4.6 | Flowchart for write requests.                                                                                                                                                                                                                                     | 81 |

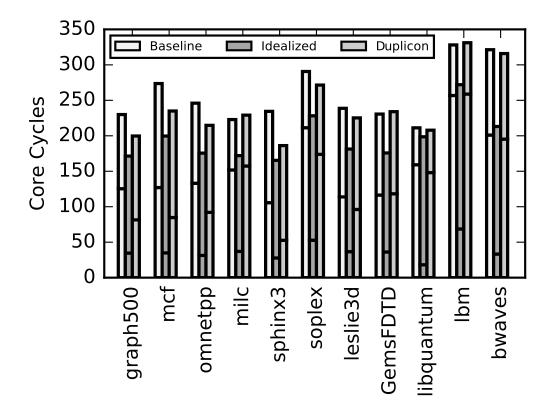

| 4.7 | Ideal vs. realized performance improvement.                                                                                                                                                                                                                       | 85 |

| -   | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                           |    |

| 4.8  | Performance without Demand Activates Filtering/Usefulness<br>Tracking                                                           | 88       |

|------|---------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.9  | Performance comparison to baseline with added LLC using dif-<br>ferent metrics: (a) Harmonic Mean of Weighted-IPCs, (b) Weighte |          |

|      | Speedup, (c) <u>Unfairness</u> $\dots \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots$                              | <u> </u> |

| 4.10 | Breakdown of average request latency.                                                                                           | 91       |

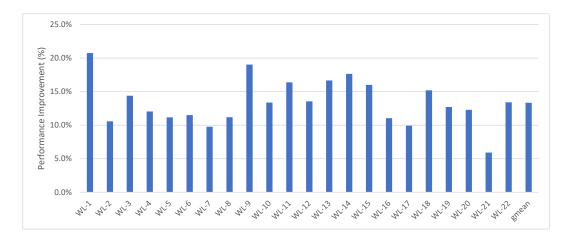

| 4.11 | Performance improvement on 8 cores                                                                                              | 95       |

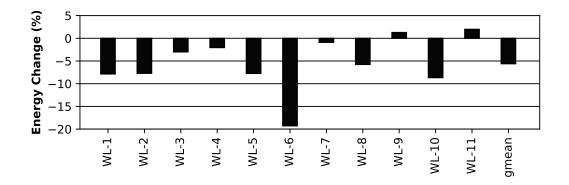

| 4.12 | Duplicon Cache energy evaluation.                                                                                               | 97       |

| 5.1  | Motivating stencil computation                                                                                                  | 102      |

| 5.2  | Candidate Sequence Identification.                                                                                              | 108      |

| 5.3  | Remap Table                                                                                                                     | 114      |

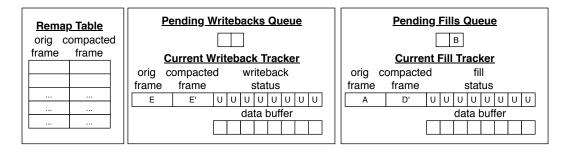

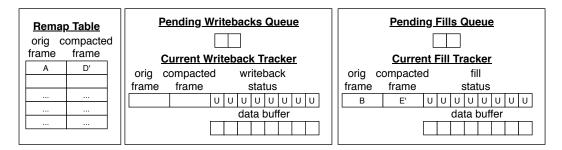

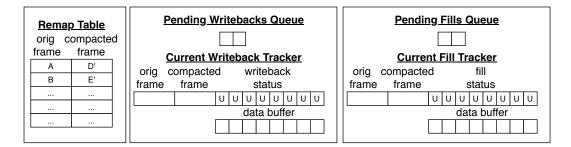

| 5.4  | Initial state of tracking structures, before replacement                                                                        | 117      |

| 5.5  | After enqueuing into the Pending Writebacks Queue and Pend-<br>ing Fills Queue                                                  | 119      |

| 5.6  | Beginning the writeback of D                                                                                                    | 119      |

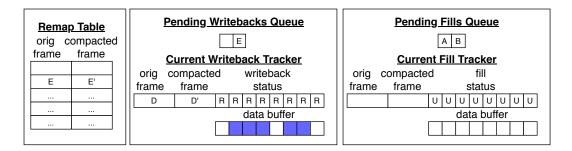

| 5.7  | All fetch requests issued, and some have returned                                                                               | 121      |

| 5.8  | Some writeback have completed                                                                                                   | 122      |

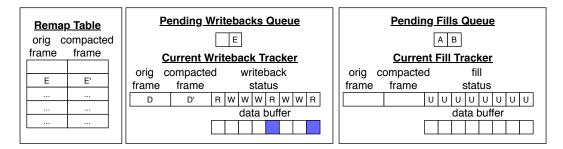

| 5.9  | Beginning to fill A into compacted frame D', and writing back<br>of E from compacted frame E'.                                  | 123      |

| 5.10 | A is remapped to D' in the Remap Table, and the filling of B into E' begins                                                     | 124      |

| 5.11 | Replacement complete                                                                                                            | 124      |

| 5.12 | Single core IPC improvement                                                                                                     | 130      |

| 5.13 | Single core DRAM Activates per kilo instructions                                                                                | 131      |

| 5.14 | Change in $L2(LLC)$ evictions per kilo instructions from baseline.                                                              | 132      |

| 5.15 | Effect on performance when writebacks and fills are made free.                                                                  | 133      |

| 5.16 | Effect of page size on benefit.                                                                                                 | 135      |

| 5.17 | Effect of increasing the number of MSHRs and prefetcher stream buffers                                                          | 137      |

| 5.18 | Selecting most frequently accessed vs. oldest candidate se-<br>quence for compaction                                            | 139      |

| 5.19 | IPC improvement over baseline with sequential vs. Most Fre-<br>quently Seen Together compaction candidate identification        | 141      |

| 5.20 | Row buffer hit rate improvement over baseline with sequential<br>vs. Most Frequently Seen Together compaction candidate iden- |      |

|------|-------------------------------------------------------------------------------------------------------------------------------|------|

|      | tification                                                                                                                    | 141  |

| 5.21 | Unified vs. Separate compaction with two channels                                                                             | 143  |

| 5.22 | 8 billion vs. 1 billion instructions warmup                                                                                   | 145  |

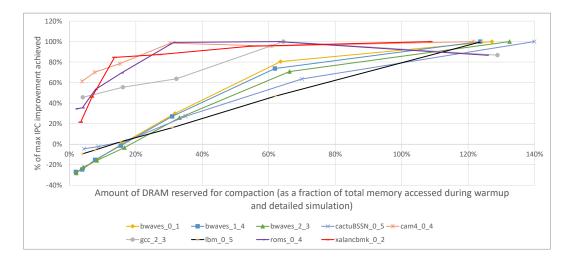

| 5.23 | Fraction of max IPC improvement achieved as a function of fraction of DRAM reserved for row compaction.                       | 146  |

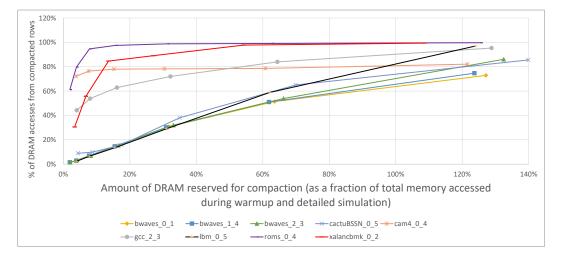

| 5.24 | Fraction of DRAM accesses from compacted rows as a function of fraction of DRAM reserved for row compaction                   | 147  |

| 5.25 | Effect of Remap Table latency (in DRAM cycles) on performance                                                                 | .148 |

| 5.26 | Effect on performance when writebacks and fills are made free                                                                 |      |

|      | for 4-cores                                                                                                                   | 151  |

| 5.27 | Change in number of DRAM Activates for 4-core mixes                                                                           | 152  |

| 5.28 | Performance improvement with varying rank and core counts.                                                                    | 154  |

| 5.29 | DRAM channel utilization improvement with varying rank and                                                                    |      |

|      | core counts.                                                                                                                  | 155  |

| 5.30 | Performance comparison to baseline with additional cache                                                                      | 157  |

## Chapter 1

## Introduction

## 1.1 The Problem

Main memory performance remains the principal bottleneck for many important applications. Main memory is organized as a hierarchy of banks, rows, and columns. Only data from a single row can be accessed from each bank at any given time. Switching between different rows of the same bank requires serializing long latency operations to that bank. Consequently, memory performance suffers on bank conflicts when concurrent requests access different rows of the same bank.

### 1.2 What Has Been Done

Prior work addressed the bank conflict problem in four ways:

• by changing the memory device itself to reduce the latencies associated with switching rows of a bank. However, such modifications create hurdles for adoption because they increase the cost of the device, and/or require changes to the memory access protocol that need to be agreed upon by all memory and processor manufacturers.

- by increasing the effective number of banks. Straight up increasing the number of banks gives the most benefit, but is also the most expensive option. Other techniques subdivide existing channels and banks into smaller independent modules (e.g., subranks and subarrays) to mimic the effect of having more banks. However, such techniques still require modifications to the memory device and/or memory access protocol, making adoption more difficult.

- by partitioning memory banks among different co-running applications to reduce bank conflicts caused by interference between different applications. However, scarcity in memory banks fundamentally limits the effectiveness of such partitioning.

- by optimizing the scheduling of memory requests to maximize utility from rows currently active in each bank. Such techniques need to strike a balance prioritizing memory requests to currently active rows in each bank while ensuring requests that conflict with the currently active rows still get serviced in a timely manner.

### 1.3 Contribution

The contribution of this thesis is two new runtime microarchitectureonly solutions to the bank conflict problem that are fully compatible with unmodified:

• Software (including OS, runtime, applications)

- Memory devices

- Memory access protocols

The first solution, Duplicon Cache, identifies frequently accessed and latency critical data that suffer from bank conflicts, then duplicates them to an alternate bank. Duplicated data can later be sourced early from its alternate bank when the original bank is currently busy, and vice versa. This substantially cuts down on memory request latency for requests that previously needed to wait for conflicts to resolve at the original bank.

The second, Continuous Row Compaction, identifies temporally correlated data that are frequently accessed together, then migrates them to a set of non-conflicting rows across different channels/ranks/banks. The migrated data can then later be accessed without bank conflicts.

All data duplications and migrations are managed at the memory controller, completely transparent to software, and performed with unmodified memory devices via existing memory access protocols.

In effect, the set of duplicated/migrated data form a cache within main memory. As this cache is resident in main memory itself, it can have considerably higher capacity than the conventional on-chip SRAM caches. Many of the challenges associated with Duplicon Cache and Continuous Row Compaction are in essence challenges associated with managing a large capacity cache in main memory. The two biggest challenges are:

- (1): How do we minimize the data duplication/migration overhead associated with filling this cache?

- (2): How do we efficiently track what has been cached (i.e., duplicated/migrated), given the large size of the cache? That is, how do we maintain an efficient tag store?

To minimize the data duplication/migration overhead, we take advantage of the enlarged capacity of this main memory cache to capture large working sets that are stable over very long time intervals, enabling one to achieve good reuse while replacing cache content very infrequently.

Efficient tag stores are maintained by using large line sizes and cache sectoring when appropriate. For Duplicon Cache, the tag store tracks what has been duplicated at 8KB granularity, but uses sectoring to allow individual 64B pieces within each 8KB line to be duplicated independently. For Continuous Row Compaction, the tag store tracks what has been migrated at 4KB granularity.

Both Duplicon Cache and Continuous Row Compaction have been evaluated on DDR4 SDRAM. They can be applied equally to other main memory technologies organized into banks and rows, such as non-volatile random-access memory (NVRAM), as well as other future memory technologies. I leave this as future work.

#### **1.4** Thesis Statement

Memory bank conflicts can be mitigated without modifying the memory device or access protocol by transparently duplicating frequently accessed and latency critical data to multiple banks, and/or migrating temporally correlated data that are frequently accessed together to non-conflicting rows across multiple banks.

#### 1.5 Dissertation Organization

The rest of the dissertation is organized as follows. Chapter 2 goes over background information on DRAM and motivates how data duplication and migration help mitigate bank conflicts. It also describes how prior work, in contrast, needs to modify the DRAM device itself in order to mitigate bank conflicts, and why this is undesirable. Chapter 3 discusses managing the overhead of extra data movement associated with data duplication/migration and tracking what has been duplicated/migrated. Chapter 4 presents and evaluates the Duplicon Cache. Chapter 5 presents and evaluates Continuous Row Compaction. Chapter 6 discusses related work. Chapter 7 presents conclusions and future work.

## Chapter 2

## **Background and Motivation**

This chapter goes over basic DRAM organization and operations, explains what bank conflicts are, why they are detrimental to performance, and motivates how data duplication across different banks (Duplicon Cache) and data migration to non-conflicting rows across different banks (Continuous Row Compaction) help mitigate bank conflicts without requiring any modifications to the DRAM device or access protocol. This chapter also describes how prior work, in contrast, modified the DRAM device in order to mitigate bank conflicts, and why this is undesirable.

The discussion is specific to DDR4 SDRAM memory, as it is the current predominant main memory technology on which the thesis evaluations are based. However, bank conflicts are also problematic for other memory technologies like non-volatile random-access memory (NVRAM), and in general the proposed solutions are sufficiently generic that they can be applied to any memory technology where bank conflicts are problematic.

### 2.1 DRAM Organization and Operations

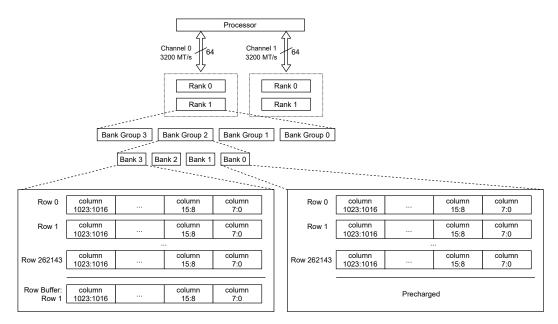

DDR4 SDRAM is organized as a hierarchy of channels, ranks, bank groups, banks, and columns. Figure 2.1 shows an example of this hierarchy with two channels and two ranks per channel.

Figure 2.1: DRAM hierarchical organization.

#### 2.1.1 Channel Bandwidth

The top level entity in the hierarchy is the channel. Each channel encompasses a subset of memory, along with the physical connections (pins,wires) that connect the subset of memory to the processor. Figure 2.1 shows two channels, labelled channels 0 and 1. Each channel is 64 bit wide. In this example, we assume each channel can transfer data at a rate of 3200 megatransfers per second (MT/s), which gives a maximum bandwidth of 23.8 GB/s.<sup>1</sup> The maximum aggregate bandwidth across both channels is thus 47.7 GB/s. This aggregate bandwidth is an upper limit on the maximum memory bandwidth available to the processor.

This upper limit can be increased by increasing:

- the number of channels

- the width of each channel

- the data rate of each channel

However, doing so comes at a cost. Increasing the data rate of each channel, as is done for graphics GDDR memory, increases the power consumption. Increasing the number of channels or the width of each channel increases the total number of physical connections between the processor and the memory, increasing the manufacturing cost. This is the most common differentiator between cost-optimized memory technology such as DDR4 that have fewer connections to the processor, and performance-optimized memory technology such as High Bandwidth Memory (HBM) that have much more connections to the processor. To support the higher number of connections between memory and processor, performance-optimized memory like HBM need to be connected to the processor using more expensive technology like

<sup>&</sup>lt;sup>1</sup>3200000000 transfers/s \* 8B/transfer = 23.8 GB/s

silicon interposers, while cost-optimized memory can use cheaper technology like printed circuit boards [2].

The aggregate channel bandwidth is an upper bound on the maximum memory bandwidth available to the processor. Yet oftentimes, due to bottlenecks in other levels of the DRAM hierarchical organization, the available channel bandwidth is underutilized, even for cost-optimized memory that have lower available channel bandwidth to begin with. The biggest of these bottlenecks are bank conflicts, described in the following sections.

#### 2.1.2 Rank, Bank Group, and Bank Level Parallelism

After the channel, the next levels in the hierarchical organization are ranks, bank groups, and banks.

Banks are individual sub-modules of memory that can each independently process memory requests. Every memory request is ultimately processed by a particular bank. However, the latency for accessing data at each bank varies depending on the state of the bank, and can be quite long. In general, the rate at which requests can be processed at a single bank is much lower than the rate needed to saturate the available channel bandwidth. Thus it is necessary to interleave requests to different banks and overlap latencies from multiple requests in order to achieve good utilization of the channel.

Consequently, it is advantageous to have as many banks as possible in order to maximize the level of interleaving. However, additional banks incur additional hardware costs. Bank groups were introduced with DDR4 to allow for additional banks while keeping hardware costs low. In essence, a bank group is a group of banks that share some hardware resources. The shared resources then only need to be replicated once per bank group, rather than once per bank. With bank groups, DDR4 was able to double the number of banks per device from 8 to 16 from DDR3, organized into four bank groups of four banks each. However, because banks of the same bank group share certain hardware resources, memory requests to the same bank group now incur additional delay, even if they are to different banks.

Finally, a rank is a group of memory devices that operate in lockstep in response to the same memory commands. Ranks are usually added to increase the memory capacity per channel, although additional ranks also increase the total number of bank groups/banks, improving performance. Figure 2.1 shows each channel is attached to two ranks, labelled ranks 0 and 1, for a total of four ranks in the system. Each rank is in turn made up of four bank groups, and each bank group made up of four banks. In total, there are 16 banks per rank, and 32 banks per channel in the example in Figure 2.1.

Each of the 32 banks belonging to the same channel share the same channel data pins. At any given time, only data from one of the 32 banks can be transferred over the channel, and interleaving is required to overlap the latencies from different requests in order to achieve good utilization of the channel. In particular, it is most advantageous to interleave requests across different bank groups. In fact, it is impossible to fully saturate the channel bandwidth without interleaving requests across different bank groups. My first proposal, Duplicon Cache, leverages this property of memory by duplicating select data across bank groups, increasing the probability that interleaving can occur, thereby increasing performance.

#### 2.1.3 Row Buffer Locality and Bank Conflicts

Data in each bank is organized into rows and columns. In Figure 2.1 there are 256K rows per bank, and 1K columns per row.

Although there are 1K columns per row, the DDR4 protocol specifies that columns must be accessed in aligned units of 8 or 4, with 8 being the most common configuration. On a read or write, the 8 columns in the aligned unit are read/written in 8 consecutive data bursts. Consequently, there are only 1K/8 = 128 addressable aligned units of data in each row.

Only data from a single row can be accessed at any given time from a bank. This is because data in DRAM is encoded via the presence of electric charge on capacitors, and before such data can be accessed, it first needs to be read out and amplified via a process called sense amplification. This involves two steps. The first is Precharge, which prepares the bank for sense amplification. The second is Activate, which reads out and amplifies an entire row's worth of data.<sup>2</sup> Once a row has been activated at a bank, it stays activated until the next Precharge operation, and subsequent reads and writes to columns in that row can be processed with low latency. The row currently

<sup>&</sup>lt;sup>2</sup>the Activate operation is also interchangeably referred to as sensing the row, activating the row, or opening the row

activated in the bank forms the row buffer (also called the DRAM page). Additional accesses to the row buffer are called row buffer hits, and the tendency for future accesses to hit in the row buffer is called row buffer locality.

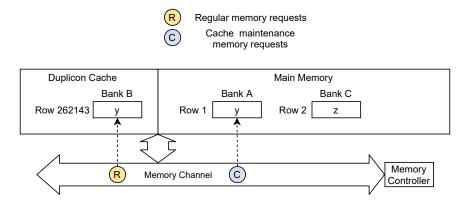

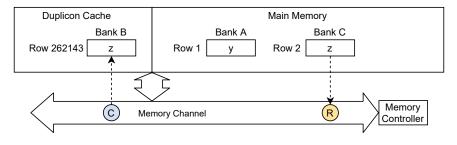

Figure 2.1 shows that row 1 has already been activated in rank 1, bank group 2, bank 3, indicated by row 1 being shown again in the area below all the others rows. In contrast, rank 1, bank group 2, bank 0 is in the precharged state, where no rows are currently activated. In general, each bank either has a particular row activated, or is in the precharged state.

The Precharge the Activate operations themselves incur long latencies and are subject to various timing constraints, resulting from physical limitations of the memory device. From a performance point of view, the worst case scenario is a row or bank conflict when data being requested belong to different rows of the same bank.<sup>3</sup> In this case the accesses are serialized, as only data from a single row of the bank can be accessed at a time. Switching between the two rows requires a long latency Precharge operation, followed by another long latency Activate operation; the Precharge and Activate operations are completely serialized with no parallelism.

Duplicon Cache mitigates the effects of bank conflicts by duplicating the data to another bank group, allowing the Precharge and Activate latencies to be overlapped to different bank groups.

$<sup>^{3}\</sup>mathrm{I}$  use the terms row conflict, row buffer conflict, and bank conflict interchangeably in the rest of the thesis

Continuous Row Compaction reduces the number of Precharge and Activate operations needed by migrating data frequently accessed together to the same row address across different channels, ranks, bank groups, and banks. For example, if data items A, B, C,..., Z were frequently accessed together, Continuous Row Compaction would migrate (i.e., compact) them to regions in memory that share the same row address (e.g. row 262143) across all channels, ranks, bank groups, and banks. Future accesses to A, B, C,..., Z are then guaranteed to not cause row/bank conflicts, and will be interleaved across all channels, ranks, bank groups, and banks.

#### 2.1.4 Memory Timing

Long serialized Precharge and Activate latencies during bank conflicts substantially hurt memory performance. The exact latencies required for Precharge and Activate operations depends on the type, order, and location of preceding memory operations.

There are four main DRAM operations: Precharge, Activate, Read, and Write. The Precharge operation prepares the bank for sense amplification, and the Activate operation activates (i.e., perform sense implication) on the desired row. Once the row with the data has been activated, Read/Write operations read/write the data at the column specified. Timing constraints, imposed due to physical limitations of the memory device, limit when Precharge, Activate, Read, or Write operations can be issued. Table 2.1 shows some relevant timing constraints that affect memory performance.

| Constraint     | Description                                             | Delay (cycles) |

|----------------|---------------------------------------------------------|----------------|

| $t_{CCD\_S}$   | delay between consecutive reads (or consecutive writes) | 4              |

|                | to different bank groups of the same rank               |                |

| $t_{CCD_{-L}}$ | delay between consecutive reads (or consecutive writes) | 8              |

|                | to the same bank group of the same rank                 |                |

| $t_{RTP}$      | delay between read and subsequent                       | 12             |

|                | precharge to the bank                                   |                |

| $t_{RAS}$      | delay between activate and subsequent                   | 56             |

|                | precharge to the bank                                   |                |

| $t_{RP}$       | delay between precharge and subsequent                  | 22             |

|                | activate to the bank                                    |                |

| $t_{RCD}$      | delay between activate and subsequent                   | 22             |

|                | read or write to the bank                               |                |

Table 2.1: DRAM timing constraints for DDR4-3200 22-22-22 memory.

We now consider how the timing for two back-to-back reads to the same device (i.e., rank) changes under various conditions. We consider reads for simplicity, but the analysis is equally applicable for back-to-back writes. However, mixing of reads and writes involves other timing constraints that I have omitted for brevity.

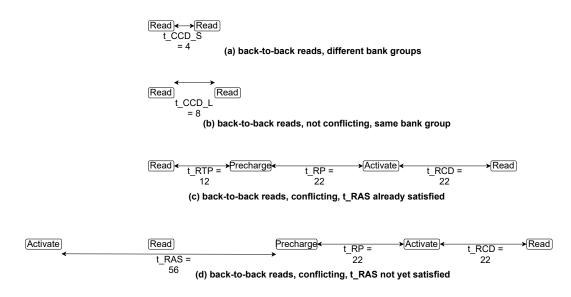

If the reads are not conflicting (i.e., they are to different banks, or they access the same row in the same bank), then  $t_{CCD}$  is the limiting timing constraint.  $t_{CCD}$  specifies the minimum delay required between back-to-back reads to the same rank, and comes in two variants. If the reads are to different bank groups, then the short variant,  $t_{CCD,S}$ , which is 4 cycles, applies. As the actual data transfer over the channel takes 4 cycles itself, being able to issue a read every 4 cycles is sufficient to saturate the channel bandwidth. The timing for this scenario is shown in Figure 2.2(a).

If the back-to-back reads are not conflicting but to the same bank group,

Figure 2.2: Back-to-back read latency for row hits and conflicts.

then long variant of  $t_{CCD}$ ,  $t_{CCD,L}$ , which is 8 cycles, applies.<sup>4</sup> This means that even if all accesses are row buffer hits, if they all access the same bank group (i.e., no bank group interleaving), then one can at most achieve 50% channel utilization (4 cycles to transfer data for each request, but only able to issue read operations once every 8 cycles). This shows the importance of having high levels of bank group interleaving. The timing for back-to-back reads to the same bank group is shown in Figure 2.2(b).

Note that it is not necessary, in the two scenario described above, for both reads to be row buffer hits at their respective banks. The reads may instead themselves require Precharge and/or Activate at their respective banks,

$<sup>^{4}</sup>$ the longer delay is required because, as explained in section 2.1.2, banks of the same bank group share certain hardware resources

but because the Precharges/Activates are to different banks, their latencies can be overlapped.

In contrast, for back-to-back conflicting reads (i.e., reads that access different rows of the same bank), the Precharge and Activate latencies become serialized and exposed. After the first read is issued, a Precharge is required to prepare the bank for sense amplification, followed by an Activate to activate the row for the second read, followed by the second read itself. The timing for the Precharge depends on how long ago the previous Activate (i.e., the Activate that activated the row for the first read) was issued. If the previous Activate was issued sufficiently long ago, then  $t_{RTP}$ , which specifies the minimum delay required between a read and subsequent Precharge to the same bank (12 cycles), determines how soon the Precharge can be issued. This case is shown in Figure 2.2(c). On the other hand, if the previous Activate was issued recently, then  $t_{RAS}$ , which specifies the minimum delay between an Activate and subsequent Precharge to the same bank (56 cycles), determines how soon the Precharge can be issued. This second case is shown in Figure 2.2(d).

After the Precharge, the remaining timing are the same for both cases (c) and (d). The Activate for the row of the second read can be issued  $t_{RP}$ (22) cycles after the Precharge, and then the second read can be issued  $t_{RCD}$ (22) cycles after the Activate.

For the case in Figure 2.2(c), the latency between two reads ends up being 12 + 22 + 22 = 56 cycles. If all memory accesses were like this, then we could only achieve 4/56 = 7.1% channel utilization, as we would only be able to issue read requests once every 56 cycles, which would occupy the channel for 4 cycles, while the other 52 cycles remain idle. For the case in Figure 2.2(d), the performance limiter would be the latency between the two Activates, which is 56 + 22 = 78 cycles. If all memory accesses were like this, then we could only achieve 4/78 = 5.1% channel utilization.

The takeaway from this example is that conflicting accesses to different rows of the same bank is particularly harmful to memory performance, as Precharge and Activate latencies, which are significant, become fully exposed. Memory controllers try to minimize such conflicting accesses through better memory scheduling and physical-to-DRAM addressing mapping. I discuss these mechanisms below, and motivate how my proposals, Duplicon Cache and Continuous Row Compaction, enhance these two existing mechanisms.

### 2.1.5 Memory Scheduling and Duplicon Cache Motivating Example

Memory controllers buffer multiple memory requests and reorders them to better exploit bank level parallelism and row buffer locality. First Ready -First Come First Serve (FR-FCFS) [52] is a common strategy for reordering memory requests. FR-FCFS prioritizes ready memory requests (i.e., requests whose timing constraints have been satisfied) over non-ready requests, and then prioritizes older requests over younger requests. Since row buffer hits have timing constraints that are much more easily satisfied than row buffer conflicts, FR-FCFS essentially prioritizes row buffer hits over other requests. FR-FCFS tends to maximize the overall memory request throughput, but introduces unfairness into the system because row conflict requests end up waiting a long time while other row buffer hits are getting processed.

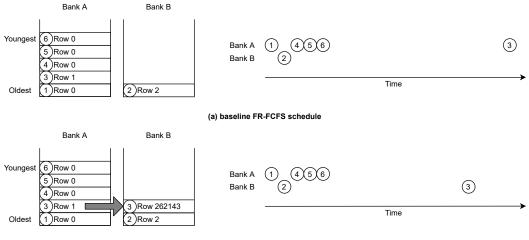

(b) improved Duplicon schedule

Figure 2.3: Baseline FR-FCFS vs. improved Duplicon Schedule.

Figure 2.3(a) shows how this can happen. We have six requests, (1) - (6), from oldest to youngest. Requests (1), (3), (4), (5), and (6) are queued in bank A, while request (2) is queued in bank B. Requests (1), (4), (5), and (6) access row 0 of bank A, while request (3) accesses row 1 of bank A. Since FR-FCFS favors row buffer hits over row conflicts, it will schedule (1), (4), (5), and (6) first, as all four can be serviced from (bank A, row 0). Request (3), which accesses (bank A, row 1), creates a bank conflict at bank A that requires a separate Precharge and Activate, and gets scheduled last, after (6).

Meanwhile, bank B happens to be lightly loaded. Request (2) gets

scheduled (due to its age) between ① and ④. After request ② is serviced, bank B becomes idle, and remains idle even while bank A is servicing requests ④, ⑤, ⑥, and ③.

One of the main insights behind Duplicon Cache is that these moments of load imbalance between banks can be exploited if data was duplicated to both banks. In Figure 2.3(b), we assume the data for request ③, in (bank A, row 1), was previously duplicated to (bank B, row 262143). This allows us to service request ③ from either bank A or B. Since bank B becomes idle in our example after servicing servicing request ②, we can now begin servicing of request ③ earlier from bank B, shortly after request ② has been serviced. Consequently, request ③ gets serviced earlier compared to the FR-FCFS baseline.

In this example bank B happened to be less loaded than bank A; in another instance, bank A may be less loaded than bank B. In either case, the duplicated data can be sourced earlier from the less loaded bank.

Duplicon Cache complements FR-FCFS nicely, because it alleviates the unfairness introduced by FR-FCFS. Normally, FR-FCFS introduces unfairness into the system because row conflict requests end up waiting a long time while other row buffer hits are getting processed. With Duplicon Cache, FR-FCFS can continue to prioritize row buffer hits to maximize overall request throughput, while Duplicon Cache identifies data that are suffering the most from row conflicts and enable them to be serviced earlier via duplication, thus reducing unfairness. Note that Duplicon Cache does not actually reduce the number of row conflicts. In fact, it can increase the number row conflicts, since requests that were previously concentrated in the same row of the same bank now get diffused across multiple banks. But Duplicon Cache allows conflicting requests to be initiated earlier in another less loaded bank.

## 2.1.6 Physical-to-DRAM Address Mapping and Continuous Row Compaction Motivating Example

Bank conflicts arise when two concurrent requests share the same channel, rank, bank group, and bank address, while differing in the row address. The channel, rank, bank group, bank, row, and column addresses collectively form the DRAM address, and are determined from the physical address. In general, they are either taken directly from a subset of the physical address bits, or are computed as hashes (usually XOR) of various physical address bits. This mapping from physical address to DRAM address directly affects the frequency of row conflicts and memory performance.

In general, the lower order physical address bits toggle the most, while the higher order bits toggle the least. Thus taking the column address directly from the lowest order physical address bits produces the highest level of row buffer locality, as this maximizes the probability for DRAM addresses of concurrent accesses to only differ in the column address, resulting in row buffer hits to the same row of the same bank. Similarly, it is advantageous to place the row address bits as high as possible to minimize row address toggling, as two accesses with the same row address cannot conflict - they will either access the same row in the same bank, or access different banks.

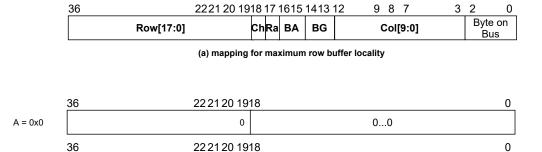

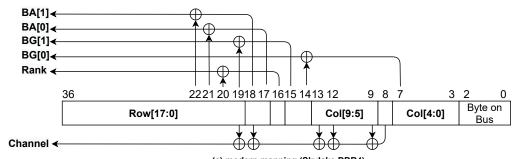

Figure 2.4(a) shows such a mapping. As the DDR4 channel data width is 8 bytes, the lowest 3 bits of the physical address specify the byte on the channel. Next come the column address bits, which are taken from bits[12:3] of the physical address, followed by the bank group (denoted as BG), bank (BA), rank (Ra), channel (Ch), and Row bits.

This mapping maximizes the row buffer locality in each bank, but can actually be harmful to performance. To see this, suppose an application makes sequential accesses to two arrays, A and B, which are aligned to 512KB boundaries (i.e., the low 19 address bits are 0) at addresses 0x0 and 0x80000, respectively, as shown in Figure 2.4(b). The first problem with the mapping in Figure 2.4(a) is that, if A and B are sequentially accessed concurrently with the same incrementing index i and stride (for example, A and B are both accessed in a for loop with the same incrementing loop variable i), then every pair of accesses will be row conflicts, because the channel, rank, bank, and bank group address of A[i] and B[i], taken from bits [18:13] of the physical address, will always be the same for all indices i, while their row addresses (taken from bits 19 and above) will always be different.

The second problem with the mapping is that it provides poor channel interleaving and parallelism. Each pair of accesses to A[i] and B[i] will always go to the same channel, and as i increments, the accesses will stay in the same channel until the channel bit (bit 18) toggles. Assuming a stride of 64 bytes,

(b) arrays A and B, aligned at 512KB granularity

0...0

1

B = 0x80000

(c) modern mapping (Skylake DDR4)

Figure 2.4: Physical-to-DRAM address mappings

this will only happen once every 4096 loop iterations.

The third problem is the mapping provides poor bank group interleaving, as A[i] and B[i] will always go to the same bank group, and the bank group bits (14 and 13) only toggle infrequently. Recall from Section 2.1.4 that bank group interleaving is advantageous because many DRAM timing constraints have more favorable (i.e., shorter delay) variants when the accesses are to different bank groups.

Figure 2.4(c) shows an improved state-of-the-art address mapping that fixes these issues [48]. The new mapping, in order to maximize row buffer locality, still takes the column address from the lowest order address bits, and the row address from the highest order address bits. However, the channel, rank, bank group, and bank addresses are now computed as XORs of several address bits, as opposed to being taken directly from the address [80]. For the channel address, the XOR-ed bits come from throughout the physical address, including one that is placed in the middle of the column bits (bit 8) [20], resulting in the channel bit toggling very frequently for both sequential and random accesses. This addresses the issue of poor channel interleaving. Likewise, one of the XOR-ed bits for the bank group comes from the low address bits (bit 7), ensuring the bank group address will also toggle frequently, providing bank group interleaving. The low 4 bits of the row address (bits [22:19]) are also now incorporated in the channel, rank, bank group, and bank computations via XORing. This fixes the problem of A[i] and B[i] always being row conflicts - since A and B differ in bit 19, and since bit 19 is now XORed as part of the channel and bank group computation, A[i] and B[i] will now access different bank groups in different channels.

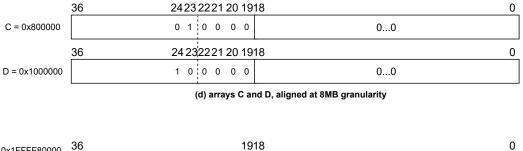

However, the improved mapping does not fundamentally solve the problem of concurrent accesses with the same index and stride to aligned arrays resulting in row conflicts. If we replace A and B with arrays C and D, which are now aligned to 8MB boundaries at addresses 0x800000 and 0x1000000 respectively (shown in Figure 2.4(d), where the low 23 address bits all 0 for both C and D), then we still have the exact same issue as before, as the channel/rank/bank group/bank computations of the new mapping only consider bits 22 and below of the physical address, which would be the same between C[i] and D[i] for all indices i.

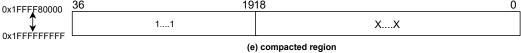

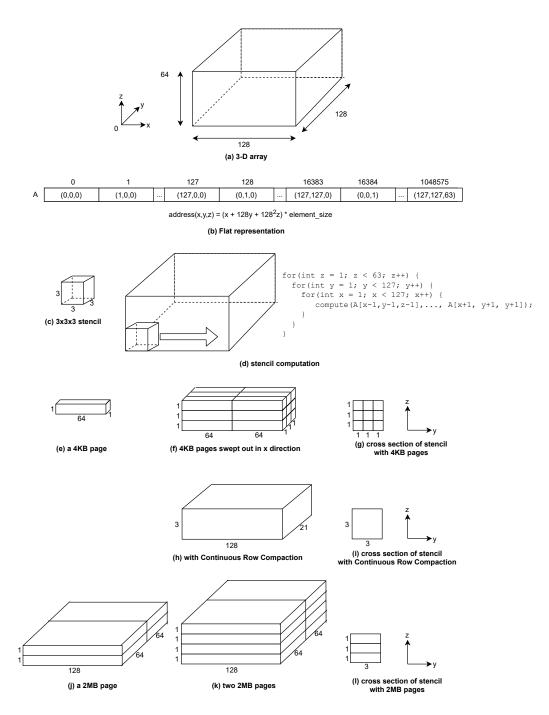

My second proposal, Continuous Row Compaction, does in fact fundamentally resolve this problem of concurrent accesses with the same index and stride to aligned arrays resulting in row conflicts. The fundamental idea behind Continuous Row Compaction is to migrate (i.e., compact) concurrently accessed data to regions in memory with the same row address. For example, suppose we reserved the row address 0x3FFFF, the largest row address possible, for exclusive use of the hardware, as shown in Figure 2.4(e). Since the row address comes from the highest order bits of the physical address, this essentially reserves the highest 512KB of the physical address space, comprised of addresses 0x1FFFF80000 through 0x1FFFFFFFFF, for the hardware (i.e., the software is made to think 0x1FFFF7FFFF is the last byte of the physical address space). The memory controller can then use this reserved region however it sees fit.

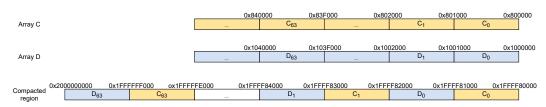

Figure 2.5: Compacting Arrays C and D into the Compacted Region

Continuous Row Compaction records the order in which 4KB memory regions are accessed by the application, and then migrates (i.e., compacts) those regions in the order they were accessed to a reserved row address. I show this in Figure 2.5. Suppose the application sequentially accesses the arrays C and D in the order C[0], D[0], C[1], D[1], C[2], D[2], and so on. Continuous Row Compaction would detect that the first 4KB region of array C (labelled  $C_0$ in Figure 2.5, 0x800000 to 0x800FFF) was accessed first, followed by the first 4KB region of array D ( $D_0$ , 0x1000000 to 0x1000FFF), followed by the second 4KB region of array C ( $C_1$ , 0x801000 to 0x801FFF), then the second 4KB region of array D ( $D_1$ , 0x1001000 to 0x1001FFF), and so on. Once enough 4KB memory regions have been recorded to fill a reserved row address, then the recorded 4KB regions can be migrated, in the order they were recorded in, to the reserved row. In our example, since the reserved row 0x3FFFF spans 512KB between the addresses 0x1FFFF80000 and 0x1FFFFFFFF, we would require 512 KB/4 KB = 128 different 4KB regions to fill the reserved row address. Consequently, we would migrate the first 64 4KB regions of array C, along with the first 64 4KB regions of array D, into the 512KB reserved region between 0x1FFFF80000 and 0x1FFFFFFFF, with the individual 4KB regions of C and D interleaved in the order in which they were accessed. Thus,  $C_0$ , the first 4KB of array C, would be migrated to the first 4KB of the reserved region, 0x1FFFF80000 to 0x1FFFF80FFF;  $D_0$ , the first 4KB of array D, would be migrated to the second 4KB of the reserved region, 0x1FFFF81000 to 0x1FFFF81FFF;  $C_1$ , the second 4KB of array C, would be migrated to the third 4KB of the reserved region, 0x1FFFF82FFFF; ....

Essentially, Continuous Row Compaction divides the arrays C and D into 4KB segments, then interleave the segments, in the order they were accessed, to the reserved region. Future accesses to the same 4KB segments can later be serviced from the reserved region without any row conflicts, as the interleaved 4KB segments all share the same row address and cannot conflict with one another.

In our example, the arrays being accessed shared the same alignment and were accessed with the same index and stride. This was chosen deliberately to emphasize the negative impact from row conflicts. However, in general any concurrent streaming accesses to arrays with different row addresses (i.e., different high order address bits) can result in row conflicts, even if they do not necessarily share the exact same alignment, index, or stride. In particular, multiple concurrent streaming accesses are very common in stencil computations (section 5.2). In these cases, Continuous Row Compaction is able to splice together 4KB segments from different streams into the same row address, removing row conflicts. In addition, note that Continuous Row Compaction can give benefit even if the order in which 4KB segments were recorded and migrated differs from the exact order in which the segments are later accessed, as long as there is enough overlap between the set of 4KB segments that were migrated, and the set of 4KB segments that were later concurrently accessed.

#### 2.1.7 The Alternative: Tweaking the DRAM Device

I have so far motivated how memory bank/row conflicts can be mitigated via data duplication (Duplicon Cache) and data migration (Continuous Row Compaction), all without changing the memory device or memory access protocol. In contrast, prior work advocated for tweaking the design of the DRAM device in order to reduce the latency of switching rows at a bank. In particular, they focused on reducing the latency of DRAM Precharge and Activate operations by reducing the effective capacitance of the shared piece of wire, called the bitline, which connects to individual DRAM storage cells.

Figure 2.6: Tweaking the DRAM device to shorten the bitlines. (from [29])

The latencies for Precharge and Activate depend on the capacitance

of the bitlines, which can be reduced in certain regions of the DRAM device via device level tweaks. This is shown in Figure 2.6. Figure 2.6(a) shows a DRAM cell, consisting of a capacitor connected to a bitline via an access transistor. A single bit is stored in the cell, via the presence (or lack) of charge on the capacitor. To access the bit, the bitline first needs to be brought (via the Precharge operation) to a reference voltage. Then the access transistor for the cell is turned on by raising the associated wordline (via the Activate operation), which connects the cell capacitor to the bitline. The presence (or lack) of charge on the capacitor will then slightly raise (or lower) the voltage on the bitline, producing a signal. However, this signal is very weak, and needs to be amplified by a sense-amplifier.

To increase the cell density, several cells share a single bitline and senseamplifier. At any time, at most only one of the cells can connect to the shared bitline. Figure 2.6(b) shows 512 cells sharing a single bitline and senseamplifier. This forms a single column of a two-dimensional matrix of storage cells, called a mat, which is shown in Figure 2.6(c).

Increasing the number of cells sharing a bitline increases the cell density and lowers the cost of the memory device. However, this also increases the bitline capacitance, which increases both the Precharge latency (latency to bring bitlines to the reference voltage,  $t_{RP}$  in Table 2.1) and Activate latency (latency to sense-amplify,  $t_{RCD}$  and  $t_{RAS}$  in Table 2.1). Cost-optimized DRAMs opt for more cells sharing the same bitline (e.g. 512 cells per bitline), like in the mat shown in Figure 2.6(c), while performance-optimized DRAM like Reduced Latency DRAM (RLDRAM) opt for fewer cells sharing the same bitline (Figure 2.6(d)).

Prior work proposed reducing the number of cells sharing a bitline in certain regions of the DRAM device. For example, Center High-Aspect-Ratio Mats (CHARM) [60] proposed replacing normal cost-optimized mats at the center of the chip with latency-optimized mats that have fewer cells per bitline, like those of Figure 2.6(d). Tier-Latency DRAM proposed adding isolation transistors that break the bitline into near and far segments (Figure 2.6(e)). When the isolation transistors are turned off, there are effectively fewer cells sharing the bitline in the near segment.

#### 2.1.7.1 Drawbacks of Modifying DRAM

The main drawback with these proposals is that they require modifications to the DRAM device, which can increase the manufacturing cost and/or reduce the yield. For example, adding the isolation transistors for Tiered-Latency DRAM can be challenging because the process technology used for DRAM is specifically optimized to allow for greater cell density, and building isolation transistors with the necessary characteristics (e.g., good isolation when off, very low resistance when on) in this process may be challenging. Cost-optimized DRAM is a commodity business with very low margins and very large volumes. Thus DRAM manufacturers have thus far not adopted these proposals.

Additionally, since these proposals also require changes to the DRAM

access protocol, consensus from different DRAM and processor manufacturers are required before these proposals can be adopted. Such consensus is often slow and difficult to reach among companies with different competing interests.

In contrast, my proposals, Duplicon Cache and Continuous Row Compaction, avoids these issues entirely, as I do not require modifications to the DRAM device or access protocol. Instead, I am able mitigate the effects of bank conflicts via transparent data duplication and migration.

# Chapter 3

# Main Memory Caches

As data are duplicated/migrated, the set of duplicated/migrated data essentially form a cache within main memory. Many of the issues that arise with data duplication/migration are in essence issues that arise when managing a large capacity cache in unmodified main memory. This chapter examines these issues.

# 3.1 Tag and Data Store

A cache needs to store both tag and data. In the context of Duplicon Cache and Continuous Row Compaction, the data is the actual data being duplicated/migrated, while the tag encompasses all the information needed to track:

- which data have been duplicated/migrated

- where the data have been duplicated/migrated to

- other information needed for the maintenance of the cache (e.g. replacement info, dirty status)

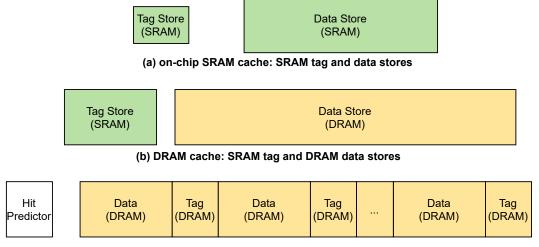

Conventional SRAM caches store tag and data in two separate structures, tag store and data store. This is shown in Figure 3.1(a).

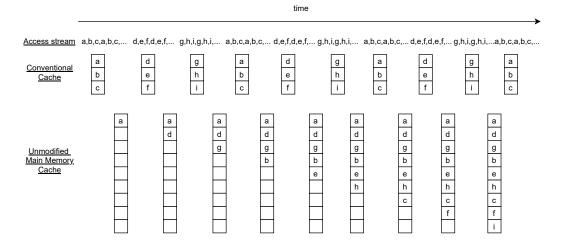

For larger capacity caches, storing the data entirely in SRAM becomes prohibitively expensive. Instead, data is stored in less expensive technology, such as DRAM. This is shown in Figure 3.1(b).

(c) DRAM cache: integrated DRAM tag and data with Hit Predictor

Figure 3.1: Tag and Data Store.

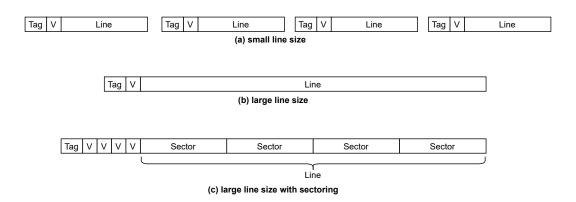

The tags, on the other hand, only require a fraction of the storage capacity of data, and can still fit in SRAM up to a point. However, for even larger capacity caches, new techniques are needed to reduce the size requirement of the tag store. One can, for example, increase the granularity at which tag information is tracked (i.e., increase the line/block size). We discuss this more in Section 3.3.2.

For the largest capacity caches, even the tags become too big to fit in

SRAM, and are instead kept in DRAM. This is shown in Figure 3.1(c). Rather than continuing to store tag and data in two separate structures, now both tag and data are integrated in the same DRAM memory, where the corresponding tag for each line/block is placed contiguous to the data. This allows both the data and tag to be accessed in a single DRAM access [51, 59]. Such caches need to be direct mapped so that one can know exactly where in DRAM to look for a particular piece of data [51]. Note that one cannot for sure know whether the data exists until one has read both the data and tag from DRAM. A hit predictor is employed to decide whether or not to parallelize the access to the DRAM cache with the access to the uncached copy of the data.

The two main memory caches I propose in this thesis, Duplicon Cache and Continuous Row Compaction, both employ SRAM tag stores and DRAM data stores. The SRAM tag store is maintained at the memory controller, giving the memory controller knowledge of which data have been duplicated/migrated, and to where. I leave adoption of DRAM tag stores as future work (Section 7.2.1).

### 3.2 Data Store

#### 3.2.1 Reserving Physical Memory for Cache Data Store

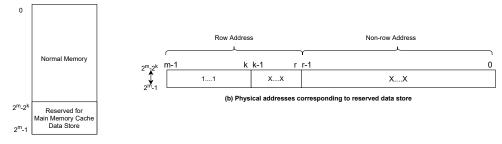

Both Duplicon Cache and Continuous Row Compaction reserve memory at the top of the physical address space as the cache data store to store duplicated/migrated data. This is shown in Figure 3.2. Suppose the total physical address space is  $2^m$  bytes, and we wish to reserve the top  $2^k$  bytes for the data store. This reservation is done by under-reporting the amount of physical memory available to the software at boot time; that is, rather than reporting there are  $2^m$  bytes of physical memory available, the hardware would report that there are only  $2^m - 2^k$  bytes of physical memory available. This prevents the software from using physical memory between the addresses  $2^m - 2^k$  and  $2^m - 1$ , . This is shown in Figure 3.2(a).

(a) Partitioning of physical address space

Figure 3.2: Reserving the top  $2^k$  bytes of an  $2^m$  physical address space.

Figure 3.2(b) shows this reserved data store maps to physical addresses where the high bits m - 1 to k are 1s. Since the row address bits are always placed at the highest order end of the physical address (see Figure 2.4(a) and (c)), we are essentially reserving the highest  $2^{k-r}$  row addresses in each DRAM device for the main memory cache data store, where r is the position of the lowest row address bit. Our example in Figure 2.4(e), where we reserved the top  $2^9 = 512$ KB at the top of the physical address space for row compaction, was an example of reserving memory for the main memory cache data store where m = 36, k = 19, and r = 19.

## 3.3 Tag Store

We now consider issues relating to the design of a main memory cache tag store.

#### 3.3.1 Serial vs. Parallel Tag and Data Accesses