Copyright

by

Feng Wen

2020

# The Dissertation Committee for Feng Wen Certifies that this is the approved version of the following dissertation:

# Strain Engineered Si-Ge Nanowire Heterostructures and Josephson Junction Field-Effect Transistors for Logic Device Applications

| Committee:                |

|---------------------------|

| Emanuel Tutuc, Supervisor |

| Edward T. Yu              |

| Leonard F. Register       |

| Li Shi                    |

| Sanjay K. Banerjee        |

# Strain Engineered Si-Ge Nanowire Heterostructures and Josephson Junction Field-Effect Transistors for Logic Device Applications

by

### Feng Wen

#### **Dissertation**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

Aug 2020

## **Dedication**

To my parents and wife for their love and support.

### Acknowledgements

I would like to thank all who have helped me through the career of a graduate student. In particular, I want to express my sincere gratitude to my advisor, Prof. Emanuel Tutuc. His unfailing guidance and thoughtful critiques of my work, combined with his extensive knowledge in this field, have paved my way to become a better graduate student and researcher. He never hesitates to get his hands dirty to help his students set up experimental facilities and solve problems. He is always there when his students seek guidance. His enthusiasm and dedication to teaching and research, and in general to science and engineering have been inspiring his students to commit to keep learning and producing quality research work. I strongly believe everyone graduating from this group will have a bright future. Over these years in graduate school, I have learned the patience and rigorous approach to solve scientific problems systematically. I also want to thank Prof. Edward T. Yu, Prof. Leonard F. Register, Prof. Li Shi and Prof. Sanjay K. Banerjee, for their time to serve in my dissertation committee and provide valuable guidance and feedback.

The support from my colleagues and friends has made this long journey a more delightful experience. I want to thank my previous and current groupmates for their assistance with the experimental facility use and helpful discussions on research. The friendship and kindness of senior groupmates Babak Fallahazad, Chris Corbet, Kayoung Lee, Kyounghwan Kim, Hema Chandra Prakash Movva and Stefano Larentis helped me fit into the group soon after I came to the country. They are always ready to answer all my questions about either research or everyday life. Younger groupmates Will Burg, Yimeng Wang and Wooyoung Yoon have also offered great help and friendship. Foremost, David Dillen, his mentorship has greatly accelerated my learning speed of the new research projects. He not only trains me on operating most of the relevant experimental

tools, but also teaches me important backgrounds and analysis skills. In addition, thanks to his excellent work, I can take many things for granted to focus on unexplored part of my research topic. I am also glad to have the opportunity to collaborate with other fellows from UT including William Hsu, Gabbi Coloyan and Brandon Smith to perform research work. I also want to thank Prof. Javad Shabani in NYU for our collaboration. He has helped arrange two visits for me to go to New York City where I can enjoy the privilege to use their fancy dilution refrigerator and live in downtown Manhattan. I also thank his students Joseph Yuan and William Mayer for their help with my measurements during my stay there. I would also like to thank my colleagues from other research groups in Microelectronic Research Center (MRC) for their friendship and inspiring conversations, including Michael Rodder, Xiao Wang, Chi-jui Chung, Zhoufeng Ying, Zeyu Pan, Hai Yan, Amritesh Rai, Anupam Roy, Andreas Hsieh, Zuoming Dong, Yinan Wang, Xian Wu, Xiaohan Wu, Hasibul Alam, Xintong Li, Boxue Chen etc.

The hard work and support from the technicians and administrators in the Department of the Electrical and Computer Engineering as well as MRC are crucial and allow me to focus on my research work. I want to thank Bill Ostler, Christine Wood, Gerlinde Sehne, James Hitzfelder, Jesse James, Johnny Johnson, Joyce Kokes, Melanie Gulick, Melody Singleton and Ricardo Garcia for their efforts. I also want to thank Andrei Dolocan and Raluca Gearba form Texas Material Institute for their assistance in operating experimental facilities.

The journey to earning this degree is challenging. Thankfully, constant encouragement and support from my parents Jiabin Wen and Meilan Zhou over the years enable me to go this far, and I want to express my best gratitude and love to them. Moreover, the challenges of either researches or life have been vastly relieved by my amazing wife Hehui Zhou. I feel blessed to have her be my

companion, life has become better day by day and I cannot wait to see where it will take us to in the next phase of my career. I also thank my parents-in-law Hongsheng Zhou and Wei Wang for their concern these years. Without the endless love and encouragement of my family throughout these years, I undoubtedly would not have become who and where I am today.

#### **Abstract**

Strain Engineered Si-Ge Nanowire Heterostructures and Josephson Junction Field-Effect Transistors for Logic Device Applications

Feng Wen, Ph.D.

The University of Texas at Austin, 2020

Supervisor: Emanuel Tutuc

There has been relentless effort on the physical scaling of silicon (Si) metal-oxidesemiconductor field-effect transistors (MOSFETs) in pursuit of higher computing power in the past decades. Silicon and germanium (Ge) based nanowires are compatible with the standard Si process and promising for the ultimately scaled devices, by allowing the gate-all-around geometry and integration of strain engineering through radial heterostructures to address device-scaling limitations. In the first part of the thesis, advances in probing the strain of radial nanowire heterostructures and carrier mobility enhancement through strain engineering are presented. We present a sequence of structural characterization techniques for Ge-Si<sub>x</sub>Ge<sub>1-x</sub> and Si-Si<sub>x</sub>Ge<sub>1-x</sub> coreshell nanowires that extends to all types of Si-Ge radial nanowire heterostructures examined in the thesis. We combine planar and cross-sectional transmission electron microscopy to identify the crystal structure, orientation and morphology of the nanowire heterostructures. We then apply continuum elasticity model to calculate the strain distribution, which coupled with the lattice dynamic theory yields the Ge-Ge or Si-Si Raman modes under strain, showing good agreement with the experimental values acquired via Raman spectroscopy. We also study the electrical properties of  $Si_xGe_{1-x}$ -Si core-shell nanowires by fabricating and characterizing *n*-type MOSFETs,

and show that the tensile strain in the Si shell leads to a 40% electron mobility enhancement compared to bare Si nanowire MOSFETs. Additionally, we demonstrate both n-type and p-type MOSFETs using  $Si_xGe_{1-x}$ -Ge-Si core-double-shell nanowires as channel, designed so that holes populate the Ge shell and electrons populate the Si shell, with mobility enhancement of both carriers thanks to the compressive and tensile strain in the respective region. We also extract the valence band offset from the decoupled hole transport in the two shells at low temperature, overcoming the issue that most techniques available to probe the band structure in planar heterostructures are not promptly applicable.

Reducing the operation temperature provides an additional path for system optimization in addition to the shrinking of device geometry. In the second part of the thesis, we explore a Boolean logic device suitable for cryogenic computing. We execute a combined effort of modeling and experimental characterization to examine the feasibility of Josephson junction field-effect transistors (JJ-FETs) for logic device applications at low temperatures. JJ-FETs are similar to MOSFETs, with their source and drain electrodes being superconducting at the operation temperature. We develop a compact model for JJ-FETs operating in the short ballistic regime, and perform circuit level simulations to investigate the criteria of signal restoration and fan-out for JJ-FET logic gates. We also experimentally demonstrate the operation of JJ-FETs based on an InAs quantum well heterostructure platform. We perform self-consistent Poisson-Schrödinger simulations, finding different gate voltage regimes where carriers populate one or more subbands in different vertical positions of the heterostructure. Furthermore, we extend the short ballistic model to interpret the experimental data, and discuss the impact of a low oxide/channel interface quality on the implementation of practical JJ-FET logic devices.

## **Table of Contents**

| List of Tables                                                                                                   | xiv                 |

|------------------------------------------------------------------------------------------------------------------|---------------------|

| List of Figures                                                                                                  | XV                  |

| Chapter 1 : Introduction and Motivation                                                                          | 1                   |

| 1.1 CMOS scaling                                                                                                 | 1                   |

| 1.2 Short channel effects                                                                                        | 4                   |

| 1.3 CMOS innovations                                                                                             | 5                   |

| 1.4 Nanowire fabrication                                                                                         | 7                   |

| 1.5 Radial nanowire heterostructure                                                                              | 9                   |

| 1.6 Cryogenic computing                                                                                          | 12                  |

| 1.6.1 Cryogenic CMOS                                                                                             | 12                  |

| 1.6.2 Josephson junction logic devices                                                                           | 17                  |

| 1.7 Chapter summary and organization                                                                             | 20                  |

| Chapter 2: Shell Morphology and Raman Spectra of Epitaxial Ge-SixGe                                              | 1-x and Si-SixGe1-x |

| Core-Shell Nanowires                                                                                             | 24                  |

| 2.1 Introduction                                                                                                 | 24                  |

| 2.2 Growth of Ge-Si <sub>x</sub> Ge <sub>1-x</sub> and Si-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowires | 26                  |

| 2.3 Planar view TEM imaging                                                                                      | 32                  |

| 2.4 Cross-sectional TEM imaging                                                                                  | 35                  |

| 2.5 Strain calculation                                                                                           | 40                  |

| 2.5.1 Introduction to strain                                                                                     | 40                  |

| 2.5.2 Strain calculations using the finite element method                                                        | 42                  |

| 2.6 Raman spectrum measurement                                                                                   | 44                  |

| 2.6.1 Introduction to Raman spectroscopy                                                                         | 44                  |

| 2.6.2 Raman Spectroscopy of Si and Ge                                                                            | 46                  |

| 2.6.3 Experimental setup of Raman spectroscopy                                                                            | 47               |

|---------------------------------------------------------------------------------------------------------------------------|------------------|

| 2.6.4 Raman spectra of Ge-Si <sub>x</sub> Ge <sub>1-x</sub> and Si-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowires | 49               |

| 2.7 Calculate the strain-induced shift of Raman modes using lattice dynamic theory                                        | 51               |

| 2.8 Simulation of the strain distribution and calculation of the strain-induced Raman mo                                  | ode shift        |

| for core-shell nanowires                                                                                                  | 54               |

| 2.9 Orientation dependent shell growth rate for Si-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowires                 | 58               |

| 2.10 Summary                                                                                                              | 60               |

| Chapter 3: Enhanced Electron Mobility in Non-Planar Tensile Strained Si Epi                                               | taxially         |

| Grown on Si <sub>x</sub> Ge <sub>1-x</sub> Nanowires                                                                      | 62               |

| 3.1 Introduction                                                                                                          | 62               |

| 3.2 Performance enhancement in tensile strained-Si <i>n</i> -type MOSFETs                                                 | 64               |

| 3.3 Growth, SEM and TEM imaging of Si <sub>x</sub> Ge <sub>1-x</sub> -Si core-shell nanowires                             | 66               |

| 3.4 Raman spectra and strain calculation of Si <sub>x</sub> Ge <sub>1-x</sub> -Si core-shell nanowires                    | 69               |

| 3.5 Diameter dependence of the strain and Si-Si Raman modes in Si <sub>x</sub> Ge <sub>1-x</sub> -Si co                   | ore-shell        |

| nanowires                                                                                                                 | 73               |

| 3.6 Electron transport in Si <sub>0.41</sub> Ge <sub>0.59</sub> -Si core-shell nanowires                                  | 75               |

| 3.7 Nanowire MOSFET fabrication                                                                                           | 79               |

| 3.8 Extraction of $C_{\Omega}$ for nanowire MOSFETs                                                                       | 81               |

| 3.9 Summary                                                                                                               | 83               |

| Chapter 4: Strained SixGe1-x-Ge-Si Core-double-shell Nanowire Heterostructu                                               | res for          |

| Simultaneous Hole and Electron Mobility Enhancement                                                                       | 84               |

| 4.1 Introduction                                                                                                          | 84               |

| 4.2 Strained Si/Ge dual-channel planar heterostructure for high mobility n-type and                                       | l <i>p</i> -type |

| MOSFETs                                                                                                                   | 86               |

| 4.3 Growth and TEM imaging of Si <sub>x</sub> Ge <sub>1-x</sub> -Ge-Si core-double-shell nanowires                        | 89               |

| 4.4 Raman spectra and strain calculation of Si <sub>0.5</sub> Ge <sub>0.5</sub> -Ge-Si core-double-shell nanowire         | es 93            |

| 4.5 Electron and hole transport in Si <sub>0.5</sub> Ge <sub>0.5</sub> -Ge-Si core-double-shell nanowires                 | 96               |

| 4.6 Band alignment between the Ge and Si shell in Si <sub>0.5</sub> Ge <sub>0.5</sub> -Ge-Si core-double-s |               |

|------------------------------------------------------------------------------------------------------------|---------------|

| 4.7 Design and optimization of Si <sub>0.5</sub> Ge <sub>0.5</sub> -Ge-Si core-double-shell nanowire MOS   |               |

| 4.8 $\mu_{eff}$ extraction and simulation of charge density and transport                                  |               |

| ,,                                                                                                         |               |

| 4.8.1 $\mu_{eff}$ extraction                                                                               |               |

| 4.8.2 Simulation of charge density and transport                                                           | 109           |

| 4.9 Summary                                                                                                | 110           |

| hapter 5: Compact Modeling and Simulation of JJ-FETs for Cryogenic F                                       | Boolean Logic |

| pplicationspplications                                                                                     | 112           |

| 5.1 Introduction                                                                                           | 112           |

| 5.2 Superconductivity and Josephson effect                                                                 | 113           |

| 5.2.1 Superconductivity                                                                                    | 113           |

| 5.2.2 Josephson effect                                                                                     | 113           |

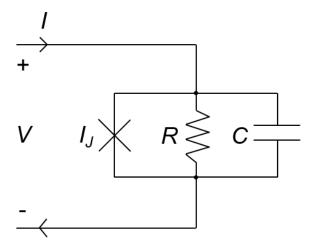

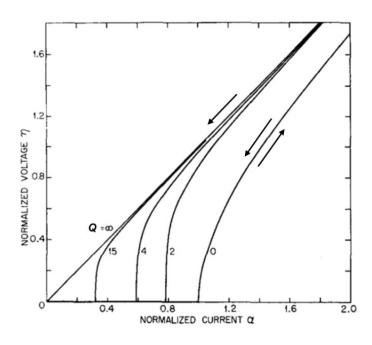

| 5.2.3 RCSJ model                                                                                           | 115           |

| $5.3 V_{DD}$ scaling at cryogenic temperatures                                                             | 118           |

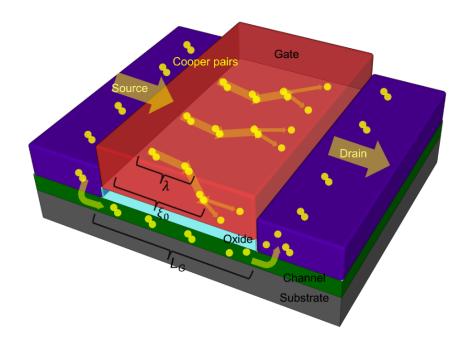

| 5.4 Device model of the JJ-FET                                                                             | 119           |

| 5.5 JJ-FET logic gate and memory                                                                           | 123           |

| 5.5.1 Static analysis                                                                                      | 123           |

| 5.5.2 Dynamic analysis                                                                                     | 127           |

| 5.5.3 Global clock to reset underdamped JJ-FETs                                                            | 133           |

| 5.6 Design considerations and trade-offs                                                                   | 136           |

| 5.7 Circuit diagram and Verilog-a code for simulation                                                      | 139           |

| 5.7.1 Circuit diagram                                                                                      | 139           |

| 5.7.2 Verilog-a code                                                                                       | 140           |

| 5.7.3 Simulation of the $I - V$ characteristics of a JJ                                                    | 142           |

| 5.8 Summary                                                                                                | 143           |

| Chapter 6: Epitaxial Al-InAs Heterostructures as Platform for Josephson Jun       | ction Field-  |

|-----------------------------------------------------------------------------------|---------------|

| effect Transistor Logic Devices                                                   | 145           |

| 6.1 Introduction                                                                  | 145           |

| 6.2 Substrate growth and device fabrication process                               | 146           |

| 6.3 JJ-FET $I - V$ characteristics                                                | 151           |

| 6.4 Self-consistent Poisson-Schrödinger simulation                                | 153           |

| 6.5~C-V and electron transport data of long-channel MOSFETs and JJ-FETs           | 156           |

| 6.6 Feasibility of JJ-FETs using the InAs quantum well heterostructure as channel | for practical |

| JJ-FET logic gates                                                                | 162           |

| 6.7 Summary                                                                       | 165           |

| Chapter 7 : Summary and Future Work                                               | 166           |

| 7.1 Thesis summary                                                                | 166           |

| 7.2 Ongoing project and outlook on future work                                    | 169           |

| Appendix A: List of Journal Publications                                          | 183           |

| Appendix B: List of Symbols                                                       | 184           |

| Appendix C: List of Acronyms                                                      | 189           |

| References                                                                        | 191           |

## **List of Tables**

| Table 1.1: Scaling rules for three approaches (Table adapted from Ref. [2])                                          |

|----------------------------------------------------------------------------------------------------------------------|

| Table 1.2: Temperature scaling factors for MOSFET operation (Table adapted from Ref. [14])15                         |

| Table 2.1: Growth conditions of the core-shell nanowires discussed in Chapter 2                                      |

| Table 2.2: Specifications of the core-shell nanowire growths discussed in Chapter 2                                  |

| Table 2.3: Surface energy of various surfaces for cubic Si and Ge [50]    39                                         |

| Table 2.4: Lattice constant and cubic elastic stiffness of Si and Ge [55, 56]                                        |

| Table 3.1: Growth conditions of the nanowires discussed in Chapter 3                                                 |

| <b>Table 3.2:</b> Deformation potentials for $\Delta$ and $L$ valleys of Si and Ge used in Chapter 3 [98] 73         |

| Table 4.1: Growth conditions of the nanowires discussed in Chapter 4    91                                           |

| Table 4.2: Deformation potentials of the Si and Ge shell used in Chapter 4                                           |

| Table 4.3: Summary of the Si and Ge shell thickness for Si <sub>0.5</sub> Ge <sub>0.5</sub> -Ge-Si core-double-shell |

| nanowires                                                                                                            |

| Table 5.1: Q of the JJ-FET inverter   131                                                                            |

| <b>Table 5.2:</b> <i>Q</i> of JJ-FET NOR gate                                                                        |

| Table 7.1: CVD growth conditions of three P-doped epitaxial Si film growths                                          |

| <b>Table 7.2:</b> $R_C$ and $R_S$ of the TLM devices, along with $t$ , $\rho$ and the phosphorus doping              |

| concentration of the Si epi-layer for the three growths                                                              |

# **List of Figures**

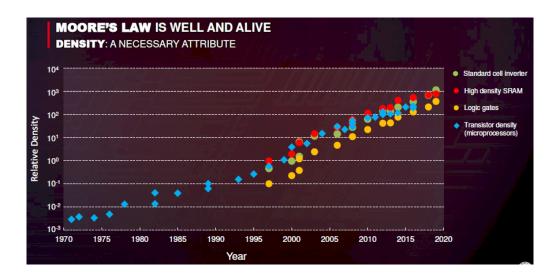

| Figure 1.1: Historical data of the CMOS scaling trend from TSMC. (Figure adapted from Ref.             |

|--------------------------------------------------------------------------------------------------------|

| [1])                                                                                                   |

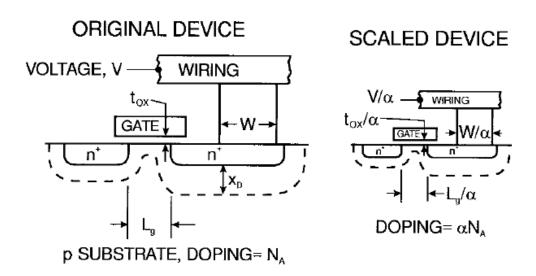

| Figure 1.2: Schematic illustration of the CMOS scaling by a factor of $\alpha$ . (Figure adapted from  |

| Ref. [2])                                                                                              |

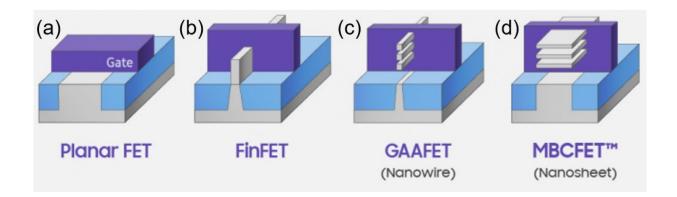

| Figure 1.3: Evolution of the MOSFET geometry to enhance the gate electrostatic control. (a)            |

| Planar MOSFET. (b) Tri-gate FinFET. (c) GAA nanowire MOSFET. (d) GAA                                   |

| nanosheet MOSFET. (Figure adapted from Ref. [4])                                                       |

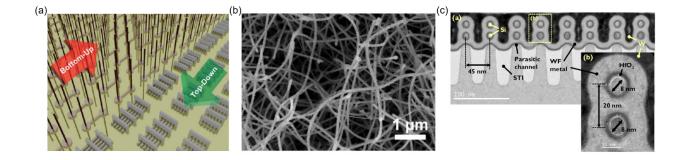

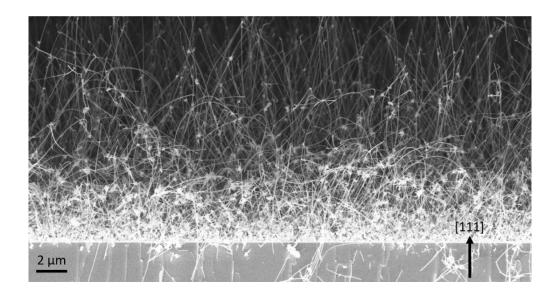

| Figure 1.4: Nanowire fabrication techniques. (a) Schematics illustrating the bottom-up and top-        |

| down nanowire fabrication approaches. (b) SEM image of an entangled mesh of Ge                         |

| nanowires grown by the SFLS method. (c) Cross-sectional TEM image of the channels                      |

| of GAA nanowire MOSFETs. (Figure adapted from Refs. [5, 6])9                                           |

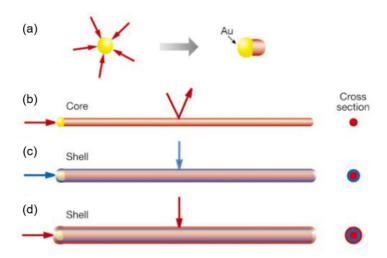

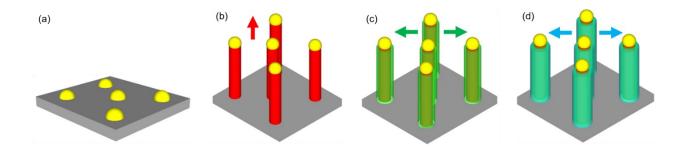

| Figure 1.5: Synthesis of core-shell nanowires. (a) Au catalyst and catalyzed nucleation of             |

| nanowire cores. (b) One-dimensional nanowire core. (c) Precursor alteration and                        |

| homogenous reactant decomposition on the nanowire surface lead to a thin, uniform                      |

| shell. (d) Shell growths can be repeated multiple times by modulating precursors.                      |

| (Figure adapted from Ref. [7])                                                                         |

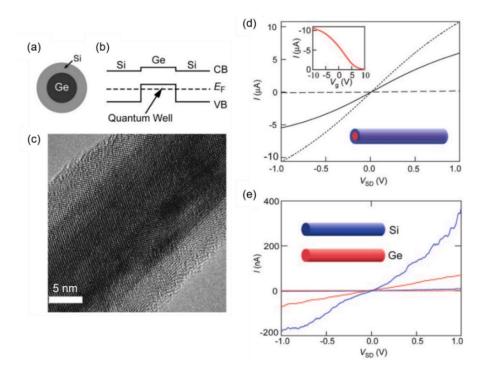

| Figure 1.6: Structure and room temperature electrical transport property of Ge-Si core-shell           |

| nanowires. (a) Schematic of the Ge-Si core-shell nanowire cross-section. (b) Band                      |

| diagram along the diameter, effectively a Si/Ge/Si heterostructure. (c) High-resolution                |

| TEM image showing a contrast due to the different atomic mass between the Ge core                      |

| and Si shell, whose diameter and thickness are 15 nm and 5 nm, respectively. (d)                       |

| Output characteristics of a Ge-Si core-shell nanowire MOSFET, where different                          |

| curves correspond to different $V_G$ of 10 V (dashed line), 0 V (solid line) and -10 V                 |

| (dotted line). The inset shows the associated transfer characteristics at $V_D = -1$ V. (e)            |

| Output characteristics of bare Ge (red curves) and Si (blue curves) nanowire                           |

| MOSFETs, at $V_G = 0 \text{ V}$ and -10 V. (Figure adapted from Ref. [8])                              |

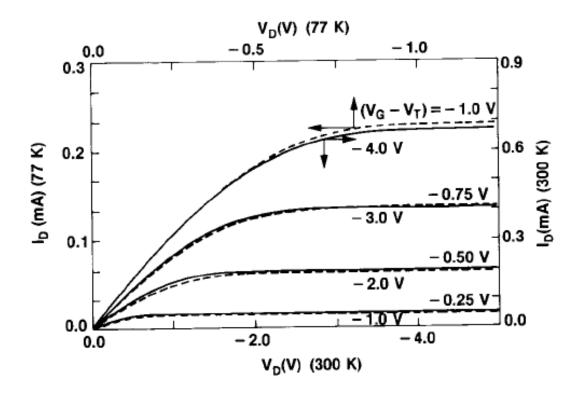

| Figure 1.7: Output characteristics of a long-channel $p$ -type MOSFET at $T=300~\mathrm{K}$ and $T=77$ |

| K. (Figure adapted from Ref. [13])14                                                                   |

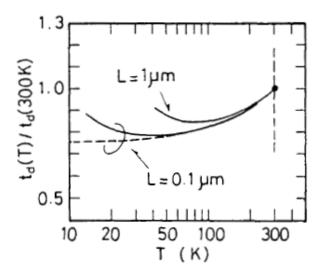

| Figure 1.8: | Temperature dependence of the gate delay time following the temperature-scaling rule                                                   |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------|

|             | summarized in Table 1.2. $V_{DD} = 5 \text{ V}$ at 300 K. The dashed line branching from the                                           |

|             | $L_G = 0.1$ µm device is calculated assuming an unscaled $V_{DD}$ of 1 V at temperatures                                               |

|             | below 60 K. (Figure adapted from Ref. [14])16                                                                                          |

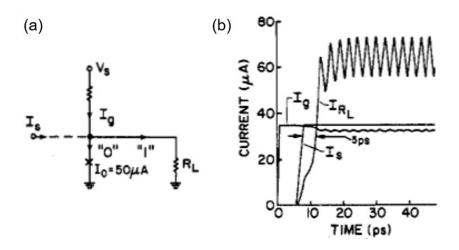

| Figure 1.9: | (a) Schematic of a JJ current-steering device. (b) Computer simulation indicating the                                                  |

|             | switching delay using $I_g = I_s = 35  \mu A$ , $I_0 = 50  \mu A$ , $R_L = 12  \Omega$ , $V_S = 10  \text{mV}$ . (Figure               |

|             | adapted from Ref. [19])                                                                                                                |

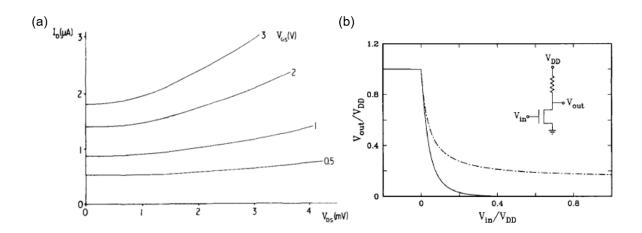

|             | 2: (a) Output characteristics of a JJ-FET. (b) Voltage transfer curves of a JJ-FET                                                     |

|             | inverter (solid line) and a NMOS inverter (dash-dotted line). Inset is the device                                                      |

|             | circuitry. (Figures adapted from Refs. [24, 26])                                                                                       |

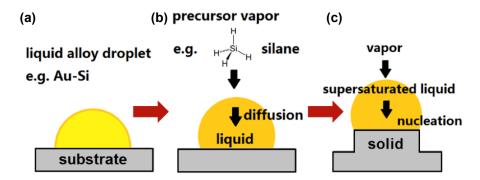

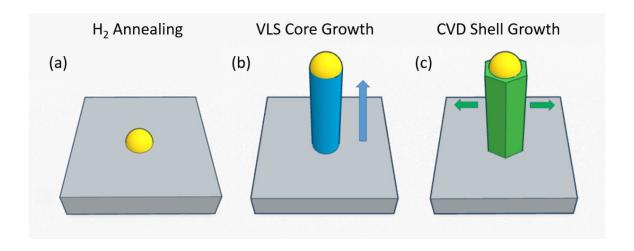

| Figure 2.1: | Schematic illustrating the VLS growth process. (a) Thermal annealing to form liquid                                                    |

|             | alloy droplet. (b) Precursor molecules cracking at the vapor/liquid interface and                                                      |

|             | diffusing through the liquid droplet. (c) Nucleation at the liquid/solid interface. (Figure                                            |

|             | adapted from Ref. [35])                                                                                                                |

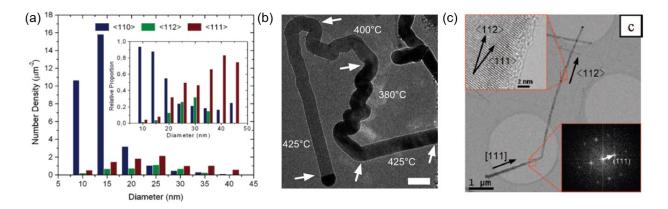

| Figure 2.2: | (a) Number density vs. diameter for different orientations of Si nanowires. Inset is the                                               |

| :           | relative proportion of each orientation. (b) A frame from an in-situ TEM imaging                                                       |

| :           | movie of the Si nanowire growth, with temperature changed a few times in the process.                                                  |

|             | Arrows mark the onset and end of the temperature window. Scale bar is 250 nm. (c)                                                      |

|             | A low-magnification TEM image of a two-step growth, the Si nanowire kinks to the                                                       |

|             | <112> direction from <111> when the total pressure of the diluted SiH <sub>4</sub> changes from                                        |

|             | 3 to 15 mBar. (Figure adapted from Refs. [38-40])                                                                                      |

| Figure 2.3: | Schematics illustrating the Ge-Si <sub>x</sub> Ge <sub>1-x</sub> or Si-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowire growth    |

|             | process. (a) Hydrogen annealing. (b) VLS core growth. (c) Epitaxial CVD shell                                                          |

|             | growth. Arrows represent the growth direction in each growth regime                                                                    |

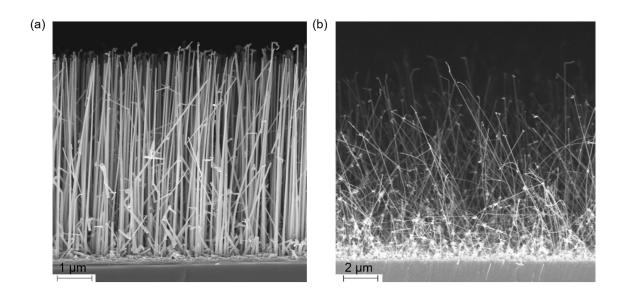

| Figure 2.4: | SEM images of (a) Ge-Si <sub>x</sub> Ge <sub>1-x</sub> and (b) Si-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowires from growth   |

|             | A and C                                                                                                                                |

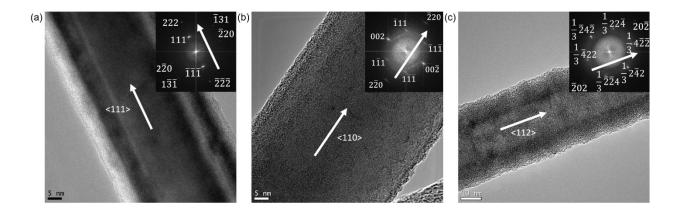

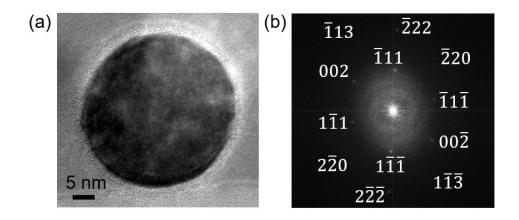

| Figure 2.5: | Planar view TEM images of Ge-Si <sub>x</sub> Ge <sub>1-x</sub> and Si-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowires. (a)      |

|             | <111> oriented Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowire. (b) <110> oriented Si-Si <sub>x</sub> Ge <sub>1-x</sub> core- |

|             | shell nanowire. (c) <112> oriented Si-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowire. The insets are the                        |

| •           | FFTs of the TEM images. Arrows indicate the nanowire growth directions in each                                                         |

|             | panel                                                                                                                                  |

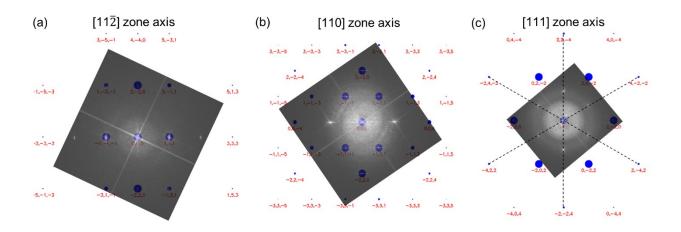

| Figure 2.6: Determ         | nination of the reciprocal lattice indices in the FFIs by overlapping the FFIs                          |

|----------------------------|---------------------------------------------------------------------------------------------------------|

| and the                    | e standard diffraction patterns of cubic Si/Ge. (a) <111> oriented Ge-Si <sub>x</sub> Ge <sub>1-x</sub> |

| core-sh                    | tell nanowire, assuming the zone axis along [11 $\overline{2}$ ]. (b) <110> oriented Si-                |

| $Si_xGe_1$                 | x core-shell nanowire, assuming the zone axis along [110]. (c) <112> oriented                           |

| Si-Si <sub>x</sub> C       | Ge <sub>1-x</sub> core-shell nanowire, assuming the zone axis along [111]34                             |

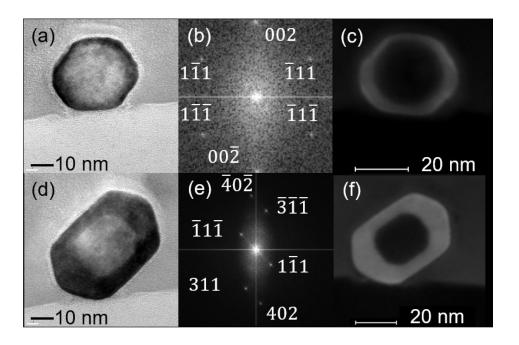

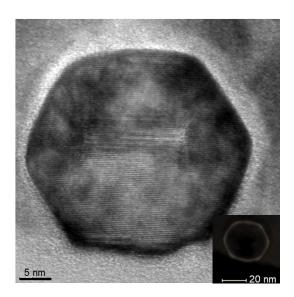

| <b>Figure 2.7:</b> (a) Cro | ess-sectional TEM image of a <110> oriented Si nanowire. (b) FFT of panel (a)                           |

| data                       |                                                                                                         |

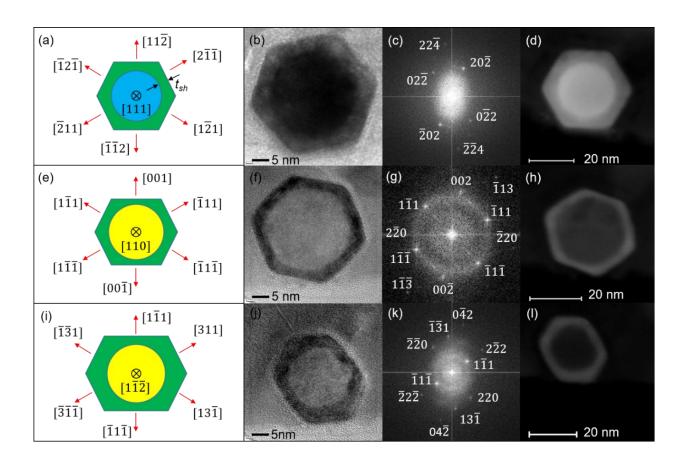

| Figure 2.8: Schem          | atics, HRTEM, FFT and STEM data of the three different types of core-shell                              |

| nanowi                     | res discussed in Chapter 2. The HRTEM images and their FFTs are identical                               |

| in orier                   | ntation, enabling a direct correspondence between FFTs to plane indices in real                         |

| space i                    | mages. (a) Ge-Si <sub>x</sub> Ge <sub>1-x</sub> nanowire with the growth direction along the <111>      |

| axis, sh                   | lowing a cylindrical Ge core, and hexagonal $Si_xGe_{1-x}$ shell with six $\{112\}$ facets.             |

| (b-d) C                    | cross-sectional HRTEM, FFT and STEM data of a Ge-Si <sub>x</sub> Ge <sub>1-x</sub> nanowire. (e)        |

| Type I                     | Si-Si <sub>x</sub> Ge <sub>1-x</sub> nanowire with the growth direction along the <110> axis, showing   |

| a cylin                    | drical Si core and hexagonal $Si_xGe_{1-x}$ shell with two {100} and four {111}                         |

| facets.                    | (f-h) Cross-sectional HRTEM, FFT and STEM data of a <110> oriented Si-                                  |

| $Si_xGe_1$                 | x nanowire. (i) Type II Si-Si <sub>x</sub> Ge <sub>1-x</sub> nanowire with the growth direction along   |

| the <11                    | 2> axis, showing a cylindrical Si core and hexagonal Si <sub>x</sub> Ge <sub>1-x</sub> shell with two   |

| {111} :                    | and four {113} facets. (j-l) Cross-sectional HRTEM, FFT and STEM data of a                              |

| <112>                      | oriented Si-Si <sub>x</sub> Ge <sub>1-x</sub> nanowire                                                  |

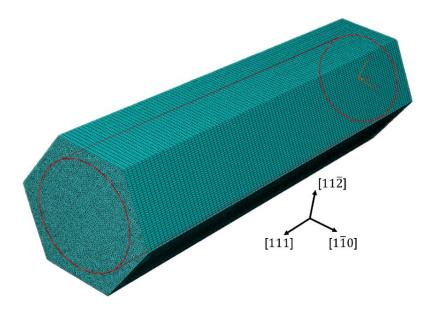

| Figure 2.9: An ex          | ample of the simulated structure for a <111> oriented Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell   |

| nanowi                     | re, where the meshing elements are displayed and the contour of the core is                             |

| highlig                    | hted by red lines. The coordinate presents the crystal orientation of the                               |

| nanowi                     | re                                                                                                      |

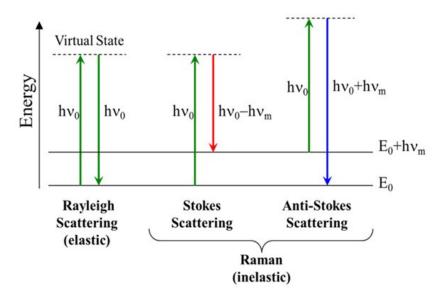

| Figure 2.10: Scher         | natics showing the elastic and inelastic scattering of photons in a material 46                         |

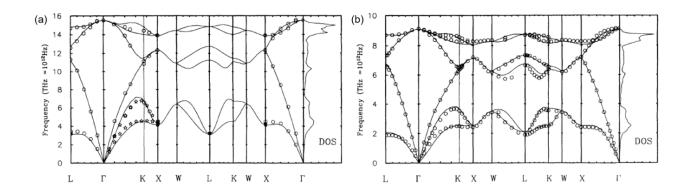

| Figure 2.11: Phone         | on dispersion relation for (a) Si and (b) Ge. (Figure adapted from Ref. [57]) 47                        |

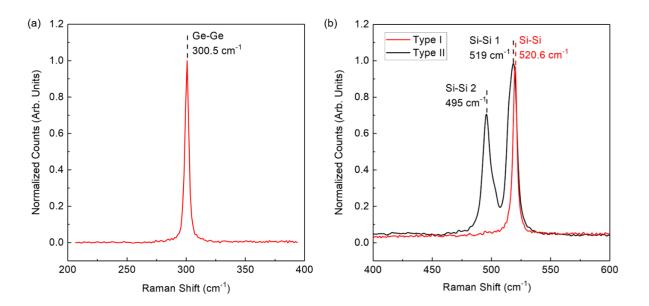

| Figure 2.12: Rama          | in spectra collected from individual Ge and Si nanowires. (a) Raman spectrum                            |

| of a Ge                    | e nanowire (NW039 in the growth catalog). (b) Raman spectra of two types of                             |

| Si nano                    | owires, presented in red and black lines, respectively (NW185 in the growth                             |

| catalog                    | ). The peak position associated with individual Raman mode is marked with a                             |

| vertical                   | l dashed line                                                                                           |

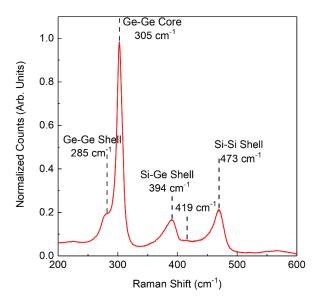

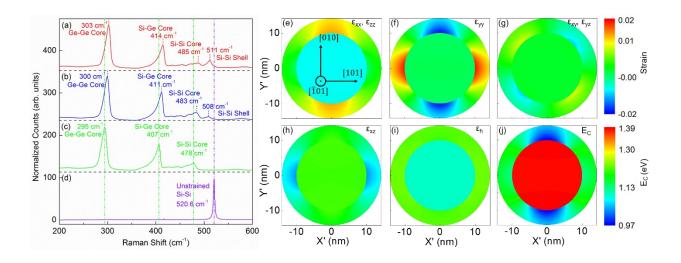

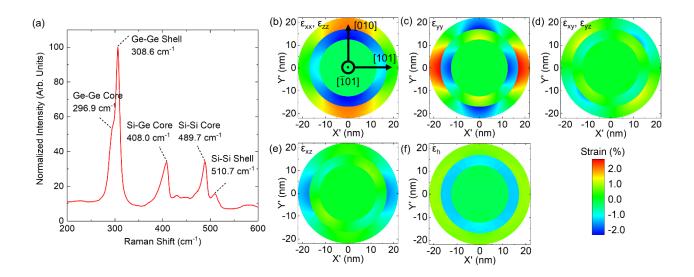

| $\textbf{Figure 2.13:} \ Raman \ spectrum \ of \ an \ individual \ Ge-Si_xGe_{1-x} \ core-shell \ nanowire. \ The \ peak \ position$       |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| associated with each Raman mode is marked with a vertical dashed line 50                                                                   |

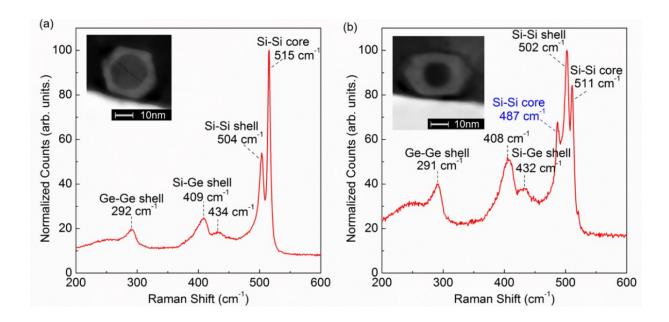

| Figure 2.14: Comparison of Raman spectra between $<110>$ and $<112>$ oriented Si-Si $_x$ Ge $_{1-x}$ core-                                 |

| shell nanowires. (a) Raman spectrum of a <110> oriented Si-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell                                    |

| nanowire with two Si-Si Raman modes. Inset: cross-sectional STEM micrograph of                                                             |

| the same nanowire as in the main panel. (b) Raman spectrum of a <112> oriented Si-                                                         |

| Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowire with three Si-Si Raman modes. An additional Si-Si core                               |

| mode is observed. The thicker shell leads to higher intensity of the Si-Si, Ge-Ge, and                                                     |

| Si-Ge shell modes. Inset: cross-sectional STEM micrograph of the same nanowire.52                                                          |

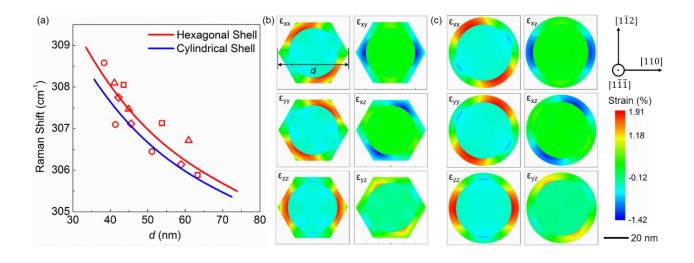

| $\textbf{Figure 2.15:} \ \ \textbf{Strain distribution and strain-induced Raman mode shift of Ge-Si}_{x} Ge_{1-x} \ \ \textbf{core-shell}$ |

| nanowires, with $x = 0.57$ . (a) Diameter dependence of core Ge-Ge Raman modes                                                             |

| measured along individual Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowires, where the nanowire                                    |

| tapering leads to a diameter change. The different symbols correspond to different                                                         |

| nanowires. The red and blue solid lines indicate the calculated core Ge-Ge Raman                                                           |

| modes using cylindrical and hexagonal shell cross-sections, respectively. (b)                                                              |

| Calculated strain contour plots of Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowire with a hexagonal                               |

| shell. (c) Calculated strain contour plots of Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowire with a                              |

| cylindrical shell                                                                                                                          |

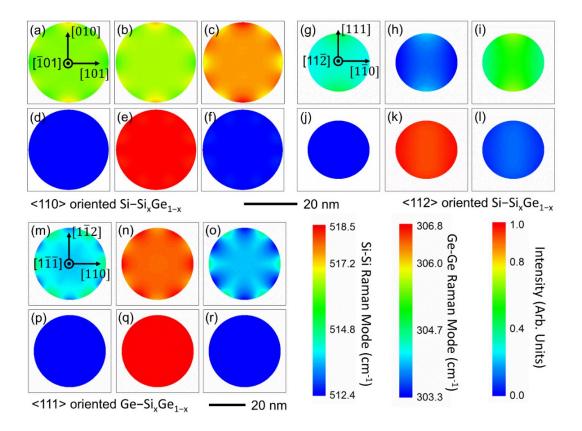

| Figure 2.16: Raman modes shift and intensity calculations for the core regions of core-shell                                               |

| nanowires. (a-c) Three Si-Si Raman modes in the core region of a <110> oriented Si-                                                        |

| Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowire and (d-f) the associated intensities. (g-i) Three Si-Si                              |

| Raman modes in the core region of a <112> oriented Si-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowire                                |

| and (j-l) the associated intensities. (m-o) Three Ge-Ge Raman modes in the core region                                                     |

| of a <111> oriented Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowires and (p-r) the associated                                     |

| intensities. Only one core Raman mode is active (with non-zero intensity) in each kind                                                     |

| of nanowire. The upper scale bar is for panels (a-l), while the lower scale bar is for                                                     |

| panels (m-r)                                                                                                                               |

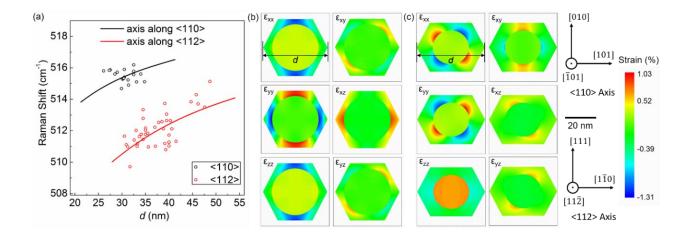

| Figure 2.17: Strain distribution and strain-induced Raman mode shift of $Si\text{-}Si_xGe_{1\text{-}x}$ core-shell                         |

| nanowire, with $x = 0.68$ . (a) Diameter dependence of core Si-Si Raman modes for the                                                      |

| two types of Si-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowires. The symbols (solid lines) represent                                |

| experimental data (calculations). (b) Calculated strain in <110> oriented, and (c)                                                         |

| <112> oriented Si-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowires. The strain profiles are distinct due to                      |

|----------------------------------------------------------------------------------------------------------------------------------------|

| the elastic constants' anisotropy                                                                                                      |

| Figure 2.18: Shell thickness difference between $<110>$ and $<112>$ oriented Si-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell           |

| nanowires are exaggerated at higher shell growth temperatures. (a-c) and (d-f) are                                                     |

| cross-sectional HRTEM, FFT and STEM images for <110> and <112> oriented Si-                                                            |

| Si <sub>x</sub> Ge <sub>1-x</sub> nanowires (growth D), respectively                                                                   |

| Figure 2.19: Cross-sectional TEM image of a Si-Si $_x$ Ge $_{1-x}$ core-shell nanowire with a very thin                                |

| $Si_xGe_{1-x}$ shell. The shell shape is still hexagonal and covers the complete perimeter of                                          |

| the core. Inset is the corresponding STEM image                                                                                        |

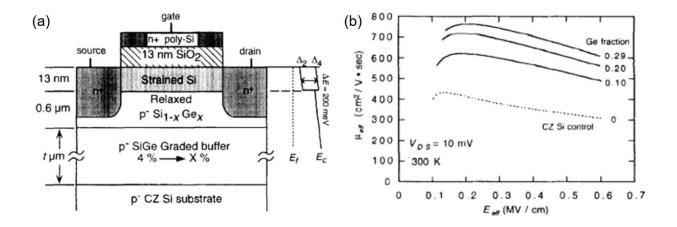

| Figure 3.1: (a) Schematic of a strained Si n-type MOSFET. The band diagram is for a Ge                                                 |

| composition of 29% in the relaxed substrate. (b) Electron $\mu_{eff}$ vs. $E_{eff}$ for long-                                          |

| channel MOSFETs with different Ge fraction in the virtual substrate. (Figure adapted                                                   |

| from Ref. [86])                                                                                                                        |

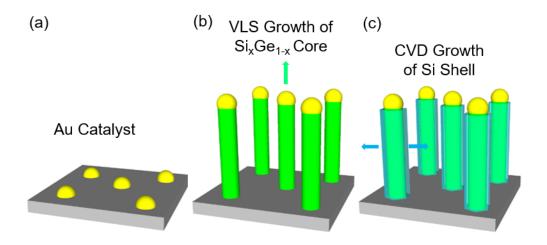

| Figure 3.2: Schematic of the Si <sub>x</sub> Ge <sub>1-x</sub> -Si core-shell nanowire growth, showing (a) Au catalyst                 |

| nanoparticles, (b) the Si <sub>x</sub> Ge <sub>1-x</sub> core growth by VLS, and (c) the Si shell growth by                            |

| CVD. Arrows indicate the growth direction in the corresponding regime 67                                                               |

| <b>Figure 3.3:</b> SEM image of Si <sub>x</sub> Ge <sub>1-x</sub> -Si core-shell nanowires.                                            |

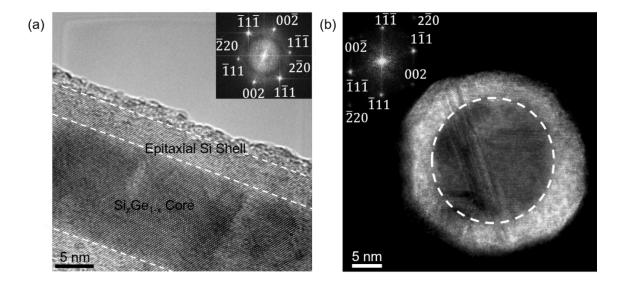

| Figure 3.4: (a) Planar view TEM image of a <110> oriented Si <sub>x</sub> Ge <sub>1-x</sub> -Si core-shell nanowire,                   |

| where interfaces are marked for clarity. Inset: FFT of the main panel data. (b) Cross-                                                 |

| sectional transmission electron micrograph of a <110> oriented Si <sub>x</sub> Ge <sub>1-x</sub> -Si core-shell                        |

| nanowire. The core-shell interface is marked for clarity. Inset: FFT of the main panel                                                 |

| data. The zone axis is assumed along [110] direction                                                                                   |

| Figure 3.5: Comparison of Raman spectra acquired from an individual (a) 28 nm diameter                                                 |

| Si <sub>0.41</sub> Ge <sub>0.59</sub> -Si core-shell nanowire, (b) 40 nm diameter Si <sub>0.41</sub> Ge <sub>0.59</sub> -Si core-shell |

| nanowire, (c) Si <sub>0.41</sub> Ge <sub>0.59</sub> nanowire, and (d) Si nanowire. The Si-Si in bulk Si, and Ge-                       |

| Ge, Si-Ge, and Si-Si in bulk Si <sub>0.41</sub> Ge <sub>0.59</sub> Raman modes are marked with vertical dash-                          |

| dotted lines. Two-dimensional contour plots of the simulated (e-h) strain tensor                                                       |

| components, (i) $\varepsilon_h$ and (j) calculated $E_C$ for a Si <sub>0.41</sub> Ge <sub>0.59</sub> -Si core-shell nanowire, with     |

| $t_{sh} = 4.2$ nm. The crystal directions are indicated in panel (e)                                                                   |

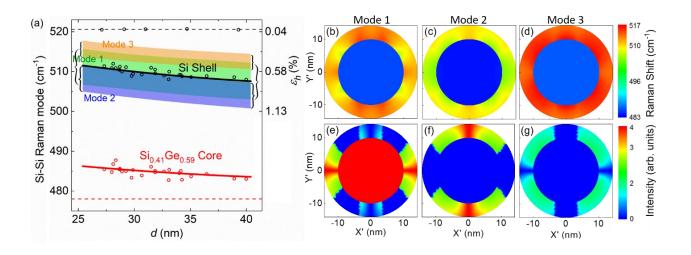

| Figure 3.6: (a) Diameter dependence of the core and shell Si-Si Raman modes for Si <sub>0.41</sub> Ge <sub>0.59</sub> -Si              |

| core-shell nanowires. The Si-Si Raman modes for core and shell are shown in black                                                      |

| calculations. The black and red dashed lines mark the position of the unstrained S1-S1                                           |

|----------------------------------------------------------------------------------------------------------------------------------|

| Raman modes in shell and core, respectively. Experimental data of Si-Si Raman modes                                              |

| acquired from bare Si nanowire are included for comparison. The calculation results                                              |

| of three different shell Si-Si modes are presented with three corridors to indicate their                                        |

| variations across the shell. Calculated (b-d) Si-Si modes Raman shift, and (e-g) the                                             |

| corresponding intensities for a coherently-strained Si <sub>0.41</sub> Ge <sub>0.59</sub> -Si core-shell nanowire,               |

| assuming the incident and scattered light are parallel to the <110> nanowire growth                                              |

| axis                                                                                                                             |

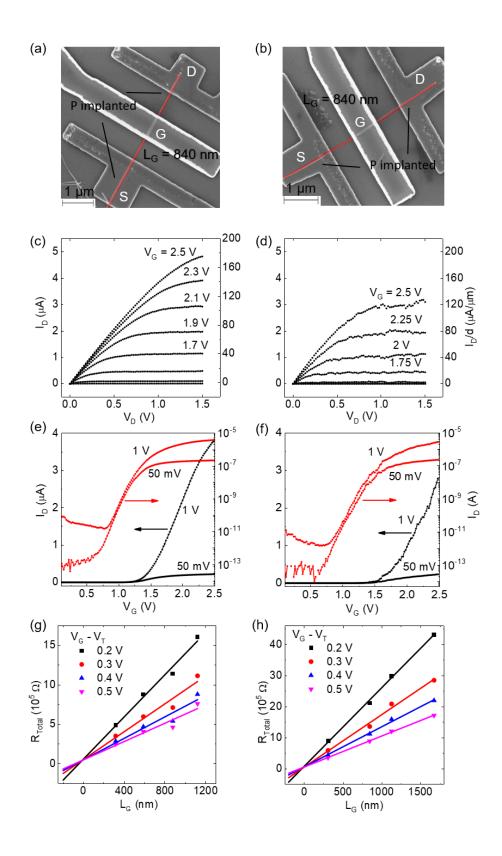

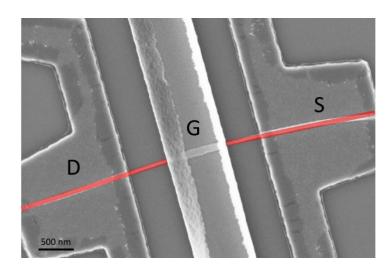

| Figure 3.7: Electrical characteristics of Si <sub>0.41</sub> Ge <sub>0.59</sub> -Si core-shell and bare Si nanowire n-type       |

| MOSFETs. SEM images of (a) a Si <sub>0.41</sub> Ge <sub>0.59</sub> -Si core-shell and (b) a bare Si nanowire                     |

| n-type MOSFETs. The source (S), gate (G), and drain (D) contacts are labeled, and                                                |

| the phosphorus implant region are shaded in red. (c-d) Output and (e-f) transfer                                                 |

| characteristics of the same devices shown in panels (a) and (b), respectively. The $V_G$                                         |

| $(V_D)$ value is indicated in each trace for the output (transfer) curves. $R_{Total}$ versus $L_G$                              |

| at different overdrive voltages $V_G - V_T$ for (g) Si <sub>0.41</sub> Ge <sub>0.59</sub> -Si core-shell and (h) bare Si         |

| nanowire n-type MOSFETs, respectively. Linear fits (solid lines) to the experimental                                             |

| data (symbols) are also included                                                                                                 |

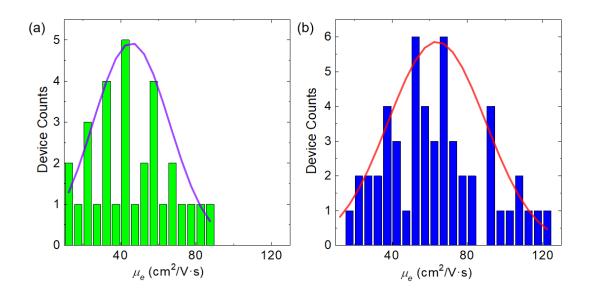

| Figure 3.8: Histograms of $\mu_e$ values in (a) 31 Si nanowire n-type MOSFETs and (b) 52                                         |

| Si <sub>0.41</sub> Ge <sub>0.59</sub> -Si core-shell nanowire n-type MOSFETs. Solid lines mark the Gaussian                      |

| distributions corresponding to the experimental data                                                                             |

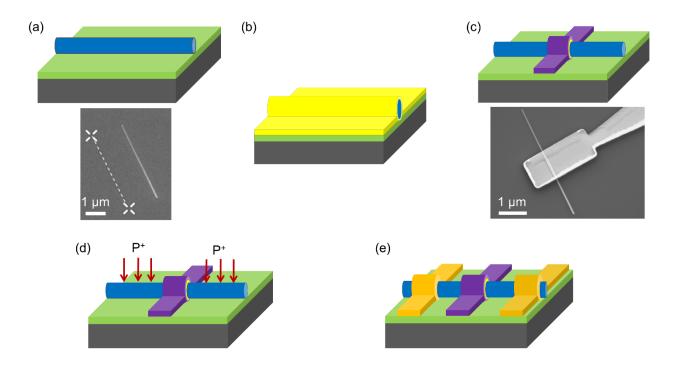

| <b>Figure 3.9:</b> Fabrication process of nanowire n-type MOSFETs. (a) Disperse Si <sub>x</sub> Ge <sub>1-x</sub> -Si core-shell |

| nanowires onto an oxidized Si substrate. (b) Deposit Al <sub>2</sub> O <sub>3</sub> gate dielectric using ALD.                   |

| (c) Perform EBL, TaN sputtering and lift-off to define the gate pattern, followed by                                             |

| etching of the dielectric film elsewhere. (d) Self-aligned phosphorus ion implantation                                           |

| to dope the exposed nanowire segment for source/drain. (e) Use EBL, Ni evaporation                                               |

| and lift-off to define the source/drain contacts. The lower parts of panels (a) and (c)                                          |

| are the SEM images of the corresponding fabrication stages. The SEM image of a                                                   |

and red, respectively. Symbols represent experimental data, and solid lines represent

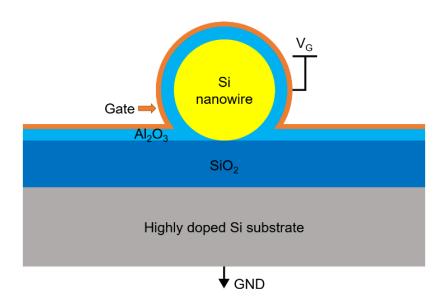

Figure 3.10: Schematic of the simulation structure to extract  $C_{\Omega}$  for Si nanowire MOSFETs. .. 81

| Figure 3.11: Carrier density per unit length and $C_{\Omega}$ vs. $d$ . (a) Number of electrons per $\mu m$ vs.            |

|----------------------------------------------------------------------------------------------------------------------------|

| positive $V_G$ and (b) $d$ dependence of the calculated $C_\Omega$ for n-type bare Si nanowire                             |

| MOSFETs. (c) Number of holes per $\mu$ m vs. negative $V_G$ and (d) $d$ dependence of the                                  |

| calculated $C_{\Omega}$ for p-type bare Si nanowire MOSFETs                                                                |

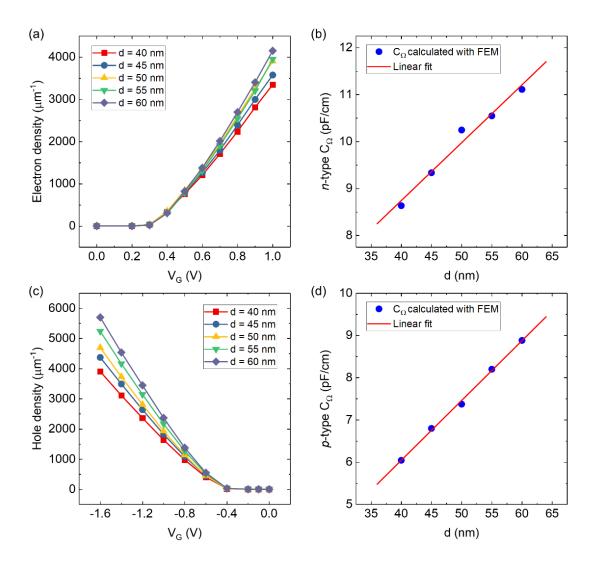

| Figure 4.1: (a) Cross-sectional TEM image of the strained Si/strained Ge planar dual-channel                               |

| heterostructure. (b) Schematic of a completed MOSFET. (c) Effective mobility of                                            |

| electrons and holes and (d) ratio of the hole effective mobility over that of electrons                                    |

| against inversion charge concentration for long-channel MOSFETs, including the                                             |

| dual-channel heterostructure, strained Si and bulk Si devices. (Figure adapted from                                        |

| Refs. [112, 114])                                                                                                          |

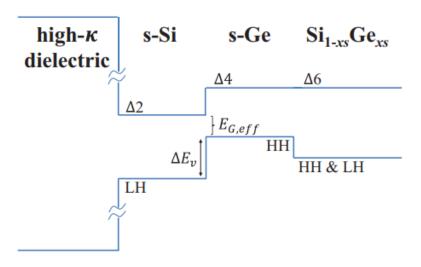

| Figure 4.2: Schematic of the energy band diagram of the planar dual-channel heterostructure,                               |

| showing a type-II band alignment between the strained Si and Ge. (Figure adapted                                           |

| from Ref. [115])                                                                                                           |

| Figure 4.3: Schematic of the Si <sub>0.5</sub> Ge <sub>0.5</sub> -Ge-Si core-double-shell nanowire heterostructure growth. |

| (a) Au catalyst formed by H <sub>2</sub> annealing. (b) Si <sub>0.5</sub> Ge <sub>0.5</sub> core growth by VLS. (c) Ge and |

| (d) Si shell growth by CVD. The arrows indicate the growth directions in the                                               |

| corresponding regime                                                                                                       |

| Figure 4.4: Cross-sectional SEM image of as-grown Si <sub>0.5</sub> Ge <sub>0.5</sub> -Ge-Si core-double-shell nanowires   |

| 92                                                                                                                         |

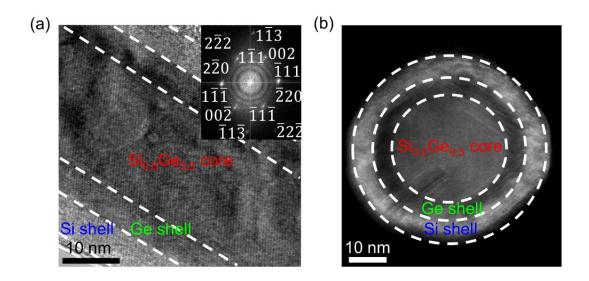

| Figure 4.5: (a) Planar view TEM image of a <110> oriented Si <sub>0.5</sub> Ge <sub>0.5</sub> -Ge-Si core-double-shell     |

| nanowire, where the interfaces between core and shells are marked for clarity. Inset:                                      |

| FFT of the main panel data, with the zone axis along the [110] direction. (b) Cross-                                       |

| sectional TEM image of a Si <sub>0.5</sub> Ge <sub>0.5</sub> -Ge-Si core-double-shell nanowire, where the                  |

| interfaces are marked for clarity                                                                                          |

| Figure 4.6: Raman spectroscopy and strain calculations of the Si <sub>0.5</sub> Ge <sub>0.5</sub> -Ge-Si core-double-shell |

| nanowire. (a) Raman spectrum acquired from an individual Si <sub>0.5</sub> Ge <sub>0.5</sub> -Ge-Si core-                  |

| double-shell nanowire. Two-dimensional contour plots of the simulated (b-e) strain                                         |

| tensor components and (f) $\varepsilon_h$ for a Si <sub>0.5</sub> Ge <sub>0.5</sub> -Ge-Si core-double-shell nanowire. The |

| crystal directions indicated in panel (b) apply to panels (b-f)                                                            |

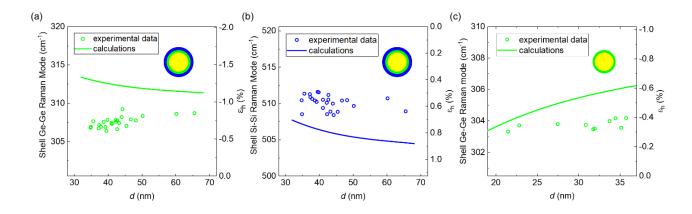

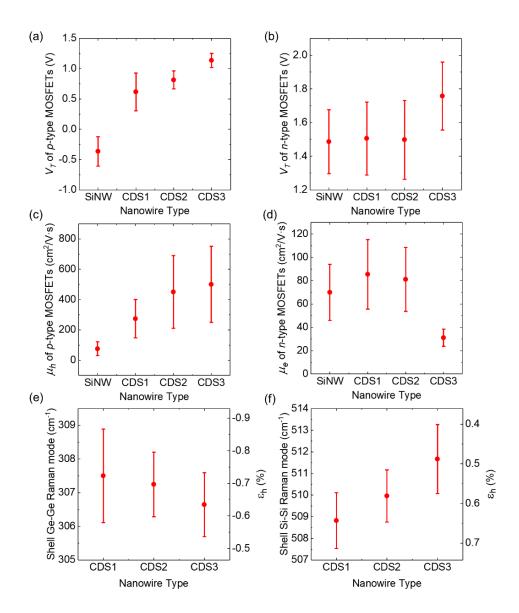

| Figure 4.7: Diameter dependence of the shell Raman modes. (a) Ge-Ge modes in the Ge shell for                              |

| Si <sub>0.5</sub> Ge <sub>0.5</sub> -Ge-Si core-double-shell nanowires. (b) Si-Si modes in the Si shell for                |

|            | S <sub>10.5</sub> Ge <sub>0.5</sub> -Ge-S <sub>1</sub> core-double-shell nanowires. (c) Ge-Ge modes in the Ge shell for                |

|------------|----------------------------------------------------------------------------------------------------------------------------------------|

|            | $\mathrm{Si}_{0.5}\mathrm{Ge}_{0.5}	ext{-}\mathrm{Ge}$ core-shell nanowires. The corresponding $arepsilon_h$ value is indicated on the |

|            | right y-axis for each panel. The symbols (lines) represent the experimental data                                                       |

|            | (calculations). The inset illustrates the geometry of the corresponding nanowire                                                       |

|            | heterostructure. 96                                                                                                                    |

| Figure 4.8 | : SEM image of a Si <sub>0.5</sub> Ge <sub>0.5</sub> -Ge-Si core-double-shell nanowire MOSFET. The gate,                               |

|            | source and drain contacts are labeled. The regions ion-implanted with boron or                                                         |

|            | phosphorus are shaded in red                                                                                                           |

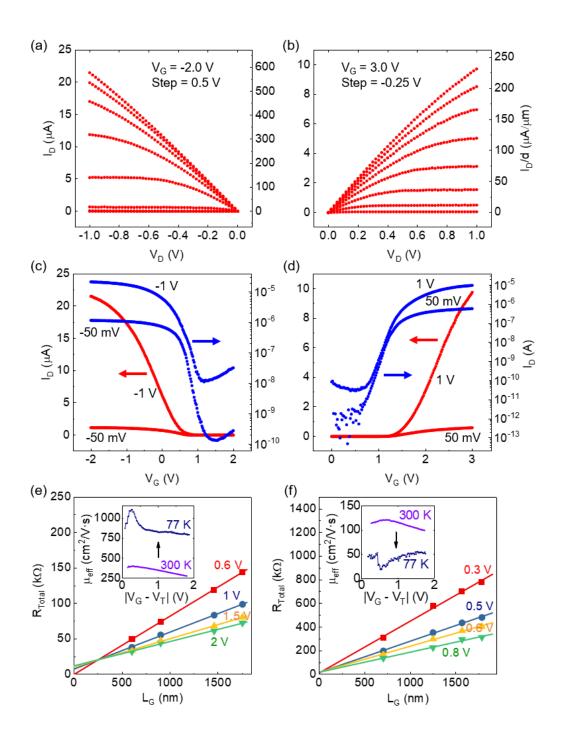

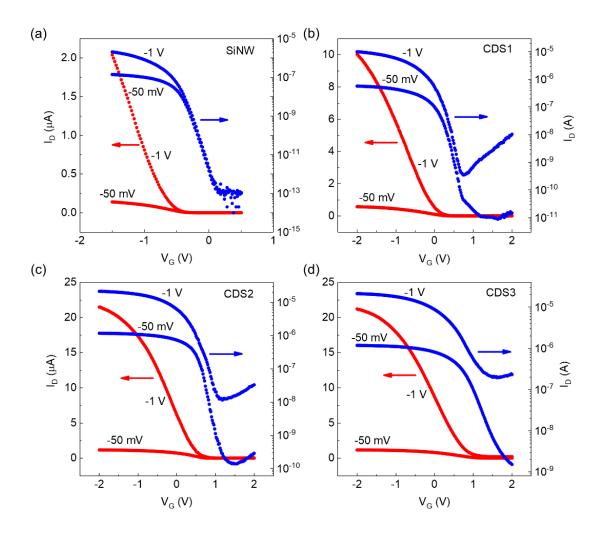

| Figure 4.9 | : Room temperature electrical characteristics of Si <sub>0.5</sub> Ge <sub>0.5</sub> -Ge-Si core-double-shell <i>p</i> -               |

|            | type and $n$ -type MOSFETs. (a-b) $I_D - V_D$ data of Si $_{0.5}$ Ge $_{0.5}$ -Ge-Si core-double-shell $p$ -                           |

|            | type ( $d=37$ nm, $L_G=950$ nm) and $n$ -type ( $d=42$ nm, $L_G=630$ nm) MOSFETs,                                                      |

|            | respectively. The y-axis labels apply to both panels. (c-d) $I_D - V_G$ data of the panel (a)                                          |

|            | and (b) devices. The $V_G$ and $V_D$ values are indicated for each trace. The y-axis labels                                            |

|            | apply to both panels. (e-f) $R_{Total}$ vs. $L_G$ at different overdrive voltages with $ V_G - V_T $                                   |

|            | indicated for each trace, measured in $Si_{0.5}Ge_{0.5}$ -Ge-Si core-double-shell $p$ -type and $n$ -                                  |

|            | type MOSFETs, respectively. Linear fits (lines) to the experimental data (symbols) are                                                 |

|            | included. Inset: hole and electron $\mu_{eff}$ vs. $ V_G - V_T $ for the same devices presented in                                     |

|            | panels (a-d)                                                                                                                           |

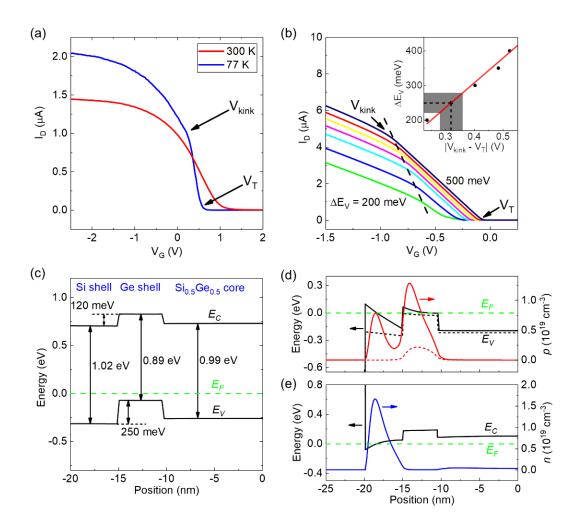

| Figure 4.1 | 0: Band offset extraction and band diagrams in Si <sub>0.5</sub> Ge <sub>0.5</sub> -Ge-Si core-double-shell                            |

|            | nanowires. (a) Experimental $I_D - V_G$ data of a Si <sub>0.5</sub> Ge <sub>0.5</sub> -Ge-Si core-double-shell                         |

|            | nanowire p-type MOSFET with $V_D = -50$ mV. The red and blue curves represent the                                                      |

|            | data measured at $T = 300 \text{ K}$ and $T = 77 \text{ K}$ , respectively. The $V_{kink}$ and $V_T$ positions                         |

|            | at $T = 77$ K are marked. (b) Calculated $I_D$ vs. $V_G$ data assuming different values of                                             |

|            | $\Delta E_V$ . The $V_{kink}$ and $V_T$ positions are marked. Inset: summary of the calculated $\Delta E_V$ vs.                        |

|            | $ V_{kink} - V_T $ . The range of experimentally extracted $ V_{kink} - V_T $ and the                                                  |

|            | corresponding $\Delta E_V$ values are indicated in grey corridors, and their mean values are                                           |

|            | marked with dashed lines. (c) Radial dependence of the band diagram under the flat                                                     |

|            | band condition for a MOSFET using Si <sub>0.5</sub> Ge <sub>0.5</sub> -Ge-Si core-double-shell nanowire                                |

|            | heterostructure as channel. Bandgaps, $E_F$ , $E_C$ and the valence band energy $(E_V)$ offsets                                        |

|            | are shown in the diagram. (d) Radial dependence of $E_V$ and hole density $(p)$ for a p-                                               |

|            | type MOSFET. The solid (dashed) lines represent the data in the regime of $V_G < V_{kink}$                                             |

|            |                                                                                                                                        |

| $(V_{kink} < V_G < V_T)$ . (e) Radial dependence of $E_C$ and electron density $(n)$ for an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ı n-       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| type MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 103        |

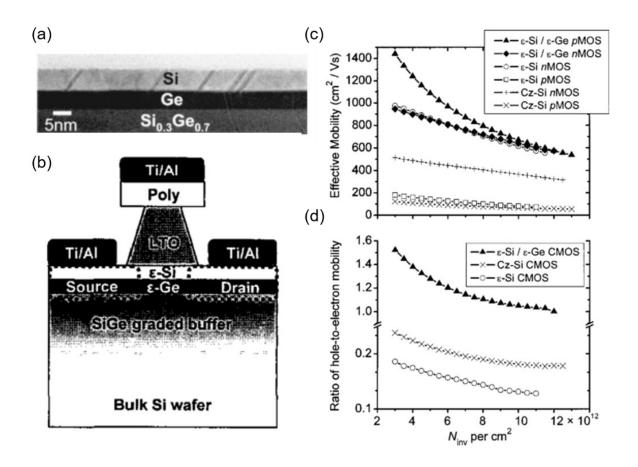

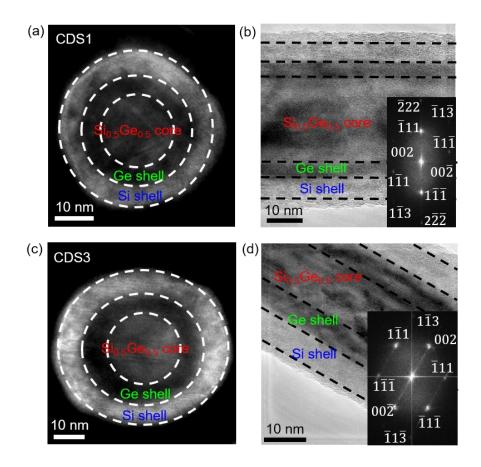

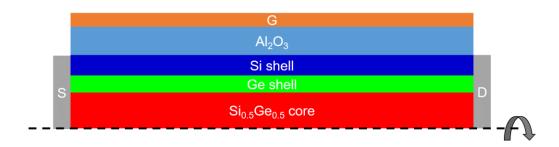

| Figure 4.11: (a) Planar view and (b) cross-sectional TEM images of <110> oriented Si <sub>0.5</sub> Ge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0.5-       |

| Ge-Si core-double-shell nanowires of growth CDS1. (c) Planar and (d) cross-section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nal        |

| TEM images of <110> oriented Si <sub>0.5</sub> Ge <sub>0.5</sub> -Ge-Si core-double-shell nanowires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | of         |

| growth CDS3. The interfaces between core and shells are marked for clarity. Insets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | s of       |

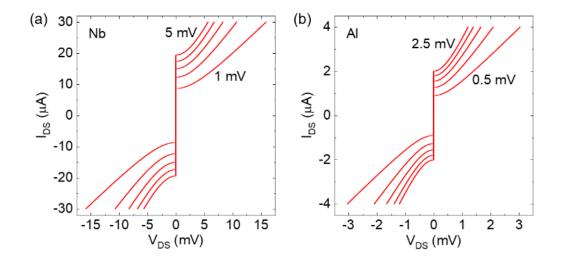

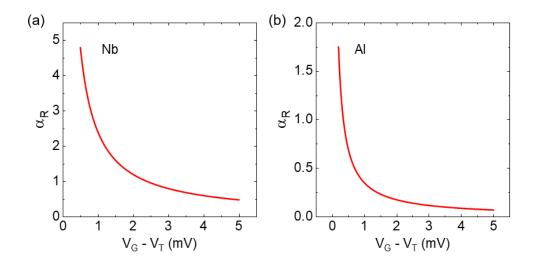

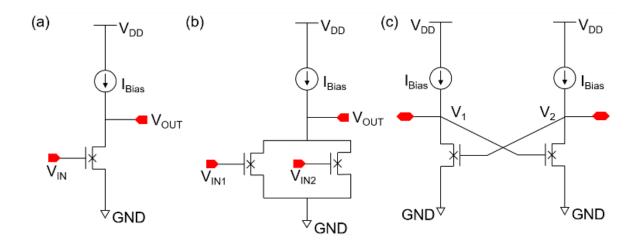

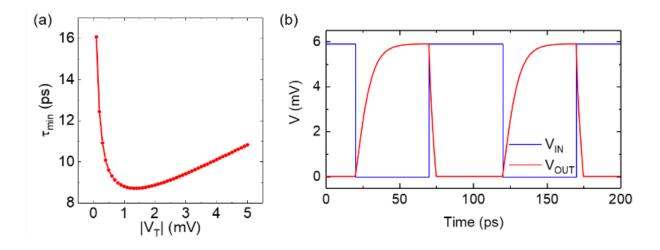

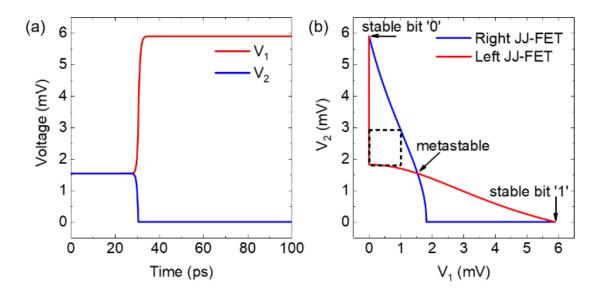

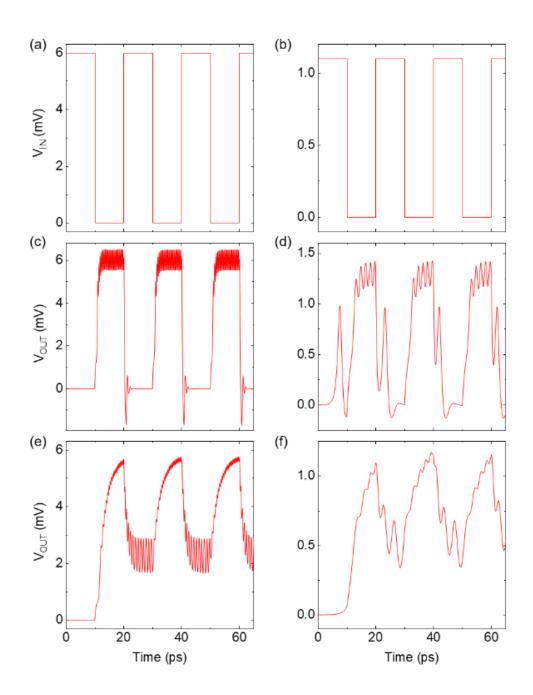

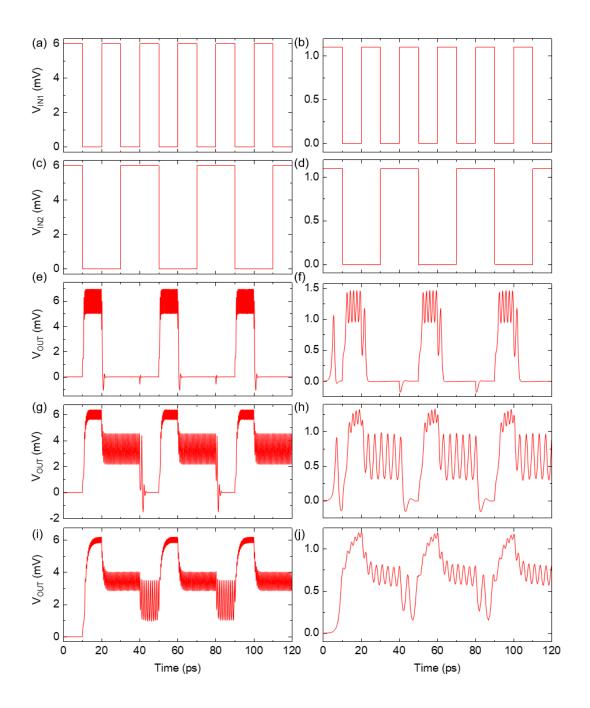

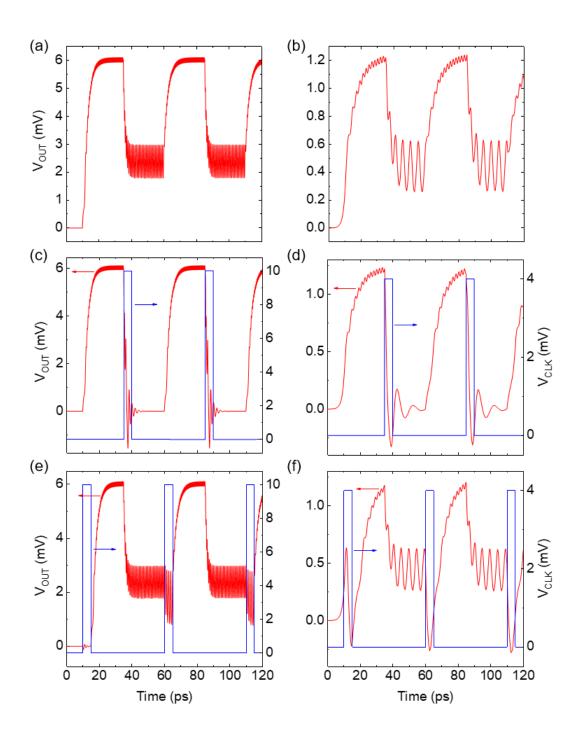

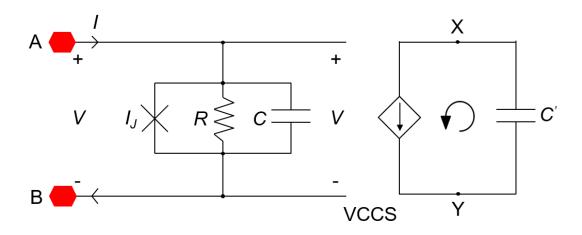

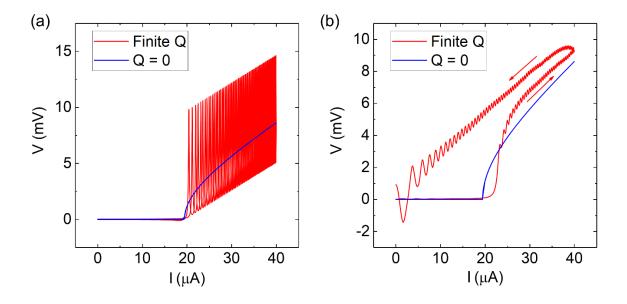

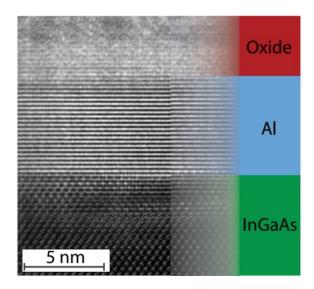

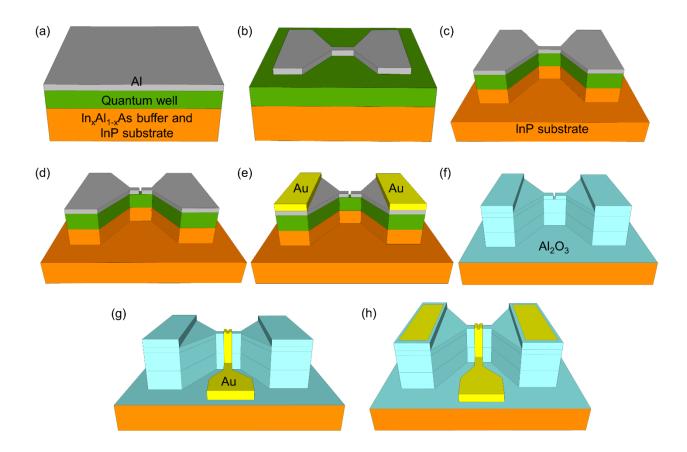

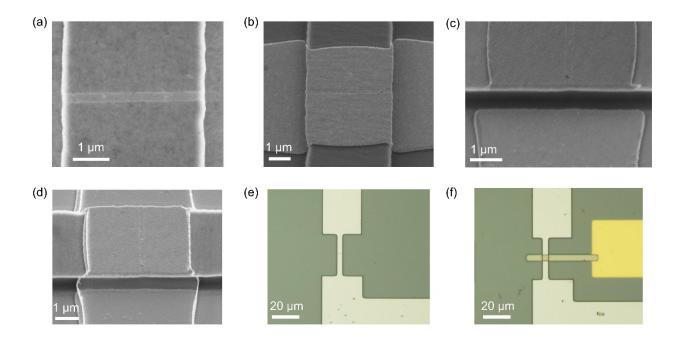

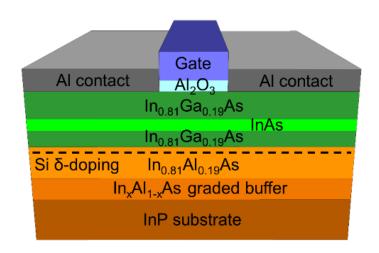

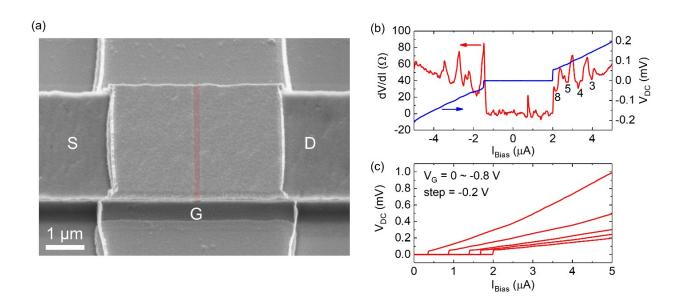

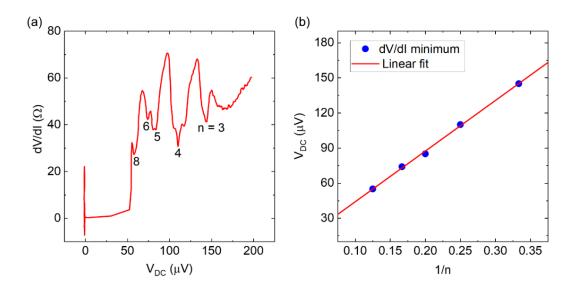

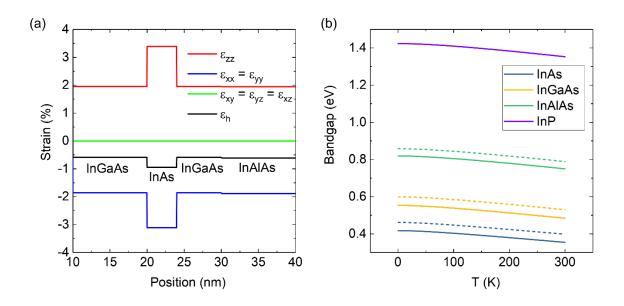

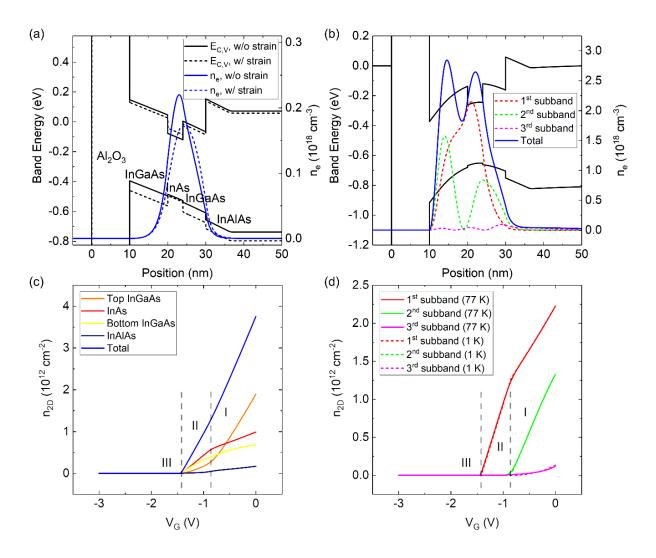

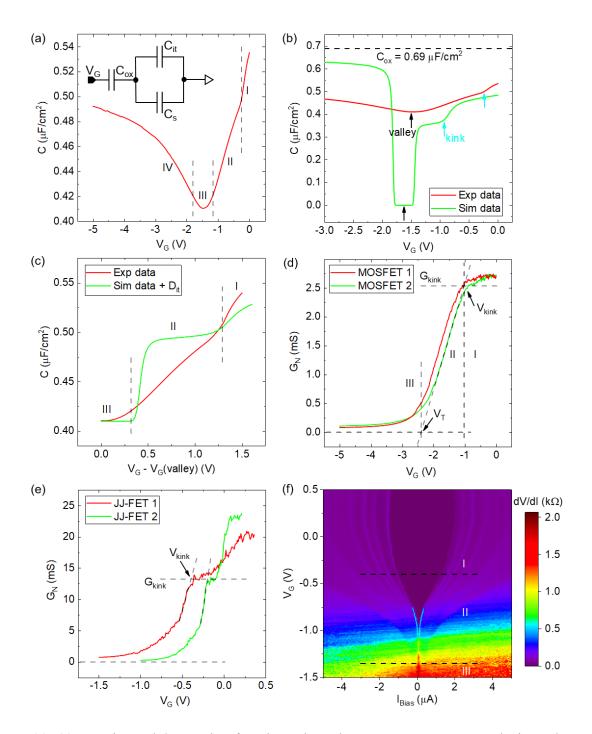

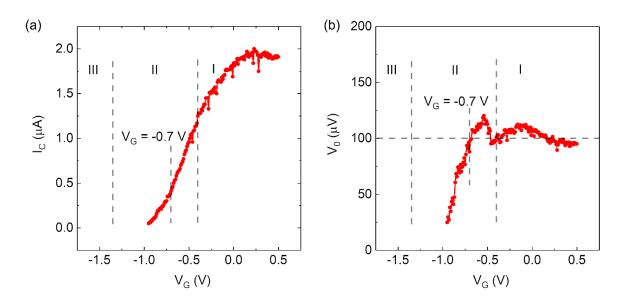

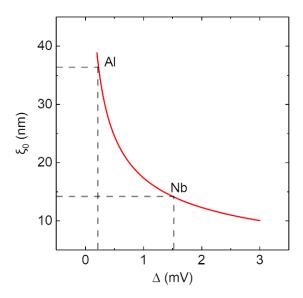

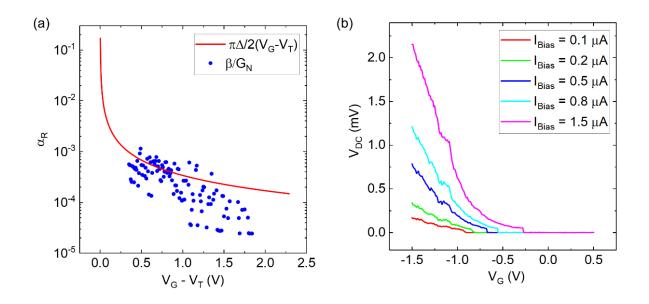

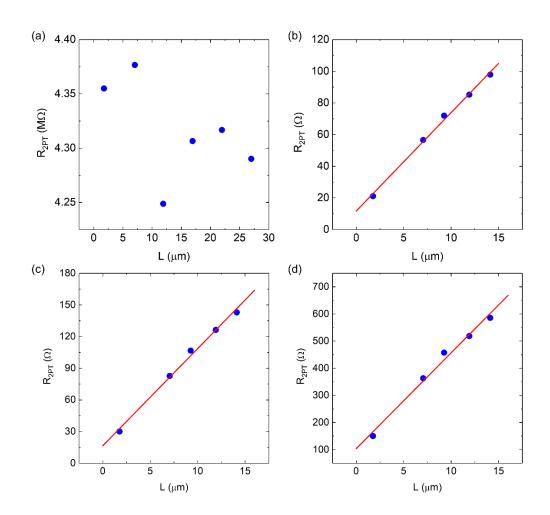

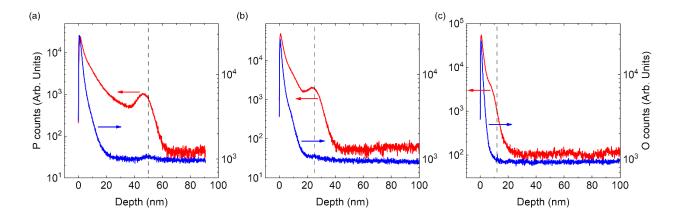

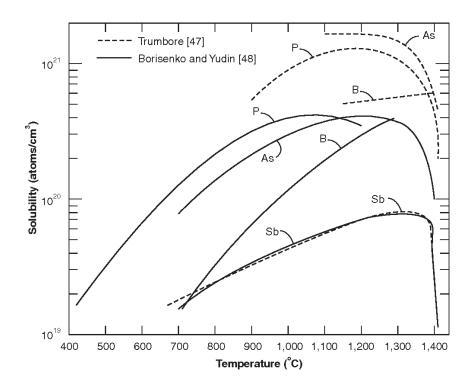

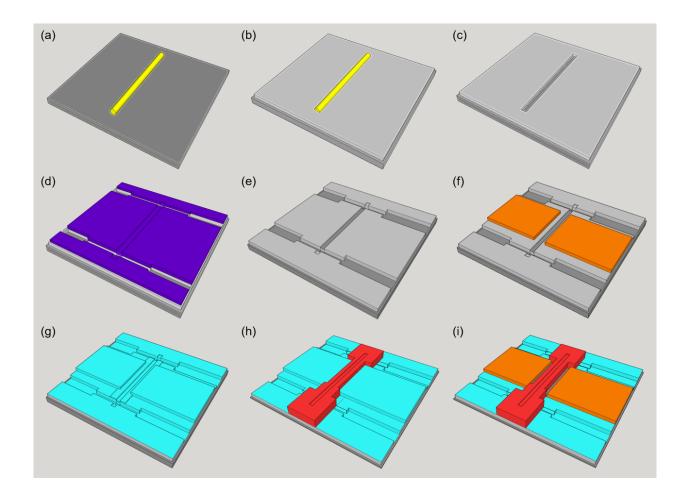

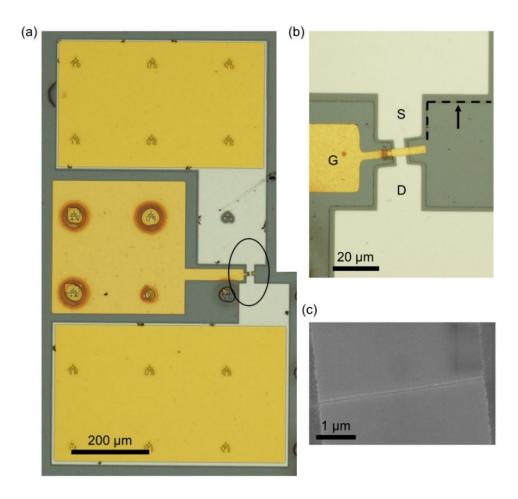

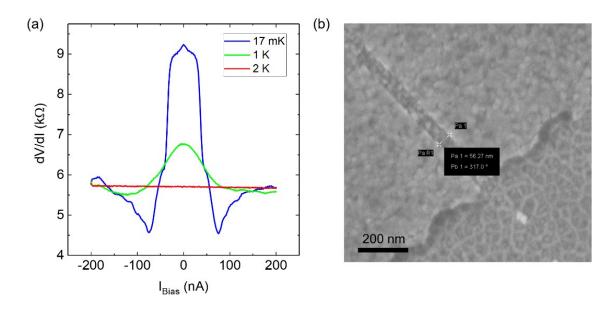

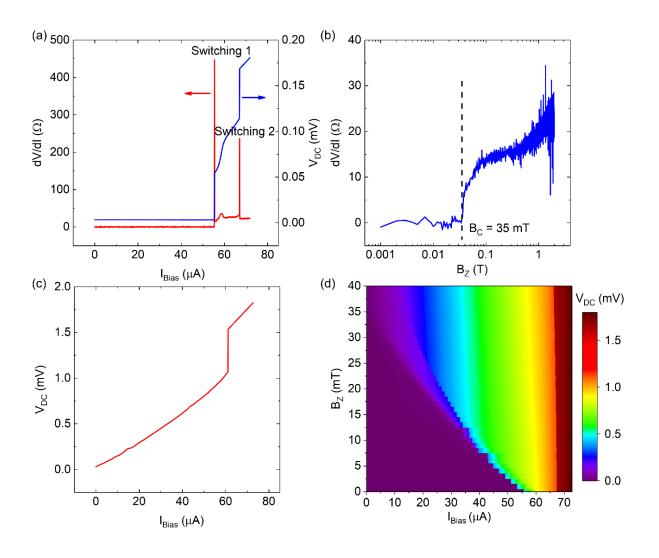

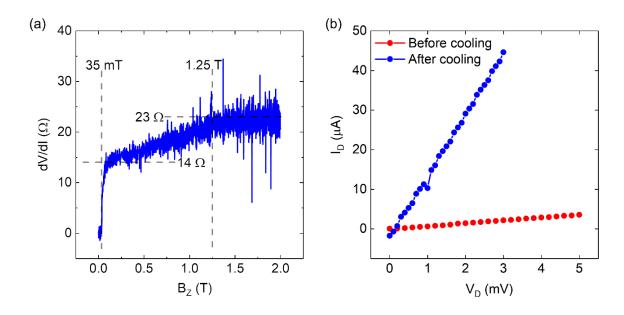

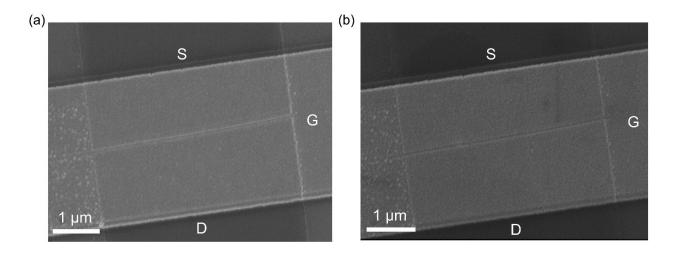

| panels (b) and (d) are the FFTs of the main panel data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 105        |