# STARS

University of Central Florida STARS

Electronic Theses and Dissertations, 2020-

2021

## Energy-Aware Real-Time Scheduling on Heterogeneous and Homogeneous Platforms in the Era of Parallel Computing

Ashik Ahmed Bhuiyan University of Central Florida

Part of the Computer Engineering Commons Find similar works at: https://stars.library.ucf.edu/etd2020 University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2020- by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Bhuiyan, Ashik Ahmed, "Energy-Aware Real-Time Scheduling on Heterogeneous and Homogeneous Platforms in the Era of Parallel Computing" (2021). *Electronic Theses and Dissertations, 2020-.* 648. https://stars.library.ucf.edu/etd2020/648

# ENERGY-AWARE REAL-TIME SCHEDULING ON HETEROGENEOUS AND HOMOGENEOUS PLATFORMS IN THE ERA OF PARALLEL COMPUTING

by

#### ASHIK AHMED BHUIYAN B.Sc., Bangladesh University of Engineering and Technology, 2013

A dissertation submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Summer Term 2021

Major Professor: Zhishan Guo

© 2021 Ashik Ahmed Bhuiyan

#### ABSTRACT

Multi-core processors increasingly appear as an enabling platform for embedded systems, e.g., mobile phones, tablets, computerized numerical controls, etc. The parallel task model, where a task can execute on multiple cores simultaneously, can efficiently exploit the multi-core platform's computational ability. Many computation-intensive systems (e.g., self-driving cars) that demand stringent timing requirements often evolve in the form of parallel tasks. Several real-time embedded system applications demand predictable timing behavior and satisfy other system constraints, such as energy consumption.

Motivated by the facts mentioned above, this thesis studies the approach to integrating the dynamic voltage and frequency scaling (DVFS) policy with real-time embedded system application's internal parallelism to reduce the worst-case energy consumption (WCEC), an essential requirement for energy-constrained systems. First, we propose an energy-sub-optimal scheduler, assuming the percore speed tuning feature for each processor. Then we extend our solution to adapt the clustered multi-core platform, where at any given time, all the processors in the same cluster run at the same speed. We also present an analysis to exploit a task's probabilistic information to improve the average-case energy consumption (ACEC), a common non-functional requirement of embedded systems.

Due to the strict requirement of temporal correctness, the majority of the real-time system analysis considered the worst-case scenario, leading to resource over-provisioning and cost. The mixed-criticality (MC) framework was proposed to minimize energy consumption and resource over-provisioning. MC scheduling has received considerable attention from the real-time system research community, as it is crucial to designing safety-critical real-time systems. This thesis further addresses energy-aware scheduling of real-time tasks in an MC platform, where tasks with varying criticality levels (i.e., importance) are integrated into a common platform. We propose an algorithm GEDF-VD for scheduling MC tasks with internal parallelism in a multiprocessor platform. We also prove the correctness of GEDF-VD, provide a detailed quantitative evaluation, and reported extensive experimental results. Finally, we present an analysis to exploit a task's probabilistic information at their respective criticality levels. Our proposed approach reduces the average-case energy consumption while satisfying the worst-case timing requirement.

Dedicated to my family members.

#### ACKNOWLEDGMENTS

First of all, thanks to my almighty lord for providing me the strength, patience, ability to make a successful end of this long journey. Without the shower of his blessing throughout my graduate life, it would be impossible to complete the research successfully.

I was fortunate to have two supervisors, *Zhishan Guo* and *Abusayeed Saifullah* (Wayne State University), in my Ph.D. life. Without them, it wouldn't have been possible to draw a successful ending. I've received an enormous amount of help and support and from both of them. I am infinitely indebted to my supervisors, and I want to express my deep and sincere gratitude. Probably like everyone else, the beginning of this journey was extremely challenging and frustrating. However, they always believe in me, give me the freedom to think and develop the research that attracts me, and help me to understand how interesting to dive into computer science research and how wonderful an academic life is. All these factors allow me to nourish myself as a successful researcher. Their guidance and motivation have a profound positive impact throughout my Ph.D. Career. Ph.D. is not only about mastering a specific problem or research domain but also about learning many valuable life lessons, such as time management, learning how to learn, communicating with people etc. Under their supervision, I have learned the methodology to carry out the research and the essential real-life skills mentioned above. During the job-hunting period, numerous recommendation letters from my supervisors (along with other recommenders) helps me tremendously to achieve my first academic position.

My sincerest appreciation goes to my other dissertation committee members: Rickard Ewetz, Fan Yao, and Yanjie Fu. Thanks to all of them for agreeing to serve on my dissertation committee and for their insightful comments on my dissertation. I am also thankful to my research collaborators: Samsil Arefin, Aamir Khan, Sai Sruti, Kecheng Yang, Di Liu, Nan Guan, Federico Reghenzani,

William Fornaciari, and Hayoi Xiong. Their fruitful discussion and collaboration help to produce several impactful works.

My six years long graduate life was indeed a pleasant experience, thanks to all members of the realtime and intelligent systems (RTIS) research group. I am lucky to have you as my labmates and co-workers. My special thanks go to Samsil Arefin, Sai Sruti, Aamir khan, Sudharsan Vaidhun, and Abdullah Arafat. I am indebted to you for your collaboration, feedback, suggestions in the presentation, job talks, research paper writing. You also helped a lot build a friendly, professional, and collaborative environment in the lab.

Finally, I am indebted to my parents for their unconditional love, sacrifice, and inspiration. They have made every effort to prepare me for a better future. To my father, I wish you could stay with us till today to see this achievement: thank you for all your effort throughout your life. To my mother, no matter how far I go, I will never forget you taught me how to make the first step. To my wife, Fayrose Sayeda, thank you for your constant support, trust, and patience. Thank you for your love and belief during many frustrating and challenging times in my life. Thanks to my brother and sister-in-law for their supports towards the completion of my degree and for taking care of our family, which keeps me relaxed and tension-free. Finally, thanks to my only niece, Rufaida, who makes me feel that life is more beautiful than I thought.

## TABLE OF CONTENTS

| LIST OF FIGURES                                                   |    |  |

|-------------------------------------------------------------------|----|--|

| LIST OF TABLES                                                    | XX |  |

| CHAPTER 1: INTRODUCTION                                           | 1  |  |

| 1.1 Challenges in Energy-Aware Real-Time Scheduling               | 2  |  |

| 1.2 Thesis Statement                                              | 3  |  |

| 1.3 Thesis Contribution and Organization                          | 4  |  |

| CHAPTER 2: PRELIMINARIES AND NOTATION                             | 6  |  |

| 2.1 Real-Time Parallel Task Model                                 | 6  |  |

| 2.1.1 DAG Task Model                                              | 6  |  |

| 2.1.2 Gang Task Model                                             | 8  |  |

| 2.2 Power/Energy Model                                            | 9  |  |

| CHAPTER 3: ENERGY-EFFICIENT FEDERATED SCHEDULING OF REAL-TIME DAG |    |  |

| TASKS WITH INTRA-TASK PROCESSOR MERGING                           | 12 |  |

| 3.1 Introduction                                                  | 12 |  |

| 3.2  | Related Work                                                             | 15 |

|------|--------------------------------------------------------------------------|----|

| 3.3  | Energy-Sub-Optimal Federated Scheduling for DAG Tasks                    | 17 |

|      | 3.3.1 Task Decomposition                                                 | 17 |

|      | 3.3.2 Segment Extension                                                  | 20 |

|      | 3.3.3 Problem Transformation                                             | 23 |

| 3.4  | Processor Sharing: Efficiency Improvement                                | 29 |

|      | 3.4.1 Merging Processors Assigned to the Same DAG                        | 31 |

| 3.5  | Simulation Study                                                         | 35 |

|      | 3.5.1 Experiment Under Single Merging of Processors                      | 35 |

|      | 3.5.1.1 Varying Task Periods                                             | 37 |

|      | 3.5.1.2 Varying Numbers of Nodes in a DAG Task                           | 38 |

| 3.6  | Conclusion                                                               | 39 |

| CHAP | TER 4: ENERGY-EFFICIENT FEDERATED SCHEDULING OF REAL-TIME DAG            |    |

|      | TASKS WITH INTER-TASK PROCESSOR MERGING                                  | 40 |

| 4.1  | Multiple Merging Among the Processors Assigned to the Same DAG           | 40 |

| 4.2  | Calculating Optimal Segment Length After the Intra-DAG Processor Merging | 41 |

| 4.3  | Merging Processors Assigned to Different DAGs                            | 43 |

| 4.4   | Experiment Under Multiple Merging of Processors                | 45 |

|-------|----------------------------------------------------------------|----|

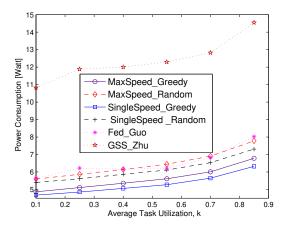

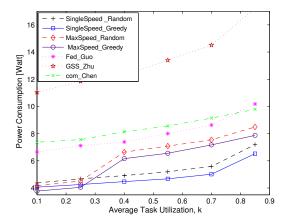

|       | 4.4.1 The Effect of Varying Task Periods or Utilization        | 47 |

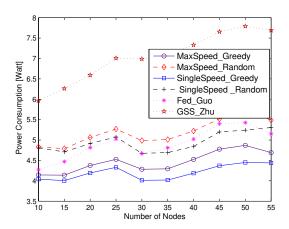

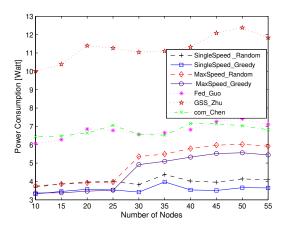

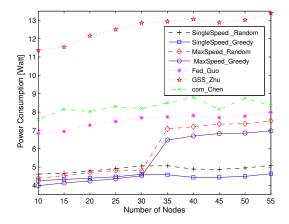

|       | 4.4.2 Varying Numbers of Nodes in a DAG Task                   | 49 |

| 4.5   | Conclusion                                                     | 50 |

| CHAPI | TER 5: ENERGY-EFFICIENT PARALLEL REAL-TIME SCHEDULING ON CLUS- |    |

|       | TERED MULTI-CORE                                               | 51 |

| 5.1   | Introduction                                                   | 51 |

| 5.2   | Related Work                                                   | 54 |

| 5.3   | Background and Existing Concepts                               | 56 |

| 5.4   | Speed-Profile for Task and Cluster                             | 58 |

|       | 5.4.1 Speed-Profile for Each DAG                               | 58 |

|       | 5.4.2 Speed-Profile for the Cluster Containing Multiple DAGs   | 62 |

| 5.5   | Task Partitioning Algorithm                                    | 63 |

|       | 5.5.1 Creating the Speed-Profile of a Task                     | 63 |

|       | 5.5.2 Task Partition: Greedy Merging with Speed-Profiles       | 67 |

| 5.6   | System Experiments                                             | 69 |

| 5.7   | Simulations                                                    | 74 |

|      | 5.7.1  | Identical Heterogeneous Platform with a Continuous Frequency Scheme | 75 |

|------|--------|---------------------------------------------------------------------|----|

|      |        | 5.7.1.1 Constrained Deadline Task                                   | 76 |

|      |        | 5.7.1.2 Implicit Deadline Task                                      | 78 |

| 5.8  | Discu  | ssions: Assumptions and Applicability                               | 79 |

|      | 5.8.1  | Assumptions Behind the Power Model                                  | 80 |

|      | 5.8.2  | A Note on the Overhead Delay                                        | 81 |

| 5.9  | Concl  | usion                                                               | 82 |

|      |        |                                                                     |    |

| CHAP | ΓER 6: | ENERGY-EFFICIENT PARALLEL REAL-TIME SCHEDULING ON CLUS              | -  |

|      |        | TERED MULTI-CORE: ADAPTING THE FREQUENCY DISCRETIZATION             | 1  |

|      |        | AND PLATFORM HETEROGENEITY                                          | 83 |

| 6.1  | Discre | etization of the Speed-Profile                                      | 83 |

| 6.2  | Handl  | ing Platform Heterogeneity                                          | 85 |

| 6.3  | Simul  | ation Study                                                         | 87 |

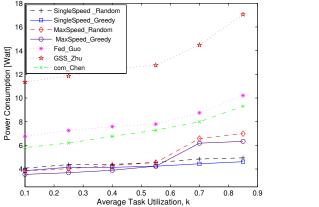

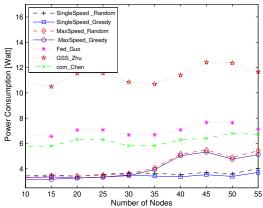

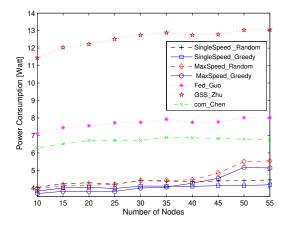

|      | 6.3.1  | Uniform Heterogeneous Platform with a Continuous Frequency Scheme   | 88 |

|      |        | 6.3.1.1 Constrained Deadline Task                                   | 88 |

|      |        | 6.3.1.2 Implicit Deadline Task                                      | 90 |

|      | 6.3.2  | Uniform Heterogeneous Platform With a Discrete Frequency Scheme     | 91 |

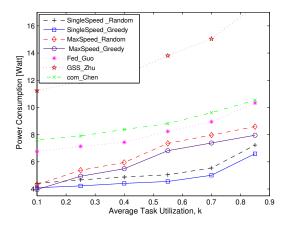

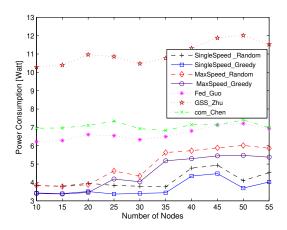

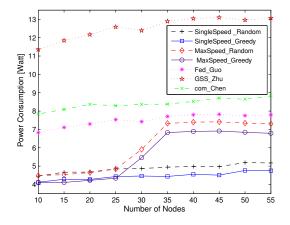

|      |        | 6.3.2.1 Constrained Deadline Task                                   | 92 |

|      |         | 6.3.2.2 Implicit Deadline Task                      | 93 |

|------|---------|-----------------------------------------------------|----|

| 6.4  | Conclu  | usion                                               | 93 |

| CHAP | PTER 7: | MIXED-CRITICALITY REAL-TIME SCHEDULING OF GANG TASK |    |

|      |         | SYSTEMS                                             | 95 |

| 7.1  | Introdu | uction                                              | 96 |

| 7.2  | Relate  | d Work                                              | 00 |

| 7.3  | Dual-C  | Criticality Gang Task Model                         | 02 |

| 7.4  | GEDF    | -VD for Dual-Criticality System                     | 07 |

|      | 7.4.1   | EDF-VD and GEDF-VD: An Overview                     | 08 |

|      | 7.4.2   | GEDF-VD: A Detailed Description                     | 09 |

|      | 7.4.3   | Proof of Correctness in the LO-Criticality Mode     | 13 |

|      | 7.4.4   | Proof of Correctness in the HI-Criticality Mode     | 15 |

| 7.5  | Speed   | -up Bound Analysis                                  | 17 |

|      | 7.5.1   | Speedup Bound for Gang Tasks under GEDF             | 20 |

|      | 7.5.2   | Speedup Bound for Gang Tasks under GEDF-VD          | 22 |

| 7.6  | Evalua  | ttion                                               | 27 |

|      | 7.6.1   | Experimental Setup                                  | 27 |

|      | 7.6.2   | Evaluation Results                                       |

|------|---------|----------------------------------------------------------|

| 7.7  | Conclu  | usion                                                    |

| CHAP |         | ENERGY EFFICIENT PRECISE SCHEDULING OF MIXED-CRITICALITY |

|      | F       | TASKS                                                    |

| 8.1  | Traditi | onal MC Task Model                                       |

|      | 8.1.1   | System Model                                             |

|      | 8.1.2   | Scheduling Policies for the Precise MC Task Model        |

|      |         | 8.1.2.1 EDF-VD                                           |

|      |         | 8.1.2.2 Fluid Scheduling                                 |

|      |         | 8.1.2.3 A Generalized Fluid Scheduling Approach          |

|      | 8.1.3   | Evaluation                                               |

| 8.2  | Probab  | pilistic MC Task Model                                   |

|      | 8.2.1   | System Model and Correctness Criteria                    |

|      | 8.2.2   | Response Time Analysis                                   |

|      |         | 8.2.2.1 Existing RTA for Non-MC and MC Tasks             |

|      |         | 8.2.2.2 RTA of Our Algorithm                             |

|      | 8.2.3   | Evaluation                                               |

| 8.3    | Conclusion                                    |

|--------|-----------------------------------------------|

| CHAP   | TER 9: CONCLUSION                             |

| 9.1    | Summary of Results                            |

| 9.2    | Future Direction                              |

| APPEN  | NDIX : PERMISSION TO REUSE PUBLISHED MATERIAL |

| LIST C | OF REFERENCES    188                          |

## LIST OF FIGURES

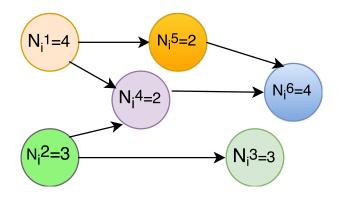

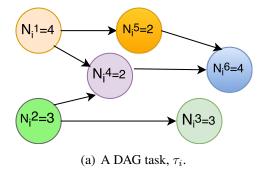

| 2.1 | An example heavy DAG task $\tau_i$                                                                                                                           | 7  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

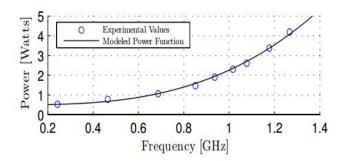

| 2.2 | Comparison of the power model (Equation (2.1)) with experimental results in [71]                                                                             | 10 |

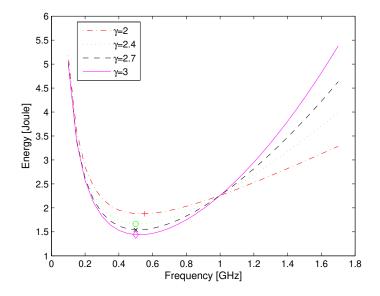

| 2.3 | Energy consumption for executing a job with $10^9$ computation cycles with a fixed $\alpha$ , $\beta$ and a variable $\gamma$ value.                         | 11 |

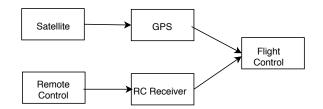

| 3.1 | Partial work-flow of a UAV system represented as a DAG                                                                                                       | 13 |

| 3.2 | A DAG task and its equivalent decomposed structure.                                                                                                          | 18 |

| 3.3 | The segment-node mapping for $\tau_i$ (from Figure 2.1) after segment extension.                                                                             | 20 |

| 3.4 | The sub-optimal segment length assignment for power efficiency of the sample task $\tau_i$ (in Figure 2.1), with an average power consumption of 2.94 Watts. | 29 |

| 3.5 | The execution pattern for $\tau_i$ (in Figure 2.1) after merging two different Processors.                                                                   | 30 |

| 3.6 | The equivalence of the MPS problem and the MIS problem                                                                                                       | 33 |

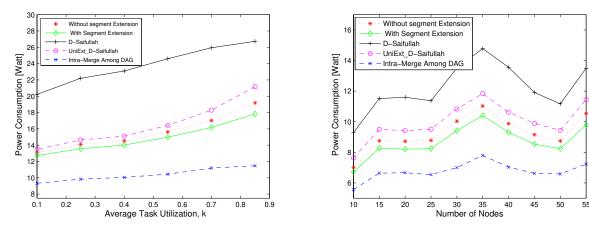

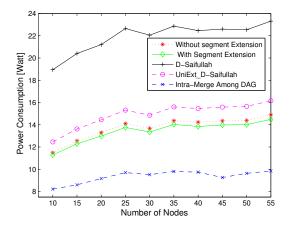

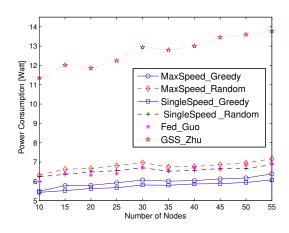

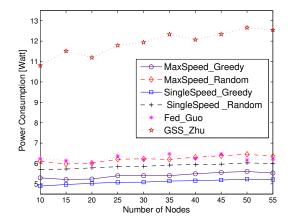

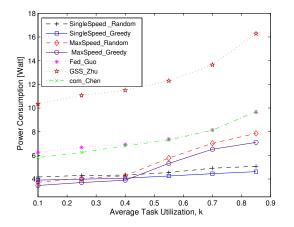

| 3.7 | Power consumption comparisons for task sets for various settings under sin-<br>gle merging                                                                   | 36 |

| 4.1 | The modified DAG task $\tau_i$ (from Figure 2.1) after applying the intra-task processors merging technique.                                                 | 42 |

| 4.2 | The sub-optimal segment length assignment (after merging Processors) for             |    |

|-----|--------------------------------------------------------------------------------------|----|

|     | power efficiency of the sample task $\tau_i$                                         | 43 |

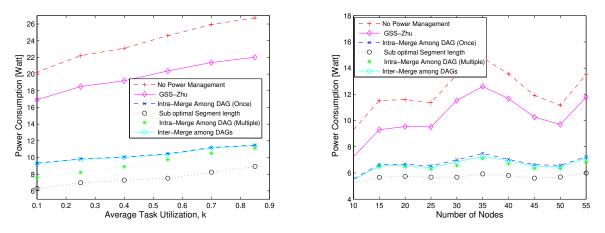

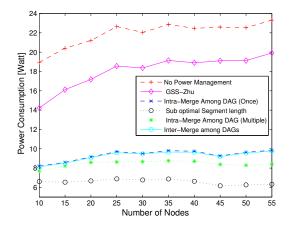

| 4.3 | Power consumption comparisons for task sets for various settings under mul-          |    |

|     | tiple merging.                                                                       | 48 |

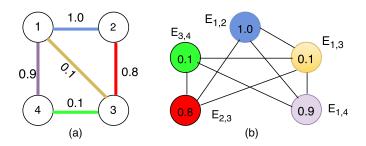

| 5.1 | (a) A DAG task, $\tau_i$ (b) transformed DAG $\tau_i$ after applying task decomposi- |    |

|     | tion. Both of them are adopted from [67].                                            | 57 |

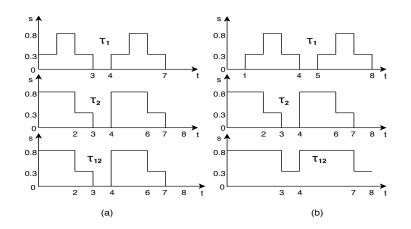

| 5.2 | Impact of different release offset when multiple tasks share the same cluster.       | 60 |

| 5.3 | The energy consumption and the frequency variation of our proposed ap-               |    |

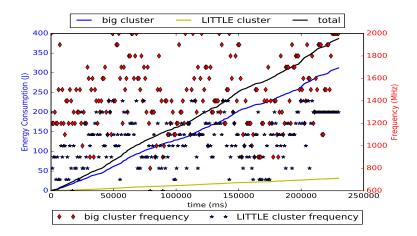

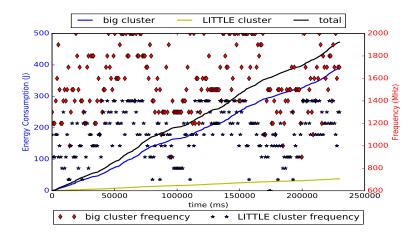

|     | proach on ODROID XU-3                                                                | 71 |

| 5.4 | The energy consumption and the frequency variation of the reference ap-              |    |

|     | proach on ODROID XU-3                                                                |    |

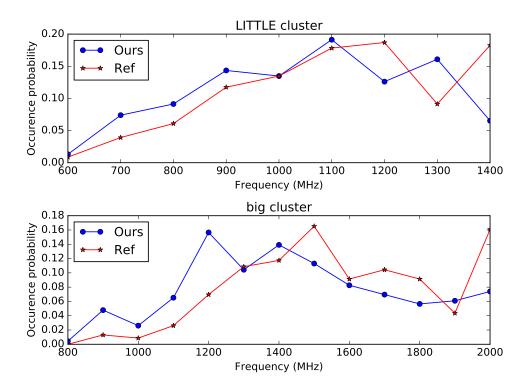

| 5.5 | Frequency occurrence probabilities.                                                  | 73 |

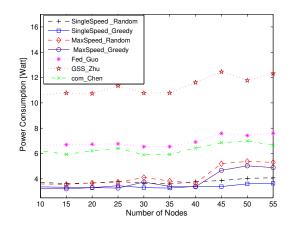

| 5.6 | Power consumption comparison between different approaches for the con-               |    |

|     | strained deadline tasks considering a continuous frequency scheme on the             |    |

|     | identical heterogeneous platform                                                     | 76 |

| 5.7 | Power consumption comparison between different approaches for the im-                |    |

|     | plicit deadline tasks considering a continuous frequency scheme on the iden-         |    |

|     | tical heterogeneous platform                                                         | 78 |

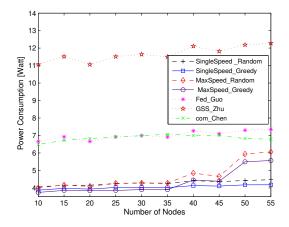

| 6.1 | Power consumption comparison between different approaches for the con-         |

|-----|--------------------------------------------------------------------------------|

|     | strained deadline tasks considering a continuous frequency scheme on the       |

|     | <b>uniform</b> heterogeneous platform                                          |

| 6.2 | Power consumption comparison between different approaches for the im-          |

|     | plicit deadline tasks considering a continuous frequency scheme on the uni-    |

|     | form heterogeneous platform                                                    |

| 6.3 | Power consumption comparison between different approaches for the con-         |

|     | strained deadline tasks considering a discrete frequency scheme on the uni-    |

|     | form heterogeneous platform                                                    |

| 6.4 | Power consumption comparison between different approaches for the im-          |

|     | plicit deadline tasks considering a discrete frequency scheme on the uniform   |

|     | heterogeneous platform                                                         |

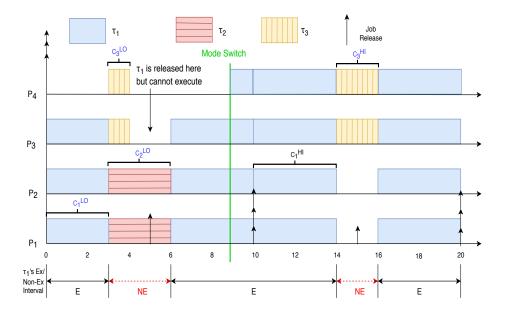

| 7.1 | A GEDF scheduling of the MC gang task-set from Table 7.1 and the execut-       |

|     | ing (E)/non-executing (NE) intervals of $\tau_1$                               |

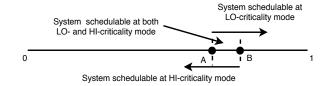

| 7.2 | Any value of the scaling factor x, where $A \leq x \leq B$ , guarantees an MC- |

|     | correct schedule                                                               |

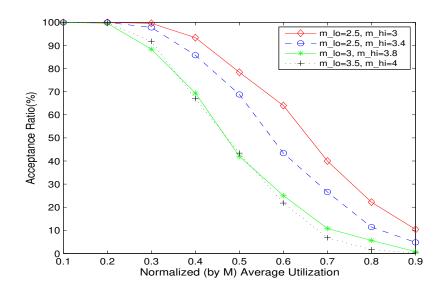

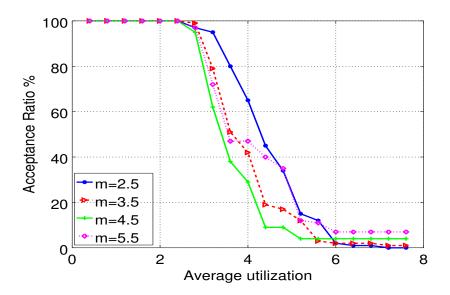

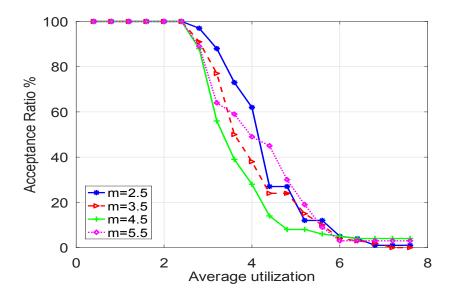

| 7.3 | Acceptance ratio for GEDF-VD with a different (after a mode-switch) aver-      |

|     | age degrees of parallelism                                                     |

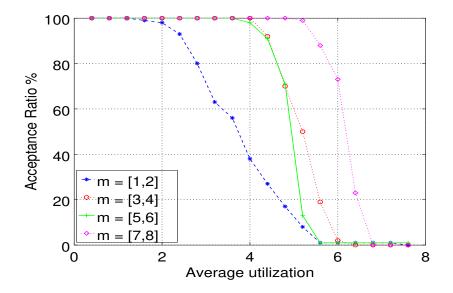

| 7.4 | Acceptance ratio for GEDF-VD in an 8-core platform with $R = 4$ , and under    |

|     | same ranges of degrees of parallelism                                          |

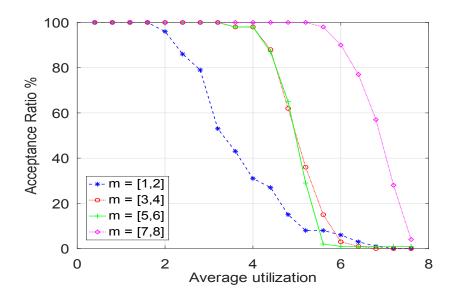

| 7.5 | Acceptance ratio for GEDF-VD in an 8-core platform with $R = 8$ , and under         |

|-----|-------------------------------------------------------------------------------------|

|     | same ranges of degrees of parallelism                                               |

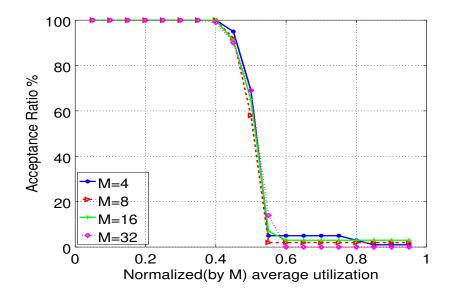

| 7.6 | Acceptance ratio for GEDF-VD in an <i>M</i> -core platform (with $R = 4$ ) 131      |

| 7.7 | Acceptance ratio for GEDF-VD in an <i>M</i> -core platform (with $R = 8$ ) 132      |

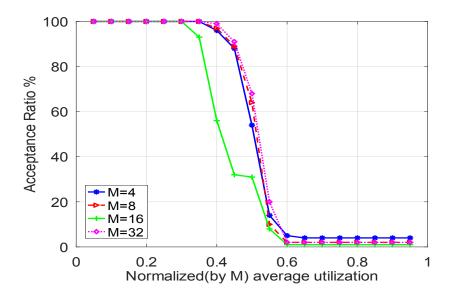

| 7.8 | Acceptance ratio for GEDF-VD in an 8-core platform with $R = 4$ and a               |

|     | varying range of $m_{avg}$                                                          |

| 7.9 | Acceptance ratio for GEDF-VD in an 8-core platform with $R = 8$ and a               |

|     | varying range of $m_{avg}$                                                          |

| 8.1 | Modified EDF-VD schedulability condition and scaling factor $x$                     |

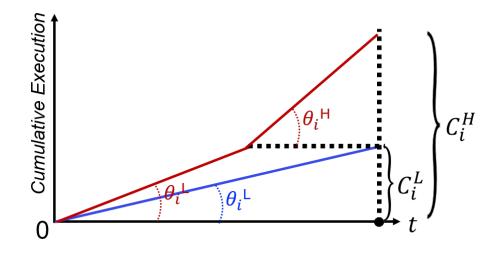

| 8.2 | Relation between fluid execution speed and cumulative execution over time           |

|     | of a task under MCF framework                                                       |

| 8.3 | Modified MCF speed assignments and schedulability condition                         |

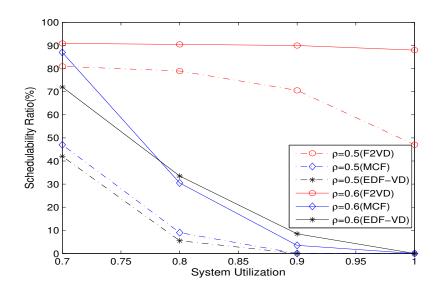

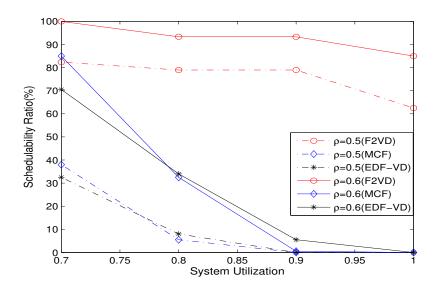

| 8.4 | Comparison of schedulability ratio between F2VD, EDF-VD and the MCF 148             |

| 8.5 | Comparison of schedulability ratio between F2VD, EDF-VD and the MCF 149             |

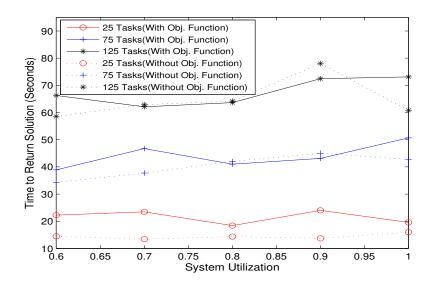

| 8.6 | Time needed by F2VD to return the solution for a different size of task-set 150     |

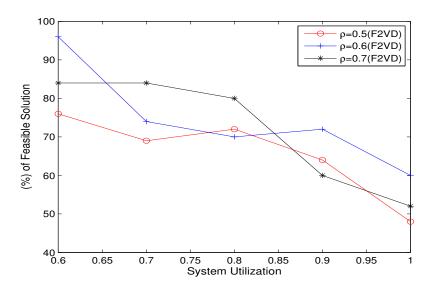

| 8.7 | Percentage of solution returned by the F2VD algorithm under different uti-          |

|     | lization and $\rho$ values                                                          |

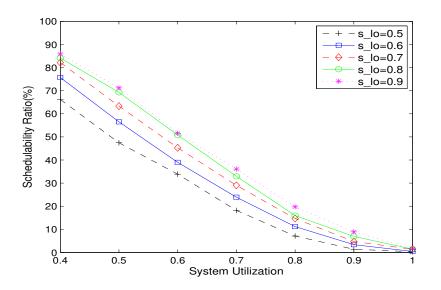

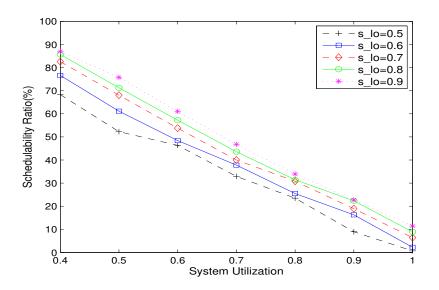

| 8.8 | Schedulability ratio based on the RTA with a different $s_{\rm LO}$ values. In this |

|     | experiment, $[Z_d, Z_u] = [1, 4]$                                                   |

## LIST OF TABLES

| 5.1 | Summary of experimental results                                                                                    |

|-----|--------------------------------------------------------------------------------------------------------------------|

| 6.1 | Estimated parameters for different cluster of an ODROID XU-3 board 86                                              |

| 6.2 | The "uncore" power consumption for different cluster of an ODROID XU-3      board.    87                           |

| 7.1 | An MC gang task set with GEDF schedule shown in Figure 7.1                                                         |

| 7.2 | Acceptance ratio for different amount of tasks generated under various aver-<br>age utilization and <i>R</i> value |

#### **CHAPTER 1: INTRODUCTION**

A real-time system application requires strict timing guarantees, energy efficiency, and high performance. Besides the high-performance requirement and *temporal* constraints, a real-time system must guarantee the *logical* constraints also, i.e., in response to the event generated by the surrounding environment, the system must react within precise time constraints. In modern society, an increasing number of complex systems depend on computer control, and real-time systems are widely deployed in these areas. In such a system, the computing platforms need to satisfy the time preciseness, e.g., chemical and nuclear plant control, automotive applications, flight control systems, smart grid, telecommunication systems, robotics, space missions, and many more [34].

Many embedded system applications have hard real-time constraints, and such an application must preserve precise timing correctness. Many real-time embedded systems include critical applications requiring not only a predictable timing behavior, but also to satisfy other system constraints. Energy consumption is one of them, which might be a non-functional or functional requirement. Embedded systems applications rely on unreliable energy sources, e.g., batteries, energy harvesters, making it essential to consider the energy-efficient design [108]. Energy-efficient design of an embedded system is a prime requirement for many reasons, such as increased battery life, reducing power bills, controlling heat dissipation etc.

Multi-core processors are increasingly receiving attention as an enabling platform for embedded system applications. In a multi-core platform, multiple tasks can execute simultaneously. However, an individual task can not execute on multiple cores simultaneously. Therefore, such a task model, i.e., the *sequential task model* fails to utilize the benefits of a multi-core platform. The *parallel task model* is introduced to tackle the problem mentioned above, where an individual task can simultaneously utilize multiple cores. Many computation-intensive systems (e.g., self-driving cars) that demand stringent timing requirements often evolve in the form of parallel tasks. Also, energy-efficient scheduling of parallel task model is a promising direction to utilize the multi-core platform's computational power. This model promotes a balanced distribution and simultaneous execution of the tasks among the computing platforms, which lead to energy efficiency and reduced computation. The directed acyclic graph (DAG) model is considered as one of the most generalized deterministic workload models to represent intra-task parallelism [17], where nodes represent threads of execution and edges represent their dependencies.

#### 1.1 Challenges in Energy-Aware Real-Time Scheduling

Many recent studies on real-time scheduling and analysis have focused on the DAG task model [102, 17, 81, 30, 109, 82, 16]. However, to date, only a little work has been done for energy-aware real-time scheduling of the DAG task models. In general, minimizing energy/power consumption of a real-time system is challenging for the following reasons:

- In real-time system, a task model is often characterized by the task arrival pattern, the deadline, and the execution time. The relation ship between platform (where the task is running) execution speed, energy consumption, and execution time of each task is non-linear.

- Some approaches proposed minimizing system energy consumption via per-core dynamic voltage and frequency scaling (DVFS). Unfortunately, per-core DVFS becomes inefficient as it increases the hardware cost [70].

- Existing policies (for energy efficiency) assumed that a task would execute up to its Worst-Case Execution Time (WCET), which often differs from reality. A task rarely executes up to its WCET [111]. For several real-life applications, WCET based schedulability analysis is proved to be very pessimistic [84], mainly because of the significant variability be-

tween actual execution requirements and their WCET. Such a WCET-based energy-efficient approach may lead to system over-provisioning, low utilization, high costs, and excessive power/energy consumption [25, 88].

- Mixed-Criticality (MC) framework [122] was proposed to efficiently utilize the non-negligible gap between the WCET and the actual execution time and to minimize energy consumption. Different software components with varying levels of criticality are integrated into a common platform in an MC setup. However, energy-efficient MC scheduling is still immature as it may entirely discard the low-criticality tasks when the system switches to a high-criticality mode [26, 25].

- Although the MC platform allows integrating different software components with varying levels of criticality into a common platform, further improvement in the resource management is possible, as the state of the arts MC scheduling approaches still rely on WCET based estimation at each criticality-levels [25].

#### 1.2 Thesis Statement

Many real-time embedded systems include critical applications requiring timing constraints and other system requirements, such as energy consumption. This thesis aims to answer whether we can integrate the existing energy-aware approaches to the intra-task parallelism so that the overall energy consumption is minimized while maintaining the temporal correctness of a real-time system application. This thesis presents the new energy-aware scheduling techniques, verifies their correctness, and reports empirical evaluation, supporting the following thesis statement:

By appropriately leveraging the energy-saving techniques with the internal parallelism of real-time embedded system applications, it is possible to significantly reduce the system energy consumption without violating the strict timing requirement imposed by the real-time system applications.

#### 1.3 Thesis Contribution and Organization

In this thesis, we tackle the above challenges and make a series of contributions to the theory and system for energy-aware real-time scheduling of parallel task model, as mentioned below:

First, we propose an energy-efficient task scheduling approach considering the DAG task model. Considering a multiprocessor platform, we propose an energy sub-optimal federated scheduling algorithm for sporadic DAG tasks with implicit deadlines (Chapter 3). Based on the solution under federated scheduling, we also present a greedy intra-task processor merging technique which improves the power efficiency. We further improve the processor intra-merge technique by allowing multiple processors to merge at a single one. Besides, we also present the inter-task processor technique (Chapter 4).

Second, we propose a novel technique for energy-efficient scheduling of both the constrained and implicit deadline parallel tasks in a cluster-based homogeneous multi-core system (Chapter 5). As stated earlier, the per-core DVFS technique is becoming inefficient because of its increased hardware cost. The cluster-based platform (processors in the same island execute at the same speed) seems a promising platform to balance energy efficiency and hardware cost. However, the cluster-based platform introduces several challenges as well. The existing solutions were deduced considering the per-core DVFS is no longer valid in a clustered platform. Also, the execution speed of a cluster becomes unpredictable if multiple tasks share it with sporadic release patterns. We introduce a new concept of *speed-profile* that models per-task and per-cluster energy-consumption variations during run-time to minimize the expected long-term energy consumption. Later, we

extend our technique to adapt the more realistic features such as discrete processor frequency scheme and the platform heterogeneity (Chapter 6).

Third, we incorporate the MC context into other well-known parallel task models, i.e., the gang task model (Chapter 7). To schedule such task sets, we propose a new technique GEDF-VD, which integrates Global Earliest Deadline First (GEDF) and Earliest Deadline First with Virtual Deadline (EDF-VD). We also derive the first speedup bound (a widely accepted tool for evaluating the effectiveness of multiprocessor scheduling algorithms) for GEDF schedulability of non-MC gang tasks and further derived the bound for GEDF-VD of MC gang tasks.

Finally, we show the response time analysis of MC task so that the probabilistic technique described in [25] minimizes the average energy consumption while guaranteeing the (worst-case) timing correctness for all tasks, under any execution condition (Chapter 8).

#### **CHAPTER 2: PRELIMINARIES AND NOTATION**

This chapter introduces a widely used representative of a real-time parallel task model, power model and some of the major notations used throughout this thesis.

#### 2.1 Real-Time Parallel Task Model

Now, we describe two different types of parallel tasks considered in this thesis. There are multiple parallel languages and libraries, e.g., Intel Cilk Plus [73], OpenMP [96], etc., to write parallel programs. The directed acyclic graphs (DAG) task model and the gang task model is often used to model these programs.

#### 2.1.1 DAG Task Model

The set of DAG task is denoted by denoted by  $\tau = \{\tau_1, \dots, \tau_n\}$ , where each  $\tau_i \in \tau$   $(1 \leq i \leq n)$ is represented as a DAG with a minimum inter-arrival separation (i.e., period) of  $T_i$  time units, and a relative deadline of  $D_i (\leq T_i)$  time units. An implicit deadline task has the same relative deadline and period, i.e.,  $D_i = T_i$ , while for a *constrained deadline* task, the relative deadline  $D_i$ is less than  $T_i$ . The *nodes* in a DAG stand for different execution requirements while the *edges* represent the dependencies among the corresponding execution requirements. A parallel task  $\tau_i$ contains a total number of  $N_i$  nodes, each denoted by  $\mathcal{N}_i^j (1 \leq j \leq N_i)$ . A directed edge from  $\mathcal{N}_i^j$  to  $\mathcal{N}_i^k (\mathcal{N}_i^j \to \mathcal{N}_i^k)$  implies that execution of  $\mathcal{N}_i^k$  can start if  $\mathcal{N}_i^j$  finishes for every instance

The contents of this chapter have been previously published at and available at:

<sup>1.</sup> Bhuiyan, A., Guo, Z., Saifullah, A., Guan, N., & Xiong, H. (2018). Energy-efficient real-time scheduling of DAG tasks. ACM Transactions on Embedded Computing Systems (TECS), 17(5), 1-25.

<sup>2.</sup> Bhuiyan, A., Yang, K., Arefin, S., Saifullah, A., Guan, N., & Guo, Z. (2021). Mixed-criticality real-time scheduling of gang task systems. Real-Time Systems, 1-34.

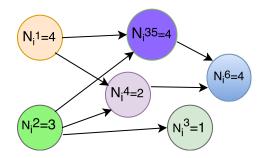

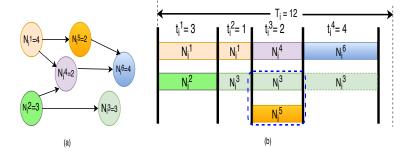

Figure 2.1: An example heavy DAG task  $\tau_i$ .

(precedence constraints). In this case,  $\mathcal{N}_i^j$  is called a parent of  $\mathcal{N}_i^k$  ( $\mathcal{N}_i^k$  is a child of  $\mathcal{N}_i^j$ ). A node may have multiple parents or children. The *degree of parallelism*,  $\mathcal{M}_i$ , of  $\tau_i$  is the number of nodes that can be simultaneously executed.  $c_i^j$  denotes the execution requirement of node  $\mathcal{N}_i^j$ .  $C_i := \sum_{j=1}^{N_i} c_i^j$  denotes the worst case execution requirement (WCET) of  $\tau_i$ .

A critical path is a directed path with the maximum total execution requirements among all other paths in a DAG.  $L_i$  is the sum of the execution requirements of all the nodes that lie on a critical path. It is the minimum make-span of  $\tau_i$ , i.e., in order to make  $\tau_i$  schedulable, at least  $L_i$  time units are required even when number of cores is unlimited. Since at least  $L_i$  time units are required for  $\tau_i$ , the condition  $T_i \ge L_i$  (implicit deadline tasks) and  $D_i \ge L_i$  (constrained deadline tasks) must hold for  $\tau_i$  to be schedulable. A schedule is said to be feasible if upon satisfying the precedence constraints, all the sub-tasks (nodes) receive enough execution from their arrival times, i.e.,  $C_i$ within  $T_i$  (implicit deadline) or  $D_i$  (constrained deadline) time units.

A DAG is *heavy* if its execution requirement is greater than its period (i.e.  $C_i > T_i$ ). A schedule is said to be *feasible* when all sub-tasks (nodes) receive enough execution (up to their execution requirements) within  $T_i$  time units from their arrivals, while all precedence constraints are satisfied. The aforementioned terms are illustrated with the help of Figure 2.1 and Example 1. **Example 1.** The DAG task  $\tau_i$  (shown in Figure 2.1) is a heavy DAG with total execution time  $C_i = 18$  and minimum inter-arrival separation  $T_i = 12$ . It has a critical path length of 10  $(\mathcal{N}_i^1 \to \mathcal{N}_i^4 \to \mathcal{N}_i^6 \text{ or } \mathcal{N}_i^1 \to \mathcal{N}_i^5 \to \mathcal{N}_i^6)$ . As the critical path length  $L_i$  is less than the task period  $T_i$ , this task may meet its deadline provided enough processors.

#### 2.1.2 Gang Task Model

In traditional gang task model, each task  $\tau_i$  is represented with a 4-tuple  $(m_i, c_i, T_i, D_i)$ , where  $m_i$  is the degree of parallelism and each job of task  $\tau_i$  requires access to  $m_i$  cores for at most  $c_i$  time units to complete its execution,  $T_i$  is the task period, and  $D_i$  is the relative deadline. In gang scheduling, each task is consists of multiple threads (referred to as a gang), and each thread of the same task occupies a processor for the same time quantum [76, 46]. Hence, in the time-space, the execution requirement of any job  $\tau_{i,j} \in \tau_i$  can be represented as an  $m_i \times c_i$  rectangle. The relative deadline  $D_i$  specifies that for each of the released jobs  $\tau_{i,j}$  (of task  $\tau_i$ ), its deadline  $d_{i,j} = r_{i,j} + D_i$ , where  $r_{i,j}$  denotes the release time of  $\tau_{i,j}$  [46].

The *utilization*  $u_i$  of each task  $\tau_i \in \tau$  is given by  $u_i = (m_i c_i)/T_i$ , and the overall system utilization is:  $U_{sum} = \sum_{\tau_i \in \tau} u_i$ . Note that, it is possible that the value of  $u_i$  is larger than one, which is different from the traditional sequential task model. Based on the scheduling flexibility, a gang task  $\tau_i$  can be categorized into three groups. A task  $\tau_i$  is said to be:

- *rigid*, if  $m_i$  is fixed a priori and does not change throughout the execution,

- moldable, if  $m_i$  is fixed during its activation and does not change throughout the execution,

- malleable, if  $m_i$  is not fixed and can be changed during its execution by the scheduler.

In this thesis, we restrict our attention to the *rigid* task model. This model suits various applications

that use parallelism, some of which are implemented using the message-passing approach and tools like MPI.

#### 2.2 Power/Energy Model

Let s(t) (we are assuming continuous frequency scheme) denote the main frequency (speed) of a processor at a certain time t. Then its power consumption P(s) can be modeled as:

$$P(s) = P_{sta} + P_{dyn}(s) = \beta + \alpha s^{\gamma}, \qquad (2.1)$$

where  $P_{sta}$  denotes the static power consumption which is introduced in the system due to the leakage current and  $P_{dyn}(s)$  denotes the active power consumption.  $P_{dyn}(s)$  is introduced due to the switching activities and it depends on the processor frequency.  $P_{dyn}(s)$  can be represented as  $\alpha s^{\gamma}$ where the constant  $\alpha > 0$  depends on the effective switching capacitance[98],  $\gamma \in [2,3]$  is a fixed parameter determined by the hardware, and  $\beta > 0$  represents the leakage power (i.e., the static part of power consumption whenever a processor remains on). Clearly, the power consumption function is a convex-increasing function of the processor frequency. By means of dynamic voltage and frequency scaling (DVFS), it is possible to reduce  $P_{dyn}(s)$  by reducing the processor frequency. In this paper, we focus on minimizing the active energy consumption (due to  $P_{dyn}(s)$ ) by means of DVFS. We also target to minimize the static power consumption (due to  $P_{sta}$ ) by reducing the number of processors by allowing intra-task processor sharing.

Note that static power consumption is partially related to frequency. It is mainly because highest frequency (that can be used) can be margined by the voltage level which is inversely proportional to the circuit delay. Such relationship is counted towards the dynamic part of the power consumption by adopting a slightly larger  $\gamma$  value. Various platforms may take different values, yet the pro-

posed approach should work in general. Besides, we assume that each core can execute with any frequency ranged between  $f_{min}$  to  $f_{max}$ , where,  $f_{min} \ge \text{critical frequencies}^1$  [98]. Within this allowable frequency range  $[f_{min} - f_{max}]$  we consider the upper bound of static energy consumption. Hence we can consider that static energy consumption is fixed w.r.t. the frequency.

Our motivation behind selecting this power model comes from the fact that it complies with many existing works in the community, few to mention [7, 98, 99, 72, 92, 67, 23]. Beside this, recently this model was shown to be highly realistic by showing its similarity with actual power consumption [99]. Figure 2.2 (adopted from [98]) shows comparison between the original power consumption results from [71] and the power model in Equation (2.1), where we consider  $\alpha = 1.76Watts/GHz^3$ ,  $\gamma = 3$ , and  $\beta = 0.5$  Watts.

Figure 2.2: Comparison of the power model (Equation (2.1)) with experimental results in [71].

The energy consumption of any given period [b, f] can be calculated as  $E(b, f) = \int_b^f P(s(t)) dt$ , which is known as a nice approximation to the actual energy consumption of many known systems. Specifically, given a unit-amount of workload to be executed on a speed-s processor, the total energy consumption is the integral of power over the period of length 1/s; i.e.,

$$E(s) = (\beta + \alpha s^{\gamma})/s = \beta/s + \alpha s^{\gamma - 1}$$

(2.2)

<sup>&</sup>lt;sup>1</sup>Optimal frequency to reduce the energy consumption (considering a negligible sleeping overhead).

Figure 2.3: Energy consumption for executing a job with  $10^9$  computation cycles with a fixed  $\alpha$ ,  $\beta$  and a variable  $\gamma$  value.

Figure 2.3 shows how different values of  $\gamma$  (varying from 2 to 3) and processor speed *s* may affect the total energy consumption to complete a certain (fixed) amount of computation. This figure reports the energy consumption for executing a job with 10<sup>9</sup> computation cycles under various  $\gamma$  values, where  $\alpha = 1.76$  watts/GHz, and  $\beta = 0.5$  watts. Energy Consumption is calculated according to Equation (2.2), and the lowest points represent the most energy efficient execution frequency, i.e., *critical frequency*. It is obvious that execution under a speed much lower than the critical frequencies is extremely energy inefficient (as leakage power becomes the major "contributior"). The power model we adapted complies with much existing (and recent) work in the community, e.g., [7] [125] [44] [98] [99] [67].

# CHAPTER 3: ENERGY-EFFICIENT FEDERATED SCHEDULING OF REAL-TIME DAG TASKS WITH INTRA-TASK PROCESSOR MERGING

This chapter studies energy-aware real-time scheduling of a set of sporadic Directed Acyclic Graph (DAG) tasks with implicit deadlines. While meeting all real-time constraints, we try to identify the best task allocation and execution pattern such that the average power consumption of the whole platform is minimized. This work addresses the power consumption issue in scheduling multiple DAG tasks on multi-cores and allows intra-task processor sharing. We adapt the decomposition-based framework for federated scheduling and propose an energy-sub-optimal scheduler. Then, we derive an approximation algorithm to identify processors to be merged together for further improvements in energy-efficiency. The effectiveness of the proposed approach is evaluated both theoretically via approximation ratio bounds, and also experimentally through simulation study. Experimental results on randomly generated workloads show that our algorithms achieve an energy saving of 60% to 68% compared to existing DAG task schedulers.

#### 3.1 Introduction

Due to size and weight limitations in embedded systems, energy consumption is a cornerstone in their design, especially for battery-operated ones. Energy-efficient and power-aware computing therefore are gaining increasing attention in the embedded systems research. It is important due to the market demand of increased battery life for portable devices. Moreover, reducing energy consumption could lead to smaller power bills. Being motivated by this goal, there has been a trend in embedded system design and development towards multi-core platforms. In order to better uti-

This chapter has been previously published at ACM Transactions on Embedded Computing Systems and available at Bhuiyan, A., Guo, Z., Saifullah, A., Guan, N., & Xiong, H. (2018). Energy-efficient real-time scheduling of DAG tasks. ACM Transactions on Embedded Computing Systems (TECS), 17(5), 1-25.

Figure 3.1: Partial work-flow of a UAV system represented as a DAG.

lize the capacity of multi-core platforms, parallel computation (where an individual task executes in multiple processors simultaneously) needs to be considered. For Example, a recent study [98] has shown that the energy consumption of executing certain workload perfectly distributed in two cores is significantly less than that of executing the same workload in one core at double frequency.

In this chapter, we deal with workloads that are represented as directed acyclic graph (DAG) — that are considered to be one of the most representative models of deterministic parallel tasks [17]. Several real-world application uses the DAG model ([68, 102, 74]). For example, consider the application shown in Figure 3.1. In this figure, we present the partial work-flow of an *unmanned aerial vehicle (UAV)* which is adopted from [112]. Here, each rectangular box denotes a subtask (or node in the DAG) with their execution requirements (not shown in the figure) and edges represent data dependencies among them. As described above, a node cannot start execution until all of its parents are completed, and some of the nodes can be executed in parallel, e.g. *Satellite* and *Remote Control*. There are many existing works that focused on real-time scheduling of parallel tasks or their schedulability analysis [17] [30] [81][10] [82]. However, none of them addressed the energy consumption issue.

**Energy-Aware Real-Time Scheduling.** In the design of embedded systems, energy minimization is a prime requirement. Much work has been done on minimizing the energy cost with respect to sequential tasks for multi-core systems [55] [99] [98] [92]. Specifically, [98] and [99] present an energy efficient task partitioning scheme, where the cores are grouped in frequency islands. The

authors in [7] considers both feasibility and energy-awareness while partitioning periodic real-time tasks on a multi-core platform. For EDF scheduling, they show that if the workload is balanced evenly among the processors, deriving optimal energy consumption and finding a feasible partition is NP-Hard. Till date, only a little work has been done for energy-aware real-time scheduling of parallel tasks. In general, minimizing energy/power consumption of a real-time system is challenging due to the complex (non-linear) relationship between frequency, energy consumption, and execution time of each task.

In this chapter, we study the scheduling of a set of sporadic DAG tasks with implicit deadlines on a multi-core platform. We assume that all the cores that are assigned to a DAG task will always remain active, which leads to a non-negligible power consumption. In order to reduce this effect, we allow intra- and inter-task processor sharing to remove or reduce the number of lightly loaded cores. After merging, the cores that are not required can be shut off completely. When the average case execution times are typically small compared to the worst-case execution time (WCET), the cores will remain idle (in that case the active power consumption will be minimized, refer to the Power model described at Chapter 2). Specifically, we make the following key contributions:

(i) We propose a power-consumption-aware scheduling algorithm for sporadic DAG tasks with implicit deadlines.

(ii) Under the federated scheduling and task decomposition framework, our table-driven scheduler is shown to be optimal in the sense of average power consumption (i.e., named sub-optimal due to extra constraints included).

(iii) We propose an efficient processor merging technique that is widely applicable for energyefficiency improvements to most of the existing work on federated DAG task scheduling. We formally prove the NP-completeness of the problem, propose an approximation algorithm, and prove the upper bound of its approximation ratio. (iv) Based on randomly generated workload, simulations are conducted to verify the theoretical results and demonstrate the effectiveness of our algorithm.

The rest of this chapter is organized as follows. Section 3.2 discusses related work. Section 3.3 adapts the task decomposition scheme and proposes an (sub-) optimal federated scheduler based on segment extension and problem transformation (into a convex optimization with linear inequality constraints). Section 3.4 relaxes the federated limitation by presenting and analyzing techniques for intra-DAG and inter-DAG processor merging, so that energy consumption is further reduced. Section 3.5 implements gradient based solvers and compares the proposed method with state-of-the-art schedulers. Section 3.6 concludes the chapter.

#### 3.2 Related Work

The work that deals with schedulability tests for various scheduling policies on parallel task model is already mentioned in Section 3.1. None of them has considered power/energy consumption issues. In addition, much work has been done in energy/power consumption minimization for sequential tasks. Bini et al. discuss the problem of finding an optimal solution for a system with discrete speed levels for a set of periodic/sporadic tasks [28]. They have considered both EDF and Fixed-Priority (FP) scheduling policies. Jejurikar has considered non-preemptive tasks in order to deal with shared resources [75]. Chen et al.and Liu et al. presents an energy-efficient design for heterogeneous multiprocessor platform in [39] and [85] respectively. No previous work considers parallel task model.

For parallel task models, several results are obtained on schedulability tests under various scheduling policies in [17] [30] [10]. [30] prove a speedup bound of (2 - 1/m) for Earliest Deadline First (EDF) and (3 - 1/m) for Deadline Monotonic (DM) respectively, where m is the number of processors. For global EDF scheduling, these techniques are further generalized [10] with an improved pseudo-polynomial time sufficient schedulability test. Analysis of federated and global EDF scheduling is performed in [81] [82]. Processor-speed augmentation bounds for both preemptive and non-preemptive real-time scheduling on multi-core processors are derived in [109]. The work in [16] studies global EDF scheduling for conditional sporadic DAG tasks, which is an extension to the normal sporadic DAG task model. Certain conditional control-flow constructs (such as *if-then-else* constructs) can be modeled using the conditional sporadic DAG tasks, none of them addresses the energy/power consumption issue.

Actually, intra-task parallelization and power consumption issues have not yet received sufficient attention. Zhu et al. have considered power-aware scheduling for graph-tasks [129]. The work in [130] proposed the greedy slack stealing algorithm that is able to deal with the task represented by AND/OR graphs. It proves the correctness of the proposed algorithm in terms of meeting the applications time constraint considering it is executing on an N-processor system. Through simulation, it has also analyzed the performance of the algorithm in terms of processor energy saving and showed that the GSS is able to achieve some energy efficiency. However, that work considered the scheduling of only a single DAG and the DAG was not periodic/recurrent. For dependent tasks, [37] provides techniques that combine dynamic voltage and frequency scaling (DVFS) and dynamic power management, where each core in the platform can be switched on and off individually. For block-partitioned multi-core processors (where cores are grouped into blocks and each block has a common power supply scaled by DVFS), energy efficiency is investigated in [103]. The authors in [101] consider power-aware policy for scheduling parallel hard real-time systems, where the multi-thread processing is used. [100] considers dealing with parallel tasks under Gang scheduling policy, where all parallel instances of a task use a processor in the same window. The authors in [124] have considered energy minimization for frame-based tasks (i.e.,

same arrival time and a common deadline for all the tasks) with implicit deadlines. Similar frame based model is considered in [64], where precedence constraints can be specified among the tasks. As mentioned previously, no existing work allows intra and inter-task processor sharing when considering the (more general) sporadic DAG task workload model.

## 3.3 Energy-Sub-Optimal Federated Scheduling for DAG Tasks

In this section, we restrict our focus on the federated scheduling of DAG tasks, refer to Section 2.1.1 for details regarding the DAG model. Under the federated approach to multi-core scheduling, each individual task is either restricted to execute on a single processor (as in partitioned scheduling), or has exclusive access to all the processors on which it may execute. Since each processor is dedicated to one DAG task, we can consider each task individually, and try to minimize the energy consumption for a single DAG task (which is the goal of this section).

Given a DAG task, we first apply the existing task decomposition [109] technique to transform a parallel task into a set of sequential tasks with scheduling window (for a specific node it denotes the time frame from its release offset to its deadline) constraints for each node (Subsection 3.3.1) – they are further relaxed into necessary conditions by segment extension (Subsection 3.3.2). By variable substitution, we then transform the energy minimization problem into a convex optimization problem with linear inequality constraints, which can be solved *optimally* with gradient-based methods (Subsection 3.3.3).

## 3.3.1 Task Decomposition

Task decomposition is a well-known technique that simplifies the scheduling analysis of parallel real-time tasks [109]. In our approach, we adopt task decomposition as the first step that converts

each node  $\mathcal{N}_i^l$  of the DAG task  $\tau_i$  to an individual sub-task  $\tau_i^l$  with a release offset  $(b_i^l)$ , deadline  $(f_i^l)$ , and execution requirement  $(c_i^l)$ . The release time and deadlines are assigned in a way that all dependencies (represented by edges in the DAG) are respected. Thus the decomposition ensures that if all the sub-tasks are schedulable then the DAG is also schedulable. For the sake of completeness, we briefly describe how task decomposition works in this subsection with an example.

We adapt a slightly modified version of the approach used in [109]. First, we perform the task decomposition using the techniques in [109] as described below. Assuming the execution of the task is on an unlimited number of cores, we draw a vertical line at every time instant where a node starts or ends for each node starting from the beginning. These vertical lines split the DAG into segments, and each segment consists of an equal amount of execution by the nodes that lie in the segment. Parts of different nodes in the same segment can now be considered as threads of execution that run in parallel, and the threads in a segment can start only after those in the preceding segment have finished their executions. Now we will say that the resulting segmented structure of the task is converted into synchronous form and will denote it as  $\tau_i^{syn}$ . We first allocate time to the segments and then add all times assigned to different segments of a node to calculate its allocated time.

(b) Scheduling window constraints for all nodes in  $\tau_i$  after task decomposition.

Figure 3.2: A DAG task and its equivalent decomposed structure.

Since the minimum makespan,  $L_i \leq T_i$ , at the end of each period, there may be a slack where all processors are idle (which is typically energy inefficient). We allocate such idle period *uniformly* by multiplying each segment by a common factor of  $T_i/L_i$  for task  $\tau_i$ . Task decomposition provides its processor assignment  $\mathcal{M}_i^l$  (i.e., a node-to-processor mapping) and a scheduling window  $[b_i^l, f_i^l)$ on top of it, in which each node  $\mathcal{N}_i^l$  of a task  $\tau_i$  will be scheduled. In Example 2 and Example 3, we demonstrate the concept of task decomposition and scheduling window.

**Example 2.** Consider task  $\tau_i$  shown in Figure 3.2(a). First, we assign all the nodes with no parent  $(\mathcal{N}_i^1 \text{ and } \mathcal{N}_i^2)$  to separate processors. Then we continue to consider nodes only when all its parent node(s) are assigned. As a result, the beginning of the node will be the latest finishing time of its parent(s) — these are boundaries of the segments, denoted by vertical lines in Figure 3.2(b). Specifically, if a node has a single parent, we can start to consider the node right after the finishing time of its parent. For example, when  $\mathcal{N}_i^2$  is completed,  $\mathcal{N}_i^3$  is immediately assigned to the same processor (as  $\mathcal{N}_i^2$  is the only parent).

When a node has multiple parents, we consider the parent that has the latest finishing time. The child node may be assigned to the same processor assigned to its parent with the latest finishing time. For example,  $\mathcal{N}_i^4$  has two parents  $\mathcal{N}_i^1$  and  $\mathcal{N}_i^2$  where  $\mathcal{N}_i^1$  completes execution later. So  $\mathcal{N}_i^4$  is assigned to the same processor of  $\mathcal{N}_i^1$ . Please note that a node may have multiple siblings such that it may not always share the same processor with its latest finished parent node — under such scenario, a new processor is allocated to the node. For example, the only parent of  $\mathcal{N}_i^5$  is  $\mathcal{N}_i^1$  which completes execution at  $t_i^2$ . So  $\mathcal{N}_i^5$  would be able to execute in the same processor starting from the third segment. But  $\mathcal{N}_i^5$  is assigned to a different processor as that specific processor at  $t_i^3$  is already "taken" by its sibling  $\mathcal{N}_i^4$ .

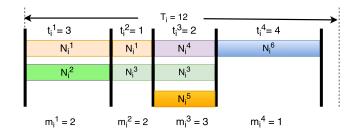

**Example 3.** Let,  $m_i^k$  denotes the degrees of parallelism at  $k^{th}$  segment and the node-core mapping is:  $\overline{\mathcal{M}}_i = \{1, 2, 2, 1, 3, 1\}$ . Scheduling windows for these nodes (from Figure 2.1) are as follows:  $\mathcal{N}_i^1 = [1, 2], \ \mathcal{N}_i^2 = [1, 1], \ \mathcal{N}_i^3 = [2, 3], \ \mathcal{N}_i^4 = [3, 3], \ \mathcal{N}_i^5 = [3, 3], \ \mathcal{N}_i^6 = [4, 4]$ . In this example,

| 4                                 |                                 | T <sub>i</sub> = 12         | >                               |

|-----------------------------------|---------------------------------|-----------------------------|---------------------------------|

| t <sub>i</sub> <sup>1</sup> = 3.6 | t <sub>i</sub> ²= 1.2           |                             | $t_i^4 = 4.8$                   |

| Ni <sup>1</sup>                   | Ni <sup>1</sup>                 | Ni <sup>4</sup>             | N <sub>i</sub> <sup>6</sup>     |

| Ni <sup>2</sup>                   | N <sub>i</sub> <sup>3</sup>     | N <sub>i</sub> <sup>3</sup> | Ni <sup>3</sup>                 |

|                                   |                                 | Ni <sup>5</sup>             |                                 |

| m <sub>i</sub> <sup>1</sup> = 2   | m <sub>i</sub> <sup>2</sup> = 2 | mi <sup>3</sup> = 3         | m <sub>i</sub> <sup>4</sup> = 2 |

Figure 3.3: The segment-node mapping for  $\tau_i$  (from Figure 2.1) after segment extension.

the average power consumption (under such settings) is 3.33 Watts after extending each segment by a common factor of  $T_i/L_i = 1.2$ .

# 3.3.2 Segment Extension

For a DAG task  $\tau_i$ , the aforementioned task decomposition results in a mapping between a node  $(\mathcal{N}_i^l)$  and a processor  $(\mathcal{M}_i^l)$ . One of the key issues with the task decomposition process is that the identified scheduling window constraints for the nodes may not be necessary. Take the task described in Figure 3.2 as an example, where Node  $\mathcal{N}_i^3$  may execute in the 4th segment. However, task decomposition requires that Node  $\mathcal{N}_i^3$  must finish by the end of Segment 3, which is unnecessary. In this subsection, we describe a systematic way of eliminating such unnecessities so that the boundary constraints for all nodes  $(b_i^l)$  and  $f_i^l$  are both *necessary* and *sufficient*.

Each DAG  $\tau_i$  is first converted to a synchronous form denoted by  $\tau_i^{syn}$  with techniques described in Section 3.3.1. We use  $m_i^k$  to denote the number of parallel threads in the k-th segment of  $\tau_i^{syn}$ . We then apply Algorithm 1 to greedily extend the deadlines  $f_i^l$  of each node  $\mathcal{N}_i^l$ , following any topological order. Note that while performing task decomposition, a node starts execution immediately when all of its predecessors finish execution. Thus the starting time  $b_i^l$  cannot be moved earlier — only  $f_i$ 's have room to be relaxed.

Task decomposition technique determines scheduling window constraints for the nodes which are sufficient but may not be necessary. If segment extension is performed (using Algorithm 1) after applying task decomposition, scheduling window constraints become *necessary* and *sufficient* (see Lemma 1). It may happen that for some particular DAG structure, Algorithm 1 fails to change (i.e. expand) scheduling window for any node. However, it does not impact the schedulability of the DAG. From this discussion, it should be clear that performing segment is not mandatory but it is done to further reduce the energy consumption.

Note that we have considered table-driven schedulers which usually pre-compute which task would run when. This schedule is stored in a table at the time the system is designed. When a set of n tasks is to be scheduled, then the entries in the table will replicate themselves after LCM  $(T_1, T_2 \cdots T_n)$ , where LCM  $(T_1, T_2 \cdots T_n)$  is the hyper-period for the tasks. However, while considering energy consumption we did not consider the space complexity of the scheduling solutions.

# Algorithm 1: Segment Extension

- 1: Input: A DAG  $\tau_i$ , scheduling windows after decomposition  $[b_i^l, f_i^l]$  for any node  $\mathcal{N}_i^l \in \tau_i$ .

- 2: **Output:** Extended segment window  $[b_i^l, f_i^l)$  for each node  $\mathcal{N}_i^l \in \tau_i$ .

- 3: Assume that all nodes  $\mathcal{N}_i^l$  are ordered topologically, such that predecessor constraint may only occur between  $\mathcal{N}_i^l \longrightarrow \mathcal{N}_i^{l'}$  when l < l'.

- 4: for each node  $\mathcal{N}_{i}^{l} \in \tau_{i}$  do 5: if node  $\mathcal{N}_{i}^{l}$  has successor node(s); i.e.,  $\exists l', \mathcal{N}_{i}^{l} \longrightarrow \mathcal{N}_{i}^{l'}$ 6: then  $f_{i}^{l} \leftarrow \min_{l' \mid \mathcal{N}_{i}^{l} \longrightarrow \mathcal{N}_{i}^{l'}} \{b_{i}^{l'}\} 1;$

- else  $f_i^l \leftarrow$  last segment of  $\tau_i^{syn}$ ; 7:

- 8: end for

- 9: **return**  $[b_i^l, f_i^l]$  for each node  $\mathcal{N}_i^l$ .

**Example 4.** Consider again the DAG task  $\tau_i$  shown in Figure 2.1. Algorithm 1 greedily extends the ending segment  $f_i^l$  of the nodes as much as possible in the topological order (i.e., increasing l). After applying Algorithm 1, scheduling windows for all the nodes changes as follows:  $[1, 2], [1, 1], [2, 4], [3, 3], [3, 3], [4, 4], i.e., Node <math>\mathcal{N}_i^3$  can now execute in Segment 4 (dashed rectangle at Figure 3.3) and the execution window for all the other nodes remain unchanged. Note that the processor assignment  $\mathcal{M}_i^l$  for any node  $\mathcal{N}_i^l$  of a task  $\tau_i$  remains unchanged in the segment extension process. Such an extension results in an average power consumption of 3.08 Watts.

**Lemma 1.** Under the task decomposition and scheduling framework, after running Algorithm 1, the timing constraints we set for each node in a DAG become necessary and sufficient.

*Proof.* First, we show that if task decomposition is considered the timing constraints set for each node in a DAG is only sufficient. Then we prove that if the segment extension is applied after employing the task decomposition, it makes the timing constraints necessary and sufficient. Upon task decomposition, calculated scheduling window for each node satisfies all predecessor constraints, without changing the deadline for the DAG and it completes the proof of sufficient part. Now we prove that the timing constraints are unnecessary by proving a simple example. Consider the task described in Figure 3.2 again. Task decomposition requires that Node  $\mathcal{N}_i^3$  must finish by the end of Segment 3, which is unnecessary because it may execute in the 4<sup>th</sup> segment.

Now consider both task decomposition and segment extension are applied to a DAG. In that case, the sufficient part is trivial. The scheduling window satisfies all predecessor constraints, while the deadline for the DAG task does not change.

Assume the window after modification  $[b_i^l, f_i^l]$  for some node  $\mathcal{N}_i^l$  is not necessary; i.e., it can be further extended. Then it must be one of the following two cases:

- An earlier  $b_i^l$  still satisfies all predecessor constraints, which is impossible since it is the time all parents are finished.

- A later  $f_i^l$  is possible, which contradicts with Lines 5 7 of Algorithm 1 as it is already the starting point of its child, or the deadline of the whole DAG.

#### 3.3.3 Problem Transformation

After task decomposition and segment extension, we have identified the scheduling window  $[b_i^l, f_i^l]$  for each node  $\mathcal{N}_i^l$ , and there is no overlap for any two windows (for different nodes) on the same processor. A natural question arises: *Given a specific node (job) with a pre-determined scheduling window on a dedicated processor, what is the most energy-efficient execution (speed) pattern?*

**Theorem 2.** The total energy consumption (assuming processor remains on)  $\int_{a}^{a+\Delta} s(t)^{\gamma} dt$  is minimized in any scheduling window  $[a, a + \Delta]$  of length  $\Delta$  when execution speed remains the same; i.e.,  $s(t) \equiv C/\Delta$ , where  $C = \int_{a}^{a+\Delta} s(t) dt$  is the (given) task demand in the window.

*Proof.* We define p(t) = s(t)/C, then p(x) is a probability density function (PDF) over  $[a, a + \Delta]$ ; i.e.,

$$\int_{a}^{a+\Delta} p(t) dt = 1.$$

(3.1)

As a result,

$$\int_{a}^{a+\Delta} s(t)^{\gamma} dt = \int_{a}^{a+\Delta} (C \cdot p(t))^{\gamma} dt$$

{re-arranging}

$$= \frac{C^{\gamma}}{\Delta^{\gamma-1}} \cdot \left(\frac{1}{\Delta} \int_{a}^{a+\Delta} (\Delta \cdot p(t))^{\gamma} dt\right)$$

(3.2)

{Jenson's Inequality [26], the conversity of function  $\pi^{\gamma}$

{Jensen's Inequality [36], the convexity of function  $x^{\gamma}$

when  $2 \le \gamma \le 3$  and  $x \ge 0$ , and p(x) being a PDF}

$$\geq \frac{C^{\gamma}}{\Delta^{\gamma-1}} \left( \int_{a}^{a+\Delta} p(t) dt \right)^{\gamma}$$

{From (3.1)}

$$= \frac{C^{\gamma}}{\Delta^{\gamma-1}}$$

(3.3)

{Definition of integrating a constant function}

$$= \int_{a}^{a+\Delta} \left(\frac{C}{\Delta}\right)^{\gamma} dt.$$

Thus, the minimal total energy consumption in the specified interval  $\int_{a}^{a+\Delta} s(t)^{\gamma} dt$  can be achieved when speed s(t) remains constant  $(C/\Delta)$  throughout the interval  $[a, a + \Delta]$ .

According to Theorem 2, executing all segments with a uniform speed yields minimum possible power consumption under such framework. Hence we can assume that *the speed of any processor does not change within a segment*. Let  $S_j^k$  denote the speed of processor j in the k-th segment (executing node  $\mathcal{N}_i^l$ ), and  $t_i^k$  denote the length of the segment. The objective is to determine the length of each segment  $t_i^k (\geq 0)$  and its execution speed  $S_j^k (\geq 0)$  such that total power consumption is minimized.

The first set of constraints guarantees the real-time correctness that each node  $\mathcal{N}_i^l$  receives enough execution within its designated window  $[b_i^l, f_i^l)$  on its assigned processor  $\mathcal{M}_i^l$ ; i.e.,

$$\forall l, \mathcal{N}_i^l \in \tau_i : \sum_{k=b_i^l}^{f_i^l} t_i^k S_{\mathcal{M}_i^l}^k \ge c_{i,l}.$$

(3.4)

We need one more set of inequalities to bound the total length for all segments of each DAG by its

period:

$$\forall i, \sum_{k} t_i^k \le T_i. \tag{3.5}$$

Any non-negative speed assignment and segment length setting that satisfy the constraints described in (3.4) and (3.5) yield a *correct* schedule that all nodes receive enough execution in their specified scheduling windows (that satisfy all predecessor constraints). Based on these constraints, we would like to add our objective for minimizing average energy consumption per period:

$$\mathbf{Minimize}_{\{t_i^k, S_j^k\}} \ M_i \beta T_i + \sum_{l=1}^{\zeta_i} \sum_{k=b_i^l}^{f_i^l} t_i^k \alpha(S_{\mathcal{M}_i^l}^k)^{\gamma},$$

where  $M_i$  is the degree of parallelism (and also the number of processors assigned to the task) and  $\zeta_i$  is the total number of segments assigned to DAG task  $\tau_i$  (determined in the previous step). Since the constraints represented in (3.4) are non-convex quadratic inequalities, it is in general computationally intractable to solve in polynomial time. We transform this problem into a convex optimization by substituting some variables.

**Remark 1.** According to Theorem 2, executing all segments with a uniform speed yields minimum possible power consumption. If any segment of any core remains idle (scheduling window for any node does not fall at that segment), we consider that the execution speed for that segment is 0.

**Remark 2.** In this chapter, we are assuming that the time required to finish a task is exactly equaled to their WCET. However, it may happen that some of the tasks may finish early than their WCET. In that case, some of the cores (that are assigned to that tasks) may remain idle for some time. In this work, we did not consider that the cores can switch into a deep sleep state during the idle time. Entering into the deep sleep state costs additional energy consumption and it is not beneficial if the idle time slot is less than a certain threshold. By remaining idle we mean that one or more cores are active but not executing any task. It helps to reduce the active power consumption (i.e.  $P_d(s)$  in Equation (2.1)). It would lead to the further minimization of the total power consumption (refer to the Power/Energy model described at Section 2). So our model actually provides the upper bound of the energy consumption.

**Replacing speed with period lengths and executions.** Fortunately, Theorem 2 provides us the basis to get rid of part of the variables. Since all nodes are executed at *constant* speeds within their scheduling windows, given the total length of each assigned segments (i.e., scheduling window), the execution speed of any given node can be determined. As a result, the energy consumption to finish this node can also be calculated. I.e., given a node  $\mathcal{N}_i^l$  with total execution requirement of  $c_i^l$ , to be executed on segments between  $b_i^l$  and  $f_i^l$ , we have:

$$\forall k \in [b_i^l, f_i^l], S_{\mathcal{M}_i^l}^k = c_i^l / (\sum_{j=b_i^l}^{f_i^l} t_j^j),$$

(3.6)

which means although a node may be executed in consecutive segments  $\forall k \in [b_i^l, f_i^l]$ , the speed remains constant throughout the scheduling window and can be represented by a function of executions  $c_i^l$  and segment lengths  $t_i^j$ . Substituting Equation (3.6) into the second term of the objective function, we have:

$$\sum_{l=1}^{\zeta_i} \sum_{k=b_i^l}^{f_i^l} t_i^k \alpha(S_{\mathcal{M}_i^l}^k)^{\gamma} = \sum_{l=1}^{\zeta_i} \left( \sum_{k=b_i^l}^{f_i^l} t_i^k \alpha(c_i^l)^{\gamma} (\sum_{j=b_i^l}^{f_i^l} t_j^j)^{-\gamma} \right)$$

{moving unrelated terms out of the summations}

$$= \alpha \sum_{l=1}^{\zeta_i} \left( (\sum_{j=b_i^l}^{f_i^l} t_i^j)^{-\gamma} (\sum_{k=b_i^l}^{f_i^l} t_i^k) (c_i^l)^{\gamma} \right)$$

{combining similar terms}

$$= \alpha \sum_{l \mid \mathcal{M}_i^l = j} c_l^{\gamma} (\sum_{k=b_i^l}^{f_i^l} t_i^k)^{1-\gamma}.$$

Thus, the original optimization problem can be equivalently transformed into the following one with only  $t_i^k$  as variables.

$$\begin{aligned} \mathbf{Minimize}_{\{t_i^k\}} \ M_i \beta T_i + \alpha \sum_{l \mid \mathcal{M}_i^l = j} c_l^{\gamma} (\sum_{k=b_i^l}^{f_i^l} t_i^k)^{1-\gamma} \\ \mathbf{Subject to} \quad \forall i, \sum_k t_i^k \leq T_i, \\ \forall i, t_i^k \geq 0. \end{aligned}$$

(3.8)

**Lemma 3.** The objective function (according to Equation (3.8)) is a convex function.

*Proof.* Since leakage power consumption remains constant (which is convex), we will prove that the dynamic part of the energy consumption function is convex:

$$E(\tau) = \sum_{1 \le i \le n} C_i^{\gamma} (\langle \alpha_i, \tau \rangle)^{1-\gamma}.$$

(3.9)

Here  $\tau$  refers to a k-dimension positive vector, in which each element is positive and refers to the length of a specific segment of a DAG task.  $\alpha_i$  is a binary vector, in which each element  $\alpha_{i,j} \in \{0,1\}$  identifies if the node is selected for the segment.  $|\alpha_i| \ge 1$  since at least one segment must be assigned).  $\langle \alpha_i, \tau \rangle$  refers to the inner-product of the two vectors,  $C_i$  refers to a nonnegative constant, and  $\gamma \in [2,3]$ . Thus the energy consumption is modeled as  $E(\tau)$  – a function over the time-allocation  $\tau \in \mathbb{R}^k_+$ .

We prove the convexity of  $E(\tau)$  when  $\tau \in \mathbb{R}^k_+$  with the following four steps:

- We name f(τ) =< α, τ > as a function of inner-product of τ with any binary vector α and |α| ≥ 1. Obviously, this function is a linear function over τ and should be both *convex* and *concave*. Further, given τ ∈ ℝ<sup>k</sup><sub>+</sub>, we have f(τ) > 0. Thus we can conclude f(τ) is a *positive concave* function.

- According to page 3-3 of [31], x<sup>p</sup> is convex when x > 0 and p ≤ 0. Thus, when γ ∈ [2,3]

(i.e., -2 ≤ 1 − γ ≤ −1) and x > 0, the function g(x) = x<sup>1−γ</sup> should be a non-increasing convex function.

- According to page 3-17 of [31], if g(x) is a non-increasing convex function and f(τ) is a concave function over ∀τ ∈ ℝ<sup>k</sup><sub>+</sub>, then g(f(τ)) is a convex function over ∀τ ∈ ℝ<sup>k</sup><sub>+</sub>.

- 4. The function  $E(\tau)$  and  $f_i(\tau)$  could be written as:

$$E(\tau) = \sum_{1 \le i \le n} C_i^{\gamma} g(f_i(\tau))$$

(3.10)

$$f_i(\tau) = (\langle \alpha_i, \tau \rangle) \tag{3.11}$$

As  $C_i^{\gamma}$  is non-negative,  $E(\tau)$  could be considered as the *non-negative-weighted sum* of convex functions (i.e.,  $g(f_i(\tau))$ ), and  $E(\tau)$  is a *convex function*.

**Theorem 4.** Any gradient based method (e.g., fmincon[56] in Matlab) would lead to sub-optimal power consumption under federated scheduling scheme with task decomposition.

*Proof.* The sub-optimality comes from three facts: