## **W&M ScholarWorks**

Dissertations, Theses, and Masters Projects

Theses, Dissertations, & Master Projects

Summer 2021

# Low-Overhead Techniques For Secure And Reliable Gpu Computing

Gurunath Kadam William & Mary - Arts & Sciences, gurunath.kadam@gmail.com

Follow this and additional works at: https://scholarworks.wm.edu/etd

Part of the Computer Sciences Commons

#### **Recommended Citation**

Kadam, Gurunath, "Low-Overhead Techniques For Secure And Reliable Gpu Computing" (2021). Dissertations, Theses, and Masters Projects. Paper 1627047873. http://dx.doi.org/10.21220/s2-jvrg-8s06

This Dissertation is brought to you for free and open access by the Theses, Dissertations, & Master Projects at W&M ScholarWorks. It has been accepted for inclusion in Dissertations, Theses, and Masters Projects by an authorized administrator of W&M ScholarWorks. For more information, please contact scholarworks@wm.edu.

## Low-Overhead Techniques for Secure and Reliable GPU Computing

#### Gurunath Kadam

Mumbai, India

Bachelor of Engineering, University of Mumbai, 2006 Master of Science, Technical University of Darmstadt, 2012

A Dissertation presented to the Graduate Faculty of The College of William & Mary in Candidacy for the Degree of Doctor of Philosophy

Department of Computer Science

College of William & Mary May 2021

#### APPROVAL PAGE

This Dissertation is submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Gurunath Kadam

Approved by the Committee, May 2021

Adwait fog

Committee Chair

Adwait Jog, Assistant Professor, Computer Science

College of William & Mary

Inter.

Dmitry Evtyushkin, Assistant Professor, Computer Science College of William & Mary

Bin Ren

Bin Ren, Assistant Professor, Computer Science College of William & Mary

diff

Evgenia Smirni, Professor, Computer Science College of William & Mary

Achitosh Posthach

Ashutosh Pattnaik, Senior GPU Architect ARM Ltd.

#### ABSTRACT

In recent years, Graphics Processing Units (GPUs) have become a de facto choice to accelerate the computations in various domains such as machine learning, security, financial and scientific computing. GPUs leverage the inherent data parallelism in the target applications to provide high throughput at superior energy efficiency. Due to the rising usage of GPUs for a large number of applications, they are facing new challenges, especially in the security and reliability domains. From the security side, recently several microarchitectural attacks targeting GPUs have been demonstrated. These attacks leak the secret information stored on GPUs, for example, the parameters of a neural network (NN) model and the private user information. From the reliability side, the innovations to improve GPU memory systems are making them more susceptible to errors. My dissertation research focuses on addressing these security and reliability challenges in GPUs while minimizing the associated overhead of the proposed protection mechanisms.

To improve GPU security, we focus on the previously demonstrated correlation timing attack. Such an attack exploits the deterministic nature of the coalescing mechanism in GPUs to correlate the execution time and the number of accesses. Consequently, an attacker can recover the encryption keys stored on GPUs. Therefore, to counter the correlation timing attack, we first introduce a randomized coalescing defense scheme (RCoal). RCoal randomizes the coalescing logic such that the attacker fails to correlate the execution time and the number of accesses. As a result, RCoal thwarts the correlation timing attack. Next, we propose a bucketing based coalescing defense scheme, BCoal, which minimizes the variation in the number of memory accesses by generating a predetermined number (called buckets) of memory accesses. With low variation in the number of memory accesses, the attacker cannot correlate the application execution time and the secret information, thus failing the correlation timing attack. BCoal generates less memory traffic than RCoal and, therefore, is performance efficient.

To improve GPU reliability, we address the data memory faults in GPU caches and DRAM. Existing reliability mechanisms of redundancy and check-pointing fail to scale with the increasing memory/computational demands on GPUs and quickly become impractical. To address this problem, we study a wide range of applications to find that a very small fraction of the data memory is most vulnerable to faults. This small fraction of the data is not only highly accessed but also highly shared across GPU threads. Consequently, we propose and develop two reliability schemes to detect-only and to detect/correct faults in this most vulnerable data while incurring low overhead. The focus of on-going and future work is to improve the reliability of machine learning applications.

## TABLE OF CONTENTS

| $egin{array}{c} 	ext{Acknowledgments} \ 	ext{} \end{array}$     | vi   |

|-----------------------------------------------------------------|------|

| Dedication                                                      | vii  |

| List of Tables v                                                | riii |

| List of Figures                                                 | ix   |

| 1 Introduction                                                  | 2    |

| 1.1 Low-Overhead Hardware Techniques for Improving GPU Security | 3    |

| 1.1.1 Problem Statement                                         | 3    |

| 1.1.2 Contributions                                             | 4    |

| 1.2 Low-Overhead Hardware Techniques for Reliable GPU Computing | 5    |

| 1.2.1 Problem Statement                                         | 5    |

| 1.2.2 Contributions                                             | 5    |

| 1.3 Dissertation Organization                                   | 7    |

| 2 A General Background on Graphics Processing Units (GPUs)      | 8    |

| 2.1 Baseline GPU Architecture                                   | 8    |

| 2.2 GPU Memory Access Optimization Techniques                   | 9    |

| 2.3 Data Memory Faults in GPUs                                  | 11   |

| 2.3.1 Data Memory Faults and Their Impact in GPUs               | 11   |

| 2.3.2 Importance of Data Memory Faults in GPUs                  | 12   |

| 3 | RCc | oal: Mitigating GPU Timing Attack via Subwarp-based Randomized  |    |

|---|-----|-----------------------------------------------------------------|----|

|   | Coa | lescing Techniques                                              | 13 |

|   | 3.1 | Introduction                                                    | 13 |

|   | 3.2 | Background                                                      | 16 |

|   |     | 3.2.1 Baseline GPU Architecture                                 | 16 |

|   |     | 3.2.2 AES Encryption                                            | 18 |

|   |     | 3.2.3 Baseline Timing Attack                                    | 20 |

|   | 3.3 | Motivation and Goals                                            | 22 |

|   | 3.4 | Subwarp based Defense Mechanisms                                | 25 |

|   |     | 3.4.1 Fixed-sized Subwarps (FSS)                                | 25 |

|   |     | 3.4.2 Random-sized Subwarp (RSS)                                | 28 |

|   |     | 3.4.3 Random-threaded Subwarp (RTS)                             | 29 |

|   |     | 3.4.4 Implementation Details                                    | 30 |

|   |     | 3.4.5 Corresponding Attacks                                     | 31 |

|   | 3.5 | Theoretical Security Analysis                                   | 32 |

|   |     | 3.5.1 Analytical Model                                          | 32 |

|   |     | 3.5.2 Analysis of Defense Mechanisms                            | 33 |

|   |     | 3.5.2.1 FSS                                                     | 35 |

|   |     | 3.5.2.2 FSS+RTS                                                 | 35 |

|   |     | 3.5.2.3 RSS+RTS                                                 | 36 |

|   |     | 3.5.3 Results                                                   | 36 |

|   | 3.6 | Experimental Analysis of Security and Performance               | 37 |

|   |     | 3.6.1 Effect on Security                                        | 38 |

|   |     | 3.6.2 Effect on Performance and Data Movement                   | 42 |

|   |     | 3.6.3 Evaluating the Trade-off Between Security and Performance | 43 |

|   |     | 3.6.4 Case Study: Plaintext with 1024 Lines                     | 43 |

|   | 3 7 | Discussion and Future Work                                      | 15 |

|   | 3.8 | Related Work                                                         | 45 |

|---|-----|----------------------------------------------------------------------|----|

|   | 3.9 | Conclusions                                                          | 46 |

| 4 | ВСо | oal: Bucketing-based Memory Coalescing for Efficient and Secure GPUs | 48 |

|   | 4.1 | Introduction                                                         | 48 |

|   | 4.2 | Background                                                           | 51 |

|   |     | 4.2.1 Basics of GPU Architecture                                     | 51 |

|   |     | 4.2.2 Bandwidth Conserving Mechanisms                                | 52 |

|   |     | 4.2.3 AES Encryption                                                 | 54 |

|   |     | 4.2.4 Baseline Attack and Defense Mechanism                          | 55 |

|   | 4.3 | Motivation and Analysis                                              | 58 |

|   |     | 4.3.1 Performance Overhead Analysis of RCoal                         | 58 |

|   |     | 4.3.2 Effect of MSHRs and Caches on Security with RCoal              | 60 |

|   |     | 4.3.3 Our Proposal and Goals                                         | 62 |

|   | 4.4 | Anatomy of Bucketing in GPUs                                         | 62 |

|   |     | 4.4.1 Bucket Features                                                | 63 |

|   |     | 4.4.2 Estimation of Number of Padded Accesses                        | 64 |

|   |     | 4.4.3 Design Challenges in Generating Padded Accesses                | 64 |

|   |     | 4.4.4 BCoal: A Secure Bucketing Scheme                               | 66 |

|   | 4.5 | Hardware/Software Overhead                                           | 67 |

|   | 4.6 | Analysis of Security & Performance                                   | 68 |

|   |     | 4.6.1 Experimental Analysis of Security                              | 69 |

|   |     | 4.6.2 Theoretical Analysis of Security                               | 71 |

|   |     | 4.6.3 Experimental Analysis of Performance                           | 74 |

|   |     | 4.6.4 Evaluating BCoal on Other Applications                         | 74 |

|   | 4.7 | Related Work                                                         | 77 |

|   | 4.8 | Conclusions                                                          | 78 |

| 5 | Dat | a-centric Reliability Management in GPUs                         | 80  |

|---|-----|------------------------------------------------------------------|-----|

|   | 5.1 | Introduction                                                     | 80  |

|   | 5.2 | Background                                                       | 82  |

|   |     | 5.2.1 Baseline GPU Architecture                                  | 82  |

|   |     | 5.2.2 Data Memory Faults in GPUs                                 | 84  |

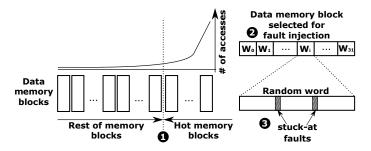

|   |     | 5.2.3 Fault Injection Setup                                      | 84  |

|   |     | 5.2.3.1 Fault Model                                              | 84  |

|   |     | 5.2.3.2 Error Metric Selection                                   | 85  |

|   | 5.3 | Motivation and Workload Analysis                                 | 86  |

|   |     | 5.3.1 Problem Definition and Goals of This Work                  | 86  |

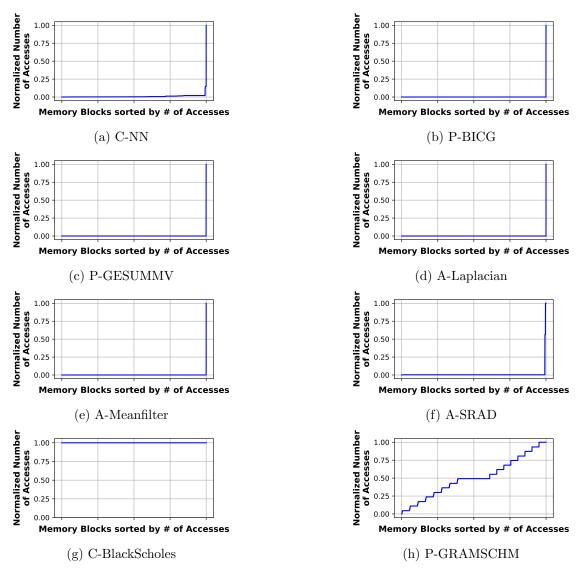

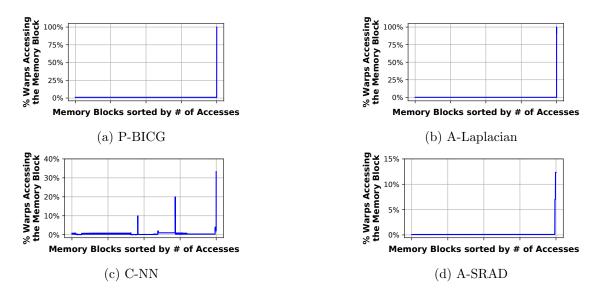

|   |     | 5.3.2 Application Access Pattern Analysis                        | 89  |

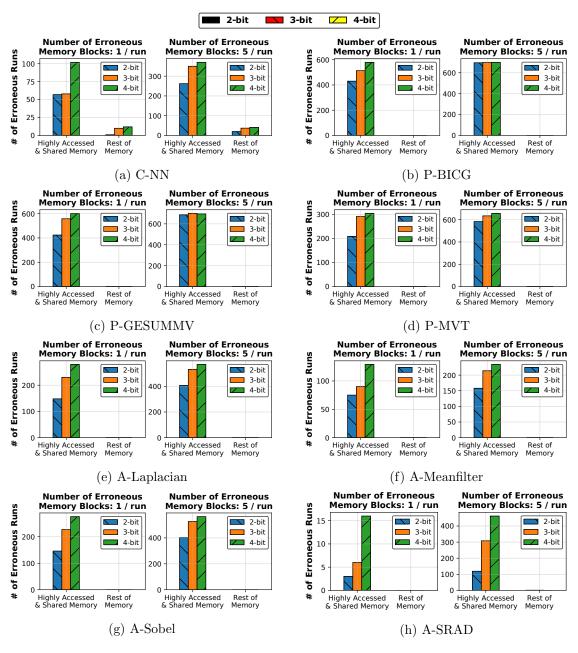

|   |     | 5.3.3 Impact of Faults in Data Memory                            | 91  |

|   | 5.4 | Data-centric Reliablity Management: Analysis, Design, and Imple- |     |

|   |     | mentation                                                        | 93  |

|   |     | 5.4.1 Application Source Code Analysis                           | 93  |

|   |     | 5.4.2 Detection and Correction Resilience Schemes                | 98  |

|   |     | 5.4.2.1 Multi-bit Fault Detection                                | 98  |

|   |     | 5.4.2.2 Multi-bit Fault Detection-and-Correction                 | 99  |

|   |     | 5.4.3 Implementation Overhead                                    | 100 |

|   | 5.5 | Experimental Results                                             | 101 |

|   |     | 5.5.1 Performance Evaluation                                     | 101 |

|   |     | 5.5.1.1 Detection-Only                                           | 101 |

|   |     | 5.5.1.2 Detection-and-Correction                                 | 103 |

|   |     | 5.5.2 Reliability Evaluation                                     | 103 |

|   |     | 5.5.3 Reliability and Performance Tradeoff                       | 106 |

|   | 5.6 | Related Works                                                    | 106 |

|   | 5.7 | Conclusions                                                      | 108 |

| 6 Exp   | loration of the Reliability of ML Models        | 110   |

|---------|-------------------------------------------------|-------|

| 6.1     | Advantages of Weight Quantization in ML Models  | . 110 |

| 6.2     | Impact of Memory Faults on the Quantized Models | . 111 |

|         | 6.2.1 Fault Model                               | . 111 |

|         | 6.2.2 Impact of Memory Faults                   | . 111 |

| 7 Con   | clusion and Future Research Directions          | 115   |

| 7.1     | Summary of Dissertation Contributions           | . 115 |

| 7.2     | Future Research Directions                      | . 117 |

| Bibliog | raphy                                           | 118   |

| Vita    |                                                 | 138   |

|         |                                                 |       |

#### ACKNOWLEDGMENTS

The following thesis and research are the culmination of guidance, encouragement, and moral support from many people throughout my graduate studies. First, I sincerely thank my advisor, Adwait Jog, for his thoughtful, patient, and diligent mentoring. Adwait taught me not only how to conduct successful research, but also how to overcome failures. He ensured that as a graduate student I maintained a work-life balance. I hope to carry these lessons with me in future work.

During my PhD, I was fortunate to collaborate with Danfeng Zhang and Evgenia Smirni. Danfeng and Evgenia have broadened my knowledge in their respective domains. I thank them for their guidance, support, and time.

I extend my gratitude to my dissertation committee members, Bin Ren, Dmitry Evtyushkin, Evgenia Smirni, and Ashutosh Pattnaik. Their generous support and attentive feedback improved this dissertation.

I thank Carlos Rozas for giving me an opportunity to intern at Intel Labs. Patrick Koeberl and Andrea Miele introduced me to new challenges in FPGA security and made my time at Intel a great learning experience.

I thank the College of William & Mary for supporting my graduate studies through a fellowship and for allowing me to conduct research through the College computing facilities. I thank Eric Walter, Laura Hild, and Jay Kanukurthy for their assistance in using the computing facilities. I also thank the Computer Science administrative staff – Vanessa Godwin, Jacqulyn Johson, and Dale Hayes – for their help to speedily resolve any administrative issues.

My time at William & Mary has been truly memorable thanks to my labmates Haonan Wang, Mohamed Ibrahim, and Hongyuan Liu. Haonan, Mohamed, and Hongyuan offered invaluable help and companionship throughout my Ph.D. life.

Finally, I would like to thank my wife, Mary Elizabeth, who firmly supported me through my graduate course work, submission deadlines, conference travels, and research. I thank all my family members for their care and encouragement without which I would not be what I am today.

To my parents.

## LIST OF TABLES

| 3.1 K            | Key configuration parameters of the simulated GPU configuration. ©   |     |

|------------------|----------------------------------------------------------------------|-----|

| 2                | 2018 IEEE                                                            | 16  |

| 3.2  S           | Security analysis results with $N=32$ and $R=16$ , where N is the    |     |

| n                | number of threads and $R$ is the number of memory blocks. Here, $M$  |     |

|                  |                                                                      |     |

| is               | s the number of subwarps and $S$ is the number of samples normalized |     |

| t                | o FSS with $M=1$ case. © 2018 IEEE                                   | 36  |

|                  | Key configuration parameters of the simulated GPU. © 2020 IEEE       | 52  |

| $4.2 \mathrm{S}$ | Security Analysis. $S$ denotes the normalized number of samples re-  |     |

|                  | · 1.                                                                 |     |

| q                | quired to successfully recover an AES key byte 49. © 2020 IEEE.      |     |

|                  |                                                                      | 73  |

| 5.1 K            | Key configuration parameters of the simulated GPU. © 2021 IEEE       | 83  |

| 5.2 (            | Output Error Metrics for Applications. © 2021 IEEE                   | 86  |

| 5.3 I            | nput data objects to the GPU applications. Data objects are sorted   |     |

| 0.0 1            | input data objects to the GFO applications. Data objects are sorted  |     |

| b                | pased on the number of accesses incurred (Highest to Lowest). The    |     |

|                  | , ,                                                                  |     |

| е                | emboldened data objects are classified as hot data objects (highly   |     |

| a                | accessed and shared). © 2021 IEEE.                                   | 97  |

| C 1 C            |                                                                      |     |

| 6.1              | Comparison between 32-bit floating-point and weight quantized        |     |

|                  | INT8) ML models.                                                     | 111 |

|                  |                                                                      |     |

# LIST OF FIGURES

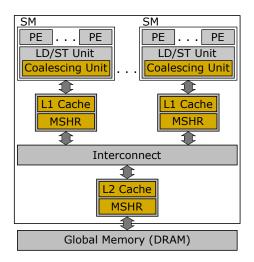

| 2.1 | Overview of GPU Architecture.                                                      | 9  |

|-----|------------------------------------------------------------------------------------|----|

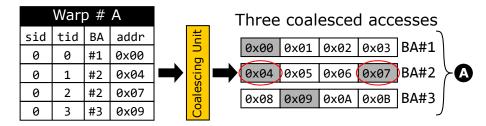

| 2.2 | Memory access coalescing in GPUs. © 2018 IEEE                                      | 10 |

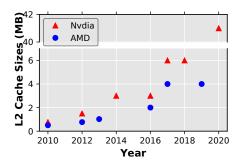

| 2.3 | L2 Cache size trend for Nvidia and AMD GPUs                                        | 12 |

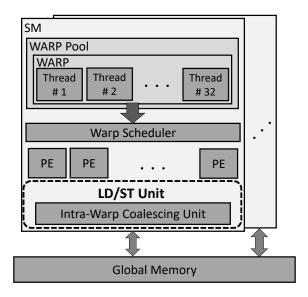

| 3.1 | Overview of Baseline GPU Architecture. © 2018 IEEE.                                | 17 |

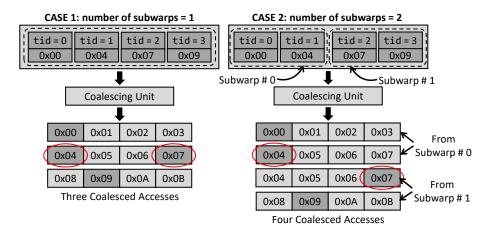

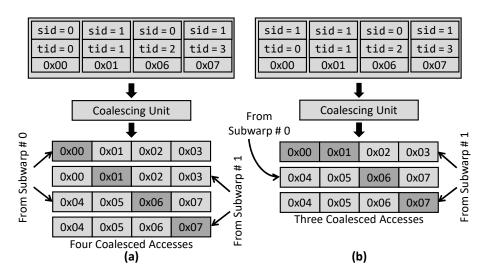

| 3.2 | Effect of subwarps on memory coalescing. © 2018 IEEE                               | 19 |

| 3.3 | Last round execution of AES-128 algorithm. The $t_i$ in $T4[t_i]$ represents       |    |

|     | the index of the table lookup operation. $k_j$ and $c_j$ represent the jth         |    |

|     | byte of the last round key and ciphertext, respectively. tid is the                |    |

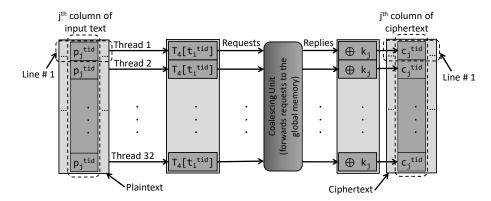

|     | thread id within a warp. © 2018 IEEE.                                              | 20 |

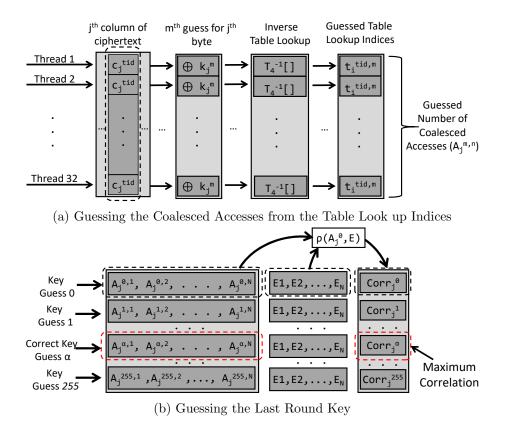

| 3.4 | Overview of the process of guessing one of the correct last round key              |    |

|     | byte $(k_j)$ . $A_j^{m,n}$ is the number of memory requests for $m^{th}$ guess of  |    |

|     | the $j^{th}$ last round key byte using $n^{th}$ plaintext. $n$ varies between 1 to |    |

|     | N, where $N$ is the number of plaintext samples. $m$ varies from 0 to              |    |

|     | 255 and $j$ varies from 1 to 16. © 2018 IEEE                                       | 21 |

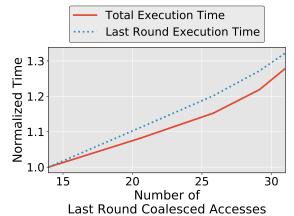

| 3.5 | Relationship between Last Round and Total Execution Time. © 2018                   |    |

|     | IEEE.                                                                              | 22 |

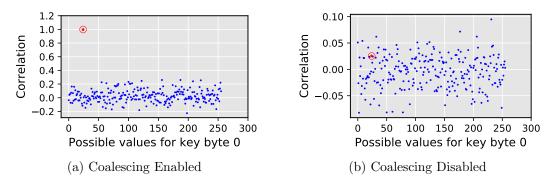

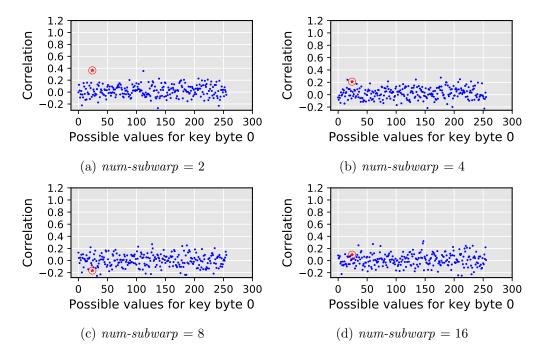

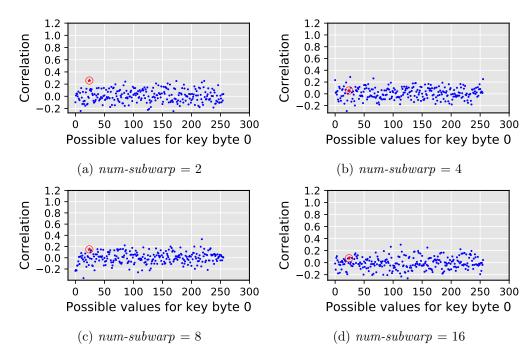

| 3.6 | Effect of Coalescing on the Recovery of $0^{th}$ Last Round Key Byte $(k_0)$ :     |    |

|     | a) Recovery is Successful when Coalescing is Enabled, b) Recovery is               |    |

|     | Unsuccessful when Coalescing is Disabled. © 2018 IEEE                              | 23 |

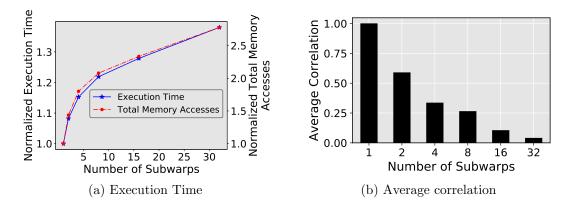

| 3.7 Performance of FSS enabled AES with respect to number of subwarps:     |    |

|----------------------------------------------------------------------------|----|

| a) Execution Time and Total Memory Accesses per plaintext with             |    |

| increasing number of subwarps, b) Average of correlations between          |    |

| the last round execution time and the last round memory accesses for       |    |

| all key bytes. The last round memory accesses are calculated assuming      |    |

| correct values of a key byte and the number of subwarps for coalescing     |    |

| to be one. © 2018 IEEE                                                     | 26 |

| 3.8 Fixed Size Subwarp (FSS) mechanism against FSS attack. © 2018          |    |

| <u>IEEE.</u>                                                               | 28 |

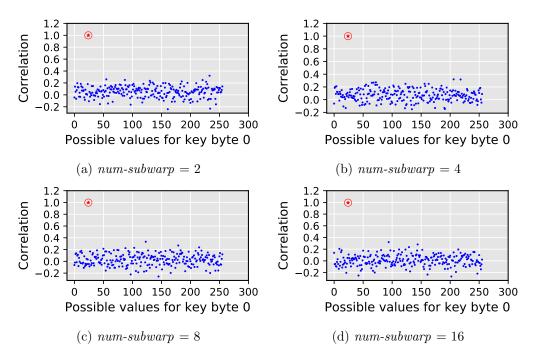

| 3.9 Subwarp size distribution of RSS for $num$ -subwarp = 4. © 2018 IEEE.  | 29 |

| 3.10 Effects of different defense mechanisms on coalescing for num-subwarp |    |

| = 2: a) FSS+RTS and b) RSS+RTS. sid represents subwarp id and              |    |

| tid represents thread id. © 2018 IEEE                                      | 30 |

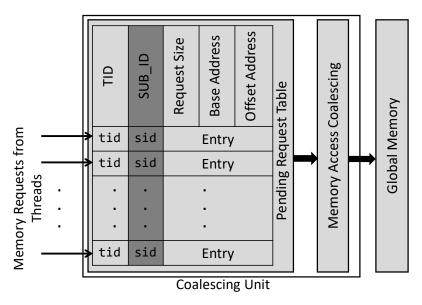

| 3.11 Modified Coalescing Unit to realize FSS, RSS, and RTS defense         |    |

| mechanisms. The additional hardware required is the field to store         |    |

| subwarp-id $(sid)$ for each thread. © 2018 IEEE                            | 32 |

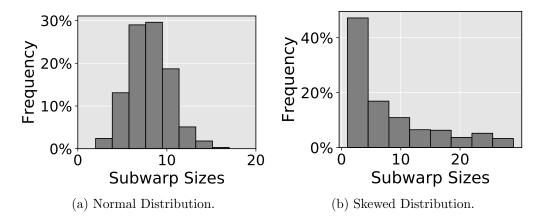

| 3.12 FSS+RTS defense mechanism against FSS+RTS attack. © 2018 IEEE.        | 39 |

| 3.13 RSS defense mechanism against RSS attack.                             | 40 |

| 3.14 RSS+RTS defense mechanism against RSS+RTS attack. © 2018 IEEE.        | 40 |

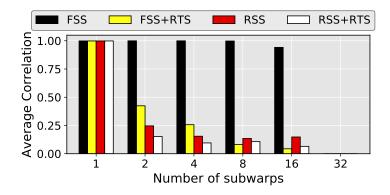

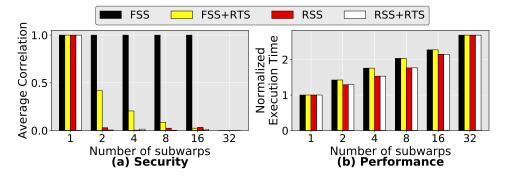

| 3.15 Comparison between the security offered by FSS, FSS+RTS, RSS and      |    |

| RSS+RTS based on the average of correlations between the last round        |    |

| coalesced accesses for all key bytes and the last round execution time     |    |

| observed during the encryption. The last round coalesced accesses are      |    |

| calculated using the <u>corresponding attacks</u> . © 2018 IEEE            | 41 |

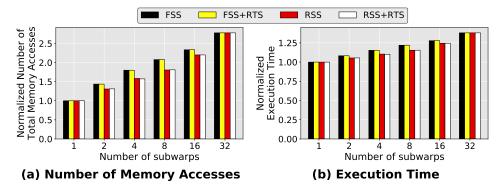

| 3.16 Performance and Data Movement Comparisons between FSS,                |    |

| FSS+RTS, RSS, and RSS+RTS. © 2018 IEEE.                                    | 42 |

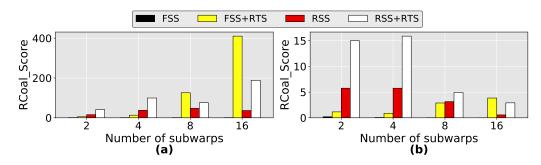

| 3.17 C | Comparison between the FSS, FSS+RTS, RSS and RSS+RTS                    |    |

|--------|-------------------------------------------------------------------------|----|

| d      | lefense mechanisms based on the RCoal score against the                 |    |

| C      | for or responding attacks: a) Security-oriented system with $a = 1$ and |    |

| _      |                                                                         |    |

| Ь      | p = 1, b) Performance-oriented system with $a = 1$ and $b = 20$ .       |    |

| 2      | 2018 IEEE                                                               | 43 |

| 3.18 E | Effects of the defense mechanisms on security against the correspond-   |    |

| ir     | ng attacks and performance with respect to the number of subwarps       |    |

| fo     | or plaintext with 1024 lines: a) Average of correlations between the    |    |

| la     | ast round coalesced accesses from the attack and the execution for      |    |

| a      | all key bytes, b) Execution time (normalized to the case when num-      |    |

| s      | ubwarp=1) with respect to the number of subwarps. © 2018 IEEE.          | 44 |

|        | <u> </u>                                                                |    |

| 4.1 C  | Overview of Baseline GPU Architecture. © 2020 IEEE                      | 52 |

| 4.2 N  | Memory access coalescing in GPUs. © 2020 IEEE                           | 53 |

| 4.3 B  | Baseline Attack. © 2020 IEEE                                            | 56 |

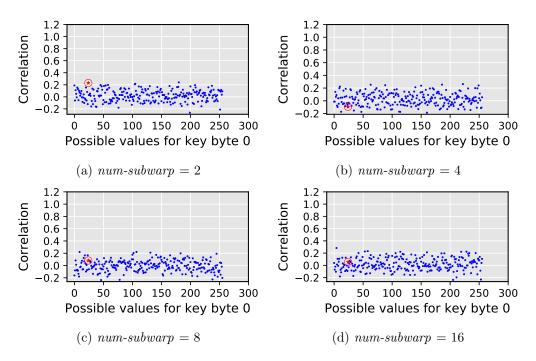

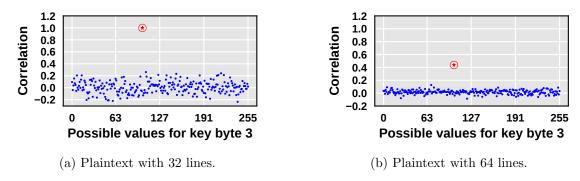

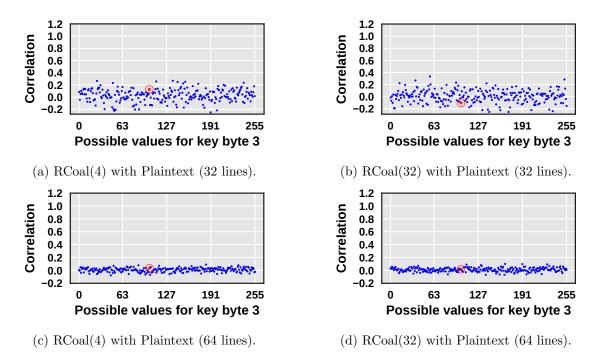

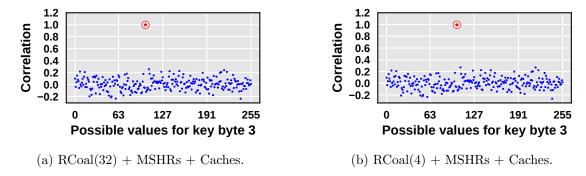

| 4.4 E  | Effect of different RCoal coalescing schemes on the recovery of one of  |    |

| t]     | he last round key byte (shown in red circle). In RCoal, the caches      |    |

| a      | and MSHRs are disabled for security reasons (refer Section 4.3-B). ©    |    |

| 2      | 020 IEEE                                                                | 57 |

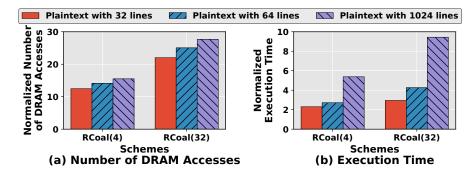

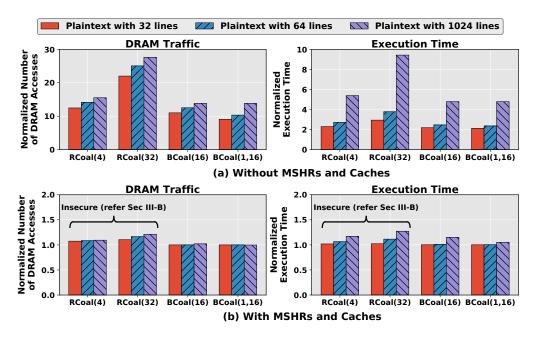

| 4.5 I  | llustrating the overhead of RCoal defense scheme for different sizes of |    |

| р      | plaintext. The results are normalized to a baseline GPU with MSHRs      |    |

| a      | and caches. © 2020 IEEE                                                 | 58 |

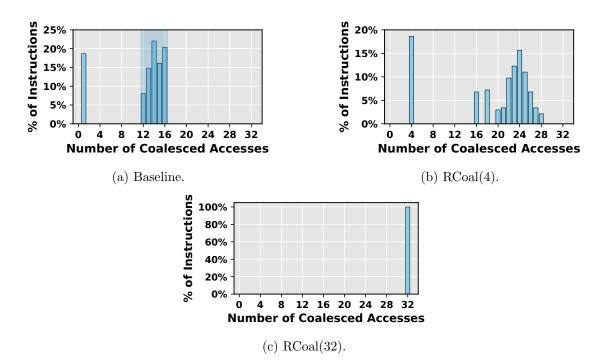

| 4.6 H  | Histogram of the number of coalesced accesses generated across a warp   |    |

| fo     | or 1000 plaintext samples each with 32 lines. © 2020 IEEE               | 59 |

| 4.7 E  | Effect of MSHRs on the cache-missed coalesced accesses in RCoal         |    |

| St     | cheme. (c) 2020 IEEE.                                                   | 61 |

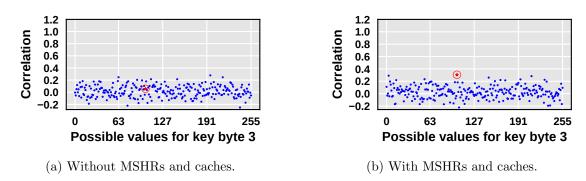

| 4.8 Th                                        | ne presence of MSHRs and caches leads to successful recovery of one  |                |

|-----------------------------------------------|----------------------------------------------------------------------|----------------|

| of                                            | the last round key bytes in RCoal(32) and RCoal(4). Plaintext has    |                |

| 32                                            | lines. © 2020 IEEE                                                   | 61             |

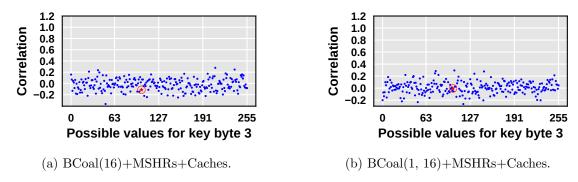

| 4.9 Ev                                        | valuation of security offered by the bucketing scheme employing      |                |

| un                                            | ique access padding mechanisms with one bucket of size 16. Plain-    |                |

| tex                                           | xt has 32 lines. © 2020 IEEE                                         | 65             |

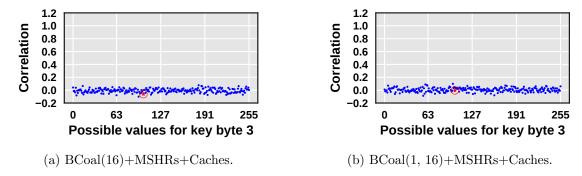

| 4.10 BC                                       | Coal defense scheme against correlation attack for plaintext with 32 |                |

| lin                                           | es. © 2020 IEEE.                                                     | 69             |

| 4.11 BC                                       | Coal defense scheme against correlation attack for plaintext with 64 |                |

| lin                                           | es. © 2020 IEEE.                                                     | 70             |

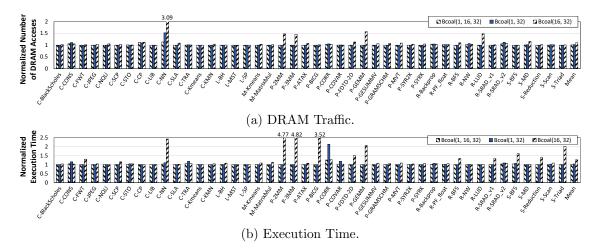

| 4.12 Pe                                       | erformance of BCoal for different plaintext sizes. All results are   |                |

| no                                            | rmalized to the baseline GPU. © 2020 IEEE.                           | 75             |

| 4.13 Pe                                       | erformance Evaluation of BCoal on GPGPU applications with            |                |

| M                                             |                                                                      |                |

| IVI                                           | SHRs/caches enabled. Results are normalized to the baseline GPU.     |                |

|                                               |                                                                      | 76             |

| (c)                                           | 2020 IEEE                                                            | 76<br>83       |

| 5.1 A                                         | 2020 IEEE                                                            | 83             |

| 5.1 A<br>5.2 L2                               | 2020 IEEE                                                            | 83             |

| 5.1 A<br>5.2 L2<br>5.3 No                     | 2020 IEEE                                                            | 83             |

| 5.1 A 5.2 L2 5.3 No                           | 2020 IEEE                                                            | 83             |

| 5.1 A 5.2 L2 5.3 No                           | 2020 IEEE                                                            | 83<br>87       |

| 5.1 A 5.2 L2 5.3 No we of 5.4 Pe              | Schematic of the Baseline GPU Architecture. © 2021 IEEE              | 83<br>87       |

| 5.1 A 5.2 L2 5.3 No we of 5.4 Pe              | Schematic of the Baseline GPU Architecture. © 2021 IEEE              | 83<br>87<br>88 |

| 5.1 A 5.2 L2 5.3 No we of 5.4 Pe 5.5 Fa       | Schematic of the Baseline GPU Architecture. © 2021 IEEE              | 83<br>87<br>88 |

| 5.1 A 5.2 L2 5.3 No we of 5.4 Pe IE 5.5 Fa ho | Schematic of the Baseline GPU Architecture. © 2021 IEEE              | 83<br>87<br>88 |

| 5.6 H | Effect of faults in the hot (highly accessed/shared) memory blocks         |     |

|-------|----------------------------------------------------------------------------|-----|

| V     | versus the rest of the memory blocks on the application output. ©          |     |

| 2     | 2021 IEEE                                                                  | 92  |

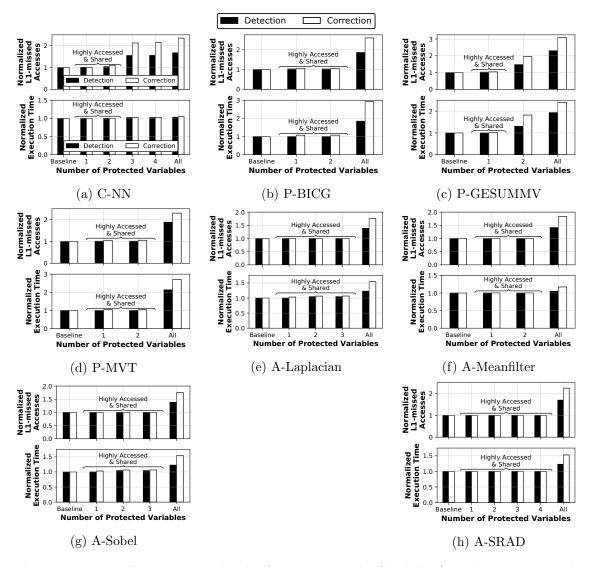

| 5.7 H | Performance overhead of Detection-only (dark bar) and Detection-           |     |

| 8     | and-Correction (white bar) resilience schemes. All numbers are nor-        |     |

| r     | malized to the baseline case (no reliability protection, 1.0). The hot     |     |

| C     | data objects reside in hot memory blocks. © 2021 IEEE                      | 102 |

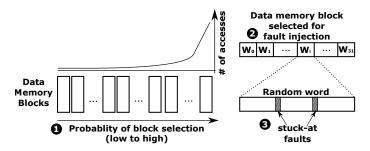

| 5.8 H | Fault injection for evaluating fault detection-and-correction: the prob-   |     |

| а     | ability of a memory block selection depends on the number of its           |     |

| I     | L1-missed accesses (since the proposed schemes address faults in L2-       |     |

| C     | caches and DRAM). © 2021 IEEE.                                             | 104 |

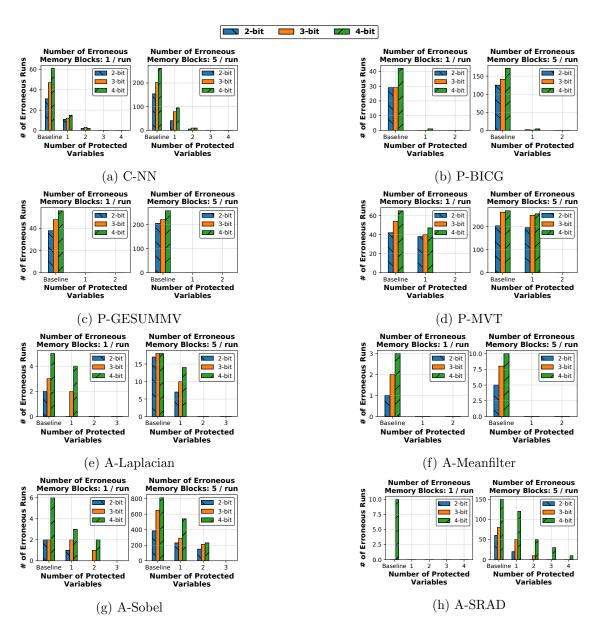

| 5.9 S | Silent data corruption due to faults in L2-cache and DRAM: The             |     |

| X     | x-axis represents the number of protected data objects cumulatively        |     |

| i     | increasing, starting from the baseline case (no data objects are pro-      |     |

| t     | tected). The y-axis shows the number of SDC outputs out of 1000 runs       |     |

| f     | for each error injection configuration. The detection-only/dectection-     |     |

| 8     | and-correction schemes stop the multi-bit data memory errors caused        |     |

| 1     | by the faults from propagating to the output. © 2021 IEEE                  | 105 |

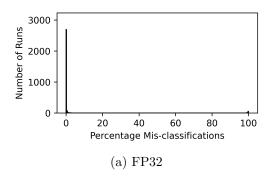

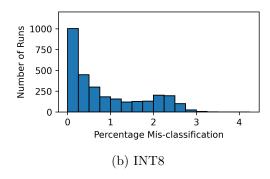

| 6.1 I | Impact of faults in a weight element on the classification accuracy in     |     |

| I     | FP32 and quantized (INT8) AlexNet model                                    | 112 |

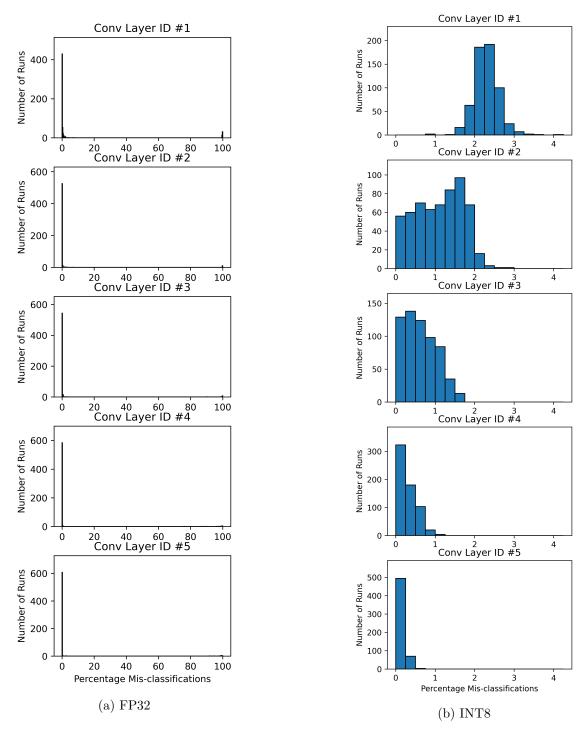

| 6.2 ( | Contribution of faults in weights of different convolution layers of float |     |

| 3     | 32 (FP32) and quantized (INT8) ML models on the classification ac-         |     |

| C     | curacy.                                                                    | 113 |

## Chapter 1

## Introduction

Graphics Processing Units (GPUs) provide significant performance and energy efficiency advantages over CPUs as the former exploits the data-level parallelism in the applications [60, 5, 69, 118, 59, 61, 106, 3, 2, 12, 54, 122]. As a result, GPUs are largely deployed to accelerate applications in various fields, such as high-performance computing (HPC), artificial intelligence (AI), finance, virtual/augmented reality, genomics, and autonomous vehicle workloads [23, 109, 122, 93, 116, 98, 91, 96, 103, 94].

With the increasing demand for GPUs in the computational and graphical workloads, the challenges faced by the GPU architecture are also increasing, especially in the security and reliability domains. For example, some of the GPU-run applications, such as DNA and financial computing, process private user data. Furthermore, while the deep learning workloads benefit from the computational power of GPUs, the neural network (NN) models are under attack to steal the confidential model parameters and the private user data processed on the GPUs [37, 81]. Also, cryptographic applications, such as AES encryption handling sensitive data, are known to achieve significant performance benefits

IEEE Copyright Note: In reference to IEEE copyrighted material which is used with permission in this thesis, the IEEE does not endorse any of the College of William and Mary's products or services. Internal or personal use of this material is permitted. If interested in reprinting/republishing IEEE copyrighted material for advertising or promotional purposes or for creating new collective works for resale or redistribution, please go to <a href="http://www.ieee.org/publications\_standards/publications/rights/rights\_link.html">http://www.ieee.org/publications\_standards/publications/rights/rights\_link.html</a> to learn how to obtain a License from RightsLink. If applicable, University Microfilms and/or ProQuest Library, or the Archives of Canada may supply single copies of the dissertation.

from GPUs [44, 128, 72, 17, 83, 42]. As a result, the secure computations on GPUs are a primary focus to ensure that the confidential and private data processed is not leaked by an attacker.

Next, emerging computing needs have fueled the growth of GPU architectures. Specifically, the growing data sizes in the deep learning and AI workloads have lead to a significant increase in the GPU storage structures [99]. Consequently, several research efforts have been made to operate these storage structures efficiently. However, the effect of these innovations on GPU reliability is not yet well-understood. For example, low voltage cache designs (i.e., AMD Killi [27] or IBM Dante [11]) for managing power consumption of large last-level caches in GPUs can increase the likelihood of multi-bit faults. Furthermore, advanced DRAM architectures make multi-bit faults more common [120], [125]. The increasing multi-bit faults in the GPU memory structures may adversely affect the output of the applications leading to less reliable GPU computations. The reduced reliable GPU computations, in turn, may lead to catastrophic failures, such as accidents of autonomous vehicles [105], [16], [15], [15], [15], [15], [16], [16], [17], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18], [18],

# 1.1 Low-Overhead Hardware Techniques for Improving GPU Security

#### 1.1.1 Problem Statement

As noted above, GPUs outperform CPUs in terms of performance and power efficiency when executing cryptographic applications, such as AES encryption [42, 72, 17, 83]. However, several new correlation timing and covert channel attacks have been demonstrated on GPUs to leak confidential and private user data [44, 80, 135, 45]. Our research focuses on the recent correlation timing attack on GPU, which exploited the correlation between the execution time and the number of coalesced accesses to memory to recover the AES

encryption keys [44]. Specifically, the attacker exploits the relationship between the coalesced accesses and AES encryption keys to reveal the encryption key through an offline correlation analysis with the help of the recorded encryption execution time and encrypted (cipher-) text.

#### 1.1.2 Contributions

We introduce two hardware-based defense mechanisms for GPUs to mitigate the correlation timing attack and prevent the leakage of security-sensitive data. The first defense mechanism, RCoal, randomizes the memory access coalescing mechanism to generate additional accesses to thwart the correlation timing attack [49]. For the second defense mechanism, we propose a bucketing-based coalescing mechanism, BCoal [50]. BCoal generates additional memory accesses whenever necessary to match the total number of accesses to a set of pre-determined numbers (called buckets). Consequently, BCoal reduces the correlation between the number of accesses and private data to mitigate the correlation timing attack. Furthermore, since BCoal generates fewer memory accesses compared to RCoal, BCoal proves to be a performance efficient defense mechanism.

Our research on secure GPU computing through hardware techniques makes the following contribution:

- We analyze the correlation timing attack on GPUs to show that the regularity and deterministic nature of the memory access coalescing is a major security vulnerability.

- We propose two novel hardware-based defense mechanisms to mitigate the correlation timing attack leveraging the memory access coalescing. The first defense mechanism, RCoal, randomizes the memory coalescing logic to eliminate the relationship between the number of memory accesses and the execution time to thwart the correlation timing attack.

- Our second defense mechanism, BCoal, implements a bucketing-based coalescing mechanism to always issue pre-determined numbers (chosen from a small set, called buckets) of coalesced accesses by padding additional accesses to the real accesses whenever necessary. As a result, the correlation between the number of accesses and the execution

time reduces thus mitigating the correlation timing attack.

- We demonstrate through the theoretical and empirical analysis that both of our defense mechanisms offer improved security against the correlation timing attack at a low performance overhead. Furthermore, both defense mechanisms offer a tradeoff between the security and performance that can be set by a user.

- We show that both, RCoal and BCoal, defense mechanisms incur a very low hardware overhead.

# 1.2 Low-Overhead Hardware Techniques for Reliable GPU Computing

#### 1.2.1 Problem Statement

The current generation of GPUs employs an error checking and correction (ECC) mechanism called single error correction and double error detection (SECDED) to detect and correct the data memory faults [58]. SECDED-ECC corrects single-bit fault and detects up to two-bit faults. However, as noted earlier, with the growing error rate in the GPU memory structures, the number of multi-bit (more than 2-bits) faults is increasing [120, 125, 27, 11]. SECDED-ECC is not capable of addressing these rising multi-bit faults and, therefore, the GPU output reliability cannot be guaranteed. A stronger ECC, such as Chipkill, can address the multi-bit faults. However, Chipkill is not feasible to implement on GPUs [58]. As a result, a performance efficient reliability mechanism to address the rising multi-bit faults is needed.

#### 1.2.2 Contributions

To devise a performance efficient reliability scheme, we adopt a data-centric approach [48]. We begin with the GPU application profiling to study how the data memory is accessed by an application during runtime. We noted that a small fraction of the data memory is

highly accessed and shared by the GPU threads as compared to the rest of the memory. We call this highly accessed and shared memory as *hot* memory. Next, we simulate the fault injections to study their impact on this small fraction of hot memory on GPU application output. We note that the faults in the hot memory spread widely across GPU warp thread instructions leading to catastrophic failures, for example, misclassifications in the neural networks. Consequently, we conclude that the hot memory should be prioritized to be covered under the reliability mechanism. Based on our observations, we develop a detection-only and detection-and-correction reliability schemes to reduce GPU output corruption.

Our research work on performance efficient reliable GPU computing makes the following contribution:

- We perform a detailed application-level analysis to show that a small fraction of data used by a large number of GPGPU application threads can dramatically increase their vulnerability to multi-bit faults. This data is usually read-only and can be profiled with low-overhead.

- We develop both detection and correction mechanisms that prioritize the reliability of this identified critical data. Our mechanisms leverage the critical data information obtained from the software for the partial data replication and execute checks only for this small fraction of data.

- Our selective detection and correction mechanisms based on partial data replication exhibit very limited overhead due to the fact that overhead of additional checks (and associated memory accesses) can be hidden thanks to latency tolerance property of GPUs. Quantitatively, we significantly improve GPU reliability, an average 98.97% drop in the number of execution runs with corrupt output while incurring a low average performance overhead of 1.2%.

## 1.3 Dissertation Organization

The rest of this dissertation is organized as follows. Chapter 2 provides an overview of GPU architecture, along with the memory access optimization techniques and data memory faults and their impact. Chapter 3 introduces our first defense scheme against correlation timing attacks which employs randomized coalescing. Chapter 4 details our bucketing-based coalescing scheme which secures the GPU against correlation timing attacks. In Chapter 5, we present our data-centric reliability mechanism to address the data memory faults in GPUs. We present the initial findings of our ongoing exploration of the reliability of the machine learning (ML) models in Chapter 6. Finally, in Chapter 7, we conclude this dissertation and provide details of possible future research directions.

## Chapter 2

# A General Background on Graphics Processing Units (GPUs)

In this chapter, we provide a general background on Graphics Processing Units (GPUs). Specifically, we focus on the GPU memory access optimization techniques and application execution on GPUs. We also introduce the data memory faults and their impact on GPU applications.

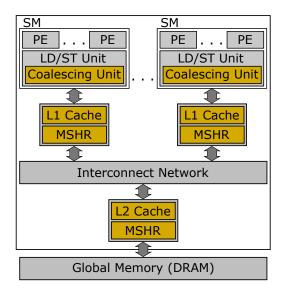

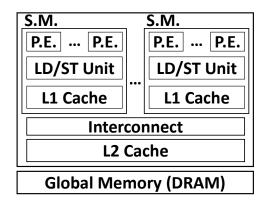

#### 2.1 Baseline GPU Architecture

Figure 2.1 shows a baseline GPU architecture. A typical GPU is comprised of a set of processing cores known as Streaming Microprocessors (SMs) in Nvidia terminology. Each SM is comprised of several processing elements (PEs), usually 32. To leverage the parallelism in applications, GPUs employ a single instruction multiple thread (SIMT) programming paradigm to launch applications on SMs. In SIMT, GPUs execute the same set of instructions with different data on multiple threads in lockstep. These threads are grouped in concurrent thread array (CTA) blocks and are launched on SMs. The SMs split each CTA block into warps (usually 32 threads/warp) and process each warp individually on the PEs. By launching multiple warps on each SM, GPUs hide memory access latency

Figure 2.1: Overview of GPU Architecture.

by executing warps in a multiplexed manner to improve the efficiency of SMs.

To address the high bandwidth requirement of the GPU applications, GPUs employ high-bandwidth global memory (DRAM) along with multi-level caches. Each SM on GPUs has a private L1 cache shared across the corresponding PEs. Next, GPUs have multiple L2 cache banks shared between all SMs connected through an interconnection network. Finally, the L2 cache banks are connected to the off-chip DRAM through separate memory channels.

## 2.2 GPU Memory Access Optimization Techniques

Memory bandwidth is one of the most performance-critical shared resources in GPUs [47]. GPUs adopt several memory bandwidth optimization techniques, such as memory access coalescing, caching and merging to reduce the number of accesses to the global memory. In this sub-section, we provide a brief overview of these optimizations.

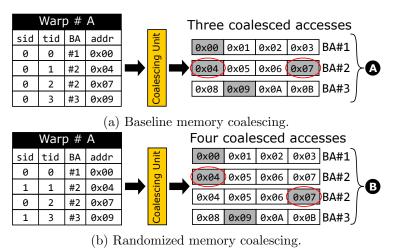

Access Coalescing. In GPUs, threads within a warp execute the instructions in lock-step. For a global memory load instruction, all 32 threads within a warp execute 32 load instructions. The coalescing unit in the LD/ST unit merges multiple memory requests from different threads of the same warp (intra-warp coalescing) into as few cache line-

sized coalesced memory accesses as possible. The intra-warp coalescing happens at the sub-warp granularity, where the coalescing unit of the SM determines the coalesced accesses of the warp by examining a group of threads belonging to the same sub-warp. If the threads of a sub-warp access data within a contiguous memory block, their requests are coalesced together to reduce memory bandwidth consumption. The size and number of sub-warps are typically fixed and remain the same throughout the application execution. However, to achieve security, the coalescing mechanisms can be randomized (RCoal [49]) so that the coalesced accesses are no longer predictable to the attacker.

Figure 2.2: Memory access coalescing in GPUs. © 2018 IEEE.

Figure 2.2 illustrates the coalescing in baseline GPU and previously proposed randomized coalescing techniques. Assume a single warp with four threads. The per-thread addresses and the requested block addresses (BA) are shown with corresponding threadids (tid) and sub-warp id (sid). In the baseline GPU, we assume a single sub-warp (sid = 0 for all threads) and hence all threads participate together in the coalescing. Since the requests from tid 1 and 2 map to the same cache block, only three accesses are generated (\texttt{\texts}) to conserve the memory bandwidth.

Caching. GPUs further conserve the memory bandwidth by exploiting the temporal and spatial locality in memory accesses across and within warps with the help of hardware caches. Current GPUs employ two levels of caches, L1-cache (shared by the warps executing on the same SM) and L2-cache (shared by the warps executing on different SMs).

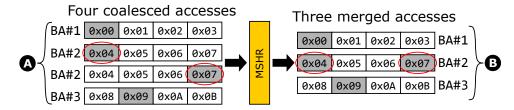

Access Merging. The coalesced memory accesses from a warp are sent to the L1-cache. Upon cache misses, the memory accesses are logged in the miss-status holding

registers (MSHRs). Multiple cache-missed coalesced accesses to the same cache block from different warps on the same SM are merged (*inter-warp merging*) in MSHRs. Note that as independent loads from the same warp can be issued to improve memory-level parallelism, MSHRs also help in merging redundant accesses from the same warp (*intra-warp merging*) if they are issued at different times. Another source of inter-warp merging is via MSHRs at L2-cache, where the redundant L2-cache misses (across different SMs) can be merged together.

### 2.3 Data Memory Faults in GPUs

#### 2.3.1 Data Memory Faults and Their Impact in GPUs

GPUs are susceptible to a variety of faults due to the manufacturing process variations, on-chip cross-talk between interconnects, alpha/neuron particle strikes, temperature variations, power supply noise, etc. [77, [125], 85], 86], [120], [121], [27]. In our research work, we focus on memory faults in GPUs. The memory faults may cause the bits of the stored data to flip to a different value than the original. This changed value of the data may lead to the silent data corruption (SDC) of the GPU output, where the application is successfully executed but results in erroneous output.

The effect of the data memory faults can be well understood when studied with respect to application usage. GPUs are increasingly used for the machine learning applications, such as self-driving cars, medical imaging, or computer virus detection. A data memory fault may cause a mis-classification in the respective machine learning application. The impact of such mis-classification itself depends upon the purpose of an application. In the case of a self-driving car, a mis-classification due to the data memory error may lead to a crash endangering lives and property. In the case of medical imaging, a mis-classification may lead to misdiagnosis leading to delay in critical care of a patient.

The faults in the hardware are addressed through an on-chip error checking and correction (ECC) mechanism, which mitigates the effect of faults on the application output.

The current generation of GPUs employs a single-bit error correction and double-bit error detection (SECDED) ECC mechanism to address the data memory faults in the caches and DRAM [58]. The multi-bit (more than two-bit) faults cannot be addressed in the current generation GPUs.

#### 2.3.2 Importance of Data Memory Faults in GPUs

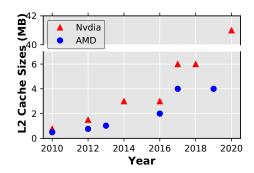

Due to the increasing workload sizes, the sizes and the operating speeds of the GPU memory are increasing rapidly. Figure 2.3 shows that the L2 cache sizes are increasing rapidly over the generations of GPUs from the major vendors. Consequently, significant research efforts have been made to operate the L2 cache at low voltage to achieve power efficiency [28, 27]. However, when operated at a low voltage, the fault rate of the L2 caches increases as well [28].

Figure 2.3: L2 Cache size trend for Nvidia and AMD GPUs.

Next, several field studies have demonstrated that the DRAMs in GPUs are more susceptible to multi-bit faults compared to the DRAMs in CPUs as the former uses a weaker ECC mechanism, SECDED, while the latter uses a stronger ECC mechanism, Chipkill [120, 121, 177]. However, the implementation of Chipkill [19] on GPUs is currently not feasible [58].

# Chapter 3

RCoal: Mitigating GPU Timing

Attack via Subwarp-based

Randomized Coalescing

Techniques

#### 3.1 Introduction

Graphics Processing Units (GPUs) are becoming an inevitable part of every computing system because of their ability to provide fast and energy-efficient computation. Given such ability, GPUs are also now being used to accelerate a variety of cryptographic algorithms. For example, the popular Advanced Encryption Standard (AES) algorithm [78] is known to achieve significant speedups on GPUs compared to CPUs [34, 41, 89, 66] as the AES algorithm exposes abundant thread-level parallelism to leverage high bandwidth and compute throughput of GPUs. With such increasing popularity of GPUs to accelerate security-sensitive applications, it is imperative to keep GPUs secure against a variety of side-channel attacks and other security vulnerabilities.

In this paper, we specifically focus on the correlation-based timing attacks on GPUs.

In general, a correlation-based timing attack exploits the relationship between the secret data and its impact on the processing time of an application: the attacker sends a large number of data samples to calculate the correlation between the actual processing time and the secret data. Among the guessed values for the secret data, the one leading to the highest correlation is the actual secret data. Notably, the recent work from Jiang et al. 44 demonstrated a correlation-based timing attack on a remote GPU server. They exploited two observations. First, the number of coalesced memory accesses in the last round can be deterministically calculated based on the last round private key byte and the encrypted text. Second, the number of coalesced accesses in the last round is correlated with the total execution time. With these two observations, an attacker can recover each key byte by picking the value that best correlates with the recorded total execution time from the remote GPU server.

The goal of this paper is to design low-overhead defense mechanisms to thwart timing attacks that exploit the memory coalescing in GPUs. To this end, a straightforward solution is to eliminate the correlation between the number of coalesced accesses and the total execution time by disabling the memory access coalescing mechanism completely. However, since the memory access coalescing is one of the key features in GPUs that optimizes the memory bandwidth consumption, the disabling of coalescing will incur a heavy performance penalty due to increase in the number of memory accesses [61], [55], [44], [112]. To provide a better trade-off between security and performance, we propose *RCoal*, a series of three tunable coalescing mechanisms to guard against correlation-based timing attacks.

The first mechanism focuses on tuning the granularity at which threads are coalesced together, thereby increasing the number of coalesced accesses at a finer granularity. We call this technique as fixed-sized subwarp (FSS) defense mechanism, where the size of subwarp determines the coalescing granularity. FSS mechanism helps to reduce the correlation between the coalesced accesses and total execution time by reducing the variance in the

<sup>&</sup>lt;sup>1</sup>Section 3.2 presents more details on the attack.

coalesced accesses. Building on the first mechanism, the second mechanism focuses on randomly changing the size of each subwarp. We call this technique as random-sized subwarp (RSS) defense mechanism where the size of each subwarp affects the attacker's ability to correctly determine the number of coalesced accesses. The final mechanism focuses on randomly changing the thread elements of each subwarp. We call this technique as random-threaded subwarp (RTS) defense mechanism as the coalescer picks random thread elements to form a subwarp. RTS can be applied to both FSS and RSS to further hinder the attacker's ability to determine the number of coalesced accesses correctly.

To the best of our knowledge, this is the first work to thwart timing attacks in GPUs via randomized coalescing techniques. In summary, this paper makes the following contributions:

- We generalize the correlation-based timing attack on GPUs and show that the regularity and determinism in memory access coalescing is a major security vulnerability.

- We propose three novel coalescing mechanisms to mitigate the timing attacks arising from memory access coalescing. These mechanisms revolve around carefully changing the size, number, and thread elements of a subwarp to reduce the correlation between the number of coalesced accesses and the total execution time.

- We present a detailed information-theoretical analysis to show that our randomized coalescing mechanisms can improve the GPU security by 24 to 961 times. Our extensive simulation results confirm the theoretical results and demonstrate that the improved security can be achieved at a performance loss of 5 to 28%.

- We propose a new metric called *RCoal\_Score* that provides an opportunity for hardware engineers to tune the security and performance trade-off as per their requirements. We discuss two such security-performance trade-off designs and conclude that RSS and RTS mechanisms provide significant advantages towards performance and security, respectively.

## 3.2 Background

In this section, we briefly introduce a) the baseline GPU architecture and the process of memory access coalescing, b) the anatomy of AES encryption, and c) the baseline timing attack assumed in this paper.

#### 3.2.1 Baseline GPU Architecture

Overview. Figure 3.1 shows a high-level schematic of the GPU architecture. A typical GPU consists of multiple cores, called as streaming multiprocessors (SMs) in NVIDIA terminology. Each SM takes advantage of the Single Instruction, Multiple Threads (SIMT) programming paradigm [54] to schedule multiple threads on its processing elements (PEs). These threads are scheduled at the granularity of a warp, which is essentially a collection of (usually 32) individual threads that execute a single instruction on the PEs in a lock step manner. Each SM can execute multiple warps concurrently in a multiplexed manner to hide the long global memory latencies and improve the utilization of core resources (e.g., register file, scratchpad memory). All SMs are connected to global memory partitions via an on-chip interconnect. In this paper, we evaluate the proposed techniques on a GPU architecture simulated using a cycle accurate GPU simulator – GPGPU-Sim [6]. More details on the simulated architecture are given in Table [3.1]

**Table 3.1**: Key configuration parameters of the simulated GPU configuration. © 2018 IEEE.

| Core Features    | 1400MHz core clock, SIMT width = $32 (16 \times 2)$                      |

|------------------|--------------------------------------------------------------------------|

| Resources / Core | 32KB shared memory, 32KB register file, 15 SMs                           |

|                  | 32 threads/warp, one subwarp per coalescing unit                         |

| Features         | immediate post dominator based branch divergence handling                |

| Memory Model     | 6 GDDR5 Memory Controllers (MCs), FR-FCFS scheduling                     |

|                  | 16 DRAM-banks, 4 bank-groups/MC, 924 MHz                                 |

|                  | memory clock Global linear address space is                              |

|                  | interleaved among partitions in chunks of 256 bytes                      |

|                  | Hynix GDDR5 Timing [39], $t_{CL} = 12$ , $t_{RP} = 12$ , $t_{RC} = 40$ , |

|                  | $t_{RAS} = 28, t_{CCD} = 2, t_{RCD} = 12, t_{RRD} = 6$                   |

| Interconnect     | 1 crossbar/direction,                                                    |

|                  | 1400MHz interconnect clock, islip VC and switch allocators               |

Memory Access Coalescing. One of the effective ways to improve the collective perfor-

Figure 3.1: Overview of Baseline GPU Architecture. © 2018 IEEE.

mance of the concurrently executing threads on GPUs is to optimize the global memory bandwidth. To this end, several techniques such as intra-warp memory access coalescing, inter- and intra-warp request merging via miss status handling registers (MSHRs), sectoring [II2], and L1/L2 caching have been proposed for GPUs. In this work, we focus on intra-warp memory access coalescing technique, which merges multiple memory requests from different threads of the same warp in to as few cache line sized coalesced memory accesses as possible.

The coalescing unit (part of LD/ST unit of the SM) performs the agglomeration of memory requests from the threads in a warp at a *subwarp* level, where the number of subwarps is an architectural parameter. If the threads of a particular subwarp request nearby data within a contiguous block of the memory, their requests are coalesced together to avoid redundant accesses. Therefore, if the memory access size, subwarp size, and thread-data pattern (e.g., if/when thread to table index mapping is known) are known, the number of memory accesses can be calculated accurately. As per CUDA programming guide [95], the scalar threads from the same warp can be coalesced together (subwarp size of 1), at a half-warp basis (subwarp size of 2) or at a quarter-warp basis (subwarp size of

4). The subwarp size is decided based on the size of the memory request from each thread. The generated coalesced accesses are serviced at the rate that matches with the underlying cache/memory bandwidth. To correctly simulate the number of coalesced accesses as that of in the baseline attack model (explained later in the section), we assume subwarp size to be 1 in our baseline architecture.

To understand the effect of subwarps on coalescing, consider an example with warp comprising of four threads under two different cases employing the number of subwarps (num-subwarp) as 1 and 2, respectively, as shown in Figure [3.2]. We assume that four threads generate four accesses and if perfectly coalesced will generate one coalesced access (memory block). When all the threads are considered together for coalescing (i.e., Case 1: num-subwarp is 1), only three coalesced accesses are generated as the requests from the second and third thread are coalesced into one request. When num-subwarp is 2 (Case 2), the coalescing is performed independently for each subwarp. Consequently, two coalesced accesses per subwarp (in total four) are generated.

#### 3.2.2 AES Encryption

Basics. The Advanced Encryption Standard (AES) [78] is a widely used symmetrickey algorithm. The AES standard specifies 128, 192, and 256 bits as the standard key lengths. Without losing generality, we focus on AES-128, which employs a 128-bit key to encrypt the plaintext. AES-128 algorithm consists of 10 rounds each with its own round key of 16 bytes, which is generated from the encryption key. In each round, subBytes() transformation (details of other transformation can be found in prior works on AES [34, 41, 89, 66) performs a table look-up operation on the substitution (S-box) table. In the last round, a table look-up operation is performed on the  $T_4$  S-box table followed by bitwise XOR operation with the last round key. This operation is expressed by Equation [3.1] for the  $j^{th}$  byte of output ciphertext  $(c_j)$  and  $i^{th}$  input state of the last round  $(t_i)$ , table lookup index) [34, 44].  $T_4$  [1] represents the last round S-box table look-up operation whose result

**Figure 3.2**: Effect of subwarps on memory coalescing. © 2018 IEEE. is XORed with  $j^{th}$  byte of the last round key  $(k_j)$ .

$$c_j = T_4 \left[ t_i \right] \oplus k_j \tag{3.1}$$

GPU Implementation of AES Encryption. A CUDA implementation of AES divides the plaintext across multiple parallel threads to improve GPU throughput. Each thread performs encryption on one line (block) of the plaintext. Therefore, each warp consists of 32 threads performing 32 different encryptions. The line to thread mapping is sequential and deterministic in the baseline implementation. If the size of the plaintext exceeds 32 lines, then it is divided sequentially among several warps. For example, a plaintext with 1024 lines will employ 32 warps each executing 32 lines of the plaintext. Figure 3.3 shows the encryption process for the last round on 32 threads of a single warp. Each thread performs encryption of a byte  $(p_j)$  of the input text, where j varies from 1 to 16. All threads of the warp work in a lock-step manner and perform the same table look up operation  $(T_4[t_i])$  with different values of  $t_i$ . The accesses are coalesced together by the coalescing unit, and when the replies come back, all threads use the same last round key  $(k_j)$  to generate one column of the ciphertext  $c_j$  as per Equation 3.2 In Equation 3.2 tid is the thread index.

**Figure 3.3**: Last round execution of AES-128 algorithm. The  $t_i$  in  $T4[t_i]$  represents the index of the table lookup operation.  $k_j$  and  $c_j$  represent the jth byte of the last round key and ciphertext, respectively. tid is the thread id within a warp. © 2018 IEEE.

$$c_j^{tid} = T_4 \left[ t_i^{tid} \right] \oplus k_j \tag{3.2}$$

#### 3.2.3 Baseline Timing Attack

In this paper, we use the correlation timing attack proposed by Jiang et al.  $\square$  as the baseline attack. The attack model assumes that the attacker sends a large number of plaintexts to a remote GPU AES encryption server. The attacker collects the ciphertexts and records the total execution time for each plaintext. The goal is to correctly find all 16 last round key bytes by exploiting a key observation that there is a high correlation between the number of memory accesses and the total execution time on GPU. The baseline attack targets the last round key since it is the most vulnerable round and key expansion is invertible (i.e., it is possible to derive the original private key from any round key)  $\square$  The observation is that each table lookup index in the last round can be computed from a byte of the last round key  $(k_j)$  and the corresponding byte of ciphertext  $(c_j)$ , independent of other ciphertext bytes (as shown in Equation 3.3). Thus, the attacker is able to observe the security leakage separately at per-byte level.

$$t_i = T_4^{-1} [c_j \oplus k_j] \tag{3.3}$$

**Figure 3.4**: Overview of the process of guessing one of the correct last round key byte  $(k_j)$ .  $A_j^{m,n}$  is the number of memory requests for  $m^{th}$  guess of the  $j^{th}$  last round key byte using  $n^{th}$  plaintext. n varies between 1 to N, where N is the number of plaintext samples. m varies from 0 to 255 and j varies from 1 to 16. © 2018 IEEE.

Figure 3.4 shows the attack process for recovering the  $j^{th}$  last round key byte  $(k_j)$ . The attack process has two major steps. The first step involves a guessed key value  $k_j^m$  where m ranges from 0 to 255. According to Equation 3.3 the table lookup index of each thread  $(t_i^{tid,m})$  can be computed, as shown in Figure 3.4a. Once the indices are obtained for all threads, the attacker can calculate the expected number of coalesced accesses  $(A_j^{m,n})$  for the  $n^{th}$  plaintext with the known and deterministic behavior of coalescing (in our configuration, 16 consecutive table elements are mapped sequentially to the same memory block). This particular attack assumes num-subwarp to be 1 (i.e., all threads in the warp are processed together for coalescing). This first step is repeated for all possible 256 key byte guesses for the  $j^{th}$  byte and for N plaintext samples. As a result, a memory access

Figure 3.5: Relationship between Last Round and Total Execution Time. © 2018 IEEE.

matrix is generated as shown in Figure 3.4b. Each row of the matrix corresponds to the number of guessed memory accesses for a particular key guess (m) across N plaintext samples  $(A_i^m)$ .

The second step involves calculating the correlation between each row (key guess) of the memory access matrix with the last round execution time (E) to encrypt each plaintext (collected by the attacker). Since both the total and last round execution time correlate with last round coalesced accesses (shown in Figure 3.5), the guessed key value  $(\alpha)$  is correct for  $k_j$  if it has the maximum correlation value  $(corr_j^{\alpha})$  with E. For the rest of the paper, we assume a stronger attack with the capability of accessing last round execution time as compared to the realistic attack, which is weaker due to the noise in the total execution time.

#### 3.3 Motivation and Goals

The primary reason behind the success of the baseline correlation timing attack is the deterministic behavior of memory access coalescing that allows accurate calculation of the coalesced accesses generated. To verify this on our GPGPU-Sim based simulation environment, we plot the correlation values  $(corr_j^m)$  of all 256 possible values of m for  $0^{th}$  key byte  $(k_0, j=0)$ . We calculate this correlation value between the coalesced accesses from the attack and the execution time of the last round of AES-128. From Figure 3.6a,

we observe that the correlation value is the highest (highlighted in red and encircled) for the correct value of the  $0^{th}$  key byte among all other guess values. We observe this trend for all 16 last round key bytes indicating that we can successfully guess all of them.

As a first step towards defending against the baseline attack, we aim to eliminate the relationship between the number of coalesced accesses and the last round execution time by disabling the coalescing mechanism. As a result, the number of coalesced accesses will always be 32 (i.e., the worst case scenario) from a warp with 32 threads. We executed the same baseline attack with coalescing disabled to find that there is no correlation between the number of coalesced accesses and the last round execution time. Consequently, we could not successfully guess any of the key byte. Figure 3.6b shows the plot of correlation values against the possible values of the  $0^{th}$  key byte. The correlation of the correct key byte is very close to zero, so as that of other key guesses.

**Figure 3.6**: Effect of Coalescing on the Recovery of  $0^{th}$  Last Round Key Byte  $(k_0)$ : a) Recovery is Successful when Coalescing is Enabled, b) Recovery is Unsuccessful when Coalescing is Disabled. © 2018 IEEE.

Although disabling the coalescing is an effective technique to defend against the base-line correlation timing attack, absence of memory access coalescing degrades the GPU performance and energy efficiency significantly [61, 55, 44, 112]. Our own experiments show that the performance degrades by up to 178% for AES-128 algorithm encrypting plaintext of 1024 lines. Also, the data movement (i.e., the number of memory accesses) increases by 2.7×. Therefore, disabling the coalescing is not an attractive solution from

the perspective of GPU efficiency.

In this paper, our goal is to design randomized coalescing techniques to carefully balance the security and performance trade-offs. Our techniques exploit two primary shortcomings of the GPU AES implementation that lead to the successful correlation timing (baseline) attack. First, all threads of a warp are grouped in a single subwarp for coalescing. As a result, the calculation of number of coalesced accesses becomes straightforward: a) determine the requested table look up indices, and then b) given that the table elements are sequentially mapped to the memory blocks and the size of each block is known, determine the number of memory blocks (coalesced accesses) required. Second, because all threads of the warp were considered together for coalescing, the order in which the threads are grouped together had no impact on the coalescing. However, if coalescing is performed at a subwarp-level (with number of subwarp being more than one), the order of grouping the threads would affect the total number of coalesced accesses depending on which threads fall into the same subwarp. To address these two shortcomings, we focus on the following three randomized coalescing aspects to weaken the correlation between the coalesced accesses calculated by the baseline attack and the execution time from the encryption.

- Number of Subwarps: We choose the number of subwarps that is unknown to the baseline attacker. The benefit of using subwarps is that the attacker may not be able to correctly estimate the number of coalesced accesses. Further, with a large number of subwarps, the variance in the number of coalesced accesses decreases, entailing more number of plaintext samples to establish a weak correlation. This weak correlation reduces the information leakage over the timing channels. We call this defense mechanism as Fixed Subwarp Size (FSS), as the size of subwarp chosen by the defense mechanism is fixed.

- Size of Subwarps: In case the attacker knows the number of subwarps (or calculates it based on the timing information), we aim to increase the strength of the defense mechanism by randomizing the number of threads per subwarp such that the total number of threads per warp still remains 32. This randomness makes the number of coalesced

accesses harder to estimate (same reasoning as FSS) even if the number of subwarps is known to the attacker. We call this defense mechanism as *Random Subwarp Size* (RSS) as the size of each subwarp is chosen randomly.

• Thread Elements of Subwarps: Our last mechanism is focused on further enhancing the GPU security by randomizing the thread elements of each subwarp (Random-threaded Subwarp (RTS)). It introduces additional randomness in the number of coalesced accesses generated. Note that RTS can be combined with both FSS and RSS defense mechanisms.

# 3.4 Subwarp based Defense Mechanisms

In this section, we discuss a series of subwarp-based defense mechanisms that are designed to weaken the deterministic memory coalescing logic in GPUs. By doing so, the baseline attack that leverages the knowledge of memory coalescing logic will find it difficult to correctly guess the last round key bytes, thereby improving the security of the GPU-based systems.

### 3.4.1 Fixed-sized Subwarps (FSS)

In the baseline attack, the attacker assumes that the number of subwarps (num-subwarp) is 1, and hence, all threads are processed together for coalescing. In our first defense mechanism, fixed size subwarps (FSS), we break this assumption by choosing a value of num-subwarp that is unknown to the attacker. In order to understand the impact of num-subwarp on performance, consider Figure 3.7a. We find that the total execution time increases with increase in the value of num-subwarp. It is because a large num-subwarp leaves few threads for being coalesced together thereby reducing coalescing possibilities across the threads within a warp. This leads to increased number of coalesced accesses resulting in the performance loss.

Advantages of FSS. Although FSS has disadvantage in terms of performance, we find

Figure 3.7: Performance of FSS enabled AES with respect to number of subwarps: a) Execution Time and Total Memory Accesses per plaintext with increasing number of subwarps, b) Average of correlations between the last round execution time and the last round memory accesses for all key bytes. The last round memory accesses are calculated assuming correct values of a key byte and the number of subwarps for coalescing to be one. © 2018 IEEE.

that such a mechanism can improve the GPU security against the baseline attack. It is because a value of num-subwarp other than 1 will generate different number of coalesced accesses than the baseline attack, which assumes num-subwarp to be 1. Therefore, the attacker will find it hard to guess the correct key byte as the correlation between the estimated number of coalesced accesses and the execution time reduces. To understand this further, we evaluate FSS-enabled GPU under the baseline attack. Figure 3.7b shows the average correlations for the correct guesses of all 16 key bytes of the last round key. As expected, we observe that the correlation between the last round execution time and coalesced accesses calculated from the attack reduces with the increase in the value of num-subwarp. Therefore, a high number of samples would be required to correctly guess the last round keys depending on the num-subwarp value.

Limitations of FSS. We evaluate the security of FSS mechanism when the attacker knows or correctly calculates the value of *num-subwarp*. For example, the calculation can be done based on the significant execution time differences across *num-subwarp* values (Figure 3.7). By repeatably measuring the execution time for encryption for a plaintext, an attacker can determine which *num-subwarp* is used by the remote GPU server. We call

this new attack as "FSS Attack", where the attacker first calculates the number of last round coalesced accesses generated per subwarp. Next, since the last round execution time correlates with the last round coalesced accesses across a complete warp, the attacker sums up the last round coalesced accesses across all subwarps in a warp. Algorithm lillilustrates the steps to calculate the number of last round coalesced accesses per warp.

**Algorithm 1** Algorithm for FSS attack to calculate the number of last round coalesced accesses for a given key byte guess while considering *num-subwarp*.

```

k_i \leftarrow guess\_value

last\_round\_mem\_accesses \leftarrow 0

for i = 0 \rightarrow num-subwarp do

mem\_accesses\_subwarp[i] \leftarrow 0

for grp = 0 \rightarrow num-subwarp do

for i = 0 \to \frac{32}{num-subwarp} do

holder[i] \leftarrow 0

\% comment: line represents plaintext line

\% comment: LEN represents the total number of lines in the plaintext

for line = \frac{grp*LEN}{num-subwarp} \rightarrow \frac{(grp+1)*LEN}{num-subwarp} do

holder[T4^{-1}[cipher[line][j] \oplus k_j] >> 4] + +

\begin{array}{c} \textbf{for } i = 0 \rightarrow \frac{32}{num\text{-}subwarp} \ \textbf{do} \\ \textbf{if } holder[i]! = 0 \ \textbf{then} \end{array}

mem\_accesses\_subwarp[grp] + +

for i = 1 \rightarrow num-subwarp do

if mem\_accesses\_subwarp[i]! = 0 then

last\_round\_mem\_accesses \leftarrow last\_round\_mem\_accesses + mem\_accesses\_subwarp[i]

```