W&M ScholarWorks

Dissertations, Theses, and Masters Projects

Theses, Dissertations, & Master Projects

Summer 2021

# Performance Optimization With An Integrated View Of Compiler And Application Knowledge

Ruiqin Tian William & Mary - Arts & Sciences, ruiqin.cn@gmail.com

Follow this and additional works at: https://scholarworks.wm.edu/etd

Part of the Computer Sciences Commons

#### **Recommended Citation**

Tian, Ruiqin, "Performance Optimization With An Integrated View Of Compiler And Application Knowledge" (2021). *Dissertations, Theses, and Masters Projects.* Paper 1627047810. http://dx.doi.org/10.21220/s2-vwgb-yw45

This Dissertation is brought to you for free and open access by the Theses, Dissertations, & Master Projects at W&M ScholarWorks. It has been accepted for inclusion in Dissertations, Theses, and Masters Projects by an authorized administrator of W&M ScholarWorks. For more information, please contact scholarworks@wm.edu.

# Performance Optimization with an Integrated View of Compiler and Application Knowledge

Ruiqin Tian

Jingning, Gansu, China

Bachelor of Engineering, Northeast Petroleum University, 2012 Master of Science, University of Chinese Academy of Sciences, 2015

A Dissertation presented to the Graduate Faculty of The College of William & Mary in Candidacy for the Degree of Doctor of Philosophy

Department of Computer Science

College of William & Mary May 2021

$\bigodot$  Copyright by Ruiqin Tian 2021

## APPROVAL PAGE

This Dissertation is submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Ruigin Tian

Ruiqin Tian

Approved by the Committee, May 2021

Bin Ren

Committee Chair Bin Ren, Assistant Professor, Computer Science College of William & Mary

d

Evgenia Smirni, Professor, Computer Science College of William & Mary

Weighen Mad

Weizhen Mao, Professor, Computer Science College of William & Mary

Pieter Peers, Associate Professor, Computer Science College of William & Mary

Gokcen Kestor, Computer scientist, HPC group Pacific Northwest National Lab

### ABSTRACT

Compiler optimization is a long-standing research field that enhances program performance with a set of rigorous code analyses and transformations. Traditional compiler optimization focuses on general programs or program structures without considering too much high-level application operations or data structure knowledge. In this thesis, we claim that an integrated view of the application and compiler is helpful to further improve program performance. Particularly, we study integrated optimization opportunities for three kinds of applications: irregular tree-based query processing systems such as B+ tree, security enhancement such as buffer overflow protection, and tensor/matrix-based linear algebra computation.

The performance of B+ tree query processing is important for many applications, such as file systems and databases. Latch-free B+ tree query processing is efficient since the queries are processed in batches without locks. To avoid long latency, the batch size can not be very large. However, modern processors provide opportunities to process larger batches parallel with acceptable latency. From studying real-world data, we find that there are many redundant and unnecessary queries especially when the real-world data is highly skewed. We develop a query sequence transformation framework *Qtrans* to reduce the redundancies in queries by applying classic dataflow analysis to queries. To further confirm the effectiveness, we integrate *Qtrans* into an existing BSP-based B+ tree query processing system, PALM tree. The evaluations show that the throughput can be improved up to 16X.

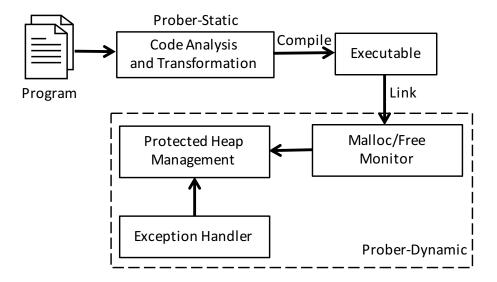

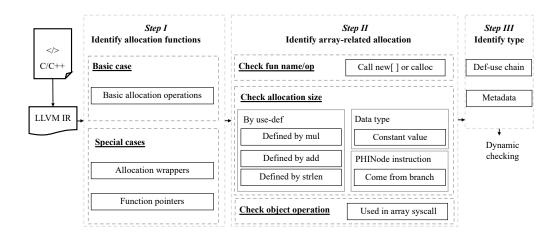

Heap overflows are still the most common vulnerabilities in C/C++ programs. Common approaches incur high overhead since it checks every memory access. By analyzing dozens of bugs, we find that all heap overflows are related to arrays. We only need to check array-related memory accesses. We propose Prober to efficiently detect and prevent heap overflows. It contains Prober-Static to identify the array-related allocations and Prober-Dynamic to protect objects at runtime. In this thesis, our contributions lie on the Prober-Static side. The key challenge is to correctly identify the array-related allocations. We propose a hybrid method. Some objects can be identified as array-related (or not) by static analysis. For the remaining ones, we instrument the basic allocation type size statically and then determine the real allocation size at runtime. The evaluations show Prober-Static is effective.

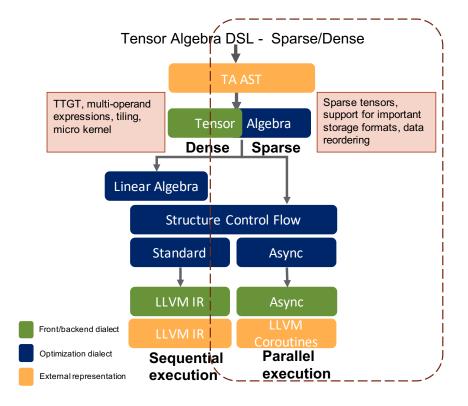

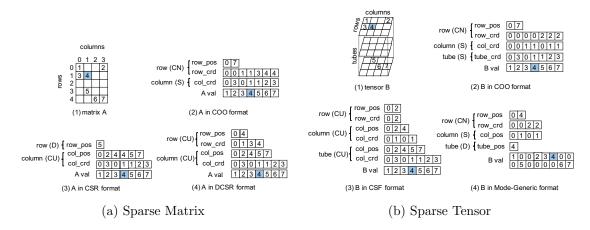

Tensor algebra is widely used in many applications, such as machine learning and data analytics. Tensors representing real-world data are usually large and sparse. There are many sparse tensor storage formats, and the kernels are different with varied formats. These different kernels make performance optimization for sparse tensor algebra challenging. We propose a tensor algebra domain-specific language and a compiler to automatically generate kernels for sparse tensor algebra computations, called SPACe. This compiler supports a wide range of sparse tensor formats. To further improve the performance, we integrate the data reordering into SPACe to improve data locality. The evaluations show that the code generated by SPACe outperforms state-of-the-art sparse tensor algebra compilers.

# TABLE OF CONTENTS

| A  | cknov              | vledgments                                                              | v  |

|----|--------------------|-------------------------------------------------------------------------|----|

| De | Dedication         |                                                                         |    |

| Li | List of Tables vi  |                                                                         |    |

| Li | List of Figures vi |                                                                         |    |

| 1  | 1 Introduction     |                                                                         |    |

|    | 1.1                | Thesis topic                                                            | 3  |

|    | 1.2                | Optimization opportunities                                              | 3  |

|    | 1.3                | Contributions                                                           | 6  |

|    |                    | 1.3.1 Improving B+ tree query processing by reducing redundant          |    |

|    |                    | queries.                                                                | 6  |

|    |                    | 1.3.2 Using compiler static analysis to assist in defending heap buffer |    |

|    |                    | overflow.                                                               | 7  |

|    |                    | 1.3.3 Building high-performance compiler for sparse tensor algebra      |    |

|    |                    | computations.                                                           | 8  |

|    | 1.4                | Dissertation Organization                                               | 9  |

| 2  | Bac                | kground                                                                 | 10 |

|    | 2.1                | Data-flow analysis                                                      | 10 |

|    | 2.2                | LLVM compiler infrastructure                                            | 11 |

|    | 2.3                | Multi-level IR compiler framework (MLIR)                                | 12 |

| 3 | Trai | nsformi  | ing Query Sequences for High-Throughput B+ Tree Processing    |    |

|---|------|----------|---------------------------------------------------------------|----|

|   | on N | Many-c   | ore Processors                                                | 14 |

|   | 3.1  | Introd   | luction                                                       | 15 |

|   | 3.2  | Backg    | ground                                                        | 18 |

|   |      | 3.2.1    | B+ Tree and Its Queries                                       | 18 |

|   |      | 3.2.2    | Latch-Free Query Evaluation                                   | 19 |

|   | 3.3  | Motiv    | ration                                                        | 21 |

|   |      | 3.3.1    | Growing Hardware Parallelism                                  | 21 |

|   |      | 3.3.2    | Highly Skewed Query Distribution                              | 21 |

|   |      | 3.3.3    | Optimization Opportunities                                    | 22 |

|   | 3.4  | Analy    | rsis and Transformation                                       | 23 |

|   |      | 3.4.1    | Overview                                                      | 24 |

|   |      | 3.4.2    | Query Sequence Analysis                                       | 24 |

|   |      | 3.4.3    | Query Sequence Transformation                                 | 25 |

|   |      | 3.4.4    | Discussion                                                    | 27 |

|   | 3.5  | Integr   | ration                                                        | 27 |

|   |      | 3.5.1    | Parallel Intra-Batch Integration                              | 28 |

|   |      | 3.5.2    | Inter-Batch Optimization                                      | 30 |

|   | 3.6  | Evalu    | ation                                                         | 31 |

|   |      | 3.6.1    | Methodology                                                   | 31 |

|   |      | 3.6.2    | Performance and Scalability                                   | 32 |

|   |      | 3.6.3    | Performance Breakdown                                         | 35 |

|   |      | 3.6.4    | Latency                                                       | 37 |

|   | 3.7  | Relate   | ed Work                                                       | 38 |

|   | 3.8  | Summ     | nary                                                          | 40 |

| 4 | Con  | npiler s | static analysis assistance in defending heap buffer overflows | 41 |

|   | 4.1  | Introduction                                                                                                                                                         |

|---|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 4.2  | Overview                                                                                                                                                             |

|   |      | 4.2.1 Observations on Heap Overflows                                                                                                                                 |

|   |      | 4.2.2 Basic Idea of Prober                                                                                                                                           |

|   |      | $4.2.2.1  \text{Prober-Static}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                     |

|   |      | Research Challenges:                                                                                                                                                 |

|   | 4.3  | Compiler Analysis and Instrumentation                                                                                                                                |

|   |      | 4.3.1 Identify Susceptible Allocations                                                                                                                               |

|   |      | 4.3.2 LLVM-IR Instrumentation                                                                                                                                        |

|   | 4.4  | Experimental Evaluation                                                                                                                                              |

|   |      | 4.4.1 Effectiveness $\ldots \ldots $                 |

|   |      | 4.4.1.1 38 Bugs from the Existing Study $\ldots \ldots \ldots$                                 |

|   |      | 4.4.1.2 Other Real-world Bugs $\ldots \ldots \ldots$ |

|   |      | 4.4.1.3 Case Study                                                                                                                                                   |

|   | 4.5  | Limitations                                                                                                                                                          |

|   | 4.6  | Related Work                                                                                                                                                         |

|   | 4.7  | Summary                                                                                                                                                              |

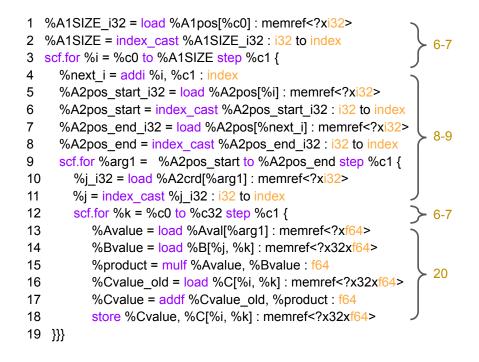

| 5 | Higl | h performance Sparse Tensor Algebra Compiler 62                                                                                                                      |

|   | 5.1  | Introduction                                                                                                                                                         |

|   | 5.2  | Background and Motivation                                                                                                                                            |

|   | 5.3  | SPACe Overview                                                                                                                                                       |

|   | 5.4  | Tensor Storage Format                                                                                                                                                |

|   | 5.5  | SPACe Language Definition                                                                                                                                            |

|   | 5.6  | Compilation Pipeline                                                                                                                                                 |

|   |      | 5.6.1 Sparse Tensor Algebra Dialect                                                                                                                                  |

|   |      | 5.6.2 Sparse Code Generation Algorithm                                                                                                                               |

|         | 5.6.3 Parallel Code Generation        | 81  |

|---------|---------------------------------------|-----|

| 5.7     | Data Reordering                       | 82  |

| 5.8     | Evaluation                            | 83  |

|         | 5.8.1 Experimentation Setup           | 83  |

|         | 5.8.2 Sparse Tensor Operations        | 84  |

|         | 5.8.3 Performance Evaluation          | 85  |

| 5.9     | Related Work                          | 89  |

| 5.10    | 0 Summary                             | 90  |

| 6 Cor   | nclusions and Future Work             | 91  |

| 6.1     | Summary of Dissertation Contributions | 91  |

| 6.2     | Future Research Direction             | 92  |

| Bibliog | graphy                                | 93  |

| Vita    |                                       | 122 |

### ACKNOWLEDGMENTS

It is a very exciting experience to pursue my Ph.D. degree in the department of computer science at the College of William and Mary. In the past several years, I gained a lot of help from the professors and the staff members in our department. More specifically, I would like to give my thanks to the following people:

First, I would like to thank my advisor, Prof. Bin Ren, for his generous support and help on my Ph.D. study. I thank him for taking me as his student. He is an open-minded professor who cares about his students' interests. When I told him I am very interested in doing compiler-related research, he gave me many opportunities to explore it. He is also a super nice person who acts not only as an advisor but also as a friend. He gave me a lot of encouragement during these years. I remembered clearly that when I had a baby, he told me that even if you work 6 hours every day, you would still get progress on your projects. These words exactly make me feel confident about finishing my Ph.D. study,

Second, I would like to thank my internship mentor, Dr. Gokcen Kestor, for the extensive guidance during my internship. She always gave me enough details and resources for me to study a new thing, which makes me feel that learning new knowledge is not terrible at all. More importantly, she always gave me trust and encouragement. When I start to handle a new problem, she always says "I trust you." The words make me feel confident. She also taught me how to make our work known to others. It's so lucky to work with her.

Third, I would like to thank our collaborators, Prof. Zhijia Zhao, Prof. Xu Liu, and Prof. Junqiao Qiu on the query redundancy elimination project, Prof. Tongping Liu and Dr. Hongyu Liu on the buffer overflow project, Dr. Luanzheng Guo and Dr. Jiajia Li on the tensor algebra compiler project. Thanks for their help on these projects.

Fourth, I would like to thank my thesis committee members, Prof. Weizhen Mao, Prof. Evgenia Smirni, Prof. Pieter Peers, and Prof. Peter Kemper for their helpful comments on my presentation and thesis. I also thank them for their generous support.

Fifth, I would like to thank our lab members, Zhen Peng, Qihan Wang, Yu Chen, and Wei Niu for sharing great thoughts on group meetings.

Sixth, I would like to thank the staff members in our department, Vanessa Godwin and Dale Hayes, for their support these years. Without their support, my Ph.D. study will not be so smooth.

At last, I would like to thank my family for their constant love and support in all my life. Without their love and support, I will not be who I am today. Special thanks to my husband, Lele Ma, for all his support in the past years.

To my family.

## LIST OF TABLES

| 3.1 | Dataset configurations                                                | 32 |

|-----|-----------------------------------------------------------------------|----|

| 3.2 | Latency for each dataset                                              | 37 |

| 4.1 | Top five vulnerabilities reported in 2018 [51]                        | 42 |

| 4.2 | Analysis on 48 heap overflows collected by [208]                      | 45 |

| 4.3 | Heap overflows between $11/01/2018$ and $02/15/2019$                  | 47 |

| 4.4 | Examples of susceptible allocations.                                  | 52 |

| 4.5 | Statically and dynamically identified callsites in buggy applications | 57 |

| 5.1 | Generated code to access nonzeros coordinates                         | 80 |

| 5.2 | Description of sparse tensors                                         | 84 |

## LIST OF FIGURES

| 1.1  | Connection between optimizations and applications                      | 5  |

|------|------------------------------------------------------------------------|----|

| 3.1  | New Optimization Opportunities                                         | 16 |

| 3.2  | A 3-order B+ tree, where key-value pairs are stored only in leaf nodes |    |

|      | (i.e., last level)                                                     | 18 |

| 3.3  | Latch-Free Query Evaluation                                            | 20 |

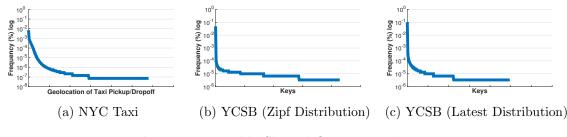

| 3.4  | Highly Skewed Query Distributions                                      | 22 |

| 3.5  | Optimization Opportunities                                             | 22 |

| 3.6  | Conceptual Workflow of QSAT                                            | 24 |

| 3.7  | Example of Query Sequence Analysis and Transformation (QSAT) $$        | 25 |

| 3.8  | Latch-Free Query Evaluation w/ <i>QTrans</i>                           | 29 |

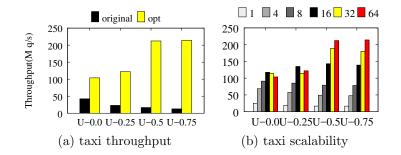

| 3.9  | Overall throughput improvement. x-axis: update ratios; y-axis:         |    |

|      | throughput of queries                                                  | 33 |

| 3.10 | Throughput scalability. x-axis: update ratios; y-axis: throughput of   |    |

|      | queries                                                                | 33 |

| 3.11 | YCSB overall throughput and scalability. x-axis: update ratios; y-     |    |

|      | axis: throughput of queries                                            | 33 |

| 3.12 | Taxi throughput and scalability.                                       | 34 |

| 3.13 | self-similar (U-0.25) leaf operations                                  | 34 |

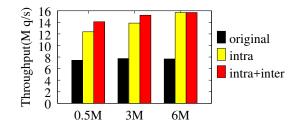

| 3.14 | self-similar throughput analysis, three bars in (c) correspond to      |    |

|      | bars in (a) and (b)                                                    | 35 |

| 3.15 | self-similar (U-0.25) throughput                                       | 36 |

| Overview of Prober                                                          | 48      |

|-----------------------------------------------------------------------------|---------|

| Identify susceptible allocations                                            | 52      |

| Bug report for the Heartbleed Problem                                       | 58      |

| An example SPACe program for Sparse Matrix-times-Dense-Matrix op-           |         |

| eration                                                                     | 68      |

| SPACe execution flow and compilation pipeline                               | 70      |

| Example matrix and tensor represented in different formats. Each            |         |

| format is a combination of the storage format attributes. $\ldots$ .        | 71      |

| Generated sparse tensor algebra dialect for SpMM operation $\ . \ . \ .$    | 75      |

| Sparse tensor data structure construction operation                         | 77      |

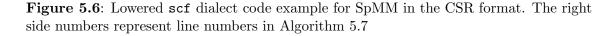

| Lowered $\mathtt{scf}$ dialect code example for SpMM in the CSR format. The |         |

| right side numbers represent line numbers in Algorithm 5.7 $\ldots$ .       | 81      |

| Sparse code generation algorithm                                            | 82      |

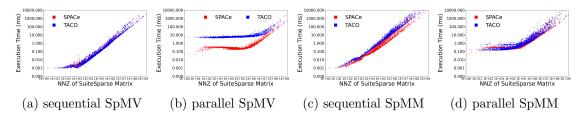

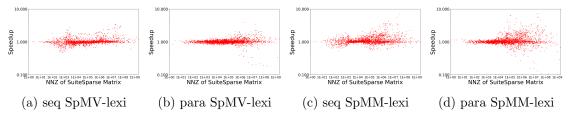

| Performance comparison with TACO on CPU                                     | 85      |

| Performance of Lexi ordering                                                | 85      |

| Visualization comparison of matrices with and without reordering $\ . \ .$  | 87      |

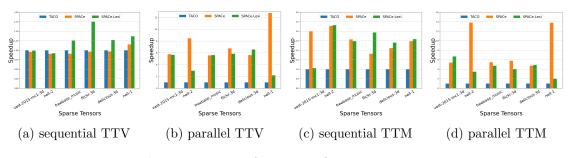

| Performance of tensor operations                                            | 88      |

|                                                                             | eration |

Performance Optimization with an Integrated View of Compiler and Application Knowledge

## Chapter 1

# Introduction

**Performance**, which is usually measured by response time, throughput, or resource utilization [130], is one of the key concerns for many applications in various areas, for example, databases [64, 85], parallel file systems [185], online analytical systems [36], security [186, 136, 28, 169], data analysis and mining applications [104, 158, 182], healthcare applications [2, 125], machine learning applications [117, 173], social network analytics [216], natural language processing [24, 145] and many others. These applications require high performance in the form of high throughput, low latency, or efficient memory usage, among others.

Compiler optimization is widely used to improve program performance through a series of optimizing transformations. These optimizations introduce a wide variety of benefits such as execution time reduction [34, 152, 59, 82], memory overhead elimination [33, 201], and/or reduced power consumption [90, 167, 89]. However, traditional compiler optimizations usually focus on analyzing code structures only, such as loop constructs, function calls, isomorphic instructions, and common expressions or sub-expressions. An example of this is loop optimizations, a major kind of compiler optimizations. Loop optimizations usually include loop unrolling, loop fusion, and loop tiling/blocking [13]. These optimizations are general; however, because of their generality, they miss some optimization opportunities due to the lack of high-level application knowledge as well.

#### 1.1 Thesis topic

Application knowledge (or application information) in this thesis refers to multiple aspects of an application, for example, input or output, function operations, data distribution or data storage. If the input of an application is a sequence of queries [74, 126, 56, 86, 206, 143], the query type and operands belong to application knowledge; if the input is a set of data elements, the data pattern, format, and distribution also belong to application knowledge [79, 98, 98, 184, 192, 108, 38].

This thesis argues that it is possible to leverage high-level application knowledge to expose more optimization opportunities to compilers to improve program performance. More specifically, this thesis aims to build an application-compilation integrated view and explore various optimizations that are provided by this integration. In other words, it is impossible to benefit from these optimizations if the application and compilation are treated separately.

### **1.2** Optimization opportunities

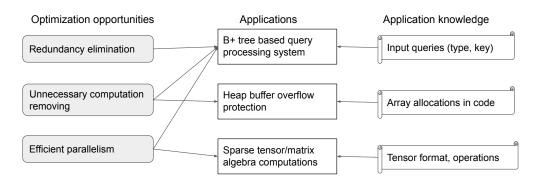

This thesis studies three main applications from various domains: B+ tree-based query processing, buffer overflow protection, and sparse tensor algebra computations. It mainly explores three optimization opportunities: redundant computation elimination, unnecessary computation removing, and efficient parallelism.

**Redundant computation elimination** corresponds to the classic compiler optimization of *partial redundancy elimination* (PRE). PRE is used to eliminate redundant code in programs. A computational statement is redundant if the same computation is calculated multiple times while the operands of the statement do not change along the path. Eliminating the redundancy computations in the program reduces the number of computations, resulting in performance improvement. Many PRE algorithms have been developed to optimize program performance [132, 57, 147, 32, 148, 101, 26]. As aforementioned, these algorithms consider code-level information only without considering any application knowledge. Redundancy elimination is also used in storage systems to improve the space utilization [189, 22, 175, 107, 151] and in network communications to reduce data transferred [215]. These strategies leverage the redundancy in data to reduce the storage space or communication overhead. This thesis does not leverage data redundancy but rather targets eliminating redundancy through the use of other kinds of application knowledge, such as the input query of the B+ tree query processing system.

Unnecessary computation removing is an effective way to remove computations that do not affect the final result. In compiler optimizations, unnecessary computation usually has two main forms, redundant computation and dead code in programs. Dead code is code that is executed but whose results are never used [5]. Many dead code elimination approaches have been proposed to improve program performance [100, 23, 203, 78, 141]. These approaches rely on analyzing the programs, i.e. only consider codelevel information. This thesis leverages application knowledge to remove the unnecessary computations. For example, it is possible to control the protection scope of buffer overflows by leveraging code patterns in programs.

**Parallelism** is key to program performance. This thesis mainly considers two types of parallelism, data parallelism and task parallelism. Data parallelism refers to distributing data to different hardware computing resources and computing them in parallel. Task parallelism refers to distributing tasks to different hardware computing resources and executing these tasks in parallel. Data parallelism is often achieved with SIMD (Single Instruction, Multiple Data) units [156, 168], and task parallelism is often achieved with multi-threads. For SIMD data parallel, SIMD utilization plays an important role in performance [156, 72, 159, 157]; for multi-thread task parallel, reducing the synchronization or communication overhead plays a key role in efficient execution [37, 44, 202]. This thesis explores efficient parallelism for B+ tree based query processing system execution and sparse tensor algebra computations.

The three studied applications share common optimization opportunities. Figure 1.1 shows the connections between the optimization opportunities and the applications.

Figure 1.1: Connection between optimizations and applications

For redundancy elimination and unnecessary computation removing, this thesis analyzes input queries in B+ tree query processing systems and identifies many redundant and unnecessary queries (application knowledge). It then applies a compiler optimization, redundancy elimination, to eliminate the redundant and unnecessary queries, thus improving the throughput. Similarly, in buffer overflow protection, this thesis analyzes dozens of heap buffer overflow bugs in C/C++ programs and discovers that all heap overflows are related to arrays (application knowledge). This means that protection of non-array objects is unnecessary for heap buffer overflows. This thesis designs a set of compiler techniques to automatically analyze source code and identify array allocations.

To improve program parallelism in B+ tree query processing system, this thesis analyzes the input queries to guarantee that the queries on the same key (or the same leaf node in B+ tree) are only processed by one thread. It therefore reduces thread conflicts and achieves better thread-level parallelism. Similarly, for sparse tensor algebra computations, the computations on each dimension of output tensor are only processed by one thread thus achieving better thread-level parallelism. Moreover, because the compiler knows the distribution of queries or the computation pattern of tensor computations, it is possible to design effective SIMD optimizations to achieve better SIMD utilization as well.

#### **1.3** Contributions

In this thesis, we explore program optimizations from an integrated view of compiler and application knowledge. As we mentioned above, we study three different types of applications. The contributions in each application are presented in the rest of this section.

# 1.3.1 Improving B+ tree query processing by reducing redundant queries.

B+ trees are used in a wide range of applications, such as database systems and file systems. Improving the performance of B+ tree processing systems has been thoroughly studied. Most efforts focus on improving concurrency. However, synchronization is still a performance bottleneck in improving concurrency. Latch-free B+ tree query [170] processing is proposed to avoid synchronizations. Queries are collected into batches and each batch is processed by threads parallel under a bulk synchronous parallel (BSP) model. The threads are carefully coordinated so that locks can be avoided. The problem is that the batch size can not be very large to avoid long delays. However, advanced modern processors make it possible to increase the batch size. In this thesis, we find that there will be more optimization opportunities beyond parallelism when the batch-size increases, especially with the highly skewed real-world datasets. We find that there are many redundancies in the queries. To identify and remove the redundant queries, we propose a query sequence analysis and transformation framework - QSAT based on applying classic data-flow analysis. For practical use, we implement a one-pass QSAT, called Qtrans. To evaluate the effectiveness, we integrate *Qtrans* into an existing BSP-based B+ tree query processing system, PALM tree [170]. The evaluation shows that *Qtrans* is effective and efficient, yield up to 16X throughput improvement.

# 1.3.2 Using compiler static analysis to assist in defending heap buffer overflow.

Heap buffer overflows are still the top vulnerabilities in C/C++ programs. Common approaches often bring too much performance overhead since they check every overflow. Efficient approaches such as Cruiser [211], DoubleTake [121], HeapTherapy [212], iReplayer [119], can not stop the vulnerabilities before overflow happens since they detect buffer overflows after the effect. We propose Prober to overcome these issues. Prober imposes a low overhead and can stop the program before overflow happens. It can also detect both read-based and write-based heap overflows. Prober is based on the key observation that overflows are typically related to arrays. This key observation identifies that we only need to protect array-related objects. Prober is composed of Prober-Static and Prober-Dynamic. Prober-Static is used to identify and instrument the array-related allocations in programs and Prober-Dynamic is for protecting the instrumented array-related objects in run-time. In this thesis, we contribute Prober on the Prober-Static side.

The key challenge of Prober-Static is to correctly identify all the array-related heap objects. On one hand, missing array-related heap objects will lead to no detection of overflows. On the other hand, including unnecessary objects will increase the run-time protection overhead. To this end, Prober-Static uses a hybrid approach. Some objects can be identified as array-related (or not) statically with the compiler. For the remaining ones, we decide in the runtime. We first instrument the size of the basic allocation type statically, then use Prober-Dynamic to determine the real allocation size in run-time. If the real allocation size is multiple times the size of the basic type, the allocation is identified as array-related allocation. Overall, Prober-Static is conservative and it does not miss any array-related allocations. The effectiveness has been evaluated in dozens of real-world heap overflow applications.

# 1.3.3 Building high-performance compiler for sparse tensor algebra computations.

Tensor algebra is at the core of numerous applications in scientific computing, machine learning, and data analytics, where data is often sparse with most entries as zeros. Achieving high-performance on sparse tensor algebra computations is important. There are many challenges in writing high-performance code for sparse tensor computations. First, the storage format will influence computation performance. There are many storage formats to store the non-zero values in sparse tensors and not a single format is good for all cases. To get high-performance for specific sparse tensors computations, users need to choose the proper format according to the feature of the sparse tensors. Second, optimizing sparse computation is difficult. Sparse tensor computations contain many indirect memory accesses and write dependencies. Besides this, different tensor expressions and different storage formats make the computation kernels different. It is necessary to use different optimizations to solve different performance bottlenecks in different computations kernels. Third, there are many back-end hardware platforms. Different hardware platforms require different code optimizations for high-performance.

To handle some of the above challenges, we propose a compiler-based approach to achieve high-performance on data-intensive sparse tensor computations. We build a sparse tensor compiler, SPACe, based on the Multi-level Intermediate Representation (MLIR) framework, a compiler infrastructure developed by Google to build reusable and extensible compilers. MLIR provides a disciplined, extensible compiler pipeline with gradual and partial lowering. Users can build customized compilers based on MLIR by creating customized domain-specific intermediate representations (IR) and implementing domainspecific optimizations. Since SPACe is built on MLIR infrastructure, it supports different hardware platforms by utilizing the powerful back-end compilation support.

SPACe supports several most common formats, such as Coordinate format, Compressed sparse fiber format and Mode-generic format with our proposed sparse tensor format attributes, which considers the format attribute of each dimension of tensors. SPACe is implemented as an extension of the MLIR framework. It contains a highly-productive domain-specific language (DSL) that provides high-level programming abstractions for tensor algebra computations. SPACe uses the high-level tensor algebra information, such as tensor expression and tensor formats, to generate the corresponding computation kernels. We also integrate the data reordering optimization into SPACe to further improve the performance. We evaluate the performance of SPACe on massive sparse matrix/tensor datasets. The results show that SPACe can generate more efficient sequential and parallel code compared to state-of-the-art sparse tensor algebra compilers.

### 1.4 Dissertation Organization

The rest of this dissertation is organized as follows. Chapter 2 introduces the necessary general background for data-flow analysis, Low-level Virtual Machine (LLVM) compiler infrastructure, and Multi-level Intermediate Representation compiler framework (MLIR) used in this thesis. Chapter 3 shows how we use redundancy elimination techniques in the compiler to improve the performance of B+ tree query processing on many-core processors. Chapter 4 shows how we use compiler static analysis techniques to assist in heap buffer overflows in C/C++ programs effectively and efficiently. Chapter 5 shows how we build the high-performance sparse tensor algebra compiler based on high-level information such as tensor operations and tensor formats. Finally, we conclude the thesis and discuss the future research directions in chapter 6.

# Chapter 2

# Background

In this section, we provide the necessary background and the compiler frameworks we use in this thesis. The compiler optimizations used in this thesis are mainly based on the data-flow analysis. The compiler frameworks we use are LLVM and MLIR.

### 2.1 Data-flow analysis

Data-flow analysis is a classic way used by the compiler to infer run-time information statically. In an optimizing compiler, data-flow analysis is mainly used for reasoning about helpful run-time information statically to get more optimization opportunities, and providing logical evidence to prove the correctness of the optimizations at some program points. Programmers can also use data-flow analysis to better understand their programs to improve the programs accordingly. Data-flow analysis is usually conducted by solving a set of equations based on a graphical representation of the program. The output of the data-flow analysis is the possible facts that can happen during run-time [46].

Data-flow analysis has variable forms, such as variable liveness analysis, expression availability analysis, reaching definition analysis and very busy expression analysis. Variable liveness analysis finds *live variables* at program points. A variable v is *live* at point p if and only if there is a path from p to a use of v and there is no redefinition of v in this path. Variable liveness analysis can be used to make global register allocation more efficient, to detect references to uninitialized variables, and so on. Expression availability analysis discovers the set of available expressions at each program point. It can be used to reason and eliminate global common sub-expressions. Reaching definition analysis finds the set of definitions that reach a block. It can be used to reason about where an operand is defined. An expression is *very busy* at a point if the expression will be guaranteed to be computed at some time in the future. Very busy expression analysis can be used to reduce the number of operations in the whole program. All these analyses play key roles in applying optimizations.

### 2.2 LLVM compiler infrastructure

LLVM is an open-source compiler infrastructure to support analyses and transformations for any program in all stages, including compile-time, link-time, install-time, run-time, and even idle time between runs. LLVM has five critical features that make it a powerful compiler infrastructure. First, LLVM provides persistent program information during a program's lifetime, which makes it possible to perform code analyses and transformations in all stages. Second, LLVM allows offline code generation. This feature makes it possible to add specific optimizations for performance-critical programs. Third, LLVM gathers user-based profiling information at runtime so that the optimizations can be adapted to the actual users. Fourth, LLVM is language independent so that any language can be compiled. Fifth, LLVM allows whole-program optimizations because it is language independent [110].

LLVM provides the above five features based on two critical parts. First, LLVM provides a low-level, but typed code representation, called LLVM Intermediate Representation (LLVM IR). LLVM IR represents the programs by using an abstract RISC-like three-address instruction set but including higher-level information such as type information, explicit control flow graphs, and data-flow representation. This higher-level information plays an important role in conducting code analysis and optimizations in all

stages. LLVM IR also provides explicit language-independent type information; it contains explicitly typed pointer arithmetic. To this end, LLVM IR also serves as a common representation for code analysis and transformations during the program's lifetime. Second, LLVM uses a compiler design to provide a combination of capabilities. Static compiler front-ends generate codes in LLVM IR and combined them into one LLVM IR code file by LLVM linker. Multiple optimizations can be applied during link-time, including the inter-procedural optimizations. The optimized code will usually be translated into native machine code according to the target given at link-time or install-time. The persistent information and the flexibility of applying optimizations make it possible for LLVM to perform code analysis and optimizations in all the stages [110].

### 2.3 Multi-level IR compiler framework (MLIR)

MLIR(Multi-level IR) is a compiler infrastructure for building reusable and extensible compilers. MLIR supports the compilation of high-level abstraction and domain-specific constructs and provides a disciplined, extensible compiler pipeline with gradual and partial lowering. The design of MLIR is based on minimal fundamental concepts and most of the IRs in MLIR are fully customized. Users can build domain-specific compilers and customized IRs, as well as combining existing IRs, opting into optimizations and analyses.

The core MLIR concepts include operations, attributes, values, types, dialects, blocks, and regions. An *operation* is the unit of semantics. In MLIR, "instruction", "function" and "module", are all modeled as *operations*. An *operation* always has a unique opcode. It takes zero or more operands and produces zero or more results. These operands and results are maintained in static single assignment (SSA) form. An *operation* may also have attributes, regions, blocks arguments, and location information as well. An *attribute* provides compile-time static information, such as integer constant values, string data, or a list of constant floating-point values. A *value* is the result of an operation or block arguments, it always has a type defined by the type system. A *type* contains compile-time semantics for the value. A *dialect* is a set of operations, attributes, and types that are logically grouped and work together. A *region* is attached to an instance of an operation to provide the semantics (e.g., the method of reduction in a reduction operation). A *region* comprises a list of blocks, and a *block* comprises a list of operations [111].

Beyond the built-in IRs in the MLIR system, MLIR users can easily define new customized IRs, such as high-level domain-specific language, dialects, types, operations, analyses, optimizations and transformation passes [111].

## Chapter 3

# Transforming Query Sequences for High-Throughput B+ Tree Processing on Many-core Processors

The throughput of B+ tree query processing is critical to many databases, file systems, and cloud applications. Based on bulk synchronous parallel (BSP), latch-free B+ tree query processing has shown promise by processing queries in small batches and avoiding the use of locks. As the number of cores on CPUs increases, it becomes possible to process larger batches in parallel without adding any extra delays. In this work, we argue that as the batch size increases, there will be more optimization opportunities exposed beyond parallelism, especially when the query distributions are highly skewed. These include the opportunities of avoiding the evaluations of a large ratio of redundant or unnecessary queries.

To rigorously exploit the new opportunities, this work introduces a query sequence analysis and transformation framework – QTrans. QTrans can systematically reason about the redundancies at a deep level and automatically remove them from the query sequence. QTrans has interesting resemblances with the classic data-flow analysis and transformation that have been widely used in compilers. To confirm its benefits, this work integrates QTrans into an existing BSP-based B+ tree query processing system, PALM tree, to automatically eliminate redundant and unnecessary queries <sup>1</sup>. Evaluation shows that, by transforming the query sequence, QTrans can substantially improve the throughput of query processing on both real-world and synthesized datasets, up to 16X.

#### 3.1 Introduction

As a fundamental indexing data structure, B+ trees are widely used in many applications, ranging from database systems and parallel file systems to online analytical processing and data mining [64, 85, 185, 36, 39]. There have been significant efforts on optimizing the performance of B+ trees, with a large portion of work aiming to improve the concurrency [161, 170, 134, 25, 27, 60]. As the memory capacity of modern servers has increased dramatically, in-memory data processing becomes more popular. Without expensive disk I/O operations, the cost of accessing in-memory B+ trees becomes more critical.

To reduce the tree accessing cost, prior work has proposed latch-free B+ tree query processing [170]. Traditionally, B+ tree query processing requires locks (i.e., latches) to ensure the correctness since queries may access the same tree node and if one of them modifies it (e.g., an insertion query), it would cause conflicts. Latch-free B+ tree query processing avoids the use of locks by adopting a bulk synchronous parallel (BSP) model. Basically, it processes the queries batch by batch, with each batch handled by a group of threads in parallel. By coordinating the threads working on the same batch, the use of locks can be totally avoided (see Section 2). To guarantee the quality of service (QoS), the size of a query batch should be carefully bounded to avoid long delays.

Fortunately, as modern processors become increasingly parallel, the size bound of a batch can be dramatically relaxed without incurring extra delays. For example, the latest

<sup>&</sup>lt;sup>1</sup>Artifact available at: https://doi.org/10.5281/zenodo.1486393

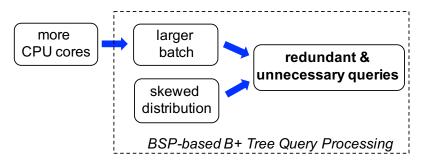

Intel Xeon Phi processors equipped with 64 cores can process 1M queries with time cost at only milliseconds (ms) level. In this work, we argue that as the batch size grows, there will be more optimization opportunities exposed beyond parallelism, which are further compounded by the fact that many real-world queries follow highly skewed distributions. The high level idea is abstractly illustrated by Figure 3.1.

Figure 3.1: New Optimization Opportunities

For example, queries to the locations where taxi drivers stop are highly biased in both the time dimension (e.g., rush hours) and the space dimension (e.g., popular restaurants). As the query batch becomes larger, there will be growing possibilities of redundant queries (e.g., a repeated search of the same location) or unnecessary queries (e.g., a later query "cancel out" the effect of an earlier query).

To identify these "useless" queries, this work proposes a query sequence analysis and transformation framework – QTrans, to systematically reason about the relations among queries and exploit optimization opportunities.

QTrans has interesting resemblances with the classic data-flow analysis and transformation, but it targets *query*-level analyses and transformations. Intuitively, QTrans treats a query sequence as a "high-level" program, where each query resembles a statement in a regular program. By tracking the queries that "define" values, QTrans is able to link search queries to their corresponding defining queries. Based on the analysis, QTransmarks all the useful queries in the sequence and sweeps the useless ones, reducing the amount of queries to evaluate. Comparing to a traditional data-flow analysis [46, 4] that iterates over cyclic control flows, QTrans only needs to perform acyclic analysis for query sequences with the most basic types of queries—although the algorithm of redundancy elimination is similar regardless of this difference.

To evaluate its effectiveness, we integrate QTrans into an existing BSP-based B+ tree processing system, called PALM tree [170]. The integration is at two levels: QTransfor each individual batch (i.e., intra-batch integration), and QTrans across batches (i.e., inter-batch integration). To minimize the runtime overhead, we also implement the parallel version of QTrans and discuss potential load imbalance issues.

Finally, our evaluation using real-world and synthesized datasets confirms the efficiency and effectiveness of *QTrans*, yielding up to 16X throughput improvement on Intel Xeon Phi processors, with scalability up to all the 64 cores.

In sum, this work makes a four-fold contribution.

- First, this work identifies a class of optimizations for B+ tree query processing, enabled by the increased hardware parallelism and the skewed query distributions.

- It proposes *QTrans*, a rigorous solution to optimizing query sequences, inspired by the conventional data-flow analysis and transformation.

- It integrates *QTrans* into an existing BSP-based B+ tree processing system and the evaluation shows significant throughput improvement.

- The idea of leveraging traditional code optimizations at the query level, in general, could open new opportunities for optimizing query processing systems.

In the following, we will first provide the background on B+ trees and the latch-free query processing (Section 3.2), then discuss the motivation of this work (Section 3.3). After that, we will present *QTrans* (Section 3.4), the integration of *QTrans* into PALM tree (Section 3.5), and the evaluation results (Section 3.6). Finally, we discuss the related work (Section 3.7) and conclude this work (Section 3.8).

### 3.2 Background

This section introduces B+ trees, its basic types of queries, and the high-level idea of latch-free query evaluation.

#### 3.2.1 B+ Tree and Its Queries

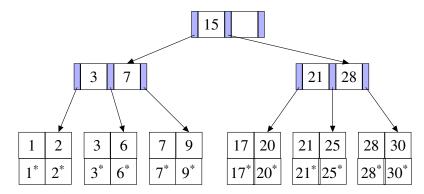

A B+ tree is an N-ary index tree. It consists of internal nodes and leaf nodes. In contrast to B trees, B+ trees only maintain the keys and their associated values in their leaf nodes, and their internal nodes are merely used to hold the comparison keys and pointers for tree traversals. The maximum number of children nodes for internal nodes is specified by the *order* of B+ tree, denoted as *b*. The actual number of children for internal nodes should be at least  $\lceil \frac{b}{2} \rceil$ , but no more than *b*. Figure 3.2 shows an example of a 3-order B+ tree. Each internal node contains comparison keys and pointers to the children nodes. The leaf nodes together hold all the key-value pairs. In the leaf nodes, the numbers represent the keys and the numbers marked with asterisks represent the values of the corresponding keys. For the 3-order B+ tree, each internal node has at least 2 children nodes, but no more than 3.

**Figure 3.2**: A 3-order B+ tree, where key-value pairs are stored only in leaf nodes (i.e., last level).

The structure of B+ tree dynamically evolves as queries to the tree are evaluated. In general, there are three basic types of B+ tree queries: (i) insertion; (ii) search; and (iii) deletion.

Given a B+ tree  $\mathcal{T}$ , suppose a function  $\text{FIND}(key_i, \mathcal{T})$  can find the leaf node of  $key_i$ if it exists or return *null* otherwise, then the semantics of queries can be described as follows.

- $I(key_i, v_j)$ : if FIND $(key_i, \mathcal{T}) \neq null$ , then update its value to  $v_j$ ; otherwise, insert a new entry of  $(key_i, v_j)$  into  $\mathcal{T}$ .

- $S(key_i)$ : if FIND $(key_i, \mathcal{T}) \neq null$ , return the value of  $key_i$ ; otherwise, return null.

- $D(key_i)$ : if FIND $(key_i, \mathcal{T}) \neq null$ , then remove the entry  $(key_i, v_i)$  from the B+ tree.

Among the three, only  $S(key_i)$  returns results;  $I(key_i, v_j)$  and  $D(key_i)$  only update/modify the B+ tree. It is important to note that, when multiple queries arrive in a sequence, the order in which the queries are evaluated may affect both the returned results and the tree structure. In other words, there exist dependencies among the queries in general.

#### 3.2.2 Latch-Free Query Evaluation

When there are multiple threads operating on the same B+ tree, it becomes challenging to evaluate the queries efficiently. First, the workload for each thread is too little to benefit from thread-level parallelism [170]; Second, since different queries may access the same node, threads have to lock the nodes (or even subtrees) that they operate, which essentially serializes the computations, wasting hardware parallelism.

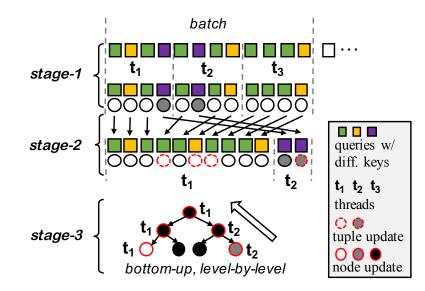

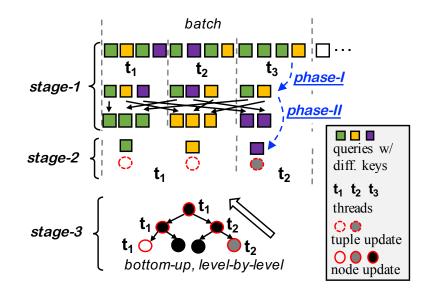

A promising solution to the above issues is *latch-free query evaluation* [170]. Basically, it adopts the bulk synchronous parallel (BSP) model and processes queries batch by batch. Threads are coordinated to process the queries in a batch in parallel without any use of locks. Specifically, each query batch is processed in three stages <sup>2</sup>, as illustrated in Figure 3.3:

<sup>&</sup>lt;sup>2</sup>For better illustration, we merged stages 3 and 4 in [170].

- Stage-1 Partition queries to threads evenly; threads then run in parallel to find the corresponding leaf nodes based on the keys in the queries;

- Stage-2 Shuffle queries based on the leaf nodes such that each thread only handle queries to the same leaf node. Evaluate queries in parallel, including returning answers to search queries and updating corresponding tuples in the leaf nodes for insert and delete queries;

Stage-3 *Modify* tree nodes bottom up:

- **Update** tree nodes in parallel and **collect** requests for updating the parent nodes (i.e., the upper level);

- *Shuffle* modification requests to the parent nodes such that each thread only modifies the same node;

- *Repeat* update-shuffle, until the root node is reached and updated as needed.

Figure 3.3: Latch-Free Query Evaluation

The shuffling in stages-2 and 3 ensures contention-free operations for each thread, guaranteeing the correctness. Comparing with lock-based schemes, this latch-free scheme

can significantly boost the throughput of query evaluation for B+ trees, up to an order of magnitude [170].

### 3.3 Motivation

On top of the promises of latch-free query evaluation, we find new opportunities to further improve the efficiency of B+ tree processing, enabled by modern many-core processors and the highly skewed query distributions.

#### 3.3.1 Growing Hardware Parallelism

As the CPU clock frequency has reached a plateau, modern processors have embraced an increase in parallelism to sustain performance gain. For example, the latest Xeon Phi processor, Knights Landing [180], contains 64 cores/256 hyper threads. This massive hardware parallelism enables high processing capacity by allowing a larger pool of threads to run in parallel.

In the context of latch-free B+ tree query processing, the availability of more hardware threads allows the use of larger batch sizes while preserving the processing delay. However, this work argues that the benefits of using larger batches are not limited to the parallelism – as the batches become larger, new optimization opportunities are exposed, especially when the queries are unevenly distributed.

#### 3.3.2 Highly Skewed Query Distribution

We observe that, the query distributions of real-world applications are often highly skewed. Take the taxi data of New York City (NYC) as an example <sup>3</sup>. The geolocations where taxi drivers pick up (or drop off) passengers follow a highly skewed distribution, as shown in Figure 3.4-(a).

The x-axis shows the geolocations and the y-axis indicates the visiting frequencies of

$<sup>^{3}</sup>$ https://s3.amazonaws.com/nyc-tlc/trip+data/yellow\_tripdata\_2009-01.csv

Figure 3.4: Highly Skewed Query Distributions

each geolocation for a period of one month. The top 1000 geolocations out of 4,194,304 (i.e., 0.02%) covers 68.272% of total visits. In this case, the skewed distribution is caused by the fact that some geolocations are much more likely to be visited by taxis, such as shopping malls or popular restaurants.

In fact, skewed distributions frequently appear in other query processing scenarios, such as BigTable [35], Azure [47], Memcached [69], among others. Figures 3.4-(b) and (c) show the key distributions in cloud workloads modeled by Yahoo Cloud Serving Benchmark (YCSB). In these cases, the top 1% keys cover 30% and 56% requests, respectively.

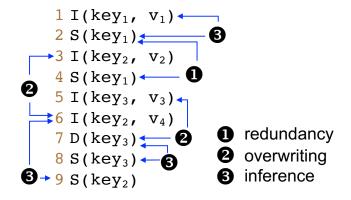

Figure 3.5: Optimization Opportunities

#### 3.3.3 Optimization Opportunities

When the distribution becomes highly skewed, queries with identical keys tend to appear more frequently. This trend not only results in repetitive queries (i.e., query redundancies), but also queries that might not have to be evaluated.

Next, we use an example query sequence, as shown in Figure 3.5, to illustrate the optimization opportunities, and informally characterize them into three categories.

- Query Redundancy  $\bigcirc$ . One obvious opportunity is for the repeated search queries like queries 2 and 4 in Figure 3.5. Since query 3 does not modify  $key_1$ , query 4 should return the same value as query 2. Thus, we only need to evaluate one of them, then forward the return value to the other.

- Query Overwriting 2. When two queries operate on the same key and both of them are either insert or delete with no search queries on the same key in between, then the second query may "overwrite" the first query. In another word, the first query becomes unnecessary, such as the overwritten queries 3 and 5 in Figure 3.5.

- Query Inference ③. For a search query, by tracing back prior queries in the query sequence, one may find an earlier query carrying the information that the search query needs, thus we may infer its return value without evaluating it, such as query pairs (1, 2), (6, 9), and (7, 8).

In addition, as existing opportunities are exploited, more opportunities might be uncovered. For example, an earlier removal of a search query may enable a new opportunity of query overwriting. As we will show in the evaluation, the above optimization opportunities frequently appear when dealing with both real-world and synthesized datasets.

# 3.4 Analysis and Transformation

In this section, we present a rigorous way to systematically exploit the new opportunities mentioned above, inspired by the classic data-flow analyses and transformations.

#### 3.4.1 Overview

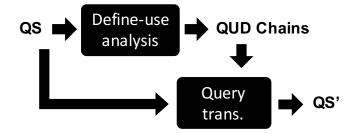

Basically, we treat the query sequence as a "program", where each "statement" is a B+ tree query. Then the optimization of query sequence follows the typical procedure of a traditional compiler optimization: it first performs an analysis over the query sequence, based on which, it then transforms the query sequence into an optimized version – a new query sequence that is expected to be evaluated more efficiently. We refer to this new optimization scheme as *query sequence analysis and transformation* or QSAT, in short.

Figure 3.6: Conceptual Workflow of QSAT

Figure 3.6 illustrated the workflow of QSAT. The original query sequence QS is first analyzed to uncover use-define relationships among queries. The output – an intermediate data structure, called QUD chains is then used to guide the query sequence transformation, which yields an optimized query sequence QS'. Next, we present the ideas of QSAT.

# 3.4.2 Query Sequence Analysis

The goal of query sequence analysis is to uncover the basic define-use relations among the queries, which will be used to facilitate the later transformation. This resembles the classic *reaching-definition analysis* used in compilers [46, 4]. Basically, it examines the queries in the sequence and finds out which queries "define" the "states" of a B+ tree and which queries "use" the "states" correspondingly.

Based on the semantics defined in Section 3.2.1, the queries that define the state are *insert* and *delete* queries, and the queries that use the state are *search* queries. The defineuse analysis matches each *search* query with its corresponding defining query (either an *insert* or a *delete*) based on the keys that the queries carry.

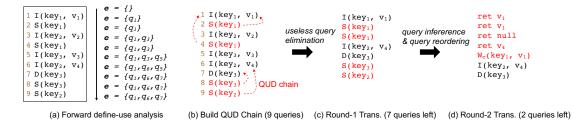

**Example**. Figure 3.7-(a) shows the define-use analysis on the running example, where  $q_i$  corresponds to the query at line *i*. Basically, the set *e* consists of the defining queries that can reach each query. For example, the defining queries  $q_1$ ,  $q_6$  and  $q_5$  can reach query  $q_7$ .

Figure 3.7: Example of Query Sequence Analysis and Transformation (QSAT)

**QUD Chain**. To represent the results of define-use analysis, we construct a data structure – query-level use-define chain (QUD chain). This data structure resembles the UD chain constructed internally by some compilers.

The construction of QUD chains is as follows. Basically, when a use query is met, the construction adds a link from the use query to its corresponding defining query (i.e., the defining query with the same key) if the later exists in current defining query set e. An example of constructed QUD chains is shown in Figures 3.7-(b).

QUD chains capture the dependence relations among the queries in a query sequence. For the query semantics defined in Section 3.2.1, the size of a QUD chain is limited to two queries. However, in general, the length of a QUD chain can go beyond two. QUD chains provide critical information for performing query sequence transformation, as shown next.

# 3.4.3 Query Sequence Transformation

The purpose of query sequence transformation is to generate an optimized version of query sequence. For clarity, we next describe the transformation with two passes. However, they can be integrated into one pass, as we will show later.

Round-1: Useless Query Elimination. This round is to eliminate queries that do not

| Algorithm 1 Useless Query Elimination (Mark-Sweep)                       |

|--------------------------------------------------------------------------|

| 1: $I = \{\}$ $\triangleright$ a list of useful queries                  |

| 2: $QUD() \Rightarrow QUD(q)$ returns the defining query of query q      |

| 3: for $q_i$ in $\{q_1 \cdots q_n\}$ do                                  |

| 4: <b>if</b> $q_i$ is a search query <b>then</b>                         |

| 5: $I.add(q_i) \triangleright mark \ a \ search \ query \ as \ "useful"$ |

| 6: <b>if</b> $\operatorname{QUD}(q_i) \neq \emptyset$ <b>then</b>        |

| 7: $I.add(QUD(q_i)) \triangleright mark defining query "useful"$         |

| 8: return I                                                              |

contribute to the final results of query processing – the returned values of search queries and the key-value pairs stored in the B+ tree. This can be achieved with a *mark-sweep* strategy that has been previously used for garbage collection and dead code elimination.

Algorithm 1 describes the useless query elimination. It first marks all the search queries as useful queries, as they need to return values. Then it traces back the QUD chains to find the corresponding defining queries, and mark them as useful queries as well. Note that the algorithm is customized to QUD chains of length 2, but it can be easily extended to handle QUD chains with arbitrary length.

**Example**. Figure 3.7-(c) lists the results after useless query elimination. The number of queries drops from 9 to 7. This round explores query overwriting (see Section 3.3.3).

**Round-2:** Query Inference & Reordering. Besides query overwriting, there are two other optimization opportunities: redundant queries and query inference (see Section 3.3.3). The second round is to explore the latter two.

Basically, for each search query, find its corresponding defining query (if exists), then retrieve the return value and return it. After this optimization, all the search queries with corresponding defining queries (i.e.,  $QUD(q_i) \neq \emptyset$ ) will be eliminated, as Figure 3.7-(d) shown (denoted as ret  $v_i$ ).

Note that, after the optimization, no return operations ret  $v_i$  depend on any other queries, hence they can be reordered – being moved to the top of the sequence. In this way, the latency of the search queries could be reduced.

An orthogonal optimization is a top-K cache. When the B+ tree is large, performance

can be benefited from putting hot key-value pairs (top K pairs) into a small cache. Thus, when an insert query with a top-K key-value pair is left after round 1, we can transform the query into a cache write operation (e.g.,  $W_c(key_i, v_j)$  in Figure 3.7-(d)).

Finally, after the two rounds of optimizations, there are only 2 queries left that need to be actually evaluated.

#### 3.4.4 Discussion

Comparison with Classic Data-flow Analysis. Despite the similarities between our define-use analysis and the traditional reaching-definition analysis, there are a couple of critical differences. First, the two analyses work at different granularities. The traditional data-flow analysis performs at the instruction level, while ours is applied at the query level. Each query itself may be implemented by a series of low-level instructions. Second, the traditional data-flow analysis operates on the control-flow graph, which may consist of cycles and take several iterations to converge. By contrast, our analysis works on a sequence of queries which imposes no "backward" control flows.

**Potential Extension**. Note that the ideas of query sequence analysis and transformation are not limited to the basic query semantics. It may benefit other batch-based query processing systems that may involve more complicated query structures as well. Consider a more advance query  $I(key_1, S(key_2))$ . The query is to insert/update  $key_1$  with the value drawn from  $key_2$ . In this case, the length of a QUD goes beyond 2.

# 3.5 Integration

To evaluate the proposed analysis and transformation, we integrate QTrans into an existing latch-free B+ tree query processing system – PALM tree [170] (see Section 3.2.2). To maximize the benefits, this section also describes a parallel implementation of QTrans and optimizations across batches.

Algorithm 2 One-Pass QSAT (for queries of the same key)

```

1: q_o = null

\triangleright the last defining query

\triangleright number of search queries

2: n_s = 0

3: I = \{\}

\triangleright a list of useful queries & operations

4: for q_i in \{q_n \cdots q_1\} do

if q_i is a search query then

5:

6:

n_{s} + +

7:

else if q_i is an insert or delete query then

if n_s > 0 then

8:

I.add(INFER\_AND\_RETURN(q_i, n_s))

9:

10:

n_s = 0

11:

if q_o = null then

12:

q_o = q_i

13: if n_s > 0 then

14:

\triangleright no defining query for the last n_s queries

15:

I.add(SEARCH_AND_RETURN(q_n, n_s))

16: if q_o = null then

17:

I.add(q_o)

18: return I

```

# 3.5.1 Parallel Intra-Batch Integration

The QTrans described in Section 4 applies optimizations sequentially over the sequence of queries. However, in the actual setting of latch-free B+ tree query processing, queries in a batch are processed in parallel for maximum performance on parallel processors. To match with the intra-batch parallel query processing scheme, we next present a parallel design of QTrans.

Given a batch of queries, the parallel QTrans creates a pool of threads based on the number of available cores N (part of latch-free query evaluation), then performs the query optimizations in two phases:

- **Phase-I**: First, partition the query batch evenly into *N mini-batches*. Then performs sequential QSAT over different mini-batches in parallel.

- **Phase-II**: Shuffle the queries generated by Phase-I based on the keys. Then let each thread perform a sequential QSAT over queries of the same key.

Figure 3.8 shows the new latch-free query evaluation with the two phases integrated.

After Phase-II, there will be at most one (defining) query left for each key. After applying the parallel *QTrans*, the following steps would be the same as the original latch-free query evaluation (see Figure 3.3).

Figure 3.8: Latch-Free Query Evaluation w/ QTrans

Advantages. Comparing with the original latch-free query evaluation (Figure 3.3), the new design (Figure 3.8) shows several advantages:

- *Faster sorting*. In the original design, query sorting is at the batch level. While in the new design, query sorting is only performed at the mini-batch level <sup>4</sup>.

- *Reduced leaf searches*. The original design searches for leaf nodes for every query in the batch; In comparison, the new design only searches for leaf nodes for each distinct key in the batch.

- **Reduced shuffle overhead**. Both the original and the new designs require to shuffle the queries in Stage 2 and Phase-II. However, in the new design, the shuffle overhead is lower, due to the query reduction in Phase-I.

<sup>&</sup>lt;sup>4</sup>For generality, query sorting is not shown in Figures 3.3 and 3.8.

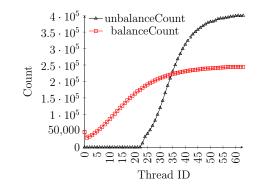

Load Balancing. Despite the above advantages, intra-batch optimization may suffer from a workload imbalance at Phase II. After Phase I, the number of remaining queries of different keys might be different. Further, after the query shuffling of Phase II, the number of keys mapped to different leaf nodes might also varies due to the skewed key distribution. Both cases can cause a load imbalance among worker threads. Note that the second case also occurs in the original design of query processing. Here, we address them with a lightweight workload balancing strategy.

Basically, our load balancing method leverages the prefix sum algorithm to calculate the starting query index for each thread, so that the number of queries assigned to each thread can be similar, but not necessarily the same. The assignment should not assign queries with different keys to different threads, which violates the correctness of BSP.

## 3.5.2 Inter-Batch Optimization

Beside intra-batch optimizations, this work also explores optimization opportunities across batches. However, it is challenging to implement inter-batch QSAT, because the intermediate results of query analysis will grow as more batches are analyzed. For example, a search query's corresponding defining query may appear in a much earlier batch. Keeping tracking all the information will overburden the QSAT, outweighing the benefits.

Instead, we adopt a more scalable strategy that is similar to the alternative solution mentioned in Section 4.4. Basically, it "simulates" the query evaluation at the inter-batch level on a different data structure. In this way, we only need to carry the "state" of key-value pairs from one batch to the next. The key is that the simulation must be faster than the actual query evaluation to bring in potential benefits. We achieve this with a top-K cache.

**Top-K Cache**. This is a small software cache with fixed number of entries – K entries. This design minimizes the costs of read/write operations. The cache can be implemented with a hash table, where the key-value pairs perfectly match with the B+ tree key-value pairs. As the number of entries is fixed, the hash function can be designed in an efficient way so that hashing conflicts can be minimized or even avoided. The entries in the top-K cache can be pre-populated with training data and periodically updated with testing data using various cache replacement policies (e.g., LRU).

To integrate the inter-batch optimization in the query evaluation system, we place the top-K cache operations in Stage 1 right after Phase II (see Figure 3.8). At this moment, the redundant and useless queries within the batch have been eliminated, hence the cache operations will be reduced to a minimum – only proportional to the number of distinct keys in the batch.

# 3.6 Evaluation

This section evaluates the efficiency and effectiveness of QTrans for optimizing the latchfree B+ query processing.

### 3.6.1 Methodology

We use an open-source implementation of latch-free B+ query processing system <sup>5</sup> as the baseline, which follows the design of PALM tree querying system [170]. It supports SIMD operations for key search within a tree node. *QTrans* is implemented in C++ language with the use of Pthread for multicore programming and is then integrated into PALM tree, serving as the optimized querying system.

**Platform**. We evaluate B+ tree query processing on the latest version of Xeon Phi, Knights Landing. Our Xeon Phi is a 64-core 7210 processor, used as a CPU, running at 1.3 GHz with 1M L2 cache shared between two cores, supporting 512-bit AVX512 instructions.

**Datasets**. To evaluate our query sequence optimization, we build B+ trees based on the unique keys from four synthetic datasets (with configurations the same as those in [170])

<sup>&</sup>lt;sup>5</sup>https://github.com/runshenzhu/palmtree

and two realistic datasets:

- gaussian: the keys of queries follow the classic Gaussian distribution with parameters  $\mu = N * 0.5, \ \delta = \mu * 0.5\%$ , where N is the range of queries;

- self-similar: the keys follow 80-20 rule, which means 80% queries cover 20% range of queries [76];

- zipf: the keys follow Zipfian [76] with  $\theta = 1.0$ ;

- uniform: the keys are uniformly distributed;

- ycsb: Yahoo! Cloud Service Benchmark (YCSB) [45] that is used to evaluate the performance of cloud systems. It includes Zipfian (ycsb-zipf) and latest (ycsb-latest); Note that zipf and ycsb-zipf are different in terms of the parameter settings.

- taxi: NYC taxi data published by New York City Taxi & Limousine Commission, containing the yellow and green trips in New York City at different time<sup>6</sup>.

All key distributions except uniform are skewed. The size of our input queries, the configuration of trees, and the input query distributions are summarized in Table 3.1. **Table 3.1**: Dataset configurations

| Dataset      | #queries         | #uniq-key       | parameters                             |

|--------------|------------------|-----------------|----------------------------------------|

| Gaussian     | 100M             | 50M             | $\mu = N * 0.5,  \delta = \mu * 0.5\%$ |

| Self-similar | 100M             | 50M             | 80-20 rule                             |

| Zipfian      | 100M             | 50M             | $\theta = 1$                           |

| Uniform      | 100M             | 50M             | /                                      |

| YCSB-latest  | 30M              | 10M             | /                                      |

| YCSB-zipfian | 30M              | 10M             | $\theta = 0.99$                        |

| Taxi         | $13.9\mathrm{M}$ | $4.1\mathrm{M}$ | /                                      |

# 3.6.2 Performance and Scalability

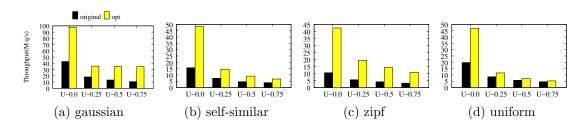

Synthesized Data. Figure 3.9 compares the original B+ tree processing with the one optimized with *QTrans* on four synthetic datasets (i.e., gaussian, self-similar, zipf and

<sup>&</sup>lt;sup>6</sup>http://www.nyc.gov/html/tlc/html/about/trip\_record\_data.shtml

Figure 3.9: Overall throughput improvement. x-axis: update ratios; y-axis: throughput of queries.

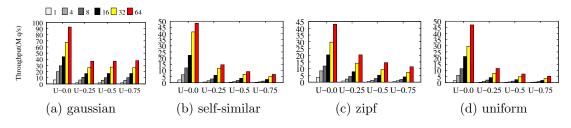

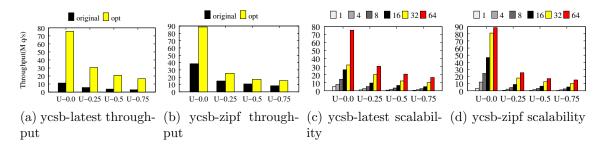

Figure 3.10: Throughput scalability. x-axis: update ratios; y-axis: throughput of queries. uniform) in terms of throughputs. For each distribution, the update ratio (i.e., the ratio of insert and deletion queries) changes from 0% to 75%. For all distributions, the one with *QTrans* (i.e., opt) shows better throughput, with up to 4.05X improvement (occurs on zipf dataset).

Specifically, for all datasets, the throughput improvement is higher when the update ratio is lower. Even for the uniform dataset, the throughput improvement reaches 2.37X. This is because *QTrans* handles all FIND queries in stage 1, thus avoiding the time consuming stage 2 in the original design. When the update ratio is greater than 0%, for the skewed datasets, such as gaussain, zipf, and self-similar, the throughput improvement

Figure 3.11: YCSB overall throughput and scalability. x-axis: update ratios; y-axis: throughput of queries.

Figure 3.12: Taxi throughput and scalability.

Figure 3.13: self-similar (U-0.25) leaf operations