#### Washington University in St. Louis

### Washington University Open Scholarship

**Engineering and Applied Science Theses &** Dissertations

McKelvey School of Engineering

Summer 8-15-2020

## Domain Specific Computing in Tightly-Coupled Heterogeneous **Systems**

Anthony Michael Cabrera Washington University in St. Louis

Follow this and additional works at: https://openscholarship.wustl.edu/eng\_etds

Part of the Computer Engineering Commons, and the Computer Sciences Commons

#### **Recommended Citation**

Cabrera, Anthony Michael, "Domain Specific Computing in Tightly-Coupled Heterogeneous Systems" (2020). Engineering and Applied Science Theses & Dissertations. 584. https://openscholarship.wustl.edu/eng\_etds/584

This Dissertation is brought to you for free and open access by the McKelvey School of Engineering at Washington University Open Scholarship. It has been accepted for inclusion in Engineering and Applied Science Theses & Dissertations by an authorized administrator of Washington University Open Scholarship. For more information, please contact digital@wumail.wustl.edu.

#### WASHINGTON UNIVERSITY IN ST. LOUIS

James McKelvey School of Engineering and Applied Science Department of Computer Science and Engineering

Dissertation Examination Committee:

Roger Chamberlain, Chair

Jonathan Beard

Jeremy Buhler

Ron Cytron

William Richard

Domain Specific Computing in Tightly-Coupled Heterogeneous Systems by

Anthony Michael Cabrera

A dissertation presented to The Graduate School of Washington University in partial fulfillment of the requirements for the degree of Doctor of Philosophy

> August 2020 Saint Louis, Missouri

# Table of Contents

| List of          | Figures                                           | $\mathbf{v}$ |

|------------------|---------------------------------------------------|--------------|

| List of          | Tables                                            | viii         |

| Ackno            | ledgments                                         | ix           |

| Abstra           | t                                                 | xiii         |

| Chapt            | 1: Introduction                                   | 1            |

| 1.1              | Research Questions                                | 5            |

| 1.2              | Contributions                                     | 5            |

| 1.3              | Outline                                           | 6            |

| Chapt            | 2: Background and Related Work                    | 7            |

| 2.1              | Domain Specific Computing                         | 7            |

| 2.2              | Data Integration                                  | 8            |

| 2.3              | Quantitative Characterization Techniques          | 10           |

| 2.4              | FPGA                                              | 11           |

|                  | 2.4.1 Intel HARPv2                                | 13           |

|                  | 2.4.2 HARP for Acceleration                       | 14           |

|                  | 2.4.3 Designing Kernels with OpenCL               | 15           |

|                  | 2.4.4 High Level Synthesis and Design             | 19           |

| $\mathbf{Chapt}$ | 3: DIBS: A Data Integration Benchmarking Suite    | 21           |

| 3.1              | Overview of Benchmark Suite and Integration Tasks | 25           |

| 3.2              | Benchmark Application Descriptions                | 26           |

|                  | 3.2.1 Computational Biology                       | 26           |

|                  | 3.2.2 Image Processing                            | 28           |

|                  | 3.2.3 Enterprise                                  | 31           |

|                  | 3.2.4 Internet of Things (IoT)                    | 32           |

|                  | 3.2.5 Graph Processing                            | 34           |

| 3.3              | Characterization of Data Integration Tasks        | 35           |

|                  | B.3.1 Locality                                    | 36           |

|                  | 3.3.2 Determinism/Branch Entropy                  | 38           |

|                | 3.3.3 Instruction Mix                                             | 38         |

|----------------|-------------------------------------------------------------------|------------|

| 3.4            | Characterization Methods                                          | 39         |

| 3.5            |                                                                   | 41         |

|                |                                                                   | 42         |

|                |                                                                   | 45         |

|                | 1 0                                                               | 48         |

|                |                                                                   | 51         |

| 3.6            |                                                                   | 52         |

| 5.0            | Conclusion                                                        | 02         |

| Chapte         | er 4: Multi-spectral Reuse Distance: Divining Spatial Information |            |

| fron           | n Temporal Data                                                   | 54         |

| 4.1            | The Data Movement Problem                                         | 55         |

| 4.2            | Methods                                                           | 57         |

|                |                                                                   | 58         |

|                | 4.2.2 Reuse Distance                                              | 58         |

|                |                                                                   | 60         |

|                |                                                                   | 62         |

| 4.3            | v 1                                                               | 63         |

| 1.0            |                                                                   | 63         |

|                | 1 0                                                               | 68         |

|                |                                                                   | 71         |

| 4.4            | ·                                                                 | 71         |

| 4.4            | Conclusion                                                        | 11         |

| Chapte         | er 5: Evaluating Portability and Performance of OpenCL FPGA       |            |

| $\mathbf{Ker}$ | nels on Intel HARPv2                                              | <b>7</b> 5 |

| 5.1            | Methods                                                           | 77         |

|                | 5.1.1 Needleman-Wunsch                                            | 78         |

|                | 5.1.2 Description of Each Kernel Version                          | 79         |

|                |                                                                   | 83         |

|                | 5.1.4 Shared Virtual Memory                                       | 86         |

| 5.2            | Ÿ                                                                 | 87         |

|                |                                                                   | 87         |

|                |                                                                   | 91         |

|                | 5.2.3 SVM Performance                                             | 94         |

| 5.3            | Conclusion                                                        | 96         |

|                |                                                                   |            |

| Chapte         | er 6: Designing Domain Specific Compute Systems                   | 98         |

| 6.1            |                                                                   | .00        |

|                | 6.1.1 Clustering of Domain Applications                           | .00        |

|                | 6.1.2 Evaluating the Hardware                                     | 01         |

|                | 6.1.3 Kernel Development                                          | 02         |

|                | 6.1.4 Hardware Design Parameters                                  | 03         |

| 6.2            | Kernels 1                                                         | $\Omega 4$ |

|        | 6.2.1   | ebcdic_txt                                                                       | 106 |

|--------|---------|----------------------------------------------------------------------------------|-----|

|        | 6.2.2   | $idx\_tiff \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$       | 108 |

|        | 6.2.3   | fix_float                                                                        | 110 |

|        | 6.2.4   | $edgelist\_csr  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 111 |

|        | 6.2.5   | 2bit_fa                                                                          | 113 |

|        | 6.2.6   | fa_2bit                                                                          | 115 |

| 6.3    | Other   | Design Considerations                                                            | 117 |

|        | 6.3.1   | Overlapping Data Transfer and Execution                                          | 117 |

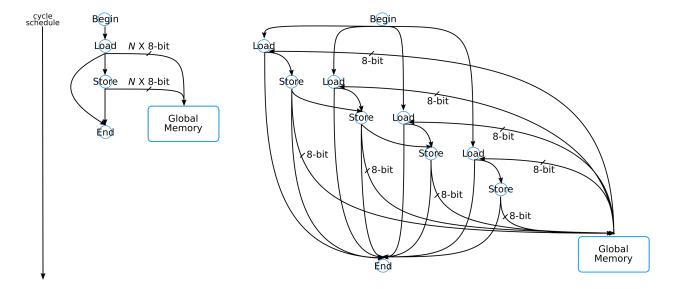

|        | 6.3.2   | Visualizing the Hardware                                                         | 118 |

|        | 6.3.3   | Widening the Data Type                                                           | 121 |

| 6.4    | Result  | S                                                                                | 123 |

|        | 6.4.1   | Design Space Search Sweeps                                                       | 124 |

|        | 6.4.2   | MWI versus SWI Implementations                                                   | 135 |

|        | 6.4.3   | Results of Widening The Datatype                                                 | 141 |

| 6.5    | Conclu  | asion                                                                            | 144 |

| Chapte | er 7: C | Conclusion and Future Work                                                       | 145 |

| 7.1    | Future  | e Work                                                                           | 147 |

| Refere | nces .  |                                                                                  | 150 |

| Vita   |         |                                                                                  | 163 |

# List of Figures

| Figure 2.1: | FPGA Block Diagram                                         | 12 |

|-------------|------------------------------------------------------------|----|

| Figure 2.2: | HARPv2 vs. PCIe Card FPGA                                  | 14 |

| Figure 2.3: | NDRange vs. SWI Block Diagram                              | 17 |

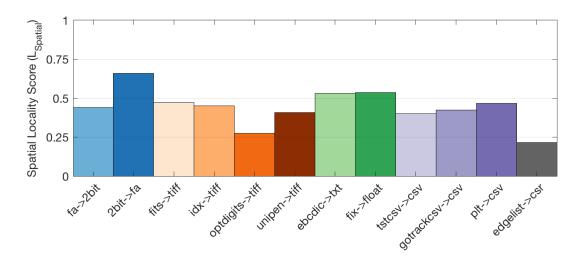

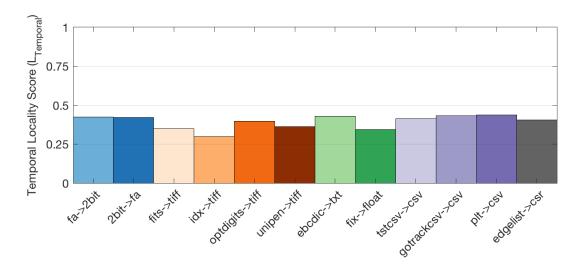

| Figure 3.1: | Spatial Locality Measure                                   | 42 |

| Figure 3.2: | Cumulative Sum of Memory References Across Strides         | 43 |

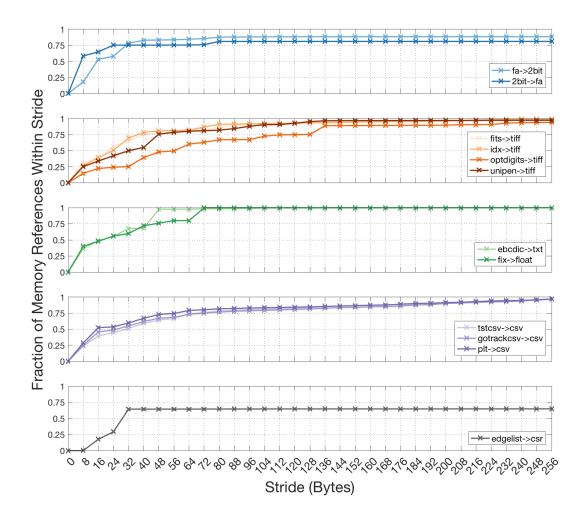

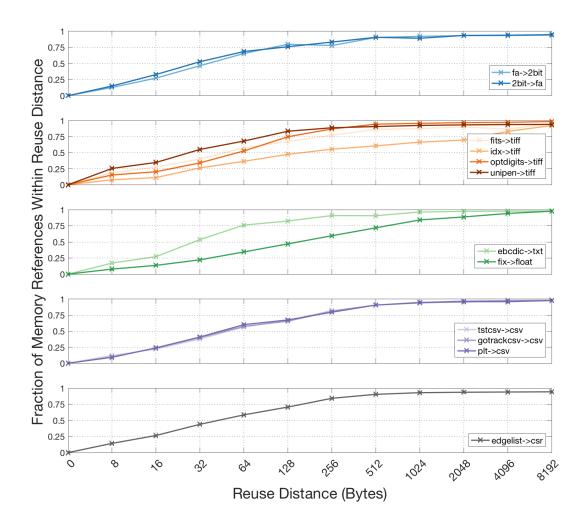

| Figure 3.3: | Temporal Locality Measure                                  | 45 |

| Figure 3.4: | Cumulative Sum of Memory References Across Reuse Distances | 46 |

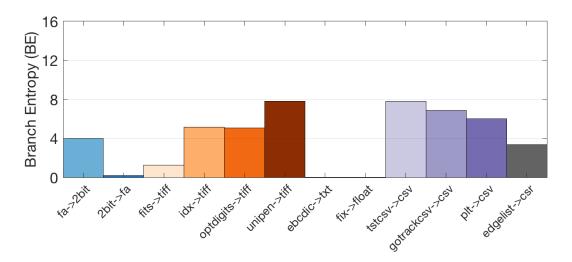

| Figure 3.5: | Branch Entropy Measure                                     | 47 |

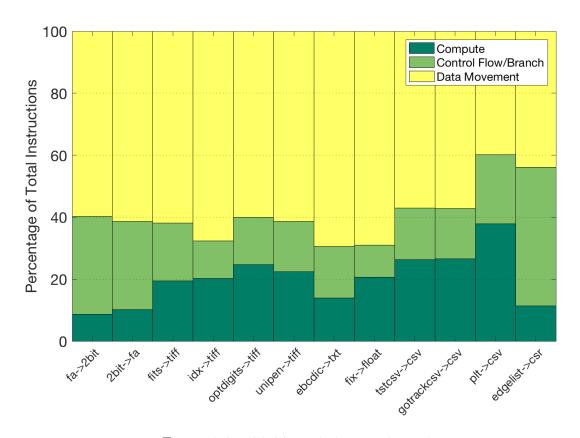

| Figure 3.6: | x86-64 Static Instruction Mix                              | 48 |

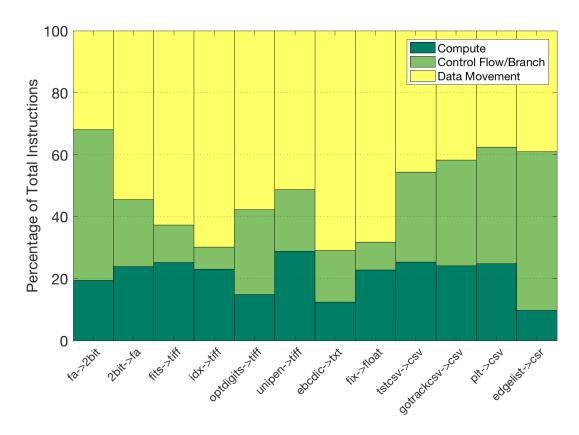

| Figure 3.7: | x86-64 Dynamic Instruction Mix                             | 49 |

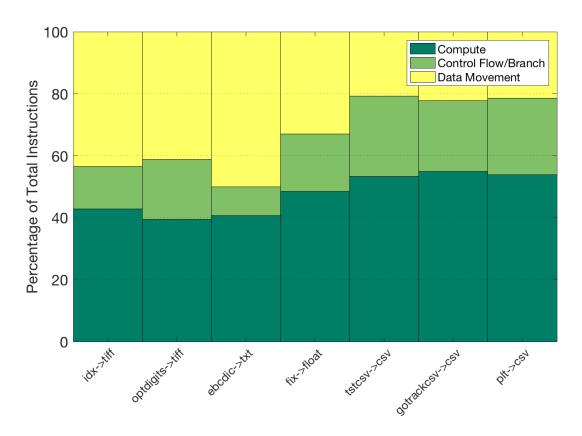

| Figure 3.8: | AArch64 Dynamic Instruction Mix                            | 50 |

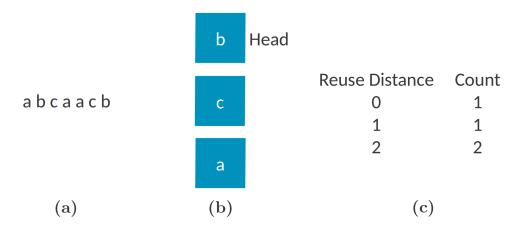

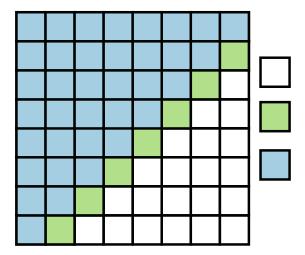

| Figure 4.1: | Reuse Distance Basics                                      | 59 |

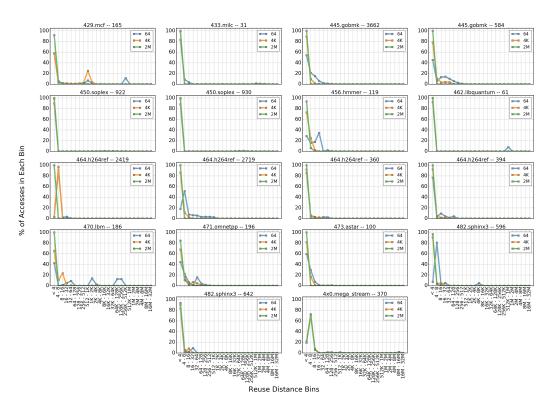

| Figure 4.2: | Reuse Distance Signatures                                  | 64 |

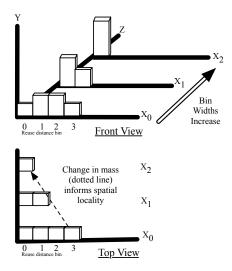

| Figure 4.3: | Intuition for Mass Shift Proof                             | 67 |

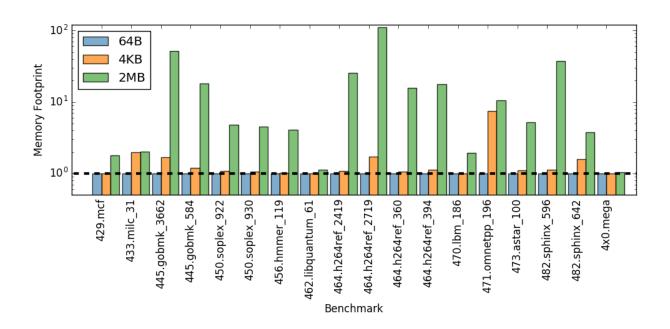

| Figure 4.4: | Memory Footprint Results                                   | 72 |

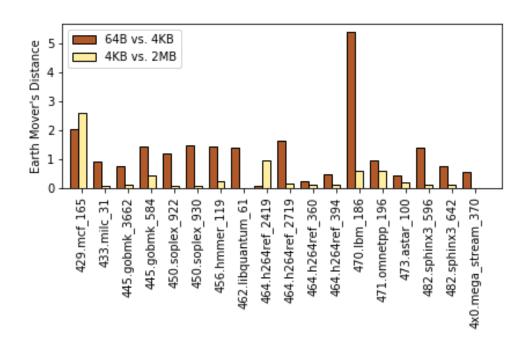

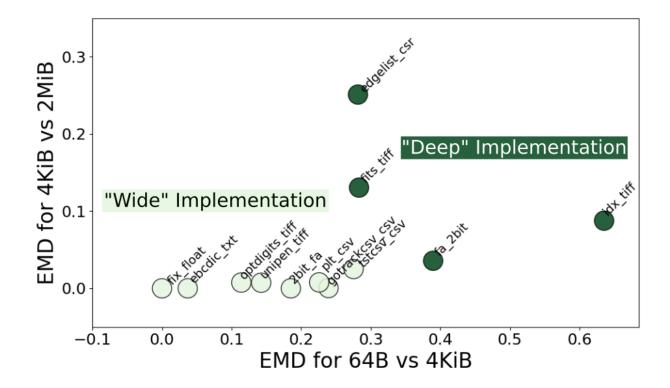

| Figure 4.5: | Earth Mover's Distance Results                             | 72 |

| Figure 5.1. | Dynamic Programming Evample                                | 70 |

| Figure 5.2:  | Diagonal Parallelism Illustration                             | 81  |

|--------------|---------------------------------------------------------------|-----|

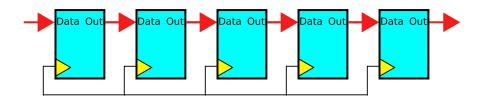

| Figure 5.3:  | Shift Register Example                                        | 83  |

| Figure 5.4:  | Staircase Shift Registers                                     | 84  |

| Figure 5.5:  | Exploiting Diagonal Parallelism and Staircase Shift Registers | 85  |

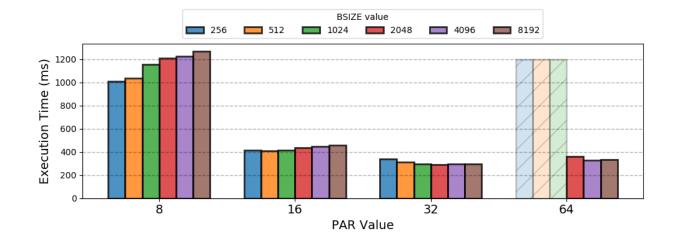

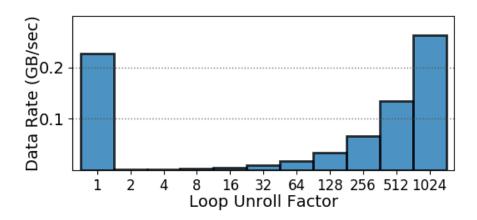

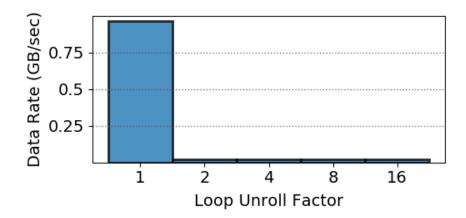

| Figure 5.6:  | NW Kernel Hardware Design Space Search                        | 91  |

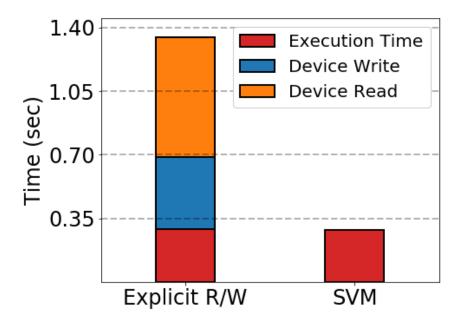

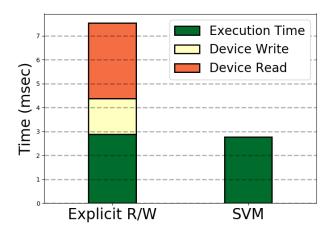

| Figure 5.7:  | Shared Memory Benefit                                         | 94  |

| Figure 6.1:  | k-means Clustering of the DIBS Applications                   | 101 |

| Figure 6.2:  | Width vs. Depth Execution Models                              | 102 |

| Figure 6.3:  | Confirmation of Shared Memory Benefit                         | 118 |

| Figure 6.4:  | CDFGs and Cycle Schedules                                     | 118 |

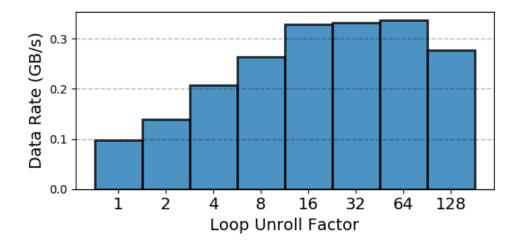

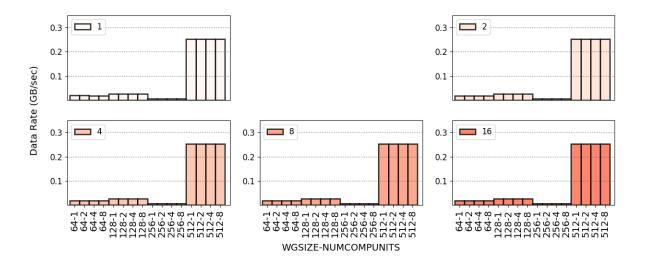

| Figure 6.5:  | idx_tiff SWI Results                                          | 124 |

| Figure 6.6:  | fix_float SWI Results                                         | 125 |

| Figure 6.7:  | edgelist_csr SWI Results                                      | 125 |

| Figure 6.8:  | 2bit_fa SWI Results                                           | 126 |

| Figure 6.9:  | ebcdic_txt SWI Results                                        | 127 |

| Figure 6.10: | fa_2bit SWI Results                                           | 128 |

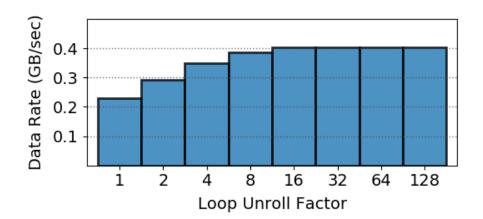

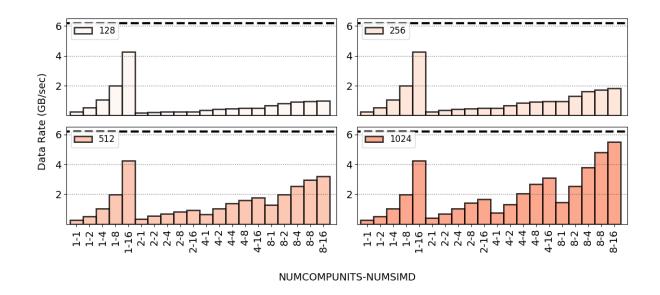

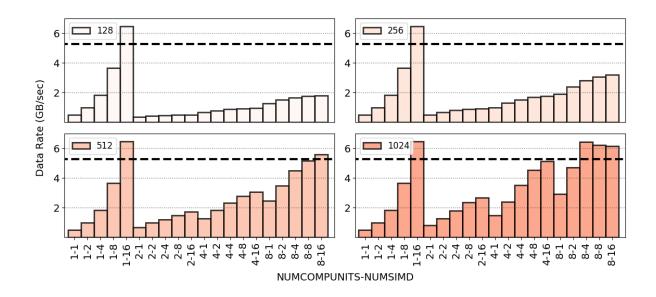

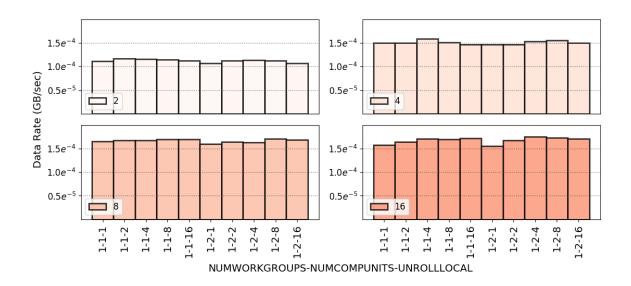

| Figure 6.11: | ebcdic_txt MWI Results                                        | 129 |

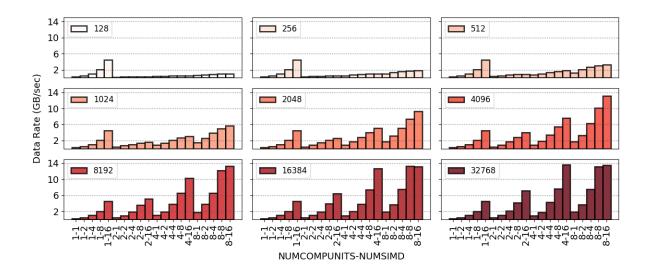

| Figure 6.12: | fix_float MWI Results                                         | 129 |

| Figure 6.13: | edgelist_csr MWI Results                                      | 130 |

| Figure 6.14: | 2bit_fa MWI Results                                           | 130 |

| Figure 6.15: | idx_tiff MWI Results                                          | 132 |

| Figure 6.16: | fa_2bit MWI Results                                           | 133 |

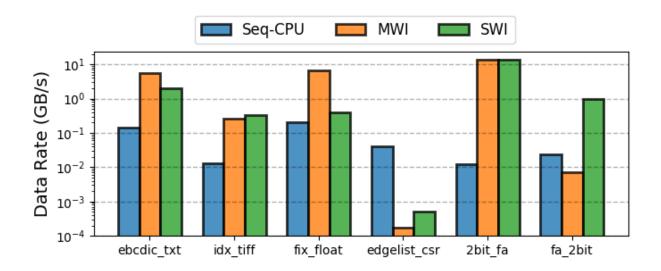

| Figure 6.17: | CPU vs. MWI vs. SWI Results                                   | 136 |

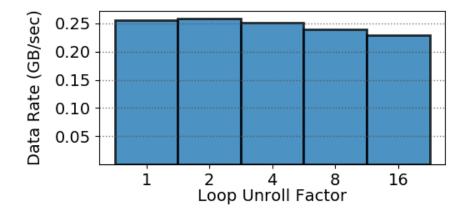

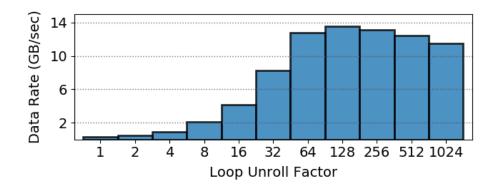

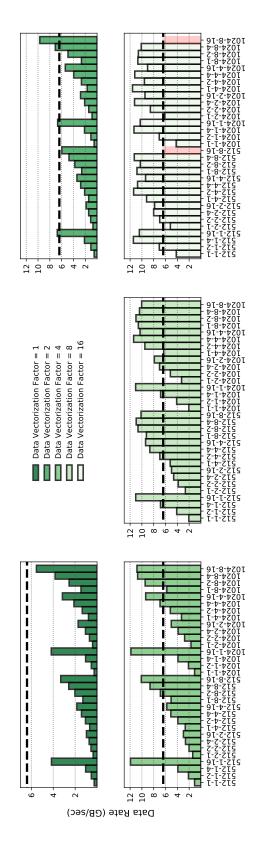

| Figure 6.18: | Data Type Vectorization Design Space Search | 139 |

|--------------|---------------------------------------------|-----|

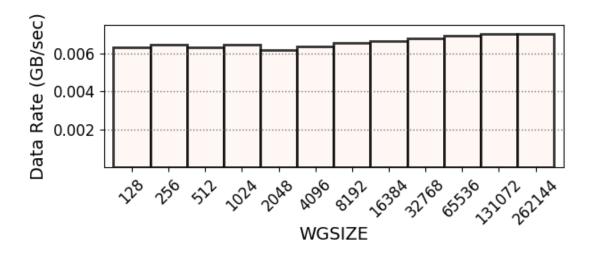

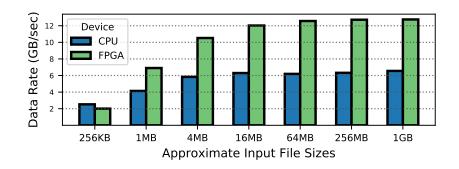

| Figure 6.19: | Input File Size Sweep                       | 141 |

# List of Tables

| Table 3.1: | Data Integration Task Classification                              | 26 |

|------------|-------------------------------------------------------------------|----|

| Table 3.2: | Experimental Machine Specifications                               | 40 |

| Table 3.3: | Throughput Results                                                | 41 |

| Table 5.1: | HARPv2 vs. PCIe Card Results                                      | 88 |

| Table 5.2: | Hardware Design Space Search for NW Kernels                       | 90 |

| Table 6.1: | MWI Design Knob Trend                                             | 31 |

| Table 6.2: | Most Performant MWI and SWI Configurations                        | 37 |

| Table 6.3: | Utilization and Performance Results for Data Type Vectorization 1 | 40 |

## Acknowledgments

Though this dissertation bears my name as sole author, this process has hardly been a solo endeavor. There are a number of people who have been in my corner throughout my life, and without them, this work would not have been possible.

First, I would like to thank my parents, Patrick and Annabelle Cabrera, and my brother, Chris Kramp, who have supported me throughout all of my endeavors. Through the baseball games, orchestra concerts, and all of my academic pursuits, they were always behind me, supporting me every step of the way and letting me know how proud they were. I could not have gotten to where I am today without their love and support.

My advisor, Dr. Roger Chamberlain, has been invaluable in so many ways during my PhD journey. He took me on as a graduate student in my second year, and trusted and respected me as if I had already been his student for years. He has been nothing short of extraordinary as a mentor, and I am thankful for his guidance. Even if it was staying up late for a paper deadline, Roger would always make time for me when I asked, and that is something that I will always appreciate.

There have also been a number of other faculty and colleagues that I would like to acknowledge. My former research advisor, Dr. Viktor Gruev, gave me my first research opportunity

as an undergraduate and is what ultimately lead me to pursue a PhD. My committee members, Drs. Jonathan Beard, Jeremy Buhler, Ron Cytron, and William Richard have all played pivotal roles in my formation as a researcher, even before they agreed to serve on my committee. My colleagues in the CSE department at WUSTL, including Clayton Faber and Drs. Steve Cole, Missael Garcia, Tim York, and many others, have been incredibly insightful, and have helped shaped my development as a researcher.

I must also thank the faculty at Hendrix College, specifically Drs. Gabe Ferrer, Karen Griebling, Damon Spayde, and Todd Tinsley, for their enthusiasm for teaching. They made learning the hard stuff fun, and they showed me what happens when faculty truly invest in their students' success.

During the summers of my third and fourth years, I had the opportunity to intern and work with some great people. I want to thank Dr. Jonathan Beard for taking me on as a research intern at ARM, and for leading me through the nasty details of modern memory subsystems and the field of High Performance Computing. Thanks also to Dr. Christine Harvey, John Hilbing, Andrew van Overloop, Rose Schneider, and Dan Aiello for giving me the opportunity to work at MITRE, and their constant support during my time as an intern and beyond.

For all of the people I have had the pleasure of calling friend over the past few years, I am also thankful. To Marcus Brown, Emily Murphy, Katy O'Keefe, and Page Vick, I am glad to have gotten to know you from the third grade to the present, and I am thankful that

we still continue to keep in touch and lift each other up. To my Hendrix friends, namely

Stephen Borutta, Ernest Perez, and Drs. Sam Bondurant, William Haden Chomphosy, Sam

Fullerton, Lance Riley, Spencer Sanson, and Erik Urban, our friendships are ones that I will

continue to cherish.

Finally, I want to thank my wife, Jillian Smith, for whom I am eternally grateful. She has

shown me a level of affection, patience, and support that I had not known was possible. She

has been a wonderful cat mom to Lil' Sebastian and Ann Purrkins. She welcomed me into

her life without hesitation, and I am grateful to have a second family in Jane, Ralph, Ben,

and Theo Smith and Shelley Bryant. Jillian has been there for me during my highest highs

and lowest lows, and she has never stopped professing how proud she is and how much she

believes in me. This achievement is just as much hers as it is mine. I love you, Jillian, and

I am fortunate to have been blessed with such a loving and supportive partner.

Anthony Michael Cabrera

Washington University in Saint Louis

August 2020

xi

Dedicated to Mom, Dad, and Jillian.

#### ABSTRACT OF THE DISSERTATION

Domain Specific Computing in Tightly-Coupled Heterogeneous Systems by

Anthony Michael Cabrera

Doctor of Philosophy in Computer Engineering

Washington University in St. Louis, 2020

Professor Roger Chamberlain, Chair

Over the past several decades, researchers and programmers across many disciplines have relied on Moores law and Dennard scaling for increases in compute capability in modern processors. However, recent data suggest that the number of transistors per square inch on integrated circuits is losing pace with Moores laws projection due to the breakdown of Dennard scaling at smaller semiconductor process nodes. This has signaled the beginning of a new "golden age in computer architecture" in which the paradigm will be shifted from improving traditional processor performance for general tasks to architecting hardware that executes a class of applications in a high-performing manner. This shift will be paved, in part, by making compute systems more heterogeneous and investigating domain specific architectures. However, the notion of domain specific architectures raises many research questions. Specifically, what constitutes a domain? How does one architect hardware for a specific domain?

In this dissertation, we present our work towards domain specific computing. We start by constructing a guiding definition for our target domain and then creating a benchmark suite of applications based on our domain definition. We then use quantitative metrics from the literature to characterize our domain in order to gain insights regarding what would be most beneficial in hardware targeted specifically for the domain. From the characterization, we learn that data movement is a particularly salient aspect of our domain. Motivated by

this fact, we evaluate our target platform, the Intel HARPv2 CPU+FPGA system, for architecting domain specific hardware through a portability and performance evaluation. To guide the creation of domain specific hardware for this platform, we create a novel tool to quantify spatial and temporal locality. We apply this tool to our benchmark suite and use the generated outputs as features to an unsupervised clustering algorithm. We posit that the resulting clusters represent sub-domains within our originally specified domain; specifically, these clusters inform whether a kernel of computation should be designed as a widely vectorized or deeply pipelined compute unit. Using the lessons learned from the domain characterization and hardware platform evaluation, we outline our process of designing hardware for our domain, and empirically verify that our prediction regarding a wide or deep kernel implementation is correct.

## Chapter 1

## Introduction

Over the past several decades, researchers and programmers across many disciplines have relied on two trends in computing. The first is that the number of transistors on integrated circuits doubles roughly every two years. The other is that the relationship between a transistor's feature size and power consumption and switching speed are constant. Together, these insights have guided the semiconductor industry towards creating smaller transistors to lower power consumption, raise clock frequencies, and increase compute capability per unit area.

These two observations, known as Moore's law [115] and Dennard scaling [12], respectively, have been the driving force behind aggressively scaling semiconductor process technologies. This allows for increases in compute capability in modern processors. However, recent data and results show that the number of transistors per square inch on an integrated circuit is losing pace with Moore's law's projection, and that second-order effects of extreme transistor scaling are cancelling out the effect of lower power consumption for smaller transistors. The impending end of Moore's law due to the breakdown of Dennard scaling will mark the end of an era characterized by relying on transistor scaling and increased clock frequencies to improve performance gains.

In response to this, modern computing systems are becoming more architecturally diverse. Architectural diversity includes any type of processing element within a computing system other than the traditional processor core. The goal of introducing heterogeneity into a computing system is to accelerate compute tasks that would otherwise be handled by a traditional processor core. One of the earliest examples of this is Intel's 8087 numeric data processor that served as a co-processor dedicated to speeding up floating point computations [102]. In the spirit of this type of hardware acceleration, modern systems are increasingly adding heterogeneity through incorporating hardware accelerators i.e., digital signal processors (DSPs), graphics processing units (GPUs), or field-programmable gate arrays (FPGAs). GPUs in particular are gaining traction, finding use in applications such as convolutional neural networks [74], molecular simulations [1], and protein sequence alignment [132].

In their 2017 ACM A.M. Turing Award speech, John Hennessey and Dave Patterson espoused the importance of architecturally diversity. They address the challenges that arise from the end of Moore's law and Dennard scaling and use this to signal a new "golden age of computer architecture". However, the onus of research in a post-Moore's law landscape was not solely placed on computer architects. In order to create effective compute solutions, researchers must embrace working across the hardware and software stack through hardware-software co-design. Additionally, they suggest that the path to a post-Moore's law world is paved, in part, by domain specific computing. This key idea means shifting the paradigm of improving general purpose processors that are good at many compute tasks towards building hardware and surrounding infrastructure for processors that do fewer things but in a high-performing manner. Between a spectrum bounded by general purpose processors and application specific integrated circuits (ASICs), domain specific architectures would occupy the middle ground by developing an architecture to accelerate a given domain or class of applications.

One way to help facilitate this shift is by using field-programmable gate arrays (FPGAs) as a platform for domain specific computing. FPGAs are a special type of integrated circuit that can be programmed to implement a desired application in hardware. Historically, FPGAs have been used for prototyping hardware or microarchitectures or as a lower-cost solution to application specific integrated circuits (ASICs). The widespread use of FPGAs, though nascent, has been burgeoning in recent years due to increased interest in industry. This forward progress is reflected by companies like Amazon and Microsoft equipping their data center nodes with FPGAs [107, 25, 5] and Intel acquiring FPGA manufacturer Altera. Additionally, there is a growing research trend toward harnessing the reconfigurability of FPGAs towards accelerating applications like neural networks [23, 43, 143], biocomputation [62, 89, 94], and many other applications [88, 117, 125, 142, 150]. One of the key ideas we present in this thesis, though, is designing techinques and tools using FPGAs to accelerate classes of applications, rather than individual applications.

A common way to incorporate hardware accelerators like GPUs and FPGAs into a computer system is to attach them through a PCIe bus. Accelerators attached in this way, though, incur considerable overhead for data movement and keeping the memory between the host and accelerator systems coherent. Recently, Intel has developed a system to address these issues by incorporating both a multicore Xeon CPU and Arria 10 FPGA into the same chip package and connected via high-speed and coherent interconnect. This particular project is known as the Heterogeneous Accelerator Research Program, or HARP, and it is the platform we use in this dissertation for developing domain specific hardware. We describe the HARP hardware futher in Section 2.4.1.

One of the steepest barriers to using FPGAs, though, is expressing a design in the first place using traditional hardware description languages (HDLs) like VHDL and Verilog. This

requires the ability to orchestrate a design at the logic gate level and at a clock-cycle granularity. The HARP system is no exception to this rule. A current research direction in lowering the barrier is High Level Synthesis (HLS), which allows a programmer to express a kernel of computation in a higher level language like C or C++ for deployment onto an FPGA. (HLS is described further in Section 2.4.4.) This circumvents the problem of having to learn an HDL to express a kernel and its low level interfaces, reduces the amount that a programmer has to understand about FPGA microarchitecture, and abstracts away the lower level details of using FPGAs. In addition to being able to author designs using an HDL, Intel has provided the infrastructure to use the Intel FPGA OpenCL SDK for HLS FPGA development [61]. While there have been recent publications targeting the HARP system with a traditional FPGA design flow [4, 28, 117, 122, 135, 144], not much is known about the experience, feasibility, and performance of targeting a HARP system using OpenCL. Our work towards this combination is one of the contributions of this thesis; we show how to effectively utilize properties of the Intel HARPv2 (the second iteration of the Intel Heterogeneous Architecture Research Platform) and evaluate its effectiveness as a domain specific computing solution.

The overarching goal of this thesis is to develop a methodology for identifying a domain and to architect performant hardware for that domain. We first define the domain of data integration as a case study and define this domain using both qualitative and quantitative methods. From there, we will evaluate the hardware design process and performance of the Intel HARPv2 system. We target the HARPv2 system using the Intel FPGA SDK for OpenCL for hardware development, which allows us to author designs in a higher level language. We develop hardware design strategies specific to our target domain, as well as strategies for generally using OpenCL to target the HARPv2 system. In order to make quantitative hardware design choices, we create a tool called multi-spectral reuse distance,

whose outputs are used as features to cluster our applications and create sub-domains of our original domain. We posit that these sub-domains represent whether a particular application would benefit more from a widely vectorized or deeply pipelined implementation, and then empirically verify our position.

## 1.1 Research Questions

In this dissertation, we make progress towards answering the following questions:

- How does one define an application domain?

- How does one architect performant hardware on the Intel HARPv2 platform using OpenCL?

- How does one effectively architect domain specific hardware?

### 1.2 Contributions

In addressing these questions, we make the following specific contributions:

- The Data Integration Benchmarking Suite (DIBS), a suite of applications that represent data integration workloads across a variety of different application domains [22].

- Using known profiling techniques to quantitatively characterize the DIBS applications [22].

- A novel tool to measure the temporal and spatial locality of a given application [20].

- A performance and portability evaluation between OpenCL kernels synthesized for FPGAs attached via PCIe card and the Intel HARPv2 system [17].

- A method using control data-flow diagrams to inform design decisions at the OpenCL kernel level.

- A method for design space enumeration and search for the two OpenCL execution models [17, 19].

- Empirically-based techniques for designing kernels for the Intel HARPv2 platform [17].

- A set of OpenCL kernels designed to target the Intel HARPv2 platform [19].

- A method leveraging an unsupervised clustering algorithm to predict the most performant OpenCL execution model for a given kernel, and empirically validating the prediction [19].

### 1.3 Outline

The rest of this dissertation is structured as follows: Chapter 2 will cover related work and background information pertaining to domain specific computing, FPGAs, and HLS. Chapter 3 will introduce the domain of data integration, the Data Integration Benchmarking Suite, and our initial characterization of the applications. Chapter 4 will present multispectral reuse distance, a novel tool and methodology to quantitatively capture both spatial and temporal locality. Chapter 5 will present a performance and portability evaluation of the Intel HARPv2 system. Chapter 6 will outline our method of domain specific hardware design. Chapter 7 will conclude this dissertation and present our directions for future work.

## Chapter 2

## Background and Related Work

## 2.1 Domain Specific Computing

Early work in domain specific computing most resembling our approach has been done by Cong et al., in which they propose a heterogeneous processor consisting of both fixed cores and configurable fabric and perform a workload characterization on a set of domain applications in order to determine which components of those applications should be implemented on the various compute units [30]. Our work differs in that we are both targeting a different execution platform (the Intel HARPv2) and we are using HLS for application expression.

With the rise in machine learning, particularly neural networks, there has been hardware created for accelerating such workloads. The Tensor Processing Unit (TPU) [69] and the Intel Nervana NNP-T [140] are examples of such hardware for training and inference, respectively. Both feature custom multiply-accumulate units to handle GEMM operations that dominate convolutional neural network applications. Our work aims to address domains that aren't so clearly dominated by one aspect of the computation.

### 2.2 Data Integration

In this dissertation, the domain that we primarily focus on is that of data integration. The issue of data integration is universal to anyone working on data driven applications and can be troublesome to deal with, often taking time comparable to the actual computation of interest [90, 91]. In general, data integration is the process of taking input data in some initial form and shaping and preparing it into a suitable form required by downstream analyses, e.g., a genome sequence application that requires a *.fasta* file be converted to *.2bit*, or transforming the bounding box labels from the *MS-COCO* training dataset to the *KITTI* format because the front-end of the target neural network training system requires it. While definitions vary, we will use the definition presented in the Data Integration Benchmark Suite (DIBS) in Chapter 3.

The data integration problem has received considerable attention already in the research community. Quoting from Kandel et al. [70], "In spite of advances in technologies for working with data, analysts still spend an inordinate amount of time diagnosing data quality issues and manipulating data into a usable form. This process of 'data wrangling' often constitutes the most tedious and time-consuming aspect of analysis." Dasu and Johnson indicate that data reformatting and cleaning accounts for up to 80% of the development time and cost in data warehousing projects [34].

Customized Domain Specific Languages (DSLs) and graphical user interfaces (GUIs) exist that are designed explicitly for describing data transformation workflows. Examples from the ETL literature include AJAX [46], Potter's Wheel [108], ARKTOS [128], BPEL [39], Wrangler [71], and OptiWrangler [124]. Work has also considered finding the right transformations, helping address issues of data integrity and consistency. Guo et al. [53] describe a model that proactively suggests data transforms. In addition, there are commercial systems

available both to specify the workflows and to execute them (either on traditional multicores or, more recently, on map-reduce clusters). Examples here include IBM's InfoSphere and Informatica.

There are also a host of systems aimed at scientific data (e.g., see [2, 13, 16, 36, 101]). While there is significant disparity of data formats in many disciplines, biology [101] for example, other disciplines, such as ecology [13, 95], have a stronger culture of data description via XML and semantic ontologies, enabling a higher degree of automation in the specification of data transformations.

While there are any number of ways that data transformations can be specified, our general interest is in helping research groups compare implementations of systems that execute data transformations by providing a baseline implementation and its accompanying characterization. The classic way to do this is via a benchmark suite. Examples of benchmark suites in other fields include: the SPEC family<sup>1</sup>, including SPEC CPU2017 and SPECjvm2008; MiBench [56], for embedded systems; PARSEC [10], for parallel applications; MediaBench [81], for multimedia computations; Rodinia [26], for heterogeneous computing with GPUs; HiBench [58], for map-reduce data processing; MachSuite [109], for accelerator architectures; and CommBench [138], for network processing. We will use this benchmarking suite as our target domain for architecting domain specific hardware.

Poess et al. [106] have developed an enterprise-centric data integration benchmark, but do not speak to the more general data integration audience. Additionally, the characterization of their benchmark suite is limited only to scalability and runtime. To the best of our knowledge, we present the first benchmark suite that broadly characterizes data integration tasks.

<sup>1</sup>http://spec.org

## 2.3 Quantitative Characterization Techniques

Characterization of both temporal and spatial locality has a long history [38]. Metrics from the literature include [31, 55, 75, 78, 119, 120, 121, 133].

Reuse distance—defined initially by Mattson et al. [92] as stack distance—is frequently used as a measure of temporal locality. For example, Weinberg et al. [136] define a temporal locality measure that is the area under the reuse distance curve, with the reuse distance expressed using a log scale. This formulation has been used for the characterization of various benchmarks [22, 27, 99, 109, 127]. Reuse distance has been compared with spatial locality by previous authors [52, 147]. All of these authors owe the gestalt of their works to the observations of Spirn and Denning [121] who made some of the earliest observations of program locality. Gu et al. [52] observed reuse distance to be a measure of both temporal and spatial locality. They used reuse distance as a measure of spatial locality as we do, by altering the granularity of the data block size. They reason that varying the block size leaves temporal locality unchanged, so distinctions between two block sizes are due to spatial locality. These authors also propose a spatial locality score SLQ. Gupta et al. [55] propose a statistical model based on the idea of "near-future windows sizes." In contrast to this work, our methodology uses Earth Mover's Distance (EMD) [110] to provide a metric that gauges spatial locality when moving histograms of multi-spectral temporal reuse data.

While the approach we espouse in Chapter 4 is driven by empirical data, others have taken a more theoretical approach, using the cache oblivious model to determine data locality [118] and graph theoretic approaches (interval graphs) [9]. These methods are of [9]) the search for multiple cliques over the entire stream of allocations and accesses of a program. While these methods are intended to inform cache behavior, our methods are intended to be more

general. We also intend to be approximate; we feel that for many cases in real world decisions, a good fast answer is far better than a too-late exact answer.

Within Chapter 4, we make the claim that prefetching of data is a difficult problem. Mittal [96] provides an excellent overview of contemporary prefetching methods and results. Plainly speaking, the dynamic random access main memory (DRAM) of modern computers is yet another level of cache, managed by the operating system. This DRAM can be composed of many different types of memory technology, as well as having NUMA [79] characteristics. The authors make no claims of use directly as a model for prefetching, however, the proposed modeling methodology could be used to determine the optimal granularity of prefetch (in the case of memory systems) and also on the selection of cost function to drive the control process. Granularity of statistical prediction has a well known relationship with a prediction's accuracy [98] (e.g., very detailed predictions with more degrees of freedom often have more uncertainty) and we make no claim to this relationship, but we do hope that this method provides a means to more optimally use coarse grained prediction effectively (through better page sizing). The problem of data placement within a tiered and NUMA system is by no means new, and heavily related to data to disk optimization problems solved as examples in [80]. Regarding domain specific hardware design, we will use the technique outlined in Chapter 4 to generate feature data to identify sub-domains within our target data integration domain.

### 2.4 FPGA

Field Programmable Gate Arrays (FPGAs) are integrated circuits that include programmable logic blocks, hardened logic blocks such as Digital Signal Processors (DSPs) and floating point units (FPUs), block RAMs (BRAMs, and referred to as M20K blocks for Intel FPGAs), and

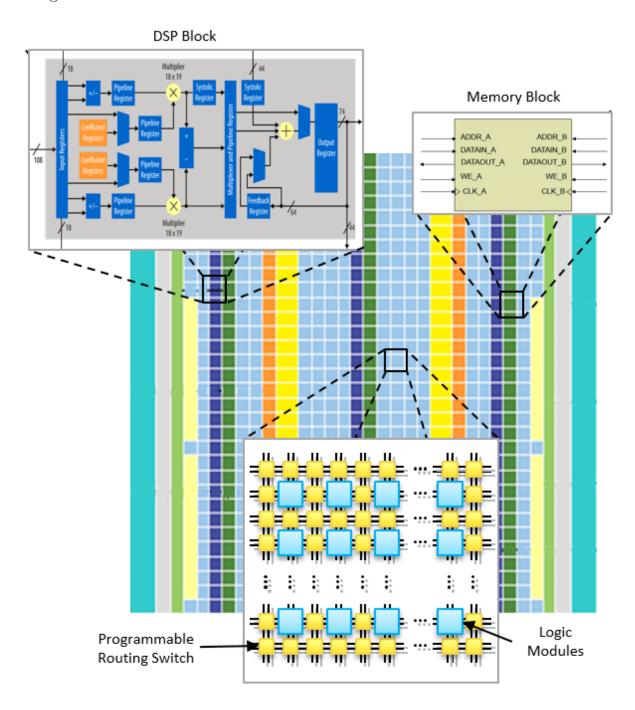

reconfigurable routing circuitry to connect these components together and to hardened I/O logic in order to interface with external hardware. A block diagram of an FPGA is shown in Figure 2.1.

Figure 2.1: A block diagram of an Intel FPGA [60].

FPGAs tend to occupy the middle ground between general purpose CPUs and application specific integrated circuits (ASICs) in terms of programmability, performance, and power consumption. FPGA developers traditionally design hardware using Hardware Description Languages (HDLs) such as VHDL or Verilog. This allows them to tailor hardware to a specific application. This usually results in better performance than CPUs. The effective use of hardware that is specific only to the problem also leads to lower power consumption.

#### 2.4.1 Intel HARPv2

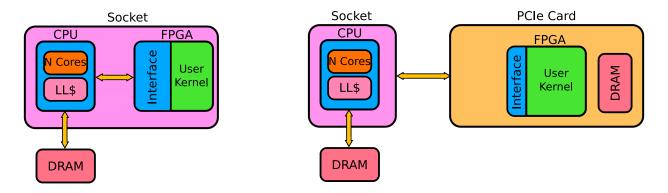

The second iteration of the Heterogeneous Architecture Research Platform (HARPv2) system incorporates a 14 core Intel Broadwell Xeon CPU with an Intel Arria 10 GX1150 in the same chip package, where both the CPU and FPGA share the same memory. The HARPv2 sstem serves as the target platform in this work. Relative to the Stratix V GX A7 in the HARPv1 system, the FPGA in HARPv2 has 1.06 times more M20K blocks, 1.82 times more logic blocks and registers, 5.93 times more DSP blocks, and is located on the same chip package as opposed to a different socket. Integrating the CPU and FPGA on the same package is different from traditional FPGA accelerator solutions that are connected via PCIe slot or on their own development board. A block diagram comparing the Intel HARPv2 system and the traditional PCIe card version are shown in Figure 2.2.

The FPGA is connected to the CPU through three physical channels: one through Intel's QuickPath Interconnect (QPI), and the other two through PCIe lanes. Intel also provides the low level interface hardware for the FPGA through their Board Support Package (BSP). Faict presents an excellent overview of the HARP system in [41].

Figure 2.2: Block diagrams of (left) the Intel HARPv2 system and (right) a traditional FPGA solution using a PCIe card.

#### 2.4.2 HARP for Acceleration

Since its inception, there have been many projects that have demonstrated the benefits of using the HARP system in a variety of different applications and domains. Podili et use the HARP as their experimental system in using Winograd FFTs to speed up convolutional layers in Convolutional Neural Networks [105]. Alves et al. utilize the lowlatency QPI channel for collision detection algorithms to demonstrate the HARP's feasibility for real-time applications [4]. Sidler et al. exploit the shared memory feature of the HARP system to reduce superfluous data movement in pattern matching for databases [117]. Stitt et al. develop a scalable window generator architecture for sliding window applications, which are a common pattern in FPGA design, to take advantage of the increased memory bandwidth in the HARPv2 system and reported future memory bandwidth increases for FPGAs [122]. Wang leverages the tighter coupling of CPU and FPGA in the HARP system as a heterogeneous platform for accelerating graph processing [135]. In all of these cases, though, custom RTL is written to express the hardware and low-level interfaces for the HARP system, which is a skill not generally in the toolbox of the modern software developer. In Chapter 5, we leverage OpenCL to allow a description of accelerator functions in C, which is a higher level language than an RTL description. Specifically, we will evaluate the performance and portability of OpenCL kernels that were originally intended for FPGAs attached via PCIe card.

#### 2.4.3 Designing Kernels with OpenCL

Traditionally, programming an FPGA requires domain specific knowledge of digital systems design, which is not a skill of most software developers. Also, the designs are historically expressed at the register-transfer level (RTL) using languages like VHDL, Verilog, or SystemVerilog. High level synthesis (HLS) addresses both of these issues. Specifically, we use the HLS framework provided by the Intel FPGA SDK for OpenCL [61].

This SDK is an implementation of the OpenCL standard API that allows for programmers to author both host and device code in a high level language. The SDK provides a runtime environment (RTE) that controls the execution of kernels on the FPGA. All of the low level interfaces and drivers that facilitate the interaction between the host and target device(s) are included in the BSP, traditionally provided by the board manufacturer. In the case of the HARPv2 platform, a pilot BSP is provided by Intel. The Intel OpenCL FPGA SDK provides an offline compiler that takes an OpenCL kernel, creates an HDL representation of that design in Verilog, synthesizes that into logical FPGA elements (RTL), maps that design into FPGA components (e.g. logic blocks, I/O blocks), places the mapped design onto the target FPGA, and routes the design.

HLS effectively allows a programmer to express a computational kernel at a higher abstraction level than RTL, allowing the programmer to focus on the functional specification. This kernel is then translated into an equivalent RTL description by the Intel tools which will be fed into the traditional FPGA synthesis flow. At this point, a bitstream to program the

FPGA is generated as if the design is written in Verilog to begin with, i.e., the resulting Verilog is synthesized, placed, and routed to generate the bitstream. From this point forward, we will refer to the tools that take the OpenCL specified kernel to perform the high level synthesis, logic synthesis, place, and route steps collectively as the *hardware compiler*.

#### OpenCL FPGA Execution Models

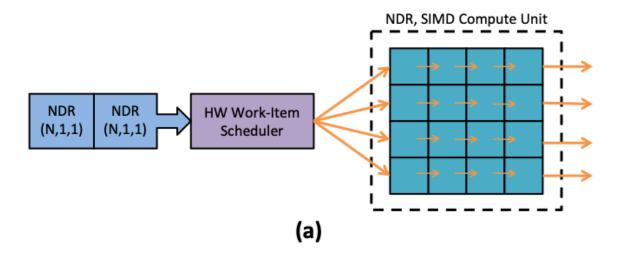

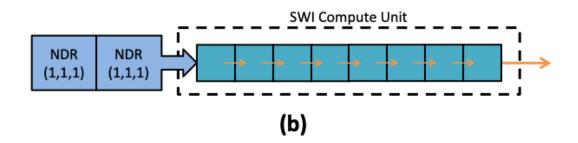

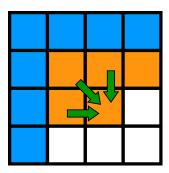

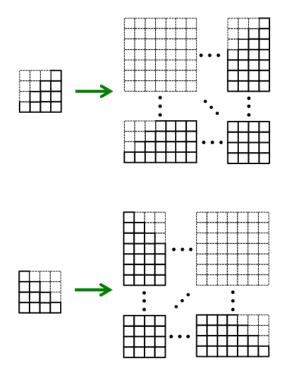

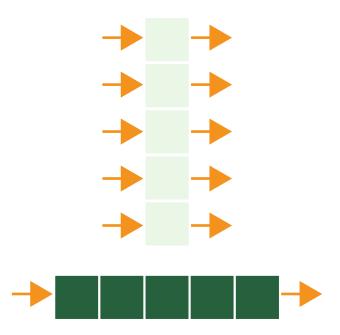

There are two main execution models for designing an OpenCL kernel to target synthesizable FPGA hardware: the Multiple Work-Item and Single Work-Item (SWI) models. MWI is also known as the NDRange (NDR) execution model. These models are pictorially described in Figure 2.3.

The MWI model expresses kernels through specifying a global amount of work (i.e. global work size) to do in (up to) a 3-dimensional space, and a local amount of work to do (i.e. local work size) in that same space that will be scheduled for execution on a processing element. In Figure 2.3, the NDRange kernel is specified in a 1-dimensional space. Kernel execution, then, must be enqueued from the host side to make sure all global work items will be executed. Each work item is then scheduled by a hardware scheduler on the FPGA side. This execution model is frequently used on GPUs, whose compute units are comprised of many SIMD vector units that are well suited to take advantage of data-level parallelism. The Single Work Item (SWI) model expresses kernels by setting the global and local work size to 1 in all dimensions so that all computation is handled by a single work item. In both cases, a custom pipeline is created for computation, as shown in Figure 2.3.

Intel recommends using the SWI model if the target kernel contains many loop and memory dependencies [60]. This allows the offline compiler to have a global view of all computation so it can account for dependencies when constructing a custom pipeline. Ideally, iterations can

Figure 2.3: (a) The NDRange model relies on using multiple work items to perform kernel computations. Each of these work items must be scheduled for execution onto the compute unit by a hardware scheduler implemented on the FPGA. In this case, there are two instances of some 1D NDRange kernel enqueued for execution that each have N global work items that need to be executed. The pipelined compute unit in this case has been vectorized by a factor of 4. (b) The Single Work Item kernel uses only one work item and thus does not need a hardware scheduler. Single work items rely on pipelining to exploit instruction-level parallelism and resolving of loop and memory dependencies between iterations without the use of costly memory barriers.

then be launched every clock cycle. Additionally, fine-grained sharing between loop iterations in an NDR kernel requires an intricate mechanism that involves local memory and barriers, and this leads to suboptimal kernel performance. Zohouri [148] takes this further and says that NDRange kernels should only be employed if loops cannot be fully pipelined due to variable exit conditions, complex loop-carried dependencies, or random external memory accesses. For all other cases, they recommend that the SWI model should be employed. However, the choice between the two models is non-trivial, as evidenced by Jiang et al. [64].

#### OpenCL FPGA in the Wild

Though there are many examples in the literature of using HLS frameworks to program FPGAs, we highlight instances that are most relevant to this work. Jin and Finkel evaluate the performance of varying the number of replicated compute units for an OpenCL kernel that computes an MD5 hash [66]. Sanaullah and Herbordt use the Verilog created by the Intel FPGA OpenCL SDK offline compiler for an OpenCL kernel that describe a fast Fourier transform, apply code structure optimizations, and outperform vendor IP-based designs while also being able to fit this modified design into existing FPGA solutions that use FFTs [112]. Zohouri et al. focus on the portability aspect of using OpenCL kernels intended for GPUs on FPGAs [149]. Sanaullah et al. propose a framework for describing OpenCL kernels that relies on the stacking of optimizations that should apply generally to all kernels [114]. However, they prescribe that the most performant version of any OpenCL kernel will use the SWI design paradigm and ignore the MWI paradigm. In this work, we explore both paradigms and find that the design choice between the two is non-trivial. Jin and Finkel perform a hardware design space search [68] similar to this work, but do not show the effect of varying the vectorized data types and their interaction with the available coarse-grained knobs. Additionally, they do not show the impact of scaling the input size.

We will address both of these issues in Chapter 6. In all cases, none of these works target the Intel HARPv2 CPU+FPGA platform using OpenCL. This work specifically evaluates the portability and performance of OpenCL FPGA system on the HARPv2 system, in which the CPU and FPGA are located on the same chip package and share a common memory. There is a only a small body of literature showing case studies that use the Intel HARPv2 platform in this way [17, 40, 42, 123, 145], and we intend for this work to add to the existing literature in order to inform more performant OpenCL-based designs for the Intel HARPv2 system.

The kernels used in Chapter 5 to evaluate performance and portability are sourced from work done by Zohouri et al. that aims to evaluate and optimize OpenCL kernels taken from the Rodinia suite [26] to evaluate the effectiveness of FPGAs in high performance computing applications [148, 149].

### 2.4.4 High Level Synthesis and Design

In addition to the Intel FPGA OpenCL SDK, there are other ways to leverage High Level Synthesis (HLS) and design to target FPGAs. One of the earliest HLS languages that preceded OpenCL for FPGAs was the Streams-C language and compiler, implemented by Gokhale et al. [50], that allowed programmers to author streaming kernels in a C-based language. They also quantified the tradeoffs between performance and ease of programmability using HLS. LegUp, developed by Canis et al., takes a C program as input and automates the process of finding segments of code that can be accelerated on an FPGA [24]. Bachrach et al. develop a hardware construction language called Chisel in the Scala programming language in order to design hardware using object-oriented principles and functional programming [6]. It is important to make the distinction that Chisel is not a "C-to-Gates" form of HLS; this

solution allows for a more expressive description of hardware using higher level ideas like object-oriented programming.

## Chapter 3

# **DIBS:** A Data Integration

# Benchmarking Suite

Generating and analyzing big data are tasks encountered by many scientists and researchers in various disciplines. Social networks, computational biology, sensor data, and entrepreneurial records are just a small sample of the range of applications that encounter various and extensive data streams. It is generally well understood that big data is voluminous and prevalent in the research and industrial communities alike, but what is less studied are all of the steps that must be completed even before the primary computation (e.g., number crunching and analysis of the data) can begin. Specifically, there is often a non-trivial amount of time, effort, and resources that are spent towards retrieving and preprocessing big data sources.

This problem of taking data in some initial form and transforming it into a desired one comes in several flavors. It might involve rearranging fields, changing the form of expression of one or more fields (e.g., translating one character set into another, such as ASCII to UTF or EBCDIC to ASCII), altering the boundary notation of records and/or fields (e.g., moving between comma-separated and fixed-length fields), encrypting or decrypting records and/or fields, parsing non-record data and organizing it into a record-oriented form, etc. We define this problem, collectively, as *data integration*.

In the business community, this is part of the Extract, Transform, and Load (ETL) process, specifically the transform step. Another phrase that is often incorporated into the scope of data integration is data cleansing, which includes notions of checking data integrity, (re)constructing missing fields, outlier detection, type checking (e.g., does a numeric field contain non-numeric contents?), etc. Yet another phrase that is relevant is the notion of pre-analytics. Here, various aggregations might be performed on the data (e.g., summation, histogram construction) the results of which are then used, downstream, during the analytics process. Beyond dealing with record-oriented data, modern data integration must deal with semi-structured and unstructured data as well [48]. Frequently, the challenges here include parsing of the data to extract what structure does exist (e.g., click streams) and text processing to address unstructured data (e.g., blog posts).

While the individual transforms are each (mostly) quite straightforward, the task is quickly complicated by the fact that individual data streams can be quite large and there are frequently many streams, each requiring a distinct transformation specification. Tens to hundreds of multi-Gigabyte data streams must be concurrently integrated, and this must be done prior to actually doing any of the real data analysis, the ultimate goal.

The issue of how to effectively achieve data integration is a pain point for enterprise data, sensor data, scientific data, financial data, etc. Data-driven public policy, economics, and journalism all rely on data from widely disparate sources that must first go through data integration prior to effective use [54]. In short, efficient data integration is crucial to effective use of big data resources.

Data integration manifests itself in many of the preliminary steps that researchers take before applying the analysis algorithms or processing steps to their data. An example is the effort expended in the effective usage of data provided by the US Virtual Astronomical Observatory (VAO). Here, a team comprised of over 11 institutions provides access to astronomical data from the National Optical Astronomy Observatory (NOAO), the National Radio Astronomy Observatory (NRAO), the Sloan Digital Sky Survey (SDSS), the 2 Micron All Sky Survey (2MASS), the Hubble Space Telescope, the Chandra X-ray Observatory, the Spitzer Space Telescope, and others. Section 5.2 of the VAO Annual Report [131], entitled "Data Sharing and Publishing," describes updates to no less than 7 different tools for accessing the disparate data available, one of which is tasked with simply telling astronomy researchers where they can download the descriptions of the data sets themselves. Another tool provides information about the various data models.

Thus, a user runs a first tool to find the format that describes the data, runs a second tool to access the data model (our user at this point finally has metadata, but no actual data), and then runs yet a different tool to access the data set itself. However, if they wish to use data from more than one source, there is still the need to unify the (differently formatted) data from these sources into a common format for analysis.

As another example, consider the needs of a researcher in biosequence analysis. Genomic and proteomic data sets are available from a wide variety of sources in a large number of disparate formats (e.g., FASTA, FASTQ, SAM, BAM, AB1/SCF, PDB, GTF, etc.). Wikipedia lists 22 distinct file formats for molecular biology and bioinformatics<sup>2</sup>. The data volumes are sufficiently large that simply transforming the data from its original form into that needed for analysis is becoming time prohibitive (e.g., three days are required to perform duplicate marking, base score quality recalibration, and local realignment on a 250 GB BAM file at  $30 \times$  coverage [91]).

<sup>&</sup>lt;sup>2</sup>http://en.wikipedia.org/wiki/List\_of\_file\_formats#Biology

While there are a number of ways in which one could attempt to organize data integration applications, we will consider an individual data integration job to be decomposed into one or more of the following three tasks:

- Parsing/Cleansing the computation associated with recognizing the records, fields, and/or other components of the input data, including checking to see if it is well-formed and addressing any example inputs that aren't well-formed.

- Transformation once parsed, the input data must be translated into the form that is expected by the primary computation, typically going from a file-oriented format to a memory-oriented format.

- Aggregation any pre-analytics computations that result in aggregate information about the input.

While the boundaries between the tasks in each category above are not always completely clear, we will use the above tasks to help us reason about how representative and comprehensive is the set of applications ultimately chosen to be in the benchmark suite.

Here, we present the Data Integration Benchmark Suite (DIBS), a set of applications spanning several different application domains and the above three types of data integration tasks. DIBS tries to be reasonably comprehensive with respect to both applications and tasks. To help us address how comprehensive they truly are, the benchmarks are characterized through different measures in order to capture the properties (and idiosyncrasies) across the various data integration tasks represented in the suite. The goals of DIBS are to provide insight into the the nature of data integration tasks to guide research in this area, and to create a way in which different research groups can compare their work [82].

## 3.1 Overview of Benchmark Suite and Integration Tasks

The challenges in selecting candidate applications for any benchmark suite include whether or not the candidates that are ultimately included are both representative of the field and comprehensive in their coverage of the field. To help us assure that the selected applications are representative, we consider each application across two dimensions.

First, we want to capture the breadth of application domains that handle large volumes of data. Scientific data are quite commonly organized in either one-dimensional or a two-dimensional form. As a representative of one-dimensional data integration, we include biosequence data from the field of computational biology. For two-dimensional data, we chose several image processing data transformations. To reflect the importance of business applications (and corresponding data volumes), we include a pair of data integration applications from the enterprise space. We round out the set of application domains by including examples from IoT data and graph processing.

Second, we want to ensure that we include tasks that span the three composite parts of data integration. For parsing and data cleansing, in many cases we are reading a human-readable format and recognizing fields, records, etc., while at the same time separating the primary data set from associated metadata. The data transformations essentially define each specific application, putting the data into the form required by the computation that follows. Finally, the aggregation tasks include counts, summations, and histograms.

The relationship between the five application domains, types of integration tasks, and elements included in the benchmark are all summarized in Table 3.1. The applications themselves (shown in the Transformation column) are each described in the following section.

Table 3.1: Data Integration Task Classification.

|                       | Data Integration Tasks                                   |                                                                                                                                                                                               |                                                           |

|-----------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Domain                | Parsing/Cleansing                                        | Transformation                                                                                                                                                                                | Aggregation                                               |

| Computational Biology | Separate bases and meta-data<br>Handle non-A,T,G,C bases | fa→2bit<br>2-bit→fa                                                                                                                                                                           | Track total size                                          |

| Image Processing      | Parse FITS tags                                          | $\begin{array}{c} \text{fits} \rightarrow \text{tiff} \\ \text{idx} \rightarrow \text{tiff} \\ \text{optdigits} \rightarrow \text{tiff} \\ \text{unipen} \rightarrow \text{tiff} \end{array}$ | Pixel statistics Histogram Taking log of pixels           |

| Enterprise            | Adjust non-ASCII characters                              | ebcdic→txt<br>fix→float                                                                                                                                                                       | Count number of elements                                  |

| Internet of Things    | Tokenize input                                           | $\begin{array}{c} \text{tstcsv} \rightarrow \text{csv} \\ \text{gotrackcsv} \rightarrow \text{csv} \\ \text{plt} \rightarrow \text{csv} \end{array}$                                          | Running total of file size                                |

| Graph Processing      | Parse edge list                                          | edgelist→csr                                                                                                                                                                                  | Get total vertex/edge count<br>Compute vertex edge degree |

To assess the extent to which the benchmark suite provides comprehensive coverage of the area, we will rely primarily on the distribution of the properties of the applications, described in Section 3.3.

## 3.2 Benchmark Application Descriptions

In this section, we will describe each of the benchmark applications, identified by their associated data transformation and organized by application domain. In all cases, the data integration applications are written in C and the input data set size is large enough such that any second-order effects caused by start-up transients can be ignored.

## 3.2.1 Computational Biology

In bioinformatics, DNA sequence alignment is the use of computing to compare sequences of DNA to determine the degree of similarity between them. Based on discovered similarities,

researchers can determine structural relationships, pinpoint evolutionary mutations, and predict biological functions [51].

Currently, there are a number of different sequence alignment computing tools and software that, at their core, compare an input sequence against a known genomic sequence. For example, the popular Basic Local Alignment Search Tool (BLAST) from Altschul et al. [3] performs the comparison by approximating the Smith-Waterman dynamic programming algorithm to find the maximal segment pair between the two sequences. Kent et al. [72] developed the BLAST-like Alignment Tool (BLAT), which performs the comparison in a similar to BLAST. It sacrifices homology depth for speed. The inputs to these tools, however, are far from standardized. BLAST accepts sequences using the FASTA format [85], which was born out of an alignment tool that predates BLAST. BLAT uses a custom 2-bit format in which the four DNA bases are represented by two bits per base. There are also a number of other DNA sequence formats that exist, such as FASTQ [29], SAM/BAM [83], and AB1 [126].

Often, it is the case that researchers will want to perform analyses on DNA sequence data that require a format that differs from the format the data is originally in. For our suite, we have chosen two of the conversion utilities available with BLAT–namely, the conversion from the FASTA form to 2-bit form, and vice versa.

#### $fa\rightarrow 2bit$

In the FASTA to 2-bit form, the input FASTA bases are parsed line by line. The set of accepted bases is  $\{a, A, g, G, c, C, t, T, n, N\}$ . For each base in a given line, its 2-bit equivalent is found and packed into bytes, with four, 2-bit bases per byte. Newlines are not recorded. There is also some metadata to be stored alongside the sequence of bases. If one or more consecutive, non-A,T,G,C bases are found, the amount of them and their relative position

are recorded. This is also computed for one or more consecutive blocks of lowercase bases. The two-bit data is then stored in a data structure that accounts for the raw data as well as metadata (e.g. name of sequence, size, count and position of non-A,T,G,C bases) associated with the raw data. A sample of FASTA human genome data³ totaling 130 MB in size is used as input. When looking at results, this transformation will be under the label fa→2bit.

#### 2bit→fa

In the reciprocal transformation, 2-bit to FASTA conversion, an input 2-bit file is parsed. Each byte is unpacked into its corresponding FASTA representation. Each character is then converted to its upper-case representation. The metadata from the 2-bit representation is used to restore the lower-case blocks as well as the blocks of the character 'N'. The 2-bit representation of the input data from the previous transformation is used as input and is 34 MB. This transformation is labeled  $2bit \rightarrow fa$ .

## 3.2.2 Image Processing

From consumers and smartphones, medical physicians and biomedical imaging systems, and astrophysicists and space telescopes, the proliferation of imaging data and has become one of the most voluminous sources of data today. As reported by Venter and Stein [129], images make up more than 80% of all corporate and public unstructured big data. For our benchmarking suite, we have selected four different image processing applications in which a non-traditional image format is converted into a more conventional one.

<sup>&</sup>lt;sup>3</sup>ftp://ftp.ensembl.org/pub/release-89/fasta/homo\_sapiens/dna/

#### $fits \rightarrow tiff$

The Flexible Image Transport System (FITS) file format was developed specifically for storing data from scientific applications, and is the most common format for astronomical imaging data. FITS files contain one or more headers that contain metadata such as data types and image dimensions. Raw data immediately follows a metadata header. Our conversion consists of three parts. First, the metadata headers are parsed and written into an accompanying JSON file. Next, the raw data is copied into a buffer that will be written into a TIFF file. Finally, descriptive statistics are calculated and a histogram of the image is created. Input data for this transformation is of the globular cluster Messier 12 through the B band recorded by the Hubble Telescope<sup>4</sup>, and totals 17 MB. This transformation is labeled fits  $\rightarrow$  tiff.

Handwriting recognition is the process of taking a source of handwritten input and converting it into a machine-readable form. There are have been many unique formats developed by researchers to store handwriting data. In our suite, we present a conversion to TIFF for three of these formats.

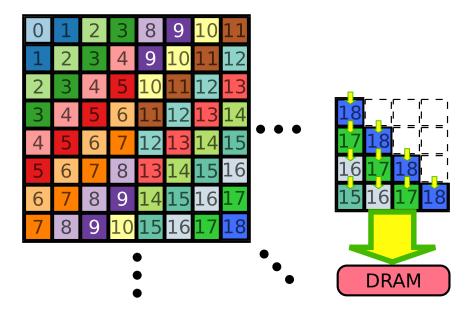

#### $idx \rightarrow tiff$

The first is the IDX file format, which is the format used by the MNIST handwriting database. IDX is comprised of two files. The raw data, which is stored in the first file (.idx3-ubyte), contains a compilation of handwriting samples. The offsets for each image's pixel data are computed using the meta-data encoded at the beginning of the .idx3-ubyte file. This meta-data includes the total number of images in the file and the number of rows and columns

<sup>4</sup>https://www.spacetelescope.org/projects/fits\_liberator/m12data/

in each image. The labels (e.g., image 701 is the number "4") associated with each image is stored in the second file (.idx1-ubyte), and can be indexed in a similar fashion as the image data. Both files are read into memory, and a different TIFF file is generated for each handwriting sample. The input to our transformation is 7.5 MB and is taken from the MNIST website<sup>5</sup>. This transformation is labeled idx $\rightarrow$ tiff.

#### $optdigits \rightarrow tiff$

The optdigits format represents a set of handwritten digits in a bitmap format encoded in ASCII. The raw handwriting data is preceded by metadata that describes the uniform height and width of each digit, as well as the total number of digits in the set. This format is used in the Optical Recognition of Handwritten Digits dataset [84], which is 2.0 MB and serves as the input for our transformation. The transformation is performed by parsing each handwritten digit separately, converting strings of '1's and '0's into 8-bit pixel values to create a TIFF image. This transformation is labeled optdigits  $\rightarrow$  tiff.

#### unipen→tiff

The UNIPEN format consists of handwriting digits that are described as a set of XY coordinates. Sets of coordinates are demarcated by keywords that denote pen strokes (i.e., it is in vector form). The transformation parses one set of coordinates associated with a given handwriting sample at a time. To construct a TIFF image from a set of coordinates, each consecutive pair of coordinates is treated as a line segment. Circles of a specified radius are drawn from the first coordinate to the second using the Midpoint Circle Drawing algorithm [44] and are then filled in after each circle is drawn. We use the 1.6 MB Pen-Based

<sup>&</sup>lt;sup>5</sup>http://yann.lecun.com/exdb/mnist/

Recognition of Handwritten Digits dataset [84] as input. This transformation is labeled unipen—tiff.

#### 3.2.3 Enterprise

Enterprise data transformations are classically considered to be part of ETL (Extract, Transform, and Load) processing. Poess et al. [106] include 18 different transformations in their benchmark suite, which includes the same tasks that we use for organization of the transformation (parse/cleanse, transform, aggregate). One thing we do not include, which is present in [106], is a join operation across two distinct inputs. A great many of enterprise transformations are motivated by businesses moving away from mainframe execution to using cloud-based machines. As such, data type transformations are quite prevalent, especially from older, legacy systems (often EBCDIC based and even not including floating-point hardware) to modern x86 platforms.

#### $ebcdic \rightarrow txt$

In our benchmark suite, we include a simple EBCDIC to ASCII transformation. Our transformation uses the traditional 7-bit ASCII encodings. Once the total number of elements is calculated, the conversion executes by referencing a look-up table to find the corresponding EBCDIC character. If a particular EBCDIC character does not have a corresponding ASCII equivalent, the offending EBCDIC encoding is assigned an unused ASCII encoding specific to that EBCDIC encoding. A 9.2 MB EBCDIC file is used as input. This transformation is labeled ebcdic $\rightarrow$ txt.

#### fix→float

Additionally, we include a conversion for fixed-point data to floating point. The input dataset is a 10 MB, random binary file<sup>6</sup>. The input data is interpreted in 16-bit chunks with a user defined number of fractional bits. Each number is then converted into a 32-bit floating point number using a bit-shift, division, and typecasts. The value is then saved into a memory buffer completing the transformation. This transformation is labeled fix—float.

## 3.2.4 Internet of Things (IoT)

The Internet of Things (IoT) represents scores of devices with newly enabled connectivity [45]. While the promise of increased functionality provided by these devices is high, there is very limited commonality in how they provide the data that they all collect. For example, we use GPS data from multiple sources [32, 97, 146], yet different transformations are required for each input data set. In our benchmark suite, we transform three different types of GPS data in order to normalize them. The normalized format is a CSV file where each record takes the form <ID>,<Latitude>,<Longitude>.

#### $tstcsv \rightarrow csv$

The CSV format used for the Taxi Service Trajectory (TST) Prediction Challenge of 2015<sup>7</sup> uses a CSV format containing data describing the trajectories of operating taxis in Porto, Portugal. The GPS trajectories are located in the last field of a data line, and are stored as a list of coordinates in the form <Longitude>,<Latitude>. Each list is record of the

<sup>&</sup>lt;sup>6</sup>http://rngresearch.com

<sup>7</sup>http://www.geolink.pt/ecmlpkdd2015-challenge/index.html

periodically recorded GPS coordinates from start to end of a fare. In our transformation, we store the unique identifier for the trip, navigate to and parse the trajectories list for that trip, swap the order of each pair of coordinates to match the normalized form, keep a running total of the size, and create a new CSV file using the normalized format. A 437 KB data set from the TST challenge [84] is used as input. This transformation is labeled tstcsv $\rightarrow$ csv.

#### $gotrackcsv \rightarrow csv$

The GPS data released by the GoTrack mobile application<sup>8</sup> is packaged in a CSV format that contains GPS coordinates, coordinate identifiers, and timestamps. In our conversion, we parse the input data line by line for the coordinate identifier and GPS coordinates. Then, we write the data using the normalized format to a new CSV file. We use a 1.1 MB set of GPS data from the GoTrack mobile application [84] as input. This transformation is labeled gotrackcsv—csv.

#### $plt \rightarrow csv$

The PLT format is used in the GeoLife project<sup>9</sup> conducted by Microsoft Research Asia to store GPS trajectories. The PLT format is essentially in CSV format, except the raw data is preceded by six lines of metadata. The raw data includes GPS coordinates, altitude, and variations of timing data. In our transformation, we calculate the total number of coordinate pairs, parse the input data line by line, extract the coordinate identifier and its corresponding <Longitude>,<Latitude> pair, and write the data using the normalized format into a new CSV file. We use a 449 KB subset of the GeoLife dataset as input. This transformation is labeled plt→csv.

<sup>8</sup>https://play.google.com/store/apps/details?id=com.numerex&hl=en

<sup>9</sup>https://www.microsoft.com/en-us/download/details.aspx?id=52367

## 3.2.5 Graph Processing