# EFFICIENTLY ACCELERATING SPARSE PROBLEMS BY ENABLING STREAM ACCESSES TO MEMORY USING HARDWARE/SOFTWARE TECHNIQUES

A Dissertation Presented to The Academic Faculty

By

Bahar Asgari

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

Electrical and Computer Engineering

Department of Engineering

Georgia Institute of Technology

May 2021

© Bahar Asgari 2021

# EFFICIENTLY ACCELERATING SPARSE PROBLEMS BY ENABLING STREAM ACCESSES TO MEMORY USING HARDWARE/SOFTWARE TECHNIQUES

Thesis committee:

Dr. Hyesoon Kim Computer Science Georgia Institute of Technology

Dr. Saibal Mukhopadhyay Electrical and Computer Engineering Georgia Institute of Technology

Dr. Moinuddin Qureshi Computer Science Georgia Institute of Technology Dr. Richard Vuduc Computer Science Georgia Institute of Technology

Dr. Tushar Krishna Electrical and Computer Engineering Georgia Institute of Technology

Date approved: April 26, 2021

Let the beauty of what you love be what you do.

Rumi

#### ACKNOWLEDGMENTS

Foremost, I would like to express my deepest appreciation to my late advisor Dr. Sudhakar Yalamanchili. I will be ever grateful for his assistance. His memory will be with me always. I would also like to extend my deepest gratitude to my advisor Dr. Hyesoon Kim for her profound belief in my abilities and my work and her unrelenting support. The completion of my dissertation would not have been possible without her support and nurturing.

I would like to extend my gratitude to the members of my thesis committee for their help in the preparation of this work – Dr. Saibal Mukhopadhyay for his valuable advice that had no small part to play in the formation of this dissertation, Dr. Tushar Krishna for always listening to my ideas and suggesting ingenious insights for improving them, Dr. Moinuddin Qureshi for his unwavering support, advice, and encouragement at any time throughout the duration of my Ph.D. studies, and Dr. Richard Vuduc for his constructive advice and practical suggestions. I am also extremely grateful to Dr. Sung-Kyu Lim whose help and contributions to this work cannot be overestimated.

I would like to gratefully acknowledge the support of the Laboratory for Physical Sciences (LPS) and extend my sincere thanks to Dr. Eric Cheng from LPS who provided insight and expertise that greatly assisted this research. I had the great pleasure of collaborating with Dr. Ramyad Hadidi, Dr. Prashant Nair, Dr. Jeffrey Young, Jiashen Cao, Da Eun Shim, Dheeraj Ramchandani, Amaan Marfatia, Nima Shoghi, Sam Jijina, Adriana Amyette, Fares Elsabbagh, Younmin Bae, Burhan Ahmad Mudassar, and Kartikay Garg, without whom I would have never completed the pieces of this work. I also would like to extend my special thanks to Dr. Fernando Mujica for his continuous support and encouragement. I cannot leave Georgia Tech without mentioning Daniela Staiculescu, who was always there to help. Thanks should also go to Jane Chisholm without whose guidance I could have never written this dissertation.

I wish to thank the former members of CASL lab, Dr. Xinwei Chen, Dr. Karthik

Rao, Dr. Chad Kersey, and Dr. He Xiao who always provided me with encouragement and enlivening. I also like to extend my gratitude to the former and current members of the HPArch lab, Dr. Hyojong Kim, Dr. Prasun Gera, Yonghae Kim, Jaewon Lee, Andrei Bersatti, Blaise Tine, and Euna Kim. I was lucky to know them during my years at Georgia Tech and have fruitful discussions with them. Many thanks are due to all my friends who made the journey of my Ph.D. most wonderful.

Above all, I am deeply indebted to my family for their unparalleled love and support. I cannot begin to express my thanks to my parents Vida Zehforoosh and Aziz Asgari who selflessly encouraged me to explore new directions in life and seek my own destiny. Last but not least, I am extremely grateful to my sister, Shadi Asgari for always being there for me as the best friend.

# TABLE OF CONTENTS

| Acknow    | vledgm   | ents                                                                     |

|-----------|----------|--------------------------------------------------------------------------|

| List of   | Tables   |                                                                          |

| List of 1 | Figures  |                                                                          |

| Summa     | ary      |                                                                          |

| Chapte    | r 1: Int | roduction and Background                                                 |

| 1.1       | Sparse   | e Problems                                                               |

| 1.2       | Contri   | butions                                                                  |

| 1.3       | Thesis   | Statement                                                                |

| Chapte    | r 2: Lit | erature Survey and the Gap of Knowledge                                  |

| 2.1       | Specia   | alized Hardware for Sparse Acceleration                                  |

|           | 2.1.1    | Near-Data Processing for Recommendation Systems                          |

|           | 2.1.2    | Hardware Accelerators for Neural Networks                                |

|           | 2.1.3    | Hardware Accelerators for Sparse Matrix Algebra and Scientific Computing |

| 2.2       | Softwa   | are Techniques for Dealing with Sparsity                                 |

|           | 2.2.1    | Pruning the Neural Networks                                              |

|        | 2.2.2 Compressing Sparse Matrices                       | 21 |

|--------|---------------------------------------------------------|----|

| 2.3    | Unsolved Challenges                                     | 24 |

|        | 2.3.1 The Underutilization of Memory Bandwidth          | 25 |

|        | 2.3.2 The Underutilization of Dense Computation         | 29 |

| Chapte | r 3: Processing Sparse Data While Gathering Them        | 31 |

| 3.1    | Main Contributions of Fafnir                            | 31 |

| 3.2    | The Top-Down Overview of Fafnir                         | 33 |

| 3.3    | Key Mechanisms                                          | 38 |

| 3.4    | Adapting Fafnir to SpMV                                 | 40 |

| 3.5    | Evaluation                                              | 43 |

|        | 3.5.1 Experimental Setup                                | 43 |

|        | 3.5.2 Latency                                           | 46 |

|        | 3.5.3 Speedup and Scalability                           | 47 |

|        | 3.5.4 Power Consumption and Area Overhead               | 49 |

| 3.6    | Summary                                                 | 52 |

| Chapte | r 4: Mathematical Transformation to Reduce Dependencies | 53 |

| 4.1    | Key Mechanisms of Alrescha                              | 53 |

| 4.2    | Compression Format for Sparse PDEs                      | 56 |

| 4.3    | Broad Applications                                      | 57 |

| 4.4    | Putting Them Together for Sparse PDEs                   | 60 |

| 4.5    | Reconfigurable Microarchitecture                        | 63 |

| 4.6    | Evaluation                                              | 64 |

|        | 4.6.1    | Experimental Setup                              | 64  |

|--------|----------|-------------------------------------------------|-----|

|        | 4.6.2    | Execution Time                                  | 66  |

|        | 4.6.3    | Energy Consumption                              | 70  |

|        | 4.6.4    | FPGA Resource Utilization and Power Consumption | 71  |

| 4.7    | Summ     | ary                                             | 72  |

| Chapte | r 5: Str | ructured Pruning for Systolic Arrays            | 74  |

| 5.1    | Lodes    | tar Pruning Algorithm                           | 74  |

| 5.2    | Eridan   | nus Systolic Microarchitecture                  | 76  |

| 5.3    | Evalua   | ntion                                           | 78  |

|        | 5.3.1    | Experimental Setup                              | 78  |

|        | 5.3.2    | Accuracy                                        | 79  |

|        | 5.3.3    | Performance                                     | 79  |

| 5.4    | Summ     | ary                                             | 81  |

| Chapte | r 6: Fas | st Decompression                                | 83  |

| 6.1    | Ascell   | a Decompression Mechanism                       | 84  |

| 6.2    | Evalua   | ation                                           | 85  |

|        | 6.2.1    | Experimental setup                              | 85  |

|        | 6.2.2    | The Overhead of Decompression                   | 94  |

|        | 6.2.3    | Latency and Balance Ratio                       | 96  |

|        | 6.2.4    | Throughput and Bandwidth Utilization            | 98  |

|        | 6.2.5    | Resource Utilization and Power Consumption      | 00  |

| 63     | Summ     | ory 1                                           | 102 |

| Chapter 7: Conclusions | <br>• | <br>103 |

|------------------------|-------|---------|

| References             | <br>  | <br>106 |

# LIST OF TABLES

| 1.1 | The challenges and applications of sparse problems, our contributions and publications to resolve the challenges, and the broader impacts that this research would have.                                                                  | 5  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | State-of-the-art approaches for accelerating graph and scientific problems .                                                                                                                                                              | 19 |

| 2.2 | The impact of pruning granularity on inference using systolic arrays                                                                                                                                                                      | 21 |

| 3.1 | FIFO buffer sizes that are sum of all buffers in all PEs (B is batch size)                                                                                                                                                                | 37 |

| 3.2 | SpMV vs. embedding lookup                                                                                                                                                                                                                 | 42 |

| 3.3 | Sparse matrices from SuiteSparse [117]                                                                                                                                                                                                    | 45 |

| 3.4 | Latency (cycles @200MHz) of the components in compute units of Fafnir for FPGA implementation                                                                                                                                             | 46 |

| 3.5 | FPGA resource utilization for Fafnir                                                                                                                                                                                                      | 50 |

| 3.6 | Area and power consumption breakdown @500MHz to switching (Sw.), interconnections (Int.), and leakage (Lkg.) for ASIC design of Fafnir @7 nm.                                                                                             | 51 |

| 4.1 | The properties of sparse kernels and corresponding dense data paths, implemented in Alrescha. Depending on the type of kernel, the <i>operation</i> in phase 1 can use the three vector operands at the same time or use just two of them | 59 |

| 4.2 | Baseline configurations                                                                                                                                                                                                                   | 65 |

| 4.3 | Alrescha Configuration                                                                                                                                                                                                                    | 66 |

| 4.4 | Resource utilization and the total dynamic power consumption                                                                                                                                                                              | 72 |

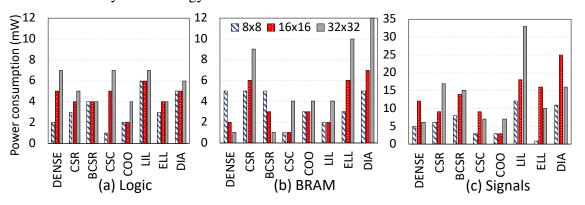

| 6.1 | Resource utilization and the total dynamic power consumption for three |     |

|-----|------------------------------------------------------------------------|-----|

|     | partition sizes (8, 16, and 32)                                        | 101 |

# LIST OF FIGURES

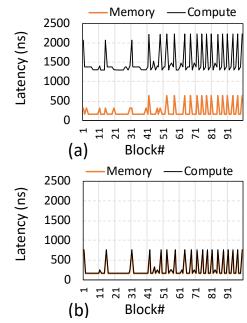

| 1.1 | Memory and computation latency for streaming blocks for (a) prior work, and (b) Ascella. Closer memory and compute is better                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Comparing NDP-based solutions for embedding lookup: (a) Baseline with no NDP, (b) TensorDIMM [35], and (c) RecNMP [36]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13 |

| 2.2 | Sparse formats: (a) The original sparse matrix in <b>dense</b> format, (b) <b>CSR</b> including offsets to indicate the number of non-zero entries per row, indices, indicating column indices of non-zero entries, and the values itself. CSC follows the same rule as CSR; (c) <b>BCSR</b> including offsets to indicate the number of non-zero 4×4 blocks per row, indices, indicating the index of the first column of non-zero blocks, and the values, indicating the flatten values of non-zero blocks; (d) <b>COO</b> including a series of (row, column, value) tuples for non-zero values; (e) <b>DOK</b> , which is similar to COO; (f) <b>LIL</b> , which pushes all the non-zero entries to top and saves the row indices; (g) <b>ELL</b> , which is similar to LIL but pushes the non-zero entries to left ans also uses a padding; and (h) <b>DIA</b> , which saves the non-zero diagonals by adding the diagonal numbers as a header to each diagonal | 23 |

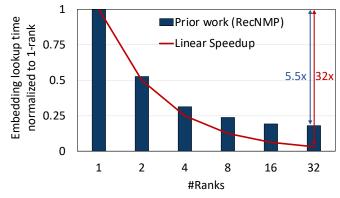

| 2.3 | The time to perform embedding lookup in recommendation systems when the size of memory system grows. Numbers are normalized to a one-rank system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25 |

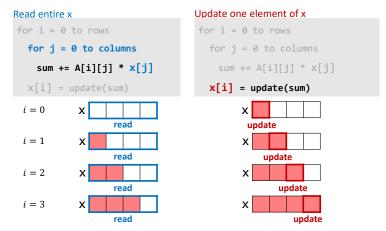

| 2.4 | Dependencies in SymGS: Each iteration of the outer loop reads the entire vector $x$ (left) and updates one element of $x$ (right). The iterations of the outer loop are dependent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 26 |

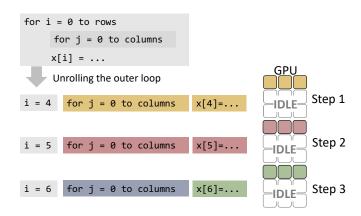

| 2.5 | Limited parallelism: Unrolling the iterations of the outer loop (left) and mapping the pararellizable iterations of the inner loop to processing units of a GPU (right).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27 |

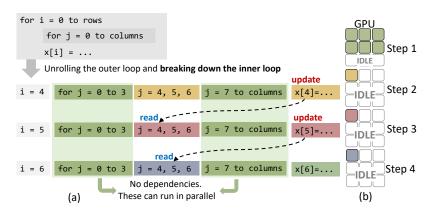

| 2.6 | (a) Key observation: the iterations of the outer loop are just <i>partially</i> dependent. In fact, only a few iterations of the inner loop read the newly updated elements. Therefore, we can break down the iterations of the inner loop across a few unrolled iterations of the outer loop, into data-dependent part $(j = 4, 5, 6)$ , and parallelizable part (green parts); (b) Key challenge: ineffectiveness of blocking technique on GPUs. More parallelism at step 1, but dependecies still create the bottleneck through steps 2, 3, and 4 | 28 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

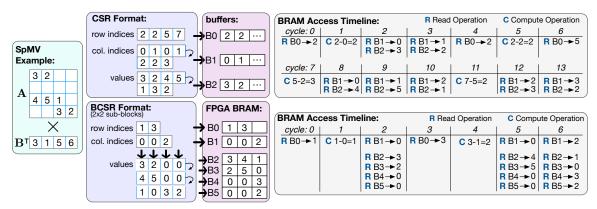

| 2.7 | The time steps required to read a sparse matrix compressed in CSR and BCSR formats, for creating the non-zero rows. For simplicity, this example (and the next example in Figure 6.1) assume only one read per cycle from a buffer                                                                                                                                                                                                                                                                                                                   | 29 |

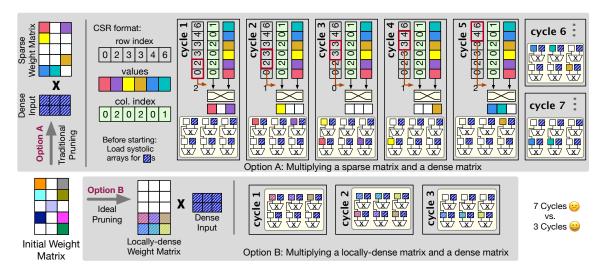

| 2.8 | Clarifying the challenge of systolic-array underutilization: Comparing the execution of a matrix-matrix multiplication using a systolic array when one operand is a dense matrix and the other operand is: (a) a sparse matrix, and (b) a locally-dense sparse matrix                                                                                                                                                                                                                                                                                | 30 |

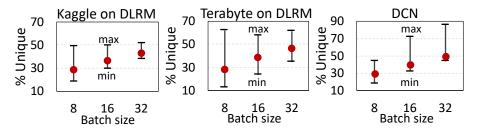

| 3.1 | The percentage of unique indices in batches of queries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33 |

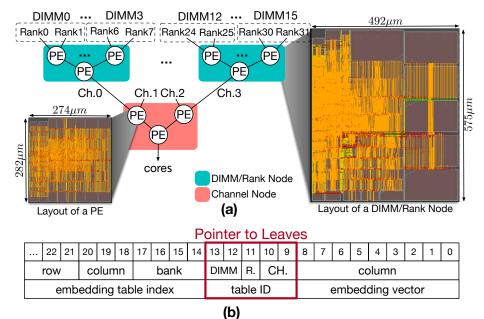

| 3.2 | (a) The architecture of Fafnir tree, consisting of DIMM/rank and channel nodes and ASIC designs at 7 nm for a PE and a DIMM/rank node. (b) The mapping of embedding tables to memory addresses                                                                                                                                                                                                                                                                                                                                                       | 35 |

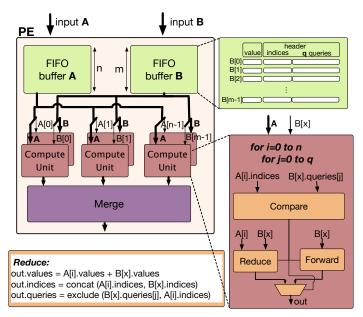

| 3.3 | The microarchitecture of a PE including FIFO buffers, compute, and merge units, showing the data path from leaves to the root                                                                                                                                                                                                                                                                                                                                                                                                                        | 36 |

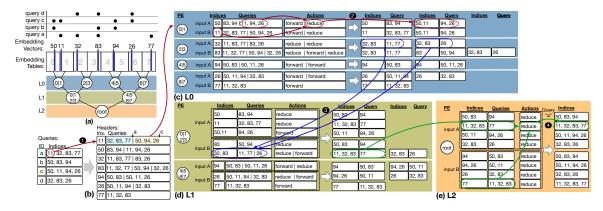

| 3.4 | Concurrent batch processing and eliminating redundant memory accesses in Fafnir: (a) A batch of four queries that access random embedding vectors from eight embedding tables and a three-level Fafnir tree (b) Extracting the unique indices of four queries and creating the headers of requests to be forwarded to Fafnir. The steps of processing the four queries through the PEs at three levels of tree: (c) L0, (d) L1, and (e) L2                                                                                                           | 38 |

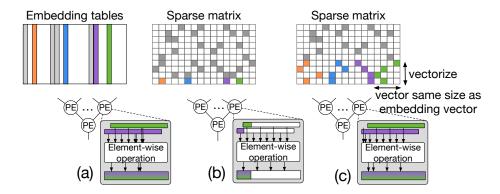

| 3.5 | (a) Embedding lookup in Fafnir, (b) Using Fafnir for an SpMV with no mechanisms, and (c) Using vectorization to fully utilize Fafnir for SpMV.                                                                                                                                                                                                                                                                                                                                                                                                       | 41 |

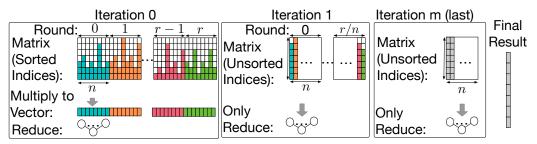

| 3.6 | The iterations and rounds for SpMV on large sparse matrices using Fafnir when only $n$ columns of the matrix fits to Fafnir at a time                                                                                                                                                                                                                                                                                                                                                                                                                | 42 |

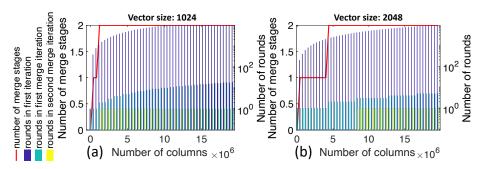

| 3.7 | The number of iterations, rounds per iteration, and required merges for matrices with up to 20 million columns, for vector sizes (a) 1024 and (b) 2048. In our configuration for SpMV, vector size (i.e., the number of columns that fit in Fafnir tree) is 2048                                                                                                                                                                                                                                                                                     | 43 |

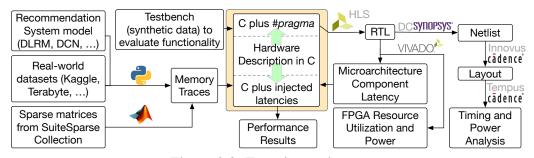

| 3.8  | Experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                   | 44 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

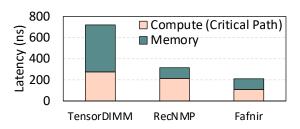

| 3.9  | Single-query latency breakdown                                                                                                                                                                                                                                                                                                                                                                                                       | 47 |

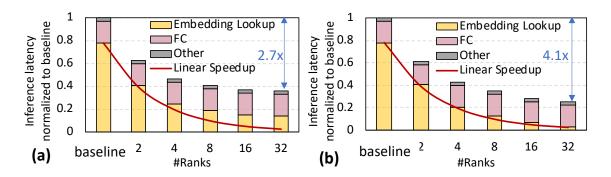

| 3.10 | End-to-end inference speedup for DLRM on Kaggle (batch size = 8): (a) RecNMP, (b) Fafnir                                                                                                                                                                                                                                                                                                                                             | 48 |

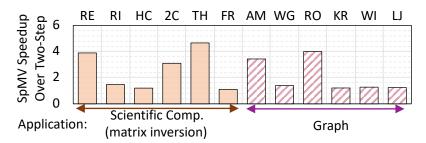

| 3.11 | Speedup of Fafnir over Two-Step algorithm [76] for two SpMV-based applications: scientific computations (matrix inversion algorithm) and graph                                                                                                                                                                                                                                                                                       | 48 |

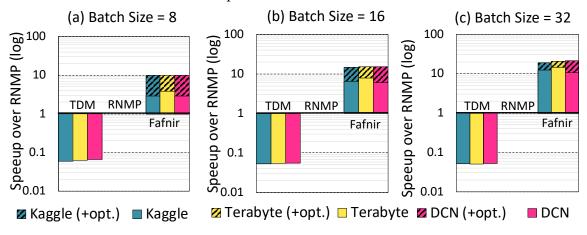

| 3.12 | Speedup of Fafnir and TensorDIMM [35] (TDM) over RecNMP [36] (RNMP) for batch sizes (a) 8, (b) 16, and (c) 32. Opt. stands for the optimization of elimination of the redundant memory accesses                                                                                                                                                                                                                                      | 49 |

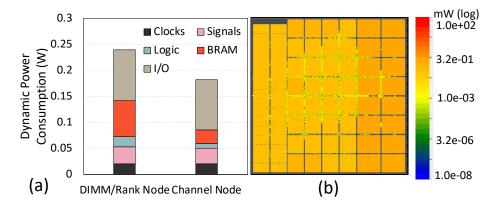

| 3.13 | (a) Dynamic power consumption breakdown of Fafnir on FPGA. (b) Power distribution of a PE in our ASIC design at 7 nm                                                                                                                                                                                                                                                                                                                 | 50 |

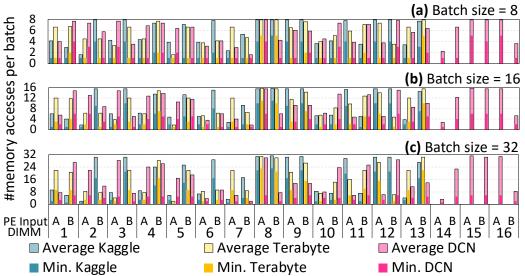

| 3.14 | Number of memory accesses at different DIMMs for three batch sizes:(a) 8, (b) 16, and (c) 32                                                                                                                                                                                                                                                                                                                                         | 51 |

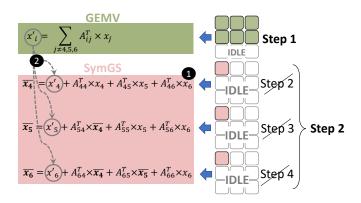

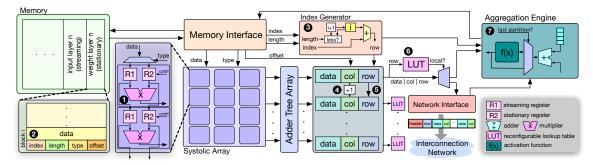

| 4.1  | Key insight of Alrescha: We divide a large SymGS into a majority of parallelizable GEMV operations (green) and a minority of <i>small</i> data-dependent SymGS (pink). We first run the GEMV and then switch to SymGS. Dependencies still exist in SymGS part but as long as it is small, we can run them in one step in hardware rather than three steps (1). Forwarding the outcomes of GEMV to the SyMGS must be fast as well (2) | 54 |

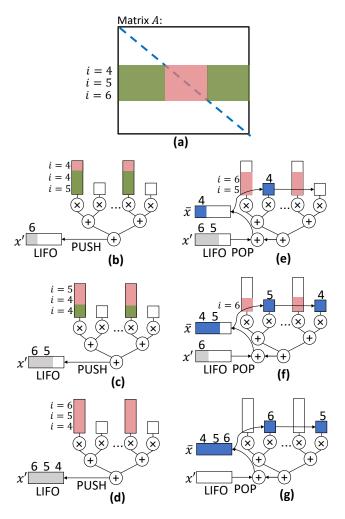

| 4.2  | Key mechanisms of Alrescha: (a) Matrix A the operand of the original large SymGS, (b, c, d) Executing GEMV and the mechanism for quickly forwarding the outcome of GEMV to SymGS using a LIFO or FIFO; and (e, f, g) Executing the small SymGS and implementing the scheme of data dependencies through the interconnections between inputs of the tree and the LIFO to quickly execute the small SymGS                              | 55 |

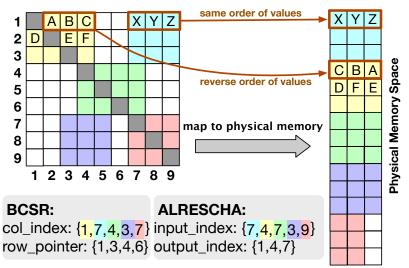

| 4.3  | Compression format of Alrescha: the col_index of BCSR and input_index (i.e., $Inx_{in}$ ) of Alrescha are color-coded to show their corresponding blocks in the matrix. Alrescha uses the index of the last column for the input index of diagonal blocks                                                                                                                                                                            | 58 |

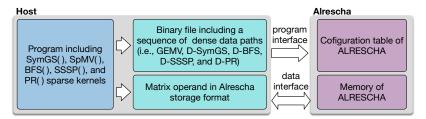

| 4.4  | The overview of Alrescha and host                                                                                                                                                                                                                                                                                                                                                                                                    | 60 |

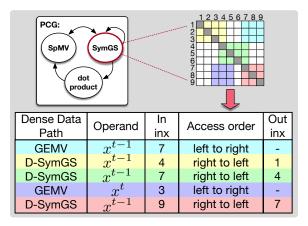

| 4.5  | The order of operations: An example of the configuration table for a SymGS kernel, in which $n = 9$ , $w = 3$                                                                                                                                                                                                                                                                                                                        | 62 |

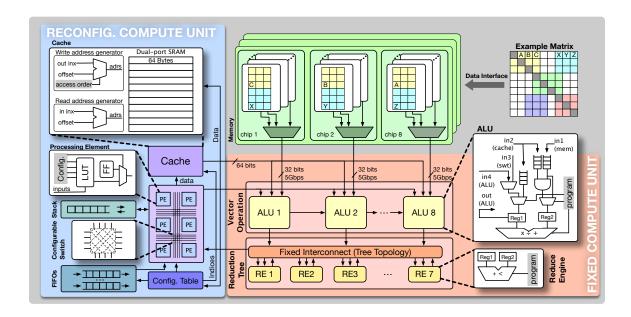

| 4.6  | The microarchitecture of Alrescha: (a) the FCU for implementing common computations, and the RCU for providing specific configuration for distinct dense data paths. Example configurations for supporting: (b) D-SymGS, (c) GEMV, and (d) D-PR.                                                                          |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

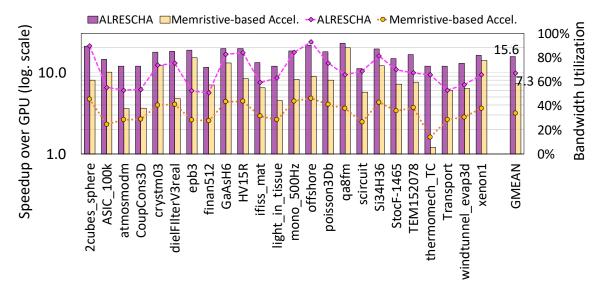

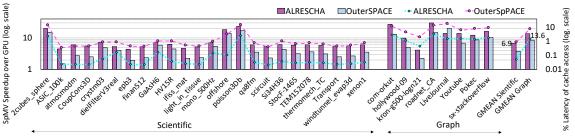

| 4.7  | Speedup: PCG algorithm on scientific datasets, normalized to GPU (bar charts), and bandwidth utilization (the lines) compared to the state-of-the-art accelerator for scientific problems [73]                                                                                                                            | 67 |

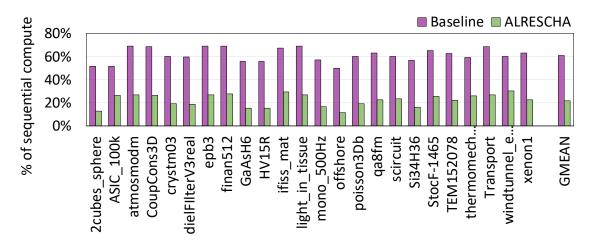

| 4.8  | Reduction in data-dependent operations: for the PCG algorithm, after applying Alrescha. The baseline shows the percentage of data-dependent operations by row-reordering optimization                                                                                                                                     | 68 |

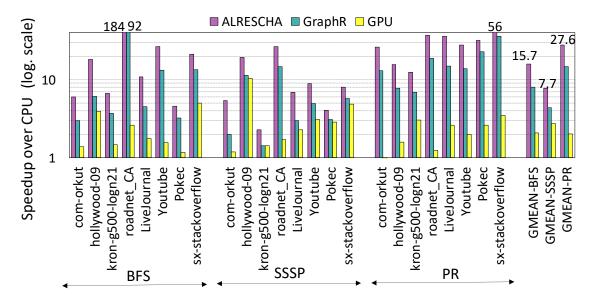

| 4.9  | Speedup: graph algorithms on graph datasets over the CPU. GraphR [72] is the state-of-the-art graph accelerator                                                                                                                                                                                                           | 69 |

| 4.10 | Speedup: executing SpMV on scientific and graph datasets normalized to GPU (bar charts), and the percentage of execution time devoted to cache accesses (the lines). OuterSPACE [69] is the state-of-the-art SpMV accelerator.                                                                                            | 70 |

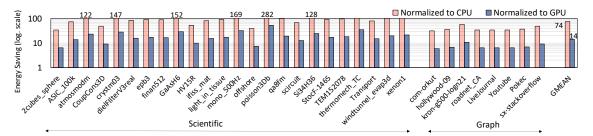

| 4.11 | Energy consumption of Alrescha normalized to CPU and GPU                                                                                                                                                                                                                                                                  | 71 |

| 5.1  | An overview of the systolic-based microarchitecture of Eridanus                                                                                                                                                                                                                                                           | 76 |

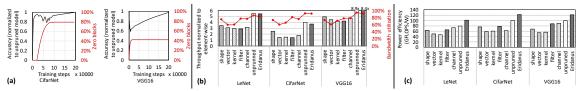

| 5.2  | The results of implementing Lodestar on Eridanus: (a) The accuracy and the percentage of zero blocks for CifarNet (pruned between step 20k, 100k) and VGG16 (pruned between steps 1, 10k). (b) Throughput and bandwidth utilization. (c) the power efficiency of three DNN models pruned by various structured techniques | 79 |

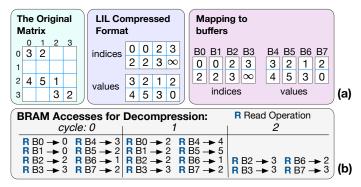

| 6.1  | (a) Compressing a sparse matrix using LIL storage. (b) Time steps of reading indices and values to decompress the non-zero rows                                                                                                                                                                                           | 84 |

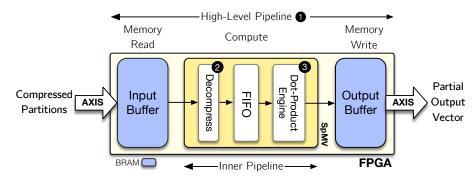

| 6.2  | The architecture of our evaluation platform: Streaming the compressed partitions of a sparse matrix from the memory to FPGA through AXI stream interfaces and processing them (i.e., SpMV) in a pipeline. The decompression component varies based on sparse format                                                       | 85 |

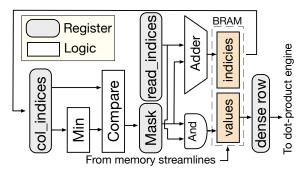

| 6.3  | The microarchitecture of Ascella for decompression                                                                                                                                                                                                                                                                        | 86 |

| 6.4  | The steps of decompression using Ascella                                                                                                                                                                                                                                                                                  | 86 |

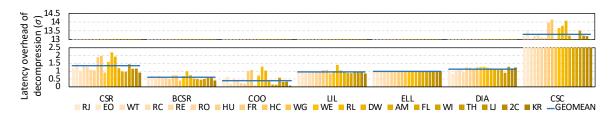

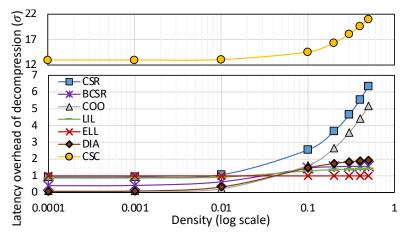

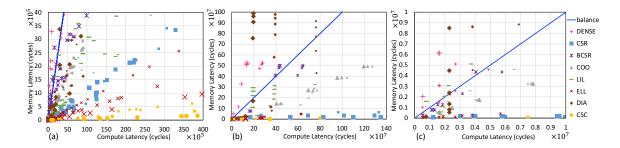

| 6.5  | Decompression overhead for SuiteSparse: comparing the latency overhead, $\sigma$ (lower is betters), of seven sparse formats for partition size of $16 \times 16$ . A darker color indicates less sparsity (i.e., higher density)               | 94 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.6  | Decompression overhead for random matrices: comparing the $\sigma$ (lower is betters) of seven formats for $16 \times 16$ partitions when density varies from 0.0001 to 0.5                                                                     | 95 |

| 6.7  | Decompression overhead for band matrices: comparing the latency overhead, $\sigma$ , of seven sparse formats for partition size of $16 \times 16$ when the width varies from 1 to 64                                                            | 95 |

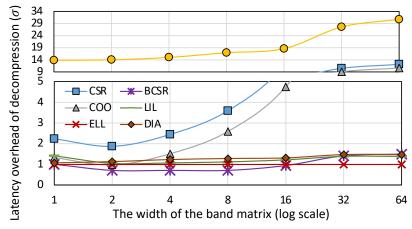

| 6.8  | Decompression overhead for various partition sizes: comparing the average $\sigma$ (lower is better) of seven sparse formats for three types of workloads (SuiteSparse, random, band) and partition sizes of 8, 16, and 32                      | 96 |

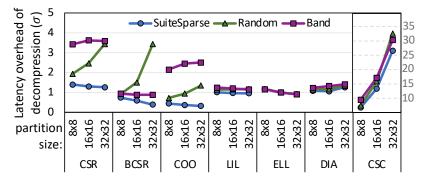

| 6.9  | Balance ratio: the relationship between the memory and compute latency for various partition sizes indicated by the size of markers for (a) SuiteSparse, (b) random workloads, and (c) band matrices. The blue line indicates balance ratio = 1 | 97 |

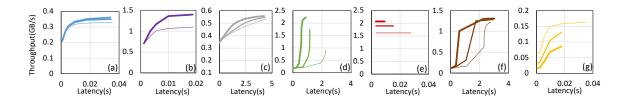

| 6.10 | Throughput vs. latency: comparing the throughput and the average time to apply SpMV on an $8000 \times 8000$ : (a) CSR, (b) BCSR, (c) COO, (d) LIL, (e) ELL, (f) DIA, and (g) CSC. Thicker lines indicate larger partition sizes                | 99 |

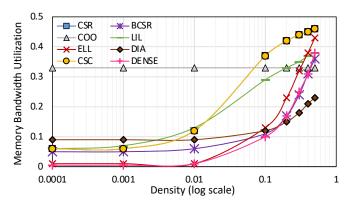

| 6.11 | Memory bandwidth utilization for random matrices: comparing seven sparse formats for partition size of $16 \times 16$ when density varies from 0.0001 to 0.5.                                                                                   | 99 |

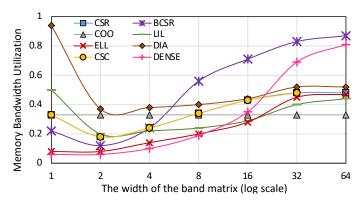

| 6.12 | Memory bandwidth utilization for band matrices: comparing seven sparse formats for partition size of $16\times16$ when the width varies from 1 to 64 1                                                                                          | 00 |

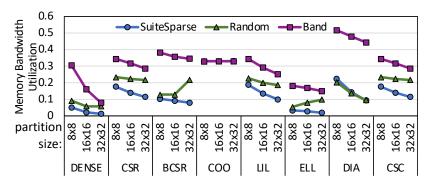

| 6.13 | Memory bandwidth utilization for various partition sizes: comparing the average memory bandwidth utilization (higher is better) on SuiteSparse, random, band workloads for partition sizes of 8, 16, and 32                                     | 00 |

| 6.14 | Dynamic power consumption: (a) logic, (b) BRAM, and (c) signals 1                                                                                                                                                                               | 02 |

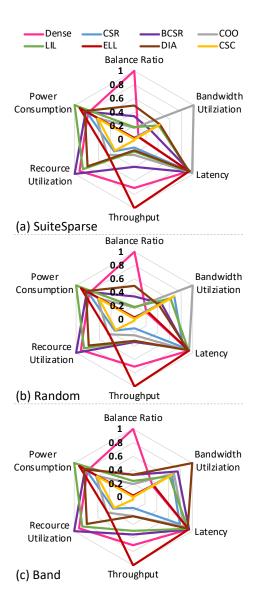

| 7.1  | Comparing sparse formats for: (a) SuiteSparse, (b) random, and (c) band matrices.  1 and 0 show best and worst, respectively                                                                                                                    | 04 |

## **SUMMARY**

Approaching the end of Moore's law has conveyed the computer architecture toward specialized hardware accelerators that have become more attractive because of the recent growing demand of compute- and memory-intensive algorithms with a high level of parallelism and/or specific patterns of data reuse (e.g., machine learning, scientific computing, and graph analytics.) The performance gained by the migration from CPUs to GPUs, FP-GAs, and ASIC has been obtained thanks to two main reasons: (i) tailoring the hardware for the requirements of the applications. This reason is more observable in the parallelizable applications such as the inference of neural networks, the performance of which can be significantly improved by heavily concurrent processors that can process hundreds of thousands of operations at a cycle (e.g. TPU); and (ii) technology scaling and thereby enabling higher clock frequency and lower switching delay. The performance gained by the implementation of a given algorithm on FPGA or ASIC is due to the second fact. Although designing hardware accelerators based on the two preceding facts has shown significant interests, that might encounter certain performance scaling limitations if they still depend on technology scaling. Independency from technology scaling indicates that unlike the general-purpose processors, specialized hardware has to be designed to utilize the maximum potential of a given hardware budget rather than to rely on extra hardware to gain performance. Based on such an approach, the specialized hardware can continue delivering gain for data- and compute-intensive dense and sparse problems.

To efficiently accelerate a problem, two ingredients are necessary (i) a balance between the computation rate and memory bandwidth, and (ii) an appropriate execution model. Since the key idea behind the specialized hardware is to not waste the compute and memory budgets, a balance between bandwidth and compute rate is necessary. This is possible by enabling stream accesses to memory from one hand by using software techniques and accelerating the computation on the other hand by using hardware techniques so that they

(data transfer and computations) work at the same pace. The second ingredient (i.e., the execution model) is closely related to the fundamental philosophy behind the specialized hardware, which supposed to have specific functionality. As the variation in the applicability of a given accelerator would be the variations in data – not the variation in the main operation, a data-driven execution model is preferred.

We seek to implement the mentioned key components on a wide range of on-demand sparse problems that we categorize into the recommendation systems, the inference of neural networks, iterative solvers of partial differential equations, and graph algorithms. The nature of each domain creates a new form of the problem. As a result, while trying to be efficient in using memory bandwidth and computation, we propose to solve the following sub-problems:

- A category of sparse problems with low data reuse rate have can potentially benefit

from state-of-the-art technologies such as near-data processing. However, the *lack of*spatial locality because of sparse accesses to memory prevent benefiting from such

efficient technologies.

- In a group of sparse problems, the efficient utilization of memory bandwidth is often the key challenge mainly because of a bottleneck in computation. Such bottlenecks that prevent benefiting from high memory bandwidth often stem in *dependencies* in computation and slow decompression mechanisms.

- Some of the sparse problems have the potential of significant parallelism. However, the *distribution* of non-zero elements in their data structure prevents them to fully benefit an efficient concurrent compute engine. In this case, even though data can be streamed efficiently, the peak *throughput* cannot be achieved.

- In super sparse data structures, using compression formats is highly beneficial in terms of storage and data transfer. However, when it comes to computation, extra

overhead of decompression is required to find the original locations of non-zero values. *Decompression* is not necessarily fast, and can create a performance bottleneck.

Some observations on the sparse problems help us to address the challenges. For instance, while the third group has the potential of revealing high compute-per-data-movement ratios, and they *allow modifications in the sparse structure*, the second group exhibit low compute-per-data-movement ratio and has stricter non-zero patterns, but they offer the chance of *transforming the mathematical expression*. Besides, we see that sparsity is orthogonal to compute-per-data-movement ratios. Therefore, the first group of sparse problems has the potential of utilizing efficient hardware designed for *dense* computation. A state-of-the-art example of such hardware is systolic arrays. Our contribution to support the rhythmic synchronous flow of data from memory to systolic arrays is to modify the distributions of the non-zero values rather than minimizing overall flops or memory footprint.

To improve the bandwidth utilization of the second group of sparse problems with data-dependent computations, we propose to extract more parallelism by mathematically transforming the computation to equivalent forms that can be easily rearranged to gain performance. Base on such transformation, we propose a light-weight reconfigurable engine that rapidly switches between the parallel and sequential parts of the sparse problem. The compute engine works with our locally-dense storage format, analogous to blocked storage formats, but with ordered values. The proposed storage format does not benefit from a specific pattern (e.g., diagonal) in sparse data structures. Instead of the traditional encoding and decoding schemes of sparse formats based on the indices of non-zero values, we propose using indices for (i) configuring the data flow simultaneously with data streaming, and (ii) placement of outputs. As a result, we use the whole available memory bandwidth for transferring payload data. Besides the reconfigurable accelerator, we proposed a fast decompression mechanism that bridges the streamlines of memory to a dense concurrent compute engine and works with well-known storage formats, supported in Python libraries.

In summary, We seek to achieve close-to-ideal performance for sparse problems, by

making the following software/hardware contributions:

- Processing data while we gather them from random locations of memory neither were they reside nor where dense computations occur.

- Mathematically transforming sparse computation to capture more parallel patterns

and running the outcome using a light-weight reconfigurable engine that enables high

utilization of memory bandwidth for scientific and graph applications.

- Proposing structured pruning algorithms for CNNs that captures dependencies in data to satisfy the data reuse patterns provided by systolic arrays.

- Sustaining a balance between computing latency and data transfer rate by avoiding streaming the unnecessary *zero* elements, and implementing fast decompression.

#### **CHAPTER 1**

#### INTRODUCTION AND BACKGROUND

Since sparse problems with several patterns of indirect memory accesses fail to effectively run on modern high-performance computers, software optimizations and hardware accelerators have been proposed to improve locality in memory accesses and enable a high degree of parallelism. However, the following unexplored challenges still exist in sparse problems, addressing which are the objective of this research. The first challenge is the lack of spatial locality that limits utilizing state-of-the-art hardware techniques for efficiently executing large-scale sparse problems. The second challenge is the limited opportunity for parallelism because several data dependencies limit utilizing the high bandwidth of the memory. The third challenge, which often occurs for the sparse problems with high data-reuse patterns (e.g., the inference of neural networks) is that the distribution of non-zero elements does not automatically match the pattern of recurrence flow of data into dense computation hardware. Finally, the compression of sparse data, often implemented for reducing memory footprint, creates a performance bottleneck. In short, the performance of running sparse problems that are memory-bounded are limited by the preceding obstacles that prevent a continuous stream of memory access. Our key insight to address the aforementioned challenges is that based on the type of the problem, we can either modify the distribution of non-zero elements, transform the computations mathematically, or change their representations. By applying such techniques, while maintaining the nature of the problem, the execution adapts more effectively to given hardware resources. Therefore, this research introduces hardware/software techniques to enable stream access to memory for accelerating sparse recommendation systems, iterative solvers of partial differential equations (PDEs), deep neural networks (DNNs), and graph algorithms.

### 1.1 Sparse Problems

Sparse data and randomness in the nature of a problem are the two main sources of sparsity and irregular memory accesses, resulting in the major problem of costly data movement [1, 2, 3, 4, 5, 6, 7, 8]. The challenge of irregular memory accesses, first identified as a major challenge in the high-performance computing (HPC) community [9], is now an obstacle to a wider range of applications in which *randomness in the nature of a problem* contributes to creating irregular memory accesses, with applications in various domains, from robotics to recommendation systems, a growing application domain that captures sparse gathering. This category of sparse problems includes a data set that randomly gets accessed. For instance, in robotics, while a robot moves and observes objects, it needs to access data corresponding to those objects which are not necessarily co-located in memory [8]. Therefore, in this category, data is dense, but the *pattern of accesses to memory is sparse*. In the following, we first describe sparsity in recommendation systems, after which we explain sparsity in the other category of sparse problems (i.e., scientific computing, neural networks, and graph analytics), in which data is sparse.

To recommend content such as music, video, and products to users, recommendation systems are broadly used throughout industry [10, 11, 12]. The recommendation systems consist of (i) embedding tables, the sets of embedding vectors that contain users' data and features, followed by (ii) neural networks, including fully connected [13] and/or rectified-linear-unit [10] layers. To recommend content, first, the related embedding vectors are gathered from the embedding tables. Then, a simple reduction operation (e.g., element-wise summation, minimum, average) is applied to the gathered embedding vectors to derive a single vector, which is then sent to the neural networks for further processing. While embedding tables are dense, looking them up causes random memory accesses, which results in the sparse gathering. Therefore, embedding lookup is the *sparse* and the memory-bandwidth-hungry part of the recommendation system. Besides, the embedding lookup

and the reduction operations capture lower computation intensity and more cache misses compared to neural networks [12]. Such characteristics put recommendation systems in the memory-bound region of the roofline model of CPUs and far below the ceiling [14] because of memory bandwidth underutilization.

Recommendation systems that create a big portion of execution cycles at data centers, for instance, 65% of artificial-intelligence cycles in Facebooks data-center [12], are just one example of sparse problems. Sparse problems are everywhere. For instance, scientific computing and graph analytics that create more than 96% of todays supercomputer workloads are sparse, too. In scientific computing, solving partial differential equations (PDEs) is a key component, which is used for modeling physical phenomena in several domains from biology to chemical science. To model a physical phenomenon using PDEs and solving them using digital computers, the first step is to discretize it into a grid and represent them as a linear system of algebraic equations: Ax = b. Discretization, however, does not occupy all the points in a 3D grid. As a result, the coefficient matrix A, used for representing the PDEs as a system of linear equations is sparse. When such a system is too large to be solved by direct methods, they can be solved by iterative algorithms such as preconditioned conjugate gradient (PCG) methods. The execution time of the PCG algorithm is dominated by two kernels, SpMV, a parallelizable algorithm, and SymGS that includes several dependencies. By assuming a vector  $(b_{1\times m})$  and a matrix  $(A_{m\times n})$  as operands, each elements of output vector  $x_{1\times n}$  is  $x_j = \sum_{i=1}^k b[A^T\_ind_i] \times A^T\_val_{ij}$  for SpMV, and  $x_j^t = \frac{1}{A_{jj}^T} - (b_j - \sum_{i=1}^{j-1} A_{ij}^T \times x_i^t - \sum_{i=j+1}^n A_{ij}^T \times x_i^{t-1})$  at each iteration (t) of SymGS.

In some other cases, such as in neural networks, although initially, data is not sparse, we make them sparse to eliminate storing unnecessary data and unnecessary computation. Neural networks are becoming more and more popular in many applications from image processing to financial problems. Once we train a neural network, several weights get close-to-zero values. As a result, a common practice is to prune those small values because they do not impact the end result. Therefore, *the 2D matrix representation of the neural*

network is sparse. A popular example of neural networks is convolutional neural networks (CNNs). The sparse inference of CNNs can be done by using well-studied sparse matrix multiplication approaches that are applicable to inference by converting convolutions to  $O_{K\times WH} = \mathbf{W}_{K\times F^2C} \times \mathbf{I}_{F^2C\times WH}$ , in which K filters of size  $F\times F\times C$  are applied to  $W\times H\times C$  images. Accelerating this general matrix-matrix multiplication (GEMM), the first operand of which is sparse, is one of the goals of this research.

Graph algorithms are the other sparse problems with several applications from social science to biology and physics. Since in a graph, not all the nodes are connected, *the adjacency matrix that represents the edges of a graph is sparse*. The sparse adjacency matrix is processed by algorithms such as breadth-first search (BFS), single-source shortest path (SSSP), and page rank (PR), all of which are similar to SpMV.

#### 1.2 Contributions

The contributions of this thesis revolve around efficiently accelerating the execution of sparse problems that as mentioned earlier, are the main component in several crucial domains such as robotics, recommendation systems, machine learning, computer vision, graph analytics, and scientific computing that remarkably impact human life. For instance, modeling/simulating a vaccine or predicting an earthquake are examples of sparse scientific computing that can save lives if done accurately and promptly. In 2020, several supercomputers from Google Could, Amazon Web Service, Microsoft Azure, and IBM, running on over 136 thousand nodes containing five million processor cores and more than 50 thousand GPUs [15] for vaccine development is compelling evidence of the importance of sparse scientific computations. However, modern high-performance computers equipped with CPUs and/or GPUs are poorly suited to these sparse problems, utilizing a tiny fraction of their peak performance (e.g., 0.5% - 3% [16]). Such conventional architectures are mainly optimized to handle *complex computation* rather than the *complex memory accesses* that are essential for sparse problems. The contradiction between the abilities of the hardware and

the nature of the problem causes sparse problems to waste extra hardware budget (high power and dollar cost) for higher performance. The goal of this thesis is to propose effective solutions that utilize the maximum potential of a given hardware budget to accelerate sparse problems. To be impactful in achieving the goal, our research suggests that software and hardware must be co-optimized. To date, several software- and hardware-level optimizations have been proposed to accelerate sparse problems; however, since they optimize either the software or the hardware in isolation, they have not fully resolved the challenges of sparse problems. Table 1.1 summarizes the common challenges of sparse problems, examples of sparse applications that suffer from these challenges, as well as the contributions of this thesis to resolving these challenges along with the broader impact that this thesis would have, as explained in the following.

Table 1.1: The challenges and applications of sparse problems, our contributions and publications to resolve the challenges, and the broader impacts that this research would have.

| Challenges           | Irregular and inefficient memor accesses                                     | Data dependencies                                                                             | Slow decompression                                                                                     | Computation underutilization                                                               |

|----------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Application          | Recommendation systems Scientific computing and graph analytics              |                                                                                               | d graph analytics                                                                                      | Computer vision                                                                            |

| Our<br>Contributions | Proposed an intelligent tree near memory to reduce data while gathering them |                                                                                               | Co-optimized<br>compression format and<br>hardware to establish a<br>balanced streaming<br>from memory | Modified the distribution of non-zero data rather than minimizing their count              |

| Our Publications     | Fafnir [HPCA'21]                                                             | Alrescha [HPCA'20]                                                                            | Ascella [DATE'20]                                                                                      | Lodestar [DAC'19]<br>Eridanus [IEEE Micro'19]                                              |

| Broader Impact       |                                                                              | ccelerating large-scale, critica<br>ch as vaccine development or<br>disaster such as earthqua | timely predicting natural                                                                              | Enabling accurate and fast manufacturing, financial services, healthcare, and agriculture. |

**Fafnir** — Irregular random memory accesses are an obstacle in large-scale applications, such as recommendation systems, that not only are widely used in industry for e-commerce and entertainment but also have broader applications in domains such as e-learning and healthcare. To reduce the amount of data movement and thereby better utilize memory bandwidth, previous studies have proposed near-data processing (NDP) solutions for recommendation systems. The issue of prior proposals, however, is that they either minimize data movement effectively at the cost of limited memory parallelism or improve memory parallelism (up to a certain degree) but cannot successfully decrease data movement, as they rely on spatial locality (an optimistic but not realistic assumption) to utilize the NDP.

Besides, neither approaches propose a solution for *gathering* data from random memory addresses; rather they just offload operations to NDP. To deal with the mentioned challenges, in **chapter 3**, we propose an efficient near-memory intelligent reduction (Fafnir)[17] tree, the leaves of which are all the units in a memory system, and the nodes gradually apply reduction operations while data is gathered from *any* memory unit. Fafnir does not rely on spatial locality; therefore, it minimizes data movement by performing *entire* operations at NDP and fully benefits from parallel memory accesses. Fafnir also offers other advantages such as eliminating redundant memory accesses without using costly and less effective caching mechanisms and being applicable to other sparse problems such as scientific computation and graph analytics. We implement Fafnir on an FPGA and in 7 nm ASAP ASIC. Our evaluation shows that Fafnir executes recommendation systems 21.3× more quickly than the state-of-the-art NDP proposal. Besides, the generic architecture of Fafnir allows the execution of the classic sparse problems using the same proposed 1.2 mm<sup>2</sup> chip up to 4.6× more quickly than the state of the art.

Alrescha — The next unsolved challenge in sparse problems (e.g., in scientific computing) is data dependency, which limits utilizing the available memory bandwidth. To minimize the negative impact of data dependencies on performance, in **chapter 4**, we propose a lightweight reconfigurable sparse-computation accelerator (Alrescha) [18], the key insight of which is to convert the mathematical dependencies to gate-level dependencies to reduce the critical-path latency. As a result, even dependent instructions can be executed mostly in parallel. Based on this insight, Alrescha breaks down a sparse problem into a majority of parallel and a minority of small data-dependent instructions that can be executed quickly (in fewer cycles) in hardware. Besides the fast execution of small data-dependent parts, Alrescha smoothly implements the switching between two groups of operations, which is the other essential requirement in achieving better performance. To do so, Alrescha modifies the execution order of operations. To provide a platform with the aforementioned characteristics, Alrescha makes two main contributions. First, it implements a compute engine

with a fixed compute unit for the parallel parts and a lightweight reconfigurable engine for the execution of the data-dependent parts. Second, Alrescha benefits from a locally dense storage format, with the right order of non-zero values to yield the order of execution dictated by the hardware. The combination of the lightweight reconfigurable hardware and the storage format enables uninterrupted streaming data from memory. Our evaluations show that Alrescha executes sparse scientific computing, including solving partial differential equations,  $15.6\times$  faster than GPUs. Moreover, compared to GPUs, Alrescha consumes  $14\times$  less energy. Thanks to its dynamic and partial reconfigurability, Alrescha can accelerate problems such as graph analytics with wide applications in social sciences, linguistics, biology, and any problem that can be represented as a graph. Alrescha processes graphs  $8\times$  faster than GPUs.

**Lodestar & Eridanus** — The next studied challenge of sparse problems is the underutilization of computation units, which concerns an isolated hardware optimization that is not effective without considering software. An example of such effort is accelerating the inference of convolutional neural networks (CNNs) using systolic arrays, the highly parallel arrays of multiplication and accumulation (MAC) units for performing matrix multiplication. However, the dense structure of systolic arrays contradicts the sparse nature of CNN inference and leads to underutilization of computation. To address this challenge, in **chapter 5**, we proposed creating locally-dense CNNs for efficient inference on systolic arrays (Lodestar) [5]. Lodestar is a structured pruning approach that produces CNNs, the non-zero values of which are clustered spatially into locally dense regions that can be compactly stored and efficiently streamed from memory. Lodestar consists of two key insights: (i) To capture the data reuse pattern in systolic arrays and enable data streaming, modifying the distribution of non-zero values is more influential than minimizing the number of operations or the memory footprint; and (ii) Examining the correlation among the filters rather than the individual filters increases the chances of creating a systolic-friendly model. To utilize Lodestar for streaming data from memory through systolic arrays, we proposed

efficiently running the inference of CNNs using systolic arrays (Eridanus) [19]. Eridanus handles the timing and indexing of streaming blocks of data. The evaluations show that Lodestar and Eridanus run CNN inference 8.4× faster than the state of the art. Although by utilizing proposed techniques we can achieve the high *throughput* offered by the MAC-based systolic arrays, achieving low *latency* and scalability will still be key challenges. To resolve these challenges, we proposed multiplying matrices efficiently in a scalable systolic architecture [20], which compared to state-of-the-art systolic arrays, offers 1.83× better single-batch inference latency by separating multipliers from the adders rather than combining them in a unified array of MACs.

Ascella — The other challenge of sparse problems concerns compression, a common software approach for storing and transferring sparse data. Although compression allows efficient data transfer, it can potentially create a computation bottleneck. This challenge is not only unresolved but also becomes more serious with the advent of domain-specific architectures (DSAs), as they intend to more aggressively improve performance. The performance implications of using compression along with DSAs have not been studied by prior work. To fill this gap of knowledge, in **chapter 6**, we introduce Ascella [21] that characterizes the performance implications of compression formats used in sparse workloads based on six key metrics, including memory bandwidth utilization, resource utilization, latency, throughput, power consumption, and balance ratio.

Ascella leads architects to knowingly choose the required sparse format and tailor their DSA for their target sparse applications, if necessary. For instance, this study helps accelerate sparse computation by enabling parallel stream accesses to memory, based on two main ingredients: (i) using a compression format that on one hand assures streaming only the non-zero values, and on the other hand, is easy to decompress using simple logic; and (ii) proposing a computation engine that follows the speed of memory streaming. To enable the latter, the central building block is optimizing the decompression

mechanism. Therefore, Ascella balances memory and computation latency while streaming blocks of data from memory into a DSA. More specifically, unlike in Figure 1.1a, where the memory and compute latency are not matched, in Figure 1.1b (Ascella), they are almost similar – the black and orange lines are close. Furthermore, Ascella reduces the maximum latency of streaming a block from 2200ns to 800ns as indicated by comparing the black line in Figure 1.1a and the lines in Figure 1.1b.

Figure 1.1: Memory and computation latency for streaming blocks for (a) prior work, and (b) Ascella. Closer memory and compute is better

#### 1.3 Thesis Statement

Since sparse problems have specific patterns of memory accesses, they cannot run efficiently on the general-purpose processors. Thus, to keep gaining performance for sparse problems from a given hardware budget, hardware/software co-optimization is necessary.

## **CHAPTER 2**

#### LITERATURE SURVEY AND THE GAP OF KNOWLEDGE

This chapter overviews the prior studies on sparse problem that are mostly related to the directions of this thesis. We mainly categorize them as specialized hardware and software techniques. First, this chapter summarizes the hardware solutions for sparse recommendation systems, neural networks, sparse matrix algebra, and scientific computing. Then, it outlines the software techniques for dealing with sparsity in neural networks as well as the common compression formats that are used in a wide range of sparse applications with various sparsity patterns.

## 2.1 Specialized Hardware for Sparse Acceleration

In this section, we overview the prior domain-specific hardware architectures that target various applications including recommendation systems, neural networks, sparse matrix algebra, and scientific computing.

### 2.1.1 Near-Data Processing for Recommendation Systems

Despite common efforts to reduce the embedding vector dimension [22] or the number of embedding vectors [14], the embedding tables occupy multiple gigabytes of memory. Such constraints necessitate the distribution of the embedding tables across multiple memory devices to satisfy memory capacity requirements [13]. Sparse gathering from random addresses scattered over a large memory system requires maximizing memory-bandwidth utilization. However, the *processor-centric* organization of CPUs and GPUs and the reused-optimized structure of their memory hierarchy, conspire against the efficient and fast sparse gathering. As a result, recommendations systems demand *data-centric* near-data processing (NDP) solutions to process data (i.e., the embedding vectors) where they reside.

NDP solutions have been explored to reduce costly data movement, a major problem of sparse problems [23, 24, 25, 6, 26, 27]. For instance, Gao et al. [23] have placed simple processing cores near hybrid memory cube (HMC) [28] and High Bandwidth Memory (HBM) [29] to propose an efficient and practical solution for data analytics including deep neural networks and graph processing. In another work, Gao et al. have proposed Tetris [26], a neural network accelerator that places an array of processing elements (PEs) close to HMC. To do this, it optimizes the size of the PE array to fit it near vaults of HMC. The programmability and scalability of NDP solutions for accelerating neural networks have been studied by Kim et al. [30] and Ahn et al. [27]. Other NDP studies have focused on accelerating graph and HPC problems, in which the majority of the operations (e.g., 80%) are sparse gathering [31]. To take advantage of 3D-DRAM-based NDP for graph processing, Nai et al. [6] have proposed GraphPIM, to offload instructions close to memory in a non-intrusive way without requiring programmers effort or ISA changes. Several other NDP solutions [2, 3, 4, 7] have proposed offloading computation to memory to reduce data movement and leverage NDP to accelerate data access and facilitate computations on sparse data structures [32, 33, 1]. Additionally, DIMMNet [34] has been proposed to accelerate gathering irregular memory accesses.

The aforementioned NDP solutions, however, are not very effective for embedding lookup of recommendation systems for several reasons. First, they decrease data movement by *rearrangement*, but do not perform *reduction* operations. Second, they are costly, as they copy a page to another in a scratchpad memory (e.g.,[31]). Finally, they are not transparent to the software. Therefore, prior work has proposed specific NDP solutions, namely TensorDIMM [35], RecNMP [36], and Centaur [37] for recommendation systems. TensorDIMM [35] splits the embedding vectors across DIMMs to utilize rank-level parallelism for reading *individual* embedding vectors. Accordingly, it splits the reduction operations across the DIMMs. As a result, TensorDIMM successfully performs all reductions at DIMMs and minimizes data movement from memory to the cores by sending only out-

come vectors rather than all embedding vectors. However, the downside of TensorDIMM is that it does not sufficiently utilize memory parallelism because it uses column-major order, which fundamentally breaks the row-buffer locality in the DRAM system. As opposed to TensorDIMM [35], RecNMP [36] utilizes rank-level parallelism for reading *distinct* embedding vectors. Thus, the performance of RecNMP scales better as more ranks are added to the memory system.

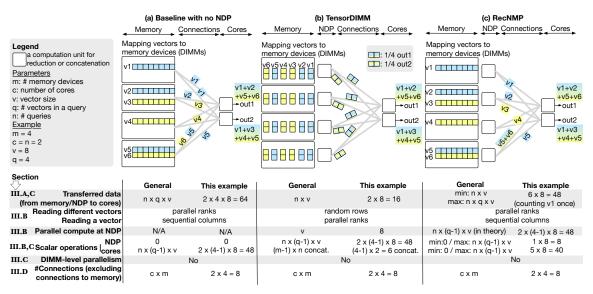

Despite the advantages of NDP solutions for accelerating the inference of recommendation systems, they left unsolved a few key challenges of *sparse gathering*. In the following, we elaborate on different challenges, solving some of which have been the target of a prior study that in turn causes the other challenges. Data movement has been the main concern of sparse gathering. For instance, as Figure 2.1a shows, to apply two non-compute-intensive reduction operations (i.e., v1 + v2 + v5 + v6 and v1 + v3 + v4 + v5) on six embedding vectors (i.e., v1, v2, v3, v4, v5, and v6), the vectors must be transferred to cores. For example, vector 5 (v5) is required by two queries; thus, it is transferred twice. In general, to perform vale vale

Even though TensorDIMM effectively reduces data movement, it is not as effective in sufficiently utilizing row-buffer hits because it uses column-major order, which fundamentally breaks the row-buffer locality in the DRAM system. More specifically, while TensorDIMM can utilize rank-level parallelism to read the elements of individual embedding vectors, split over different DIMMs, it must access random rows to read *distinct* embedding vectors in a query (e.g. vectors of query 1 including v1, v2, v5, and v6). Accordingly, only

Figure 2.1: Comparing NDP-based solutions for embedding lookup: (a) Baseline with no NDP, (b) TensorDIMM [35], and (c) RecNMP [36].

v scalar operations can be performed in *parallel* at NDP. Although TensorDIMM performs all  $n \times (q-1) \times v$  operations at NDP, only v of them are processed in *parallel*, while the rest can be *pipelined*. For instance, for query 1, all DIMMs do the following subsequently: read their own part of v1 from a row (but not necessarily reading the entire row buffer), then read v2 from another row, do a partial sum of size v/m (v1+v2), simultaneously access another row to read v5, add it to the partial sum while reading v6 from another row. This approach particularly disturbs achieving low latency.

Splitting embedding vectors across more ranks causes poor utilization of row-buffers (i.e., we must open a row, but read a *smaller* fraction of it). To improve parallel computation at NDP, RecNMP [36] distributes embedding vectors across the ranks, as shown in Figure 2.1c. In this approach, reading *distinct* embedding vectors utilizes rank-level parallelism, while elements of each vector are read from sequential columns. As a result, RecNMP can more effectively increase rank-level parallelism by adding more ranks to the system. However, the downside of this approach is that even though in theory entire operations for all queries (i.e.,  $n \times (q-1) \times v$ ) can be performed in parallel at NDP, RecNMP might not achieve it because of imperfect spatial locality.

Although RecNMP utilizes rank-level parallelism in reading distinct embedding vec-

DIMM-level parallelism. In many real-world applications, embedding vectors of a query are scattered over many random DIMMs, where DIMM-level parallelism (i.e., channel-level reduction) is essential. For instance, based on the birthday paradox, the probability of having a query with indices on the same channel is only up to 25% in a four-channel system. Consequently, as in many cases, the raw data needs to be transferred to the cores, memory bandwidth may not be fully utilized. Thus, even though under perfect circumstances, maximum  $n \times (q-1) \times v$  operations can be done at NDP, in the worst case, all of them might need to be done at the cores. For instance, in Figure 2.1c, only two embedding vectors (i.e., v5 and v6) are reduced at NDP, and others are forwarded to the cores. Relying on spatial locality has two other consequences. First, increasing batch size does not necessarily result in more utilization of parallel computation at NDP, hence achieving higher throughput. Second, while in the perfect scenario only n output vectors (i.e.,  $n \times v$  elements) are transferred from the memory to the cores, in the worst case, all  $n \times q \times v$  elements must be transferred. Therefore, reducing data movement is also not guaranteed.

The other challenge of implementing embedding lookup is the overhead of connections. As the embedding tables are often large, they necessitate model parallelism (i.e., splitting and distributing tables across memory devices), as shown in Figure 2.1a. On the other hand, the neural network layers of the embedding systems are small enough to utilize data parallelism (i.e., mapping copies of a neural network on different computing devices). The combination of model parallelism for embedding tables and data parallelism for neural networks in recommendation systems requires costly all-to-all connections [13] (e.g., Figure 2.1a) between the memory devices and computing devices (e.g., CPU or GPU cores) so that embedding vectors can be gathered from any memory device and be forwarded to any computing device. The previous studies have not proposed any solutions to reduce the number of connections. Therefore, similar to the baseline, they all require  $c \times m$  connections to implement all-to-all communication, which is not only costly but also limits the

scalability. To accelerate sparse gathering and prevent the communication from becoming a bottleneck, Centaur [37] uses high-bandwidth communication links and then applies the reduction operations in a separate unit. Thus, unlike TensorDIMM, Centaur does not reduce data movement but instead transfers data more quickly.

The last challenge of implementing NDP solutions for embedding lookup is eliminating extra memory accesses. Observations suggest that a batch of queries has common embedding vectors. Thus, not all the memory accesses corresponding to every single embedding vector are necessary. RecNMP [36] proposes using caches at NDP. Caching, however, is not the most effective solution, as no more than a 50% hit rate can be achieved [36]. Furthermore, even achieving such a hit rate requires a 128 KB cache that adds extra hardware overhead (e.g., 38% area [36]). Besides, the cache accesses can potentially cause a performance bottleneck.

### 2.1.2 Hardware Accelerators for Neural Networks

Various types of hardware accelerators have been proposed to efficiently execute neural networks. In the following, we summarize five categories of them.