### PERFORMANCE PRIMITIVES FOR ARTIFICIAL NEURAL NETWORKS

A Thesis Presented to The Academic Faculty

by

Marat Dukhan

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Computational Science and Engineering

Georgia Institute of Technology May 2021

# PERFORMANCE PRIMITIVES FOR ARTIFICIAL NEURAL NETWORKS

#### Approved by:

Professor Edmond Chow, Committee Chair School of Computational Science and Engineering

Georgia Institute of Technology

Professor Richard Vuduc, Advisor School of Computational Science and Engineering Georgia Institute of Technology

Professor Irfan Essa School of Interactive Computing Georgia Institute of Technology Professor Robert van de Geijn Department of Computer Sciences The University of Texas at Austin

Nicolas Vasilache

$Google\ Research$

Jeff Hammond

*NVIDIA*

Date Approved: 30 April 2021

# TABLE OF CONTENTS

| LIS           | о Т           | F TAE  | BLES                                | vi  |  |  |

|---------------|---------------|--------|-------------------------------------|-----|--|--|

| LIS           | вт О          | F FIG  | URES                                | vii |  |  |

| $\mathbf{SU}$ | MM.           | ARY .  |                                     | xi  |  |  |

| Ι             | INTRODUCTION  |        |                                     |     |  |  |

| II            | CO            | NVOL   | UTIONAL NEURAL NETWORKS             | 5   |  |  |

|               | 2.1           | Fully  | Connected Layers                    | 8   |  |  |

|               | 2.2           | Convo  | olutional Layers                    | 12  |  |  |

|               |               | 2.2.1  | im2col+GEMM algorithm               | 18  |  |  |

|               |               | 2.2.2  | Fast Convolution algorithms         | 20  |  |  |

| III           | PR            | IMITI  | VES FOR HIGH-INTENSITY CONVOLUTIONS | 30  |  |  |

|               | 3.1           | Introd | luction                             | 30  |  |  |

|               | 3.2           |        |                                     |     |  |  |

|               |               | 3.2.1  | Layout of FFT coefficients          | 34  |  |  |

|               |               | 3.2.2  | Composition of 2D FFTs              | 34  |  |  |

|               |               | 3.2.3  | Fused Butterfly Operations          | 36  |  |  |

|               | 3.3           | Winog  | grad Transforms                     | 37  |  |  |

|               | 3.4           | Matrix | x Multiplication                    | 38  |  |  |

|               | 3.5           | Perfor | mance                               | 39  |  |  |

|               | 3.6           | Curre  | nt Limitations and Future Work      | 44  |  |  |

|               | 3.7           | Concl  | usion                               | 44  |  |  |

| IV            | $\mathbf{PR}$ | IMITI  | VES FOR LOW-INTENSITY CONVOLUTIONS  | 46  |  |  |

|               | 4.1           | Introd | luction                             | 46  |  |  |

|               |               | 4.1.1  | Limitations                         | 48  |  |  |

|               | 4.2           | The In | ndirect Convolution algorithm       | 48  |  |  |

|               |               | 4.2.1  | GEMM Primitive                      | 49  |  |  |

|               |               | 4.2.2  | From GEMM to Indirect GEMM          | 50  |  |  |

|              |     | 4.2.3  | Indirection Buffer                                         | 53  |

|--------------|-----|--------|------------------------------------------------------------|-----|

|              | 4.3 | Experi | imental Evaluation                                         | 54  |

|              |     | 4.3.1  | Experimental Setup                                         | 55  |

|              |     | 4.3.2  | Experimental Results                                       | 59  |

|              | 4.4 | Analys | sis                                                        | 60  |

|              | 4.5 | Conclu | asion                                                      | 61  |

| $\mathbf{V}$ | PRI | MITI   | VES FOR SPARSE CONVOLUTIONS                                | 63  |

|              | 5.1 | Sparse | Inference                                                  | 64  |

|              | 5.2 | Consti | raints on Computer Vision models                           | 67  |

|              | 5.3 | SpMM   | Primitive                                                  | 70  |

|              | 5.4 | Experi | imental Evaluation                                         | 73  |

|              |     | 5.4.1  | Platform                                                   | 73  |

|              |     | 5.4.2  | Protocol                                                   | 73  |

|              |     | 5.4.3  | Pixelwise Convolutions                                     | 74  |

|              |     | 5.4.4  | Randomized Models                                          | 76  |

|              |     | 5.4.5  | End-To-End Models                                          | 78  |

|              | 5.5 | Conclu | ısion                                                      | 79  |

| VI           | PRI | IMITI  | VES FOR SOFTMAX                                            | 81  |

|              | 6.1 | The T  | hree-Pass Algorithm                                        | 83  |

|              | 6.2 | The T  | wo-Pass Algorithm                                          | 85  |

|              | 6.3 | Theore | etical Analysis                                            | 89  |

|              | 6.4 | Experi | imental Evaluation                                         | 90  |

|              |     | 6.4.1  | Platform                                                   | 90  |

|              |     | 6.4.2  | Protocol                                                   | 90  |

|              |     | 6.4.3  | Implementation                                             | 91  |

|              |     | 6.4.4  | The Three-Pass Algorithms and Bandwidth Saturation $\ \ .$ | 93  |

|              |     | 6.4.5  | The Two-Pass Algorithm                                     | 98  |

|              |     | 646    | Multi-Threaded Performance                                 | 100 |

|        | 6.4.7  | Comparison with Intel DNNL           | 02 |

|--------|--------|--------------------------------------|----|

|        | 6.4.8  | Validation on Alternative Processors | 04 |

| 6.5    | Conclu | usion                                | 05 |

| VII CO | NCLU   | SION                                 | 07 |

| REFER  | ENCE   | $\mathbf{cs}$                        | 10 |

# LIST OF TABLES

| 1  | Single-core performance on MobileNet v3 Large model on TensorFlow<br>Lite framework with the XNNPACK inference engine                                                               | 5  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | 2D image tensor layouts in popular neural network frameworks                                                                                                                        | 8  |

| 3  | Shape of input, output, and weights matrices in a fully-connected layer                                                                                                             | Ĝ  |

| 4  | High-performance BLAS implementation for popular platforms                                                                                                                          | 20 |

| 5  | Configurations of parameters in convolutional layers in early CNN architectures                                                                                                     | 30 |

| 6  | Instruction characteristics on Intel Skylake [26]                                                                                                                                   | 33 |

| 7  | Configurations of convolutional layers in performance evaluation $\dots$                                                                                                            | 40 |

| 8  | Transformation costs, measured through FP_ARITH_INST_RETIRED hardware counter                                                                                                       | 44 |

| 9  | Characteristics of mobile devices in performance evaluation. Microarchitecture (uArch) is specified for the big cores                                                               | 55 |

| 10 | Types and count of Convolution operators in SqueezeNet 1.0 and ResNet-18 models. Convolutions with identical parameters are counted only once                                       | 59 |

| 11 | Geomean performance of modified GEMM primitive relative to standard GEMM primitive on 1x1 and non-1x1 Convolutions in ResNet-18 model                                               | 59 |

| 12 | Geomean performance of modified GEMM primitive relative to standard GEMM primitive on 1x1 and non-1x1 Convolutions in SqueezeNet 1.0 model                                          | 59 |

| 13 | Parameters of the first convolution in mobile-optimized computer vision models                                                                                                      | 67 |

| 14 | Comparison of dense and sparse model sizes, flops, and inference latencies. All times are in milliseconds. *This model uses 80% unstructured sparsity in all pointwise convolutions | 78 |

| 15 | Characteristics of several public machine learning datasets                                                                                                                         | 82 |

| 16 | Theoretical analysis of memory complexity and bandwidth costs of the three softmax algorithms                                                                                       | 89 |

| 17 | Characteristics of the Intel Xeon W-2135 processor used for experimental evaluation of the softmax algorithms                                                                       | 90 |

# LIST OF FIGURES

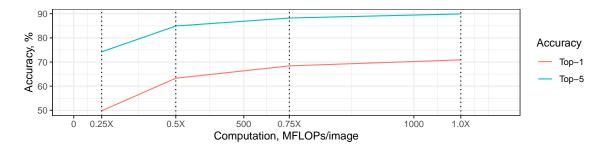

| 1  | Accuracy and inference computations for the MobileNet v1 family of neural network architectures                                                                                                                               | 1  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

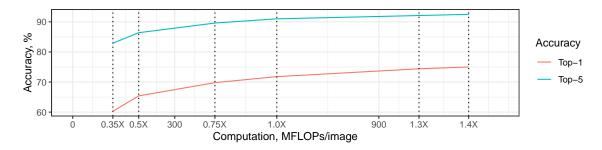

| 2  | Accuracy and inference computations for the MobileNet v2 family of neural network architectures                                                                                                                               | 2  |

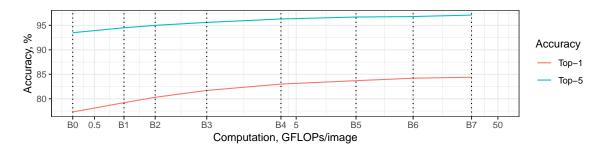

| 3  | Accuracy and inference computations for the EfficientNet family of neural network architectures                                                                                                                               | 2  |

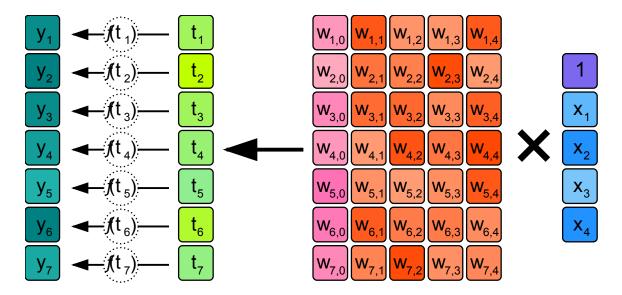

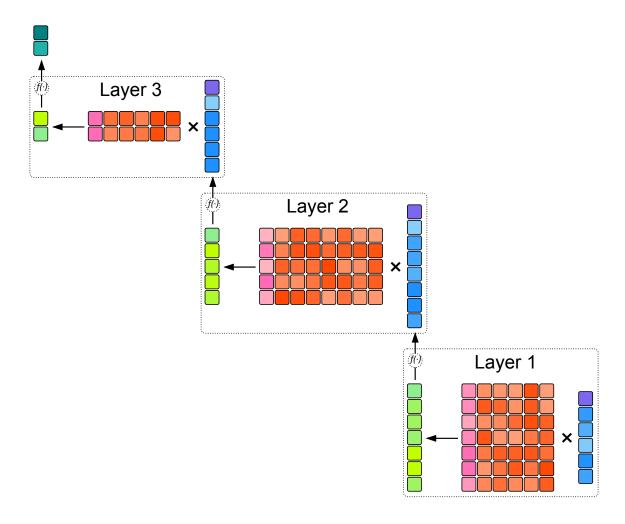

| 4  | Traditional neural network layer with 4 input and 7 output neurons $$ .                                                                                                                                                       | 5  |

| 5  | Example of a deep neural network with three layers                                                                                                                                                                            | 6  |

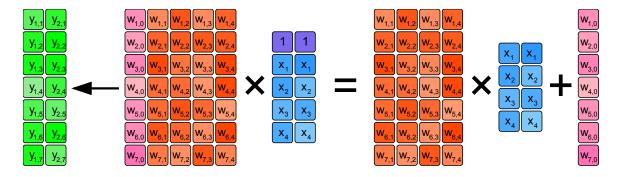

| 6  | The representation of a fully connected layer with implicit unit inputs as a matrix-matrix multiplication with bias. The bias is broadcasted along the column dimension and added to each column of the weights-input product | 9  |

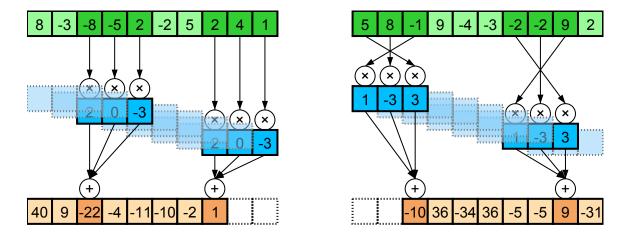

| 7  | One-dimensional cross-correlation (left) and convolution (right). The key difference is the traversal order of the kernel over the input                                                                                      | 13 |

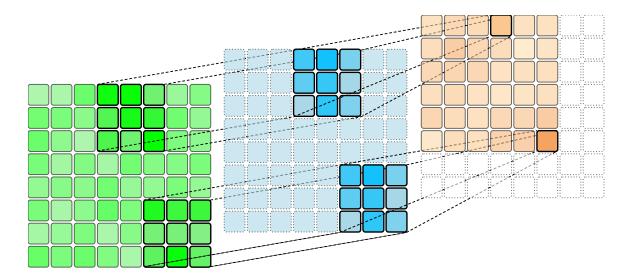

| 8  | Two-dimensional cross-correlation. A 2D kernel (middle) slides along the 2D input (left) to produce elements of the 2D output (right). The same kernel elements are reused at different positions of the input                | 14 |

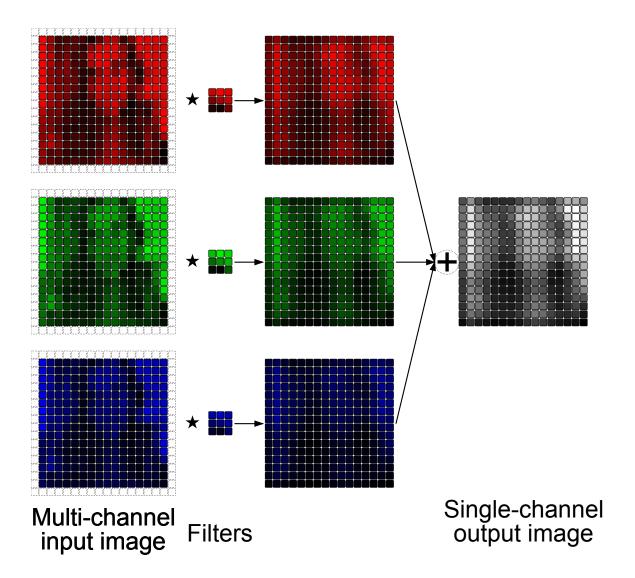

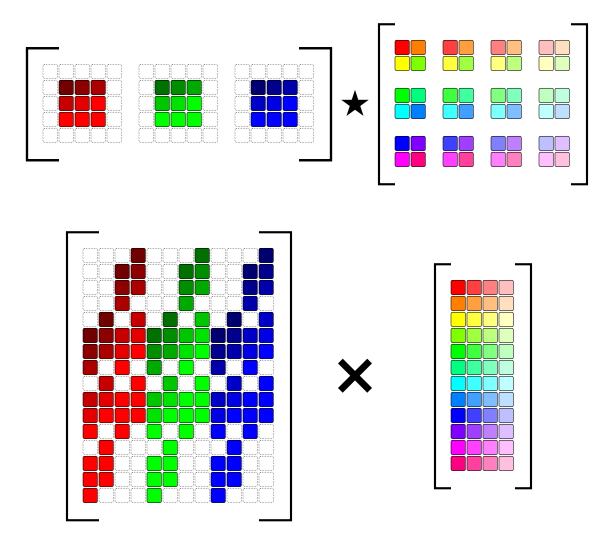

| 9  | Forward propogation in a 2D convolutional layer with 3-channel input. The $\star$ operator denotes cross-correlation operation                                                                                                | 15 |

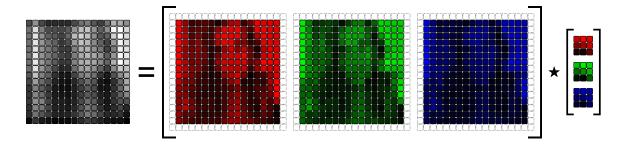

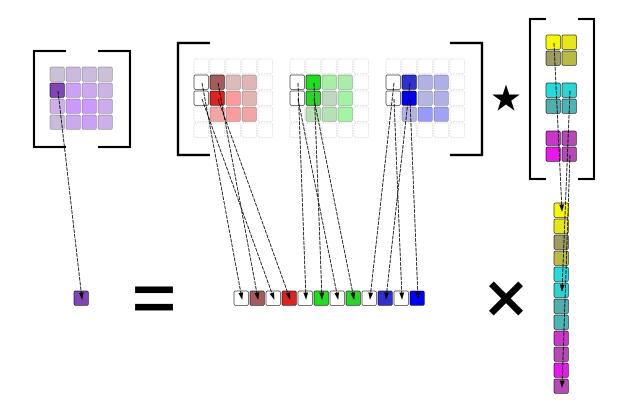

| 10 | Representation of forward propagation in a 2D convolutional layer as a dot product operation                                                                                                                                  | 16 |

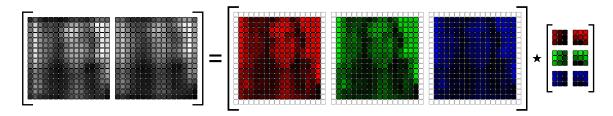

| 11 | Representation of forward propogation in a 2D convolutional layer with multiple filters as a vector-matrix product operation                                                                                                  | 16 |

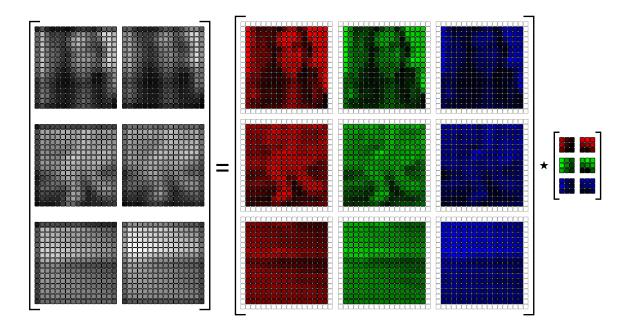

| 12 | Matrix-matrix multiplication-like structure of computations in the forward propagation of a 2D convolutional layer with multiple filters and a batch of input/output images                                                   | 17 |

| 13 | Transformation of forward propagation in a convolutional layer into a real matrix-matrix multiplication problem                                                                                                               | 18 |

| 14 | Repacking of elements in the im2col+GEMM algorithm                                                                                                                                                                            | 19 |

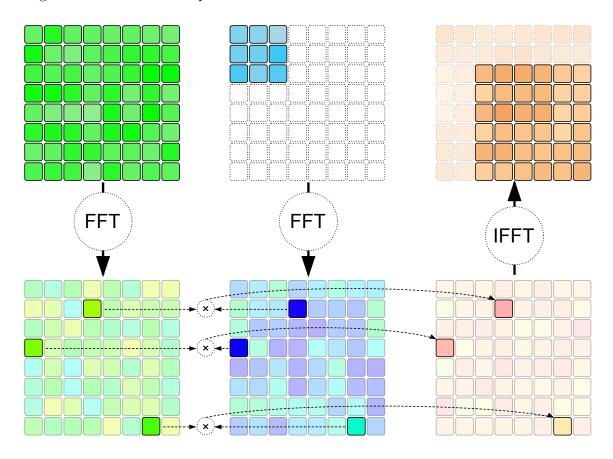

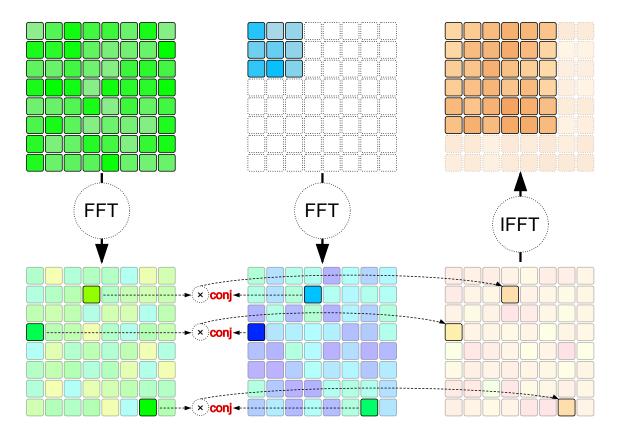

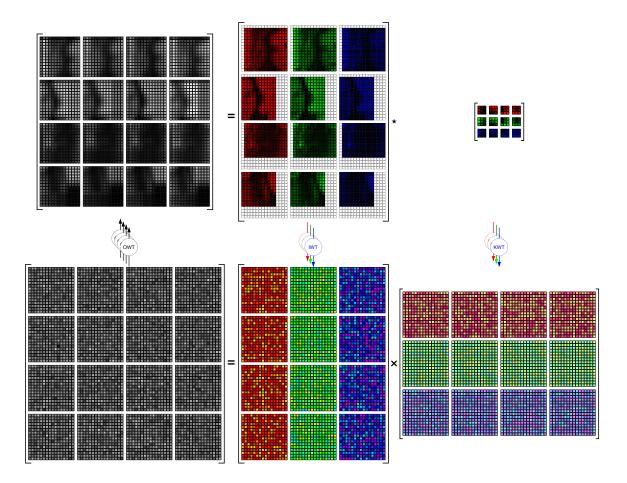

| 15 | 2D convolution algorithm based on Fourier transform                                                                                                                                                                           | 21 |

| 16 | Circular 2D cross-correlation                                                                                                                                                                                                 | 22 |

| 17 | 2D cross-correlation algorithm based on Fourier transform                                                                                                                                                                     | 23 |

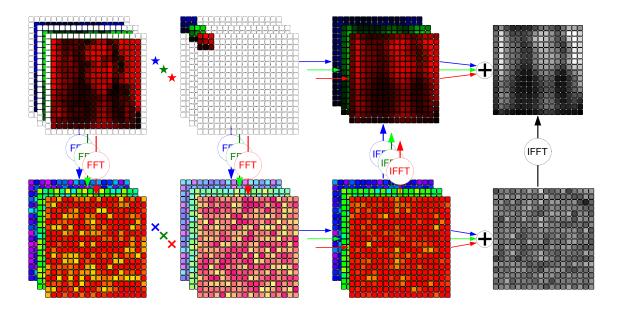

| 18 | Forward pass of a 2D convolutional layer based on Fourier transform.                                                                                                                                                                                                                                                     | 24 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

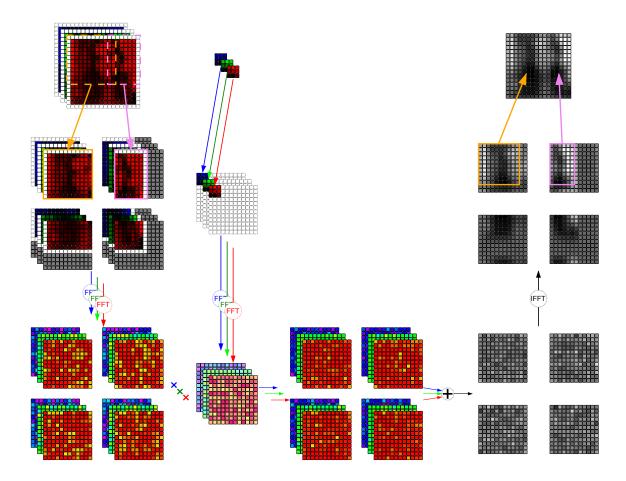

| 19 | Forward pass of a 2D convolutional layer based on Fourier transform with tiling                                                                                                                                                                                                                                          | 25 |

| 20 | 2D convolution algorithm based on Fourier transform                                                                                                                                                                                                                                                                      | 26 |

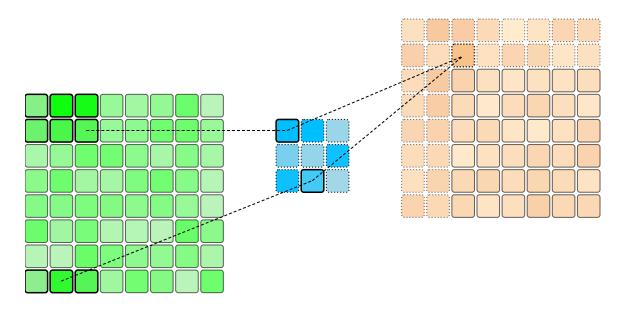

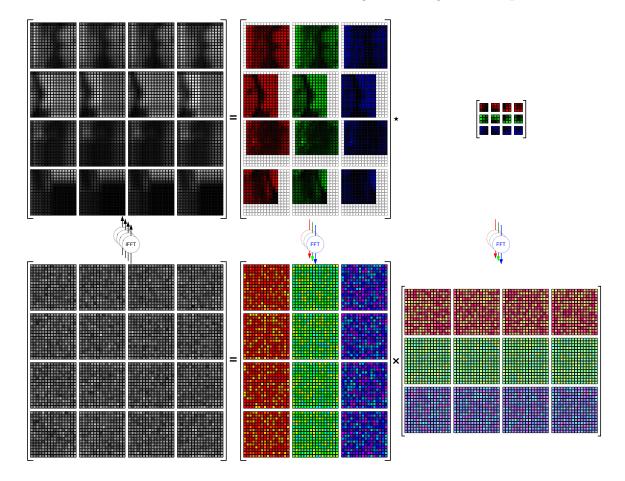

| 21 | 2D convolution algorithm based on the Winograd transform                                                                                                                                                                                                                                                                 | 28 |

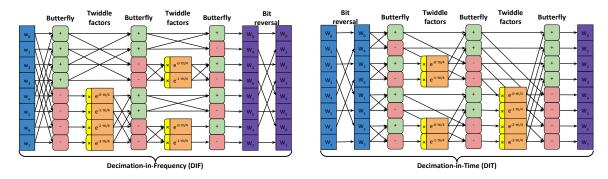

| 22 | Decimation-in-frequency and decimation-in-time FFT algorithms for 8-sample sequence                                                                                                                                                                                                                                      | 31 |

| 23 | Layouts of real-to-complex coefficients FFT of 8 samples                                                                                                                                                                                                                                                                 | 34 |

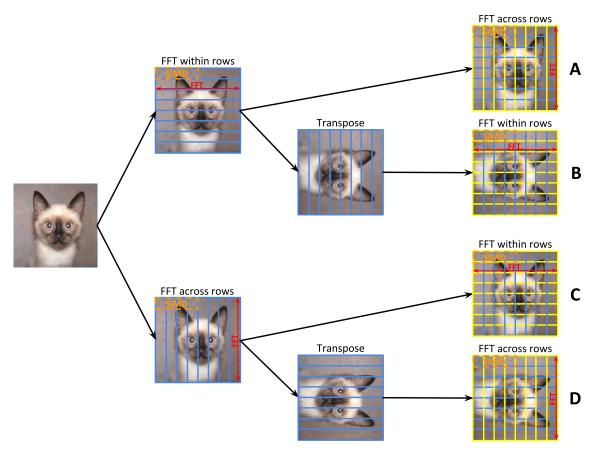

| 24 | Implementation options for 2D FFT                                                                                                                                                                                                                                                                                        | 35 |

| 25 | Layout of an $8 \times 8$ block of FFT coefficients. Red blocks indicate real coefficients, and yellow and green blocks indicate real and imaginary components of complex coefficients                                                                                                                                   | 38 |

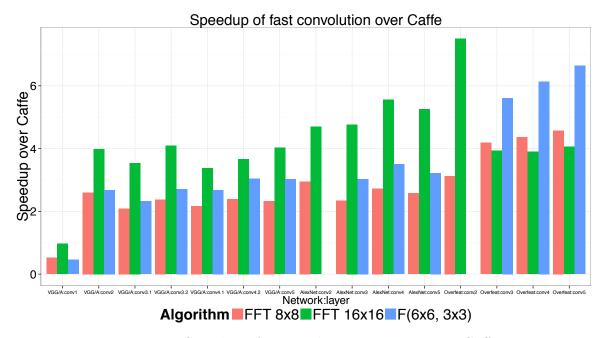

| 26 | Speedup of my implementations against Caffe                                                                                                                                                                                                                                                                              | 41 |

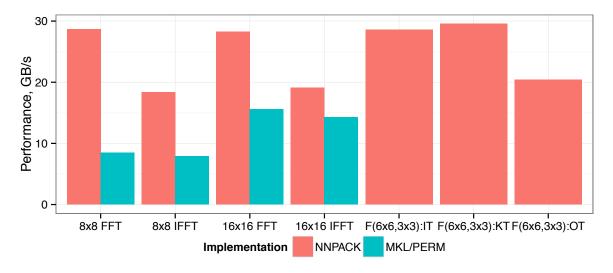

| 27 | Performance of batch transforms. The custom 2D FFT implementation specialized for $8 \times 8$ and $16 \times 16$ blocks substantially outperform the more generic implementations in Intel MKL. Both the 2D FFT and the 2D Winograd transforms demonstrate performance close to the memory bandwidth peak of the system | 42 |

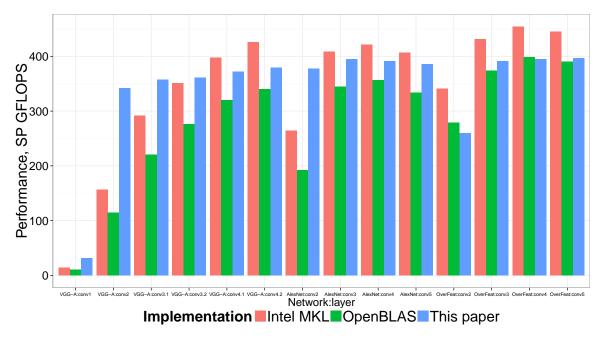

| 28 | Performance of complex matrix multiplication. For my implementation I report performance of reduction of blocks of $8 \times 8$ FFT coefficients. For MKL and OpenBLAS with report CGEMM performance with $M = B, N = C_o, K = C_i$                                                                                      | 43 |

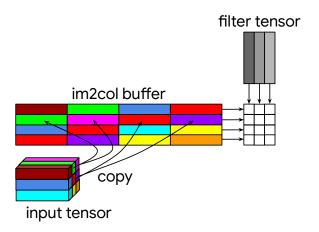

| 29 | GEMM operation as a component of GEMM-based convolution algorithm. im2col buffer represents matrix A, filter tensor - matrix B, and their product constitutes the output tensor.                                                                                                                                         | 49 |

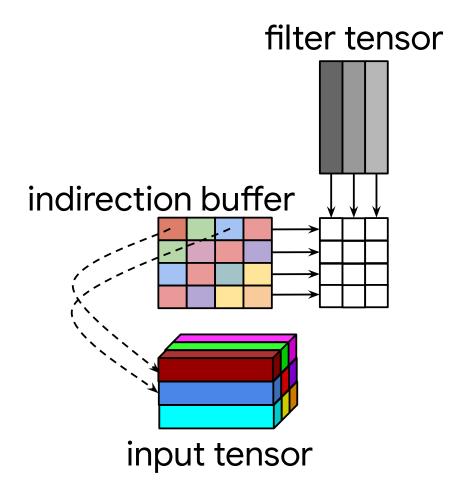

| 30 | Indirect GEMM operation as a component of Indirect Convolution algorithm. The indirection buffer contains only pointers to rows of the input tensor, and the Indirect GEMM operation reads rows of data directly from the input tensor                                                                                   | 51 |

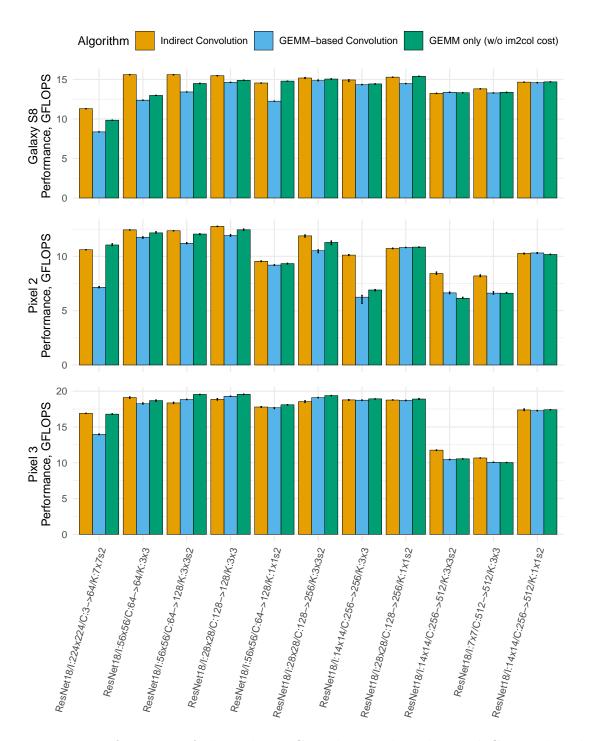

| 31 | Performance of the Indirect Convolution algorithm and GEMM-based Algorithm on convolution operators of the ResNet-18 model. Opaque bars represent median performance across 25 runs. Error bars represent 20% and 80% quantiles                                                                                          | 57 |

| 32 | Performance of the Indirect Convolution algorithm and GEMM-based Algorithm on convolution operators of the SqueezeNet 1.0 model. Opaque bars represent median performance across 25 runs. Error bars represent 20% and 80% quantiles.                                                                                    | 58 |

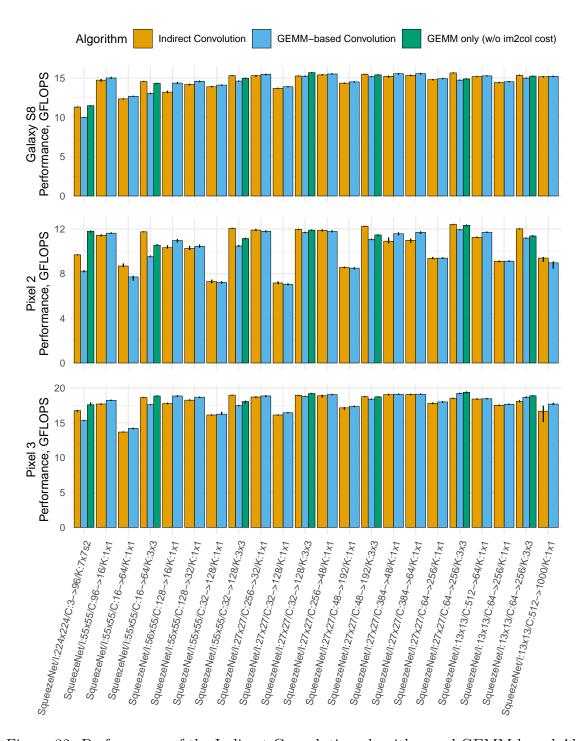

| 33 | Examples of sparsity structure in a scientific computing problem and trained neural network weights. Left: matrix dwt_209 from SuiteSparse matrix collection [18]). Right: filter tensor of a pixelwise convolution in a sparse EfficientNet B0 model | 65    |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

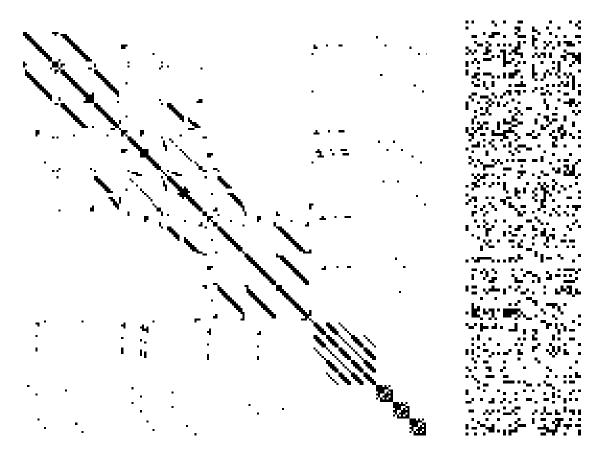

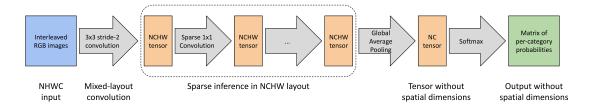

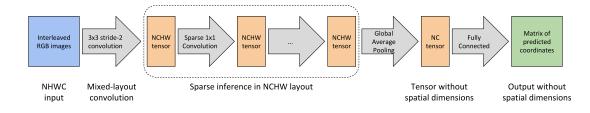

| 34 | Illustration of sparse inference for image classification tasks                                                                                                                                                                                       | 68    |

| 35 | Illustration of sparse inference for object detection and other regression tasks                                                                                                                                                                      | 68    |

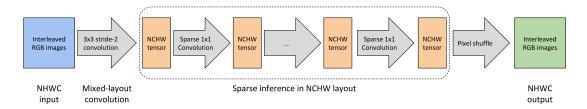

| 36 | Illustration of sparse inference for segmentation and other dense prediction tasks                                                                                                                                                                    | 69    |

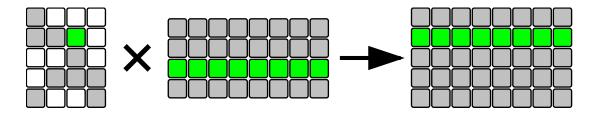

| 37 | SpMM Primitive implemented using Read-Modify-Write microkernel.                                                                                                                                                                                       | 71    |

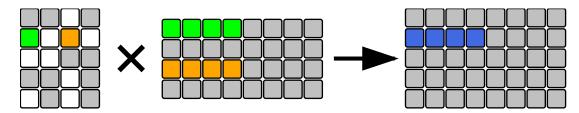

| 38 | SpMM Primitive implemented using Read-Accumulate microkernel                                                                                                                                                                                          | 71    |

| 39 | Block-SpMM Primitive implemented using Read-Accumulate microkernel                                                                                                                                                                                    | 72    |

| 40 | Performance of matrix multiplication problems corresponding to the pixelwise convolutions in the MobileNet v1 architecture                                                                                                                            | 75    |

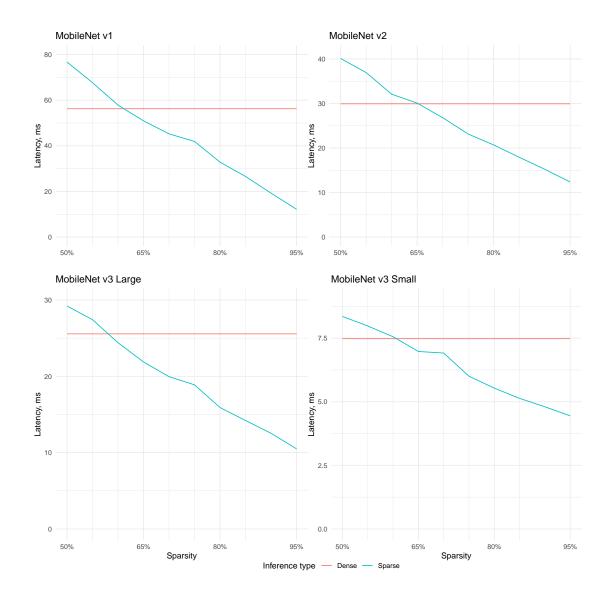

| 41 | Dense and sparse inference latency in the three generations of MobileNet architectures                                                                                                                                                                | 77    |

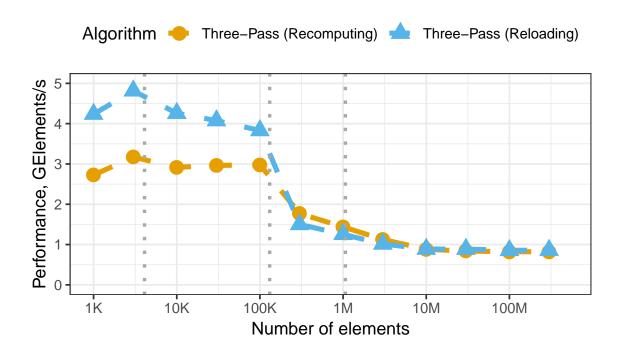

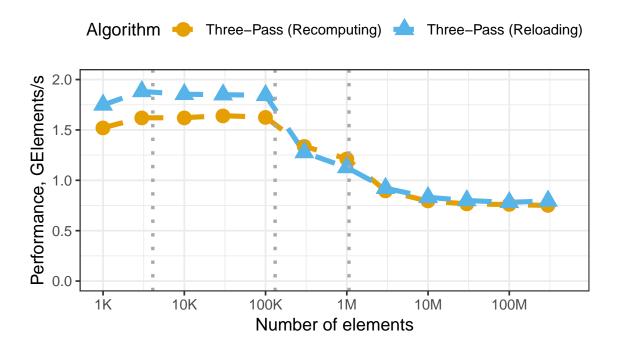

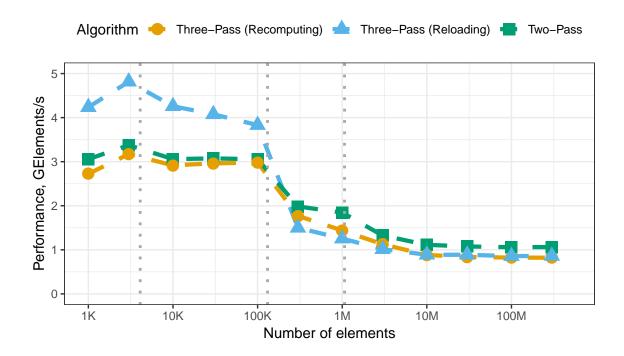

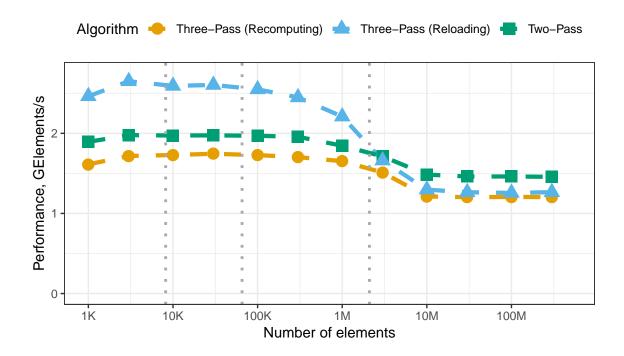

| 42 | Single-threaded performance comparison of the Softmax algorithms 1 and 2 in the AVX512 implementations on the Skylake-X system. Gray dotted lines denote boundaries of level-1, level-2, and level-3 caches. $\cdot$                                  | 93    |

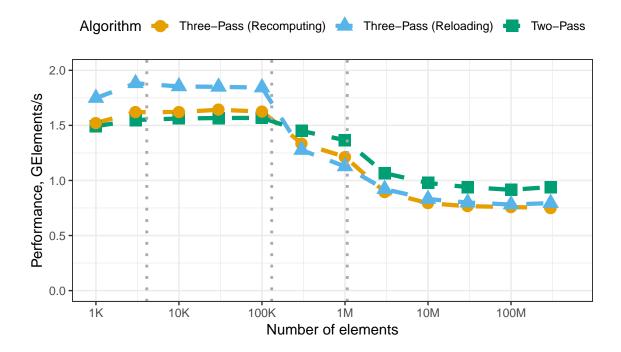

| 43 | Single-threaded performance comparison of the Softmax algorithms 1 and 2 in the AVX2 implementations on the Skylake-X system. Gray dotted lines denote boundaries of level-1, level-2, and level-3 caches                                             | 94    |

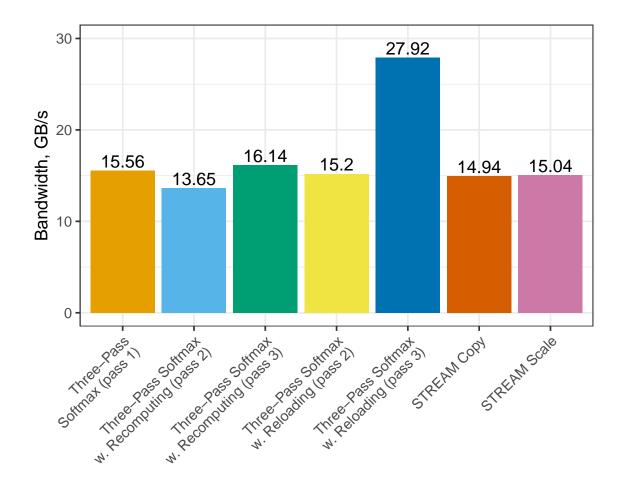

| 44 | Measured single-threaded memory bandwidth on the Skylake-X system in the three passes of the Softmax algorithms 1 and 2, and in the STREAM benchmark. Both the softmax implementations and the STREAM benchmark use AVX512 instructions               | 95    |

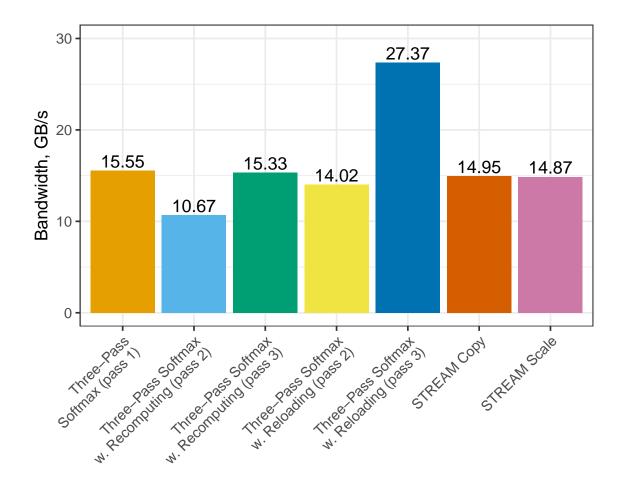

| 45 | Measured single-threaded memory bandwidth on the Skylake-X system in the three passes of the Softmax algorithms 1 and 2, and in the STREAM benchmark. Both the softmax implementations and the STREAM benchmark use AVX2 instructions                 | 96    |

| 46 | Single-threaded performance comparison of the Algorithms 1, 2, and 3 in the AVX512 implementations. Gray dotted lines denote boundaries of level-1, level-2, and level-3 caches.                                                                      | 98    |

| 47 | Single-threaded performance comparison of the Algorithms 1, 2, and 3 in the AVX2 implementations. Gray dotted lines denote boundaries of level-1, level-2, and level-3 caches.                                                                        | 99    |

|    | N. V.J. I., IV.V.E. J., AHU JEVEL J. LALIED.                                                                                                                                                                                                          | .~1~1 |

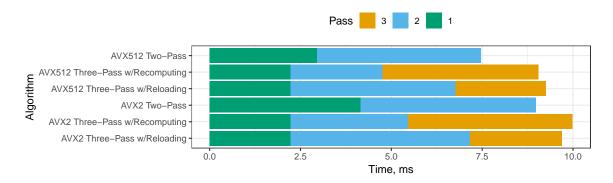

| 48 | Absolute runtime of the passes in the Algorithms 1, 2, and 3 in both the AVX2 and the AVX512 implementations. The algorithms were evaluated on arrays of 8,650,752 single-precision elements on a single threaded of the Skylake-X system | 100 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

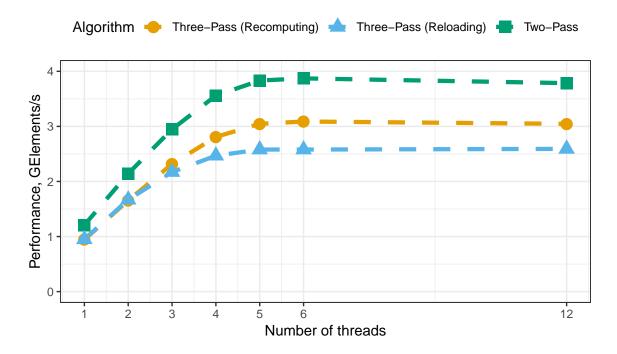

| 49 | Weak scaling (the number of elements scales proportionally to the number of threads used) of the softmax algorithms in the AVX512 implementations on the Skylake-X system                                                                 | 101 |

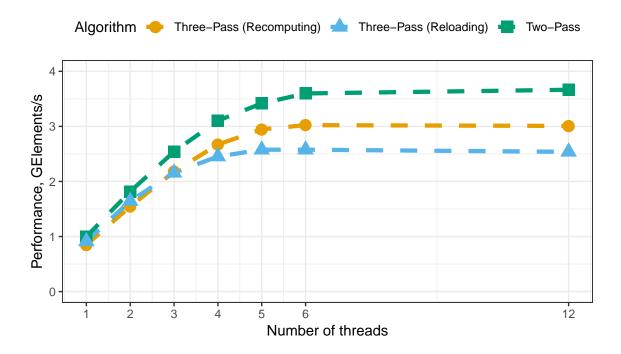

| 50 | Weak scaling (the number of elements scales proportionally to the number of threads used) of the softmax algorithms in the AVX2 implementations on the Skylake-X system                                                                   | 102 |

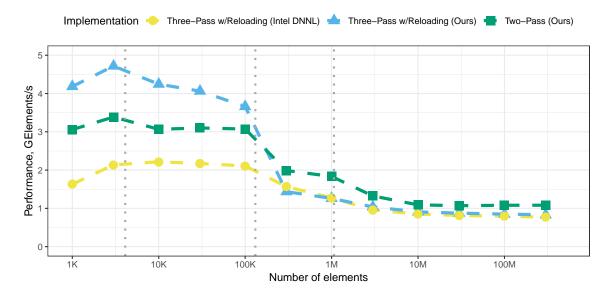

| 51 | Performance comparison of my implementation of Algorithms 1, 2, and 3, with the softmax implementation in Intel DNNL library. Gray dotted lines denote boundaries of level-1, level-2, and level-3 caches.                                | 103 |

| 52 | Performance comparison of Algorithms 1, 2, and 3 on an Intel Broadwell-based system. Gray dotted lines denote boundaries of level-1, level-2, and level-3 caches.                                                                         | 104 |

| 53 | Performance comparison of Algorithms 1, 2, and 3 on a Ryzen 9 3900X system. Gray dotted lines denote boundaries of level-1, level-2, and level-3 caches                                                                                   | 105 |

#### SUMMARY

Optimized software implementations of artificial neural networks leverage primitives from performance libraries, such as the BLAS. However, these primitives were prototyped decades ago and do not necessarily reflect the patterns of computations in neural networks. I propose modifications to common primitives provided by performance libraries to make them better building blocks for artificial neural networks, with a focus on inference, i.e., evaluation of a pre-trained artificial neural network. I suggest three classes of performance primitives for the convolutional operators and two optimized building blocks for softmax operators.

High-intensity convolutional operators with large kernel sizes and unit stride benefit from asymptotically fast convolution algorithms based on Winograd transforms and Fast Fourier transforms. I jointly consider Fourier or Winograd transforms and the matrix-matrix multiplication (GEMM) of blocks of transformed coefficients and suggest a tuple-GEMM primitive, which balances the number of irregular memory writes in the transformation with sufficient register blocking and instruction-level parallelism in the matrix-matrix multiplication part. Tuple-GEMM can be thought of as a batched GEMM with a fixed architecture-dependent batch size and can be efficiently implemented as a modification of the Goto matrix-matrix multiplication algorithm. I additionally analyze small 2D Fast Fourier transforms and suggest options that work best for modern wide-SIMD processors.

Lower-intensity convolutional operators with small kernel sizes, non-unit strides, or dilation do not benefit from the fast convolution algorithms and require a different set of optimizations. To accelerate these cases I suggest replacing the traditional

GEMM primitive with a novel Indirect GEMM primitive. Indirect GEMM is a slight modification of GEMM and can leverage the extensive research on efficient GEMM implementations. I further introduce the Indirect Convolution algorithm. It builds on top of the Indirect GEMM primitive, eliminates the runtime overhead of patchbuilding memory transformations, and substantially reduces the memory complexity in convolutional operators compared to the traditional GEMM-based algorithms.

Pointwise, or 1x1, convolutional operators directly map to matrix-matrix multiplication and prompt yet another approach to optimization. I demonstrate that neural networks heavy on pointwise convolutions can greatly benefit from sparsifying the weights tensor and representing the operation as a sparse-matrix-dense-matrix multiplication (SpMM). I introduce neural network-optimized SpMM primitives. While SpMM primitives in Sparse BLAS libraries target problems with extremely high sparsity (commonly 99% or more) and non-random sparsity patterns, the proposed SpMM primitive is demonstrated to work well with moderate sparsity in the 70-95% range and unpredictable sparsity patterns.

The softmax operator is light on elementary floating-point operations but involves evaluation of the exponential function, which in many implementations becomes the bottleneck. I demonstrate that with a high-throughput vector exponential function the softmax computation saturates the memory bandwidth and can be further improved only by reducing the number of memory access operations. I then constructively prove that it is possible to replace the traditional three-pass softmax algorithms with a novel two-pass algorithm for a runtime reduction of up to 28%.

I implemented the proposed ideas in the open-source NNPACK, QNNPACK, and XNNPACK libraries for acceleration of neural networks on CPUs, which at the time of their releases delivered state-of-the-art performance on mobile, server, and Web platforms.

### CHAPTER I

#### INTRODUCTION

Artificial neural networks are a powerful tool. They are the state-of-the-art models for image classification [41], object recognition [80, 62, 79], artistic image manipulation [51, 29, 54], speech recognition [4], speech synthesis [91], machine translation [97], and many other artificial intelligence tasks. However, neural networks stand out not only in impressive effectiveness on a variety of artificial intelligence problems, but also in their insatiable appetite for computational power. A higher computational budget lets artificial intelligence researchers build larger models, scaling them up to the limits of the modern hardware results in progressively higher accuracy [78, 89, 65]. Fig. 1, 2, 3 illustrate this relationship on three popular families of neural networks architectures: MobileNet v1 [46], MobileNet v2 [82], and EfficientNets [89].

Machine learning on live perceptual data, such as video and audio streams, is particularly challenging as real-time processing imposes a strict time limit for neural network inference, while low latency requirements and privacy considerations associated with perceptual data dictate that neural network processing happen locally, on the same end-user device that produced the audio or video stream. These devices can

Figure 1: Accuracy and inference computations for the MobileNet v1 family of neural network architectures

Figure 2: Accuracy and inference computations for the MobileNet v2 family of neural network architectures

Figure 3: Accuracy and inference computations for the EfficientNet family of neural network architectures

range from IoT with microcontrollers to mobile phones to desktop computers, but share two features: a CPU as the least common denominator of fragmented hardware and orders of magnitude lower computational capabilities than the HPC-class GPUs and neural network accelerators (TPUs) used to train neural network models. Table 1 illustrates practically achievable performance on four types of end-user devices and suggests that neural network models operate in the mode where even slight reductions in model complexity to improve inference time costs a steep degradation in the quality metrics for model outputs.

Table 1: Single-core performance on MobileNet v3 Large model on TensorFlow Lite framework with the XNNPACK inference engine.

| Device              | Form-Factor | Environment | Performance, GFLOPS |  |

|---------------------|-------------|-------------|---------------------|--|

| MacBook Pro 11,3    | laptop      | macOS       | 46                  |  |

| MacBook Pro 11,3    | laptop      | WAsm        | 5.1                 |  |

| Pixel 2             | phone       | Android     | 9.9                 |  |

| Pixel 2             | phone       | WAsm        | 1.5                 |  |

| Raspberry Pi 4      | embedded    | Linux       | 5.9                 |  |

| Raspberry Pi Zero W | IoT         | Linux       | 0.26                |  |

Researchers have explored two different paths to improve CPU performance on neural network layers, which can be termed as the performance library approach and the compiler approach. The performance library approach, implemented in most deep learning frameworks, is to leverage existing scientific computing libraries for portable, yet optimized implementation. In particular, the most computationally intensive neural network components – convolutional, recurrent, and fully-connected operators – can be built upon the GEMM primitive from the BLAS libraries. For fully connected and recurrent operators, a GEMM-based implementation is trivial, but convolutional layers need certain data repacking that was first suggested by Chellapilla et al [10], and then rediscovered and popularized by the author of Caffe [53]. Mathieu et al [67] justified using a Fourier transform for convolutional layers, and Zlateski et al [103] presented an implementation on top of Intel's MKL FFT, fftw, and cuFFT libraries. Later, Lavin [58] suggested using Winograd transforms for convolutional layers and demonstrated implementation of top of the Intel's MKL SGEMM primitive<sup>1</sup>. Another approach is to build a compiler to synthesize implementations optimized for

$<sup>^{1}\</sup>mathrm{A}$  later version of the same paper, co-authored by Lavin and Gray, presents results only on GPU, with a custom GEMM implementation.

specific cases that appear in neural networks. This approach can exploit all available information, including parameters of the layers and their position in the computational graph. A modern take on this method is represented by TensorFlow XLA [59], Apache TVM [12], and PyTorch Glow [81] frameworks, which leverage LLVM infrastructure for code-generation down to machine instructions. The compiler approach, however, tends to suffer from less optimal code-generation in the critical loops than expert-tuned assembly in performance libraries.

Here, I present a middle-ground approach. I aim to improve the performance of neural network layers built on top of a low number of scientific computing primitives, while preserving the portability inherent to this approach. I suggest that a slight modification of conventional scientific computing primitives — basic linear algebra subroutines (BLAS), Fast Fourier transform, and elementary functions — is sufficient to produce a high-performance implementation of common neural network layers. This approach leverages the wealth of existing research on efficient algorithms for scientific computing primitives and improves code portability by sharing high-level parts of algorithms implementation, as well as unit tests and benchmarks, for architecture-specific micro-kernels. Some of the proposed modified primitives fit into other modern developments in scientific computing, e.g., batched and mixed-precision BLAS, and could share parts of implementation with next-generation performance libraries that address these needs.

#### CHAPTER II

#### CONVOLUTIONAL NEURAL NETWORKS

Figure 4: Traditional neural network layer with 4 input and 7 output neurons

Artificial neural networks are machine learning models loosely inspired by neuroscience, a scientific discipline about the organization of the nervous system. In artificial neural networks computations are organized in layers. A layer applies a linear transformation to its input (a vector), produces an output vector, and then transforms the output vector with a nonlinear activation function. Fig. 4 illustrates this process. It is common to augment the input vector with an element hard-wired to 1.0 (purple input on fig. 4) so that, with some transformation parameters, the linear transformation could produce negative outputs even if all inputs are positive. Most practical activation functions transform each element independently, and the most popular activation function – the rectified linear unit (ReLU) – just replaces negative components with zeros.

Figure 5: Example of a deep neural network with three layers

A single layer has a limited capability of learning relationships in the data, so artificial neural networks use multiple layers stacked on top of each other: the output of one layer serves as input for another layer. For this reason, multi-layer artificial neural networks are often called **deep neural networks**, and in advances in the structure and initialization of neural networks increased the viable number of layers from about a half-dozen to over a thousand [85, 88, 41]. Fig. 5 demonstrates the data flow in a three-layer deep neural network. Besides stacking layers, it is common for neural network architectures to concatenate outputs of several layers [88, 49, 47] or combine them through addition [41] or maximum [31] operations.

The linear transformations in the neural network layers can express contributions

LeCun et al [60] discovered that artificial neural networks achieve better results on computer vision tasks if they restrict the possible connections between inputs and outputs to preserve locality and suggested the LeNet architecture for handwritten digit recognition. Unlike previous neural network architectures, LeNet used new types of layers, which take into account the 2-dimensional structure of images: convolutional layers and pooling layers. A convolutional layer restricts the linear transformation so that each output pixel depends only on a small neighborhood of input pixels. A pooling layer aggregates a tile of neighboring pixels into a single output pixel, and, in general, is not a linear transformation. Neural networks with convolutional layers are called **convolutional neural networks**, and convolutional layers are typically their most computationally intensive parts. Later research generalized convolutional and pooling layers to arbitrary numbers of dimensions and demonstrated the usefulness of 1D convolutions for speech recognition [2] and natural language processing tasks as well as 3D convolutions for video classification.

Parameters of the linear transformation in neural network layers are learned in a training process. During training samples from a dataset are supplied as inputs to the first layer of a neural network, and weights are adjusted to make outputs closer to the reference outputs from the dataset. Usually this process involves a two-step backpropagation algorithm: first, in the forward pass, propagate the signals from the input layers towards output layers and calculate the loss between the computed output and reference output; then, in the backward pass, propagate the gradient of the loss from the output layers towards the input layers. Additionally, the backward pass computes the gradients of layer parameters with respect to loss. These gradients are then used to update the parameters' values. Most commonly, the stochastic gradient descent with a momentum algorithm [57] is used to update the parameters, albeit several advanced algorithms were suggested [21, 99, 56, 63, 44]. For better efficiency,

training usually consumes a dataset in batches of multiple samples. The batch size is limited by the memory footprint of the network, including all intermediate signals and gradients. Batches of up to 8,096 were reported to be practical [34], and a typical batch size is 64 - 512 samples.

After the training process converges to a good set of parameters, the neural network is ready to make predictions on new inputs – a process called inference. In inference only the forward pass of a neural network is computed, and no gradients are involved. Most applications of neural networks to live perceptual data are latency-sensitive and limit the batch size in inference to a single image.

Table 2: 2D image tensor layouts in popular neural network frameworks

| Name | Shape                                              | Frameworks                           |  |  |

|------|----------------------------------------------------|--------------------------------------|--|--|

| NCHW | $batch \times channels \times height \times width$ | PyTorch [76], Caffe [53], Theano [3] |  |  |

| NHWC | $batch \times height \times width \times channels$ | Tensorflow [1], CNTK [98]            |  |  |

| CHWN |                                                    | cuda-convnet2, Neon                  |  |  |

A number of high-level frameworks [76, 1, 53, 16, 3, 11, 98] were developed to assist artificial intelligence research. These frameworks differ in the tensor layout they use in their layers' implementation, summarized in Table 2. NCHW layout enjoys the widest support: even Tensorflow and CNTK frameworks, which started with native NHWC-layout layers, can optionally use NCHW. However, NHWC and CHWN layouts have their benefits, too: NHWC simplifies implementation of convolutional layers via matrix-matrix multiplication, and the CHWN layout with large batch sizes is particularly efficient for training on GPUs.

### 2.1 Fully Connected Layers

A fully connected layer represents a general linear transformation without any constraints. These layers consume and produce 2D tensors. If the layer input has more

than 2 dimensions, e.g., a multi-channel 2D image, its dimensions are reshaped into a 2D matrix. Thus, in both the NCHW and NHWC frameworks, the inputs to the fully connected layer have the same dimensions. Layer parameters are represented by a 2D weights matrix, which has the same dimensions in NCHW, NHWC, and CHWN layouts. Table 3 details dimensions of matrices in all three layouts.

Table 3: Shape of input, output, and weights matrices in a fully-connected layer

| Layout | Input matrix                 | Output matrix                 | Weights matrix                        |

|--------|------------------------------|-------------------------------|---------------------------------------|

| NCHW   | $batch \times channels_{in}$ | $batch \times channels_{out}$ | $channels_{out} \times channels_{in}$ |

| NHWC   | $batch \times channels_{in}$ | $batch \times channels_{out}$ | $channels_{out} \times channels_{in}$ |

| CHWN   | $channels_{in} \times batch$ | $channels_{out} \times batch$ | $channels_{out} \times channels_{in}$ |

A fully connected layer can be thought of as an affine transformation of the input matrix and can be implemented via matrix-matrix multiplication (GEMM) in a BLAS library. If the input vectors are augmented with unit elements, this augmentation is performed implicitly: the matrix-matrix multiplication of explicit input elements is followed by the addition of a bias vector, which contains the column of weights corresponding to the implicit unit element. This case is demonstrated in Fig 6.

Figure 6: The representation of a fully connected layer with implicit unit inputs as a matrix-matrix multiplication with bias. The bias is broadcasted along the column dimension and added to each column of the weights-input product.

High-performance BLAS libraries for CPUs typically implement the Goto algorithm for matrix-matrix multiplication [33]. Goto and van de Geijn suggested that the most important factor for efficient matrix-matrix multiplication is cache blocking, i.e., reuse of loaded memory blocks, on multiple levels of the memory hierarchy: registers, level-1 cache, and higher level caches. Their algorithm for matrix-matrix multiplication, now widely adopted, arranges computations in several layers of blocking. On the lower level, it relies on a "micro-kernel", which accumulates in registers a product of long panels of the two matrices.

The micro-kernel is the key to the overall algorithm's efficiency: Van Zee et al [92] demonstrated that so long as the micro-kernel is well-optimized, all other parts of the algorithm can be portably implemented in a high-level language and still produce a state-of-the-art implementation. The micro-kernel is typically implemented in assembly and makes heavy use of SIMD, architecture-specific instruction features, software prefetching, and pipelining. The micro-kernel expects one panel to reside in the level-1 cache, and another panel to be streamed from the level-2 cache to the level-1 cache. The width of the panels is limited by the number of registers, and their length is dictated by the level-1 cache size. A loop around the micro-kernel iterates panels of the second matrix factor inside level-2 cache, and another, outer, loop iterates panels of first matrix factor inside level-3 cache. Additionally, two other outer loops traverse level-3 cache-sized blocks of the first matrix factor and level-2 cache-sized blocks of second matrix factor to produced the complete matrix-matrix multiplication algorithm.

To satisfy cache-associativity limitations, input matrices are typically repacked so that the panels accessed by the micro-kernel are contiguously stored in memory. With large matrices, the cost of repacking is negligible compared to the cost of matrix-matrix multiplication: if the matrices are  $N \times N$ , then the cost of repacking is  $O(N^2)$  while computational cost is  $O(N^3)$ . However, for small matrices repacking can take

a considerable fraction of time and may offset the benefits of the blocked implementation. Recent studies have proposed several methods to improve BLAS efficiency on small problems.

First, some BLAS libraries provide an interface to separately repack input matrices and perform computations on repacked representations. This interface enables reuse of a repacked representation for multiple operations and is particularly helpful for neural network inference. In inference mode, the weights matrix is static and can be repacked during initialization, and then re-used for multiple forward passes.

Secondly, it is possible to modify micro-kernels to access one or both panels in the original layout without repacking. If the matrix is small, it may fit into cache without associativity conflicts, but the efficiency of the micro-kernel would still suffer from an imperfect operation of hardware prefetchers.

The third method is a variation of this approach where the code is generated for the specific matrix shapes of the application. Heinecke et al [42] evaluated the use of just-in-time (JIT) compilation for small-size BLAS problems and demonstrated possible speedups of over 10x.

Unbatched inference deserves special attention, because in this common case matrix-matrix multiplication becomes matrix-vector multiplication, and BLAS libraries provide a separate primitive (GEMV) for this operation. While matrix-matrix multiplication is often compute-bound, matrix-vector product is intrinsically bandwidth-bound. Matrix-vector multiplication can be decomposed into a series of dot products and implemented on top of the DOT primitive from BLAS. In this approach the input vector would be loaded into registers and, potentially, a higher level of the memory hierarchy for each row of the factor matrix, which limits performance of this bandwidth-bound operation. The number of loads can be reduced by combining the computation of several dot products in a fused-DOT operation [92].

Alternatively, it can be thought of as a matrix-vector multiplication where the matrix has a fixed small number of rows. The number of rows is limited by two factors: floating-point registers and cache associativity. The multiple dot products are accumulated in floating-point registers, and thus the number of floating-point registers on the target architecture puts an upper bound on the fusion factor. But a fused-DOT micro-kernel also reads multiple rows of the matrix in parallel, and if the matrix length is close to a large power of 2, these loads may compete for the same sets in the cache. Thus, cache associativity puts another, and usually tighter, limit on the fusion factor.

### 2.2 Convolutional Layers

A convolutional layer a special linear transformation that consumes and produces multi-channel 1D, 2D, or 3D signals<sup>1</sup>. Convolutional layers reuse the same set of learned parameters at multiple locations of the image, which induces locality, and improves model accuracy, especially on computer vision tasks. Due to the reuse of parameters, convolutional layers are more computationally intensive than fully-connected layers. Together with the closely related deconvolutional layers, they are typically the most computationally expensive parts of neural networks.

<sup>&</sup>lt;sup>1</sup>Generalizations to higher dimension exist, but are rarely used in practice.

Figure 7: One-dimensional cross-correlation (left) and convolution (right). The key difference is the traversal order of the kernel over the input.

A convolutional layer is built on top of two signal processing operations: cross-correlation and convolution. Fig. 7 illustrates this operation in the 1D case. A kernel (blue) slides along the input vector (green) and produces output elements (orange) through a dot product operation. The same kernel parameters are reused in all locations. The major difference between cross-correlation and convolution is in the order in which the sliding kernel traverses the input: in cross-correlation the kernel elements start traversing from the beginning of the input signal and are multiplied by the signal in their direct order; in convolution the kernel traverses from the end towards the beginning of the input, and its elements are multiplied by the signal in reverse order. Importantly, the number of elements in the input, kernel, and output vectors is linked through the relation

$$N_{\text{out}} = N_{\text{in}} - K + 1 \tag{1}$$

where  $N_{\text{out}}$  and  $N_{\text{in}}$  is the number of elements in the output and input vector respectively, and K is the number of elements in the kernel vector. As seen in Fig. 7, this equation holds because there are not enough valid inputs to produce the last (first) outputs of the cross-correlation (convolution).

Figure 8: Two-dimensional cross-correlation. A 2D kernel (middle) slides along the 2D input (left) to produce elements of the 2D output (right). The same kernel elements are reused at different positions of the input.

The two-dimensional case is presented in Fig. 8 and is widely used in image processing. Here, a 2D kernel slides along the input image and produces the output image through a dot product with input subimages. The shapes of the input, kernel, and output images are connected through the equations,

$$H_{\text{out}} = H_{\text{in}} - H_{\text{K}} + 1$$

$$W_{\text{out}} = W_{\text{in}} - W_{\text{K}} + 1$$

(2)

where  $H_{\text{out}}$ ,  $W_{\text{out}}$ ,  $H_{\text{in}}$  and  $W_{\text{in}}$  are the height and width of the output and input images respectively, and  $H_K$  and  $W_K$  are the kernel height and width.

Figure 9: Forward propogation in a 2D convolutional layer with 3-channel input. The \* operator denotes cross-correlation operation.

Convolutional layers add another dimension to the cross-correlation and convolution operations: channels. A convolutional layer combines multiple kernels – as many as there are channels in the input – into a filter. In the forward pass of a 2D convolutional layer, every channel of the input is cross-correlated with a channel of a filter, and then all channels are accumulated to produce a single-channel output. Figure 9 illustrates this computation.

Figure 10: Representation of forward propagation in a 2D convolutional layer as a dot product operation.

Computations in the convolutional layer exhibit structure similar to BLAS operations. If one replaces multiplication  $(\times)$  with a cross-correlation  $(\star)$ , the computation in Fig. 9 could be instead represented as a dot product operation, as in Fig. 10. This representation is useful for analyzing the computational properties and limits of convolutional layers, which are well-studied for BLAS operations.

Figure 11: Representation of forward propogation in a 2D convolutional layer with multiple filters as a vector-matrix product operation.

In practical convolutional neural networks, convolutional layers have not one, but many, filters. In the forward pass, the multi-channel input is cross-correlated with each multi-channel filter to produce multiple output channels (as many as there are filters). In the space with (+,\*) operations, this computation can be represented as a vector-matrix multiplication, depicted in Fig. 11.

Figure 12: Matrix-matrix multiplication-like structure of computations in the forward propagation of a 2D convolutional layer with multiple filters and a batch of input/output images.

During model training and, in many use-cases, during inference, convolutional layers are fed with a batch of inputs and produce a batch of outputs. In this operation, every channel of every input image is cross-correlated with every channel of every filter, and structure of computations, illustrated in Fig. 12 resembles matrix-matrix multiplication. The dimensions of the input, filter, and outputs matrices in this representation are batchsize × channels, channels × filters, and batchsize × filters respectively.

Matrix-matrix multiplication performs  $O(n^3)$  operations on  $O(n^2)$  elements and is compute bound for large problem sizes. Thus, the forward pass in the convolutional layer is compute bound when batch size, number of channels, and number of filters are all large, regardless of kernel size. Moreover, the commonly-used kernel sizes of  $3 \times 3$  (18 FLOPs per output) and  $5 \times 5$  (50 FLOPs per output) shift the balance even further towards saturation of compute units.

#### 2.2.1 im2col+GEMM algorithm

Figure 13: Transformation of forward propagation in a convolutional layer into a real matrix-matrix multiplication problem.

A popular method to implement forward and backward propagation in convolutional layers is to transform a convolution into a matrix-matrix multiplication and leverage matrix-matrix multiplication (GEMM) routines in a BLAS library to do the actual computation. This method, illustrated in Fig. 13 and commonly known as the im2col+GEMM algorithm, was first suggested by Chellapilla et al [10], and popularized in the Caffe framework [53].

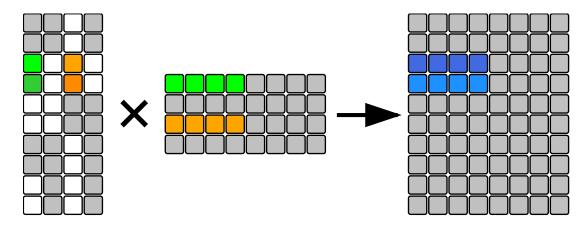

Figure 14: Repacking of elements in the im2col+GEMM algorithm.

Fig. 14 provides the intuition behind the transformation of forward propagation in a convolutional layer into a matrix-matrix multiplication problem. Each element of the output tensor (on the left) is a dot product of a filter (on the right) by a multi-channel subimage of the input (middle). Different pixels of the same channel of the output tensor are produced as a dot product of different multi-channel subimages of the input and the same filter. Pixels in the same position in other channels are produced via dot product of the same subimage of the input by different filters.

Table 4: High-performance BLAS implementation for popular platforms

| Platform | OpenBLAS | BLIS | Eigen | Accelerate | MKL | ACML | ESSL | QSML |

|----------|----------|------|-------|------------|-----|------|------|------|

| x86      | Yes      | Yes  | Yes   | Yes        | Yes | Yes  | No   | No   |

| x86-64   | Yes      | Yes  | Yes   | Yes        | Yes | Yes  | No   | Yes  |

| ARM      | Yes      | Yes  | Yes   | Yes        | No  | No   | No   | Yes  |

| ARM64    | Yes      | Yes  | Yes   | Yes        | No  | No   | No   | Yes  |

| POWER    | Yes      | Yes  | Yes   | Yes        | No  | No   | Yes  | No   |

| PNaCl    | No       | Yes  | Yes   | No         | No  | No   | No   | No   |

| Asm.js   | No       | Yes  | Yes   | No         | No  | No   | No   | No   |

The im2col+GEMM algorithm has its pros and cons. On the plus side, it combines good performance with universal portability: popular platforms provide a choice of multiple high-performance BLAS implementations (see Tab. 4), and exotic platforms can bootstrap an optimized BLAS implementations through auto-tuning [95]. The major drawback of this algorithm is the substantial memory overhead of  $K_H \times K_W$  times the size of layer input. Intermediate tensors are usually the largest memory consumers in convolutional neural networks, especially with non-unit batch size, and the proportial increase in memory consumption can be prohibitive in mobile, Web, and IoT environments.

#### 2.2.2 Fast Convolution algorithms

The convolution theorem states that, under certain conditions, a Fourier transform of a convolution of two signals is a pointwise product of their Fourier transforms. Combined with a Fast Fourier Transform algorithm, the convolution theorem suggests a less computationally intensive alternative to the im2col+GEMM algorithm. Fig. 15 demonstrates the FFT-based 2D convolution algorithm: zero-pad the kernel to the size of the input, transform the padded kernel and the input to the Fourier domain,

elementwise multiply the Fourier images, and compute the inverse FFT on the product to get the convolution output.

Figure 15: 2D convolution algorithm based on Fourier transform.

The Fourier transform assumes periodic signals, and the full output computed through the convolution theorem represents a circular convolution: its outputs near the top-left border depend on a block of input that wraps around its border, as shown in Fig. 16. These outputs are meaningless for the normal convolution operation, thus it discards them and only uses the bottom-right block of  $(H_{\rm in} - H_{\rm K} + 1) \times (W_{\rm in} - W_{\rm K} + 1)$  outputs.

Figure 16: Circular 2D cross-correlation.

Computation of a 2D cross-correlation on top of the Fast Fourier Transform and the convolution theorem differs in two details: we multiply the Fourier transform of the input by the complex conjugate of the Fourier transform of the zero-padded kernel and use the top-left block of inverse FFT outputs while discarding the outputs near the bottom-right border. Fig. 17 illustrates the computations involved.

Figure 17: 2D cross-correlation algorithm based on Fourier transform.

A 2D cross-correlation trivially extends to multiple channels, as illustrated in the first three columns of Fig. 18. The algorithm from Fig. 17 applies to each channel of the input and the filter to produce channels of the output image, which are subsequently accumulated together. However, as the Inverse Fourier Transform is a linear transformation, it can be factored out after the accumulation. The improved algorithm, illustrated in the fourth column of Fig. 18, accumulates blocks of FFT coefficients for the output image, and then computed the Inverse FFT of the result.

Figure 18: Forward pass of a 2D convolutional layer based on Fourier transform.

By leveraging Fast Fourier Transforms and the convolution theorem, the algorithm in Fig. 18 reduces the number of floating-point operations in the forward pass of a 2D convolutional layer compared to direct computation, but also involves two inefficiencies that dramatically limit its practical applicability.

First, the filter needs to be zero-padded to the size of the input image. This procedure is an intrinsically memory-intensive operation, and it greatly increases the memory footprint of the filter. Commonly-used filter sizes are  $3 \times 3$  and  $5 \times 5$ , while input images can be on the order of QVGA ( $320 \times 240$ ) or higher, resulting in over 1,000 times expansion in the memory footprint! Such an increase in would typically exceed the capacity of the system, especially on mobile and embedded systems.

Secondly, the algorithm implies doing a Fast Fourier Transform on input imagesized blocks, which are generally unconstrained. Although algorithms for doing Fast Fourier Transform on arbitrary-sized blocks are known [27], their efficiency varies across input sizes, resulting in unexpected performance cliffs.

Figure 19: Forward pass of a 2D convolutional layer based on Fourier transform with tiling.

These inefficiencies can be resolved by tiling the Fourier transform-based convolution algorithm [93]. This modification, illustrated in Fig. 19, rather than computing the Fourier transform of the input image all-at-once, splits the input image into fixed-sized input tiles, computes the convolution of these tiles with the kernels using the Fourier transform and the convolution theorem, and then concatenates output tiles to cover the whole output image. Importantly, the output is densely covered with non-overlapping tiles, but the corresponding input tiles do overlap, because they are  $(H_K - 1) \times (W_K - 1)$  pixels bigger.

Tiling works around the inefficiencies of the naive Fourier transform-based algorithm. First, the filter is zero-padded only to the size of a tile, which is typically

much smaller than input image. Second, an implementation may choose the tile size that is convenient for a Fast Fourier transform algorithm, e.g., a small power of two.

Figure 20: 2D convolution algorithm based on Fourier transform.

Fig. 20 illustrates how the Fast Fourier Transform with tiling transforms the nature of the computation in the convolution operator. In the top row, the matrix elements represent tiles of the input, output, and filter tensors, and "multiplication" of these elements is represented by 2D cross-correlation operation. Importantly, the number of multiply-adds in the 2D cross-correlation operation is directly proportional to the kernel size in the filters. In the bottom row, the matrix elements represent frequency-domain tiles of input, output, and filter tensors, and multiplication of these elements is represented by elementwise multiplication of their complex-domain components. Thus, in the bottom row, each multiplication costs two multiply-adds, regardless of

the kernel size in the filters. This simplification of the elementary operations is the principal reason for the high efficiency of the FFT-based convolution algorithm.

Conversion between the top row and the bottom row representations requires a Fourier transform on the tiles, and its cost cuts into the savings from multiplying individual tiles. However, as seen in Fig 20, this conversion has lower asymptotic complexity than the "matrix multiplication" part: we transform  $O(N^2)$  elements in each matrix to make the  $O(N^3)$  matrix-matrix multiplication cheaper. Thus, when the number of input channels, output channels, and input tiles is sufficiently large, the cost of a Fourier transform on the tiles is negligible compared to the multiplication-accumulation of the transformed tiles.

The Fourier transform-based convolution algorithm in Fig. 20 drastically reduces the number of floating-point operations compared to im2col-based algorithms, but it is possible to do even better. The Winograd transform-based convolution algorithms [58] further reduces the number of floating-point operations by close to  $2\times$ . Fig. 21 illustrates the general structure of computations in this algorithm, with its substantial similarities to a Fourier transform-based algorithm. In fact, there are just two differences between the Winograd transform-based and Fourier transform-based algorithms:

- 1. These algorithms replace Fast Fourier transform (FFT) and Inverse FFT with Winograd transforms. The algorithm uses three different Winograd transforms, each specific to the type of blocks of coefficients: input Winograd transform (IWT), kernel Winograd transform (KWT), and output Winograd transform (OWT). Each Winograd transform is a linear transformation of a block of coefficients with a rather sparse transformation matrix.

- 2. While Fourier-transformed blocks contain complex elements, Winograd-transformed

blocks use only real coefficients. Multiplication-accumulation of complex numbers involves four floating-point operations, but multiplication-accumulation of real numbers requires only two floating-point operations. Thus, the matrix-matrix multiplication part in Fig. 21 is twice cheaper than the same part in Fig. 20, and constitutes the main advantage of a Winograd transform-based algorithm over a Fourier transform-based one.

Figure 21: 2D convolution algorithm based on the Winograd transform.

The Winograd transform-based method comes with its own disadvantages, too. First, input/kernel/output Winograd transforms are specific not only to the tile size, but also to the kernel size. If an implementation intends to support arbitrary kernel sizes, it needs to provide many variants of Winograd transforms. Secondly, while FFT

involves only order-of-one coefficients, Winograd transform involves a combination of large and small coefficients, which results in poor numerical stability. Thirdly, while FFT can be used with very large tiles without becoming inaccurate, a Winograd transform loses too much accuracy beyond  $8 \times 8$  tiles.

## CHAPTER III

## PRIMITIVES FOR HIGH-INTENSITY CONVOLUTIONS

#### 3.1 Introduction

| Model    | $1 \times 1$ | $3 \times 3$ | $5 \times 5$ |

|----------|--------------|--------------|--------------|

| VGG      | Yes          | Yes          | No           |

| U-Net    | Yes          | Yes          | No           |

| ResNet   | Yes          | Yes          | No           |

| AlexNet  | No           | Yes          | Yes          |

| Overfeat | No           | Yes          | Yes          |

Table 5: Configurations of parameters in convolutional layers in early CNN architectures.

Early convolutional neural network architectures for computer vision extensively relied on convolutions with large kernels to aggregate information across large neighborhoods of pixels. Table 5 illustrates that many of these networks incorporated  $3 \times 3$ ,  $5 \times 5$ , or even larger convolution kernels. Even though these neural network architectures are no longer state-of-art in terms of accuracy and efficiency, for a variety of reasons they remain widely used in both research and industry, for the following reasons.

- These neural network architectures are well-understood, covered in even introductory books on deep learning, and implemented in all major neural network frameworks.

- The above neural network architectures are relatively simple, and can be easily adapted to new datasets and experimental deep learning techniques, such as quantization and pruning. ResNet and U-Net are often considered as a baseline that new methods should be evaluated on or against.

Figure 22: Decimation-in-frequency and decimation-in-time FFT algorithms for 8-sample sequence

• Image features produced by VGG architectures are knows to produce more visually appealing results than features extracted by other architectures. This advantage is intrinsically subjective and its origins are not well-understood, but research on style transfer tends to prefer VGG architectures as feature extractors.

Due to the above factors, achieving good performance and efficiency on legacy neural network architecture remains an important goal. These architectures devote the majority of their FLOPs budget to convolutions with large kernel sizes, and thus the Fast Convolution algorithms that can reduce the computational complexity of such convolutions are of crucial importance to accelerating legacy neural network architectures. In this chapter, I present the details of adapting Fast Convolution algorithms to modern wide-SIMD processors and suggest modifications to the standard FFT and GEMM primitives that make them efficient building blocks for the Fast Convolution algorithms.

I consider two types of transformations for the Tiled Fast Convolution algorithm: the Fast Fourier transform and the Winograd transform.

# 3.2 Fast Fourier Transforms

The Fast Fourier Transform (FFT) is a family of algorithms to compute discrete Fourier transforms in  $O(n \log n)$  operations instead of  $O(n^2)$  operations in its naive implementation as a matrix-vector multiplication. Several variants of FFT algorithms were proposed in the literature; for this research I choose to implement the radix-2 Cooley-Tukey algorithm, which has a simple structure and operates on blocks that can be efficiently implemented on SIMD architectures. The radix-2 Cooley-Tukey algorithm recursively reduces an FFT of N elements to two FFTs of  $\frac{n}{2}$  elements.

Two variants of radix-2 Cooley-Tukey FFT algorithm are known: decimation-in-time (DIT) and decimation-in-frequency (DIF) algorithm. The algorithms differ by the order of recursive FFT steps: DIF algorithm starts with high-order FFT steps and then descends to a two-sample FFT while DIT starts with a two-sample FFT and then ascends to high-order FFT steps. The DIF algorithm expects the input in normal order and produces output in bit-reversed order; a separate shuffle step is required to rearrange the output to normal order. The DIT algorithm expects the input in bit-reversed order and produces output in normal order. Fig. 22 illustrates the difference between the two algorithms.

Additional optimizations are possible for Fourier transforms of real data. One algorithm performs the FFT on a real sequence of N samples using a complex FFT of  $\frac{N}{2}$  samples. Another algorithm is known to do an FFT of two interleaved sequences of N real samples each using a complex N-sample FFT.

Table 6: Instruction characteristics on Intel Skylake [26]

| Instructions       | Execution Port | Latency |

|--------------------|----------------|---------|

| FP ADD/SUB         | 0 or 1         | 4       |

| FP MUL/FMA         | 0 or 1         | 4       |

| FP LOGICAL         | 0, 1 or 5      | 1       |

| FP STATIC BLEND    | 0, 1 or 5      | 1       |

| FP PERMUTE/SHUFFLE | 5              | 1 or 3  |

| INT ALU            | 0, 1, 5 or 6   | 1       |

| INT MUL            | 1              | 3       |

A large fraction of floating-point performance in modern CPUs comes from SIMD instructions. Intel Skylake features 256-bit wide SIMD with AVX2 and FMA3 instruction sets, with instruction characteristics detailed in Tab. 6. The processor is capable of issuing two floating-point additions, multiplications, or FMA instructions each cycle, which produces a result after 4 cycles. Thus, at least eight independent floating-point instructions are needed to saturate the computational resources. Two kinds of instructions could lower the compute peak: integer multiplications and SIMD shuffles. Integer multiplications run on port 1, same as floating-point instructions, so each integer multiplication reduces the achievable compute peak. SIMD shuffles issue in parallel with floating-point computations, but the processor is capable of executing only one shuffle per cycle, and it can become a bottleneck. Logical and blend SIMD instructions, as well as simple scalar integer instructions can issue on many execution ports, and are less likely to become a bottleneck.

#### 3.2.1 Layout of FFT coefficients

Figure 23: Layouts of real-to-complex coefficients FFT of 8 samples

A Fourier transform of N real samples produces N complex samples, which can be represented with 2N real numbers. Many of these numbers are redundant, and the layout of coefficients of real-to-complex FFT is an important aspect of a high-performance implementation. Fig. 23 illustrates several possible layouts, with mathematically related numbers sharing the same color. The top row displays the layout of N complex FFT coefficients. The coefficients exhibit Hermitian symmetry:

$$W_{rac{N}{2}+i}\equiv W_{rac{N}{2}-i}$$

for  $i=1\dots rac{N}{2}-1.$

The symmetry makes it possible to drop the last  $\frac{N}{2}-1$  coefficients. The resulting layout, called CCS, is shown in the second row. CCS layout is nearly standard and supported by all major FFT libraries, including Intel MKL, FFTW, and FFTS. However, this layout is not favorable to wide SIMD units: when N is a power of two, which is convenient and efficient for SIMD implementation, the  $\frac{N}{2}$ th element would alone occupy a SIMD register. One solution is to pack this coefficient into the imaginary component of element 0, which is implemented in PERM format in Intel MKL, shown in row 3. In my implementation I use MKL PERM format and its structure-of-arrays variant in row 4.

#### 3.2.2 Composition of 2D FFTs

There are four options for implementing a 2D FFT, illustrated in Fig. 24. The implementation of all four options would be very labor-intensive, so I argue about

Figure 24: Implementation options for 2D FFT

the optimal option from a theoretical analysis.

The main concern in the 2D FFT implementation is to keep the ratio of SIMD shuffles to floating-point instructions as low as possible, to avoid bottlenecks on shuffle units. The 1D FFT within rows and the 1D FFT across rows uses different numbers of shuffle instructions. The within-rows variant does butterflies between elements of the same SIMD register, which requires shuffling the register. The across-rows variant does not need any shuffles. In addition to the 1D FFTs, options B and D include transposition of the image tile. A SIMD implementation of transposition consists mostly of SIMD shuffles, and it uses the same number of shuffle instructions as the within-row FFT of a tile. Now we can subsequently eliminate most options:

• We can eliminate option B, because it consists of two 1D FFTs within rows and

a transposition and needs a redundant number of shuffle instructions.

- Options A and C differ only in the order of within-rows and across-rows FFTs. I suggest that it is better to first do FFT across rows, because the first transformation is a real-to-complex FFT, and it exposes additional symmetries, which are easy to use in an across-rows algorithm but require additional shuffles in within-rows variant. This observation eliminates option A in favor of option C.

- Options C and D use the same number of shuffles (transposition needs as many shuffles as within-row FFT of a tile), but in Option D they are all concentrated in the transposition operation, and in Option C they are interleaved with floating-point computations. Therefore, option C is less likely to create a pipeline bubble of shuffle instruction, and should therefore be preferred over option D.

### 3.2.3 Fused Butterfly Operations

The butterfly is one of the two computational components of the FFT. Given two elements, the bufferfly operation computes their sum and difference:

$$a_{\text{out}}, b_{\text{out}} := a_{\text{in}} + b_{\text{in}}, a_{\text{in}} - b_{\text{in}}$$

Some operations can be fused into butterfly at no cost:

- Negation of  $b_{\text{in}}$ :  $a_{\text{out}}, b_{\text{out}} := a_{\text{in}} b_{\text{in}}, a_{\text{in}} + b_{\text{in}}$ .

- Negation of  $b_{\text{out}}$ :  $a_{\text{out}}, b_{\text{out}} := b_{\text{in}} + a_{\text{in}}, b_{\text{in}} a_{\text{in}}$ .

On modern processors the FMA operation often has the same performance characteristics as floating-point addition/subtraction. It makes it possible to fuse scaling of either  $a_{\rm in}$  or  $b_{\rm in}$  by an arbitrary factor, e.g., butterfly $(a_{\rm in}, b_{\rm in} \cdot c)$  can be computed with:

$$a_{\text{out}}, b_{\text{out}} := \underbrace{b_{\text{in}} \cdot c + a_{\text{in}}}_{\text{fma}(b,c,a)}, \underbrace{-b_{\text{in}} \cdot c + a_{\text{in}}}_{\text{fnma}(b,c,a)}$$

No explicit product  $b_{\text{in}} \cdot c$  is formed, and the resulting code has the same cost as a regular butterfly.

I use the fusion technique in the FFT across rows, with the following benefits:

- Eliminate all multiplications by twiddle factors in a 4-sample complex FFT (and an 8-sample real FFT)

- Replace all multiplications by twiddle factors in an 8-sample complex FFT (and a 16-sample real FFT) with only two floating-point additions.

- $\bullet$  Eliminate final scaling by  $\frac{1}{N}$  in the inverse FFT.

- Eliminate several negations and multiplications in the real-to-complex 1D FFT

# 3.3 Winograd Transforms

I follow the specification of  $F(6 \times 6, 3 \times 3)$  – the largest transformation described by Lavin [58] – which extends  $3 \times 3$  kernels and  $8 \times 8$  input tiles into  $8 \times 8$  blocks of transformed coefficients. The convolution of the original tile with the kernel is equivalent to elementwise real product of transform coefficients. The output transform produces a  $6 \times 6$  tile of output samples. Thus, the  $F(6 \times 6, 3 \times 3)$  Winograd transform behaves similarly to an  $8 \times 8$  Fourier transform on  $3 \times 3$  kernels. Unlike the Fourier transform, the Winograd transform depends on the kernel size: my implementation following Lavin [58] handles only  $3 \times 3$  kernels; support for other sizes is possible, but would require a separate implementation.

The 1D Winograd transform is a linear transformation and can be defined by a transformation matrix. The transformation matrix has many zeroes and additional structure, which I exploit in the implementation. I apply a 1D transform across rows

of data block, then transpose it, and apply the same transformation again. Overall, both in the number of operations and in the structure of algorithm, the 2D Winograd transform is simpler than the 2D FFT.

# 3.4 Matrix Multiplication

Figure 25: Layout of an  $8 \times 8$  block of FFT coefficients. Red blocks indicate real coefficients, and yellow and green blocks indicate real and imaginary components of complex coefficients.