## COMET-GPU: A GPGPU-ENABLED DETERMINISTIC SOLVER FOR THE CONTINUOUS-ENERGY COARSE MESH TRANSPORT METHOD (COMET)

A Dissertation Presented to The Academic Faculty

by

Paul Burke

In Partial Fulfillment of the Requirements for the Degree Doctorate in Nuclear Engineering in the George W. Woodruff School of Mechanical Engineering

> Georgia Institute of Technology May 2021

# **COPYRIGHT © 2021 BY PAUL BURKE**

## COMET-GPU: A GPGPU-ENABLED DETERMINISTIC SOLVER FOR THE CONTINUOUS-ENERGY COARSE MESH TRANSPORT METHOD (COMET)

Approved by:

Dr. Farzad Rahnema, Co-Advisor School of Mechanical Engineering *Georgia Institute of Technology*

Dr. Umit Catalyurek, Co-Advisor School of Computational Science and Engineering *Georgia Institute of Technology*

Dr. Daniel Gill Advisor Engineer Naval Nuclear Laboratory, Bettis Dr. Bojan Petrovic School of Mechanical Engineering *Georgia Institute of Technology*

Dr. Dingkang Zhang School of Mechanical Engineering *Georgia Institute of Technology*

Date Approved: April 22, 2021

To my family, friends, and anyone who helped me along the way. I could not have done this without you all.

## ACKNOWLEDGEMENTS

This research was performed under appointment to the Rickover Fellowship Program in Nuclear Engineering sponsored by the Naval Reactors Division of the U.S. Department of Energy.

This research made use of the resources of the High Performance Computing Center at Idaho National Laboratory, which is supported by the Office of Nuclear Energy of the U.S. Department of Energy and the Nuclear Science User Facilities under Contract No. DE-AC07-05ID14517.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                                                   | iv              |

|----------------------------------------------------------------------------------------------------|-----------------|

| LIST OF TABLES                                                                                     | vii             |

| LIST OF FIGURES                                                                                    | viii            |

| LIST OF SYMBOLS AND ABBREVIATIONS                                                                  | X               |

| SUMMARY                                                                                            | xii             |

| CHAPTER 1. Introduction                                                                            | 1               |

| 1.1Motivation1.2Objectives                                                                         | 1<br>4          |

| CHAPTER 2. Background and Theory                                                                   | 6               |

| 2.1 Neutron Transport and the COMET method                                                         | 6               |

| 2.1.1 COMET Theory                                                                                 | 7               |

| 2.1.2 COMET Numerical Steps                                                                        | 11              |

| <ul><li>2.1.3 COMET Parallelization Study</li><li>2.2 General-Purpose GPU Computing</li></ul>      | 13<br><b>16</b> |

| 2.2.1 GPU Programming Considerations                                                               | 16              |

| 2.2.2 GPGPU Programming Interfaces                                                                 | 20              |

| 2.2.3 GPGPU As Applied to Neutron Transport                                                        | 20<br>24        |

| 2.3 Interpretation                                                                                 | 27              |

| CHAPTER 3. COMET-CPP Development and Methodology                                                   | 29              |

| 3.1 Host COMET-cpp Solver Development                                                              | 31              |

| 3.1.1 Solver Front-end                                                                             | 32              |

| 3.1.2 CPU-only Generic BLAS Back-end                                                               | 35              |

| <ul><li>3.2 GPU Back-end Development</li><li>3.3 Post-processing and Visualization Tools</li></ul> | 40<br>54        |

| CHAPTER 4. Benchmark Timing Study                                                                  | 62              |

| 4.1 Benchmark Problems                                                                             | 62              |

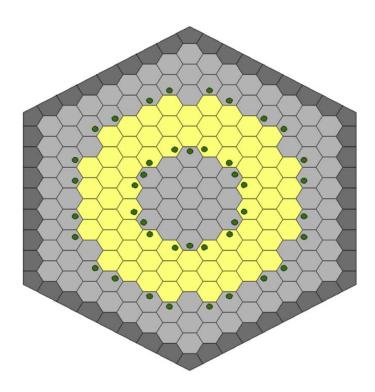

| 4.1.1 Very-High-Temperature Reactor                                                                | 63              |

| 4.1.2 Integral Inherently Safe Light Water Reactor                                                 | 65              |

| 4.1.3 Advanced High-Temperature Reactor                                                            | 66              |

| 4.2 Timing Comparison Methodology                                                                  | 68              |

| 4.3 Results                                                                                        | 72              |

| CHAPTER 5. Convergence Threshold Sensitivity Study                                                 | 83              |

| 5.1 Methodology                                                                                    | 83              |

| 5.2 Results                                                                                        | 87              |

| 5.2.1 Overall Quantitative Results                                                                 | 87              |

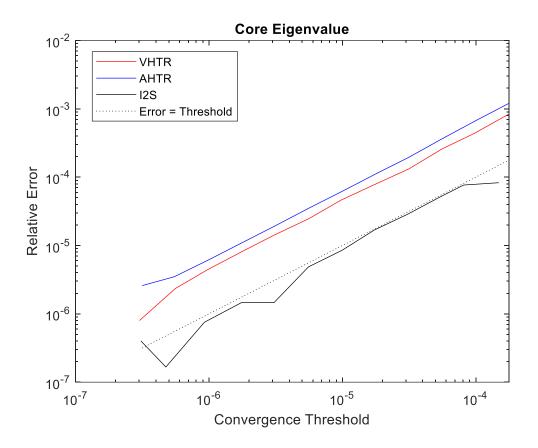

| 5.2.2 Per-Problem Convergence Assessment                                                           | 90              |

| CHAPTER 6.  | Summary, Conclusions, and Future Work | 98  |

|-------------|---------------------------------------|-----|

| APPENDIX A: | Raw Benchmark Timing Data             | 102 |

| REFERENCES  | 5                                     | 105 |

# LIST OF TABLES

| Table 1: UVM Test Results    4                             | 11 |

|------------------------------------------------------------|----|

| Table 2: cuBLAS Comparison Results       4                 | 18 |

| Table 3: Output Tables    5                                | 55 |

| Table 4: Serial Solver Performance    7                    | 73 |

| Table 5: COMET-cpp CPU-only Performance                    | 73 |

| Table 6: COMET-cpp GPU-Accelerated Performance       7     | 75 |

| Table 7: AHTR Inner Iteration Execution times              | 78 |

| Table 8: Small Chunk Kernel Execution Times                | 79 |

| Table 9: AHTR Scaling, Small-Chunk Solver                  | 30 |

| Table 10: Achieved GPU Performance Metrics    8            | 31 |

| Table 11: Raw VHTR Benchmark Timing Data       10          | )2 |

| Table 12: Raw I <sup>2</sup> S Benchmark Timing Data    10 | )3 |

| Table 13: Raw AHTR Benchmark Timing Data    10             | )4 |

# LIST OF FIGURES

| Figure 1: Geometric Domain Composition (Figure from [2])14                               |

|------------------------------------------------------------------------------------------|

| Figure 2: COMET-MPI Scaling Study Results (Reconstructed from data in [2])15             |

| Figure 3: CPU vs. GPU Architectures (Figure from [4])17                                  |

| Figure 4: CUDA Execution Hierarchy (Figure from [7])                                     |

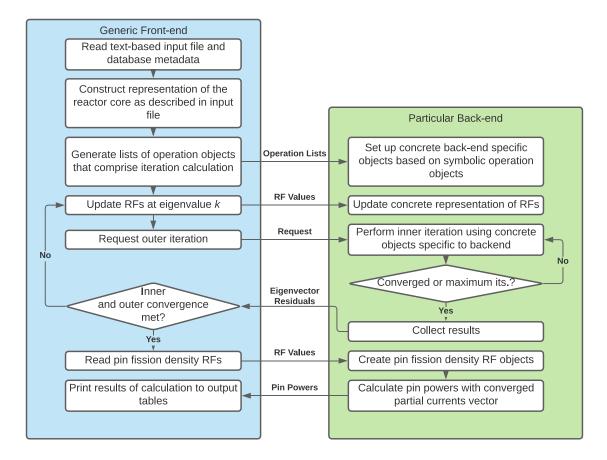

| Figure 5: Separation and Exchange Between Front- and Back-ends                           |

| Figure 6: Example Problem Geometry and Vector                                            |

| Figure 7: Small Dense Matrix Multiplications for Inner Iteration                         |

| Figure 8: Intermediate Results Reduction                                                 |

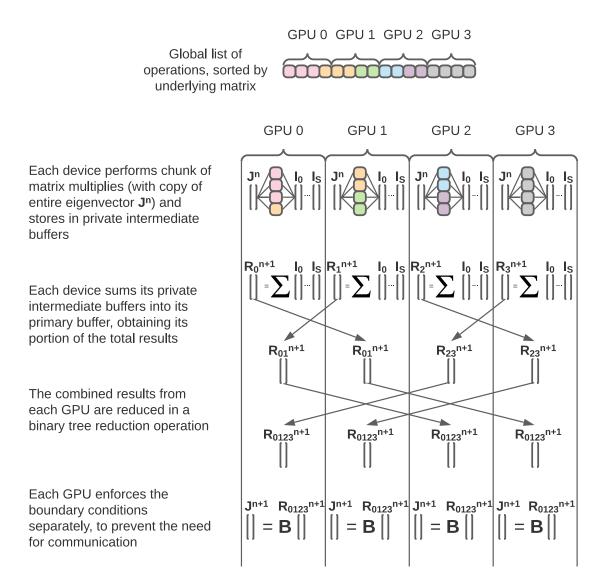

| Figure 9: Multi-GPU Calculation Scheme                                                   |

| Figure 10: Batched-GEMV Pseudo-code                                                      |

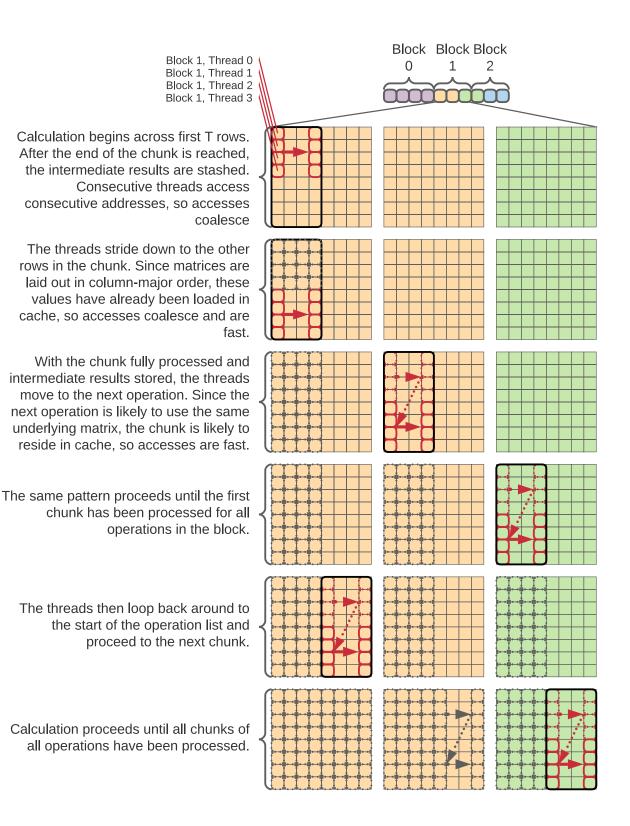

| Figure 11: Batched-GEMV Kernel Visualization                                             |

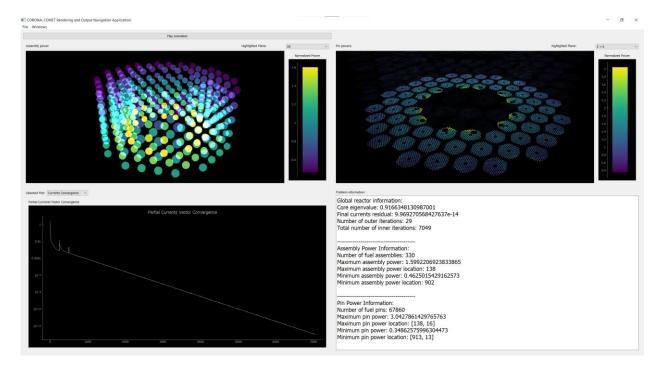

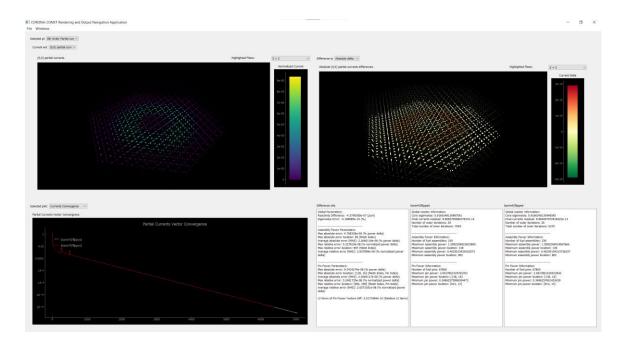

| Figure 12: Single-core Visualization Mode Screenshot                                     |

| Figure 13: Two-Core Difference Visualization Mode Screenshot                             |

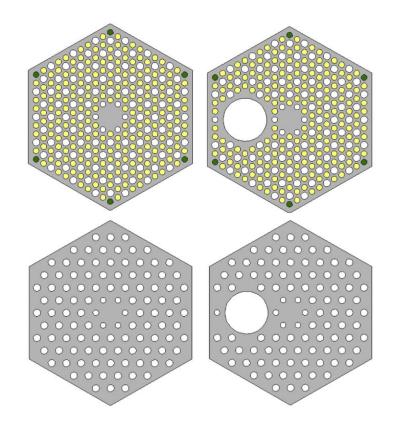

| Figure 14: VHTR Layer Depiction (Figure from [29])63                                     |

| Figure 15: VHTR Component Blocks (from [29]): Fuel Block (top left), Fuel Block with     |

| Control Channel (top right), Reflector Block (bottom left), Reflector Block with Control |

| Channel (bottom right)                                                                   |

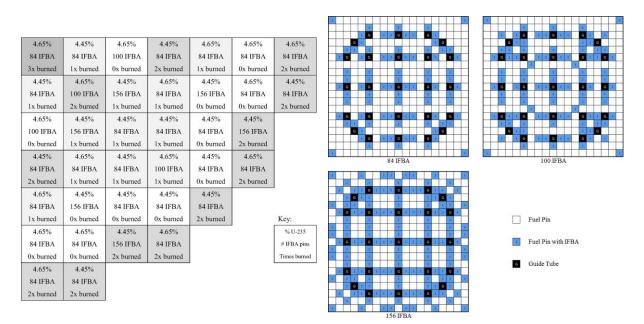

| Figure 16: I <sup>2</sup> S Loading Plan (from [28])65                                   |

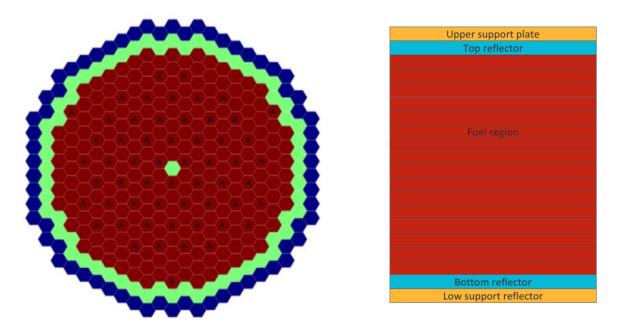

| Figure 17: AHTR Problem Layout (from [36]): Radial (left), Axial (right)                 |

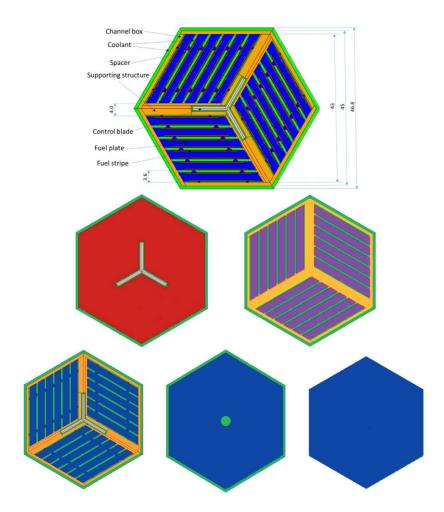

| Figure 18: AHTR Mesh Composition (from [36]): Fuel (top), Upper Support (middle      |

|--------------------------------------------------------------------------------------|

| left), Lower Support (middle right), Top/Bottom Reflector (bottom left), Replaceable |

| Reflector (bottom middle), Permanent Reflector (bottom right)                        |

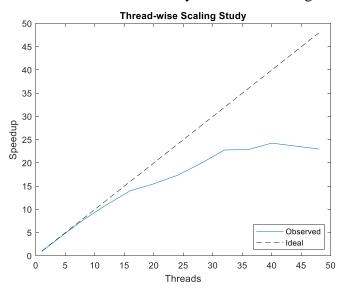

| Figure 19: CPU-only Thread-wise Scaling Study74                                      |

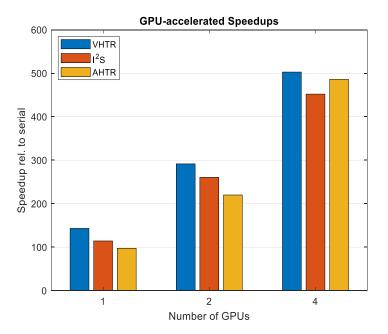

| Figure 20: GPU Acceleration Relative to Serial Solver                                |

| Figure 21: AHTR 1 GPU Profiling77                                                    |

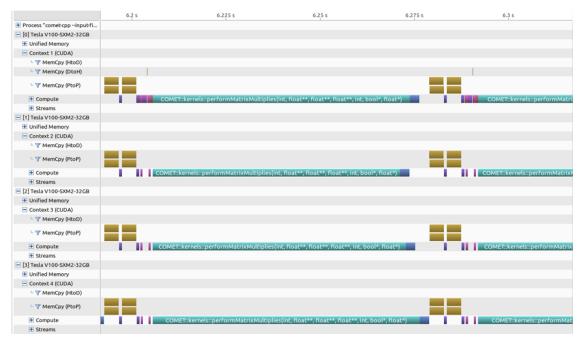

| Figure 22: AHTR Multi-GPU Profiling: 2 Devices (top), 4 GPU (bottom)78               |

| Figure 23: Small Chunk Solver Profiling79                                            |

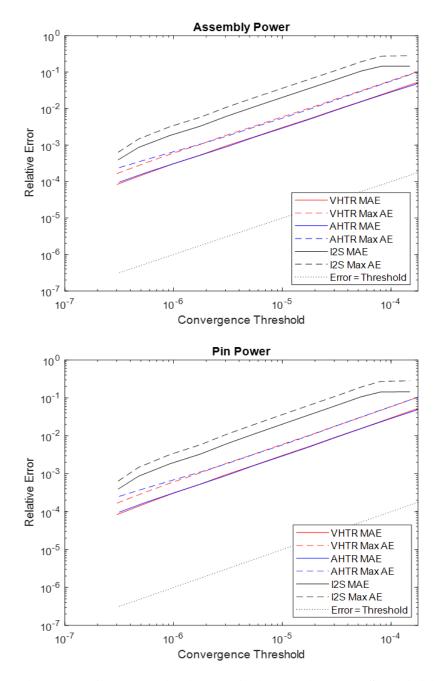

| Figure 24: Criticality Eigenvalue Sensitivity                                        |

| Figure 25: Assembly (top) and Pin (bottom) Power Sensitivities                       |

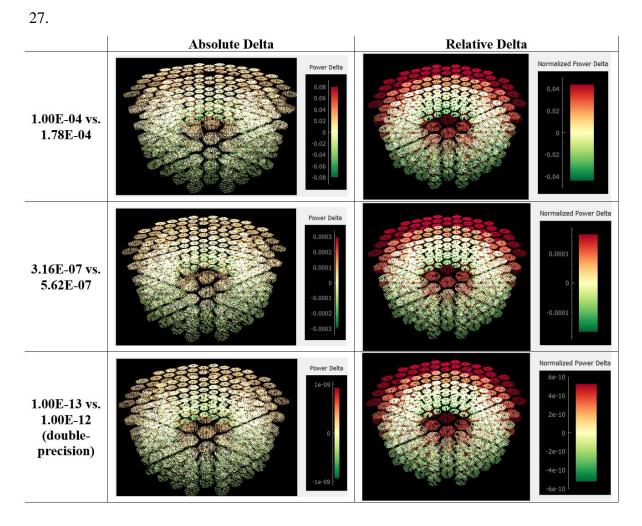

| Figure 26: VHTR Pin Power Differences                                                |

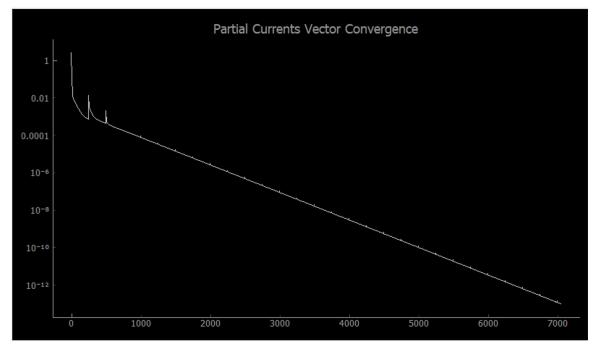

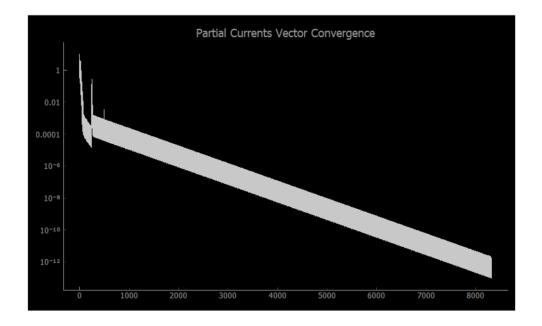

| Figure 27: VHTR Partial Currents Vector Convergence                                  |

| Figure 28: I <sup>2</sup> S Assembly Power Differences                               |

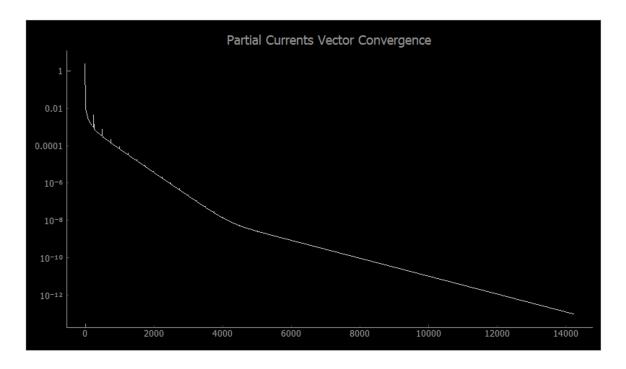

| Figure 29: I <sup>2</sup> S Partial Currents Vector Convergence                      |

| Figure 30: AHTR Partial Currents Vector Convergence                                  |

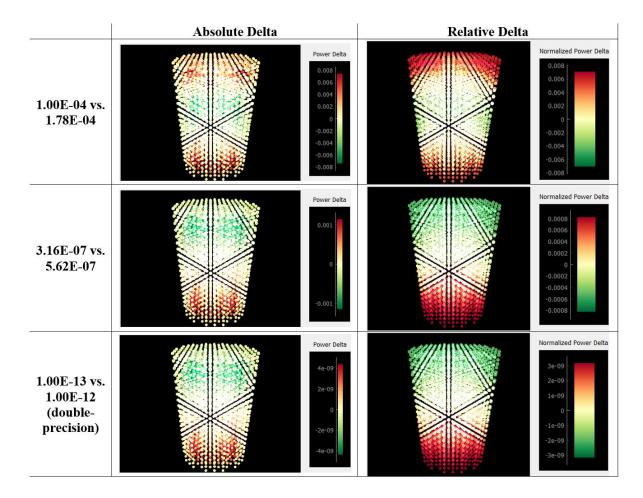

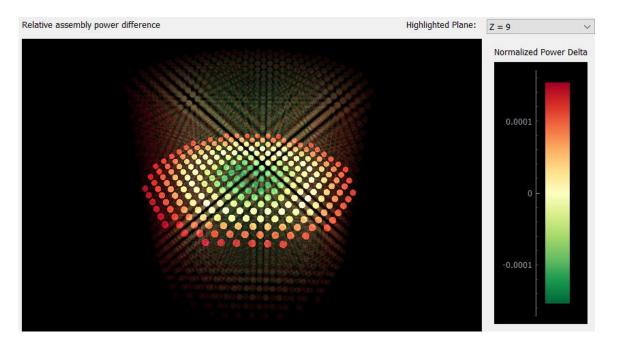

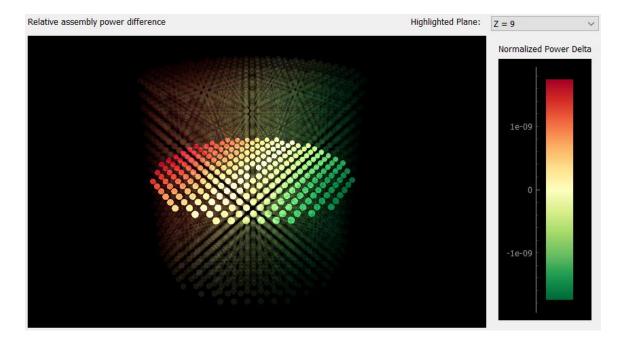

| Figure 31: AHTR Assembly Power Relative Differences, 3.16E-07 vs. 5.62E-0796         |

| Figure 32: AHTR Assembly Power Relative Differences, 1.0E-13 vs. 1.0E-12             |

# LIST OF SYMBOLS AND ABBREVIATIONS

## AE Absolute Error

| AHTR  | Advanced High-Temperature Reactor        |

|-------|------------------------------------------|

| ARI   | All-rods-in                              |

| BLAS  | Basic Linear Algebra Subprograms         |

| CDF   | Common Data Format                       |

| CE    | Continuous Energy                        |

| CMFD  | Coarse Mesh Finite Difference            |

| COMET | Coarse Mesh Transport                    |

| GEMM  | Generic Matrix-Matrix                    |

| GEMV  | Generic Matrix-Vector                    |

| GPU   | Graphics Processing Unit                 |

| GPGPU | General Purpose Graphics Processing Unit |

- I<sup>2</sup>S Integral Inherently Safe Reactor

- **J** Global partial current moments vector

- *k* Core criticality eigenvalue

- MAE Mean Absolute Error

- MPI Message Passing Interface

- ms Milliseconds

- RF Response Function

- SIMD Single-instruction-multiple-data

- SM Streaming Multiprocessor

- TRISO Tri-structural Isotropic

- UVM CUDA Unified Virtual Memory

- VHTR Very-High-Temperature Reactor

## SUMMARY

The Continuous-Energy Coarse Mesh Transport (COMET) method is a neutron transport solution method that uses a unique hybrid stochastic-deterministic solution method to obtain high-fidelity whole-core solutions to reactor physics problems with formidable speed. This method involves pre-computing solutions to individual coarse meshes within the global problem, then using a deterministic transport sweep to construct a whole-core solution from these local solutions. In this work, a new implementation of the deterministic transport sweep solver is written which includes the ability to accelerate the calculation using up to 4 Graphics Processing Units (GPUs) on one computational node. The new implementation is written in C++ with GPU-facing logic leveraging the CUDA API.

To demonstrate the new implementation, three whole-core benchmark problems were solved using the previous serial solver and various configurations of the new solver, with the relative performance compared. In this comparison, it was found that the application of one GPU to the problem resulted in between a 100x-150x speedup (depending on the specific problem) relative to the old serial solver. Excellent scaling up to 4 GPUs was observed, which brought the total speedup up to 450x-500x. Although the magnitude of the speedup was found to be problem dependent, it is noted that the overall strategy of the acceleration is not problem dependent.

As an example of a new type of analysis which is enabled by the improved speed of the solver, a sensitivity study was performed on the convergence thresholds used in controlling the inner and outer iteration processes. This study involves repeatedly solving whole-core problems using slightly varying thresholds, including computing a "goldstandard" solution to double-precision. These various runs would be prohibitively expensive if run using the old solver (upwards of weeks) but in this work were completed in around an hour. The results of the sensitivity study show that some examined cases indicate that converging the problem completely to the limits of single-precision numbers can result in pin power errors on the order of 0.1% as compared to a completely converged double-precision result. This behavior was found to be problem dependent.

## CHAPTER 1. INTRODUCTION

In the design and operation of a nuclear reactor, accurate modeling of the neutronic characteristics of the reactor is of paramount importance. This involves obtaining a solution to the Boltzmann neutron transport equation. The steady-state neutron transport equation involves 6 independent variables. As a result, the equation cannot be solved analytically in all but the simplest cases. To obtain solutions for real-word problems, numerical solution methods must be used. One such numerical transport method is the continuous-energy (CE) Coarse Mesh Transport (COMET) method developed at the Computational Reactor and Medical Physics Laboratory at Georgia Tech [1]. The COMET method uses a unique hybrid stochastic-deterministic solution method to obtain high-fidelity whole-core solutions to reactor physics problems with formidable speed. In this work, a new implementation of the CE-COMET method will be developed to leverage Graphics Processing Unit (GPU) architectures.

## 1.1 Motivation

The High-Performance Computing (HPC) landscape for scientific computing has seen a rise in General-Purpose GPU (GPGPU) computing. GPUs differ from regular CPUs in that their architecture is designed to support many more cores (5,120 CUDA cores on the NVIDIA Tesla V100 [2]) than a CPU. These cores are designed to support the execution of the same set of operations on a large number of different data regions. As a result, these devices excel in terms of both speed and efficiency at "data-parallel" problems: problems which perform a similar set of operations repeatedly over a large amount of data. The advancement of this technology has resulted in a shift in recent years toward an increased GPU to CPU balance ratio. The flagship HPC resources from Oak Ridge National Laboratory demonstrate this trend: Titan (1:1 ratio, 2012, [3]), Summit (6:2 ratio, 2018, [4]), and Frontier (4:1 ratio, scheduled 2021, [5]).

To effectively implement an algorithm on GPU architectures, the maximum possible degree of data parallelism must be exposed in the problem. In this context, the deterministic transport sweep of the CE-COMET method is an excellent fit for GPU parallelization. The transport sweep consists of a nested iteration process in which the inner iterations correspond to a power iteration method used to converge to the dominant eigenvector of the global reactor problem. In the power method, the n<sup>th</sup> guess at the eigenvector is constructed using data only from the previous guess. With this, the operations used to update the eigenvector can be performed entirely independently, as will be shown in Chapters 2 and 3. This fact places the COMET transport sweep in a class of problems that can be called "embarrassingly parallel". It is this inherent parallelism that will be exploited in this work to construct a GPU implementation of the method.

Whole-core CE-COMET problems are an excellent candidate for a GPUaccelerated parallel implementation. Calculations for these problems generally involve performing up to several hundred thousand dense matrix multiplications, with matrices up to 720 x 720 or larger in size. These matrix multiplications generally comprise upwards of 99% of the program runtime, with operations taking place on tens-hundreds of gigabytes of data. These operations and memory accesses are highly regular, which are excellent features for a GPU implementation. It is well-demonstrated (as will be discussed in Chapter 2) that, in highly regular operations such as these, one GPU can provide as much as 2+ orders of magnitude speedup as compared to one CPU thread. Such a speedup for a CPU- only parallel implementation would likely require multi-threaded and multi-node execution, which brings extra complication when it comes to communication, problem decomposition, and work distribution. It is thus of great interest to explore shared-memory parallelism and GPU-acceleration to demonstrate the speed that could be achieved on one computational node before moving to a multi-node implementation.

The fact that the block of matrix multiplication operations is so monolithic also implies that more than 1 GPU could be effectively employed in solving the problem. Since GPU-to-GPU data transfer is quite fast, the cost of communication can be kept low. It is thus reasonable to expect that additional GPUs applied to a CE-COMET problem will provide additional speedup, firmly planting the total speedup between 2 and 3 orders of magnitude. A multi-GPU approach also provides an additional benefit in that it enables larger problems to fit entirely into device memory (generally limited to a couple tens of GB). This is an excellent feature that enables continued applicability of the GPU solver as COMET is extended to operate on problems with larger and larger memory footprints.

The promise of more than 2 orders of magnitude speedup and the suitability of COMET for a GPU implementation thus forms the motivation for this work. The implications of such a speedup for the future of the method are extensive. The speed could enable multi-physics, time-dependent, and depletion calculations while maintaining a reasonable total runtime. It will also be demonstrated in this work that this could enable a mixed-precision approach to the numbers involved in calculation. The objectives of this work are designed to demonstrate the applicability of the problem to a GPU-accelerated implementation and show the benefits of the additional speedup.

#### 1.2 Objectives

In this work, a new implementation of the COMET method will be developed that targets calculation on GPU architectures. As will be explained in Chapter 3, part of this undertaking involved the development of new host code as well, converting the serial Fortran solver into a C++ solver. This allows the opportunity to re-order operations and re-arrange memory to allow for an optimized parallel implementation. A CPU-only shared-memory parallel solver will also be developed as a secondary objective.

As a demonstration of the improved performance due to the newly developed capabilities, in Chapter 4 the new solver is applied to a set of whole-core benchmark problems. The performance of the code is demonstrated via comparison against the current serial solver, and scaling studies are performed for 1, 2, and 4 GPU configurations. The GPU-accelerated solver is demonstrated to have 2+ orders of magnitude speedup as compared to the serial solver.

As an example of a type of additional analysis unlocked by the new speed of the GPU-accelerated solver, a sensitivity study was performed on the specific thresholds used in truncating the iteration process. The methodology and results of this study are documented in Chapter 5. This type of analysis would have been technically possible with the serial solver (except for the double-precision runs), but the computation time alone would have spanned weeks, effectively prohibiting such a study. The specific runs for this study were completed in around an hour, including two special runs (per problem) in which gold-standard solutions were converged in double-precision (rather than the single-precision COMET typically uses) to around machine epsilon. The results of the study

indicate that the problem-dependent nature of the convergence of COMET solutions can result in varying differences between solutions obtained with a specific set of convergence criteria and the gold-standard solution, including up to 3-4 orders of magnitude difference between the input threshold on relative residual eigenvector norm and the resulting error.

In Chapter 6, a set of conclusions are drawn from the results of this work. Implications of the increased computational speed are discussed, and a recommendation is made for future work both on the solver itself and as studies unlocked by the speed.

## CHAPTER 2. BACKGROUND AND THEORY

In this chapter, the requisite background knowledge and theory for the work is described. The first section deals with background information on the neutron transport equation and the COMET solution method (primarily as described in [1]). This first section also includes a review of previous work that examined CPU-only parallelization of the method [6]. The second section gives background knowledge on GPU parallelization and the specific considerations that must be examined when writing GPU-capable programs. This section also includes a review of other neutron transport solvers (stochastic and deterministic) that have leveraged GPU architectures. The third section provides a brief interpretation of this background information that forms the basis for the following work.

## 2.1 Neutron Transport and the COMET method

The Boltzmann neutron transport equation (eq. 2.1.1) describes the distribution of neutrons in a steady-state system. In this equation,  $\vec{r}$  indicates the position in 3-dimensional space,  $\hat{\Omega}$  indicates the angle of the neutron flight, E indicates the neutron's energy,  $\psi(\vec{r}, \hat{\Omega}, E)$  indicates the angular neutron flux,  $\sigma$ ,  $\sigma_s$ , and  $\sigma_f$  indicate the total, scatter, and fission cross sections, k indicates the criticality eigenvalue,  $\chi$  indicates the fission spectrum, and  $\nu$  indicates the neutrons emitted per fission. This "steady-state transport equation" is observed to have 6 independent variables (3 spatial variables, 2 angular variables, and 1 energy variable), which makes direct solution impossible in all but the simplest cases. As such, obtaining solutions to whole-core problems involves the use of numerical methods and approximations.

$$\begin{split} \widehat{\Omega} \cdot \nabla \psi(\vec{r}, \widehat{\Omega}, E) &+ \sigma(\vec{r}, E) \psi(\vec{r}, \widehat{\Omega}, E) \\ &= \int_{0}^{\infty} dE' \int_{4\pi} d\widehat{\Omega}' \, \sigma_{s}(E', \widehat{\Omega}' \to E, \widehat{\Omega}) \psi'(\vec{r}, \widehat{\Omega}', E') \\ &+ \frac{1}{k} \frac{1}{4\pi} \chi(\vec{r}, E) \int_{0}^{\infty} dE' \, \nu \sigma_{f}(\vec{r}, E') \int_{4\pi} d\widehat{\Omega}' \, \psi'(\vec{r}, \widehat{\Omega}', E') \end{split}$$

(2.1.1)

For brevity, we define an operator form of the transport equation (eq. 2.1.2), where **H** is termed the transport operator, **F** the fission operator, and **B** the boundary conditions for the problem.

$$H\psi(\vec{r},\hat{\Omega},E) = \frac{1}{k}F\psi(\vec{r},\hat{\Omega},E), \quad \vec{r} \in V,$$

$$\psi(\vec{r},\hat{\Omega},E) = B\psi(\vec{r},\hat{\Omega},E), \quad \vec{r} \in \partial V \& \hat{\Omega} \cdot \hat{n} < 0$$

$$H = \hat{\Omega} \cdot \nabla + \sigma(\vec{r},E) - \int_{0}^{\infty} dE' \int_{4\pi} d\hat{\Omega}' \sigma_{s}(E',\hat{\Omega}' \to E,\hat{\Omega})$$

$$F = \frac{1}{4\pi}\chi(\vec{r},E) \int_{0}^{\infty} dE' \nu \sigma_{f}(\vec{r},E') \int_{4\pi} d\hat{\Omega}'$$

(2.1.2)

## 2.1.1 COMET Theory

One such numerical solution method for the neutron transport equation is the continuous-energy COMET method. In the COMET method [1], the spatial domain of the problem *V* is divided into a number of contiguous coarse meshes  $V_i$ . From there, the angular flux that lies on the boundary of each mesh  $\partial V_i$  is expanded in terms of an orthogonal basis set as in eq. 2.1.3, where  $\psi_{is}^{\pm}$  represents the outgoing or incoming flux on surface *s* of the

$i^{\text{th}}$  coarse mesh,  $J_{is}^{\pm,m}$  represents the corresponding surface *flux expansion coefficient*, W(E) is a positive weight function (discussed later in this section), and  $\Gamma_m$  is the  $m^{\text{th}}$  member of an orthogonal basis function set of M members.

$$\psi_{is}^{\pm}(\vec{r}, \widehat{\Omega}, E) \approx \sum_{m=1\dots M} J_{is}^{\pm, m} W(E) \Gamma_m(\vec{r}, \widehat{\Omega}, E) \quad , \quad \vec{r} \in \partial V_{is} \quad (2.1.3)$$

With the flux on the surface of each mesh expanded in terms of the basis set, we can then express the flux in the interior of each mesh in terms of a *surface-to-volume response function*, as in eq. 2.1.4.

$$\psi_i(\vec{r}, \widehat{\Omega}, E) = \sum_{s,m} J_{is}^{-,m} R_{is}^m(\vec{r}, \widehat{\Omega}, E) \quad , \quad \vec{r} \in V_i$$

(2.1.4)

These surface-to-volume response functions can be interpreted as the solution to a corresponding local problem in which a surface flux in the shape of the specific response function  $\Gamma_m$  is imposed on surface *s*, as in eq. 2.1.5.

$$R_{is}^{m}(\vec{r}, \widehat{\Omega}, E; k) = \frac{1}{k} F R_{is}^{m}(\vec{r}, \widehat{\Omega}, E; k) , \quad \vec{r} \in V_{i}$$

$$R_{is}^{m}(\vec{r}, \widehat{\Omega}, E; k) = \begin{cases} W(E) \Gamma_{m}(\vec{r}, \widehat{\Omega}, E) , & \vec{r} \in \partial V_{is}, \ \widehat{\Omega} \cdot \widehat{n}_{is}^{+} < 0 \\ 0 , & otherwise, \ \widehat{\Omega} \cdot \widehat{n}_{is}^{+} < 0 \end{cases}$$

$$(2.1.5)$$

By examining the value of  $R_{is}^m$  along the surface of the mesh and expanding it in terms of the basis set in the **outgoing** direction, we arrive at the *surface-to-surface response* function coefficient  $R_{isrs}^{m'm}$ , which represents the response on surface s in moment m due to a unit incoming flux on surface s' in moment m'. Due to the linearity of the transport and

fission operators, the relationship between the outgoing and incoming flux expansion coefficients can be expressed as in eq. 2.1.6.

$$J_{is}^{+,m} = \sum_{s'} \sum_{m'} R_{is's}^{m',m}(k) J_{is'}^{-,m'}$$

(2.1.6)

By expressing the partial current expansion coefficients in vector form across the individual moments in the expansion basis set, eq. 2.1.6. can be expressed as a matrix-vector operation as in eq. 2.1.7, where  $\mathbf{r}_{isrs}$  represents an  $M \ge M$  surface-to-surface response function matrix for mesh *i* from surface *s* ' to *s*, and  $\mathbf{j}_{is}^{\pm}$  represents an  $M \ge 1$  column vector of the outgoing/incoming individual partial current expansion coefficients for surface *s* of mesh *i*.

$$\boldsymbol{j}_{is}^{+} = \sum_{s'} \boldsymbol{r}_{is's}(k) \boldsymbol{j}_{is'}^{-}$$

(2.1.7)

These surface-to-surface response function coefficients can be used to construct a solution to the global problem by ensuring continuity between the outgoing flux expansion coefficient for a given mesh and surface and the corresponding incoming flux expansion coefficient on the neighboring mesh/surface. By concatenating the individual flux expansion vectors  $\mathbf{j}_{is}^{\pm}$  for the problem into a global *partial current expansion coefficients* vector  $\mathbf{J}$ , this continuity condition can be expressed as in eq. 2.1.8, where  $\mathbf{R}$  represents a block-sparse matrix corresponding to the collection of the above  $\mathbf{r}_{isrs}$  for the global problem,  $\mathbf{M}$  represents a connectivity matrix that connects the incoming and outgoing partial current expansion coefficients, and  $\lambda$  represents the discontinuity resulting from differences between the evaluated k and the true core eigenvalue k.

$$MR(k)J = \lambda J \tag{2.1.8}$$

In the case where the response functions for the global problem R are evaluated at the true core eigenvalue,  $\lambda$  is equal to unity and J represents the true inter-mesh partial current expansion coefficients for the problem.

Now, if the orthogonal basis set chosen to expand the surface flux (eq. 2.1.3.) is complete (infinite), then the solution is exact. The approximation in the method is introduced when selecting which basis set to use and at the order at which the set is truncated. For the COMET method, the typical basis set uses Legendre polynomials  $P_n$  in the *x*, *y*, and azimuthal ( $\phi$ ) variables and Chebyshev polynomials of the second kind  $U_n$  in the (polar)  $\mu$  variable, as in eq. 2.1.9.

The dependence of the angular flux on the energy variable generally varies too sharply for a similar type of polynomial expansion method to be applicable. Instead, a weight function W(E) is included in the expansion (eq. 2.1.3.) and divisions of unity (or zeroth-order B-splines) across a set of energy groups g are used to satisfy the orthogonality condition. The complete basis set is thus seen in eq. 2.1.9.

$$\Gamma_{ijklg}(x, y, \mu, \phi, E) = P_i(x)P_j(y)U_k(\mu)P_l(\phi)B_{g,0}(E)$$

(2.1.9)

For a continuous-energy treatment, the weight function W(E) is typically chosen to be the asymptotic neutron spectrum, computed from a typical single assembly or color set calculation. It is observed that the lowest-order base case corresponding to W(E) = 1describes a multi-group treatment. To create an expression for the core criticality eigenvalue k, it is useful to define two new response functions  $RNF_{is}^{m}(k)$  and  $RAB_{is}^{m}(k)$ , describing the total fission and total absorption in a mesh i due to a unit flux imposed on surface s with shape m. A global particle balance can then be used to create an expression for k based on these total fission and absorption response functions and the flux expansion moments  $J_{is}^{-,m}$  as in eq. 2.1.10.

$$k = \frac{\sum_{i,s,m} J_{is}^{-,m} RNF_{is}^{m}}{\sum_{i,s,m} J_{is}^{-,m} RAB_{is}^{m} + \sum_{\partial V_{is} \in \partial V} (J_{is}^{+,0} - J_{is}^{-,0})}$$

(2.1.10)

It is useful to condense the summation across the *m* index (as in going from eqs. 2.1.6 to 2.1.7 above). By doing so, we express a vector inner product between the surfacewise partial current moments vector  $\mathbf{j}_{is}^-$  and a total absorption or a total fission response vector  $\mathbf{rab}_{is}$  or  $\mathbf{rnf}_{is}$  representing the total absorption or fission in the mesh due to an incident flux  $\mathbf{j}_{is}^-$ . This condensation results in a new surface-wise particle balance equation, as in eq. 2.1.11.

$$k = \frac{\sum_{i,s} rnf_{is}^{T} j_{is}^{-}}{\sum_{i,s} rab_{is}^{T} j_{is}^{-} + \sum_{\partial V_{is} \in \partial V} (J_{is}^{+,0} - J_{is}^{-,0})}$$

(2.1.11)

#### 2.1.2 COMET Numerical Steps

When solving a reactor problem, COMET proceeds as a two-phase process. In the first phase, Monte Carlo transport is used to generate the requisite response functions by solving the local problems described by eq. 2.1.5. This phase is not the subject of the work described in this document, and thus a description of the process is omitted. In principle, the method used to generate the response functions is not required to even be Monte Carlo

transport and could instead be any solver capable of solving the local problems described by eq. 2.1.5. For more information on the response function generation phase, interested readers are directed to [1].

The second phase of the COMET method is a deterministic transport sweep to determine the true core criticality eigenvalue k and partial currents expansion eigenvector j as described in Section 2.1.1. This is a nested iteration process consisting of inner iterations on the eigenvector j and outer iterations on the criticality k. The inner iterations solve the generalized eigenproblem described by eq. 2.1.8. The outer iterations update the guess for the core criticality k using the particle balance described in eq. 2.1.11. With this, the deterministic transport sweep algorithm proceeds (from [1]) as:

- 1. Guess the initial eigenvalue  $k_0$

- 2. Perform inner iterations for the specific eigenvalue computed in the previous step.

- a. Normalize the outgoing partial current moments.

- b. Use the external boundary condition or the internal interface condition to update the incoming partial current moments.

- c. Use response function coefficients to compute the outgoing partial current moments.

- d. Repeat (a.) (c.) until the partial current moments are converged.

- 3. Use the global particle balance to update the eigenvalue guess *k*.

- 4. Repeat (2.) and (3.) until the eigenvalue is converged.

The current implementation of this process is written in Fortran. It stores the response function matrices in Common Data Format (CDF) [7], a self-describing portable binary data format maintained by the Space Physics Data Facility at Goddard Space Flight Center. In practice, the power method is used to solve the inner iteration eigenproblem, with a Chebyshev polynomial filtering acceleration method applied. It leverages Intel MKL [8] to perform the individual matrix multiplies expressed in eq. 2.1.7. The production build is serial, with no parallel computation capabilities (shared- or distributed-memory) for the deterministic transport phase of calculation. The results of the calculations are printed in output text files and parsed with a variety of post-processing tools.

The order in which the code performs the individual small matrix multiplications (called the "sweep order") can have a strong effect on the runtime of the program. For the current serial COMET, the sweep order used in practice groups together all multiplications by coarse mesh fill type and surface, such that consecutive multiplies are likely to use the same underlying response function matrix  $r_{isrs}$ . In this way, it is more likely that the matrix will already reside in cache, and as such can be read and used in multiplication faster than if it needed to be fetched from memory. In principle, however, since the power iteration process only relies on the previous guess for the eigenvector, these multiplications can be performed in any arbitrary order, with any arbitrary degree of concurrency. In this way, the COMET method is ripe for parallelization.

### 2.1.3 COMET Parallelization Study

A previous Ph.D. dissertation examined the possibility of extending the COMET method to distributed-memory (CPU-only) parallel systems [6]. In this work, a proxy app

called COMET-MPI was developed as a fork of the (at the time) production build of the main COMET app. Written in Fortran, it leverages the Message Passing Interface (MPI) to distribute work to many independent processes, either residing on one or many physical CPUs. As a distributed-memory parallel program, each process maintains its own independent memory space and communicates with other processes by explicitly sending and receiving data.

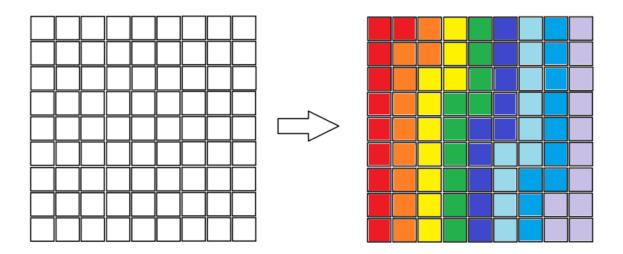

The COMET-MPI study used a geometric decomposition to partition work between the multiple processors, as seen in Figure 1. In such a scheme, the problem is divided such that each processor works on all calculations for a group of meshes that are contiguous in geometric space. In this way, processors need only exchange information about the borders between its own domain and that of the other processors. During each inner iteration, each processor performs the matrix multiplies necessary to update its own domain, then exchanges this new information with its neighbors.

Figure 1: Geometric Domain Composition (Figure from [2])

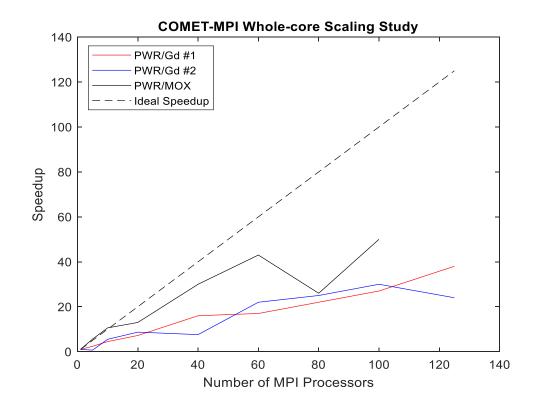

Testing with the proxy app indicated performance that was promising. The code was demonstrated on up to 125 MPI processors on two PWR problems, one with gadolinium and one with MOX. The results can be seen in Figure 2. It is observed that a maximum speedup of 50x was achieved with 100 processors on the PWR/MOX problem. Efficiency was problem-dependent and even varied depending on the specific run, but hovered between 20% and 60% for the investigated range. It is noted that these runs were performed on a shared cluster, and as such the absolute metrics could be expected to vary from run to run. However, the general trend was that of marginally decreasing efficiency with increased numbers of processors.

Figure 2: COMET-MPI Scaling Study Results (Reconstructed from data in [2])

The study identified a hybrid approach in which distributed-memory and sharedmemory parallelism are combined as an area of possible future work. This was partially in response to a case with higher-order function basis sets in which the distributed-memoryonly solver would run out of memory due to the fact that each process needs its own memory space, even when it resides on the same physical processor. The study implemented an initial hybrid implementation with OpenMP + MPI, but the results remained inconclusive, with the code showing either improved or worsened performance.

## 2.2 General-Purpose GPU Computing

General-purpose GPU (GPGPU) computing is a field in which Graphics Processing Units (GPUs) are applied to non-graphics workloads. This practice has been applied broadly to many different areas of scientific computing, including neutron transport.

#### 2.2.1 GPU Programming Considerations

Due to the differences in design between GPUs and CPUs, writing programs that run on a GPU can involve restructuring large parts of algorithms and implementations. However, depending on the specific workload, this strategy can result in exceptional performance increases due to the strengths of GPUs.

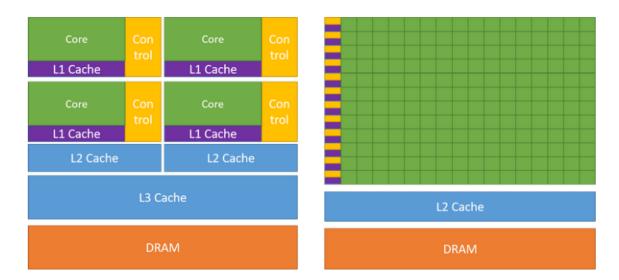

To understand the strengths of GPUs and thus the goals of GPGPU computing, it first of use to establish the differences between a GPU and a CPU. The primary purpose of a CPU is to perform an arbitrary string of operations as quickly as possible. Since the CPU must be general purpose, it needs to be able to quickly handle things like conditional branches that require dedicated circuitry to handle quickly (Figure 3). As a result, CPUs can generally only perform operations on 10s of threads at a time, but each thread can operate independently and branch on its own with minimal performance impact.

Figure 3: CPU vs. GPU Architectures (Figure from [4])

By contrast, GPUs (often simply called devices in the context of GPGPU computing) excel at single-instruction-multiple-data (SIMD) computation. In such computation, the same set of instructions is performed on multiple different data streams. This type of computation comprises the bulk of graphics workloads, in which points in 2D or 3D space have the same geometric transforms imposed upon them. To accommodate this type of SIMD computation, the silicon at the core of a GPU has a much higher proportion of transistors devoted to arithmetic and logic, rather than control circuits and cache (Figure 3). As a result, any individual GPU thread is comparatively weaker than a CPU thread. However, a GPU can operate many more threads at once than a CPU (1,000s to 10,000s).

As a result of these device design features, there are several key differences between the way programs execute on a GPU vs. on a CPU. The most immediate difference between parallel programs on a CPU and on a GPU is that, on GPUs, threads are broken into groups that must operate in lockstep. For NVIDIA GPUs, this grouping is called a "warp" and contains 32 threads on the Tesla and Ampere architectures [2], [9]. For the AMD CDNA architecture, this grouping is called a "wavefront" and contains 64 "workitems" [10]. For the remainder of this document, unless otherwise specified, the NVIDIA terminology will be used for consistency, since the devices/library used in this work come from NVIDIA.

The warp distinction is significant because all threads in a warp share only one actively executing instruction per cycle. If for some reason (e.g. conditional branching) one thread jumps to a different instruction than the remaining threads in a warp, that thread will sit idle while the others execute until its instruction is reached. For branch-heavy operations, this can be a significant performance penalty. If 16 threads branch to one instruction while the other 16 threads branch to a different instruction, the effective rate at which instructions are being executed is halved, as those threads are forced to sit idle. As such, it is imperative for maximum performance that the number of threads executing the same instruction (to the warp level) is maximized. The ratio between the number of threads in a streaming multiprocessor (SM) that *are* executing to the number that *could be* executing is called **occupancy**. Occupancy is affected by thread divergent execution, but can also be limited by the number of registers that a thread needs relative to the available resources on the SM, etc.

The second difference between effective CPU and GPU programs is in optimal memory access patterns. For CPU programs, memory is often laid out to maximize the use of the cache. As such, it is generally structured such that consecutive **instructions** access

consecutive locations in memory. On the first access, the entire page is loaded into cache, so it is likely subsequent instructions will access memory locations that have already been loaded into cache. Since accessing cache is faster than accessing memory, performance is generally improved. An example of this is a matrix-vector multiplication in which the matrix is laid out in **row-major** order, such that a thread reads consecutive locations in memory as it accumulates across a matrix row.

Optimal GPU memory layout requires slightly different logic, due in part to the warp-level threading considerations described above. If a warp is fully executing in lockstep, each of the 32 threads will reach a load instruction at the same time. In general, device memory is only capable of accommodating one request at a time. As such, this request would generally be serialized, and each thread would be served in turn. However, there are some specific access patterns for which these accesses "coalesce" and are condensed into fewer instructions that are served more quickly. The first is a "broadcast" type of read in which threads all read from the same memory location. The second is a read in which consecutive threads read from consecutive locations in memory. If the memory accesses match these patterns (with some paging and alignment concerns, per [11]), these reads will be served at the same time. As such, device memory is generally structured such that consecutive threads access consecutive locations in memory. An example of this is a matrix-vector multiplication in which the matrix is laid out in **column-major** order. In such an operation, each thread is responsible for one row, and consecutive threads read consecutive locations in memory from one column at a time.

One more higher-level programming consideration for developing GPU programs derives from the way in which GPUs interact with the system. GPUs are devices that are attached to a host node, typically over the PCI bus. As a result, transferring data between the host and the device is a relatively slow process, especially compared to either the host or device reading from its own memory. As such, it is imperative to transfer as much data as possible to the device before beginning computation, or to hide the transfer time by overlapping transfer and computation via a pipelining scheme.

### 2.2.2 GPGPU Programming Interfaces

GPU functions are called from a program running on the CPU. To interface with the GPU from such a program, it is required to use one of many APIs, libraries, or interfaces available for most programming languages. These interfaces range in origin from GPU manufacturers to open standards. They also range in granularity of control, with some comprising OpenMP-style compiler pragmas, with others providing explicit control over device memory allocation and movement. A brief overview of a set of the most common GPU interfaces is provided in this section.

### 2.2.2.1 CUDA

One of the most ubiquitous GPU computing libraries is CUDA, a first-party interface from NVIDIA [11]. CUDA allows the developer to write custom "kernels" that run on the device and provides a C++ API to interact with the devices, allocate and transfer memory, and launch kernels. CUDA programs are compiled using *nvcc*, a custom compiler driver that generates appropriate device code. CUDA defines a programming model that allows for concurrent execution of multiple threads and kernels.

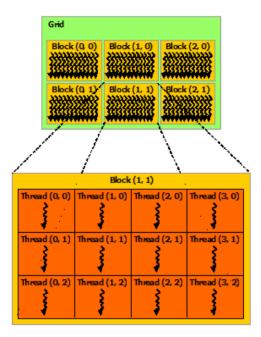

The execution hierarchy in CUDA can be seen in Figure 4. The most atomistic unit of the CUDA programming model is the **thread**. When a kernel launches, each assigned thread runs a copy of the same kernel. Threads are first bundled into a **block**. Currently, blocks can consist of up to 1024 threads. The threads in a block are guaranteed to be assigned to the same compute core and thus can share certain types of on-processor memory/cache. Kernels are launched in a **grid** of such blocks. These blocks are not guaranteed to execute in any particular order or with any guarantee of concurrency or synchronicity. As such, each block needs to represent work that can be processed entirely independently of other blocks in the grid.

Figure 4: CUDA Execution Hierarchy (Figure from [7])

In the CUDA model, the host and the device maintain separate memory spaces. Memory must be explicitly allocated on the device, and data transfer between the host and the device must be explicitly requested. This generally increases the complexity of CUDA code, as data structures must generally be created on the host, have space allocated for them on the device, then instantiated manually with a memory copy call from host memory to device memory. To manage this complexity, newer CUDA devices also have a "unified" memory space, in which data can be allocated and accessed from both the host and the device at the same address [12]. In the case in which the memory has not been transferred to the device, the page will be fetched from the host memory automatically. However, to maximize performance, unified memory still needs to be pre-fetched or copied directly, which adds some (perhaps lesser) degree of complexity.

The CUDA suite also provides several higher-level libraries and programs to aid in the development of CUDA programs. These include profilers to analyze the performance of CUDA kernels and programs, a linear algebra library (cuBLAS), and others.

## 2.2.2.2 OpenACC

The OpenACC standard is a higher-level approach to enabling GPGPU computation [13]. It takes the form of a set of compiler directives to directly expose parallelism in the code and allow the compiler to build parallel versions for a variety of different device backends. The primary goal of OpenACC is to prioritize portability across different compilers and device architectures. A limitation of this approach is that it often results in code that is marginally less efficient than a full hand-tuned implementation, but portability is vastly improved as opposed to e.g., a CUDA implementation, as the same code could be compiled and run with a different compiler/architecture stack.

Programs that leverage OpenACC are marked up with pragmas that direct the compiler to data and operations that can be parallelized. The semantics of data allocation, transfer, specific calculation parameters, and results transfer are (unless necessary) the

responsibility of the compiler, rather than the developer. In this way, the details and best practices associated with different device architectures need not be handled by the developer, and the compiler can generate correct code with good performance.

#### 2.2.2.3 Kokkos

Kokkos is a C++ library developed at Sandia National Laboratory [14]. It provides a programming model (and layer of abstraction) above vendor-specific GPU backends that aims to provide portability to different architectures while maintaining a degree of finegrained control over device memory and operations. The goal of this approach is to allow developers to write one set of source code that can be effectively deployed across parallel architectures, including multi-core and CPU-GPU architectures.

Kokkos accomplishes this portability by allowing the developer to write algorithms that use templated Kokkos-specific data types and parallel execution patterns (including parallel\_for, reduce, etc.). Beneath this layer of abstraction is one of several different "Execution Spaces" and "Memory Spaces" available to the developer. These spaces serve to translate the intermediate Kokkos representation to the specific representation that makes the most sense for the desired architecture. In this way, optimizations such as the row- vs. column- major matrix example described above are abstracted away from the user. Along with the library, the Kokkos ecosystem also includes extra features including BLAS functionality, profiling tools, and debugging tools.

#### 2.2.2.4 OpenMP Accelerator Support

The OpenMP standard is a standard that is most often used to enable sharedmemory multi-threading on a CPU via a set of compiler directives. Beginning with the OpenMP 4.0 standard in 2013, the standard also provides a set of pragmas that enable the offloading of computation to an attached device [15]. As another pragma-based interface, the pros and cons of working with OpenMP accelerator support are similar to those of OpenACC. The primary benefit of such an interface is an increase in portability, as the compiler can translate these instructions for any arbitrary target architecture. The cost of this portability is not being able to control the more fine-grained aspects of memory movement and execution.

#### 2.2.2.5 <u>HIP</u>

The Heterogeneous-compute Interface for Portability (HIP) is an API that aims to provide developers a level of control over execution that is akin to CUDA but does not limit the user to NVIDIA GPUs [16]. The HIP API includes many functions that represent a direct counterpart to a CUDA function (for example, hipMalloc/hipMemcpy vs. cudaMalloc/cudaMemcpy). The similarities are so strong that the HIP ecosystem offers a set of tools called hipify which are able to scan CUDA source code and either offer a direct HIP translation or identify the calls which are not translatable.

#### 2.2.3 GPGPU As Applied to Neutron Transport

GPGPU computing techniques have been applied to a wide range of scientific computing workloads, and neutron transport is no exception. There have been examples of

deterministic and stochastic methods that have been applied to GPU architectures with varying degrees of success. This section provides a brief overview of a few of the most prominent examples, including case studies of both stochastic and deterministic methods.

#### 2.2.3.1 <u>WARP</u>

The WARP (which can stand for "Weaving All the Random Particles") code is a neutron transport solver developed from the ground up for computation on GPU architectures [17]. The algorithm used for WARP is based off research performed in 1984 by Brown and Martin [18] which established a unique "event-based" Monte Carlo algorithm for SIMD vector computers.

In a traditional Monte Carlo transport algorithm (referred to for comparison as "history-based" algorithm), threads proceed by calculating the entirety of a particle's lifetime, then proceeding to a new particle. This type of algorithm is not well-suited for computation on a SIMD vector processor (or, in modern cases, GPUs) because, by the very definition of the Monte Carlo method, different particle lifetimes will play out differently. As such, consecutive particle histories can (and indeed are expected to) vary in terms of number of collisions, number of surfaces met, etc. As such, a new "event-based" algorithm was proposed in which particles are grouped into vectors based on the operation which is required by the current point in their history. For example, all particles currently undergoing a surface crossing operation are placed in a surface crossing buffer, and so on for other operations including scattering, etc. This exposes a much more SIMD calculation pattern, as most events of the same type require similar operations, even if being performed on different histories.

WARP was programmed in CUDA C++ and leveraged the NVIDIA first-party OptiX library to handle geometric specification and ray-tracing operations. Since the code was designed from the ground up for GPU computation, the work does not provide a direct performance comparison to an equivalent CPU execution, since no such direct comparison exists. A looser comparison can be found in a companion paper [19], wherein WARP was benchmarked against the mature CPU-only Monte Carlo transport codes Serpent and MCNP. In this study, it was found that one GPU using the warp code achieved performance equivalent to 0.84x-7.61x the performance of a modern CPU node.

#### 2.2.3.2 Shift

Shift is a massively parallel Monte Carlo radiation transport package from Oak Ridge National Laboratory [20]. A 2019 study using both a history-based and an event-based approach to extend the code to include operation on GPUs [21]. The GPU calculation logic for this study was written in CUDA C++. The study found that the event-based algorithm in which kernels only process one type of event at a time (either transport or collision) vastly outperforms the history-based algorithm in which threads process an entire particle history. The study found that this was due to increased occupancy (as described in Section 2.2.1 above) resulting from decreased divergent execution, which is likely to occur in a history-based approach as, e.g., some particles die off before others.

The results produced by the study were very promising. For the event-based approach (with an additional fuel-partitioning optimization), it was determined that an NVIDIA V100 GPU provided the performance of about 150 individual CPU cores for the examined benchmark problems.

#### 2.2.3.3 <u>OpenMOC</u>

OpenMOC is an open-source method of characteristics neutral particle transport code developed at the Massachusetts Institute of Technology [22]. The code uses the method of characteristics to solve 2D problems, with solvers for multi-core CPUs as well as GPUs. The GPU solver is written in CUDA C++. The initial documentation surrounding the release of the code indicated an acceleration of 50x with respect to a single-threaded CPU solver when using a Tesla C2070 GPU.

### 2.2.3.4 <u>nTRACER</u>

The nTRACER code package is a direct whole-core neutron transport solver developed by Seoul National University [23]. nTRACER employs a hybrid method in which 2D problems are solved to high detail using the method of characteristics, and the solutions of these 2D solves are fed into a 3D coarse mesh finite difference (CMFD) solver. In a study which examined expanding the nTRACER neutronic solver to GPU architectures, it was determined that the GPU-accelerated version of the code would see a speedup of between 8.3x to 11x relative to a CPU-only version [24].

#### 2.3 Interpretation

In this section, a description of the COMET method was provided, and results from a previous CPU-only COMET parallelization study were presented. A set of basic considerations for GPU programming were presented, along with an overview of a selection of interfaces and libraries available to write GPU programs. Finally, overviews for a set of GPU acceleration studies for other neutron transport codes (both stochastic and deterministic) were presented.

It is clear from this review that there is a strong case to be made for GPU acceleration of the COMET method. The matrix multiplies required to perform one inner iteration can be performed entirely independently, placing the method in a class of problems which can be called "embarrassingly parallel". This parallelism was exploited in the COMET-MPI project in a distributed-memory manner, and shared-memory parallelism was suggested for further study.

Furthermore, the specific considerations necessary for efficient GPU programming can be handled by the method. The response function libraries can fit entirely in device memory, which restricts communication of large amounts of data over the PCI bus to primarily the beginning of each outer iteration. The bulk of the runtime for COMET is associated with the small dense matrix multiplies (eq. 2.1.7), operations which can be speedily performed with the floating-point compute units on a GPU. The matrices can be laid out in column-major order on the device, ensuring that memory accesses will coalesce to a high degree, and thus memory performance (which usually bottlenecks matrix multiplies as low arithmetic intensity operations) can be made high.

# CHAPTER 3. COMET-CPP DEVELOPMENT AND METHODOLOGY

In this section, the development of a GPU-accelerated version of the COMET deterministic solver (including multi-GPU support) will be described. Although it would be technically possible to modify the existing COMET Fortran codebase to add GPU support, attempting to do so was not likely to result in an efficient implementation due to the order in which calculations are currently performed. Due to this ordering, memory layout concerns, and the lack of relative maturity for GPU interfaces in Fortran, the decision was made to develop an all-new implementation of the transport sweep portion of the COMET method in C++. The benefit of the ability to re-order calculations, restructure the way in which memory is laid out, and add a degree of modularity/separation between the philosophical representation of the problem and the raw matrices and vectors involved in calculation was determined to outweigh the cost of developing this all-new implementation. For the remainder of this document, the new implementation will be called "COMET-cpp" or the "new implementation", and the original Fortran solver will be called the "serial solver" or the "old implementation".

It was decided that the GPU calculation capability for the new solver would be implemented in CUDA. There are several reasons for which CUDA was selected as the interface for use in this study:

• As described in Section 2.2.3, CUDA has already been used to accelerate several different neutron transport methods.

- The machines on which the development of COMET-cpp was to take place all contained NVIDIA GPUs, which prevented the need for a more portable interface. The solver was developed to allow for clean connection points between the calculation front-end and back-end such that, if more portability is desired, a new calculation back-end could be written in a more portable interface. One possibility is porting the CUDA directly using the hipify toolchain discussed in Section 2.2.2.5.

- The CUDA ecosystem itself includes the possibility for many different implementations for the GPU operations, including the use of the first-party linear algebra library cuBLAS and the use of CUDA unified memory. These were both investigated before the final full implementation was written.

- As described in Section 2.2.2.1, the CUDA interface allows for very finegrained control of memory allocation, movement, and GPU operation. Since the solver was already being rewritten to pay careful attention to memory layout, the opportunity to write this logic from the ground up was already present.

The first section of this chapter describes the new implementation of the CPU-only solver, including design elements to allow for switching on the calculation back-end. A CPU-only BLAS back-end is also described. The second section of the chapter describes the design of the GPU-accelerated algorithm, including details about memory movement and calculation kernel structure. This section also includes details about early attempts to leverage CUDA unified memory and the cuBLAS library, before settling on the final implementation that uses explicit memory management and custom calculation kernels. The third section of this chapter describes a set of newly developed post-processing and visualization tools to interpret the text-based output from the new solver and plot the results.

#### 3.1 Host COMET-cpp Solver Development

As described in the introduction, it was decided that a new host solver should be created as the development target for GPU calculation capabilities. To maintain a reasonable scope for the project while maximizing the utility of the solver (and allowing for the possibility for continued development), a set of goals for the solver were set forth, with some items explicitly excluded from scope:

- The solver should have total backward compatibility with the current libraries and input files read by the serial solver. This clearly facilitates the continued development and use of the solver, but it also aids in restricting scope, as testing can be performed with the library of benchmark problems that have already been solved with COMET.

- The solver should have the capability to perform regular forward transport calculations, with or without Chebyshev polynomial acceleration. The other functions of the deterministic solver (e.g. adjoint calculations, uncertainty calculations) rely on similar calculations, so regular forward calculation with Chebyshev acceleration is sufficient to demonstrate the techniques that would be involved in implementation of the other features.

- Because COMET post-processing tools are currently written on a per-problem basis, backwards compatibility with the output file format was decided not to

be a goal of the new solver. Instead, a new format for output files was created, and a unified post-processing suite of tools was developed (per Section 3.3).

• The new solver should have a modern build system generator and should be configurable at compile-time and run-time to include support for CPU-only (with configurable BLAS backend) or GPU-accelerated calculation on supported systems.

The result of this refactor of the serial code was a new implementation of the deterministic sweep calculation which was more suitable for parallel computation, both CPU-only as described in Section 3.1.2 and GPU-accelerated as in Section 3.2.

# 3.1.1 Solver Front-end

The purpose of the COMET-cpp solver front end is to construct an interpretation of the reactor core represented by the text-based COMET input file for the run and interface with the CDF database files that contain the underlying  $r_{isrs}$  matrices used in calculation. The front-end first constructs a series of objects that contain information about the problem meshes (in-core location, material composition, etc.). From there, a set of information is assembled into packages that get passed to the back-end:

- A mapping is made for each individual mesh *i*, surface *s*, and moment *m* entry into one global eigenvector *J*.

- A list of small dense matrix operations is constructed (eq. 2.1.7) that, in total, describe the surface-to-surface current transfer for the global problem. These operation objects containing the following information:

- Offset into the global eigenvector of the "from" surface, giving the location of the first element of  $j_{isi}$ ,

- Offset into the global eigenvector of the "to" surface, giving the location of the first element of  $j_{is}^+$ ,

- An object that describes the surface-to-surface response function matrix  $r_{isrs}$  to use in the multiplication.

- A list of boundary condition operations is constructed to enforce periodic or reflective boundary conditions for the global problem, if necessary.

- A list of total absorption operations is constructed that, in total, comprise the total absorption for the problem (corresponding to the *rab* term in eq. 2.1.11).

These operation objects contain the following information:

- Offset into the global eigenvector of the "from" surface, giving the location of the first element of  $j_{is}$ ,

- An object that describes the total absorption response vector  $rab_{is}$ .

- A list of total fission operations is constructed that, in total, encompass the total fission for the problem (corresponding to the rnf term in eq. 2.1.11). These operation objects contain much the same information as the absorption operations above, except the objects describe the total fission response vector  $rnf_{is}$  instead of the absorption vector.

- A list of the ordinate combinations *i* and *s* for which the surface lies on the boundary of the global problem (that is, ∂V<sub>is</sub> ∈ ∂V). This is necessary to construct the leakage term in eq. 2.1.11.

The information passed to the back-end is designed to completely describe the problem and the calculations necessary for the inner and outer iteration process while avoiding information that may vary between different calculation back ends. A graphical depiction of the exchange of information between the front-end and any particular back-end can be seen in Figure 5 below. In this figure, the logic contained in the blue front-end box is constant regardless of the particular back-end used, and the logic contained in the green back-end box can vary depending on the target architecture, library, etc.

Figure 5: Separation and Exchange Between Front- and Back-ends

The COMET-cpp front-end has two external dependencies. The gflags library [25] is used for command-line argument parsing. The CDF C library [7] is used to interface

with the CDF response function database files. Rather than use an external library to parse the text-based input files used by COMET, a new custom parser was developed.

#### 3.1.2 CPU-only Generic BLAS Back-end

A CPU-only back-end for COMET-cpp was also developed in this work. This backend was developed for several reasons:

- If COMET-cpp were to continue as the main development branch of the project, a CPU-only solver would be required to enable calculation on systems for which GPUs are not present.

- By expressing the problem in the symbolic objects described in Section 3.1.1 above, an opportunity for shared-memory parallelism is immediately available. It is thus of interest to gauge the performance of a shared-memory parallel implementation of the method (as recommended by the COMET-MPI study described in Section 2.1.3 above).

- Having a CPU-only solver that matches the program flow of the GPU solver is a useful tool for debugging and correctness checks.

Although it is not the main subject of this study, the details of the CPU-only sharedmemory parallel back-end are useful for understanding the techniques that will be used in the GPU back-end logic. As such, to provide a basis for full illustration of the similarities and differences between the two, the CPU-only solver is documented fully in this section.

The first notable distinguishing feature of a particular back-end is the object that it uses to represent a particular  $r_{is/s}$  matrix in memory. For the CPU-only backend, this object

is relatively straight-forward. It uses a C++ standard library vector of single-precision (usually, although a double-precision version is explored in Chapter 5) floating-point values. The matrix is stored in row-major order for the cache-optimization rationale described in Section 2.2.1 above. The pointer to this matrix which is ultimately fed into the Basic Linear Algebra Subprograms (BLAS) function calls is obtained by calling the data() function on this vector.

As described in Sections 2.1.2 and 2.1.3, a key feature of the COMET method which makes it an excellent candidate for parallel implementations is that the individual small matrix multiplications that comprise an inner iteration can be performed in any arbitrary order, called the "sweep order". In the current serial COMET implementation, this sweep order groups together all operations that use the same underlying response function matrix (that is, operations on meshes that have the same material composition, from the same surface number to the same surface number) [1], [6]. This is done to optimize performance by maximizing re-use of matrices between contiguous operations, thereby maximizing cache use.

In Section 3.1.1 and Figure 5 above, it is described how the individual operations are communicated from the front-end to the back-end in a 1-dimensional list of operation objects. In this context, any particular sweep order can be thought of as one permutation of this master list of operations. To recreate the sweep order explicitly enforced by the nature of the order of the serial solver operations, the COMET-cpp CPU-only backend begins setup by sorting the master list of operations according to the following variables in order of importance:

- Material number

- "From" surface number

- "To" surface number

- "From" offset into global eigenvector

- "To" offset into global eigenvector

This sorting operation results in a list ordering that maximizes cache use in the same manner as the serial solver, grouping together operations that use the same underlying matrix.

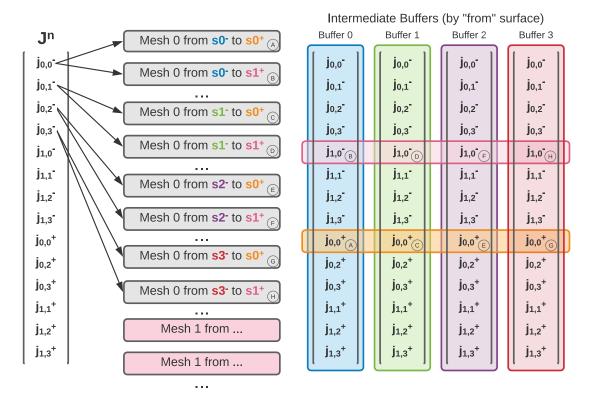

It is noted from eq. 2.1.7 that each outgoing partial current expansion coefficient for surface *s* of mesh *i* is a summation over the results of several matrix multiplies over the incoming surfaces *s'* for the mesh. This means that any individual  $j_{is}^+$  for the problem is obtained by summing the results of *S* matrix multiplies, where *S* is the number of surfaces per coarse mesh for the specific problem geometry (4 for 2-D Cartesian, 6 for 3-D Cartesian, 8 for 3-D hexagonal). On the surface, this poses a problem for the independence of the operations, as the current due to one surface must be added to the current due to the other incoming surfaces. COMET-cpp gets around this problem by setting up a set of *S* unique "intermediate results" buffers to which the results of the multiplies can be written independently. Once all the multiplies have been performed, these buffers can be summed and written to a final combined results buffer.

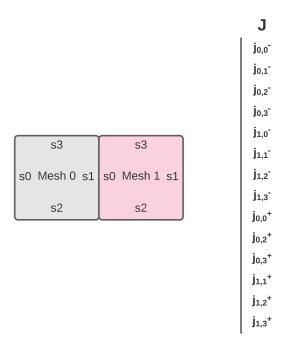

A graphical depiction of this process for a 2-dimensional Cartesian problem with 2 meshes can be seen below. A depiction of the problem geometry and the resulting global partial currents vector J can be seen in Figure 6. It is noted that, due to the continuity

condition, there is no explicit entry in the vector for the entries  $j_{0,1}^+$  and  $j_{1,0}^+$ . The partial currents moments that correspond to these surfaces are already represented by  $j_{1,0}^-$  and  $j_{0,1}^-$  respectively, and as such there is no need for them. In general, *outgoing* partial current moments are only explicitly given their own entry in the global vector if they lie on the global boundary of the problem, and as such are not represented by any incoming partial current moments.

#### Figure 6: Example Problem Geometry and Vector

The individual small dense matrix multiplies for the problem can be seen in Figure 7. The full set of small matrix multiplies for the problem is of size 32 (4 incoming surfaces per mesh \* 4 outgoing surfaces per mesh \* 2 meshes), 10 of which are depicted in the figure. It is observed that, by having the results of each multiplication written to a different intermediate buffer based on the inward-facing surface number, no two operations write to the same location in memory. As such, there is no need for the operations to be performed

with any particular order, synchronicity, or grouping. Thus, the need for atomic operations is not present, and the ordering of these operations can be changed arbitrarily.

#### **Small Matrix Multiplies**

**Figure 7: Small Dense Matrix Multiplications for Inner Iteration**

To obtain the full results of these multiplications, the intermediate buffers must be reduced, as in Figure 8. In the CPU-only backend, the results of this reduction are stored in the primary buffer as the most up-to-date guess for the eigenvector.

As with the old serial solver, the Intel Math Kernel Library (MKL) [8] is leveraged to perform the matrix multiplies. However, to aid in the portability of the code to arbitrary systems, compile-time switches were also implemented to allow for building of the code with an open-source alternative, the OpenBLAS [26] library.

| Buffer 0                  |   | Buffer 1                  |   | Buffer 2                  |   | Buffer 3                  |   | <b>J</b> n+1              |

|---------------------------|---|---------------------------|---|---------------------------|---|---------------------------|---|---------------------------|

| jo,o                      | + | <b>j</b> o,o <sup>-</sup> | + | <b>j</b> o,o <sup>-</sup> | + | <b>j</b> o,o <sup>-</sup> | = | <b>j</b> o,o <sup>-</sup> |

| j0,1 <sup>-</sup>         |   | <b>j</b> 0,1 <sup>-</sup> |   | <b>j</b> 0,1 <sup>-</sup> |   | j0,1 <sup>-</sup>         |   | j0,1 <sup>-</sup>         |

| jo,2 <sup>-</sup>         |   | jo,2 <sup>-</sup>         |   | jo,2 <sup>-</sup>         |   | jo,2 <sup>-</sup>         |   | j0,2 <sup>-</sup>         |

| <b>j</b> o,3 <sup>-</sup> |   | <b>j</b> o,3 <sup>-</sup> |   | jo,3 <sup>-</sup>         |   | <b>j</b> o,3 <sup>-</sup> |   | <b>j</b> o,3 <sup>-</sup> |

| j1,0                      |   | <b>j</b> 1,0 <sup>-</sup> |   | j1,0 <sup>-</sup>         |   | <b>j</b> 1,0 <sup>-</sup> |   | j1,0 <sup>-</sup>         |

| j1,1                      |   | <b>j</b> 1,1 <sup>-</sup> |   | j1,1 <sup>-</sup>         |   | j1,1 <sup>-</sup>         |   | j <sub>1,1</sub> -        |

| j <sub>1,2</sub>          |   | j1,2 <sup>-</sup>         |   | j1,2 <sup>-</sup>         |   | j <sub>1,2</sub> -        |   | j <sub>1,2</sub> -        |

| j <sub>1,3</sub>          |   | j <sub>1,3</sub> -        |

| jo,o+                     |   | jo,o+                     |   | jo,o+                     |   | jo,o+                     |   | jo,o+                     |

| <b>j</b> 0,2 <sup>+</sup> |   | <b>j</b> 0,2 <sup>+</sup> |   | <b>j</b> 0,2 <sup>+</sup> |   | <b>j</b> 0,2 <sup>+</sup> |   | <b>j</b> 0,2 <sup>+</sup> |

| j0,3+                     |   | <b>ј</b> о,з+             |   | <b>ј</b> о,з+             |   | <b>ј</b> о,з+             |   | <b>j</b> 0,3 <sup>+</sup> |

| j1,1+                     |   | j1,1+                     |   | j1,1+                     |   | j1,1+                     |   | j1,1+                     |

| <b>j</b> 1,2 <sup>+</sup> |   | j <sub>1,2</sub> +        |   | j <sub>1,2</sub> +        |   | j <sub>1,2</sub> +        |   | j1,2+                     |

| j <sub>1,3</sub> +        |   | j <sub>1,3</sub> +        |   | <b>j</b> 1,3 <sup>+</sup> |   | <b>j</b> 1,3 <sup>+</sup> |   | <b>j</b> 1,3 <sup>+</sup> |

Intermediate Result Reduction

**Figure 8: Intermediate Results Reduction**

To exploit the parallelism exposed by the above-described untangling of front- and back-ends, a simple OpenMP loop over the (sorted) list of matrix multiplies is used, giving each thread a contiguous chunk of the global list. Because CPU parallelism was not the primary focus of this work, no further effort was made to optimize this strategy. Regardless, the examination of program execution seen in Chapter 4 clearly demonstrates the strength of the overall approach used by COMET-cpp to separate these operations.

#### **3.2 GPU Back-end Development**

The primary focus of this work is the development of a GPU-accelerated version of the solver. With the host front-end described in Section 3.1.1 and Figure 5, this problem is reduced to the development of a GPU-accelerated back-end.

The first notable feature of the GPU backend is the object used to store the  $r_{is's}$  matrices used in computation. The initial implementation of this object was one that stored

the matrix in CUDA unified virtual memory (UVM) [12]. This is a natural first test for a number of reasons, not least of which being that the same memory address can be directly written to on the host then pre-fetched on the device. The relative performance of this initial implementation was demonstrated in a brief test on a machine with a Ryzen 3800X and an NVIDIA GTX 1080 with 8GB of video memory. This test demonstrates the throughput of (an older build of) the algorithm on the VHTR benchmark problem [27], [28]. Note, this test was not performed with the most efficient version of the compute kernels (for compatibility reasons), and as such the absolute metrics should NOT be taken as indicative of overall performance. This test is only relevant as one measure of the relative performance of the UVM and explicit memory treatments achieved by COMET-cpp. The results of the test can be seen in Table 1. It is observed that the use of UVM to store the underlying matrices (with careful attention paid to prefetching) results in a modest performance penalty as compared to an explicit treatment. However, in the pursuit of maximum performance (as well as explicit control over the movement of memory between the host and one or more devices) an explicit treatment was subsequently developed.

| Memory Treatment    | Throughput (GB/s) | Relative performance |