## SCALABLE ENERGY-EFFICIENT MICROARCHITECTURES WITH COMPUTATIONAL ERROR TOLERANCE

A Dissertation Presented to The Academic Faculty

By

Bobin Deng

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Computer Science

Georgia Institute of Technology

May 2021

Copyright © Bobin Deng 2021

## SCALABLE ENERGY-EFFICIENT MICROARCHITECTURES WITH COMPUTATIONAL ERROR TOLERANCE

Approved by:

Dr. Thomas M. Conte, Advisor School of Computer Science *Georgia Institute of Technology*

Dr. Hyesoon Kim School of Computer Science *Georgia Institute of Technology*

Dr. Alexandros Daglis School of Computer Science Georgia Institute of Technology Dr. Arijit Raychowdhury School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Jeanine Cook Computer Science Research Institute Sandia National Laboratories

Date Approved: April 22, 2021

Enjoy a grander sight by climbing to a greater height

Zhihuan Wang

#### ACKNOWLEDGEMENTS

Thanks to my family for giving me unlimited tolerance and encouragement in the past few years. Their support gave me continuous motivation to complete my Ph.D. degree.

Thanks to my thesis advisor, Dr. Thomas M. Conte. He has given me great support in all aspects, including research work, writing, presentation, and teaching skills, so that I can successfully complete my degree.

Thanks to Dr. Erik Debenedictis and Dr. Jeanine Cook for giving me many support and suggestions on research projects, which helped me quickly enter a new research domain and gave very constructive feedback on my research.

Thanks to all the members of TINKER and CRNCH, through continuous learning and discussion with each other, my research capability and knowledge have been significantly improved.

Thanks to thesis committee members, Dr. Thomas M. Conte, Dr. Hyesoon Kim, Dr. Alexandros Daglis, Dr. Arijit Raychowdhury and Dr. Jeanine Cook, for their time to give very valuable feedback on my thesis and research.

# TABLE OF CONTENTS

| Acknow    | vledgments                                                      |

|-----------|-----------------------------------------------------------------|

| List of 7 | <b>Fables</b>                                                   |

| List of l | Figures                                                         |

| Summa     | <b>ry</b>                                                       |

| Chapte    | r 1: Introduction and Background                                |

| 1.1       | Computational Error Tolerance                                   |

|           | 1.1.1 Dual/Triple Modular Redundancy                            |

|           | 1.1.2 Residue Checking                                          |

|           | 1.1.3 Residue Number Systems (RNS)                              |

|           | 1.1.4 Redundant Residue Number Systems (RRNS)                   |

| 1.2       | Contributions                                                   |

| 1.3       | Thesis Statement                                                |

| 1.4       | Thesis Outline                                                  |

| Chapte    | r 2: Scalable RRNS Microarchitectures for Millivolt Switches 11 |

| 2.1       | (4,2)-RRNS Error Detection/Correction Algorithm                 |

| 2.2       | Error-tolerant Capability of (4,2)-RRNS                         |

| 2    | 3   | (n,r)-RRNS Error-Tolerant Extension                                         | 15 |

|------|-----|-----------------------------------------------------------------------------|----|

| 2.4  | 4   | Signed Number Representation                                                | 16 |

| 2.:  | 5   | Correction Factors                                                          | 18 |

| 2.   | 6   | Overflow Detection                                                          | 21 |

|      |     | 2.6.1 Unsigned Number Overflow Detection                                    | 21 |

|      |     | 2.6.2 Signed Number Overflow Detection                                      | 22 |

| 2.   | 7   | Comparison                                                                  | 24 |

| 2.3  | 8   | Optimized Multiplier Unit Design                                            | 25 |

| 2.   | 9   | Base Selection for Scalable Systems                                         | 27 |

| 2.   | 10  | RRNS Fixed Point Arithmetic                                                 | 29 |

|      |     | 2.10.1 2-RRNS Concat Representation                                         | 29 |

|      |     | 2.10.2 RRNS Logical Partition Representation                                | 31 |

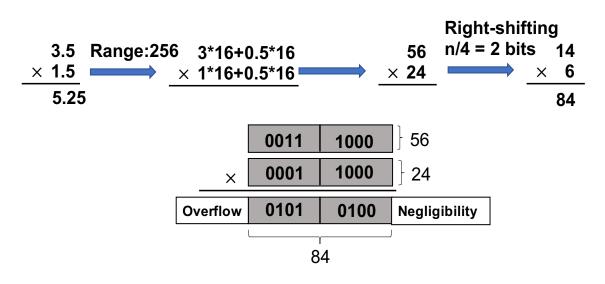

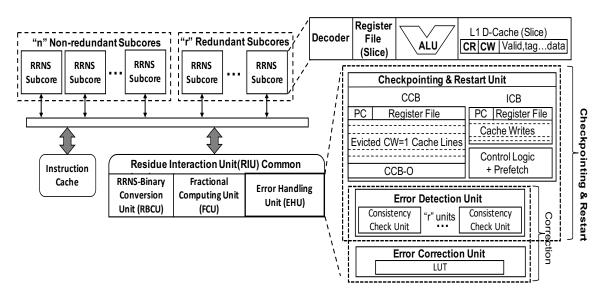

| 2.   |     | A Scalable (n,r)-RRNS Microarchitecture Supporting Detection and Correction | 33 |

| 2.   | 12  | Related Work                                                                | 35 |

|      |     | 2.12.1 RNS and RRNS                                                         | 35 |

|      |     | 2.12.2 Other Error-tolerant Techniques                                      | 36 |

|      |     | 2.12.3 State-of-the-art Checkpointing Schemes                               | 37 |

| Chap | ter | 3: (n,r)-RRNS Detection&Restart-only Systems for Millivolt Switches .       | 39 |

| 3.   | 1   | RRNS Checkpointing&Restart Overview                                         | 39 |

| 3.2  | 2   | RRNS Checkpointing Operations                                               | 41 |

| 3.   | 3   | RRNS Checkpointing Hardware Overheads                                       | 43 |

| 3.4  | 4   | Adaptive Checkpointing Schemes                                              | 43 |

|       | 3.4.1                     | Stochastic Overhead Estimation (SOE)                                   | 44 |

|-------|---------------------------|------------------------------------------------------------------------|----|

|       | 3.4.2                     | Error Interval Heuristics (EIH)                                        | 49 |

| 3.5   | 5 Evalua                  | tion Methodology                                                       | 50 |

| 3.6   | 6 Experi                  | mental Results                                                         | 51 |

|       | 3.6.1                     | Exploration of The Minimum Signal Energy                               | 51 |

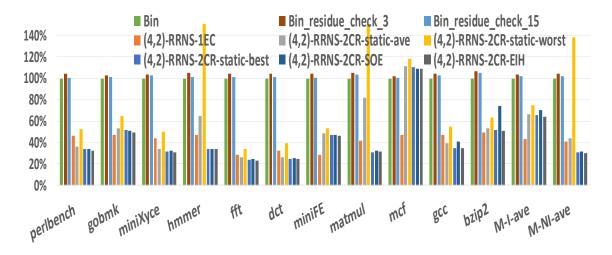

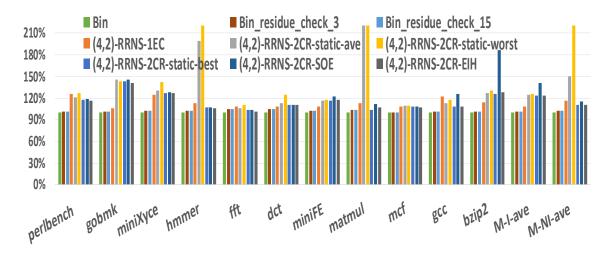

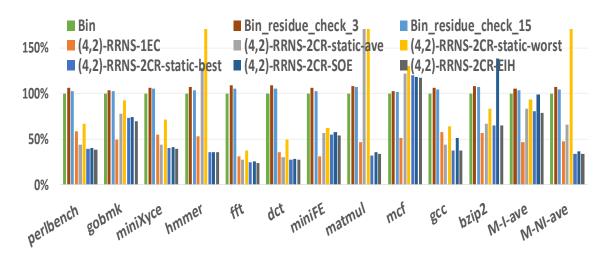

|       | 3.6.2                     | The Potential of Checkpointing&Restart Systems                         | 52 |

|       | 3.6.3                     | The Best Checkpointing & Restart Scheme                                | 55 |

| 3.7   | Conclu                    | ision                                                                  | 57 |

| Chapt | t <b>er 4: (</b> n,1      | <i>r</i> )- <b>RRNS</b> Correction-only Systems for Millivolt Switches | 58 |

| 4.1   | Size of                   | Ferror Correction Lookup Table                                         | 59 |

| 4.2   | 2 Energy                  | Delay Production (EDP) Comparison                                      | 59 |

| Chapt | t <b>er 5: (</b> n,1      | r)-RRNS Hybrid Systems for Millivolt Switches                          | 61 |

| 5.1   | ( <i>n</i> , <i>r</i> )-H | RRNS Hybrid System Design                                              | 61 |

| 5.2   | 2 Desigr                  | Space Exploration of ( <i>n</i> , <i>r</i> )-RRNS                      | 61 |

| Chapt | ter 6: Th                 | read-level Fault-tolerance for Exascale Computing                      | 65 |

| 6.1   | Motiva                    | ation and background                                                   | 65 |

| 6.2   | 2 Async                   | hronous Many-Task (AMT) Programming model                              | 67 |

| 6.3   | 3 Thread                  | I-level RRNS Resiliency                                                | 71 |

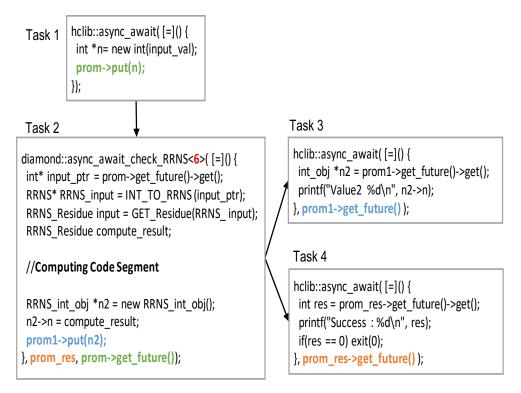

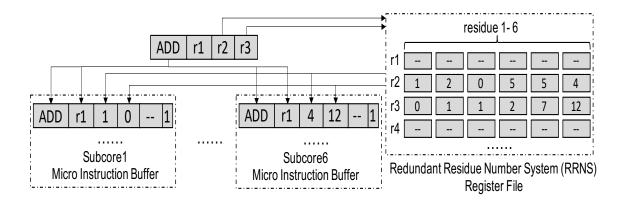

|       | 6.3.1                     | RRNS-AMT Overview                                                      | 71 |

|       | 6.3.2                     | Thread-level RRNS Limitations and Solutions                            | 73 |

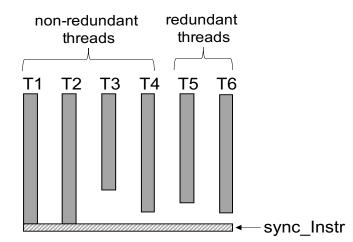

|       | 6.3.3                     | RRNS-AMT Microarchitecture                                             | 75 |

| 6.4     | Evalua  | tion Methodology And Experimental Results                    |

|---------|---------|--------------------------------------------------------------|

|         | 6.4.1   | Benefits of Branch Predictor Combination                     |

|         | 6.4.2   | Error-free Scenarios                                         |

|         | 6.4.3   | Error-prone Scenarios                                        |

| 6.5     | Relate  | d Work                                                       |

| Chapte  | r 7: Co | nclusion and Future Work 89                                  |

| 7.1     | Conclu  | usion                                                        |

| 7.2     | Future  | Work                                                         |

|         | 7.2.1   | Energy and Speedup Tradeoff of Different Pipeline Designs 91 |

|         | 7.2.2   | Error Model Improvement                                      |

|         | 7.2.3   | RRNS Deep Neural Network                                     |

| Referen | ices .  |                                                              |

# LIST OF TABLES

| 1.1 | A $(4, 2)$ -RRNS example with a toy base set $(3, 5, 2, 7, 11, 13)$ . 11 and 13 are the redundant bases.                                                                                                                                               | 6  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Error Correction table of RRNS System with Moduli (3,5,2,7,11,13)                                                                                                                                                                                      | 12 |

| 2.2 | Unsigned Number Overflow Examples in RRNS with Moduli (3,5,2,7,11,13)                                                                                                                                                                                  | 22 |

| 2.3 | Excess- $\frac{M}{2}$ Overflow Examples for addition of two positive numbers in RRNS with Moduli (3,5,2,7,11,13)                                                                                                                                       | 22 |

| 2.4 | Excess- $\frac{M}{2}$ Overflow Examples for addition of two negative numbers in RRNS with Moduli (3,5,2,7,11,13)                                                                                                                                       | 23 |

| 2.5 | Mapping table of $GF(59)$ with a primitive root of 11 ( $g = 11$ )                                                                                                                                                                                     | 26 |

| 2.6 | Mapping table of $GF(2^6)$                                                                                                                                                                                                                             | 27 |

| 2.7 | Conditions for choosing RRNS moduli: Multiple error detection (+), single error correction (*), fractional multiplication optimization(#), index-sum multiplication optimization (O), number of redundant moduli (r), number of detectable errors (e). | 28 |

| 2.8 | Possible (4,2)-RRNS-DED Base Sets                                                                                                                                                                                                                      | 29 |

| 3.1 | Equation Terminologies                                                                                                                                                                                                                                 | 45 |

| 6.1 | Percentages of RRNS unfriendly instructions                                                                                                                                                                                                            | 73 |

# LIST OF FIGURES

| 1.1  | Triple Modular Redundancy in action.                                                                                          | 3  |

|------|-------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Residue Checking Flowchart                                                                                                    | 4  |

| 2.1  | (4,2)-RRNS is capable of 1EC or 2ED                                                                                           | 13 |

| 2.2  | Complement M*MR signed representation                                                                                         | 17 |

| 2.3  | Complement M signed representation                                                                                            | 17 |

| 2.4  | Excess -M/2 signed representation                                                                                             | 18 |

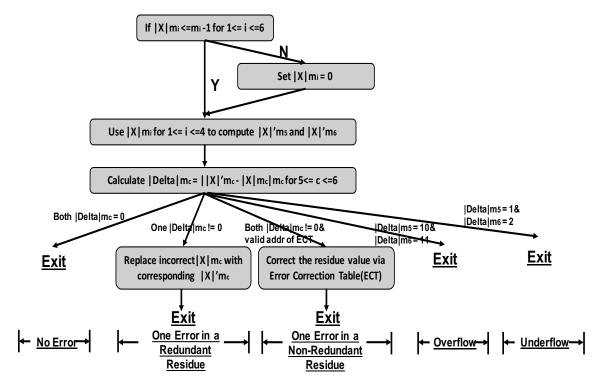

| 2.5  | One error detection and correction algorithm with overflow/underflow de-<br>tection                                           | 23 |

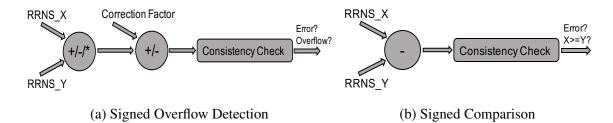

| 2.6  | Signed Overflow Detection and Comparison                                                                                      | 25 |

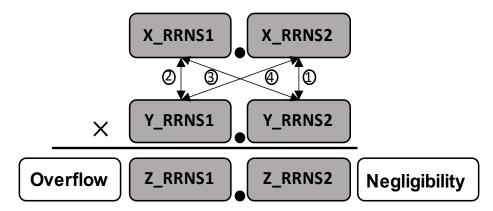

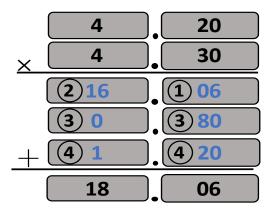

| 2.7  | 2-RRNS Concat Multiplication                                                                                                  | 30 |

| 2.8  | An Example of 2-RRNS Concat Multiplication                                                                                    | 30 |

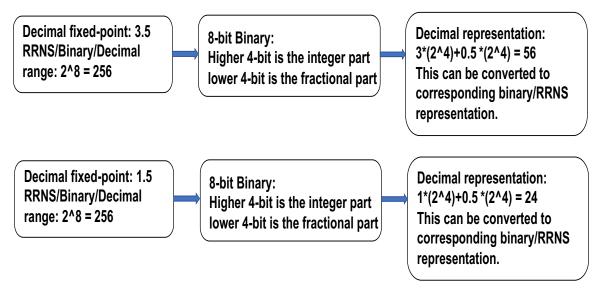

| 2.9  | Converting fixed-point representation to integer representation                                                               | 32 |

| 2.10 | Logical Partition Multiplication                                                                                              | 32 |

| 2.11 | Converting integer representation back to fixed-point representation                                                          | 32 |

| 2.12 | The overview of a scalable $(n,r)$ - <i>RRNS</i> microarchitecture capable of check-<br>pointing/restart and error correction | 33 |

| 2.13 | Error-tolerant techniques of components                                                                                       | 33 |

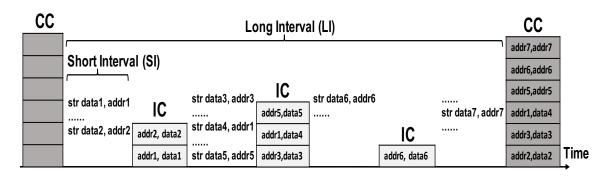

| 3.1  | RRNS Checkpoint Overview                                                                                                      | 40 |

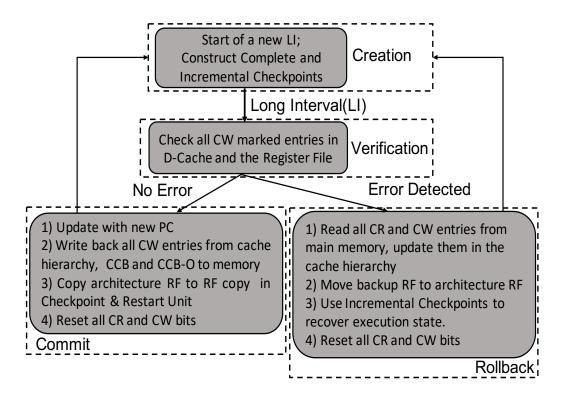

| 3.2  | RRNS Checkpointing&Restart Flowchart                                                                                                                                                       | 41 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

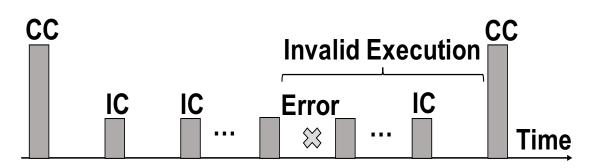

| 3.3  | Invalid Execution Segment                                                                                                                                                                  | 46 |

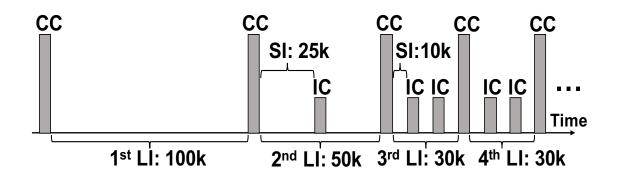

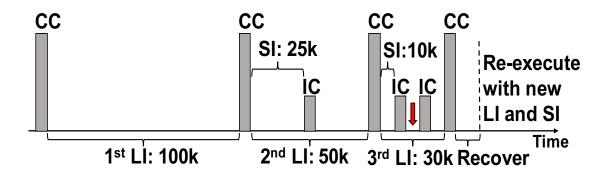

| 3.4  | Error Interval Heuristics (EIH) Mechanism Examples; Default parameters:<br>latest Error Interval(EI,200k cycles), minimal LI(30k cycles), minimal SI<br>(10K cycles); No error detected    | 49 |

| 3.5  | Error Interval Heuristics (EIH) Mechanism Examples; Default parameters:<br>latest Error Interval(EI,200k cycles), minimal LI(30k cycles), minimal SI<br>(10K cycles); An error is detected | 49 |

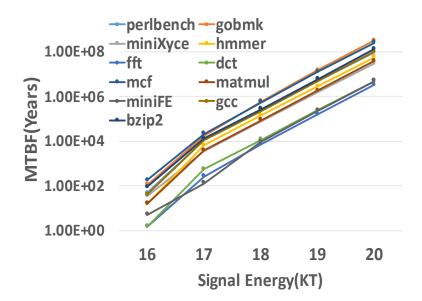

| 3.6  | Minimal MTBF of computational logic in (4,2)-RRNS-2ED                                                                                                                                      | 53 |

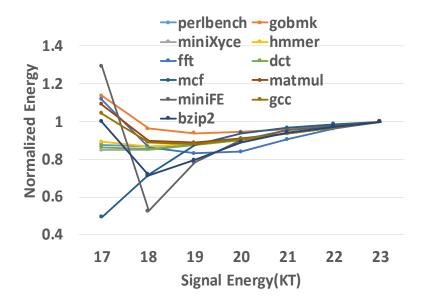

| 3.7  | Minimal Energy of computational logic in (4,2)-RRNS-2ED                                                                                                                                    | 53 |

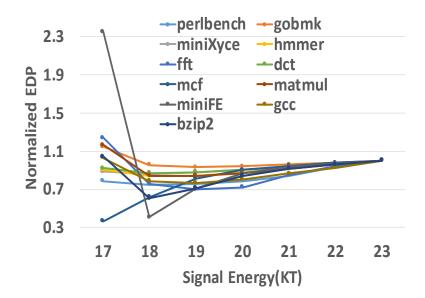

| 3.8  | Minimal EDP of computational logic in (4,2)-RRNS-2ED                                                                                                                                       | 54 |

| 3.9  | EDP of 1EC vs 1ED vs 2ED                                                                                                                                                                   | 54 |

| 3.10 | Comparison of Checkponting&Restart Energy                                                                                                                                                  | 55 |

| 3.11 | Comparison of Checkponting&Restart Runtime                                                                                                                                                 | 56 |

| 3.12 | Comparison of Checkponting&Restart EDP                                                                                                                                                     | 56 |

| 4.1  | Energy Delay Production (EDP) Comparison                                                                                                                                                   | 59 |

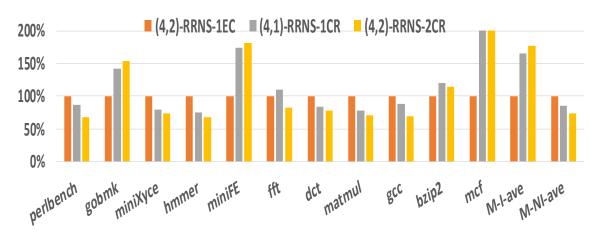

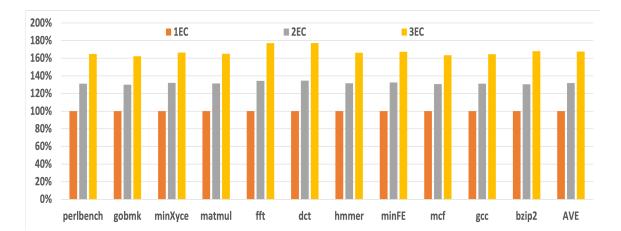

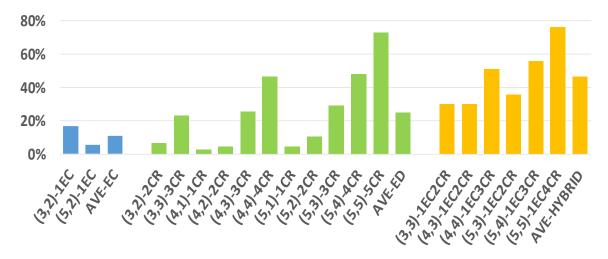

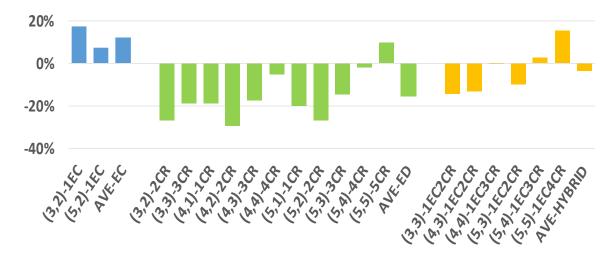

| 5.1  | Memory-intensive; The energy consumption of RRNS schemes normalized to (4,2)-RRNS-1EC                                                                                                      | 62 |

| 5.2  | Non-memory-intensive; The energy consumption of RRNS schemes nor-<br>malized to (4,2)-RRNS-1EC                                                                                             | 62 |

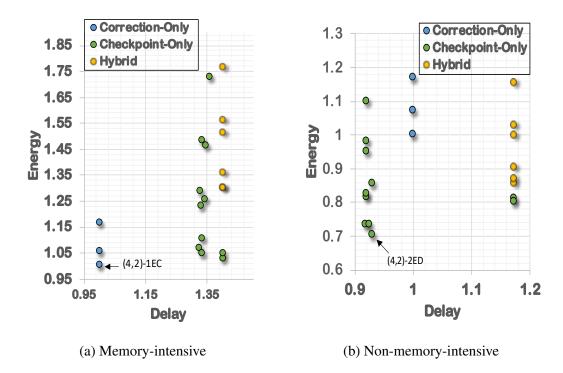

| 5.3  | Energy Delay Pareto normalized to (4,2)-RRNS-1EC                                                                                                                                           | 63 |

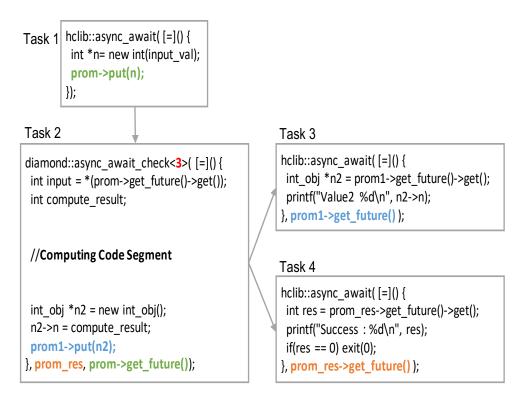

| 6.1  | TMR-AMT Example                                                                                                                                                                            | 69 |

| 6.2  | RRNS-AMT Example                                                                                                                                                                           | 70 |

| 6.3  | (4,2)-RRNS-AMT Overview                                                                                                                                                                    | 72 |

| 6.4  | The Resilient Microarchitecture Overview of Thread-level Redundant Residue Number System                                                                                                                                                                                                                  | 75 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.5  | An Example of Converting An ADD Instruction Into Multiple ADD Micro-<br>instructions In The Decode Stage                                                                                                                                                                                                  | 76 |

| 6.6  | Performance Improvement (Delay Reduction) of Branch Predictor Combi-<br>nation                                                                                                                                                                                                                            | 80 |

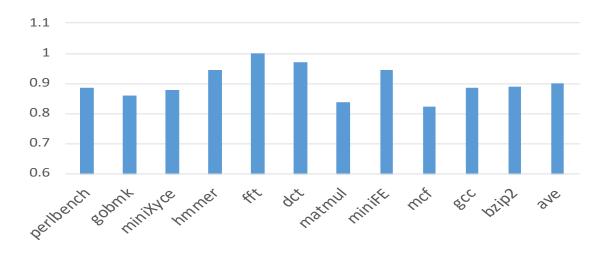

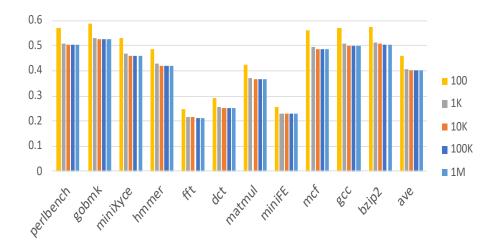

| 6.7  | Delay of Thread-level Redundant Residue Number System (RRNS); The values in this figure are normalized to Triple Modular Redundancy (TMR) .                                                                                                                                                               | 82 |

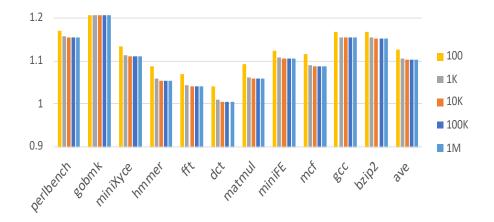

| 6.8  | Energy of Thread-level Redundant Residue Number System (RRNS); The values in this figure are normalized to Triple Modular Redundancy (TMR) .                                                                                                                                                              | 83 |

| 6.9  | Energy Delay Product (EDP) of Thread-level Redundant Residue Number<br>System (RRNS); The values in this figure are normalized to Triple Modular<br>Redundancy (TMR)                                                                                                                                      | 83 |

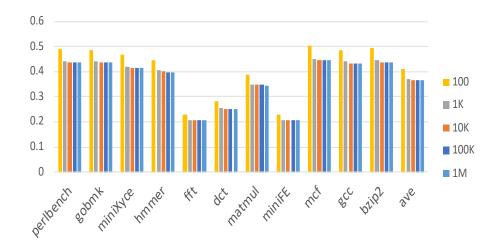

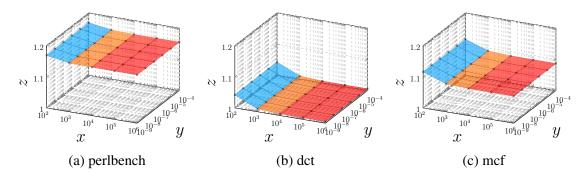

| 6.10 | Normalized delay results for different error detection frequencies and error rates; X-Axis: error detection frequencies range from $10^2$ to $10^6$ ; Y-Axis: instruction error rates range from $10^{-4}$ to $10^{-9}$ ; Z-Axis: Normalized thread-level RRNS delay (TMR results are normalized to 1)    | 84 |

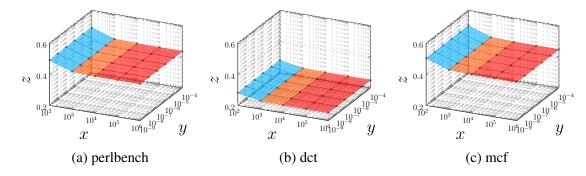

| 6.11 | Normalized energy results for different error detection frequencies and error rates; X-Axis: error detection frequencies range from $10^2$ to $10^6$ ; Y-Axis: instruction error rates range from $10^{-4}$ to $10^{-9}$ ; Z-Axis: Normalized thread-level RRNS energy (TMR results are normalized to 1). | 84 |

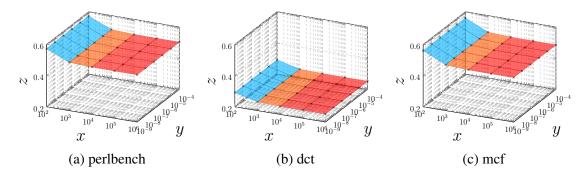

| 6.12 | Normalized EDP results for different error detection frequencies and error rates; X-Axis: error detection frequencies range from $10^2$ to $10^6$ ; Y-Axis: instruction error rates range from $10^{-4}$ to $10^{-9}$ ; Z-Axis: Normalized thread-level RRNS EDP (TMR results are normalized to 1).       | 84 |

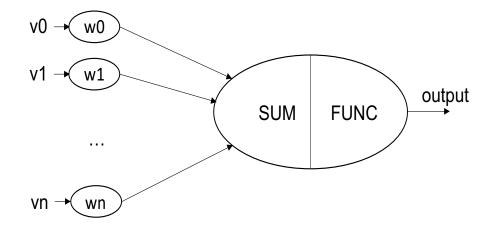

| 7.1  | A Conventional Neuron of Deep Neural Network                                                                                                                                                                                                                                                              | 92 |

#### SUMMARY

Dennard scaling of conventional semiconductor technology has reached its limit resulting in issues pertaining to leakage current and threshold voltage. Energy-savings found at the transistor level by simply lowering supply voltage are no longer available for these devices (e.g., MOSFETs) and has reached the Landauer-Shannon limit. Recent proposals of minivolt switch technologies aim to extend the technology scaling roadmap by maintaining a high on/off ratio of drain current with a much lower supply voltage. However, high intermittent error probabilities in millivolt switches constraints their  $V_{dd}$  reduction for traditional architectures. Thus, there is an urgent need for scalable and energy-efficient micro-architectures with computational error-tolerance.

This thesis systematically leverages the error detection and correction properties of the Redundant Residue Number System (RRNS) by varying the number of non-redundant (n) and redundant (r) components (residues), and selects and discusses trade-offs about configuration points from a two-dimensional (n, r)-RRNS design plane that meet certain capabilities of error detection and/or correction. Being able to efficiently handle resilience in this (n, r)-RRNS plane significantly improves reliability, allowing further  $V_{dd}$  reduction and energy savings.

First, the necessary implementation details of RRNS cores are discussed. Second, scalable RRNS micro-architectures that simultaneously support both error-correction and checkpointing with restart capabilities for uncorrectable errors are proposed. Third, novel RRNS-based adaptive checkpointing&restart mechanisms are designed that automatically guarantee reliability while minimizing the energy-delay product (EDP). Finally, the RRNS design space is explored to find the optimal (n, r) configuration points. For similar reliability when compared to a conventional binary core (running at high  $V_{dd}$ ) without computational error tolerance, the proposed RRNS scalable micro-architecture reduces EDP by 53% on average for memory-intensive workloads and by 67% on average for non-memory-

intensive workloads.

This thesis's second topic is to alleviate fault rate and power consumption issues of exascale computing. Faults in High-Performance Computing (HPC) have become an urgent challenge with estimated Mean Time Between Failures (MTBF) of exascale system projected as only several minutes with contemporary methodologies. Unfortunately, existing error-tolerance technologies in the context of HPC systems have serious deficiencies such as insufficient error-tolerance coverage, high power consumption, and difficult integration with existing workloads. Considering Department of Energy (DOE) guidelines that limit exascale power consumption to 20 MW, this thesis highlights the issue of energy usage and proposes a thread-level fault tolerance mechanism compatible with current state-of-the art exascale programming models while simultaneously meeting the requirements of full system error protection. Additionally, an efficient micro-architecture and corresponding mechanisms that can support thread level RRNS are discussed. Experimental results show that this strategy reduces energy consumption by 62.25% and the Energy-Delay-Product by 58.67% on average when compared with state-of-the-art black box resilience techniques.

# CHAPTER 1 INTRODUCTION AND BACKGROUND

Dennard scaling [1] has been one of the critical technology roadmap trendings through past decades for computer efficiency improvement. This scaling's main idea is that transistors consume the same amount of power per unit area as they scale down in size. However, leak-age current and threshold voltage issues from smaller MOSFET devices caused Dennard scaling to be terminated [2]. This termination essentially negates possible performance benefits that Moore's law may provide.

This has not reached the limit of irreversible logic operations. Landauer [3] presented the lower bound of energy dissipation of an irreversible logic operation to be on the order of kT, where k is the Boltzmann's constant and T is the absolute temperature. However, MOSFET is constrained by the 50× higher Landauer-Shannon limit [4]. The reason for this disparity is that MOSFETs are limited to a sub-threshold slope of  $\frac{kT}{q}ln10 \approx 60$ mV/decade. Certain new devices, known as millivolt switches, such as Tunnel FETs [5] and Ferroelectric FETs [6], are possible to break through this wall. However, as the signal strength of a cell phone becomes weaker as it moves further from the transmitter tower, Agarwal et al. [7] conclude that error probability increases exponentially as signal energy is lowered:  $P_e = exp(-\frac{E_{signal}}{kT})$ .  $P_e$  in this equation denotes error probability, and  $E_{signal}$ represents the signal energy of this transistor. If the size of a new device continually scaling, it eventually leads to an error because there is no enough energy to distinguish the '0' or '1' status.

Therefore, to keep the failure rate of millivolt switch-based microarchitectures within bounds and achieve optimal or suboptimal energy reduction, error-tolerance consideration must be incorporated. In other words, to punch through the existing power wall via millivolt switches, efficient error-detection, correction, and/or checkpoint&rollback schemes are required. The technology roadmap would then be possible to scale further by reducing the switch signal energy to close the Landauer limit.

#### 1.1 Computational Error Tolerance

Standard error-correcting codes (ECC) [8] has already widely been using in modern communication systems and storage units. However, *ECC lacks the theoretical capability to protect the computational units and corresponding components, such as Arithmetic Logic Unit (ALU) or accumulator.* Therefore, traditional ECC is insufficient to protect the whole computing system at a low  $V_{dd}$ . Computational error-tolerant techniques that are commonly used are now described in the following subsections.

#### 1.1.1 Dual/Triple Modular Redundancy

Dual or Triple Modular Redundancy (D/TMR) is a conventional computational error-tolerant scheme [9]. From the perspective of error-tolerant capability, DMR is able to detect one error while TMR can correct one error from one of the components. As shown in Figure 1.1,the basic idea of TMR is to make two additional copies of the existing computational logic and then followed by a majority vote from these three outputs. If one of the computational components arises an error while TMR is simple and straightforward to implement, its overhead is more than 200% in both component area and power to detect and correct the single error. The energy-saving potentials from lowering  $V_{dd}$  would therefore be eliminated.

#### 1.1.2 Residue Checking

IBM commercial processor series, such as z990, z10, z196, POWER6 and POWER7 [10, 11, 12, 13] use residue checking scheme to achieve the error tolerance. A residue is the remainder from a given number is divided by a predefined module. The residue check-

Figure 1.1: Triple Modular Redundancy in action.

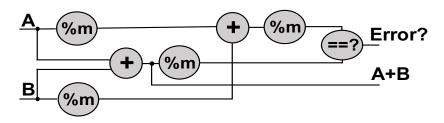

ing methodology consists of two independent datapaths followed by a comparator, and leverages the closure property of residue arithmetic wherein  $(A\%m \ op \ B\%m)\%m = (A \ op \ B)\%m$ , for integers A, B, modulus m and arithmetic operation op. An error is detected whenever the comparator returns a not-equal output. From the flowchart in Figure 1.2, m usually is represented by a small integer, such as 3, 9, or 15 in IBM processor series.

Generally speaking, the overhead of residue checking technologies' one-time error detection is low. This is mainly because the bit-width of its redundant datapath is constrained by the selected modulus, which is usually less or equal to 4 bits. Unfortunately, this lightweight protection may negatively impact the full system reliability. For example, for m = 5,  $\frac{1}{5}$  of possible errors are undetectable (say the correct value is 2, all erroneous values v satisfying v%5 = 2 such as 7, 12, 17 etc. would remain undetectable).

Furthermore, an error detection operation must be performed right after every arithmetic computation. If no residue error check is inserted after the corresponding arithmetic operation, then this error generated during the computation becomes undetectable forever. Finally, as the residue checking datapath can only detect errors generated during the current arithmetic computation, the input values must be verified (such as via performing an ECC check on every register read) before this computation.

Figure 1.2: Residue Checking Flowchart

An improved computational error-tolerant approach (RRNS, described below) overhauls residue checking to eliminate the above issues while still maintaining excellent system robustness. RRNS has the following benefits:

- 1. RRNS may significantly reduce the undetectable error rate in general.

- 2. RRNS does not require checking the output of every arithmetic operation.

- 3. RRNS does not require checking input values.

Furthermore, ALU optimizations become feasible in RRNS, resulting in significantly more energy-efficient addition, subtraction, and multiplication. Before discussing RRNS, the Residue Number Systems (RNS) needs to be first described.

#### 1.1.3 Residue Number Systems (RNS)

Residue Number Systems (RNS) have been widely utilized in many popular application domains such as digital signal processing (DSP) [14, 15, 16], cryptography (RSA) [17, 18, 19] and in-memory neural network acceleration [20]. Due to the carry-free property [21, 22] and small bit-width datapaths, RNS is able to get benefits via replacing the conventional binary system in computationally intensive domains. In an *n*-RNS, a non-negative integer X < M bijectively maps to a set of *n* smaller integers, known as residues. Given a set of *n* co-prime bases or moduli  $B = \{m_i \in \mathbb{N}, i = 1, 2, 3, ..., n\}$ , the *i*<sup>th</sup> residue is defined as  $|X|_{m_i} = X \% m_i$ . The RNS range of representable numbers is equal to  $M = \prod_{i=1}^n m_i$ . The arithmetic operations of RNS, such as addition, subtraction, and multiplication, are very efficient. This is mainly because each residue performs parallel and independent arithmetic computations and does not interfere with and interact with each other. The parallel and independent properties offer great potential to improve the performance and energy reduction, particularly for multiplication which is always slow and power-hungry with conventional binary design. However, the general RNS division operation requires relatively high overhead algorithms [23, 24], and most RNS architectures avoid division-intensive workloads. For workloads with only a small ratio of division instructions, besides the specific RNS division algorithm, RNS can also be converted to binary to perform a binary division and then convert the output from binary back to RNS format after the binary division completes.

#### 1.1.4 Redundant Residue Number Systems (RRNS)

AS the residue has independence and isolation properties, the error generated on a particular residue should not propagate to others. By adding r redundant moduli to an n-RNS system, error tolerance can then be achieved. This is known as the Redundant Residue Number System, or (n,r)-RRNS in this case and now has an extended set of bases/moduli:  $B = \{m_i \in \mathbb{N}, i = 1, 2, 3, ..., n, n+1, ..., n+r\}$ . Any non-negative integer number smaller than  $M (= \prod_{i=1}^{n} m_i)$  can still be represented uniquely by its original n non-redundant residues while the remaining r residues store redundant information to support error tolerance.

Since errors in a particular residue are self-contained, these errors from a particular reisue should not infect the others. Furthermore, the errant residue can be detected and/or corrected via the remaining residues [25]. Table 1.1 provides a simple (4,2)-RRNS system (n = 4, r = 2) example with a toy base set (3, 5, 2, 7, 11, 13) to explain how RRNS works for arithmetic computation. Table 1.1 is extended from the example table in [26]. Decimal  $10 \equiv (2, 4, 1, 1, 7, 3)$  in this example and the range  $M = 3 \times 5 \times 2 \times 7 = 210$ .

| Decimal   | %3        | %5 | %2 | %7 | %11 | %13 |

|-----------|-----------|----|----|----|-----|-----|

| 10        | 1         | 0  | 0  | 3  | 10  | 10  |

| 19        | 1         | 4  | 1  | 5  | 8   | 6   |

| 10+19=29  | (1+1)%3=2 | 4  | 1  | 1  | 7   | 3   |

| 10*19=190 | (1*1)%3=1 | 0  | 0  | 1  | 3   | 8   |

Table 1.1: A (4, 2)-RRNS example with a toy base set (3, 5, 2, 7, 11, 13). 11 and 13 are the redundant bases.

In practice, base sets with more realistic ranges, such as (211, 421, 256, 347, 503, 509), are discussed in Section 2.9. A (4,2)-*RRNS* system has the capability of correcting a one residue in error (One Error Correction;1EC) *or* detecting two residues in error (Two Error Detection;2ED) [25]. The relationships between (n,r) and RRNS error tolerance capabilities with other related details are discussed in Chapter 2.2 and 2.3.

In general, RRNS is a great error-tolerant methodology with energy-efficient and low area overhead potentials. Based on these advantages, RRNS can be widely used in remote embedded systems, high-performance computers, spacecraft design, etc., all of which have specific requirements of fault tolerance and low energy consumption. This thesis analyzes RRNS from bit-level parallelism for millivolt switch and thread-level parallelism for exascale computing. It also proposes related microarchitectures to achieve error-tolerance and energy-efficiency goals.

#### 1.2 Contributions

While modeling the RRNS cores with some empirical configuration points may get more energy-efficient than unprotected binary ones with similar reliability, a systematic (n, r)-*RRNS* design exploration yields even more energy benefit and is able to find out the corresponding optimal or suboptimal configurations. On the one hand, by thoroughly exploiting the potential of RRNS reliability, millivolt switches' signal energy can further approach the theoretical Landauer limit. On the other hand, by applying the RRNS methodology at thread level granularity, the two urgent challenges of exascale computing, fault tolerance and high energy consumption, can be alleviated to a certain extent.

This thesis starts with a specific RRNS configuration(zero-dimension, (4,2)-RRNS) and verifies the feasibility and the potential of this resilient methodology. And then enhancing the zero-dimensional design to a two-dimensional *scalable* scalable architecture framework supporting *c*-residue error correction and *d*-residue error detection (*c*EC*d*ED). In theory, *c* and *d* can be any non-negative integers. For example, 1EC is equivalent to 1EC0ED, and 2ED is represented as 0EC2ED. The term 'scalable' above means that the number of RRNS non-redundant (*n*) and redundant (*r*) moduli can be extended with error tolerance adjustment. As such, the following key contributions are made for microarchitecture designs of millivolt switches:

- Propose a scalable, energy-efficient RRNS-based microarchitecture that simultaneously supports error correction and checkpointing&restart, when used with upcoming millivolt switches.

- 2. Design and analysis of an efficient RRNS multiplier unit using the index-sum technique.

- 3. Design a set of novel RRNS-based checkpointing&restart mechanisms that benefit from optimized checkpoint size and adaptive time interval adjustment. They narrow the signal energy gap further to close the theoretical Landauer limit. Moreover, compared with other checkpointing technologies, these methodologies further improve memory usage efficiency.

- 4. Perform a systematic design space exploration of (n,r)-RRNS-cECdCR microarchitectures via a tradeoff analysis between reliability and energy-delay overheads of error correction and checkpointing. Solving such a discrete convex optimization problem results in finding out the best RRNS configurations that minimize energydelay-product (EDP) while maximizing reliability.

The bit-level RRNS evaluation results with reasonable (n,r)-RRNS configurations (more details are available in Chapter 2.3) present three insights: (i) Cores that employ a *hybrid* detection-correction strategy (i.e., cd > 0) are more resilient. However, they suffer from the combined overhead of both mechanisms in terms of energy as well as performance. (ii) For memory-intensive workloads, the EDP of *correction-only* systems (d = 0) are superior to *detection-only* (c = 0) ones within a reasonable range, resulting in 53% EDP reduction. This is because of the higher state overheads in checkpoint-based systems for memory-intensive workloads. (iii) For non-memory-intensive workloads, detection-based systems are superior, resulting in 67% EDP reduction. Unless otherwise mentioned, all results in this topic are compared against a conventional binary core that is not computationally error-tolerant (runs at high  $V_{dd}$ ) of similar reliability<sup>1</sup>.

In the optimization of exascale computing, the fault-tolerant RRNS API is added to the Habanero C/C++ library (HClib)[27], which provides easy-to-use interfaces for the programming model of exascale computing. Moreover, the thread-level RRNS CPU microarchitecture is proposed. When applications that require high fault-tolerance requirements in a heterogeneous exascale computing system, they can be assigned to these fault-tolerant cores to execute and achieve the purpose of fault-tolerance. Compared with the traditional Triple Modular Redundancy(TMR) method, RRNS has the advantage of lower energy consumption. Therefore, the following contributions are made for thread-level RRNS design:

- Propose a thread-level Redundant Residue Number System (RRNS) scheme and design the corresponding microarchitecture by following the unique execution mode of thread-level RRNS. This allows RRNS to be efficiently applied to exascale systems improving their fault-tolerance and energy-efficiency.

- 2. Propose the RRNS API compatible with the current Habanero C/C++ library (HClib)[27], which demonstrates the feasibility of thread-level RRNS in the current Asynchronous

<sup>&</sup>lt;sup>1</sup>Mean Time Between Failures (MTBF) > Average Human Lifespan (100 years).

Many-Task (AMT)[28] programming model widely used for programming exascale systems.

Through further optimizations of thread-level RRNS microarchitecture, this method shows 62.25% and 58.67% reduction respectively in energy and Energy Delay Product (EDP), compared with the state-of-the-art Asynchronous Many-Task (AMT) blackbox resiliency method.

#### **1.3 Thesis Statement**

Error-tolerant microarchitectures via Redundant Residue Number System can further extend the semiconductor technology roadmap, and alleviate reliability and power challenges of exascale computing.

#### 1.4 Thesis Outline

Chapter 2, 3, 4, and 5 of this thesis discuss the scalable energy-efficient and error-tolerant CPU microarchitecture designs for millivolt switches.

Chapter 2 introduces the basic RRNS concepts, approaches, and optimizations that are necessary for the CPU microarchitecture design. A scalable RRNS microarchitecture framework that can be compatible with error correction and detection&restart is also proposed. The publications related to Chapter 1 and Chapter 2 are [7, 26, 29, 30, 31].

Chapter 3 discusses the RRNS checkpointing&restart mechanisms in detail. First introduced the static checkpointing&restart method, and then implemented two adaptive checkpointting&restart strategies based on the system's historical information. Finally, it shows experimental results and analysis based on the (4, 2)-RRNS configuration.

Chapter 4 introduces the correction-only RRNS system and discusses the range of reasonable error correction capabilities for the RRNS microarchitecture framework.

Chapter 5 demonstrates the hybrid RRNS system with the capability of both correction

and checkpointing&restart. Then find out the optimal or suboptimal design configuration in the (n, r)-RRNS setting space with different fault-tolerant capabilities. The publication related to Chapter 3, Chapter 4 and Chapter 5 is [26].

Chapter 6 introduces thread-level RRNS and its related microarchitecture. This design aims to alleviate the critical exascale computing challenges regarding high error rates and high energy consumption. Finally, through experimental simulation, it is found that threadlevel RRNS has better Energy Delay Product (EDP) results than thread-level TMR (Triple Modular Redundancy). The publication related to Chapter 6 is waiting to submit.

Finally, Chapter 7 summarizes the previous discussions and proposes future work that is related to this topic.

#### **CHAPTER 2**

### SCALABLE RRNS MICROARCHITECTURES FOR MILLIVOLT SWITCHES

This chapter first describes the error-tolerant capabilities of one configuration point: (4,2)-RRNS. The first digit '4' refers to the number of non-redundant moduli/residues, and the second digit '2' refers to the number of redundant moduli/residues. Then, discussing the relationship between the number of moduli/residues and the capability of fault-tolerance in the entire design space. This chapter also introduces several detailed considerations that are essential for the scalable RRNS microarchitecture design, including signed number representation, correction factors, arithmetic overflow detection, comparison, multiplier optimization, and RRNS base selection. Finally, a scalable RRNS microarchitecture that can support error correction and error detection&roolback is proposed for the millivolt switches.

#### 2.1 (4,2)-RRNS Error Detection/Correction Algorithm

The algorithm for one error detection/correction was originally given by Watson [25]. However, RNS renders comparison and arithmetic overflow detection to be a non-trivial exercise. This section presents algorithms to perform these functions by augmenting the error checking algorithm. This way, no extra hardware is warranted beyond that required by the error checking.

The one error correction algorithm proposed by Watson [25] is based on an error correction table. The working steps of this algorithm for a system with 4 non-redundant moduli  $(m_1, m_2, m_3, m_4)$  and 2 redundant moduli  $(m_5, m_6)$ , for any given integer X ( $< M = m_1m_2m_3m_4$ ) is as follows: (a) Use a base-extension Algorithm [32, 33, 25] to compute  $|X'|_{m_5}$  and  $|X'|_{m_6}$ , where  $|X'|_{m_5}$  and  $|X'|_{m_6}$  are the outputs of the the base-extension algorithm algorithm. The inputs to the base-extension algorithm are from the outputs of

| $\Delta m_5, \Delta m_6$ | $i' \epsilon$ |

|--------------------------|---------------|--------------------------|---------------|--------------------------|---------------|--------------------------|---------------|--------------------------|---------------|

| 1,10                     | 46            | 4,5                      | 11            | 5,12                     | 31            | 7,7                      | 43            | 9,3                      | 22            |

| 2,10                     | 23            | 4,6                      | 44            | 6,1                      | 31            | 7,8                      | 12            | 10,3                     | 41            |

| 2,12                     | 46            | 4,7                      | 21            | 6,4                      | 24            | 8,1                      | 22            |                          |               |

| 3,3                      | 11            | 4,11                     | 45            | 6,5                      | 43            | 8,4                      | 4 2           |                          |               |

| 3,9                      | 45            | 5,8                      | 44            | 7,2                      | 42            | 8,10                     | 12            |                          |               |

| 3,12                     | 23            | 5,9                      | 21            | 7,6                      | 42            | 9,1                      | 41            |                          |               |

Table 2.1: Error Correction table of RRNS System with Moduli (3,5,2,7,11,13)

non-redundant subcores:  $|X|_{m_1}$ ,  $|X|_{m_2}$ ,  $|X|_{m_3}$  and  $|X|_{m_4}$ , where  $|X|_m = X \mod m$ ; the computational output of the subcore with  $m_i$  modulus. (b) For i = 5, 6: compute  $\Delta m_i = ||X'|_{m_i} - |X|_{m_i}|_{m_i}$ . (c) A non-zero difference indicates the presence of an error. This pair of differences may index into an entry of a pre-computed (fixed) error correction table, which contains the index of the residue that is in error and a correction offset that needs to be added to that residue to correct said error.

The RRNS Error detection/correction algorithm could easily be activated via scheduling the RRNS check instruction, which has been defined in CREEPY ISA [30]. For the error detection step, the system would perform (a) and (b) to get values of  $\Delta m_5$  and  $\Delta m_6$ . For the error correction step (if necessary), it performs (c). Analysis of the algorithm reveals that the error detection step would take 8 cycles while the correction step takes 2 cycles. Therefore, once the system inserts an RRNS\_check instruction, the first step is to execute the 8-cycle error detection procedure. If no error is found, then this RRNS\_check instruction is complete and it takes 8 cycles in total. But if an error is detected, then we need 2 more cycles for the RRNS correction operation to complete (resulting in 10 cycles in total).

For ease of presentation, we present such an error correction table for a smaller (toy) set of RRNS base moduli in Table 2.1. The total entries in such a table is at most  $2\sum_{i=1}^{4}(m_i - 1)$ . For the remainder of this chapter, this set of bases are used for explanatory purposes.

|                                                                       | One Error Correction Lookup                                 |     |                   |                   |     |        |     |                                   |                      |                          |                      |                             |                      |  |

|-----------------------------------------------------------------------|-------------------------------------------------------------|-----|-------------------|-------------------|-----|--------|-----|-----------------------------------|----------------------|--------------------------|----------------------|-----------------------------|----------------------|--|

| 1 Error                                                               | Binary                                                      | %3  | %5                | %2                | %7  | %11    | %13 | Table with moduli (3,5,2,7,11,13) |                      |                          |                      |                             |                      |  |

| Intended                                                              | 168                                                         | 0   | 3                 | 0                 | 0   | 3      | 12  | $\Delta r_5$ , $\Delta r_6$       | <b>i</b> ′, <i>ϵ</i> | $\Delta r_5, \Delta r_6$ | <b>i</b> ′, <i>ϵ</i> | $\Delta r_5$ , $\Delta r_6$ | <b>i</b> ′, <i>ϵ</i> |  |

| Actual                                                                | 42                                                          | 0   | 2                 | 0                 | 0   | 3      | 12  | 1,10                              | 4,6                  | 4,11                     | 4,5                  | 7,7                         | 4,3                  |  |

| $r'_5 =  42$                                                          | $r'_5 =  42 _{11} = 9$ $\Delta r_5 =  r_5 - r'_5 _{11} = 5$ |     |                   |                   |     |        |     |                                   | 2,3                  | 5,8                      | 4,4                  | 7,8                         | 1,2                  |  |

| $r'_6$ =  42                                                          | $r'_6 =  42 _{13} = 3$ $\Delta r_6 =  r_6 - r'_6 _{13} = 9$ |     |                   |                   |     |        |     |                                   | 4,6                  | 5,9                      | 2,1                  | 8,1                         | 2,2                  |  |

| 2 Error                                                               | Binary                                                      | %3  | %5                | %2                | %7  | %11    | %13 | 3,3                               | 1,1                  | 5,12                     | 3,1                  | 8,4                         | 4,2                  |  |

| Intended                                                              | 0                                                           | 0   | 0                 | 0                 | 0   | 0      | 0   | 3,9                               | 4,5                  | 6,1                      | 3,1                  | 8,10                        | 1,2                  |  |

| Intended                                                              | 0                                                           | 0   | 0                 | 0                 | 0   | 0      | 0   | 3,12                              | 2,3                  | 6,4                      | 2,4                  | 9,1                         | 4,1                  |  |

| Actual                                                                | 160                                                         | 1   | 0                 | 0                 | 6   | 0      | 0   |                                   |                      |                          |                      |                             | -                    |  |

| 1 - 14 - 14                                                           | 4,5 1,1 6,5 4,3 9,3 2,2                                     |     |                   |                   |     |        |     |                                   |                      |                          |                      | 2,2                         |                      |  |

| $r'_5 =  160 _{11} = 6$ $\Delta r_5 =  r_5 - r'_5 _{11} = 5$ 4,6  4,4 |                                                             |     |                   |                   |     |        |     |                                   |                      | 7,2                      | 4,2                  | 10,3                        | 4,1                  |  |

| r <sub>6</sub> ' =  160                                               | $0 _{13} = 4$                                               | 4 4 | ∆r <sub>6</sub> = | =  r <sub>6</sub> | - r | 6 13 = | 4,7 | 2,1                               | 7,6                  | 2,4                      |                      |                             |                      |  |

Figure 2.1: (4,2)-RRNS is capable of 1EC or 2ED

#### 2.2 Error-tolerant Capability of (4,2)-RRNS

Similar to other resilient techniques, the RRNS error-tolerant capability depends on the amount of redundancy, i.e., the number of redundant moduli. For example, a (4,2)-RRNS is capable of *either* 1EC *or* 2ED, but not both simultaneously. The term '1EC' refers to '1 Error Correction', and '2ED' stands for "2 Error Detection". The reasoning for this, as well as the working of the RRNS detection and correction algorithms, are now explained by means of an example.

Consider there is a (4,2)-RRNS with toy bases (3,5,2,7,11,13). Say the result from an operation is intended to be (0,3,0,0,3,12) whereas, due to a transient fault, the second residue changes from 3 to 2 (Figure 2.1). If an RRNS error detection is performed immediately, the Chinese Remainder Theorem [34] or the Base Extension Algorithm [35, 25] can be used to re-generate the redundant residues ( $r_5' = 9$ ,  $r_6' = 3$ ) from the non-redundant residues ( $r_1 = 0$ ,  $r_2 = 2$ ,  $r_3 = 0$ ,  $r_4 = 0$ ). Now, the delta\_value\_pair ( $\Delta r_5 = 5$ ,  $\Delta r_6 = 9$ ) is used to infer the possibility of an error and potentially restore the correct result. Three cases arise for the delta\_value\_pair:

1. Both are zero. This implies that there are no errors in the RRNS data. No correction

or recovery is necessary.

- 2. 1EC mode:

- Exactly one of them is non-zero. This indicates that the corresponding non-zero redundant residue is in error. Correction is performed by overwriting the errant redundant residue with the re-generated value.

- Both are non-zero. It means that exactly one of the non-redundant residues is in error, and a single error correction LUT<sup>1</sup> must be consulted to handle the error.

- 2ED mode: One of them is non-zero. This implies that at least one residue is in error. No LUT consultation is necessary for error detection, but an efficient checkpointing/restart mechanism is necessary (Chapter 3)

In 1EC mode, the delta\_value\_pair ( $\Delta r_5 = 5$ ,  $\Delta r_6 = 9$ ) should be used as an input to index into the one error correction LUT. This returns (*i*'=2, $\epsilon$ =1), which translates to the following: a correction offset of '1' is to be added to the 2<sup>nd</sup> residue in order to correct its errant value. However, consider the example of the double errors in Figure 2.1 where two residues are actually incorrect. Observe that the delta\_value\_pair is again ( $\Delta r_5 = 5$ ,  $\Delta r_6 = 9$ ), and 1EC mode performs incorrect restoration by accessing LUT, resulting in system failure because its correction error model tolerates at most one residue in error. However, if the (4,2)-RRNS system was working in a 2ED mode rather than 1EC, then such a double error would indeed be detected. In other words, (4,2)-RRNS is capable of exactly one of 1EC or 2ED. If both 1EC and 2ED are simultaneously supported in a (4, 2)-RRNS system, it will cause similar delta\_value\_pair conflictions as shown in Figure 2.1, resulting in incorrect behaviors. More redundant information is needed to support both 1EC and 2ED in the same RRNS.

<sup>&</sup>lt;sup>1</sup>The one error correction Lookup Table (LUT) is unique to the RRNS base set, and its size grows linearly with the magnitude of the base moduli (summation).

#### 2.3 (n,r)-RRNS Error-Tolerant Extension

The number of non-redundant moduli (n) and redundant moduli (r) can be adjusted for a performance-energy-reliability tradeoff. n has a direct impact on the amount of bit-level parallelism that one can leverage. Of more fundamental interest to this thesis, r has a direct impact on error tolerance capabilities, as summarized in the two lemmas below by [36]:

- 1. An (n, r)-*RRNS* code can detect upto r residue errors, *or* correct upto  $\lfloor \frac{r}{2} \rfloor$  reside errors.

- 2. An (n, r)-*RRNS* code can correct upto t residue errors and simultaneously detect upto v (> t) errors if  $t + v \le r$ .

The precondition for these lemmas is that the redundant moduli must be larger than the non-redundant ones. This condition, along with other considerations for designing a set of RRNS base moduli for energy-efficient and error-resilient microarchitectures are described in detail in Section 2.9.

Using the lemmas, as an example, a (4,3)-RRNS architecture can either employ 0EC3ED or 1EC2ED, while a (4,4)-RRNS architecture can choose between 0EC4ED and 1EC3ED. The key advantage of a hybrid (correction+detection&rollback) architecture is that thanks to the correction, rollbacks become statistically less expensive in terms of latency and energy. In theory, timely correction can avoid the frequency of rollbacks at a certain probability. On the other hand, with the help of detection&rollback, a higher error (multiplicity) tolerant capability is achieved, which can in turn enable higher energy savings due to lowering  $V_{dd}$  further. These benefits are, of course, subject to the runtime overheads of error correction and detection&rollback, therefore resulting in an expansive RRNS design space. In other words, this thesis explores the optimal or suboptimal values for n, r, c and d in an (n,r)-RRNS-cECdED architecture, given the constraints above.

Increasing n improves the parallelism in RRNS operations, upto a certain point, after which the overheads of routing and duplication overshadow the benefits. Furthermore, too

large a value can hinder base selection in its ability to find co-primes, since larger the value of n, lower is the bit width of each modulus for a given range. Finally, a higher value of n also slows down the RRNS-Binary Conversion Unit (as shown in Figure 2.11). Hence, the reasonable value of n is limited to  $\{3, 4, 5\}$  in RRNS design space exploration.

Increasing r improves reliability in general and can therefore help reduce  $V_{dd}$  and save energy. However, after a certain point, the added overhead of the redundant residues and the Error Detection Units (as shown in Figure 2.11) outweigh the savings due to lower  $V_{dd}$ . As a thumb rule, r > n is avoided as the bit widths of redundant residues are at least as wide as the non-redundant ones, and r > n would therefore add significant overhead.

Given the nature of increasing either n or r as outlined above, minimizing Energy Delay Product (EDP) is therefore a discrete convex optimization problem in both these dimensions. As such, it is sufficient to evaluate the ranges of  $3 \le n \le 5$  and  $1 \le r \le n$ as long as the minimum does not lie on the boundary of this surface. The results from the empirical evaluation in Chapter 5.2 confirm this and finds that the checkpoint/restart mechanism in isolation is generally superior to other approaches for non-memory-intensive workloads. But for memory-intensive ones, the correction-only approach is the best bet.

#### 2.4 Signed Number Representation

This chapter discusses and compares three competing ways of representing signed numbers. Each presents its set of trade-offs, which will be discussed in detail below. M is the product of all the non-redundant moduli (M = m1\*m2\*m3\*m4 in (4,2)-RRNS) and MR is the product of all the redundant moduli (MR = m5\*m6 in (4,2)-RRNS).

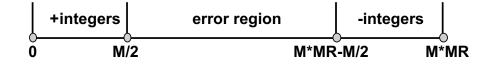

#### 1. Complement M\*MR Signed Representation

The M\*MR complement signed representation is depicted by Figure 2.2. To provide a few examples, 0 is represented by 0, 1 is represented by 1,  $\frac{M}{2} - 1$  is represented by  $\frac{M}{2} - 1$ , -1 is represented by M \* MR - 1 and  $-\frac{M}{2}$  is represented by  $M * MR - \frac{M}{2}$ .

This is similar to signed binary representation. However, representing numbers in this manner breaks known error correction algorithms[25].

Figure 2.2: Complement M\*MR signed representation

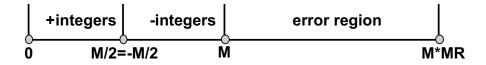

### 2. Complement M Signed Representation

The M complement signed representation is depicted in Figure 2.3. This is similar to the M\*MR complement representation, except that the wrap-around occurs at M as opposed to M\*MR. This representation does not break error correction algorithms, provided that some correction factors (scaling and offset) are applied to the result of each arithmetic operation. However, further analysis indicates that these correction factors require knowledge of the signs of the operands, which are not trivial to determine like in binary. The RRNS sign determination is a time-consuming algorithm. Moreover, THE overflow detection of an arithmetic operation is unknown for this representation.

Figure 2.3: Complement M signed representation

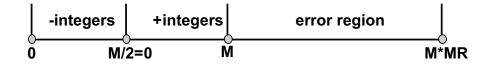

# 3. Excess- $\frac{M}{2}$ Signed Representation

The Excess- $\frac{M}{2}$  signed representation is depicted in Figure 2.4. The excess notation, sometimes known as offset notation, merely shifts each number by  $\frac{M}{2}$ . To further elaborate, 0 is represented by  $\frac{M}{2}$ , 1 is represented by  $\frac{M}{2} + 1$  and -1 is represented by  $\frac{M}{2} - 1$ . Similar to the M Complement representation, the results of arithmetic

operations must be offset by a correction factor before they can be corrected. However, these correction factors turn out to be independent of the sign of the operands. Moreover, this representation enables simple algorithms for comparison (and thereby sign detection) and overflow detection of an arithmetic operation. In fact, these algorithms make use of a technique used in the error detection/correction algorithm itself. These algorithms are discussed in detail in Section 2.6 and Section 2.7.

Figure 2.4: Excess -M/2 signed representation

Through the above comparisons,  $\text{Excess-}\frac{M}{2}$  was chosen as the de facto signed representation scheme.

#### 2.5 Correction Factors

This section discusses the addition, subtraction and multiplication operations on two numbers with correction factors that do not generate any overflow. Recall from Section 2.4 that suggests to use the Excess- $\frac{M}{2}$  notation, which means that there is a bijective mapping from any number x such that  $-\frac{M}{2} < x < \frac{M}{2}$  to  $x + \frac{M}{2}$ . Because of this offset, arithmetic operations results need to be re-adjusted using values called *correction factors*. [However, this has nothing to do with the RRNS error correction operation.]

Addition Consider the addition of two numbers x and y. To represent the mapping, define a and b such that  $0 \le a, b < \frac{M}{2}$  so that there is no overflow.

Case 1:  $x, y \ge 0$

Consider x = a and y = b. The sum x + y can be represented for each subcore  $1 \le i \le n + r$  as follows:

$$\left| \left| \frac{M}{2} + a \right|_{m_i} + \left| \frac{M}{2} + b \right|_{m_i} \right|_{m_i} = \left| |M|_{m_i} + |a + b|_{m_i} \right|_{m_i}$$

(2.1a)

$$= |a+b|_{m_i} \text{ for } 1 \le i \le n \tag{2.1b}$$

However, the expected addition result is:

$$\left|\frac{M}{2} + a + b\right|_{m_i} = \left|\frac{M}{2}|_{m_i} + |a + b|_{m_i}\right|_{m_i}$$

(2.2)

It follows that:

- 1.  $1 \le i \le n$  and  $m_i$  is odd: Examining equations 2.1b and 2.2 imply that no correction factor is necessary.

- 2.  $1 \le i \le n$  and  $m_i$  is even: Examining equations 2.1b and 2.2 implies that a constant correction factor of  $|\frac{M}{2}|_{m_i}$  needs to be added to the result.

- 3.  $n + 1 \le i \le n + r$ : Examining equations 2.1a and 2.2 imply that a constant correction factor of  $|\frac{M}{2}|_{m_i}$  needs to be subtracted from the result.

**Case 2**: *x*, *y* < 0

Setting x = -a and y = -b, and re-working equations similar to Equations 2.1a, 2.1b and 2.2 result in correction factors that are identical to Case 1.

**Case 3**: x > 0, y < 0 (Without loss of generality.)

Setting x = a and y = -b, and re-working equations similar to Equations 2.1a, 2.1b and 2.2 result in correction factors that are identical to Case 1.

**Subtraction** Due to the symmetric and offset based nature of the Excess- $\frac{M}{2}$  representation, just one of the working cases is presented; without loss of generality: x = a and

y = b. Then, x - y becomes:

$$\left| \left| \frac{M}{2} + a \right|_{m_i} - \left| \frac{M}{2} + b \right|_{m_i} \right|_{m_i} = |a - b|_{m_i}$$

(2.3)

However, the expected subtraction result is:

$$\left|\frac{M}{2} + a - b\right|_{m_i} = \left|\frac{M}{2}\right|_{m_i} + |a - b|_{m_i}\Big|_{m_i}$$

(2.4)

From examining equations 2.3 and 2.4, it follows that:

- 1.  $1 \le i \le n$  and  $m_i$  is odd: No correction factor is necessary.

- 2.  $1 \le i \le n$  and  $m_i$  is even: A constant correction factor of  $|\frac{M}{2}|_{m_i}$  needs to be added to the result.

- 3.  $n+1 \le i \le n+r$ : A constant correction factor of  $|\frac{M}{2}|_{m_i}$  needs to be added to the result.

- **Multiplication** Again, for brevity, we only present the case where two positive integers are multiplied; without loss of generality: x = a and y = b; the product xy becomes:

$$\left| \left| \frac{M}{2} + a \right|_{m_i} \left| \frac{M}{2} + b \right|_{m_i} \right|_{m_i} = \left| \left| \frac{M^2}{4} + \frac{(a+b)M}{2} \right|_{m_i} + |ab|_{m_i} \right|_{m_i}$$

(2.5)

However, the expected multiplication result is:

$$\left|\frac{M}{2} + ab\right|_{m_i} = \left|\frac{M}{2}|_{m_i} + |ab|_{m_i}\right|_{m_i}$$

(2.6)

As residues are typically 8-bit wide, consider a 511 entry LUT per subcore that stores the following:

$$LUT(s) = \left| \frac{M^2}{4} + \frac{(s-1)(M)}{2} \right|_{m_i}$$

(2.7)

From examining equations 2.5, 2.6 and 2.7, it follows that:

- 1.  $1 \le i \le n$  and  $m_i$  is odd: No correction factor is necessary.

- 2.  $1 \le i \le n$  and  $m_i$  is even: The correction factor can be effected by computing s = a + b and then subtracting LUT(s) from the result of the multiplier.

- 3.  $n+1 \le i \le n+r$ : The correction factor can be effected by computing s = a+band then subtracting LUT(s) from the result of the multiplier.

The addition and subtraction operations' correction factors require a single, constant addition/subtraction operation, whereas for multiplication, 2 additions/subtractions and a modest table lookup are required. Another advantage of the schemes presented here is that sign determination is not necessary and that they can be performed at the subcore level, without the involvement of the Residue Interaction Unit (RIU).

#### 2.6 Overflow Detection

#### 2.6.1 Unsigned Number Overflow Detection

In the absence of any error or overflow, adding 2 unsigned RRNS numbers results in both  $\Delta m_5$  and  $\Delta m_6$  being zero. As has been just explained, the presence of an error is handled by the error correction table. In the absence of error, it could be observed that any overflow manifests itself as a fixed index into the error correction table, with the entry not corresponding to any error. Table 2.2 provides some examples of this observation. While the computation of the deltas is most efficient using a base-extension algorithm, the Chinese Remainder Theorem(CRT) method is used to first convert the RRNS number to a binary number before computing the delta\_value\_pair. This is solely for explanatory purposes; binary conversion is not actually necessary to detect overflow.

By iterating through all possible combinations of numbers and operations, it can be observed that the delta\_value\_pair ( $\Delta m_5$ ,  $\Delta m_6$ ) of overflow is fixed. Moreover, ( $\Delta m_5$ ,  $\Delta m_6$ ) = (10,11) is not a legitimate address of the error correction table (Table 2.1), thus enabling a distinction between an error and an overflow. This approach, however, does

| X+Y     | X RRNS        | Y RRNS        | X+Y RRNS      | CRT/MRC                         | $ X' m_5,  X' m_6$                            | $\Delta m_5, \Delta m_6$ |

|---------|---------------|---------------|---------------|---------------------------------|-----------------------------------------------|--------------------------|

| 2+209   | (2,2,0,2,2,2) | (2,4,1,6,0,1) | (1,1,1,1,2,3) | $(1,1,1,1) \Leftrightarrow 1$   | $ 1 _{11}=1,  1 _{13}=1$                      | 10 11                    |

| 3+209   | (0,3,1,3,3,3) | (2,4,1,6,0,1) | (2,2,0,2,3,4) | $(2,2,0,2) \Leftrightarrow 2$   | $ 2 _{11}=2,  2 _{13}=2$                      | 10 11                    |

|         |               |               |               | •••                             |                                               | 10 11                    |

| 209+209 | (2,4,1,6,0,1) | (2,4,1,6,0,1) | (1,3,0,5,0,2) | $(1,3,0,5) \Leftrightarrow 208$ | 208  <sub>11</sub> =10, 208  <sub>13</sub> =0 | 10 11                    |

Table 2.2: Unsigned Number Overflow Examples in RRNS with Moduli (3,5,2,7,11,13)

Table 2.3: Excess- $\frac{M}{2}$  Overflow Examples for addition of two positive numbers in RRNS with Moduli (3,5,2,7,11,13)

| X+Y   | X RRNS        | Y RRNS        | X+Y RRNS      | Add Correction Factors | CRT/MRC                       | $ X' m_5,  X' m_6$                       | $\Delta m_5, \Delta m_6$ |

|-------|---------------|---------------|---------------|------------------------|-------------------------------|------------------------------------------|--------------------------|

| 1+104 | (1,1,0,1,7,2) | (2,4,1,6,0,1) | (0,0,1,0,7,3) | (0,0,0,0,1,2)          | $(0,0,0,0) \Leftrightarrow 0$ | 0  <sub>11</sub> =0, 0  <sub>13</sub> =0 | 10 11                    |

| 2+104 | (2,2,1,2,8,3) | (2,4,1,6,0,1) | (1,1,0,1,8,4) | (1,1,1,1,2,3)          | $(1,1,1,1) \Leftrightarrow 1$ | $ 1 _{11}=1,  1 _{13}=1$                 | 10 11                    |

|       |               |               |               |                        |                               |                                          | 10 11                    |

not apply to multiplication.

#### 2.6.2 Signed Number Overflow Detection

Recall from Section 2.4 that the Excess- $\frac{M}{2}$  signed representation is used. There are two independent scenarios of overflow:

- 1. Two positive numbers addition Table 2.3 provides a few examples illustrating the algorithm (Correction factors are explained in detail in Section 2.5). The 1 + 104 in the first column is represented in decimal. After Excess- $\frac{M}{2}$  mapping, the computing equation is transformed to 106 + 209 since  $\frac{M}{2} = 105$  for the toy set of moduli. Therefore, the X RRNS value is the the RRNS of 106 and Y RRNS value is the RRNS of 209. We observe that the delta\_value\_pair ( $\Delta m_5, \Delta m_6$ ) remains at a fixed value (10,11).

- 2. Two negative numbers addition Similarly, examples for adding two negative numbers are shown in Table 2.4. In this case, we can observe that the delta\_value\_pair  $(\Delta m_5, \Delta m_6)$  is fixed to (1,2).

Note that neither (10, 11) nor (1, 2) is a legitimate entry index of Table 2.1, thereby enabling a distinction between an error and an overflow. However, while this method works for both addition and subtraction, it does not hold for detection of multiplication overflow as the

Table 2.4: Excess- $\frac{M}{2}$  Overflow Examples for addition of two negative numbers in RRNS with Moduli (3,5,2,7,11,13)

| X+Y    | X RRNS         | Y RRNS        | X+Y RRNS       | Add Correction Factors | CRT/MRC                            | $ X' m_5,  X' m_6$                            | $\Delta m_5, \Delta m_6$ |

|--------|----------------|---------------|----------------|------------------------|------------------------------------|-----------------------------------------------|--------------------------|

| -1-105 | (2,4,0,6,5,0)  | (0,0,0,0,0,0) | (2,4,0,6,5,0)  | (2,4,1,6,10,12)        | $(2, 4, 1, 6) \Leftrightarrow 209$ | 209 11=0,209 13=1                             | 12                       |

| -3-104 | (0,2,0,4,3,11) | (1,1,1,1,1,1) | (1,3,1,5,4,12) | (1,3,0,5,9,11)         | $(1,3,0,5) \Leftrightarrow 208$    | 208  <sub>11</sub> =10, 208  <sub>13</sub> =0 | 12                       |

|        |                |               |                |                        |                                    |                                               | 12                       |

Figure 2.5: One error detection and correction algorithm with overflow/underflow detection

delta-pair is not constant and sometimes indexes into a legal error correction table entry.

Figure 2.5 shows the overview of One error detection and correction algorithm with overflow/underflow detection.

It can be observed that the described algorithm works in a similar manner even with the base sets that meet particular requirements. E.g. Waston's bases (199,233,194,239,251,509), an overflow results in a delta-pair of (77, 289), whereas an underflow results in (174, 220). Both these pairs do not index into legitimate entries of the error correction table for these set of bases (*cf.* Appendix E, Watson [25]).

# 2.7 Comparison

Comparison is an essential operation because it may use in determining the direction of the control flow. In a manner similar to overflow detection, the potential algorithms are explored to perform RRNS comparison without incurring unnecessary hardware overhead.

Jen-shiun et al. [37] and Omondi [32] proposed number comparison methods for residue numbers based on parity bits. However, a prerequisite of these parity comparison methods is that all moduli are supposed to be odd (in addition to being pair-wise relatively prime). In some other systems, one of the non-redundant moduli is even (to enable fast fractional multiplication [25]), therefore this approach is not suitable in these scenarios.

Instead, this scheme leverages the error check algorithm itself to check for an overflow post a subtraction: to compare X and Y, perform X-Y and derive the delta\_value\_pair  $(\Delta m_5, \Delta m_6)$ . Then,  $X \ge Y$  iff the delta\_value\_pair is (0, 0) (*i.e.*, no overflow) and X < Y iff the delta\_value\_pair is (174, 220) (*i.e.*, X - Y results in an underflow).

This new residue number comparison method can be used for both unsigned and Excess- $\frac{M}{2}$  signed numbers. It is straightforward that this idea is suitable for unsigned residue numbers: if X < Y, then  $X - Y \notin [0, M)$ , thereby resulting in an underflow. For an Excess- $\frac{M}{2}$  signed number X, an injective mapped residue number can be defined as follows:  $X_{mapped} = \frac{M}{2} + X$ . Therefore,  $X \ge Y$  iff  $X_{mapped} \ge Y_{mapped}$ , which reduces to an unsigned comparison. A caveat to note is that correction factors should not be added for a comparison operation. These are summarized in Figures 2.6a and 2.6b. In summary, this RRNS comparison is performed via combining a simple subtraction with error checking. If a comparison instruction is followed by an error checking instruction, this comparison could be replaced with a subtraction. From another aspect, by executing this comparing algorithm, a free error checking can be achieved on the corresponding data.

Figure 2.6: Signed Overflow Detection and Comparison

# 2.8 Optimized Multiplier Unit Design

Many workloads in the domains of multimedia, image processing and digital signal processing are highly multiplication intensive [38]. Index-sum multiplication [39, 40] was proposed and its principle is analogous to using a *logarithm* operation, *i.e.*, a multiplication can be achieved via a table lookup, addition and a reverse table lookup, as summarized as follows for the product of two numbers X and Y:

- 1. Use a pre-defined mapping table to generate index(X) and index(Y).

- 2. Compute the sum Z = index(X) + index(Y).

- 3. Use a pre-defined reverse mapping table to return the product XY as  $reverse\_index(Z)$ .

If the computing data is 32-bit, the sizes of mapping tables are huge and need high area and hardware overhead. RNS can significantly reduce the table size by separating the data bit-width [39, 40]. This idea is extended into RRNS by adjusting the RRNS bases (*cf. Section* 2.9) to be amenable to index-sum LUTs, the requirements for which, are summarized below.

Index-sum multiplication is based on the theory of Galois fields, which can be classified into 3 types: GF(p),  $GF(p^m)$  and  $GF(2^m)$ , where, p is an odd prime number and  $m \in \mathbb{Z}^+$ . The range of integers that can be represented bijectively in Galois fields, and the encoding methodology depends on the GF type[40]: (The methodology of deriving  $GF(p^m)$  is skipped as these microarchitectures do not utilize this.)