# OVERCOMING NOISE AND VARIATIONS IN LOW-PRECISION NEURAL NETWORKS

A Dissertation Presented to The Academic Faculty

By

Devon D. Janke

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

Georgia Institute of Technology

August 2021

Copyright © Devon D. Janke 2021

# OVERCOMING NOISE AND VARIATIONS IN LOW-PRECISION NEURAL NETWORKS

Approved by:

Dr. David Anderson, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Arijit Raychowdhury School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Aaron Lanterman School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Shaolan Li School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Hyesoon Kim School of Computer Science *Georgia Institute of Technology*

Date Approved: May 6, 2021

Any intelligent fool can make things bigger and more complex. It takes a touch of genius — and a lot of courage — to move in the opposite direction.

E. F. Schumacher

I dedicate this dissertation to my wife, Natalee. I would never have made it to where I am nor become who I am now without your constant, patient support. Thank you for being my greatest catalyst for growth.

#### ACKNOWLEDGEMENTS

I cannot begin to give thanks for those who supported my success without first acknowledging the earnestness to learn and succeed that my parents planted in me at an early age. They gave so much time and energy to my education and helped me to get on this path.

Nance Ericson gave me my first internship at Oak Ridge National Labs, where he showed me a variety of exciting projects that were available in the world of research. It was because of the hours he spent personally mentoring me and being my friend that I was able to really appreciate the importance of what I was learning and how crucial it was for me to thoroughly understand and internalize each principle.

I had my first independent research project under Shiuh-hua Chiang at Brigham Young University, Provo. The trust he placed in me to work and succeed taught me that I am capable and creative enough to contribute to the state of the art. He pushed me to apply for more prestigious graduate schools than I ever would have considered. I never would have submitted my application to Georgia Tech without his guidance.

A large part of my discovery for my current passions came through trial and error, and the time spent doing research with Dr. Ayazi and Dr. Rincon-Mora were a big part of that. They encouraged me to broaden my horizons of my interests and taught me how to begin a thorough research project and develop an intuition for technical material.

Andy Smith and the guys in "group" were crucial to my personal development. I will never forget the hundreds of hours they gave to helping me discover and redefine the way I view myself. I do not believe I would have successfully completed my doctorate without following the encouragement from my wife to seek counsel from Andy to begin this path of change.

I must also acknowledge my committee and the time they gave up from their own research to check my work, ask questions, and provide feedback. A special thanks to Arijit Raychowdhury for meeting with me personally as I begin my work on this topic.

v

I am very grateful to Tom Darbonne for trusting me with this fascinating research topic and for the opportunities you gave me for professional growth. Tom gave a wealth of time to me in one-on-one mentoring as I navigated the realm of entrepreneurialism as a complete novice.

Of course, I cannot neglect to give my gratitude to David Anderson. David was very supportive of me exploring this field despite needing to learn from the very basics of machine learning and provided all the support I needed while pushing me to be creative and self-sufficient in my research. His academic, professional, and personal guidance are invaluable and helped drive me to finish successfully.

### TABLE OF CONTENTS

| Acknov    | vledgmo  | ents                                       |

|-----------|----------|--------------------------------------------|

| List of ' | Tables   | xi                                         |

| List of ] | Figures  | xii                                        |

| Introdu   | iction   |                                            |

| Chapte    | r 1: Int | elligent Sensor Processing 1               |

| 1.1       | Sensor   | rs on the Edge                             |

| 1.2       | Machi    | ne Learning and Neural Networks            |

|           | 1.2.1    | Neural networks                            |

|           | 1.2.2    | Common layer types                         |

|           | 1.2.3    | Activation functions                       |

| 1.3       | Genera   | al Overview of Machine Learning Algorithms |

|           | 1.3.1    | Data Preprocessing                         |

|           | 1.3.2    | Forward Propagation                        |

|           | 1.3.3    | Loss Function                              |

|           | 1.3.4    | Backpropagation                            |

|           | 1.3.5    | Parameter Update                           |

| 1.4     | Mini-b   | atch Training: Redundant Training Sets                 | 11 |

|---------|----------|--------------------------------------------------------|----|

| Chapter | : 2: Imj | plementing Neural Networks                             | 15 |

| 2.1     | Digital  | Implementation                                         | 15 |

|         | 2.1.1    | Binary Arithmetic                                      | 16 |

| 2.2     | Poweri   | ng Down                                                | 19 |

| 2.3     | Analog   | g Hardware                                             | 22 |

|         | 2.3.1    | Arithmetic blocks                                      | 22 |

|         | 2.3.2    | Limitations                                            | 25 |

| 2.4     | Introdu  | acing Analog Into Machine Learning and Neural Networks | 27 |

|         | 2.4.1    | Full Replacement                                       | 28 |

|         | 2.4.2    | Computation Acceleration                               | 29 |

|         | 2.4.3    | Deployment                                             | 30 |

| 2.5     | Trainir  | g-to-Deployment Translation                            | 31 |

| 2.6     | Modeli   | ing PVT in Analog Neural Networks                      | 33 |

| Chapter | : 3: Gei | neralizing and Fitting                                 | 36 |

| 3.1     | Improv   | ving Generalization                                    | 38 |

|         | 3.1.1    | Dropout Training                                       | 38 |

|         | 3.1.2    | Data Augmentation                                      | 39 |

|         | 3.1.3    | Early Stopping                                         | 40 |

|         | 3.1.4    | Weight Regularization                                  | 40 |

| 3.2     | Device   | Fitting                                                | 41 |

|         | 3.2.1    | Understanding the Problem                              | 42 |

|        | 3.2.2    | Breaking from Traditional Techniques                 | 42 |

|--------|----------|------------------------------------------------------|----|

| 3.3    | Popula   | tion Training                                        | 43 |

| Chapte | r 4: Bui | ilding robustness into the network                   | 47 |

| 4.1    | Selecti  | ng a better activation function                      | 48 |

| 4.2    | Effects  | s of the Network Shape                               | 51 |

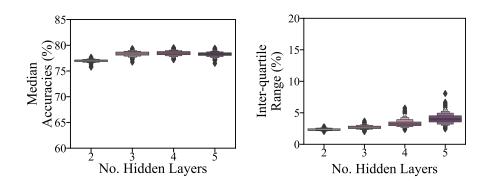

|        | 4.2.1    | Effect of depth                                      | 51 |

|        | 4.2.2    | Effect of layer sizes                                | 53 |

|        | 4.2.3    | Conclusion: best parameters for variation resilience | 55 |

| 4.3    | Sparse   | network connections                                  | 57 |

| Chapte | r 5: Ger | nerating the Best Sparse Networks                    | 63 |

| 5.1    | Genetic  | c Programming                                        | 63 |

| 5.2    | Synapt   | ic Pruning                                           | 65 |

|        | 5.2.1    | One-time pruning                                     | 66 |

|        | 5.2.2    | Gradual Pruning                                      | 69 |

|        | 5.2.3    | Repeated full pruning                                | 72 |

| 5.3    | Again,   | But With More Parameters                             | 75 |

| Chapte | r 6: Fut | ure Work                                             | 80 |

| 6.1    | Better   | Modeling                                             | 80 |

| 6.2    | Improv   | ving the Sparse Network Search                       | 80 |

| 6.3    | Low-po   | ower Binary Multiplication: Bit Shift                | 81 |

|        | 6.3.1    | Quantization Error                                   | 83 |

| 6                                                                | 3.2 Training for One-Hot Quantization             | . 87  |  |  |

|------------------------------------------------------------------|---------------------------------------------------|-------|--|--|

| 6                                                                | 3.3 N-Hot Quantization                            | . 88  |  |  |

| Chapter 7                                                        | Conclusion                                        | . 90  |  |  |

| Appendix                                                         | A: Datasets                                       | . 94  |  |  |

| A.1 C                                                            | ustom Voice Activity and Noise Dataset            | . 94  |  |  |

| A.2 N                                                            | licrosoft Deep Noise Suppression (MDNS) Challenge | . 95  |  |  |

| A.3 T                                                            | he Wisconsin Breast Cancer Dataset                | . 95  |  |  |

| A.4 E                                                            | lectrical Grid Stability Dataset                  | . 95  |  |  |

| A.5 N                                                            | INIST                                             | . 95  |  |  |

| <b>Appendix B: Voice Activity Detection — Feature Extraction</b> |                                                   |       |  |  |

| Appendix C: Modeling Feature Noise                               |                                                   |       |  |  |

| Reference                                                        | s                                                 | . 111 |  |  |

## LIST OF TABLES

| 4.1 | Neural Network Layers and Sizes Used In Comparing Activation Functions | 51 |

|-----|------------------------------------------------------------------------|----|

| 4.2 | Activation Functions Compared and Their Associated Equations           | 51 |

| 5.1 | Neural Network Layers and Sizes Used In Sparsity Analysis              | 66 |

### LIST OF FIGURES

| 1.1 | Illustration of neuron/synapse connectivity in human brain                                                                                           | 4  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Block diagrams for a single artificial neuron and a MLP                                                                                              | 4  |

| 1.3 | Depictions of convolutional and recurrent layers of neural networks                                                                                  | 6  |

| 1.4 | Three common activation functions used in nonlinear neural networks                                                                                  | 8  |

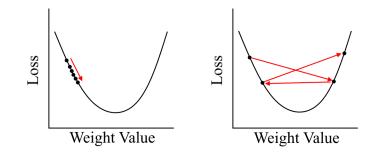

| 1.5 | Consequences of using a learning rate that is too small (left) or too large (right)                                                                  | 11 |

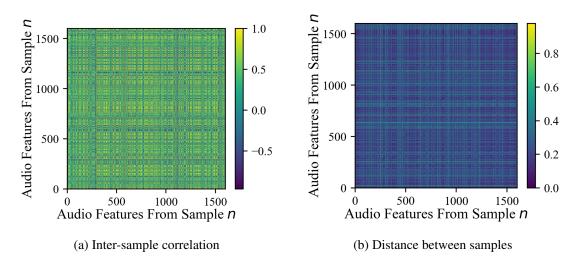

| 1.6 | Color map plots showing how many of the samples used for training closely resemble one another, both in terms of correlation and euclidean distance. | 12 |

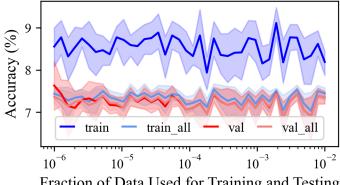

| 1.7 | Plot showing how repetition in data does not justify randomly selecting a subset to use for training                                                 | 13 |

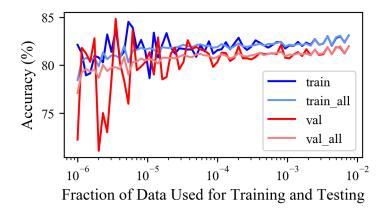

| 1.8 | Plot showing the effectiveness of mini-batch optimization in machine learning                                                                        | 14 |

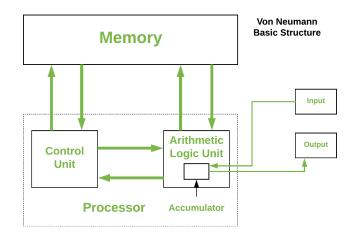

| 2.1 | Diagram of the basic Von Neumann architecture                                                                                                        | 16 |

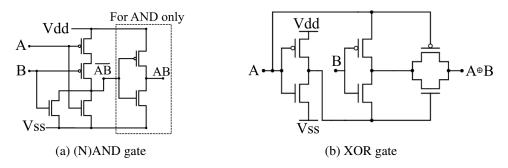

| 2.2 | Transistor diagrams for (N)AND and XOR binary logic gates                                                                                            | 16 |

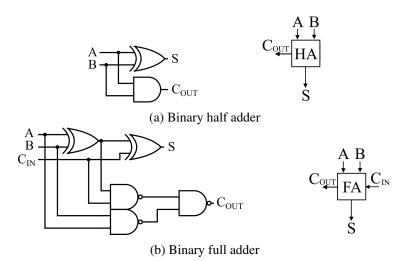

| 2.3 | Gate- and block-level diagrams for the binary half and full adders                                                                                   | 17 |

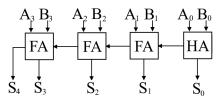

| 2.4 | Example of binary addition and ripple adder architecture                                                                                             | 17 |

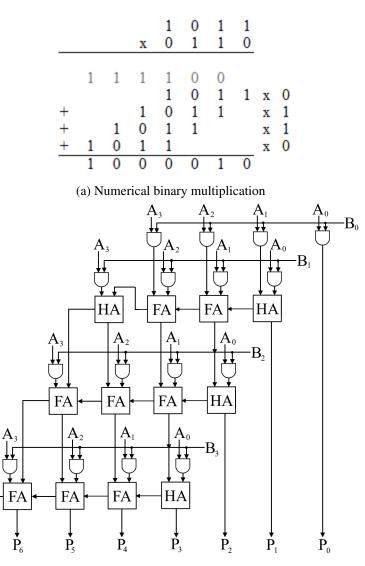

| 2.5 | Example of binary multiplication and ripple-adder-based multiplier architec-<br>ture                                                                 | 19 |

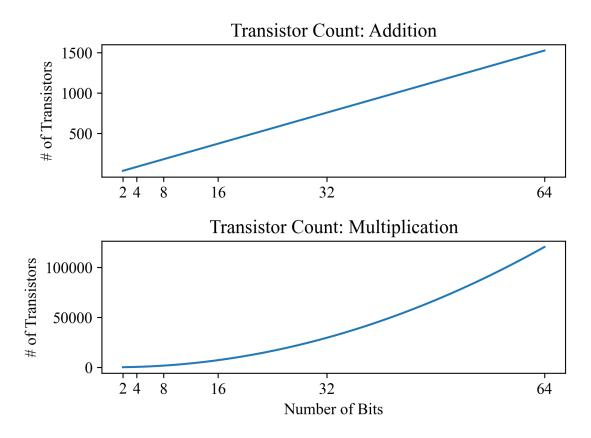

| 2.6 | Plots showing the relationship between transistor count and binary number bit length.                                                                | 20 |

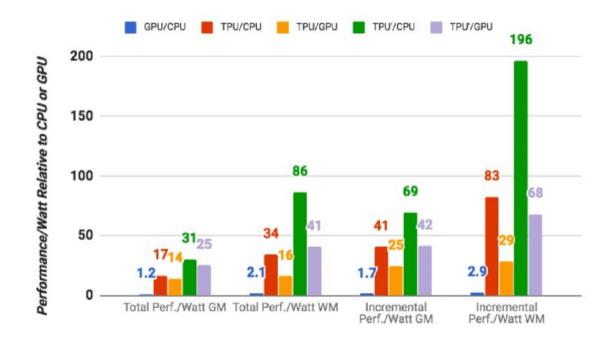

| 2.7 | Plot illustrating the relative performance per power for GPUs and TPUs in relation to CPUs.                                                          | 22 |

| 2.8  | Block and transistor diagrams for components in analog multipliers                                                                                                                                    | 23 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.9  | Kirchoff's Current Law and an OpAmp voltage adder                                                                                                                                                     | 24 |

| 2.10 | Three simple architectures that can act as (a) an artificial neuron and (b) a complete fully-connected layer in a neural network.                                                                     | 25 |

| 2.11 | Examples of nonlinear phenomena in analog multipliers                                                                                                                                                 | 26 |

| 2.12 | CMOS floating gate transistor                                                                                                                                                                         | 27 |

| 2.13 | Illustration of how the noise vectors transform one network into many variations                                                                                                                      | 35 |

| 3.1  | Examples of edge-case images that may be misclassified                                                                                                                                                | 37 |

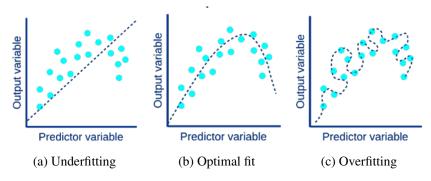

| 3.2  | Illustrations of the concept of fitting a function to the data.                                                                                                                                       | 37 |

| 3.3  | An example of how connections may be disabled for dropout training                                                                                                                                    | 39 |

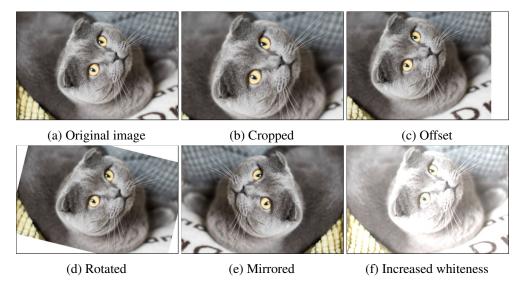

| 3.4  | Figures demonstrating how a single image can become six different examples in a training set by applying simple alterations.                                                                          | 39 |

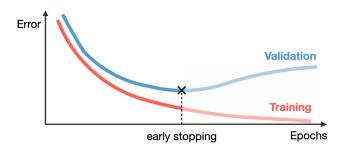

| 3.5  | Visualization of the early-stop point in relation to the validation and training loss as a function of number of epochs trained                                                                       | 40 |

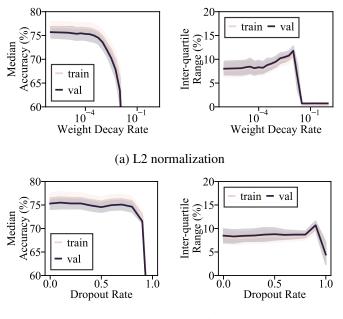

| 3.6  | Effects of (a) L2 normalization and (b) dropout training on device overfitting.                                                                                                                       | 43 |

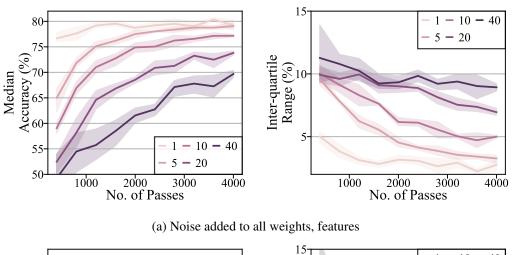

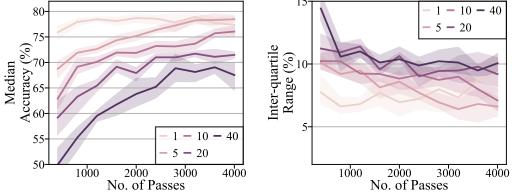

| 3.7  | Performance of population training with gradients averaged. The colors represent different numbers of noised networks that are trained in parallel, with darker lines using more devices in parallel. | 45 |

| 3.8  | Performance of population training with gradients summed                                                                                                                                              | 46 |

| 3.9  | Performance of population training with summed gradients and learning rate proportional to $\sqrt{p}$ .                                                                                               | 46 |

| 4.1  | Activation functions and some of their derivatives                                                                                                                                                    | 49 |

| 4.2  | Difference in performance variation when using similar activation functions but with different slopes                                                                                                 | 50 |

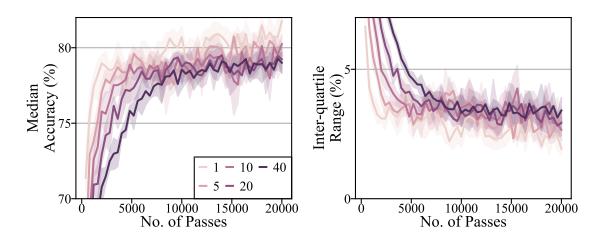

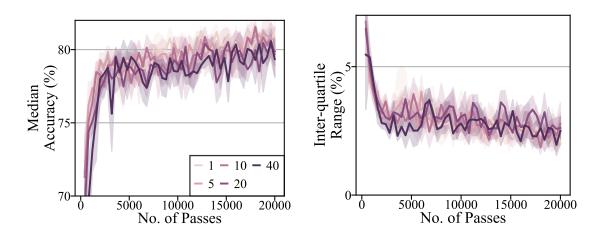

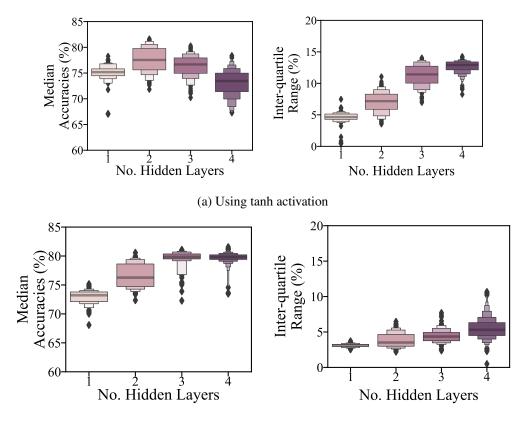

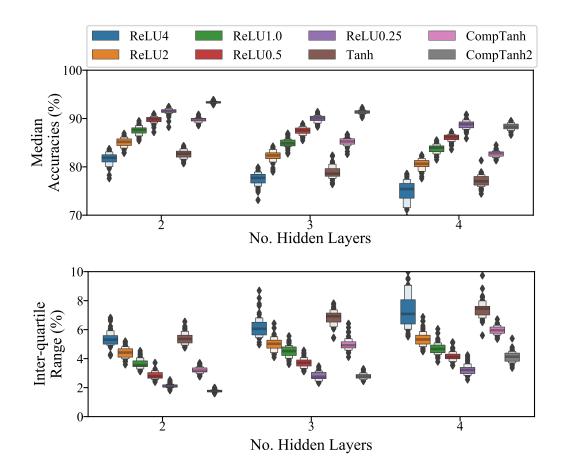

| 4.3  | Comparison of activation functions including ReLU with a variety of slopes                                                                                                                            | 52 |

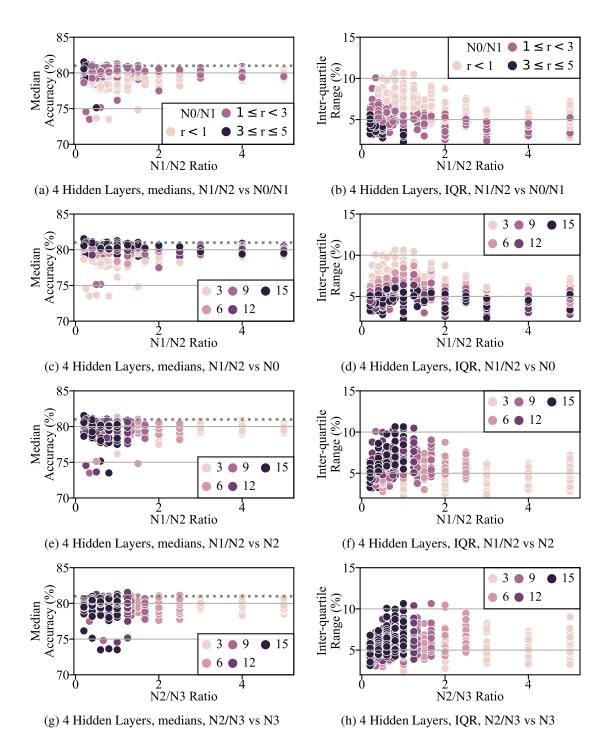

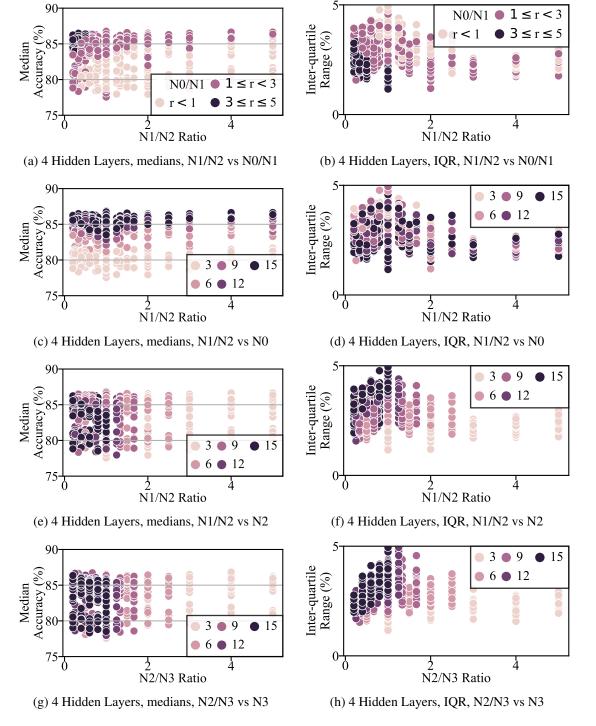

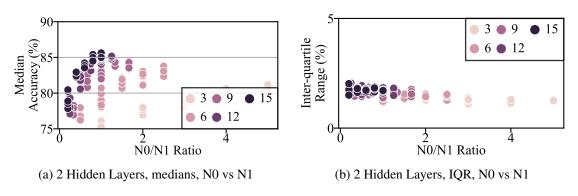

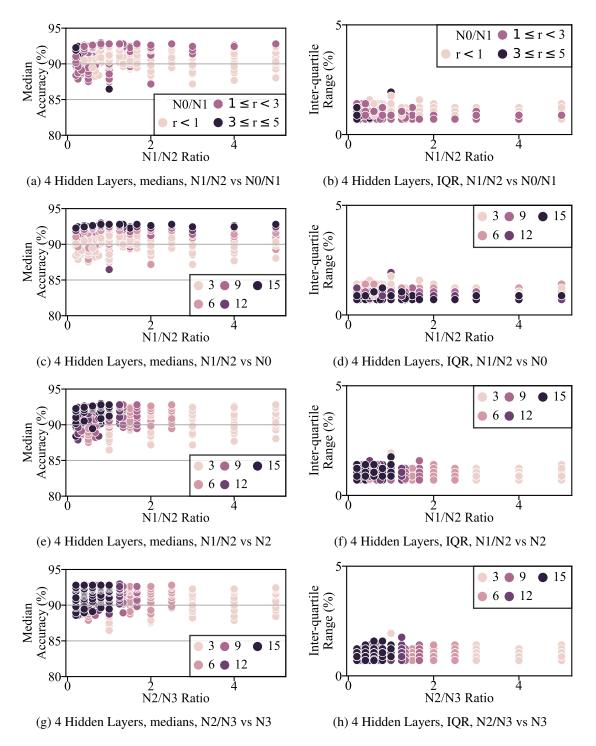

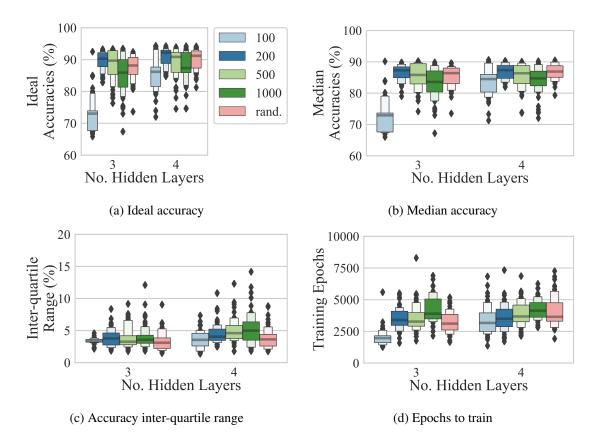

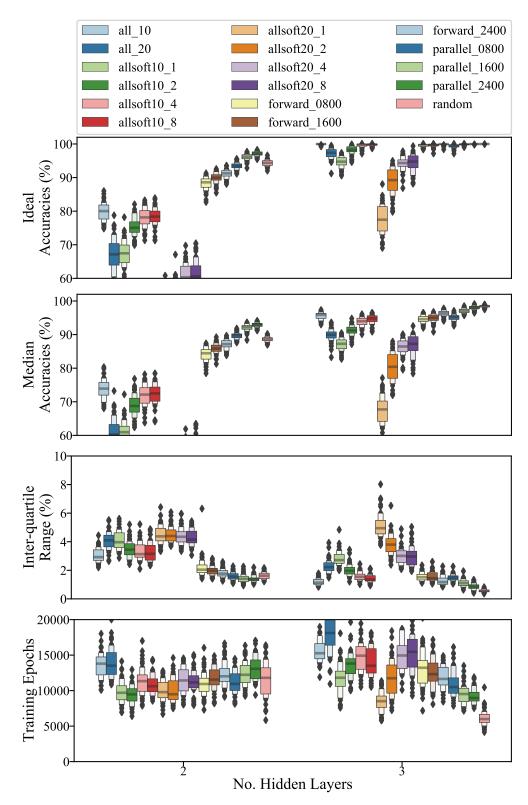

| 4.4  | Plots demonstrating the relationship of various network layer sizes affects the median and IQR of the network accuracies when subjected to variations. The networks represented here have four hidden layers.                                                              | 54 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

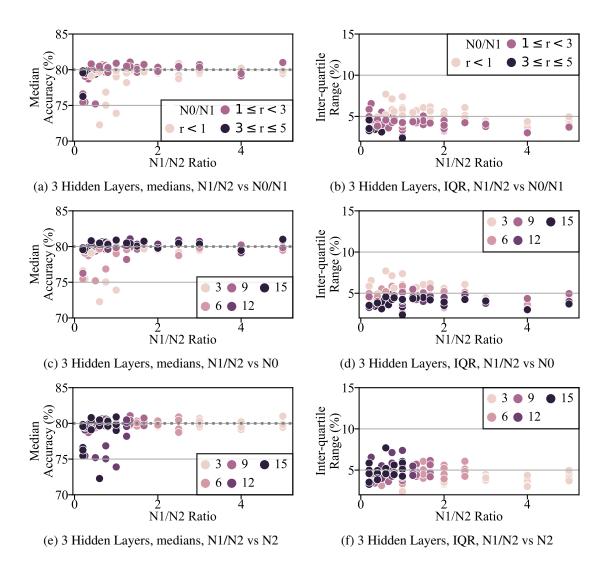

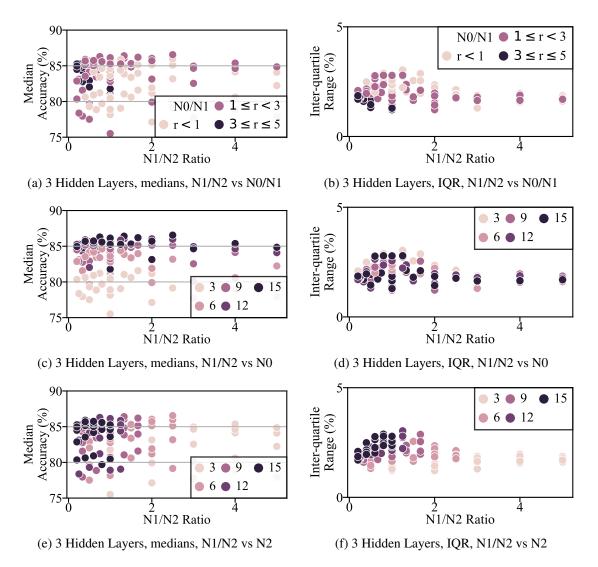

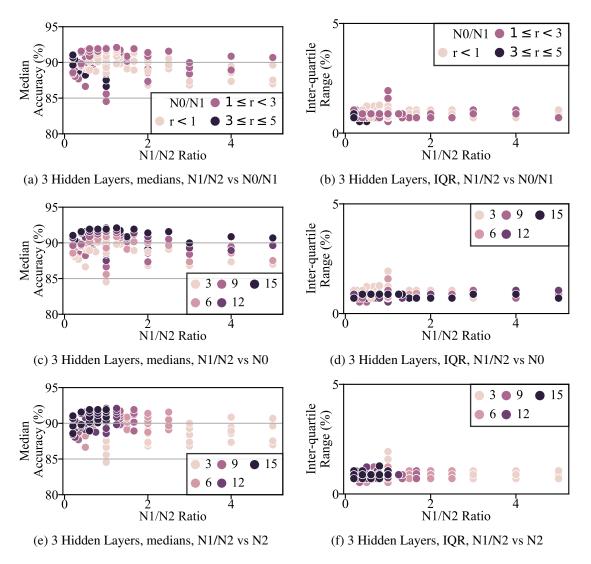

| 4.5  | Plots demonstrating the relationship of various network layer sizes affects the median and IQR of the network accuracies when subjected to variations. The networks represented here have three hidden layers                                                              | 56 |

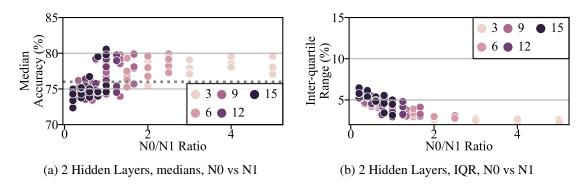

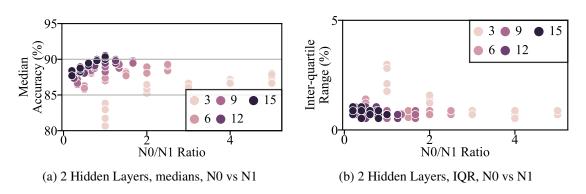

| 4.6  | Plots demonstrating the relationship of various network layer sizes affects the median and IQR of the network accuracies when subjected to variations. The networks represented here have two hidden layers.                                                               | 56 |

| 4.7  | Demonstration of how introducing sparsity to a neural network serves to reduce the effects of variations in the neural network parameters when trained and tested under the same conditions as those in Fig. 4.2b                                                          | 58 |

| 4.8  | Plots demonstrating the relationship of various network layer sizes affects the median and IQR of the network accuracies when subjected to variations. The networks represented here have four hidden layers, and the Electrical Grid Stability dataset is used            | 59 |

| 4.9  | Plots demonstrating the relationship of various network layer sizes affects<br>the median and IQR of the network accuracies when subjected to variations.<br>The networks represented here have three hidden layers, and the Electrical<br>Grid Stability dataset is used. | 60 |

| 4.10 | Plots demonstrating the relationship of various network layer sizes affects<br>the median and IQR of the network accuracies when subjected to variations.<br>The networks represented here have two hidden layers, and the Electrical<br>Grid Stability dataset is used.   | 60 |

| 4.11 | Plots demonstrating the relationship of various network layer sizes affects the median and IQR of the network accuracies when subjected to variations. The networks represented here have four hidden layers, and the Wisconsin Breast Cancer dataset is used              | 61 |

| 4.12 | Plots demonstrating the relationship of various network layer sizes affects the median and IQR of the network accuracies when subjected to variations. The networks represented here have three hidden layers, and the Wisconsin Breast Cancer dataset is used             | 62 |

| 4.13 | Plots demonstrating the relationship of various network layer sizes affects<br>the median and IQR of the network accuracies when subjected to variations.<br>The networks represented here have two hidden layers, and the Wisconsin<br>Breast Cancer dataset is used      | 62 |

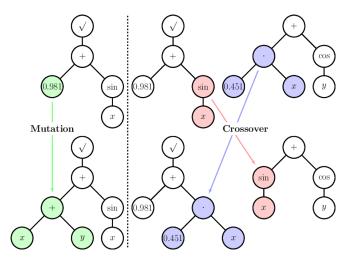

| 5.1 | Illustration of mutation and crossover in genetic programming                                                                                                                                                             | 64 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

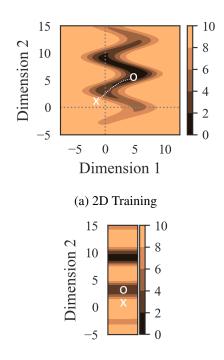

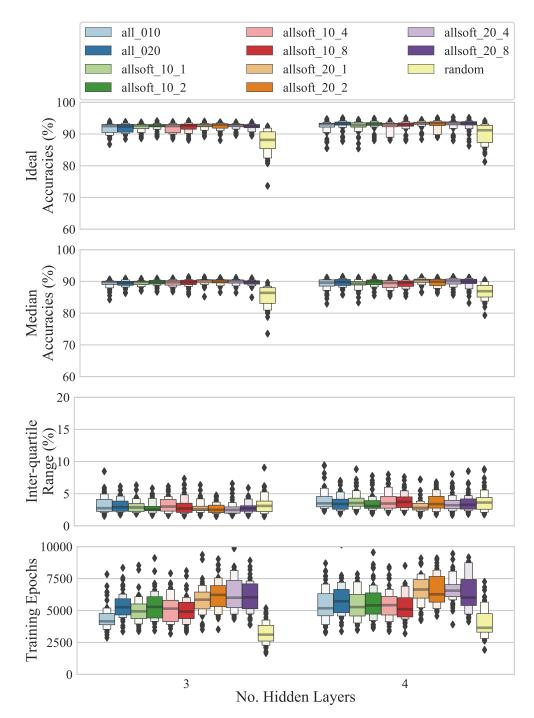

| 5.2 | Plots showing how differing methods of weight initialization for training sparse neural networks may affect the training of the final neural network .                                                                    | 67 |

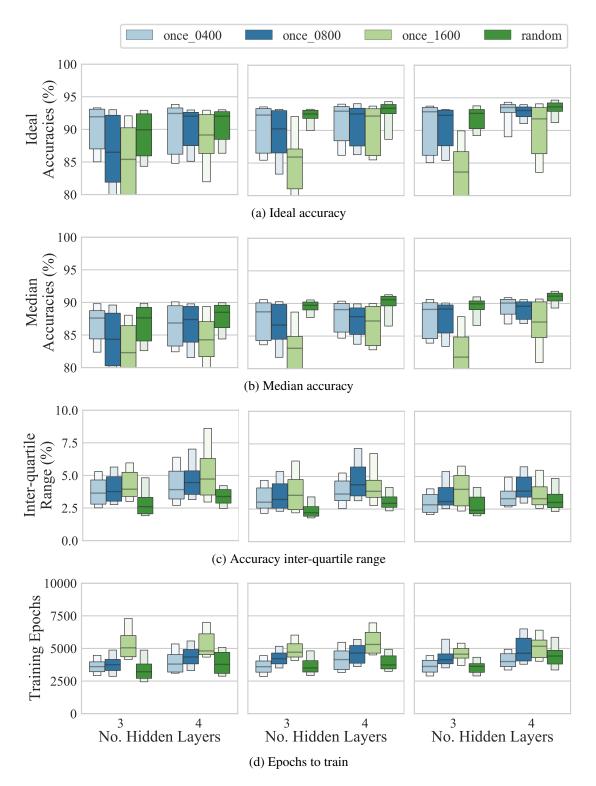

| 5.3 | Results of using the "prune once" technique to generate sparse neural networks                                                                                                                                            | 68 |

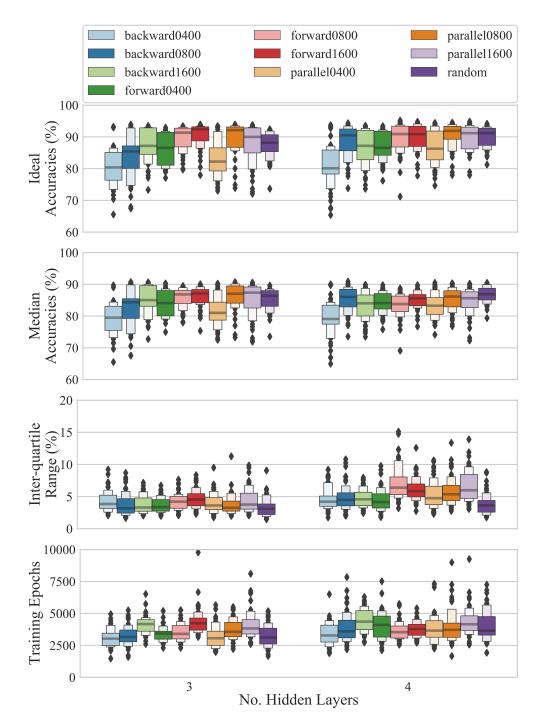

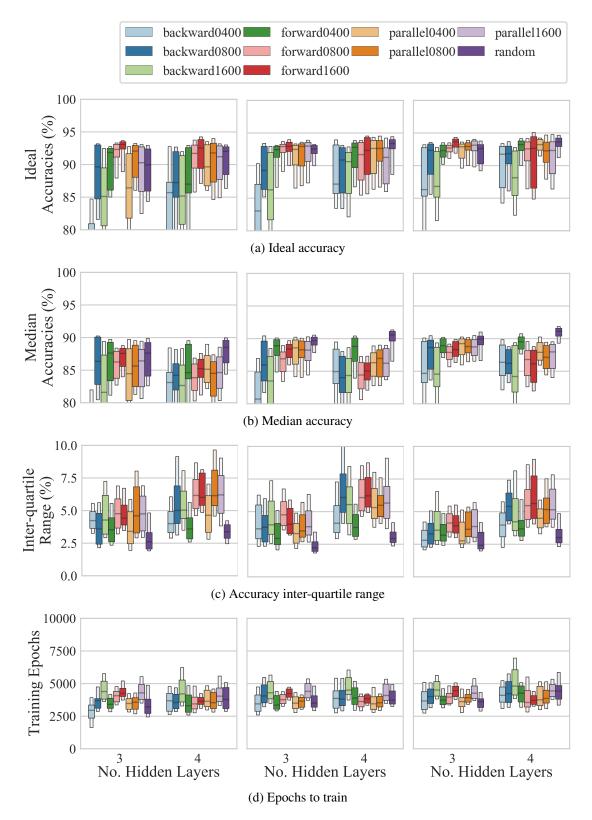

| 5.4 | Results of using gradual pruning to introduce sparsity into a neural network                                                                                                                                              | 70 |

| 5.5 | Results of using repeated full pruning to introduce sparsity into a neural network                                                                                                                                        | 74 |

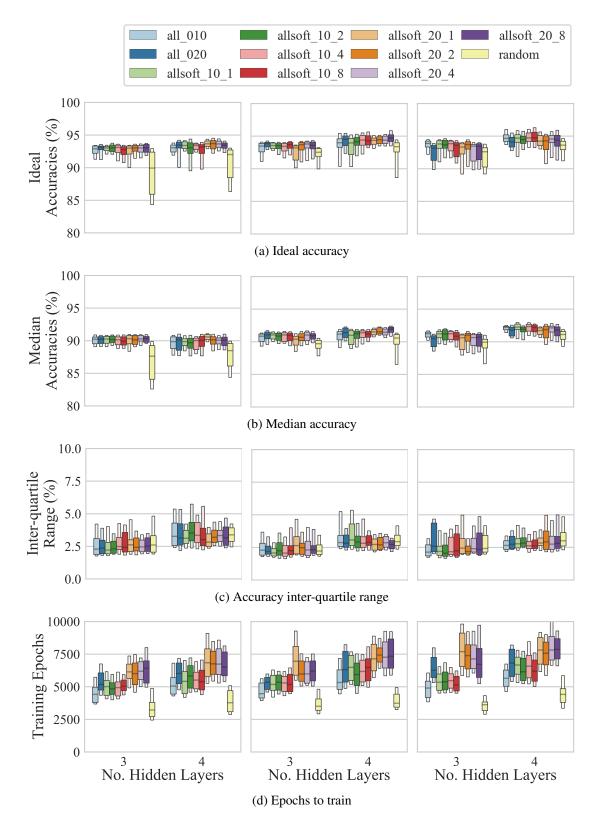

| 5.6 | Results for repeated full pruning methods when starting out with larger hidden layers with 12, 20, and 30 neurons per layer                                                                                               | 77 |

| 5.7 | Results for gradual pruning methods when starting out with larger hidden layers with 12, 20, and 30 neurons per layer                                                                                                     | 78 |

| 5.8 | Results for repeated full pruning methods when starting out with larger hidden layers with 12, 20, and 30 neurons per layer                                                                                               | 79 |

| 6.1 | Pruning methods using larger neural networks with a subset of the MNIST dataset.                                                                                                                                          | 82 |

| 6.2 | Example of multiplying a number by $4 = 2^2$ , which is the same as a shifting all bits to the left (or "decimal point" to the right) two positions                                                                       | 83 |

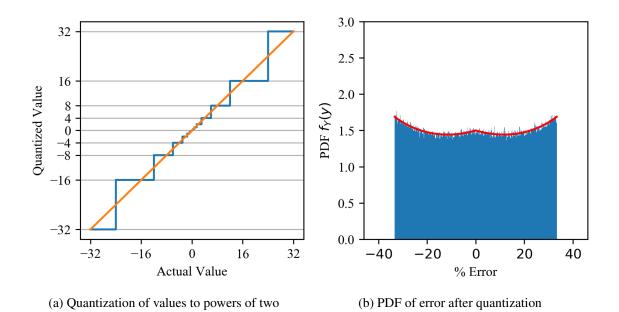

| 6.3 | Plot showing how the full-precision values between $-32$ and $32$ are quantized down to one-hot form (closest power of two). Histogram of the resulting errors when comparing the original value to the quantized value . | 86 |

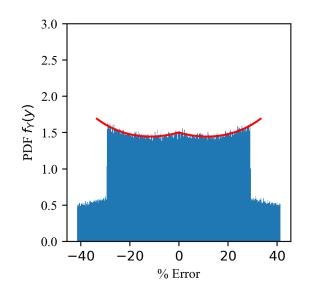

| 6.4 | Histogram of quantization error when using equation (6.7)                                                                                                                                                                 | 86 |

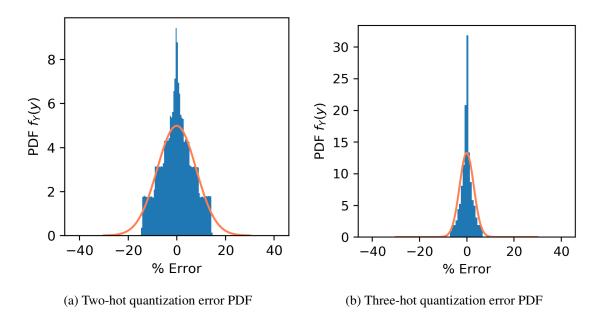

| 6.5 | Plots showing the histograms of quantization errors for two- and three-hot quantization                                                                                                                                   | 89 |

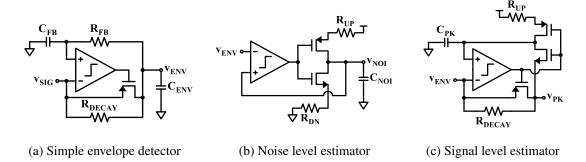

| B.1 | Example schematics for possible implementations of the signal and noise level estimators used in feature detection.                                                                                                       | 97 |

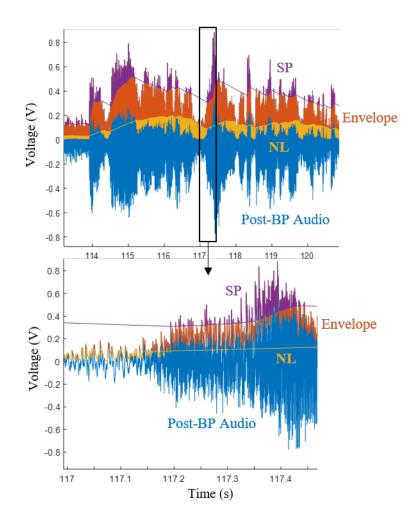

| B.2 | Example signals generated by the circuits in Fig. B.1.                                                                                                                                                                    | 98 |

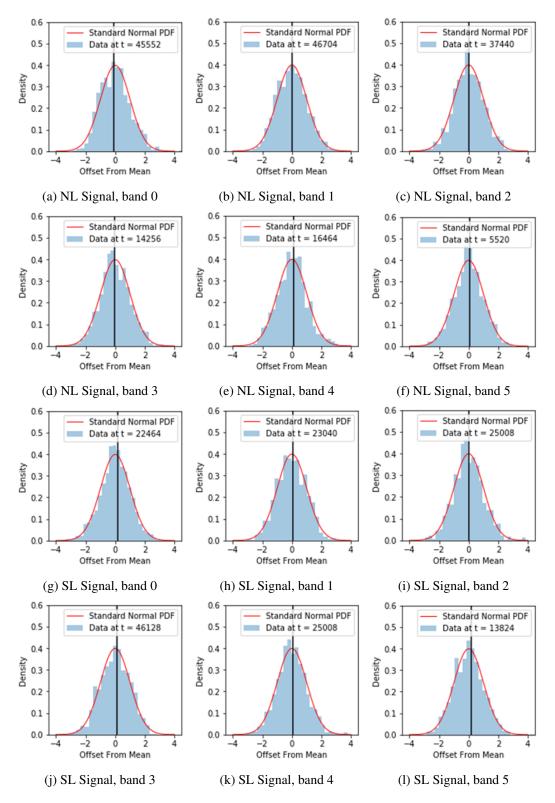

| C.1 | Plots demonstrating the gaussian nature of the features extracted when<br>subjected to gaussian noise added to various parameters. The vertical black<br>line is the ideal value, and t is the number of samples from the start of the<br>audio (at 16kSps). The time shown is randomly selected from the given<br>sample and feature |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

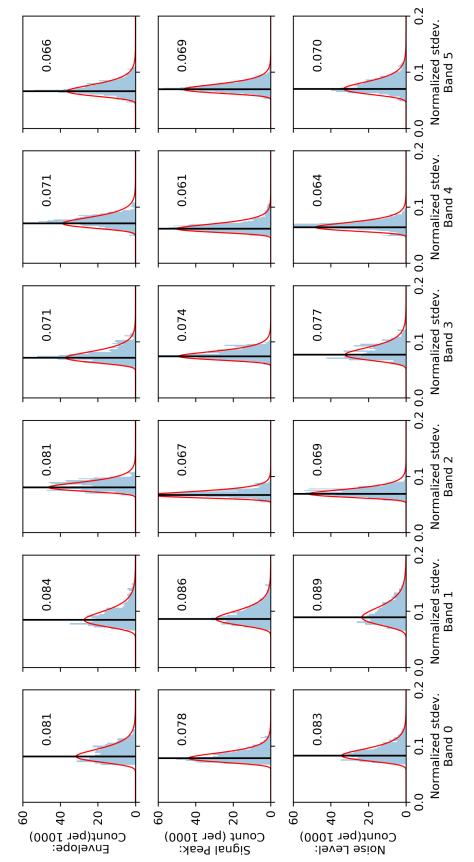

| C.2 | For a given extracted feature and across all bands, the standard deviation and mean of the feature value is calculated at all time points, and the standard deviations are all normalized to the mean. The vertical black line is the average standard deviation for that feature and band                                            |

#### **SUMMARY**

Machine learning and artificial intelligence have become commonplace in all aspects of everyday life. They drive the decision-making process for major corporations by deriving insights from data that may have otherwise gone unnoticed. At they same time, they provides simple and accurate information about the world to help average consumers optimize their own lives. From doorbells to refrigerators and smartphones to security systems, machine learning has had an irreplaceable impact on the way people carry out their day-to-day activities, and its reach is only becoming more and more ubiquitous.

Traditional machine learning algorithms and neural networks are implemented using powerful digital computational architectures such as GPUs, TPUs, and FPGAs, demonstrating high performance and successfully completing previously impossible tasks. Unfortunately, the power required to train and generate predictions with the neural networks is too high to be implemented in energy-constrained systems such as implants and edge devices. Many of these systems would significantly benefit from on-board neural networks that could respond to stimuli in real time. The important question that this work seeks to address is how to bring the game-changing power of neural networks closer to the edge of the internet of things without significant degradation of performance or battery life.

# CHAPTER 1 INTELLIGENT SENSOR PROCESSING

In the age of the "Internet of Things" (IOT), data is transmitted to and from almost anything imaginable including phones, televisions, cameras, ovens, and even doorbells. These connected devices have integrated sensors that collect information about their surroundings: audio, visuals, temperature, and anything else that can be quantified. After collecting the data, so-called smart devices adjust their performance and carry out tasks based on user interaction and preferences. The key to transforming simple transducers into smart sensors lies in machine learning and neural networks.

Machine learning has transformed the way people approach data processing. In a machine learning algorithm, the computer reads through vast amounts of data in a fraction of the amount of time required by humans. Using this data, it ajusts the parameters of a neural network by performing repetitive guess, check, and update cycles via billions of multiplications, additions, and read and write operations on devices made up of billions of transistors. In this way, the machine "learns" the trends and patterns within the data and generates an approximation of the functions that govern the task, such as classification or prediction. This learned information is part of what is referred to as artificial intelligence (AI).

A properly designed and trained neural network can perform prediction and classification tasks as well as or better than the average person. Many of these neural networks can be designed, trained, and deployed on a consumer-grade computer. In a sense, machine learning has made data processing more accessible by leveraging the mass amounts of computational power and data now available.

In order to attain such impressive performance, some neural network architectures have grown from a few layers of fully-connected neurons to networks such as Microsoft's T- NLG, natural language processing (NLP) network with 17 billion trainable parameters [1]. Training such large networks to achieve state-of-the-art accuracy can take days, weeks, or months of constant computing before arriving at the final trained state.

As these models continue to grow, the energy needed for training and inferencing with them grows as well. The process of training can demand between 100 W and 250 W on a single GPU, with each training step costing at least 200 mJ per image [2] The energy required to make predictions varies depending on the architecture, quoted at about 60 mJ and 1180 mJ per image for state-of-the-art architectures AlexNet and VGG-16 respectively on the Nvidia GeForce GTX Titan X GPU [3]. This not only goes contrary to the energyreduction mantra in an economy focused on a greener future; it inhibits classifiers from being implemented in power-starved IoT edge devices.

#### **1.1** Sensors on the Edge

It can likely be assumed that with adequate time, energy, data, and hardware, any problem can be learned via machine learning and approximated with a neural network. However, many applications that would benefit from added intelligence cannot afford all of these resources due to space or energy limitations. A simple approach to overcoming computational power limits such as in edge devices in the IoT is to send sensor data elsewhere for processing before performing a desired task, but for many cases this may not be feasible or desirable.

Frequent wireless transmission of data from edge devices requires significant amounts of energy, decreasing operational lifetime [4, 5]. Even in cases where energy limitations are not an issue, transmitting data elsewhere for computation adds latency to the data-processing pipeline and introduces security risks like interception of or tampering with data. Local computing is one of the major appeals of edge AI, so turning to distributed computing methods is not a desirable way forward.

One specific application that we explored was livestock behavioral monitoring for early detection of illnesses. In this case, the end goal is to attach a device to an animal, such as a

cow or a pig, that will sense movement, sounds, and other information from the animal and its environment. This information could then be used to predict whether or not the animal is sick or if livestock managers need to pay close attention to it. Cattle and swine tend to move around a lot; it is not likely that they will stay in one place to continuously transmit data to wireless receiver points, and they definitely won't want to be connected to a power supply. In cases like these, on-board computing is the only option for providing accurate and timely information for livestock caretakers to make informed decisions.

These and other edge applications present a new set of challenges that are not common to most high-performance state-of-the-art neural networks.

#### **1.2 Machine Learning and Neural Networks**

Machine learning is the process of training some mathematical model, such as a neural network or an equation, to approximate some function that governs a task such as prediction or classification. To better understand how the machine learning process can be altered for improved performance, a thorough understanding of neural networks and the process of training is required. This section gives an overview of what neural networks are and how they work and an intuitive explanation for how training can bring a randomly-generated NN to its final state. While the structure of the neural network and the training process may seem complicated, the basic functions needed to make it work are very simple.

#### 1.2.1 Neural networks

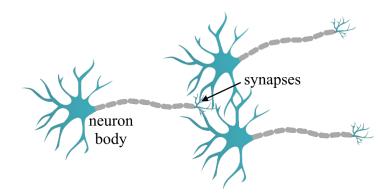

Neural networks are meant to imitate the functionality of the brain. The brain is made up of neurons which are interconnected via synapses (see Fig. 1.1); each neuron can output electric pulses to other neurons, and these pulses allow the neurons to communicate and tell the body what to do. As the brain learns, these synaptic connections grow weaker or stronger based on which synaptic connections are most important for a given task. The basic building block for artificial NNs is called the "neuron" because it behaves and learns in a

Figure 1.1: Illustration of neuron/synapse connectivity in human brain.

similar way. The artificial neuron is a single output of a layer in a NN. The value of the output is governed by a linear combination of its weighted inputs; these weights are often referred to as the synaptic weights of the neuron.

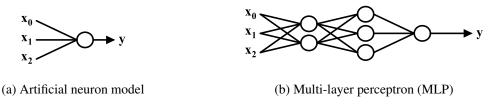

Fig. 1.2a shows a simplified diagram of a single neuron with (1.1) as the function relating the inputs to the output.

$$y = g(w_0 x_0 + w_1 x_1 + w_2 x_2) \tag{1.1}$$

Put simply, all of the inputs  $x_i$  are summed together, weighted by scalars  $w_i$ . The sum is usually passed through a nonlinear function g (i.e., the activation function) such as the hyperbolic tangent or sigmoid functions to get the output y. One of the most common layers used in NNs, the fully-connected layer, is formed by stacking multiple neurons such that every input is connected to each output neuron. In this configuration, the output of each neuron is a linear combination of all the inputs, which can be written in a simplified way as

Figure 1.2: Block diagrams representing (a) an artificial neuron and (b) a multi-layer perceptron.

in (1.2), where m is the number of inputs, n is the number of outputs, and g is the activation function that follows the layer.

$$\bar{\mathbf{y}} = g(W\bar{\mathbf{x}}), \bar{\mathbf{x}} \in \mathbb{R}^m, \bar{\mathbf{y}} \in \mathbb{R}^n, W \in \mathbb{R}^{n \times m}$$

(1.2)

A sequence of fully-connected layers and non-linear activation functions makes up the multi-layer perceptron (MLP), shown in Fig. 1.2b, which is one of the earliest architectures used in both regression and classification tasks and is still widely used today.

The full equation for the network shown in Fig. 1.2b is given in (1.3). The equation is purposefully overcomplicated and redundant so that very complex relationships between variables can be approximated; depending on the actual transfer function, the network and its function may need to grow or shrink to provide a better fit.

$$\begin{split} \bar{\mathbf{y}} &= g_2(W\bar{\mathbf{s}}) = g_2(Wg_1(V\bar{\mathbf{r}})) = g_2(Wg_1(Vg_0(U\bar{\mathbf{x}}))) \\ y &= g_2(w_0s_0 + w_1s_1 + w_2s_2) \\ &= g_2(w_0(g_1(v_{00}r_0 + v_{01}r_1) + w_1(g_1(v_{10}r_0 + v_{11}r_1) + w_2(g_1(v_{20}r_0 + v_{21}r_1)))) \\ &= g_2(w_0(g_1(v_{00}g_0(u_{00}x_0 + u_{01}x_1 + u_{02}x_2) + v_{01}g_0(u_{10}x_0 + u_{11}x_1 + u_{12}x_2))) \\ &+ w_1(g_1(v_{10}g_0(u_{00}x_0 + u_{01}x_1 + u_{02}x_2) + v_{11}g_0(u_{10}x_0 + u_{11}x_1 + u_{12}x_2))) \\ &+ w_2(g_1(v_{20}g_0(u_{00}x_0 + u_{01}x_1 + u_{02}x_2) + v_{21}g_0(u_{10}x_0 + u_{11}x_1 + u_{12}x_2))))) \end{split}$$

(1.3)

#### 1.2.2 Common layer types

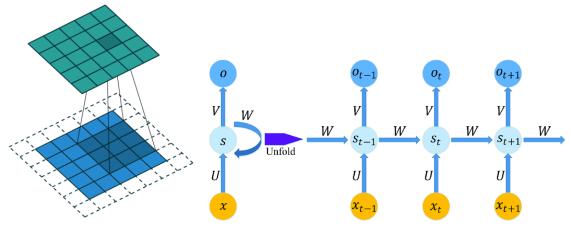

Different types of neural network layers work better with different types of data. As an example, the fully connected layer works well with data that can be represented as a vector, such as a list of attributes for a house or a plant. On the other hand, image data is twodimensional (2D) and may contain important relationships between neighboring pixels that may not be captured when represented as a one-dimensional (1D) vector. Color images are usually represented by three images that contain information about the red, blue, and green

(a) Depiction of convolutional layer

(b) Folded and unfolded views of the recurrent layer

Figure 1.3: Depictions of convolutional and recurrent layers of neural networks. In (a), the green square on the top represents the output of the convolutional layer, the dark area on the lower blue square represents the area of the filter and the input values that are used to calculate the output (from [8]). In (b), a depiction of the recurrent layer shows how the layer can be "unfolded" to visualize how the different time steps in the input data interact (from [7]).

light intensity, making the image more like a three-dimensional (3D) object. Video and audio data include a time component, which becomes even more impractical to represent as a single vector.

Neural networks for image classification tasks have worked much better using twodimensional synapse structures (known as filters). With these types of layers, each neuron output is a weighted linear combination of a 2D subset of the image. The filter is swept over the image horizontally and vertically to produce the full output, which is why these types of layers are called "convolutional" [6]. For data with temporal relationships, recurrent neural network layers provide a way to detect patterns and relationships between different points in time. A feedback path in the network uses both the current datapoint and a combination of the outputs from the data at earlier points in time to generate the current time output [7]. These and other types of layers are extremely important and provide more tools for working with all kinds of data media; for the work and purposes of this research, our focus will be on the multi-layer perceptron and fully-connected layers.

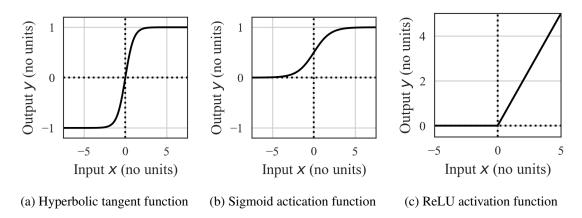

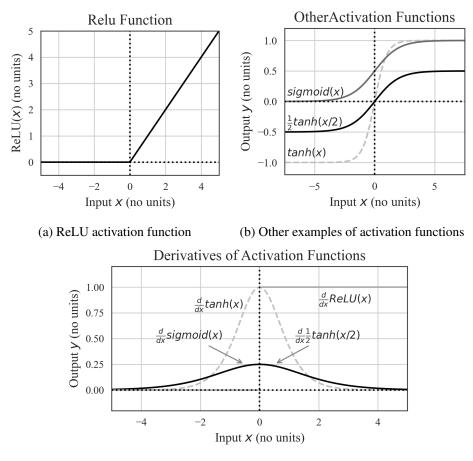

#### 1.2.3 Activation functions

The activation function is a critical part of any neural network. Most real-world systems have transfer functions (i.e., input-output relationships) that are nonlinear, so in order to represent them accurately, the approximating function or decision boundary must also be nonlinear. Recall that the function that represents a fully-connected layer is a linear combination of the inputs to the layer for each neuron in the layer. The same is also true for convolutional and recurrent layers. As such, the best that a neural network made up of only these layers can achieve is a linear function.

By inserting nonlinear functions in various points within the network (e.g., between layers), it becomes possible to approximate nonlinear functions as well, and adding more layers with more nonlinear functions adds to the amount of nonlinearity that can be estimated. This is the purpose of activation functions, which are represented by the  $g_i$  functions in (1.3). There are a number of activation functions that have been used in practice, most of which are described in [9], along with their benefits and problems and a comparison of their performance. Three of the most common activation functions are the hyperbolic tangent (1.4), sigmoid (1.5), and rectified linear unit (ReLU) (1.6) functions, shown in Fig. 1.4.

$$tanh(x) = \frac{e^x - e^{-x}}{e^x + e^{-x}}$$

(1.4)

$$sigmoid(x) = \frac{1}{1 + e^{-x}} \tag{1.5}$$

$$ReLU(x) = \begin{cases} x, x > 0\\ 0, x \le 0 \end{cases}$$

(1.6)

Usually, the same activation function is used on the output of every neuron from a given layer. For example, if the ReLU function is used on the output of layer i, then the output of

Figure 1.4: Three common activation functions used in nonlinear neural networks.

each neuron in the layer  $y_{ij}$  can be represented as in

$$y_{ij} = g_i(\bar{v}_j \bar{x}_i) \tag{1.7}$$

which, when all the output values are stacked in vector form, becomes (1.2).

#### 1.3 General Overview of Machine Learning Algorithms

The goal of the machine learning algorithm is to set the synaptic weights of a neural network to values such that passing a set of input values to the network will generate an output that matches some expected result. Because the function that governs the input/output relationship (i.e., the transfer function) is unknown, the best that the network can do is approximate it.

#### 1.3.1 Data Preprocessing

Before the data can be used to train the neural network, it usually needs to be scaled or processed into a more practical form. For example, audio data is difficult to interpret just as a string of values representing the signal magnitude, and some features may be on different orders of magnitude, such as the sqare-foot area of a house versus the number of bedrooms. There are a number of different ways to preprocess data to make it usable. While the different means of extracting and preparing features in data are beyond the scope of this research, one example for how we created usable features for audio classification is given in appendix B. The importance of the scale of each of the features is covered more detail in the next sections.

#### 1.3.2 Forward Propagation

The forward propagation step computes the initial predicted output  $\hat{y}$  based on the inputs  $\bar{x}$  and the current synaptic weights of the network. This step is so named because the inputs (i.e., the features of the input data) are propagated from one layer to the next until the output values are generated. These output values can be used to generate predictions, but it is these raw output values that are used during training to determine how to update the parameters. Since the outputs of each layer are simply linear combinations, the math functions needed for forward propagation are multiplication, addition, and the activation functions (see (1.3)).

#### 1.3.3 Loss Function

The output from the forward propagation step  $\hat{y}$  is compared to the list of ground-truth values or classes y to calculate an error or "loss" value for the network and training data. The loss function is determined by the task and can be customized based on the nature of the dataset, the class priority, and other training adjustments such as regularization. Almost any differentiable function can be used as long as it increases with error and decreases as the network predicts more accurately, though some functions work better than others. For binary classification tasks, the cross entropy loss function shown in (1.8) is most commonly used, while mean-squared error loss (1.9) is most common for regression. In general, the operations required for loss calculations are addition, subtraction, multiplication, integration, and a nonlinearity such as log or square.

$$loss = \frac{1}{M} \sum_{m=1}^{M} y log(p) + (1-y) log(1-p)$$

(1.8)

$$loss = \frac{1}{M} \sum_{m=1}^{M} (y-p)^2$$

(1.9)

#### 1.3.4 Backpropagation

Backpropagation is the process of determining how to adjust internal parameters to reduce the loss function. This can be done by individually perturbing every weight by a small amount and calculating the amount of change in the loss, but there is a much more efficient means of calculating all of the gradients which takes advantage of the linear algebra (i.e., matrix multiplications) within the network as well as the chain rule in differentiation.

The name "backpropagation" is derived from the way these gradients are calculated. First, the derivative of the loss is calculated with respect to the last layer of the network to obtain the gradients  $\Delta_k$  for the last layers synaptic weights  $W_k$ . Using the chain rule and the gradients  $\Delta_k$ , the derivative with respect to the next-to-last layer is calculated to obtain  $\Delta_{k-1}$ . This iterative process is repeated as the gradients  $\Delta_i$  are propagated backward to the very first layer. The math involved in this process is outside the scope of this work, but the functions required are addition, multiplication, and the derivative(s) of the activation functions(s) used in the network.

#### 1.3.5 Parameter Update

Finally, all the parameters are updated in the network using the calculated gradients. To decrease the error of network, they are adjusted in the opposite direction of the slope calculated during backpropagation and at a fraction of the full slope with the fraction determined by a parameter called the "learning rate"  $\alpha$  (1.10).

$$W_i' = W_i - \alpha \Delta_i \tag{1.10}$$

Figure 1.5: Consequences of using a learning rate that is too small (left) or too large (right)

The learning rate can have a huge impact on the training performance of the network as a small value will cause the network to take longer to train, but a large value may prevent the network from converging at the optimal solution (see Fig. 1.5). To avoid this, the learning rate can start large and shrink over time as the loss decreases.

The parameter update method just discussed is known as gradient descent. It works very well in most cases, but it does have a tendency to get stuck in non-optimal local minima instead of the global minima. There are many other optimization algorithms available to help get around this problem, though this is not discussed in detail in this work. For the four steps needed to train a network, the mathematical functions needed are addition, subtraction, multiplication, integration, the activation functions and their derivatives, and a nonlinearity for the loss function. This is important because it shows that the process of machine learning can achieve successful results representing very complex functions using only simple operations.

#### 1.4 Mini-batch Training: Redundant Training Sets

For two of the datasets that were used in our experiments, the data was audio MP3 files, all of which were sampled at 16 kSps. The dominant frequencies for human voice are in the low hundreds of Hz (i.e., 100-400) when considering all ages and genders, so this sampling rate should be more than adequate to capture both the fundamental frequencies and other frequency components of voice. Because our application of voice activity detection required being able to detect human speech at any moment in time, five seconds of audio,

enough for a short phrase to be spoken, would contain 80,000 samples for the training or test set. Taking into account multiple possibilities for signal-to-noise ratio (SNR), speakers, vocal fluctuations, and different noise sources, the number of audio clips needed to perform reliable grows to an unreasonably high number, easily more than billions of samples for a thorough dataset.

Fortunately, it is not necessary to use every sample in the input data for each weight update step. In our case, the features we were using were dependent on the envelope of the audio rather than the actual signal value. The envelope changes much less drastically than the audio signal, so many neighboring samples are very similar to one another, and with the same speaker and background noise, it is likely that there will be many similar input values throughout the audio clip.

Fig. 1.6 shows an example of how similar the features are for an audio clip generated using the Microsoft DNS Challenge dataset and library. There are 1600 randomly selected samples from over 30 seconds (480000 samples) of audio. Fig. 1.6a is a color map of how correlated each sample is to each of the other samples. The correlation value ranges from -1 to 1, where 0 represents no correlation and -1 and 1 represent perfectly negative or positive

Figure 1.6: Color map plots showing how many of the samples used for training closely resemble one another, both in terms of correlation and euclidean distance. In (a), the light colors represent high positive correlation. In (b), the dark colors represent a small euclidean distance between samples.

correlation respectively. Most of the plot is light green or yellow, which shows that many of the feature vectors are highly-correlated with one another. Fig. 1.6b is a color map that shows the measure of the euclidean distance between each feature vector. Since most of the plot is darkly-colored, it shows that most of the feature vectors are not far apart from one another.

When training a neural network with traditional gradient descent, the machine learning algorithm uses all data from the training dataset to calculate the loss and the gradients for each trainable parameter in the network. The gradient of the loss is calculated for each sample from the data and averaged together to get the final result. The problem with this is that the neural network must process every input before taking the next step. Because there is so much correlation between the samples in our dataset, it may seem that we can use only a small fraction of the dataset to reduce the amount of time and energy required to train the neural network However, it not usually obvious which samples are the most critical, and randomly selecting a subset to use for training will lead to a significant difference in performance between the fractional training set and the rest of the data. Fig. 1.7 demonstrates that randomly selecting a subset of the data will lead to a difference in performance between the subset and the full training set, such that the full training set essentially becomes a

Fraction of Data Used for Training and Testing

Figure 1.7: This plot shows how repetition in data does not justify randomly selecting a subset to use for training. The blue lines are the training datasets and training and the red lines represent the validation data. The light colored area surrounding each line shows how the results varied over ten different tests.

validation set. Rather than sorting through the data to hand-pick which to use, it is more effective to rotate through all of the samples in the data set but in smaller batches.

Research has shown that a neural network can be trained effectively by processing only a portion of the training data before taking an update step and then looping through the entire dataset in these smaller batch sizes [10]. This method of training became known as "minibatch gradient descent". Stochastic gradient descent takes this even further by taking using only one random data point for each update step. Because of the similarities in the inputs, the algorithm is able to move the weights of the neural network in the general direction of the desired final state much more quickly because it is taking steps more frequently. The path to the end result is not as direct, but the final accuracy is just as good as the accuracy would have been if the entire batch of inputs were used for training. Fig. 1.8 shows how, with the Microsoft DNS Challenge audio, we can reliably train and test the neural network using only 0.02% of the data for each step with good matching to using the entire dataset, and we have almost perfect matching using 1% of the data.

Figure 1.8: This plot shows how only a small fraction of the Microsoft DNS Challenge dataset can be used for each gradient calculation while still expecting the performance to match what could be attained if the entire dataset was used for training. The blue lines represent the portion of the dataset used for training and the red lines represent the portion that was set aside for validation.

# CHAPTER 2 IMPLEMENTING NEURAL NETWORKS

#### 2.1 Digital Implementation

Almost all modern machine learning is implemented in digital hardware. Whereas analog computation was more established in the mid-1900s, digital storage and computing quickly overtook it in terms of density and accuracy as CMOS technologies progressed at a rate famously observed and predicted by Gordon Moore [11]. This explosion of the capabilities of digital systems is what has allowed modern machine learning to be so successful.

Hundreds and thousands of gigabytes of information can be stored in chips smaller than a US dime, and CPUs with four or more processing threads are common in practically all smartphones. For tasks outside of the capabilities of portable devices, data can be transmitted and processed with remote cloud computing services on large amounts of computation hardware, such as Google Cloud's TPU pods. Regardless of the platform, practically all general purpose digital hardware is capable of performing all the mathematical operations required to train a neural network.

Unfortunately, the price for added computational power is just that: power. Progress in increasing performance of digital systems is approaching a wall [5, 12]. Traditional transistors are reaching the physical limitations of silicon, and practices of digital architectures such as the standard Von Neumann have speed and energy issues due to repeated off-chip memory access [5, 13, 14] as shown in Fig. 2.1. Aside from that, the circuit blocks for performing basic arithmetic such as addition and multiplication tend to be made up of a large number of transistors.

Figure 2.1: Diagram of the basic Von Neumann architecture for flexible computer processing. When multiplying a vector by a matrix, where the matrix is stored in memory, each number in the input vector is loaded one at a time and multiplied with each associated value in the matrix, which also must be iteratively loaded from memory. Delay and loss are associated with the data request and transmission along the interconnecting data lines. Taken from [15].

#### 2.1.1 Binary Arithmetic

The basic units for binary arithmetic are the full adder and half adder, which are made up of AND, NAND, and XOR logic gates. The schematic diagrams for each of these logic gates are shown in Fig. 2.2. The half adder, shown in Fig. 2.3a, takes in two bits and outputs two one-bit values: the sum and the carry-over bits. It takes one AND gate and one XOR gate to form this logic block for a total of 12 transistors. The full adder in Fig. 2.3b takes two input bits and a carry-in bit to generate the sum and carry-out bits. This logic block is made up of two XOR gates and three NAND gates, which takes 24 transistors.

Figure 2.2: Transistor diagrams for (N)AND and XOR binary logic gates.

Figure 2.3: Gate- and block-level diagrams for the binary half and full adders.

Adding two N-bit binary numbers can be accomplished by chaining together N - 1 full adders and one half adder, as shown in Fig. 2.4b. This particular adder is referred to as the "ripple" adder because of how the carry-out bit must be calculated before the next block can complete its own sum and carry-out values, making the output calculation ripple across the blocks. To reduce the delay time caused by the rippling calculation, the adder can calculate all of the carry-out bits independently so that each adder's output can be generated in parallel, but this requires significantly more logic gates. The number of transistors  $T_{ADD}$

| 1 | 1 | 1 | 0 |   |

|---|---|---|---|---|

|   | 1 | 0 | 1 | 1 |

| + | 0 | 1 | 1 | 0 |

| 1 |   |   | 0 |   |

(a) Numerical binary addition

(b) Chaining four adder blocks together to add two four-bit binary numbers

Figure 2.4: This figure shows an example of how binary addition is carried out with two four-bit binary numbers. The lighter-colored numbers in the top row of the upper figure are the carry-over bits. The lower figure is a block diagram for how three full adders and one half adder can be chained together to create a four-bit ripple adder.

needed for a an N-bit ripple adder can be calculated as

$$T_{ADD} = (N-1)T_{full} + T_{half}$$

=  $(N-1)[2T_{XOR} + 3T_{NAND}] + T_{XOR} + T_{AND}$  (2.1)

=  $(2N-1)T_{XOR} + 3(N-1)T_{NAND} + T_{AND}.$

Binary multiplication can also be accomplished using these basic adder blocks. By following the same pattern for binary multiplication as shown in 2.5a, a simple multiplier using N-bit ripple adders can be generated as in 2.5b. This multiplier is intended for unsigned binary numbers, so different architectures are needed for signed or floating point numbers. However, using unsigned-only architectures will still give a relatively accurate view of how large and complex digital arithmetic circuits can be.

For a N-bit multiplier, the transistor count  $T_{MULT}$  can be calculated as

$$T_{MULT} = (N^2 - 2N)T_{full} + NT_{half} + N^2T_{AND}$$

=  $(N^2 - 2N)(2T_{XOR} + 3T_{NAND}) + N(T_{XOR} + T_{AND}) + N^2T_{AND}$  (2.2)

=  $(2N^2 - 3N)T_{XOR} + (3N^2 - 6N)T_{NAND} + (N^2 + N)T_{AND}.$

The plots in Fig. 2.6 show how the number of transistors grows to accommodate higherbit arithmetic. While the relationship is linear for the adder, there is a quadratic increase in the transistor count for the multiplier as the number of bits increases. As stated before, there are alternate architectures that can change the speed and reduce the number of transistors, and these numbers do not directly apply to other binary number formats. However, even an optimized 32-bit float multiplier requires over 20,000 transistors [16], which is close to what is shown in the lower plot in Fig. 2.6.

(b) Block diagram for four-bit unsigned binary multiplier

Figure 2.5: This figure shows an example of how binary multiplication is carried out with two four-bit binary numbers. The lighter-colored numbers in the upper figure are the carry-over bits. The lower figure is a block diagram for how three full adders and one half adder can be chained together to create a four-bit ripple adder.

#### 2.2 Powering Down

**P**<sub>7</sub>

Significant research has been invested into methods of reducing the amount of energy required by neural networks, both in terms of training and inferencing with models. Lowering numeric precision has proven promising for many applications. Instead of using 32- or 64-bit numbers, some researchers have found that a neural network only needs to work

Figure 2.6: Plots showing the relationship between transistor count and binary number bit length.

with four or eight bits of precision with little to no loss in performance [17]. An alternative neural network architecture that has been explored more recently is the binarized neural network (BNN) [12, 18–23]. This type of neural network takes an extreme approach to precision reduction. For BNNs, the forward propagation step is performed with weights and/or activation function outputs fixed to either -1 or 1. In the backpropagation step, the actual weights and gradients are stored with full precision and clipped to stay within the (-1, 1) range. These networks have drastically reduced energy consumption, and the accuracy is reduced only by a small amount in many cases.

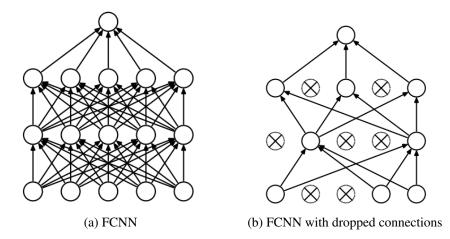

Another method for reducing computation energy requirements is eliminating unneeded connections in a neural network (i.e., sparsity) [24]. Once again, this method was taken by looking at how biological brains develop. Throughout the early years of human development, the number of neurons in the brain increases, but after reaching some age, the number starts

to decrease. This suggests that the brain eliminates unneeded or redundant neurons or synaptic connections while still maintaining similar or better performance. Sparsity will be covered in greater detail in chapter .

Some researchers have shown that it is possible to shrink a neural network down to a smaller size with minimal loss in accuracy by changing the reference values used for the "ground truth" when computing the loss function. Instead of using the labels from the dataset, the class labels predicted by a larger pre-trained neural network are used to train a smaller or compressed version of the network. This is known as Knowledge Transfer [25]. An alternative method, Knowledge Distillation, uses the raw output values, of the larger network rather than the class labels [25].

Aside from techniques that reduce the size or complexity of the model or training algorithm, there is also the possibility of using specialized hardware. Most computers use CPUs and GPUs, which are general-purpose computing devices. However, the generality of the hardware means that there is excess hardware that may not be needed for neural networks, increasing the size and power required. Tensor processing units (TPUs) are better suited for matrix and vector operations. As such, they are capable of completing an order of magnitude more operations for the same amount of power as GPUs, and CPUs (see Fig. 2.7) [26].

Neural network architectures that operate using different mechanisms than standard digital arithmetic can also lead to energy savings. In an attempt to more closely mimic the brain, Spiking Neural Networks encode information into continuous-time voltage spike trains. Because of this, the computation only occurs when spikes are present, and it can run asynchronously and in discrete sections. These networks rely on integrate-and-fire circuits, which are not present in standard computational hardware; special neuromorphic hardware is used for deployment [27]. Finally, there has been also been a movement to return to the roots of electronic computing by re-exploring analog circuits.

Figure 2.7: Plot illustrating the relative performance per power for GPUs and TPUs in relation to CPUs. The TPU' represents a second-generation improved TPU core. For more information about this plot, see [26].

# 2.3 Analog Hardware

#### 2.3.1 Arithmetic blocks

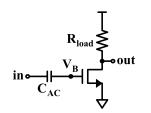

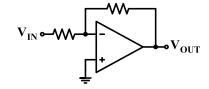

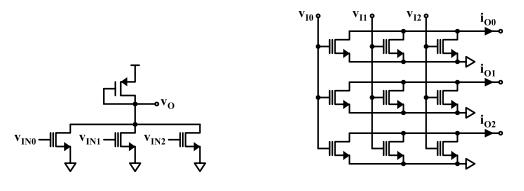

Although analog computing was largely abandoned for the digital revolution, many have been looking to it as the solution to the limitations with current digital machine learning. Rather than relying on digital arithmetic and logic, analog computing uses the physical properties of semiconductor devices [28]. An operation such as multiplication, which requires thousands of transistors in digital, can be reduced to only a handful of transistors in analog. Fig. 2.8 illustrates the small number of transistors that can be used to create a pure analog multiplier. The number of transistors in the multiplier depends on the specifications required, such as linearity and whether the synaptic weight (i.e., gain) should be able to represent either positive or negative values but the opamp represented in Fig. 2.8b can use five to seven transistors (about as much as an AND gate) or as much as ten to twenty for

(a) Single-transistor analog multiplier

(b) Analog OpAmp multiplier

(c) Input multiplying stage of a Gilbert multiplier

Figure 2.8: Block and transistor diagrams for components in analog multipliers. (a) is the basic singletransistor multiplier, which supports limited two-quadrant multiplication. (b) is a more complex operational amplifier based multiplier, which offers more flexibility and benefits such as extended linearity. (c) is the Gilbert multiplier, which is used when multiplying two analog values that can take on both positive or negative values, such as in RF mixers.

Gilbert multipliers for four-quadrant multiplication as in Fig. 2.8c.

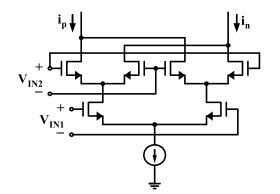

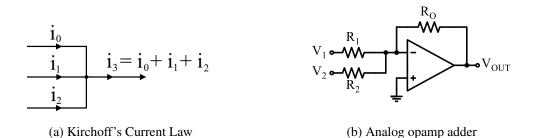

Other mathematic operations such as summation and integration can also be implemented with analog devices with similar transistor count reduction. According to Kirchoff's current law, the current in one conductive path (i.e., wire) is equal to the summation of the currents in all other connected wires, as in Fig. 2.9a. Using this law, we can build a simple summation block using only a few devices that regulate current flow into a wire. Fig. 2.9b shows how this can be done using resistors to set the summation weights. The input voltages on the left are translated to currents by their respective resistors, and the currents are summed together at the input of the opamp. The total current is translated back to a voltage by the feedback

Figure 2.9: Current summation is a built-in property of electronic devices and can be used to add voltages translated to currents through resistors.

resistor above the opamp. This relationship can be represented as

$$v_{OUT} = \frac{R_1}{R_0} v_1 + \frac{R_2}{R_0} v_2 \tag{2.3}$$

The voltage across a capacitor  $v_{cap}$  is approximated as

$$v_{cap} = \int_{t_1}^{t_2} i_{cap} dt \tag{2.4}$$

where  $i_{cap}$  is the current into the capacitor, so with one component, we can integrate currents over time. Because of the reduced transistor count and simple structures, analog circuits are comparatively low-power, faster, and smaller than their digital counterparts [12, 28– 38]. Using these simple architectures, it is possible to create an artificial neuron and a vector-matrix multiplier (i.e., fully-connected layer) as in Fig. 2.10.

Analog circuits are also not limited by clocking or serial computation, where one set of instructions must complete before another set can start, unlike their digital counterparts. Multiple system components will operate in parallel independent of other blocks, further enhancing overall computation speed [37]. This is normally only possible in digital if there are multiple independent processing cores (or threads), and even then, the parallelism is not as massive.

A research team at IBM has recently demonstrated all of these benefits by employing analog in-memory computation [39]. As stated earlier, memory access is an expensive

(a) three-input artificial neuron

(b) Fully-connected neural network layer

Figure 2.10: Three simple architectures that can act as (a) an artificial neuron and (b) a complete fully-connected layer in a neural network.

process for high-speed systems, both in terms of time and energy. The large blocks needed for digital logic and arithmetic necessitate this separation. The inherent smaller size and built-in parallelism of analog circuits allows us to build the multipliers and adders right next to each other, elimitating the read and load times for multiplicative weights. It is also possible to store the weights as voltages directly on the multipliers, as in  $V_B$  in Fig. 2.8a.

# 2.3.2 Limitations

Despite all these benefits that analog can offer to computing, it has not been widely adopted for several important reasons. The most significant limitation in analog circuits is the interdevice variability. Due to small inconsistencies in the fabrication process, voltage sources, and temperature, often referred to collectively as PVT variation, post-fabrication, devices such as capacitors and resistors can vary up to 25% from their expected values making it difficult to know their actual properties and causing offset and mismatch errors [40–42].

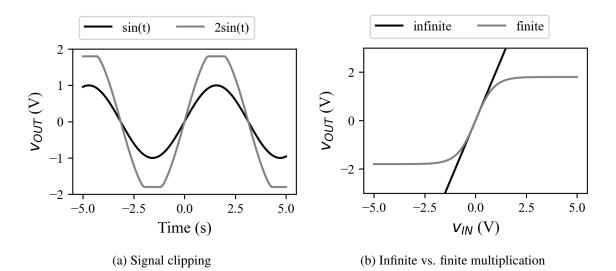

The relationships between physical properties of semiconductor devices are nonlinear and have limited ranges, which may lead to unexpected operation. For example, if the circuit is operating on a voltage supply range of -1.8 Volts to 1.8 Volts and we want to multiply a unit sine wave by two, it would be impossible to correctly represent the sine wave using the analog circuit because the range is restricted to a peak magnitude of 1.8 Volts. The resulting sine wave would be clipped as in Fig. 2.11a. The actual transfer function for a multiplier is not a straight line as expected for linear systems; it is more like a hyperbolic tangent function, where smaller inputs may be multiplied by an amount similar to the expected gain, but larger inputs would become distorted by the limited range (see Fig. 2.11b). The range of input values allowed with minimal distortion in te output is referred to as the input dynamic range.

Analog also has no perfect long-term storage; most storage methods suffer from leakage, low-precision, or limitations in writability [12, 37, 43]. Capacitors are ubiquitous in physical circuits, whether they are placed intentionally or as parasitic effects of the manufacturing process. While they are very useful for short-term voltage storage, they do not work well as long-term storage. Capacitors are typically charged through "switches", or transistors turned on and off. When the "switch" opens, it actually becomes a high-resistance path rather than an open circuit. If there is any difference in voltage between the two sides of the transistor, current will leak through and change the value over time.

Another option is floating gate transistors. These are similar to the transistor in Fig. 2.8a, but the capacitor  $C_{AC}$  is built into the transistor with the intermediate gate completely

Figure 2.11: (a) The clipping of a sinusoid multiplied by 2 inside a limited voltage range. (b) The black line is a linear function, y = 2x, and the grey line represents what an actual analog 2x multiplier would look like.

isolated from any conductive path (see Fig. 2.12). The electrical isolation allows the voltage to stay virtually unchanged for over a decade. The voltage is set on the floating gate by using second-order effects of CMOS transistors. Using hot-electron injection, the charge (voltage) is reduced. Electron tunneling removes negative charge from the gate, reducing the voltage. Both of these processes require very-high voltages, which are difficult to generate on-chip and degrade the device oxide, leading to more device property changes. A more recent alternative for long-term storage is the memristor, which is used in the memory array in [39]. As the name suggests, it is essentially a variable resistor that holds its value even when disconnected from the rest of the circuit. While it has its own challenges, it has been used with a lot of success. For the remainder of this dissertation, it will be assumed that floating-gate transistors are being used to store the multiplicative weights.

The challenges described here are the reason why analog circuits are not as flexible as their digital counterparts [12, 29, 30, 40], and training methods such as backpropagation are more difficult to implement on chip [40, 44]. All these issues limit analog computation to applications with low- to medium-precision data [12, 29, 42, 45].

# 2.4 Introducing Analog Into Machine Learning and Neural Networks

The techniques used to minimize the inherent issues depend on the approach taken to introduce analog into the computation and classification flow of common machine learning architectures. The most common ways are via full replacement, computation acceleration, and deployment.

Figure 2.12: CMOS floating gate transistor

## 2.4.1 Full Replacement

Introducing analog circuits by full replacement is the effort to complete the entire machine learning process (i.e., forward computation, backpropagation, weight learning/storage, and classification) entirely with analog blocks. The basic functions needed to implement ML are inherently available in hardware, including summation, multiplication by scalar, and nonlinear functions. Integrals and derivatives are also computable using common circuit components. Using all of these, it is theoretically possible to train and use an analog classifier implementing many popular ML algorithms.

This approach is very desirable, especially for power-starved computing-on-the-edge applications. Allowing disconnected devices to independently handle sensor output would significantly reduce the power drain from constantly broadcasting data to a base station for processing [4], and it would increase the level of privacy and security for such devices. These classifiers would be able to learn from their immediate environment and then make decisions without ever leaving the field. Because the actual device undergoes training, the classifier learns in the presence of the device variations, which results in performance competitive with an ideal digital classifier [33, 37, 43, 44, 46–52]. Many prototypes are reported in research with surprising amounts of success, and quite a few commercial products have been developed.

The biggest drawback for these types of classifiers is that the information learned is very difficult to share and reproduce. Because each fabricated circuit can vary significantly from another, the multiplicative weights learned on one chip are unlikely to directly translate to another without some amount of retraining. Being able to read the weight values is another issue entirely as each read process can also introduce noise that corrupts the learned value [42]. Because of this, the classifier becomes a black box, where very little intuition can be gained about what has been learned. Each device must be trained by the end user and is not ready for immediate use.

Backpropagation, one of the most common training algorithms, can be very difficult to

implement accurately in analog. Although it is possible to calculate gradients, it is difficult to design a reliable differentiation circuit because they are heavily influenced by device variations and noise. Some have managed to use backpropagation on chip [30, 48, 53, 54], but others have opted for alternative learning rules such as weight perturbation learning [31, 44, 55, 56], which randomly adjusts each weight in series or parallel and keeps the weights that result in better performance. This algorithm takes much longer to converge, but it is much easier to implement in analog.

## 2.4.2 Computation Acceleration

Network training is by far the most demanding step in machine learning in terms of power and resources. As the boundaries of what digital can do have become more difficult to push, many have looked to analog hardware to accelerate the learning process while also reducing the power required [13, 39, 57]. Rather than completely do away with the entire digital system, this approach seeks to augment the capabilities of the system by using analog circuits for the most demanding tasks, such as matrix multiply-and-accumulate functions. However, while this may accelerate the actual computation, latency is introduced due to the required data conversion.

Except in the case of multi-core systems, digital calculations are completed serially—the next set of multiplications cannot start until the current set has completed. Part of the reason for this is because digital architectures make use of resource sharing, which allows the same hardware to be used for multiple tasks at different time intervals. A major time and energy bottleneck in digital classifiers is the reading and loading of synaptic weight values from digital memory to the multiplier blocks [39]. This is a problem both during training and in deployment. On the other hand, analog is inherently parallel. [39] demonstrates that the entire vector-matrix multiplication step in forward propagation can be simplified to a single parallelized step by implementing analog multipliers within analog memory, thus eliminating the read and load steps. Since far fewer components are required to perform

arithmetic tasks, massive parallelism is very easy to implement when computing with analog circuits.

The most common way to implement this is to convert sensor data using an analog-todigital converter (ADC), perform any necessary pre-processing on the data in the digital domain, and then convert each value back to analog using digital-to-analog converters (DACs). In order to store results and interface with the digital system, values will also need to be converted back with an ADC. To ensure accuracy, each of these DACs and ADCs must either be trimmed, calibrated, and designed with large silicon real estate. Each DAC or ADC also introduces latency to the training path, which offsets the speed benefit from using analog. Some applications have suggested completing the feature extraction and pre-processing stages in analog as well, eliminating one ADC and one DAC [20].

One huge issue with using analog computation in a digital system is that high linearity and precision are required. For the acceleration to be useful, there must be a direct translation from analog circuit to digital model, which requires precise trimming and control of each data converter and arithmetic block. This level of precision is especially required if the intention is to use the learned weight values in a digital system or other hardware classifiers for deployment. Full replacement and acceleration are both very important steps toward low-power machine learning, but they have significant hurdles to becoming reality.

## 2.4.3 Deployment

The third method for replacing digital with analog in machine learning systems is to implement the trained digital system as an analog classifier. In this case, the training is completed on a digital system such as a computer, and the learned network characteristics (including feature extraction, and multiplicative weights) are downloaded to the device [13, 19, 28, 32, 36, 58–60]. After the device is programmed, it is ready for use in its selected application. There are three benefits to this approach. First, the deployed classifiers are inherently low-power compared to contemporary digital systems and can operate for

much longer. Second, the same set of weights can be used for all devices, improving the manufacturing throughput. Third, the weights are externally programmable, allowing for some flexibility should the weights need updating or if device-level trimming is implemented.

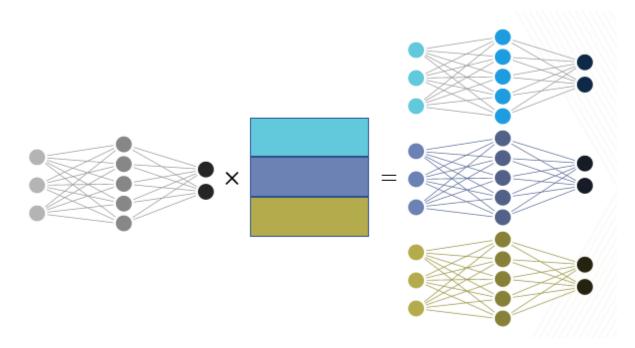

Just as with the other methods, the best set of parameters for one device is not the best for another due to process variations and other randomness such as when programming weights onto analog storage. For the same reason, the trained weights of an ideal system cannot be downloaded to an analog classifier and produce the same accuracy. To minimize the performance degradation due to these nonidealities, the architecture and training algorithm must generalize well to all variations that could occur within the classifier [61].

# 2.5 Training-to-Deployment Translation