# HIGH-SPEED CHANNEL ANALYSIS AND DESIGN USING POLYNOMIAL CHAOS THEORY AND MACHINE LEARNING

A Dissertation Presented to The Academic Faculty

by

Majid Ahadi Dolatsara

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology May 2021

**COPYRIGHT © 2021 BY MAJID AHADI DOLATSARA**

# HIGH-SPEED CHANNEL ANALYSIS AND DESIGN USING POLYNOMIAL CHAOS THEORY MACHINE LEARNING

#### Approved by:

Dr. Madhavan Swaminathan, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Sung-Kyu Lim School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Saibal Mukhopadhyay School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Arijit Raychowdhury School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Suresh K Sitaraman School of Mechanical Engineering Georgia Institute of Technology

Dr. Duen Horng Chau School of Computational Science and Engineering Georgia Institute of Technology

Date Approved: 01/27/2021

#### **ACKNOWLEDGEMENTS**

I would like to express my gratitude to my advisor, Dr. Madhavan Swaminathan, and my PhD committee members, Dr. Sung-Kyu Lim, Dr. Saibal Mukhopadhyay, Dr. Arijit Raychowdhury, Dr. Suresh K Sitaraman, and Dr. Duen Horng Chau. In addition, I thank my collaborators and coauthors, including but now limited to Dr. Jose Ale Hejase and Dr. Wiren Dale Becker from IBM, since this work would not be possible without their collaboration. Finally, I appreciate the support of my family, friends, and my colleagues at the 3D Systems Packaging Research Center (PRC) at the Georgia Institute of Technology and the NSF IUCRC center for Advanced Electronics through Machine Learning (CAEML).

### **TABLE OF CONTENTS**

| ACKNOWLEDGEMENTS                                                     | iv   |

|----------------------------------------------------------------------|------|

| LIST OF TABLES                                                       | vii  |

| LIST OF FIGURES                                                      | viii |

| LIST OF SYMBOLS AND ABBREVIATIONS                                    | xi   |

| SUMMARY                                                              | xiii |

| CHAPTER 1. Introduction                                              | 1    |

| 1.1 Objectives                                                       | 1    |

| 1.2 Description of the Problem                                       | 1    |

| 1.3 Jitter and Eye Estimation with Polynomial Chaos Surrogate Models | 4    |

| 1.4 Worst-case Eye Analysis with Bayesian Optimization               | 5    |

| 1.5 Inverse Design of CTLE with Invertible Neural Networks           | 7    |

| 1.6 Prior Art                                                        | 8    |

| 1.6.1 Transient Eye                                                  | 9    |

| 1.6.2 Statistical Eye Estimation Methods                             | 9    |

| 1.6.3 Analytical Eye Diagram Estimation                              | 11   |

| 1.6.4 Using Surrogate Models for Eye Estimation                      | 12   |

| 1.6.5 Eye Analysis with Simulating All Possible Waveforms            | 13   |

| 1.6.6 Worst-case Eye Diagram with Evolution Based Optimization       | 13   |

| 1.6.7 Worst-case Eye Diagram with Random Tree Based Optimization     | 14   |

| 1.6.8 Inverse Design with Neural Networks                            | 14   |

| 1.7 Challenges and Contributions                                     | 17   |

| 1.8 Organization of This Dissertation                                | 20   |

| 1.9 Summary                                                          | 21   |

| CHAPTER 2. Polynomial Chaos Surrogate Modeling Approach For High-sp  | peed |

| Channels 22                                                          | 22   |

| 2.1 Objectives                                                       | 22   |

| 2.2 Polynomial Chaos Theory                                          | 22   |

| 2.3 Modified PC Modeling Approach                                    | 25   |

| 2.4 Computational Cost Analysis                                      | 32   |

| 2.5 Numerical Examples                                               | 33   |

| 2.5.1 Example 1                                                      | 33   |

| 2.5.2 Example 2                                                      | 39   |

| 2.6 Summary                                                          | 43   |

| CHAPTER 3. Worst-case Eye Analysis of High-speed Channels Based on   |      |

| Bayesian Optimization                                                | 45   |

| 3.1 Objectives                                                       | 45   |

| <b>3.2</b>   | Background Review                                                   | 45        |

|--------------|---------------------------------------------------------------------|-----------|

|              | Reflected Binary Code (Gray Code)                                   | 45        |

|              | Bayesian Optimization (BO)                                          | 47        |

|              |                                                                     | 49        |

| 3.3.1        | Proposed Worst-eye Approach Intuition                               |           |

|              |                                                                     | 50        |

|              | Mapping Scheme                                                      | 51        |

|              | Optimization                                                        | 54        |

|              | Crosstalk                                                           | 59        |

|              | Numerical Examples                                                  | 62        |

|              | Example 1                                                           | 62        |

| 3.4.2        | Example 2                                                           | 68        |

| 3.4.3        | Example 3                                                           | 72        |

| 3.5          | Summary                                                             | 77        |

|              |                                                                     |           |

| CHAP         | <b>FER 4.</b> Invertible Neural Networks for Inverse Design of CTLE | 79        |

| 4.1          | Objectives                                                          | 79        |

| 4.2          | Invertible Neural Networks                                          | <b>79</b> |

| 4.2.1        | INN Structure                                                       | 79        |

| 4.2.2        | Maximum Mean Discrepancy                                            | 80        |

| 4.2.3        | Reversible Blocks in INN                                            | 81        |

| 4.3          | Continuous Time Linear Equalizer                                    | 83        |

|              | Inverse Design of CTLE                                              | 85        |

|              | Numerical Example                                                   | 87        |

|              | Summary                                                             | 92        |

|              |                                                                     |           |

| CHAPT        | TER 5. Conclusion                                                   | 93        |

| <b>5.1</b> ] | Discussion                                                          | 93        |

| <b>5.2</b> ] | Future Work                                                         | 94        |

| 5.3          | State of ML for electronics design and analysis                     | 96        |

|              | List of Publications                                                | 97        |

| REFER        | PENCES                                                              | 101       |

## LIST OF TABLES

| Table 1 | – RMS jitter values of Example 1.                                                         | 36 |

|---------|-------------------------------------------------------------------------------------------|----|

| Table 2 | - Computation times of different steps in Example 1.                                      | 38 |

| Table 3 | – RMS jitter values of Example 2.                                                         | 42 |

| Table 4 | – Binary numbers with 3 bits and their corresponding Gray Codes.                          | 46 |

| Table 5 | - Transient eye and worst-eye analysis results in Example 1.                              | 65 |

| Table 6 | - Transient eye and Worst-eye analysis results in Example 2.                              | 69 |

| Table 7 | - Transient eye and Worst-eye analysis results in Example 3.                              | 74 |

| Table 8 | <ul> <li>Accurate and candidate CTLE designs and their corresponding EH and EW</li> </ul> | 90 |

## LIST OF FIGURES

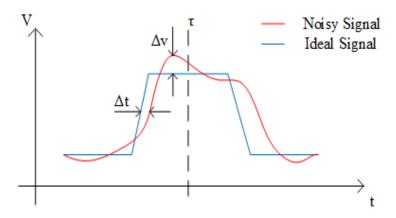

| Figure 1  | – Ideal and noisy signal, showing voltage noise $\Delta v,$ jitter $\Delta t,$ and sampling point $\tau.$                                                                                                                                                    | 2  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

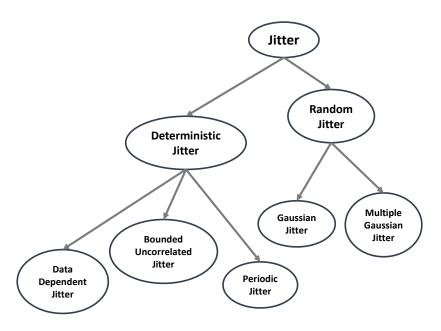

| Figure 2  | – Classification of jitter types.                                                                                                                                                                                                                            | 3  |

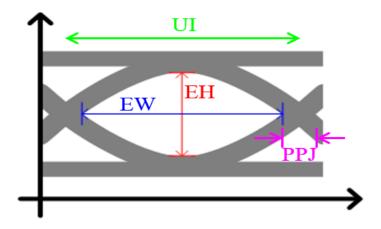

| Figure 3  | – Eye height (EH), eye width (EW), peak to peak jitter (PPJ), and unit interval (UI) shown on an eye diagram.                                                                                                                                                | 6  |

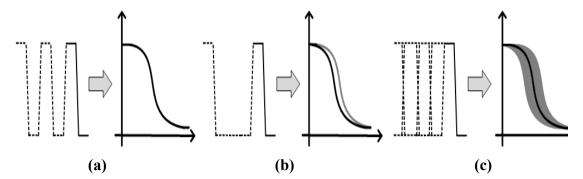

| Figure 4  | <ul> <li>Simplified input and output signals of a channel for illustrating cause of data dependent jitter in a falling edge. a) A sample signal.</li> <li>b) Small change in previous bits of (a). c) All possible combinations of previous bits.</li> </ul> | 27 |

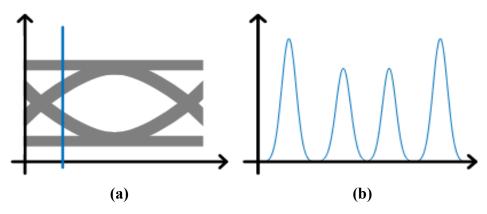

| Figure 5  | <ul> <li>A typical eye diagram with distributions of possible transitions at<br/>a sample time point. a) Eye diagram. b) Distribution of transitions.</li> </ul>                                                                                             | 28 |

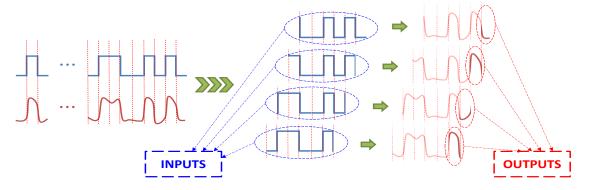

| Figure 6  | - Extraction of training samples from a single transient simulation.                                                                                                                                                                                         | 30 |

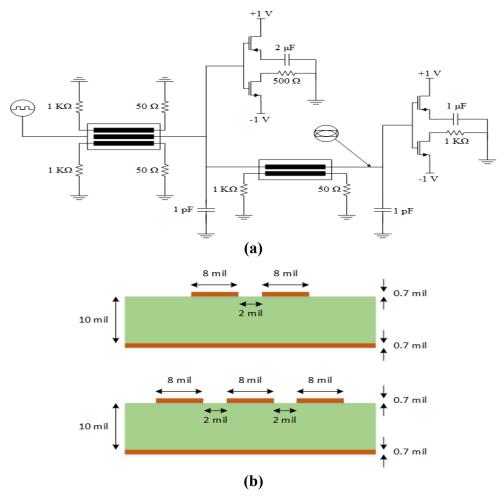

| Figure 7  | <ul> <li>Example 1: A single-ended signaling high-speed link with coupled transmission lines and nonlinear terminations. a) Circuit schematics.</li> <li>b) Cross section of the transmission lines.</li> </ul>                                              | 34 |

| Figure 8  | <ul> <li>Estimation of the output voltage for validation of the surrogate<br/>models in example 1.</li> </ul>                                                                                                                                                | 36 |

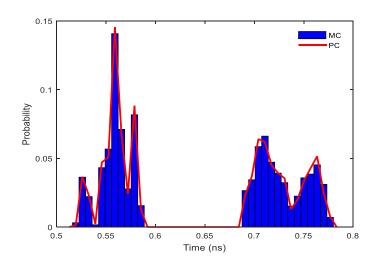

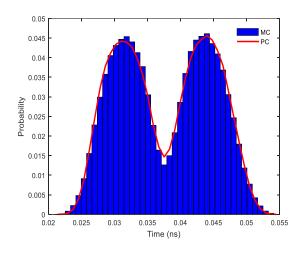

| Figure 9  | – Distribution of jitter seen in the output of Example 1.                                                                                                                                                                                                    | 37 |

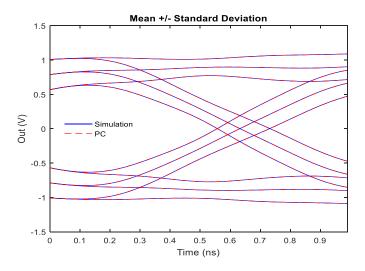

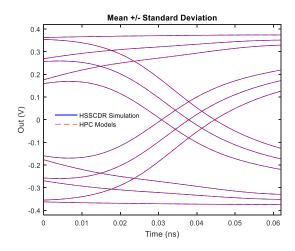

| Figure 10 | <ul> <li>Mean +/- Standard deviation of the four possible transitions of the<br/>output in Example 1.</li> </ul>                                                                                                                                             | 37 |

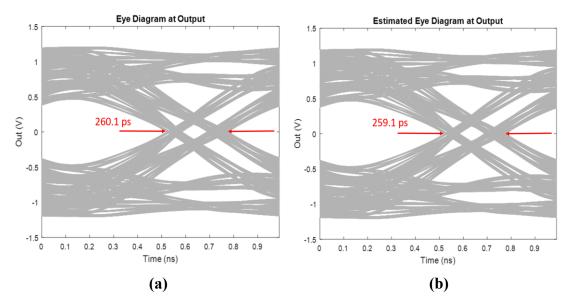

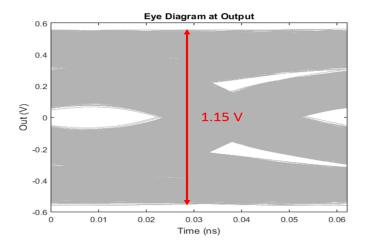

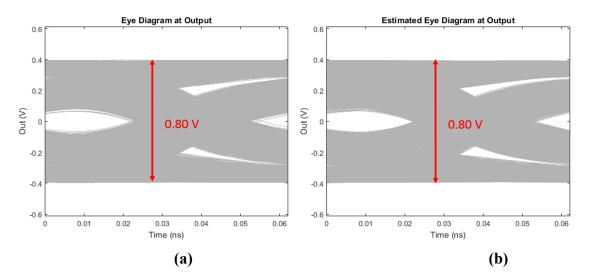

| Figure 11 | <ul> <li>Eye diagram and peak to peak jitter of the output in Example 1, showing 10000 out of one million random bits. a) Transient eye. b)</li> <li>Proposed approach.</li> </ul>                                                                           | 38 |

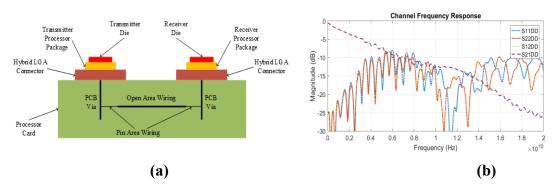

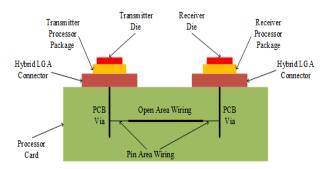

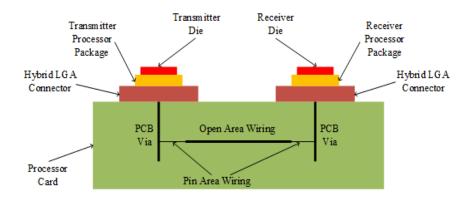

| Figure 12 | <ul> <li>Example 2: A SerDes channel including packages, vias and<br/>differential wiring. a) Schematics of the channel. b) Frequency<br/>response.</li> </ul>                                                                                               | 39 |

| Figure 13 | - Transient eye diagram of the output in example 2 before decreasing the compression point of the receiver, showing 10000 out of one million random bits.                                                                                                    | 40 |

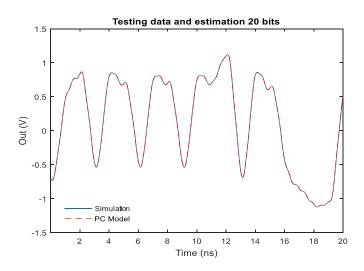

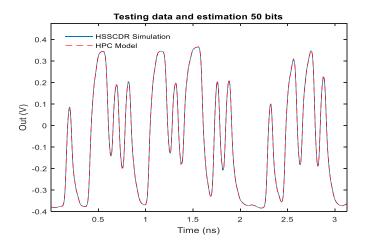

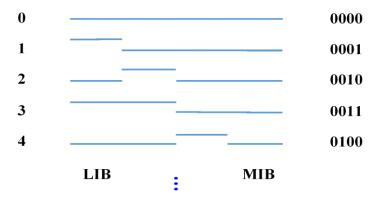

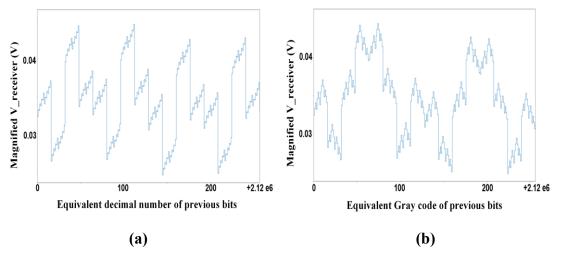

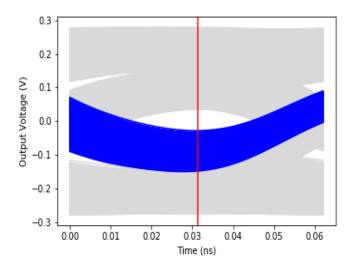

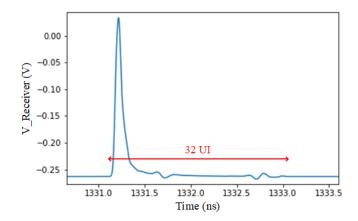

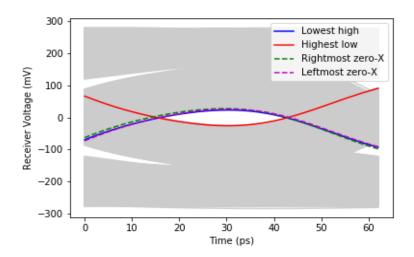

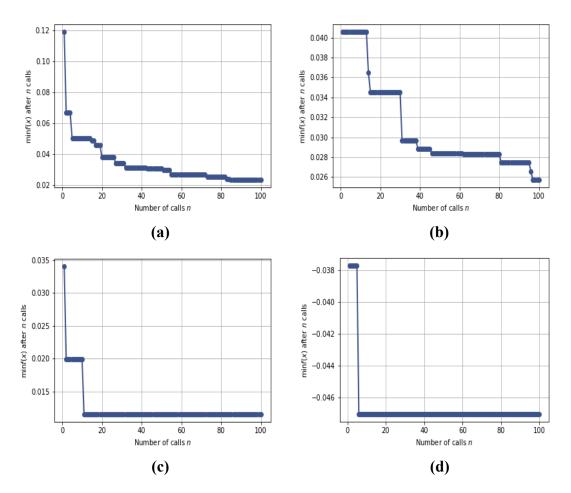

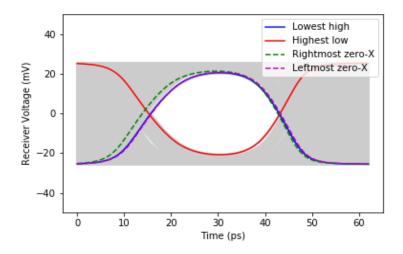

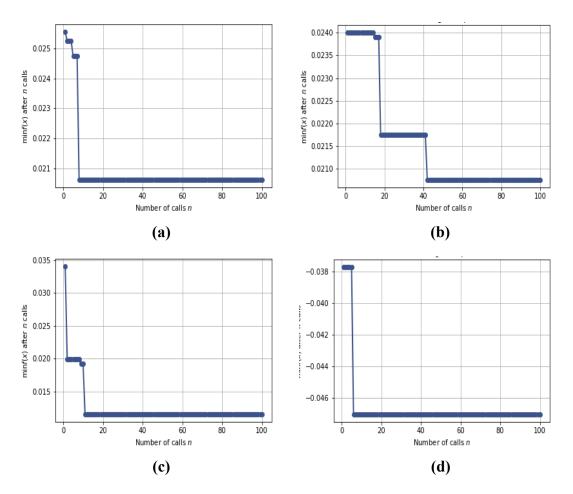

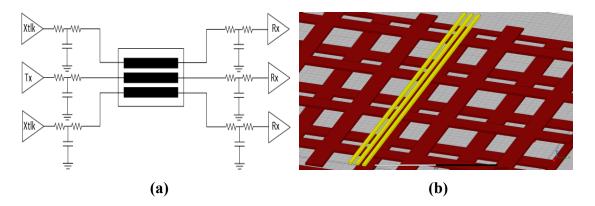

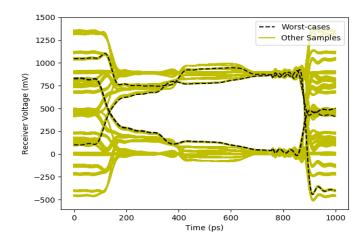

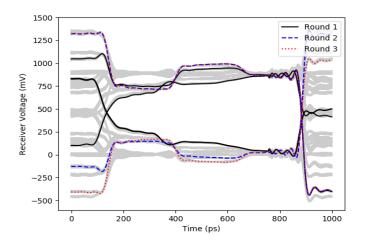

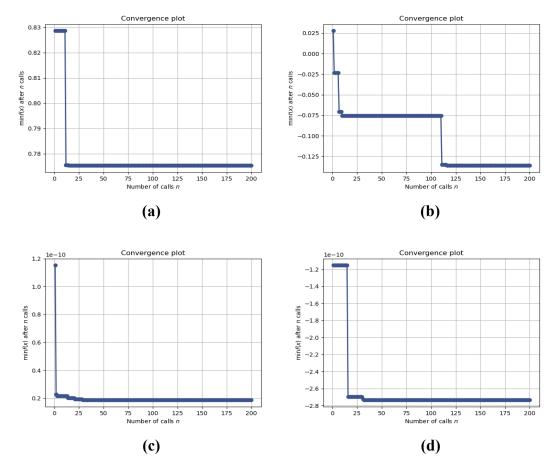

Figure 14 – Estimation of the receiver voltage for validation of the surrogate 41 models in example 2. Figure 15 – Distribution of jitter seen in the receiver voltage of example 2. 43 Figure 16 – Mean  $\pm$  of four possible transitions in example 2. 43 Figure 17 – Eye diagrams of the output in example 2 after decreasing 44 compression point of the receiver, showing 10000 out of one million random bits. a) Transient eye. b) Proposed approach. Figure 18 – Indexing of the bit patterns for n=4 in the binary format. 53 Figure 19 - Receiver voltage as a function of the index values corresponding 54 to the previous bit patterns. a) Binary order. b) Gray code order. - Example eye diagram and the waveforms corresponding to the bit 57 Figure 20 patterns ending in $\{\lambda_{-1} = 1, \lambda_0 = 0, \lambda_1 = 1\}$ , shown in blue. Figure 21 – The objective function which is passed to BO to find  $V_{HL}$  in Figure 57 20. Figure 22 – The high-speed SerDes channel in Example 1, comprised of two 63 packages, vias, and differential wiring. 64 Figure 23 – Pulse response of the channel in Figure 22 when pulse width = 62.5 ps. Figure 24 – Transient eye and the Worst-eye waveforms in Example 1. 67 Figure 25 – Convergence plots of the four worst-case variables in Example 1. 68 a)  $V_{LH}$ . b)  $-V_{HL}$ . c)  $t_{LX}$ . d)  $-t_{RX}$ . Figure 26 – Transient eye and the Worst-eye waveforms in Example 2. 70 Figure 27 – Convergence plots of the four worst-case variables in Example 2. 71 a)  $V_{LH}$ . b)  $-V_{HL}$ . c)  $t_{LX}$ . d)  $-t_{RX}$ . Figure 28 - The high-speed channel of Example 3. a) Schematics. b) Physical 72 design of the embedded microstrip lines. Figure 29 – Comparison of the worst-case waveforms and other waveforms 75 found in the first round of the proposed approach in Example 3. Figure 30 - Transient eye and 3 rounds of worst-case waveforms in Example 75 3.

| Figure 31 | – Convergence plots of the four worst-case variables in Example 3. a) $V_{LH}$ . b) $-V_{HL}$ . c) $t_{LX}$ . d) $-t_{RX}$ .                                                                                                        | 77 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

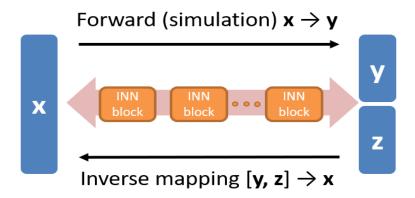

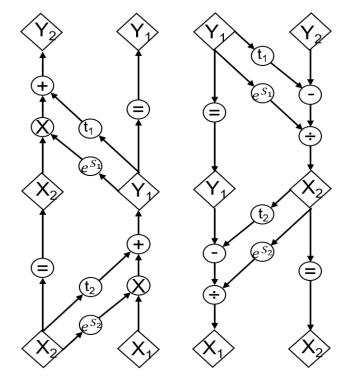

| Figure 32 | – Structure of the invertible neural networks.                                                                                                                                                                                      | 80 |

| Figure 33 | – Structure of a single INN block.                                                                                                                                                                                                  | 82 |

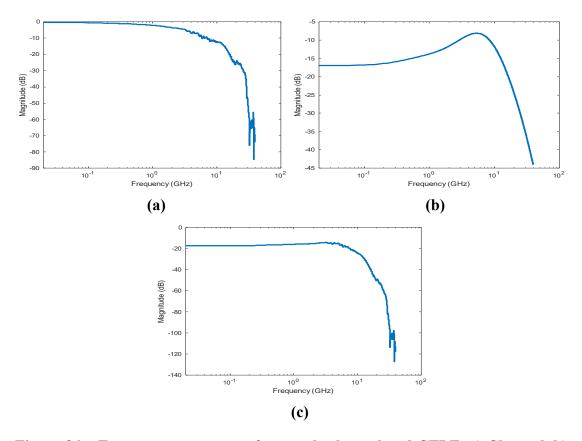

| Figure 34 | <ul><li>Frequency responses of a sample channel and CTLE. a) Channel.</li><li>b) CTLE. c) Cascaded channel and CTLE.</li></ul>                                                                                                      | 84 |

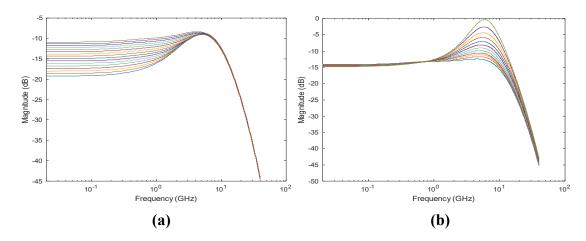

| Figure 35 | <ul> <li>Variations of CTLE by DC gain and peaking. a) Constant peaking and variable DC gain. b) Constant DC gain and variable peaking.</li> </ul>                                                                                  | 86 |

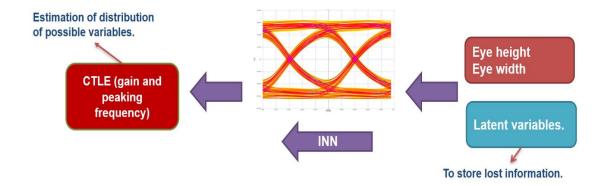

| Figure 36 | – Flow of the algorithm for inverse design of CTLE.                                                                                                                                                                                 | 87 |

| Figure 37 | - High-speed SerDes channel in the numerical example.                                                                                                                                                                               | 88 |

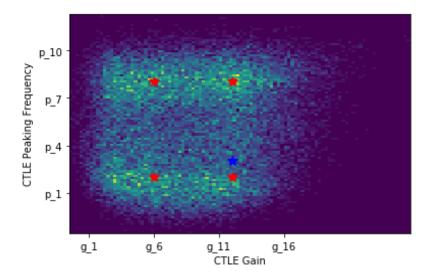

| Figure 38 | – Joint distribution of CTLE peaking $(p_i)$ and CTLE DC gain $(g_j)$ in the numerical example. Candidate designs are shown with red stars and the accurate design is shown with a blue star.                                       | 89 |

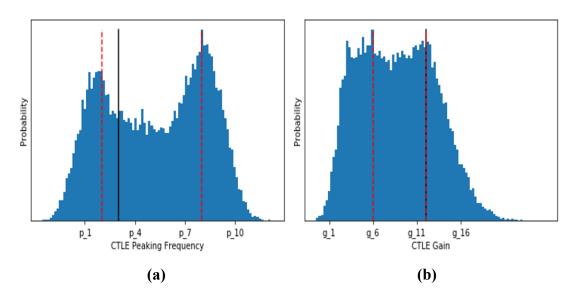

| Figure 39 | – Marginal distributions of the CTLE parameters in the numerical example. Candidate designs are shown with red dashed lines and the accurate design is shown with a black line. a) CTLE peaking $(p_i)$ . b) CTLE DC gain $(g_j)$ . | 89 |

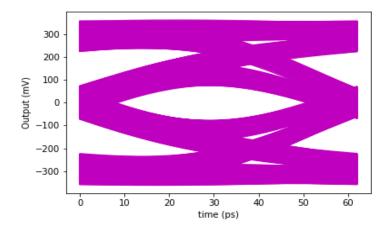

| Figure 40 | <ul> <li>Eye diagram of the channel in the numerical example when the<br/>INN2 design is used for CTLE.</li> </ul>                                                                                                                  | 91 |

#### LIST OF SYMBOLS AND ABBREVIATIONS

LTI linear time invariant BER bit error rate BO Bayesian optimization **CDF** cumulative distribution function CTLE continuous time linear equalizer duty cycle distortion DCD DDJ data dependent jitter **DDN** data dependent noise **DFE** decision feedback equalizer EH eye height ΕI expected improvement **EW** eye width **FFE** feed forward equalizer FIR finite impulse response GP Gaussian process **HPC** hyperbolic Polynomial Chaos i.i.d independently and identically distributed INN invertible neural network intersymbol interference ISI LCP liquid crystal polymer LGA land grid array

LIB

least important bit

MC Monte Carlo

MIB most important bit

ML machine learning

MLP multilayer perceptron

MMD maximum mean discrepancy

NN neural network

NRZ non-return-to-zero

P probability

PC Polynomial Chaos

PDA peak distortion analysis

PDF probability distribution function

PI probability of improvement

RJ random jitter

RN random noise

s Frequency parameter

t time

UCB upper confidence bound

UI unit interval

λ vector of random variables

μ mean

σ standard deviation

$\phi_i$  *i*-th polynomial function

#### **SUMMARY**

With the exponential increase in the data rate of high-speed serial channels, their efficient and accurate analysis and design has become of crucial importance. Signal integrity analysis of these channels is often done with the eye diagram analysis, which demonstrates jitter and noise of the channel. Conventional methods for this type of analysis are either exorbitantly time and memory consuming, or only applicable to linear time invariant (LTI) systems. On the other hand, recently advancements in numerical methods and machine learning has shown a great potential for analysis and design of high-speed electronics. Therefore, in this dissertation we introduce two novel approaches for efficient eye analysis, based on machine learning and numerical techniques. These methods are focused on the data dependent jitter and noise, and the intersymbol interference. In the first approach, a complete surrogate model of the channel is trained using a short transient simulation. This model is based on the Polynomial Chaos theory. It can directly and quickly provide distribution of the jitter and other statistics of the eye diagram. In addition, it provides an estimation of the full eye diagram. The second analysis method is for faster analysis when we are interested in finding the worst-case eye width, eye height, and inner eye opening, which would be achieved by the conventional eye analysis if its transient simulation is continued for an arbitrary amount of time. The proposed approach quickly finds the data patterns resulting in the worst signal integrity; hence, in the closest eye. This method is based on the Bayesian optimization. Although majority of the contributions of this dissertation are on the analysis part, for the sake of completeness the final portion of this work is dedicated to design of high-speed channels with machine learning since the

interference and complex interactions in modern channels has made their design challenging and time consuming too. The proposed design approach focuses on inverse design of CTLE, where the desired eye height and eye width are given, and the algorithm finds the corresponding peaking and DC gain of CTLE. This approach is based on the invertible neural networks. Main advantage of this network is the possibility to provide multiple solutions for cases where the answer to the inverse problem is not unique. Numerical examples are provided to evaluate efficiency and accuracy of the proposed approaches. The results show up to 11.5X speedup for direct estimation of the jitter distribution using the PC surrogate model approach. In addition, up to 23X speedup using the worst-case eye analysis approach is achieved, and the inverse design of CTLE shows promising results.

#### CHAPTER 1. INTRODUCTION

#### 1.1 Objectives

The problems under consideration in this dissertation are discussed in this chapter. Subsequently, the developed solutions are introduced, which includes two novel eye analysis methods and an inverse design approach. Next, the prior art is discussed, which is followed by the main challenges and contributions of this dissertation. The chapter ends with a section on organization of this document.

#### 1.2 Description of the Problem

In the past decades the bandwidth of high-speed channels has increased exponentially. As frequency of systems increase, it becomes more challenging to avoid undesired deviations in the transmitted signal due to amplitude noise and timing jitter. Figure 1 shows an example of such deviations. In this figure, the noise shown as  $\Delta v$  causes a failure in data transmission if it pushes the signal beyond the threshold voltage of the receiver. Besides, the jitter shown as  $\Delta t$ , causes an error if it moves the rising or falling edge over the sampling point  $\tau$ . Error caused by jitter and noise is often measured by bit error rate (BER). Additionally, the eye diagram, bathtub curve, and probability distribution functions (PDFs) are used to evaluate quality of the signal [1]. In this section we focus on jitter; however, a parallel discussion can be applied to noise as well. To study jitter, its various causes need to be considered. In general, jitter sources are divided into intrinsic

Figure 1 – Ideal and noisy signal, showing voltage noise  $\Delta v$ , jitter  $\Delta t$ , and sampling point  $\tau$ .

and non-intrinsic. The intrinsic jitter sources are based on physical properties of the materials, and the non-intrinsic sources are related to the design parameters. The latter includes duty cycle distortion (DCD), crosstalk and intersymbol interference (ISI). Amongst them, ISI is a result of memory and capacitive effects in circuits, which is challenging to model. On the other hand, jitter can be divided into random and deterministic types. Random jitter is mainly caused by intrinsic sources, which can be added to the signal in post-simulation with some considerations. The root cause of deterministic jitter is effects such as reflection, crosstalk, electromagnetic interference, etc. In other words, it is generated by design of the channel. Furthermore, deterministic jitter is divided into periodic jitter, bounded uncorrelated jitter, and data dependent jitter (DDJ). DDJ depends on the data pattern, and it is caused by DCD and ISI. Different jitter types are demonstrated in Figure 2 [1].

Figure 2 – Classification of jitter types.

Current simulation methods are not always accurate in capturing the ISI and DDJ; thus, in the analysis part of this work we focus on estimating this type of jitter. The proposed approaches can be combined with other estimation methods to efficiently predict BER. Jitter is often evaluated by deriving an eye diagram. Traditionally, it is done with a lengthy transient simulation (transient eye). Although it is straightforward, generating the transient eye requires high computational time and memory storage. For instance, if the BER is 10<sup>-12</sup>, it is expected that data transmission of 10<sup>12</sup> bits be simulated to observe one bit failure. Such a long simulation is not practical for complex circuits. Hence, methods based on extrapolation and approximation from a shorter transient simulation (e.g., 10<sup>10</sup> bits) are used, which reduce the accuracy. Furthermore, statistical methods have been developed to quickly estimate the eye diagram [2], [3]; however, these methods are only

applicable to LTI systems. To address these issues, we suggest two new efficient eye analysis methods, which are introduced in 1.3 and 1.4, respectively.

The final portion of this dissertation is dedicated to inverse design of high-speed channels. Since data rate of the channels has increased exponentially, their design has become more challenging. Designers need to set many design parameters and consider several constraints to satisfy the performance criteria, including a low BER. One of the critical tasks in this process is design of the equalization, which is often done with feed forward equalizer (FFE), decision feedback equalizer (DFE), and continuous time linear equalizer (CTLE). FFE and DFE coefficients are often calculated adaptively. Although the frequency response of CTLE can be found theoretically, in reality it does not always provide a satisfactory result. Therefore, engineers depend on simulating the channel with all practical CTLE settings. Unfortunately, this method can be very time consuming. It is possible to utilize human tuning or optimization methods; however, the best solution may still not be achieved, or several satisfactory possibilities could be ignored due to the nature of these algorithms. To address these issues, in 1.5 we introduce an inverse design approach to find the CTLE settings, which includes the peaking and DC gain value of CTLE's frequency response.

#### 1.3 Jitter and Eye Estimation with Polynomial Chaos Surrogate Models

The first analysis approach is partially based on uncertainty quantification, which can be defined as the study of propagation of random variables in a system [4]. This method

can be applied to estimation of the data dependent jitter and noise which are a function of random input pulses. The most well-known uncertainty quantification method is Monte Carlo (MC) analysis. MC can be prohibitively time consuming; hence, more efficient methods have been developed [4], [5], [6], [7], [8], [9]. A popular concept used in such methods is the generalized Polynomial Chaos (PC) theory [10], where random variables are approximated as sum of an expansion of orthogonal polynomials. In the proposed approach, based on PC theory and uncertainty quantification, we propose a methodology to predict jitter, eye diagram, and statistics of high-speed channels' output. This is done by training a surrogate model of the system using a transient simulation, which is significantly shorter than the simulation required for the transient eye analysis. In addition, this approach is applicable to non-LTI systems.

#### 1.4 Worst-case Eye Analysis with Bayesian Optimization

Although the PC surrogate models reduce the computational costs of eye analysis and simplify the statistical equations, building the surrogate models can introduce some inaccuracy as a result of the simplifications. In addition, it can still be computationally expensive due to the overhead cost of training the models. Therefore, development of more advanced methods is appreciated.

To further alleviate the computational costs and provide a higher accuracy, we propose a second approach, named Worst-eye. In this method, the bit patterns resulting in the worst-case signal integrity are identified with an optimization algorithm. Then, the eye

Figure 3 – Eye height (EH), eye width (EW), peak to peak jitter (PPJ), and unit interval (UI) shown on an eye diagram.

height, eye width, and the inner eye opening (worst-case eye) are found from the resulting signals. In this method, initially the search space is mapped to a low dimensional space using the reflected binary code (Gray code) [11] to reduce the dimensionality and sparsity. Then, after preparations based on the domain knowledge, Bayesian optimization (BO) [12] is applied to find the bit patterns resulting in the worst-case waveforms which pass through the points defining eye height and eye width as shown in Figure 3. BO is selected for this approach because the objective functions are nonlinear and nonconvex. Therefore, the classic optimization algorithms are not suitable. The worst-case eye is estimated by overlaying the resulting waveforms. Furthermore, this approach is extended to find the worst-case bit patterns of crosstalk resulting in the worst-case eye. Note that the advantage of the PC surrogate modeling approach over the worst-case eye method is providing the full eye diagram, statistics of the signal, and the jitter distribution, while the worst-case eye only reports the eye height, eye width, and the inner eye opening. On the other hand, the

worst-case eye method is faster, and since it derives the results from actual transient simulations it can provide more accurate results.

It is worth noting that, BO-based methods have been previously used in optimization of electronic designs [13], [14], [15]. In [13], BO is used to minimize the clock skew rate in 3D systems by co-optimization of thermal and electrical performance. The input parameters in this paper are geometrical and physical characteristics of the materials used in the 3D system such as thermal conductivity of the PCB, and thermal conductivity and thickness of the thermal interface material. In [13] the BO algorithm finds the optimal input values that result in the minimum clock skew rate. However, in the proposed approach we efficiently estimate the eye diagram for a fixed design. Here, the input parameters are the data patterns, and the proposed approach finds the patterns that result in the worst signal degradation to estimate the worst-case eye characteristics. In addition, [14] and [15] suggest variations of the BO algorithm to optimize design characteristics by finding optimal physical parameters, similar to [13]. Moreover, [16] suggests a BO-based approach to determine physical variables that produce the closest eye, where the closest eye refers to the worst signal quality caused by changing the physical variables. Novelty of the proposed approach is in finding the data patterns and waveforms causing the worst-case eye characteristics. In other words, the goal in this approach is to reduce the computational costs of finding the worst-case eye diagram for a set of fixed physical parameters.

#### 1.5 Inverse Design of CTLE with Invertible Neural Networks

In the traditional design and modeling process, from a combination of design parameters (inputs) the output of the system is found. In contrast, in the inverse approach we start from the output objectives and derive the corresponding input parameters that satisfy these objectives. The inverse problem has been a popular concept for decades. However, recently with the advancements in machine learning (ML), there has been several attempts for inverse design of high-speed electronics by exploiting the ML techniques [17], [18], [19], [20], [21], [22]. From these techniques, invertible neural networks (INNs) [23] have shown a great potential. A main advantage of these networks is providing distribution of the design parameters instead of deterministic values. This advantage can be used to deal with the non-uniqueness of the solution issue, which can be a major problem in inverse design with traditional approaches. Using INNs, we can derive several possible combinations of the design parameters instead of one. Then a satisfactory design can be selected based on other constraints. Previously INNs have been used for design of SIW filters in D-band [22]. In this work, we investigate to see if a similar approach can be used to derive the peaking and DC gain of CTLE from the desired eye height and eye width. This is a challenging problem because the considered CTLE settings are discrete. In addition, the outputs have a nonlinear relationship with the design parameters.

#### 1.6 Prior Art

In this section various existing methods for the problems considered in this dissertation, namely full eye analysis, worst-case eye analysis, and inverse design of

electronics, are reviewed. In addition, shortcomings of these methods and the reason to develop a new approach is discussed.

#### 1.6.1 Transient Eye

Transient eye is the conventional method to derive the eye diagram [1]. In this method, first a lengthy transient simulation is performed. Next, the received signal is divided to sections with length of one unit interval (UI), which are then superimposed. The resulting diagram has an eye shape; hence the name. A smaller eye opening implies higher jitter and noise, while a larger eye opening shows better quality of the signal. As discussed before, this method can be prohibitively time and memory consuming; therefore, various techniques are developed to increase the efficiency of eye analysis.

#### 1.6.2 Statistical Eye Estimation Methods

To address limitations of the transient eye analysis, statistical methods have been developed. One of these methods is peak distortion analysis (PDA), which is used to find the worst-case eye opening of an LTI system [2], [24]. Initially in this method, the response to a single pulse is determined. The pulse response can be longer than one unit interval (UI), and it can overlap with response of another symbol, causing ISI. Therefore, the response of a sequence of pulses is found by superposition of shifted pulse responses, which is applicable if the system is LTI. The lowest logical one and the highest logical zero are calculated at the sampling point, and their difference is reported as the worst-case

vertical eye opening. The worst-case eye shape can also be found by repeating this analysis at multiple sampling points and superimposing the results [25].

To extend the worst-case eye analysis, the StatEye method has been developed [3]. This method suggests that the same superposition technique can be used to find the response to any combination of input pulses. Based on this idea, a statistical method has been developed to find the distribution of receiver voltages. This is done statistically to avoid substantial CPU run times and high memory requirements. The StatEye method considers probability of different pulse combinations, and finds the distribution of ISI at an arbitrary sampling point. By connecting different sampling points, the statistical eye is formed. Furthermore, BER is calculated as the ratio of area in the jitter's/noise's PDF that crosses the time/voltage threshold. Finally, bathtub curve is determined by drawing the cumulative distribution function (CDF) of BER over one UI [1].

Although efficient, both PDA and Stat-Eye are only applicable to LTI systems since the result is based on linear superposition of the pulse responses. However, non-LTI components, such as I/O drivers and receivers, can be present in high-speed channels and can contribute to jitter and noise. Notably, this is observed in single-ended signaling, such as DDR signaling in memory systems. In these systems rising and falling edge responses can be asymmetric, which shows that the system is non-LTI. Recent work has tried to extend statistical methods to non-LTI cases. In [26], it has been suggested to estimate the receiver voltage using the superposition of responses of a rising edge and a falling edge.

This method improves the result since the difference between the rising and falling edge is considered. However, calculating the statistical eye is challenging since edge responses are not independent of each other. Therefore, [26] develops an inductive technique to find the distribution of receiver voltage, which is derived from steady state responses step by step. However, using this approach, improvements in accuracy of non-LTI systems is not always sufficient. Therefore, [25] expands this method by using various edge responses, which are different in the bits prior to the rising or falling edge. For instance, if M bits are considered,  $2^M$  responses are generated. Nevertheless, it is hard to generalize the edge response-based methods since their accuracy depends on number of considered responses, which increases exponentially with M. Moreover, they are an extension of the superposition method; thus, they fail for more complicated non-LTI systems.

#### 1.6.3 Analytical Eye Diagram Estimation

If the analytical formula describing a system is known, it would be easy to estimate the eye diagram since such functions are often evaluated quickly for arbitrary inputs. In addition, if the derived transfer function is LTI, statistical methods can be applied. Therefore, there has been several attempts to develop mathematical models to describe high-speed channels [27], [28], [29], [30], [31], [32], [33]. In [27], the voltage transfer function of a channel with a single pair of differential microstrip lines on PCB is obtained from the ABCD parameters of its components. Then, a modified PDA method is proposed, that utilizes multiple pulse responses and the transfer function to address the asymmetrical

rise/ fall times. In [28], based on RLGC models, Telegrapher's equations, and a finite impulse response (FIR) equalization, a deterministic formula for crosstalk and ISI is derived. This formula describes noise and jitter, and it is used to find the bit patterns that cause worst-case noise and jitter, by using a binary search algorithm. Furthermore, assuming a linear channel, [29] does an extensive analysis to develop closed form equations for eye height and eye width from ISI and DDJ, respectively. This paper takes into account the effects of reflection, attenuation, shunt capacitance, and passive equalization.

Unfortunately, analytical methods cannot be generalized since they use mathematical formulations that are limited to the considered systems. In addition, simplifications and assumptions are often made to make the derivation of analytical equations possible. Finally, designers need to have expert knowledge on nature of the system to derive these equations. Therefore, development of more general approaches is needed.

#### 1.6.4 Using Surrogate Models for Eye Estimation

There are many candidates in machine learning for developing surrogate models. Using neural networks (NNs) has been previously suggested to generate surrogate models of nonlinear circuits. In [34] and [35], recurrent NNs is used to model nonlinear I/O drivers, and in [36] recurrent NNs is used to model SerDes channels. This is similar to our proposed approach where PC theory is exploited to develop surrogate model of the system. However, training NNS is generally more complicated and time consuming compared to PC models.

Moreover, NNs can accumulate error over time, and can become significantly large for channels with large memory. In addition, PC provides statistical moments of the output as a byproduct of the training process with no additional costs, while numerous evaluations using the NN model are necessary to determine the statistics.

#### 1.6.5 Eye Analysis with Simulating All Possible Waveforms

As our computing resources increases, it becomes more enticing to simulate all possible combinations of the previous bits to obtain the eye diagram. In fact, in transient eye analysis we hope to achieve all the combinations in our random sequence. In [37] and [38], authors have developed methods that take advantage of simulating all possible ISI combinations. One advantage of this method is that it can confidently report the worst-case eye. Additionally, it handles non-linear systems because it is based on transient simulation. However, this method is reasonable when number of symbols with effective ISI is small since  $2^n$  simulations are needed for n symbols. Moreover, unlike transient eye, simulations are done separately. The overhead cost of calling the simulation software  $2^n$  times, and waiting for the channel to achieve steady state before simulating the intended sequence, can be prohibitive. In, fact it might be faster to run the transient eye simulation.

#### 1.6.6 Worst-case Eye Diagram with Evolution Based Optimization

To improve the previous approach, one can apply evolution-based optimization algorithms, where each transient simulation is a sample, to find the worst bit pattern which

corresponds to the worst-case eye. [39] and [40] use the genetic algorithm and particle swarm optimization, respectively, to find the worst bit pattern. However, evolution-based optimization methods are proved to have a low convergence rate. Besides, as the number of bits with effective ISI increases it would be more challenging to run enough simulations for these algorithms due to curse of dimensionality.

#### 1.6.7 Worst-case Eye Diagram with Random Tree Based Optimization

A random tree optimization approach to find the eye diagram of high-speed CMOS circuits is suggested in [41]. However, this method only considers a very short sequence of deterministic input symbols. Then, it introduces random processes as perturbations on timing of signals, and voltages of different nodes of the circuit. The perturbation parameters are simply modeled as truncated Gaussian random processes. Finally, this method finds impact of the introduced random processes on the output eye diagram. Applying this method on high-speed channels can be problematic because considering a very short input bit sequence results in missing certain ISI patterns. Moreover, assuming Gaussian distributions for voltage and timing variables on input of the receiver is oversimplification and can result in inaccurate results.

#### 1.6.8 Inverse Design with Neural Networks

Neural networks have been used for the inverse design of electromagnetic systems in several works in the past decades. In the following some of these papers are discussed.

In [42], an inverse problem approach is suggested, which is used to reconstruct the permittivity and conductivity of a medium from its measured scattered electromagnetic fields. This approach trains a Hopfield neural network, which is connected to a linear programming network, to find the solution of inverse problem.

In [43], a simple multilayer perceptron (MLP), with one hidden layer, is trained in the forward direction to model the relationship of the geometrical variables and electromagnetic fields in sample test cases. Although this network is not inherently invertible, [43] tackles the inverse problem by defining an error threshold for the objective functions and iteratively updating the outputs and inputs of the hidden layer, and subsequently the input design parameters, until achieving a viable solution.

An inverse design approach for determination of the geometrical variables of microstrip bandpass filters from the desired filter response is suggested in [17]. In this method, two neural networks, each of them including only one hidden layer, are trained for the forward and inverse mapping of the design parameters and the output objective functions. The inverse network receives the target response and yields an initial guess of the design parameters. Then, the forward mapping network along with an optimization algorithm is used iteratively to tune these variables in order to achieve the desired response.

A similar approach is developed in [18] for inverse design of the Raman amplifier by deriving the design parameters from the desired gain values. In this method, multi-layer NNs are used for inverse and forward mapping. Furthermore, approximation result of the inverse network is fine-adjusted using the forward network and the gradient descent algorithm.

It is observed that the methods described above make an approximation of the target variables using relatively simple NNs, which is then fine-tuned with different methods. Although this approach can be successful for relatively simple cases, it does not provide a general solution for complicated systems where multiple designs can result in the same response. Hence, development of more advanced inverse design methods is necessary.

Larger NNs have been used in [44] for inverse design of plasmonic nanostructures, where the required nanostructure geometry is found from the target optical response spectrum. The idea behind this method is similar to [17] and [18]; however, in addition to the difference in the size of NNs, [44] suggests simultaneous training of the cascaded inverse and forward mapping networks instead of using an optimization algorithm for tuning the inverse response. Note that, larger networks require more training samples (the example in [44] takes 15000 samples), and it still does not provide a general solution for the inverse problems.

Finally, we like to mention the application of generative adversarial networks (GANs) for inverse design of electronics. GAN is a neural network comprised of a generative network and a discriminative network. The generative network seeks to generate samples similar to the training data, while the discriminative network is tasked to distinguish the original samples and the ones fabricated by the generative model. The

competition between the two result in generation of realistic samples by GAN which have never been seen before [45]. In [46] authors have exploited this structure for inverse design of metasurface structures. This method receives the desired optical spectra and generates the candidate patterns matching that spectra. Nevertheless, GANs are not an ideal candidate for inverse design because of the possible instability in their training process. In addition, they cannot systematically solve the non-uniqueness problem because the model needs to estimate the multi-modal distribution of the design parameters in such problems, which can be problematic for GANs [22].

#### 1.7 Challenges and Contributions

As mentioned earlier, the rapid increase in bandwidth of high-speed channels and the decrease in the required BER has made channels' analysis and design more complicated and time consuming. In this section, the challenges in this area that are addressed by the proposed methods and the main contributions of this dissertation are discussed.

Traditional eye analysis of high-speed channels can be memory and time consuming. Fast statistical approaches exist; however, they are generally only applicable to LTI systems. Our first analysis method alleviates these issues by introducing a quick surrogate modeling approach, based on the Polynomial Chaos theory, for DDJ, DDN, and ISI analysis. We have focused on this type of jitter and noise because it is challenging to estimate them by traditional methods. This approach is trained with a much shorter transient simulation, and it is applicable to LTI systems. Additionally, since the surrogate

model is comprised of orthogonal polynomials, it simplifies the statistical equations of the received signal, which will be further explained in CHAPTER 2. After further examination it was observed that size of the surrogate model increases near exponentially with delay of the channel. This is because a channel with a larger delay needs to consider a higher number of previous bits for determining ISI, which increases the size of the surrogate model. Therefore, we use a modified PC expansion, called the hyperbolic Polynomial Chaos (HPC) expansion, and develop a smaller model for channels with large delays. The modified model significantly reduces computational costs with minimal decline of accuracy. This work provides the instructions to choose between the PC and HPC models to balance accuracy and efficiency. Other considerations for channels with large delays are provided as well. Furthermore, we have suggested use of the ridge regression for training the proposed surrogate models to provide more stable results, which to our knowledge has not been used before for PC surrogate models. Another contribution of this work is providing a direct jitter model to estimate distribution and statistics of the jitter. This model is much faster than finding the complete eye diagram, and it provides a comprehensive evaluation of jitter. Moreover, the computational cost analysis of this approach is provided, and its performance is evaluated on complex examples.

The second approach provides a higher speedup for cases where we are primarily interested in the eye height, eye width, and the inner eye opening (worst-case eye) caused by DDJ and DDN. For this task, the proposed approach finds the bit patterns causing the worst ISI signals by searching the random space of several previous bits. To find such bit

patterns, we have taken advantage of the Bayesian optimization. The proposed approach is advantageous compared to earlier works that search for the worst-case eye opening by means of the evolutionary algorithms [39], [40] since BO's convergence rate is proven to be faster. For instance, a comparison of BO and the genetic algorithm has been previously done in [13], where the genetic algorithm needed more than 26 times samples compared to BO for optimization of a complex function. Nevertheless, finding the target bit patterns is still a challenging problem because the objective functions are nonconvex and nonlinear. In addition, the search space is high-dimensional and sparse. Therefore, we have developed a mapping algorithm based on the domain knowledge and the Gray code to simplify the optimization. Another contribution of this work is incorporating the crosstalk in this problem and predicting its effect on the worst-case eye. Furthermore, an iterative algorithm is suggested to ensure accuracy of the worst-case eye by repeating the proposed approach at different sampling points. Finally, numerical examples along with their computational costs and convergence rates are provided to show performance of the proposed approach.

On the design side, we have proposed an inverse design approach to configure the CTLE. We have focused on CTLE since its design can be complicated and time consuming and require sweeping over all the possible designs. In inverse design, design parameters are derived from the desired outputs, which is moving in the opposite direction of the traditional forward design approach. The main challenge in inverse design is the possibility of existence of multiple designs that result in the same output, which is called non-uniqueness of the solution. In these cases, a regular regression approach would be incapable

of finding a solution since the system would be ill-posed. To address this issue, we have used the invertible neural network. This network provides distribution of the input variables based on the desired outputs. Therefore, it can facilitate prediction of multiple solutions for a single objective. This approach is advantageous compared to forward optimization techniques since it does not become trapped in local minima. In addition, providing multiple solutions is advantageous for the designer since it provides the flexibility to choose from the possible solutions based on other design constraints. Nevertheless, the CTLE design is not a straightforward problem, and the proposed approach needs to address other challenges including the nonlinear relationship between the CTLE parameters and the output signal. Additionally, in the past INN has been studied for continuous input variables, while the CTLE parameters are discrete. In this work, we evaluate performance of the INN for such variables with a numerical example.

#### 1.8 Organization of This Dissertation

In this dissertation two novel eye analysis methods, and an inverse design approach for CTLE are proposed. Each approach is preceded by a review of the main required knowledge and techniques for that approach. Organization of the rest of this dissertation is as follows. In CHAPTER 2, the PC theory and its training process is reviewed, which is followed by the proposed PC surrogate modeling approach, its computational cost analysis, and numerical examples. Next, the Gray Code and Bayesian optimization are reviewed in CHAPTER 3. Then, the proposed worst-case eye analysis approach with examples is

presented in the same chapter. INN is discussed at the beginning of CHAPTER 4. Afterwards, the basics of CTLE is reviewed in this chapter. Then, the proposed CTLE inverse design approach is introduced and its performance is evaluated on an example. Finally, the dissertation is concluded in CHAPTER 5, which includes a discussion on the proposed methods, possible future works, and list of the publications resulted from this work.

#### 1.9 Summary

This chapter covered an introduction on the problems addressed in this dissertation, which includes improvements to efficiency of the analysis and design of high-speed channels using numerical and machine learning approaches. The proposed approaches are based on Polynomial Chaos theory, Bayesian optimization, and invertible neural networks. Additionally, several state-of-the-art methods in this area and their pitfalls were reviewed. Challenges and contributions of this work were discussed, and the chapter ended with describing the organization of this document.

# CHAPTER 2. POLYNOMIAL CHAOS SURROGATE MODELING APPROACH FOR HIGH-SPEED CHANNELS

#### 2.1 Objectives

In this chapter our first efficient eye diagram analysis approach is presented. This approach develops a surrogate model for the high-speed channel to quickly perform the eye analysis. In addition, it directly provides the jitter distribution and other statistics of the eye diagram with significantly less computational costs. The surrogate model is based on the Polynomial Chaos (PC) theory. Therefore, the PC theory is discussed at the beginning of this chapter. Afterwards, the proposed approach is discussed in detail. Finally, the chapter ends with numerical examples, demonstrating the performance of this approach.

#### 2.2 Polynomial Chaos Theory

In this section, PC surrogate models, and a training method are discussed.

Generalized PC theory suggests approximating a smooth function of random variables as:

$$f(\lambda) \approx \sum_{i=0}^{P} c_i \phi_i(\lambda)$$

(1)

where  $\lambda = [\lambda_1, \lambda_2, ..., \lambda_n]$  represents a vector of random variables,  $c_i$  are unknown coefficients, P is truncated length of the expansion, and  $\phi_i(\lambda)$  are multidimensional

polynomials, which are orthonormal with respect to the distribution of  $\lambda$  [4], [10]. Using the orthogonality condition, mean and variance are found analytically:

$$E(f(\lambda)) \approx c_0 \tag{2}$$

$$var(f(\lambda)) = \sigma^2 = \sum_{i=1,2,\dots} c_i^2,$$

(3)

where  $\sigma$  is the standard deviation. It is worth noting, that mean and variance are found directly from coefficients of the PC expansion at no extra cost. When analyzing jitter, we use (3) to find Jitter RMS value since it has zero mean. Finally, to determine the PDF from the PC expansion, an approach similar to MC analysis is taken, by evaluating the PC expansion of (1) at numerous sample points, which is relatively quick since it is done analytically and without the need for circuit simulations. Furthermore, the multidimensional polynomials,  $\phi_i(\lambda)$ , are found as:

$$\phi_i(\lambda) = \prod_{j=1}^n \phi_{\alpha_j}(\lambda_j), \tag{4}$$

where  $\phi_{\alpha_j}(\lambda_j)$  is a 1-D polynomial at the *j*-th dimension, and  $\boldsymbol{\alpha} = [\alpha_1, \alpha_2, ..., \alpha_n]$  shows index of selected 1-D polynomials. Traditionally,  $\alpha_j$  are selected with a linear constraint:

$$\|\boldsymbol{\alpha}\|_1 = \alpha_1 + \alpha_2 + \dots + \alpha_n \le m. \tag{5}$$

Number of terms selected in (5) determines length of the expansion in (1):

$$P + 1 = {m+n \choose m} = \frac{(m+n)!}{m! \, n!},\tag{6}$$

where m shows the maximum order of each polynomial term in the expansion. For smooth functions, good approximation is achieved with m set to 2 or 3. Unfortunately, P scales near exponentially with n, and size of the PC expansion becomes prohibitive when n is greater than 20. For the problems addressed in this work, expansions with n as large as 50 are required; hence, development of a modified approach is necessary. We propose using the hyperbolic Polynomial Chaos (HPC) expansion [9], when it is necessary. HPC uses, the following constraint instead of (5), to select the multidimensional polynomial basis:

$$\|\boldsymbol{\alpha}\|_{u} = \sqrt[u]{\sum_{j=1}^{n} \alpha_{j}^{u}} \le m. \tag{7}$$

Here the first norm of  $\alpha$  is replaced by its *u*-norm, where u < 1 to provide a concise selection of the basis. This process drastically reduces length of the expansion in (1).

The next step is finding the  $c_i$  coefficients in (1), which alternatively can be called training the model. For this purpose, a non-intrusive linear regression method can be used [6], [7]. In this method, N random training samples are generated from distribution of  $\lambda$ , where N = 1

k(P+1), and  $k \ge 2$ . We show these samples as  $\lambda^1$  to  $\lambda^N$ . By placing them in the PC expansion of (1) and writing them in matrix form, we have:

$$A\Gamma = E, \tag{8}$$

$$\mathbf{A} = \begin{bmatrix} \phi_0(\lambda^1) & \dots & \phi_P(\lambda^1) \\ \vdots & \ddots & \vdots \\ \phi_0(\lambda^N) & \dots & \phi_P(\lambda^N) \end{bmatrix}, \mathbf{\Gamma} = \begin{bmatrix} c_0 \\ \vdots \\ c_P \end{bmatrix}, \mathbf{E} = \begin{bmatrix} f(\lambda^1) \\ \vdots \\ f(\lambda^N) \end{bmatrix}. \tag{9}$$

Next, the solution is found by using the least squares method. Although this approach minimizes the error for training data, it does not always provide the best result for testing data. In other words, the solution does not always generalize well. Therefore, we suggest improving the model by using Ridge Regression, which is a regularized regression method [47]. This approach suggests adding a regularization term to the least squares method:

$$\hat{\mathbf{\Gamma}} = \frac{Argmin}{\mathbf{\Gamma}} \|\mathbf{E} - \mathbf{A}\mathbf{\Gamma}\|_{2}^{2} + \|\mathbf{B}\mathbf{\Gamma}\|_{2}^{2},\tag{10}$$

with **B** being equal to  $\sqrt{\beta}$ **I**, except that **B**(0,0) is kept at zero. Moreover, **I** is the unity matrix, and  $\beta$  is a constant that determines the weight of regularization. With optimization, it can be shown that (10) is minimized when:

$$\hat{\mathbf{\Gamma}} = (\mathbf{A}^{\tau} \mathbf{A} + \mathbf{B}^{\tau} \mathbf{B})^{-1} \mathbf{A}^{\tau} \mathbf{E}. \tag{11}$$

### 2.3 Modified PC Modeling Approach

Jitter and noise parameters in the eye diagram have stochastic characteristics, which enables using uncertainty quantification approaches to calculate them. In fact, this work is inspired by the similarities between the transient eye [48] and the MC [49] analysis. In the MC approach, random variables in the system are sampled at numerous points. Then, the system is simulated at the samples, and the results are used to estimate distribution of output random variables. Similarly, in the transient eye, a long physical simulation is performed to calculate the uncertainty of output. This simulation is the response to a long sequence of random pulses, and it is equivalent to finding the output at various sample points in the MC analysis. In this case the outputs are noise and jitter. Both methods are straightforward and accurate if given enough time to complete; however, their computation costs can be prohibitive for complex systems. On the other hand, modern uncertainty quantification methods, such as PC theory, are substantially more efficient than MC. The idea behind this approach is to use PC to develop surrogate models for estimating jitter and eye diagram, as an efficient alternative to the transient eye.

The simplified process is illustrated in Figure 4, where random input patterns, and a falling edge in the output are shown. Intuitively, it can be said that different previous bits cause different jitter. Figure 4 (a) shows the response to a falling edge after a sample signal. However, the response can be shifted from its original place by changing the previous bits, as shown in Figure 4 (b). Moreover, Figure 4 (c) shows all possible combinations of previous bits and the corresponding outputs. Both previous bits and jitter are random and lead to the memory effect described in Figure 4. The goal in this work is therefore to find

Figure 4 – Simplified input and output signals of a channel for illustrating cause of data dependent jitter in a falling edge. a) A sample signal. b) Small change in previous bits of (a). c) All possible combinations of previous bits.

the relationship between them, and determine how the randomness propagates from data to jitter. Unlike statistical methods, in this approach the system does not have to be LTI.

As mentioned earlier, PC methods are suitable for smooth variations in the output. However, the output signal of a channel can show a wide variation, between logical zero and one, as shown in Figure 5. Therefore, directly applying the existing PC approaches to this problem can yield inaccurate results. To address this issue, we suggest breaking the problem to four smaller cases and developing four sub-models. Figure 5 (a) shows a typical eye diagram of an NRZ signal, where at an arbitrary point on the X-axis, shown with a blue line, four possible transitions can be seen. The transitions are zero to zero, zero to one, one to zero, and one to one. The response to each transition is disturbed from its average value by variations in the previous bits. Moreover, Figure 5 (b) shows distribution of the signal at the blue line in Figure 5 (a). Each Gaussian curve in this figure shows distribution of one of the possible transitions. It is observed that, by modeling each transition separately the

Figure 5 - A typical eye diagram with distributions of possible transitions at a sample time point. a) Eye diagram. b) Distribution of transitions.

variation of output is significantly limited, which makes the PC methods applicable. Similarly, this approach can be extended to other coding schemes such as PAM4.

In this approach, inputs are the previous bits that cause effective ISI, while the last two bits show the transition. These two bits are used to divide the training and testing data into four categories, and show which sub-model needs to be used for each category. The remainder of the previous bits disturbs output of each transition from its average value, and they are therefore inputs to the four sub-models. In the remainder of this chapter, we label these bits as  $\lambda = [\lambda_1, \lambda_2, ..., \lambda_{n-2}]$ . Furthermore, we define two types of outputs for two different ways of evaluating the degraded signal. The first method is a quick and direct method to find jitter, which can also be applied to other eye parameters such as eye height and eye width. Training data is obtained directly by measuring jitter at each instance. Moreover, only rising and falling transition sub-models are needed because steady one and steady zero do not have a zero crossing. Using (1), the surrogate models for rising and falling edge jitter,  $J_r(\lambda)$  and  $J_f(\lambda)$ , are defined as:

$$J_r(\lambda) \approx \sum_{i=0}^{P} C_{r_i} \phi_i(\lambda), \quad J_f(\lambda) \approx \sum_{i=0}^{P} C_{f_i} \phi_i(\lambda),$$

(12)

where  $C_{r_i}$  and  $C_{f_i}$  are unknown coefficients for the rising edge and falling edge models, respectively. Using these coefficients, the RMS value of jitter for rising and falling edges, and the jitter distribution are calculated.

To create the full eye, we define a second type of output, which is the voltage of each time point on the X-axis of the eye diagram. In other words,  $V(t, \lambda)$  is modeled over one UI. Training data is obtained by measuring the voltage of each time point over a number of intervals, and the surrogate models is found as:

$$V_{\rm rs}(t, \lambda) \approx \sum_{i=0}^{P} C_{rs\_i}(t) \phi_i(\lambda),$$

(13)

where  $0 \le t \le T$ , and  $r, s \in \{0,1\}$ , which represent the four sub-models needed for modeling the receiver voltage. Thus,  $C_{00\_i}$ ,  $C_{01\_i}$ ,  $C_{10\_i}$ , and  $C_{11\_i}$ , are the unknown coefficients for steady zero, rising edge, falling edge, and steady one models, respectively. With these coefficients, mean and variance of the receiver voltage are found using (2) and (3), respectively. Furthermore, to draw the eye diagram, (13) is evaluated at an arbitrary number of possible samples, then the results are overlaid over one UI.

There are  $2^{n-2}$  possible combinations of  $\lambda$  in (12) and (13). If  $n \le 20$ , all possible combinations are calculated for drawing the jitter distribution and the eye diagram. Note that using more samples does not improve the results since all the possible values are

Figure 6 – Extraction of training samples from a single transient simulation.

included. If n > 20, it is not practical to estimate all possible outputs. Hence, a large enough subset of the samples is selected randomly.

Next, we discuss the training process. It is not efficient to run a separate simulation for each training sample. Hence, all necessary information is extracted from a single short transient simulation, with length of the simulation being much greater than P+1 and much smaller than the traditional eye. This process is illustrated in Figure 6. In this figure, input and output signals of the channel are shown. Imagine a box, with length of n bits, moving from end of the input signal to the left, with n being number of bits with effective ISI. Similarly, imagine a box with length of one bit, moving from end of the output signal to the left. We crop the signals at each instance, then boxes are moved one bit to the left. Each pair of corresponding inputs and outputs shows one sample or experiment. Number of input bits, n, is calculated based on the channel, using some heuristics. However, we use a rule of thumb, which states that  $n * T \approx 3 * D$ , where T is length of one unit interval, and D is delay of the channel. This formula considers effective ISI for a signal traveling through a

channel and its two reflections. For  $n \le 20$ , size and cost of creating the regular PC model is justifiable; however, for channels with a longer memory the computational cost can be prohibitive. Therefore, we suggest a hybrid methodology where the regular PC expansion is used for channels with  $n \le 20$  to obtain more accurate results, and the HPC expansion is applied for channels with a longer memory to reduce CPU costs. We show PC and HPC models with the same formulation; nevertheless, polynomials  $\phi_i$ , and length of the expansions, shown with P, are different.

To find the coefficients with the regularized regression approach, suggested in 2.2, N samples are extracted from a short transient simulation, which provides  $\lambda^1$  to  $\lambda^N$  and  $f(\lambda^1)$  to  $f(\lambda^N)$ . Using these values, matrices A and E in (8) are filled. Matrix A needs to be full rank in order to do the matrix inversion in (11). Initially, this might not be true because all the input variables are 0 or 1, which makes some of the columns a linear combination of other columns. Therefore, we remove the repeated columns and their corresponding polynomials  $\phi_i$  since they do not provide any additional information. This would not cause a problem for estimation of new test samples because they are a combination of zeros and ones as well. After this modification, matrix A becomes full rank, and the unknown coefficients are found with the matrix inversion in (11). For example, coefficients in the surrogate model of the rising edge are found as:

$$\widehat{\mathbf{\Gamma}_{01}}(\mathbf{t}) = (\mathbf{A}^T \mathbf{A} + \mathbf{B}^T \mathbf{B})^{-1} \mathbf{A}^T \mathbf{E}(t), \tag{14}$$

where  $\widehat{\Gamma_{01}}(t)$  is a vector of  $C_{rs\_i}$  coefficients. After training the models, we use the surrogate models of (13) for a validation step, where they are used to estimate the receiver voltage for a short sequence of random input pulses, not used for model training. If this matches with the actual transient simulation, we proceed to find the statistics and the estimated eye. Otherwise, the parameters are further tuned to provide a more accurate surrogate model.

It is worth noting, that random jitter can be added to this analysis later as single or multiple Gaussian distributions. Adding random jitter in post-processing is a common practice in commercial solvers such as HSSCDR, a specialized channel simulator, used by IBM [50]. Therefore, we suggest the same technique to integrate the random jitter with results of the proposed approach.

# 2.4 Computational Cost Analysis

The proposed approach can reduce cost of the physical transient simulation significantly. We suggest using this approach for problems where overhead cost of developing the surrogate models is negligible compared to the transient simulation. Note that,  $\phi_i$  polynomials are known beforehand, and by keeping the same sequence of random training data, all the parameters of  $(A^TA + B^TB)^{-1}A^T$  in (11) can be calculated and stored in advance. Therefore, the main overhead cost in the training process is the remaining matrix vector multiplication in (11). The computations cost of this multiplication is  $O((P+1)^2)$ , and it needs to be calculated for every sub-model in (13). There are four sub-models, and assuming there are  $\Psi$  time points in one UI, the corresponding overhead cost

is  $O(4\Psi(P+1)^2) = O(\Psi P^2)$ . Cost of the direct method for training the jitter models in (12) is negligible in comparison since the matrix vector multiplication is done only twice. Furthermore, the testing process and calculating the full eye diagram involves evaluating (13) at  $\nu$  samples, where the  $\phi_i(\lambda)$  values can be calculated beforehand. In the matrix form, this process is similar to (8), where A is computed in advance and  $\Gamma$  is known. Hence, the computational cost to find E is of a matrix vector multiplication, which is  $O(\nu(P+1))$ . With  $\Psi$  time points in one UI, the corresponding cost for evaluating the voltage models is  $O(\Psi \nu(P+1)) = O(\Psi \nu P)$ . Again, the CPU cost of directly finding jitter for  $\nu$  samples is negligible in comparison. Therefore, the total overhead cost is  $O(\Psi \nu P + \Psi P^2)$ . It is worth noting, this approach is highly parallelizable; hence, its computation time can significantly decrease with parallelization

## 2.5 Numerical Examples

In this section the proposed approach is applied to numerical examples to evaluate the performance of the PC based surrogate models. PC calculations and modeling are done in MATLAB R2015a, while transient simulation is performed using available commercial software.

### 2.5.1 Example 1

The circuit in Figure 7 (a) is considered for observing performance of the proposed approach, when memory of the channel is relatively small, and a full PC expansion can be

Figure 7 – Example 1: A single-ended signaling high-speed link with coupled transmission lines and nonlinear terminations. a) Circuit schematics. b) Cross section of the transmission lines.

used. This example shows a single-ended signaling system, which includes two sets of coupled microstrip lines and nonlinear terminations. The cross section of microstrip lines is shown in Figure 7 (b). The first set of lines are three coupled lines that are 4 inches long, while the second set consists of two coupled lines with length of 2 inches. All conductors are copper; dielectric permittivity is 4.5, and  $\tan \delta = 0.02$ . The PMOS and NMOS

transistors in the terminations are Schicman-Hodges models. Supply voltage is  $\pm$ 1 V, and the circuit is fed through a voltage source with 50  $\Omega$  resistance, using a random trapezoidal pulse with  $V_{high} = 1$  V and  $V_{Low} = -1$  V. Bit rate is 1 Gb/s; rise time and fall time are both 100 ps, and output voltage is observed at the shown eye probe. Finally, the transient simulation is done using ANSYS Electronics Desktop 17.2 circuit simulator [51].

In this example, 20 bits are considered to capture the effective ISI. Hence, we use the regular PC expansion. In addition, there are 2<sup>20</sup> possible combinations of these bits; therefore, all possible outputs are estimated. Note that using more samples does not change the result since all the possible combinations are included. The results are compared with an actual transient simulation with one million random bits. We did not use more than one million samples for the transient eye since variations in the outcome were minimal, and we were limited by the memory of our machine. Moreover, maximum order of expansion, m, is set to 3. For training the models, first a short transient simulation is performed, with its length being more than 60000 bits. From this simulation, four sets of training data are extracted. Each set shows a different transition and has about 15000 samples. Using them and the proposed method, jitter and voltage surrogate models are generated. For validation, the receiver voltage for a short sequence of random pulses is estimated. The result is shown in Figure 8, and compared with the actual circuit simulation. Since the model shows perfect accuracy, we continue to calculate the statistical results and the eye diagram. Next, the jitter RMS is directly calculated, and it is presented in Table 1. Additionally, distribution of jitter

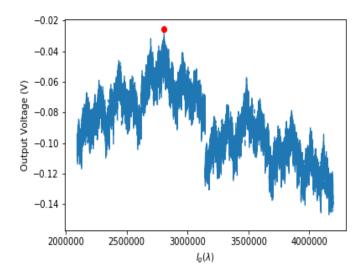

Figure 8 – Estimation of the output voltage for validation of the surrogate models in example 1.

Table 1 – RMS jitter values of Example 1.

|                        | Low to high RMS jitter | High to low RMS jitter |

|------------------------|------------------------|------------------------|

| Transient eye analysis | 87.2 ps                | 87.9 ps                |

| Proposed PC approach   | 87.3 ps                | 87.8 ps                |

is calculated and shown in Figure 9 and compared with transient simulation, showing a good agreement.

In the next step, the mean and standard deviation of receiver voltage is calculated over one UI, and the results are shown in Figure 10. In this figure, the mean and mean +/- standard deviation of the four possible transitions are shown, and compared with the transient simulation. Figure 10 gives us an idea about quality of the signal. The mean and standard deviation in this figure are found using only coefficients of the voltage model;

Figure 9 – Distribution of jitter seen in the output of Example 1.

Figure 10 - Mean + /- Standard deviation of the four possible transitions of the output in Example 1.

hence, it reduces time and memory. Finally, the eye diagram is evaluated, and shown in Figure 11 (b). The eye diagram, from the transient simulation with one million bits, is shown in Figure 11 (a). Peak to peak jitter is also displayed in the Figure 11 (a) and (b), which is calculated from the final eye diagram. In all the results it is observed that the

Figure 11 – Eye diagram and peak to peak jitter of the output in Example 1, showing 10000 out of one million random bits. a) Transient eye. b) Proposed approach.

Table 2 – Computation times of different steps in Example 1.

|                                    | Time    |

|------------------------------------|---------|

| 60000 bits sim. with Ansys         | 663 s   |

| Training jitter and voltage models | 102 s   |

| Jitter Distribution                | 196 s   |

| 1 million bits estimation with PC  | 3827 s  |

| 1 million bits sim. with Ansys     | 11055 s |

proposed approach matches well with the transient simulation. Moreover, computation time of the main steps, except the initialization, are reported in Table 2. It is observed that the CPU cost for determining jitter and statistics is negligible. The full eye diagram

Figure 12 – Example 2: A SerDes channel including packages, vias and differential wiring. a) Schematics of the channel. b) Frequency response.

evaluation is more time consuming; however, it is about 3 times faster than the transient eye. Note that this time can be significantly reduced by using a shorter expansion. Moreover, the required memory for finding mean and variance values is reduced by about 35%.

# 2.5.2 Example 2

The purpose of this example is to show performance of the proposed approach for a channel with long memory, where the Hyperbolic PC expansion needs to be used. Therefore, a commercial SerDes channel with differential signaling is considered, provided by IBM. This channel is shown in Figure 12 (a), and its frequency response is presented in Figure 12 (b). Output of the system is the receiver voltage. Moreover, the channel is comprised of two processor packages, communicating with each other and interfaced to a board with two hybrid land grid array (LGA) connectors. The transmitter and receiver processor packages contain 85 Ohm differential stripline wiring in GZ41 material (Dk  $\sim$  3.31 and Df  $\sim$  0.0092 at 1 GHz), and have 31 mm and 34 mm lengths, respectively. The