# RELIABILITY AND DATA ANALYSIS OF WEAROUT MECHANSIMS FOR CIRCUITS

A Dissertation Presented to The Academic Faculty

by

Shu-han Hsu

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology August 2020

# COPYRIGHT © 2020 BY SHU-HAN HSU

# **RELIABILITY AND DATA ANALYSIS OF WEAROUT**

# **MECHANSIMS FOR CIRCUITS**

Approved by:

Dr. Linda Milor, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Mark Davenport School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. David Keezer School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Benjamin Klein School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Ben Wang School of Industrial and Systems Engineering *Georgia Institute of Technology*

Date Approved: [July 16, 2020]

## ACKNOWLEDGEMENTS

I would like to thank Professor Linda Milor for her insightful guidance and mentoring throughout my PhD journey. I am very grateful for the opportunity to be her student, because she has shown me how to become a better researcher, as well as opened my mind to allow me to explore exciting research topics. Professor Milor is my biggest inspiration for pursing an academic career, which would not have been possible without her help, and I hope that I can be able to mentor others as she has mentored me.

I also would like to thank Professor Mark Davenport, Professor Ben Klein, Professor David Keezer, and Professor Ben Wang for their helpful suggestions and serving as committee members.

I would also like to thank Professor Azad Naeemi for his help and support.

In addition, I would like to thank Taizhi Liu, Dae-Hyun Kim, Kexin Yang, and Rui Zhang in our lab for their support, collaboration, comments, and feedback.

I would like to specially thank Dr. Yi-Da Wu for his mentoring, discussion, and help. You are an amazing researcher, and I am grateful to be able to learn from you. I also want to thank Dr. Li-Hsiang Lin for his help and discussions, which allowed me to further understand problems. Yen Pang Lai and Muya Chang, thank you for your support. Mayank Parasar, thank you for all your help with discussions. Thanks also to all my friends for being on this journey.

I would like to thank my family for their support. This thesis is dedicated to them.

# **TABLE OF CONTENTS**

| ACKNOWLEDGEMENTS                                                     | iii  |

|----------------------------------------------------------------------|------|

| LIST OF TABLES                                                       | vi   |

| LIST OF FIGURES                                                      | vii  |

| LIST OF SYMBOLS AND ABBREVIATIONS                                    | xii  |

| SUMMARY                                                              | xiii |

| CHAPTER 1. Introduction                                              | 1    |

| 1.1 Planar MOSFET and FinFET Device Structures                       | 3    |

| 1.2 Statistical Analysis of Reliability Data                         | 7    |

| 1.2.1 Weibull Distribution                                           | 8    |

| 1.2.2 Maximum Likelihood Estimation                                  | 9    |

| 1.2.3 Quasi-Newton Method                                            | 10   |

| 1.3 Wearout Mechanisms                                               | 10   |

| 1.3.1 Front-end Wearout Mechanism                                    | 11   |

| 1.3.2 Back-end Wearout Mechanisms                                    | 13   |

| 1.3.3 Middle-of-line Wearout Mechanism                               | 15   |

| 1.4 Circuit Case Studies                                             | 17   |

| 1.4.1 Process Design Kit (PDK)                                       | 17   |

| 1.4.2 Ring Oscillators                                               | 17   |

| 1.4.3 Static random-access memory (SRAM)                             | 18   |

| 1.5 Research Objectives                                              | 19   |

| 1.6 Thesis Overview                                                  | 20   |

| CHAPTER 2. Failure Analysis of Circuits                              | 21   |

| 2.1 Separation of competing wearout mechanisms in circuits           | 21   |

| 2.1.1 Methodology                                                    | 23   |

| 2.1.2 Investigation of Initial Conditions vs. Sample Size            | 27   |

| 2.1.3 Identification of Wearout Mechanism for Each Individual Sample | 30   |

| 2.2 Failure Analysis for On-line Testing                             | 41   |

| 2.2.1 Methodology                                                    | 43   |

| 2.2.2 Error Analysis                                                 | 49   |

| CHAPTER 3. Accelerated Testing                                       | 58   |

| 3.1 Failure Probability vs. Test Time                                | 59   |

| 3.2 Sample Size vs. Test Time                                        | 60   |

| 3.3 Effects of the Number of Stages                                  | 64   |

| 3.4 Lifetime Estimation Method for Use Conditions                    | 66   |

| 3.5 Testing Conditions                                               | 67   |

| 3.5.1 Computing the Error for the Accelerated Test Conditions        | 67   |

| 3.5.2 Test Plans                                                     | 68   |

| 3.6 Error Reduction Through Sampling                             | 70 |

|------------------------------------------------------------------|----|

| 3.6.1 Adjusting Sample Fractions for a Fixed Overall Sample Size | 70 |

| 3.6.2 Minimum Sample Size to Achieve Fixed Tolerance             | 74 |

| 3.6.3 Lowest Tolerance and Total Sample Size                     | 77 |

| 3.7 Summary                                                      |    |

| CHAPTER 4. Conclusions                                           | 79 |

| 4.1 Summary                                                      | 79 |

| 4.2 Future Work                                                  | 80 |

| REFERENCES                                                       | 81 |

# LIST OF TABLES

Table 195% Confidence Intervals for 11-stage ring oscillators at40accelerated conditions (1.37V, 194.72°C)40

# LIST OF FIGURES

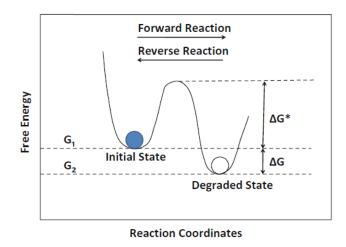

| Figure 1  | <ul> <li>Illustration of the material degradation reaction. The material<br/>will move from the initial state to the degraded state in order to<br/>lower its Gibbs Potential Free Energy [12].</li> </ul> | 2  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

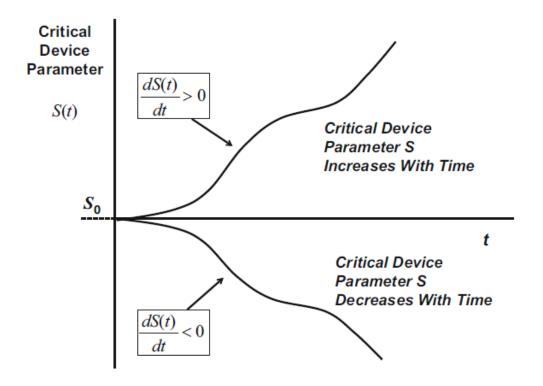

| Figure 2  | – Materials degradation in a device can cause device parameter S to degrade with time, which can be increasing or decreasing [12].                                                                         | 2  |

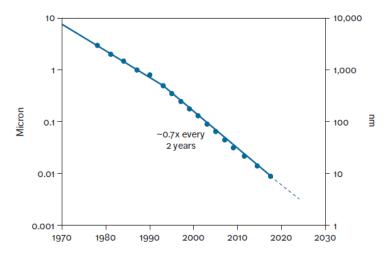

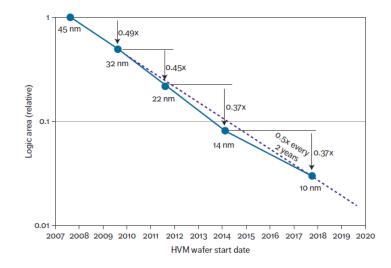

| Figure 3  | – Minimum feature size scaling trend for Intel logic technologies [15, 19].                                                                                                                                | 3  |

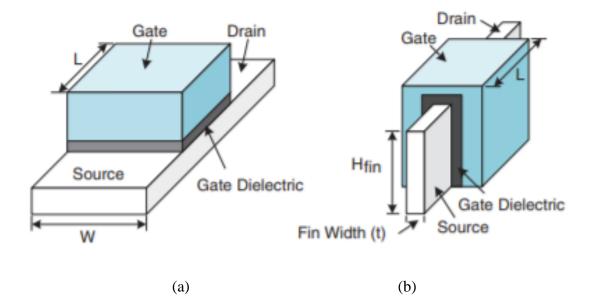

| Figure 4  | – Structure of (a) Planar MOSFET and (b) FinFET device [23].                                                                                                                                               | 4  |

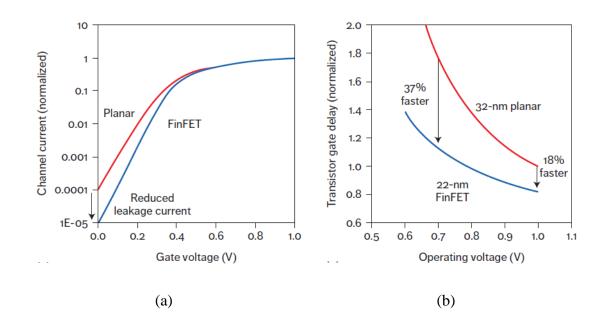

| Figure 5  | <ul> <li>Comparison of planar versus FinFET transistor electrical characteristics. (a) Channel current versus gate voltage. (b) Transistor gate delay versus operating voltage [15].</li> </ul>            | 5  |

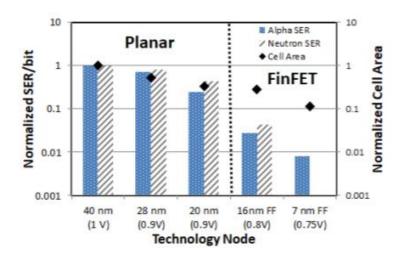

| Figure 6  | – Normalized scaling trends in the per-bit alpha and neutron SER of SRAMs as a function of technology node [22].                                                                                           | 6  |

| Figure 7  | - Intel's development of the technology node for the past five generations [15].                                                                                                                           | 6  |

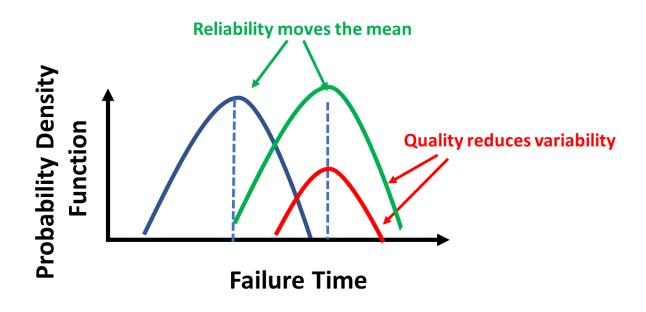

| Figure 8  | – Difference between the purposes of reliability and quality.                                                                                                                                              | 7  |

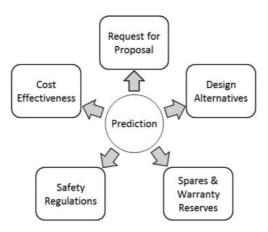

| Figure 9  | – Prediction uses [33].                                                                                                                                                                                    | 8  |

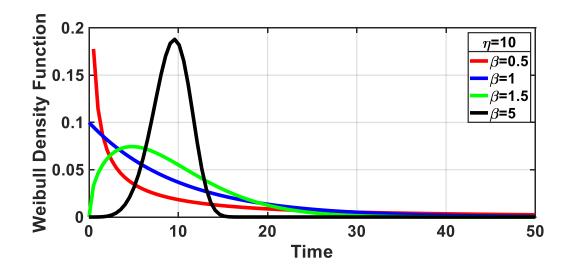

| Figure 10 | – Weibull distributions with different shape parameters, $\beta$ , and same scale parameter, $\eta$ .                                                                                                      | 9  |

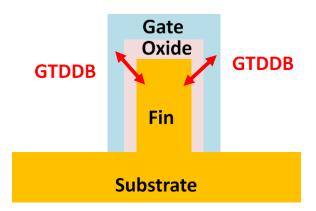

| Figure 11 | - FEOL TDDB breakdown in the gate region of a FinFET transistor.                                                                                                                                           | 12 |

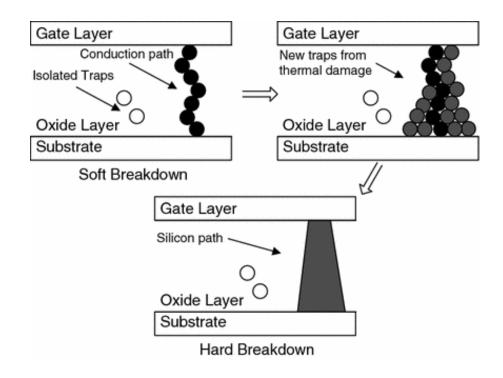

| Figure 12 | - Generation of traps leading to gate oxide breakdown [42].                                                                                                                                                | 12 |

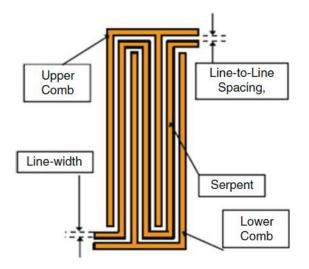

| Figure 13 | - BEOL TDDB breakdown occurs between the spacing of two interconnect wires [47].                                                                                                                           | 14 |

| Figure 14 | – Formation of hillock and void resulting from electromigration.                                                                                                                                           | 15 |

| Figure 15 | – Electromigration breakdown in an interconnect wire [52].                                                                                                                                                 | 15 |

| Figure 16 | – MTDDB breakdown occurs in the region between the contact and the gate.                                                                                                                                   | 16 |

| Figure 17 | <ul> <li>Ring oscillator composed of identical invertors and physical<br/>interconnections connected together.</li> </ul>                                                                                                                                                                                                                                                | 18 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

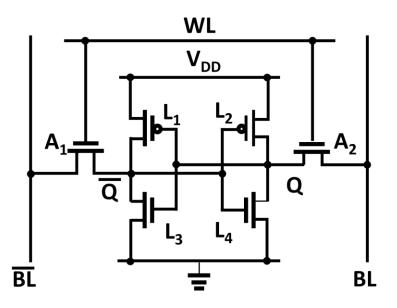

| Figure 18 | – An SRAM is composed of six transistors, where $A_1$ and $A_2$ are the access transistors, and $L_1$ , $L_2$ , $L_3$ and $L_4$ are the latch transistors.                                                                                                                                                                                                               | 19 |

| Figure 19 | – Illustration of a test structure [12].                                                                                                                                                                                                                                                                                                                                 | 22 |

| Figure 20 | – Implementation of the MLE algorithm.                                                                                                                                                                                                                                                                                                                                   | 22 |

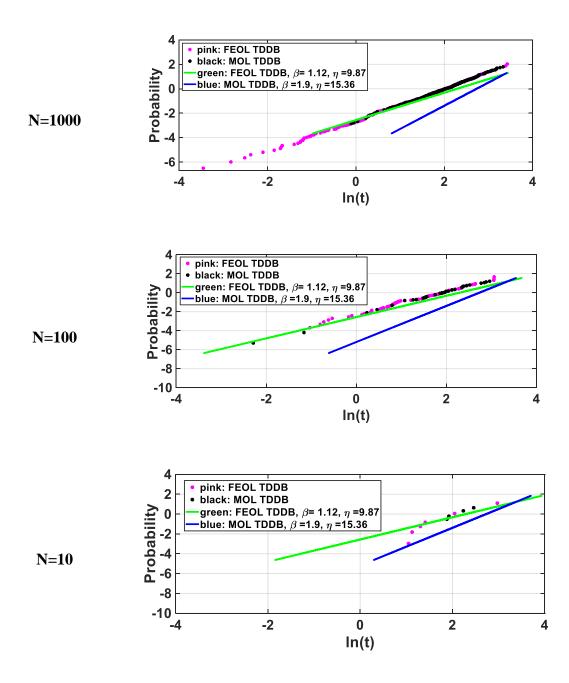

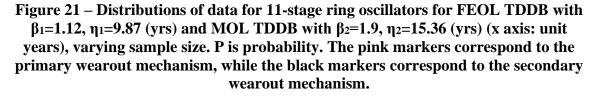

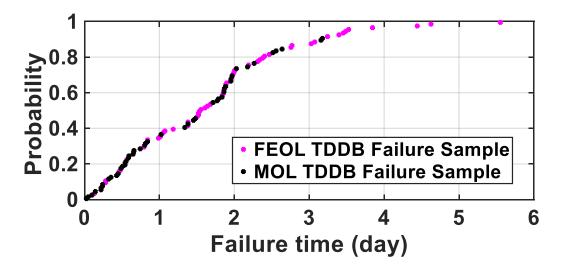

| Figure 21 | – Distributions of data for 11-stage ring oscillators for FEOL TDDB with $\beta_1$ =1.12, $\eta_1$ =9.87 (yrs) and MOL TDDB with $\beta_2$ =1.9, $\eta_2$ =15.36 (yrs) (x axis: unit years), varying sample size. P is probability. The pink markers correspond to the primary wearout mechanism, while the black markers correspond to the secondary wearout mechanism. | 28 |

| Figure 22 | – Parameter errors as a function of sample size for extracted competing mechanisms, FEOL TDDB with $\beta_1$ =1.12, $\eta_1$ =9.87 (yrs) and MOL TDDB with $\beta_2$ =1.9, $\eta_2$ =15.36 (yrs).                                                                                                                                                                        | 29 |

| Figure 23 | – Sorting accuracy of 93.0% for FEOL TDDB (1 <sup>st</sup> dist.) vs. EM failure (2 <sup>nd</sup> dist.) in 14nm FinFET ring oscillators for a sample size of 100.                                                                                                                                                                                                       | 34 |

| Figure 24 | - FEOL TDDB selectivity in 14nm FinFET ring oscillators.                                                                                                                                                                                                                                                                                                                 | 36 |

| Figure 25 | – MOL TDDB selectivity in 14nm FinFET ring oscillators.                                                                                                                                                                                                                                                                                                                  | 37 |

| Figure 26 | <ul> <li>Test times for 11-stage ring oscillators at accelerated conditions</li> <li>(1.37V, 194.72OC) for a sample size of 100.</li> </ul>                                                                                                                                                                                                                              | 37 |

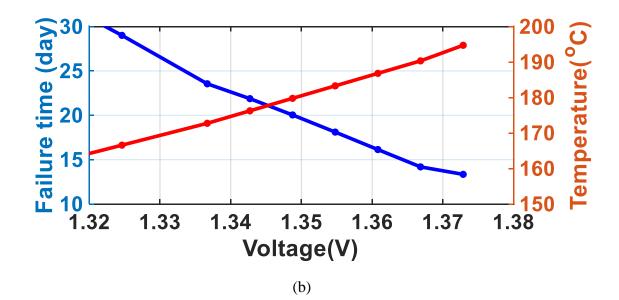

| Figure 27 | - Failure time for 100th sample out of 100 samples at FEOL TDDB=0.5 selectivity (a) as a function of voltage and temperature (b) close-up.                                                                                                                                                                                                                               | 38 |

| Figure 28 | - Failure time for 1000th sample out of 1000 samples at FEOL TDDB=0.5 selectivity (a) as a function of voltage and temperature (b) close-up.                                                                                                                                                                                                                             | 39 |

| Figure 29 | – Sorting accuracy of 80% for FEOL TDDB (1st dist.) vs. MOL failure (2nd dist.) in 14nm FinFET ring oscillators for a sample size of 100.                                                                                                                                                                                                                                | 40 |

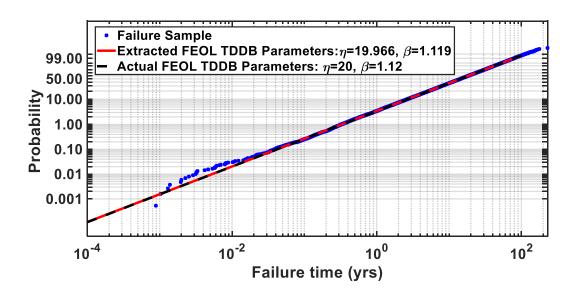

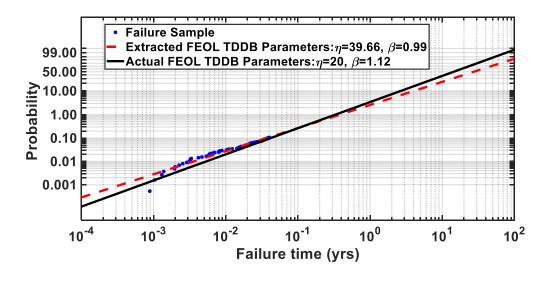

| Figure 30 | – SRAM failure samples due to FEOL TDDB for (a) a sample size of 94,000 with extracted FEOL TDDB failure parameters, $\eta$ = 19.966 and $\beta$ =1.119, and (b) a sample size of 100 out of 94,000                                                                                                                                                                      | 46 |

|           | SRAM cells with extracted FEOL TDDB failure parameters of $\eta$ =39.66 and $\beta$ =0.99.                                                                                                                                                                                                                                                  |    |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

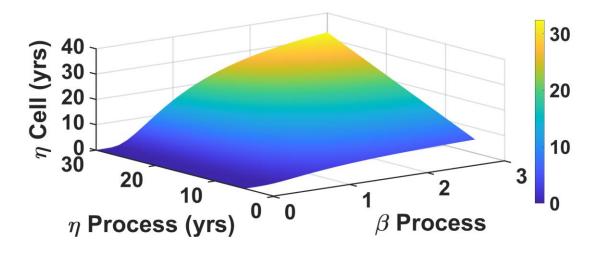

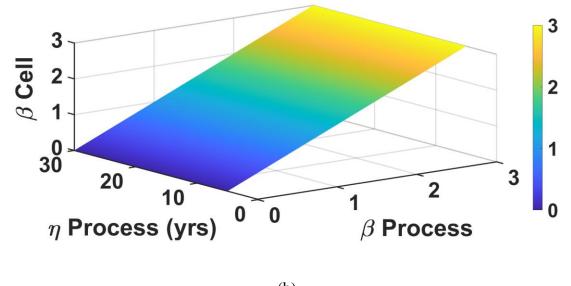

| Figure 31 | – Mapping between process-level Weibull parameters ( $\eta$ and $\beta$ ) and SRAM cell Weibull parameters for (a) $\eta$ and (b) $\beta$ for FEOL TDDB.                                                                                                                                                                                    | 47 |

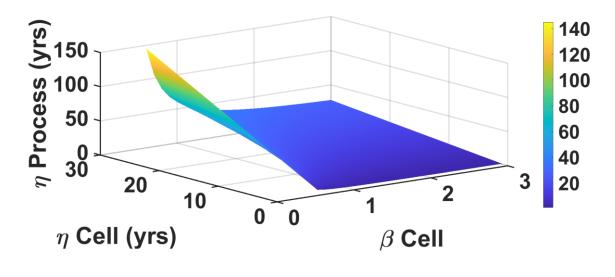

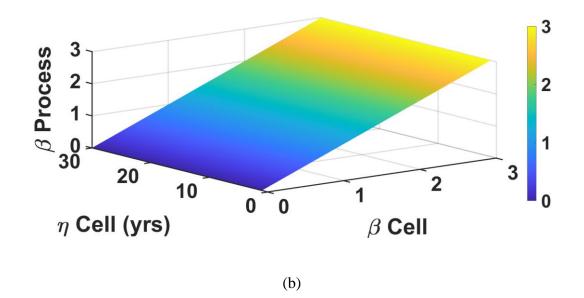

| Figure 32 | – Inverse mapping between process-level Weibull parameters ( $\eta$ and $\beta$ ) and SRAM cell Weibull parameters for (a) $\eta$ and (b) $\beta$ for FEOL TDDB.                                                                                                                                                                            | 48 |

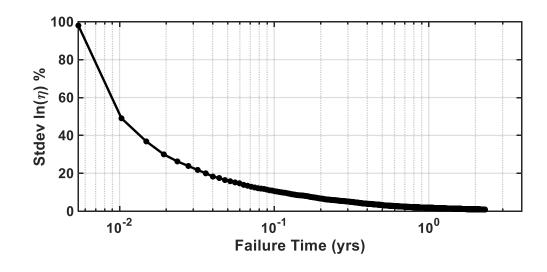

| Figure 33 | – Standard deviation error of the extraction of $ln(\eta)$ as a function of time for the (a) SRAM with $\eta$ =20 yrs, $\beta$ =1.12 and (b) a single device.                                                                                                                                                                               | 50 |

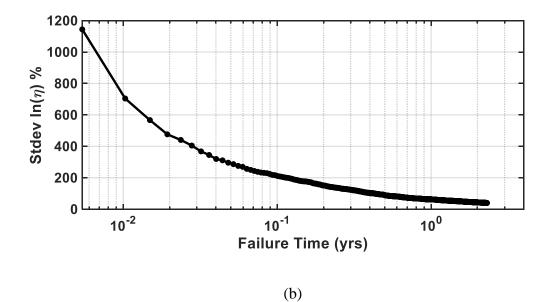

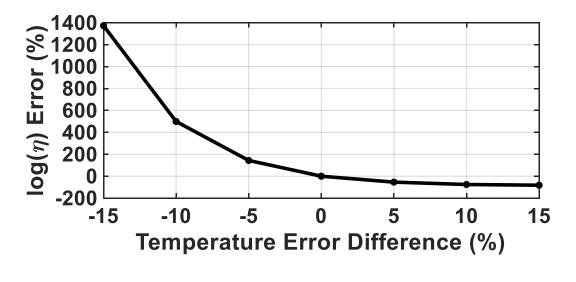

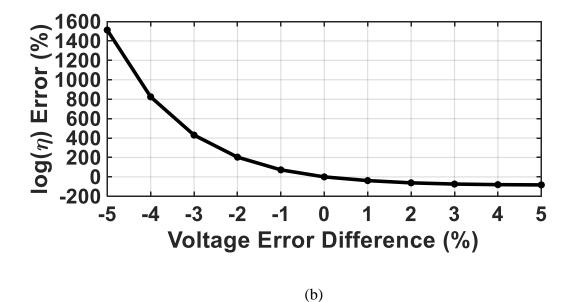

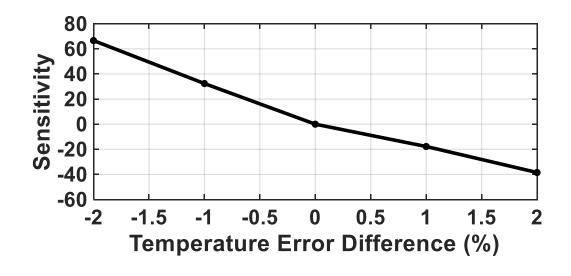

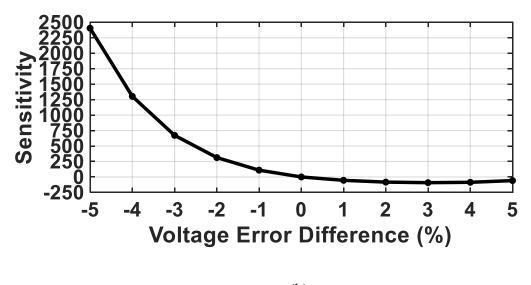

| Figure 34 | <ul> <li>Percent changes in errors in device characteristic lifetime estimation from variations in (a) temperature and (b) voltage.</li> <li>Voltage error differences above 5% causes the SRAM to fail upon startup and below -5% causes the SRAM to have essentially infinite characteristic lifetimes (e.g. above 300 years).</li> </ul> | 52 |

| Figure 35 | – Sensitivity of the extraction of ln ( $\eta_{device}$ ) to changes in (a) temperature and (b) voltage.                                                                                                                                                                                                                                    | 54 |

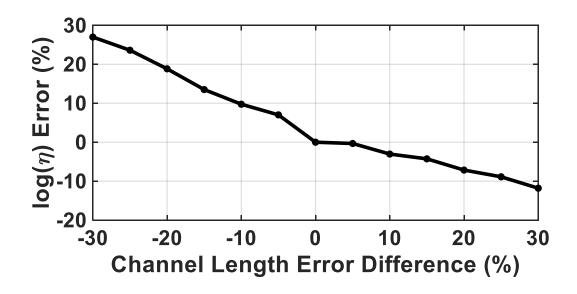

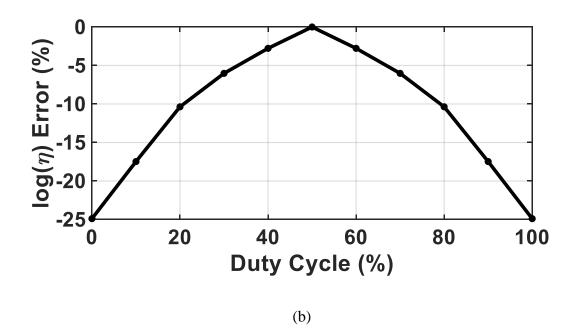

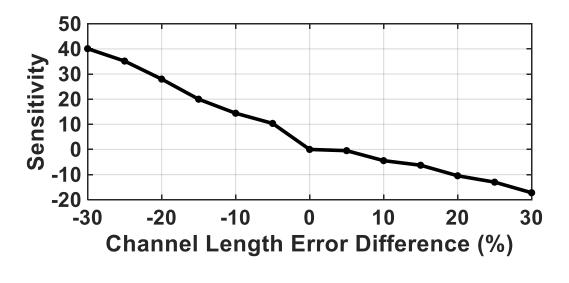

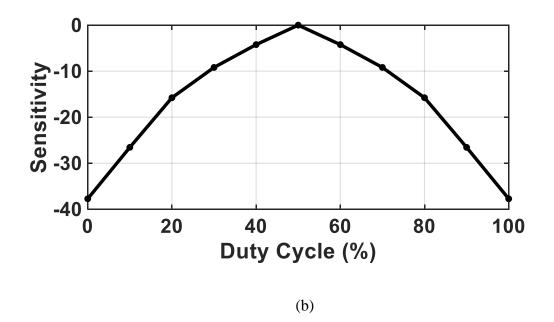

| Figure 36 | - Percent changes in errors for characteristic lifetime from variations in (a) channel length and (b) duty cycle (error calibrated to a duty cycle of 50%).                                                                                                                                                                                 | 56 |

| Figure 37 | - Sensitivity resulting from changes in (a) channel length and (b) duty cycle.                                                                                                                                                                                                                                                              | 57 |

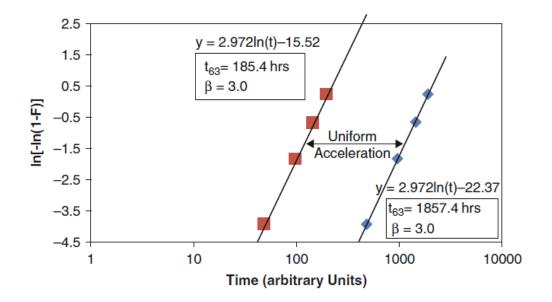

| Figure 38 | – Example of acceleration of failure distribution [12].                                                                                                                                                                                                                                                                                     | 58 |

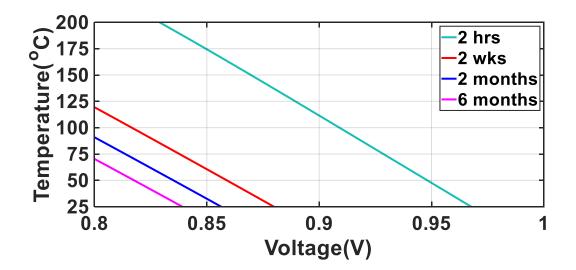

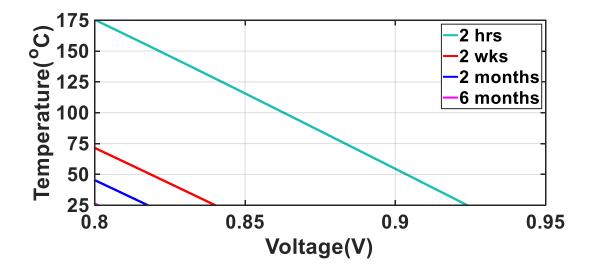

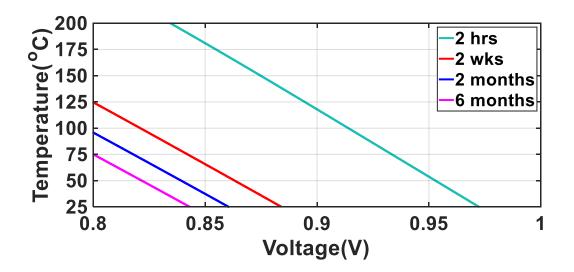

| Figure 39 | - Contour plot of the 63% failure probability (characteristic lifetime) as a function of temperature and voltage acceleration, for accelerated testing of the 1001-stage ring oscillator, with testing times ranging from two hours to six months.                                                                                          | 60 |

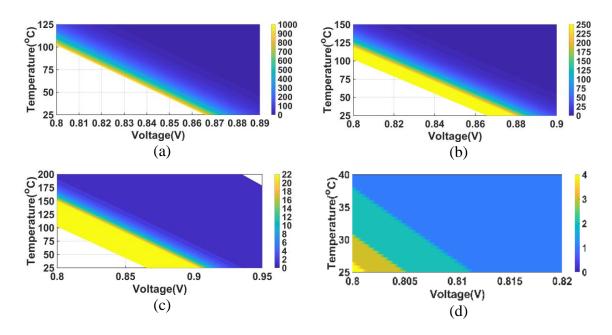

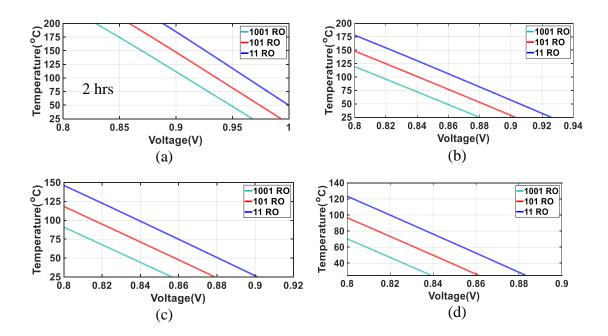

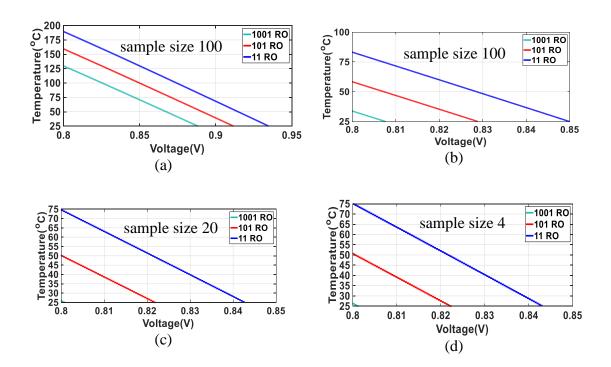

| Figure 40 | - Sample size needed produce a single failure with 95% confidence as a function of voltage and temperature for a 1001-stage ring oscillator for a testing time of (a) two hours (b) two weeks (c) two months and (d) six months.                                                                                                            | 62 |

| Figure 41 | – Contour plot for sample size of four to produce at least 1 failure with 95% confidence as a function of voltage and temperature for a 1001-stage ring oscillator with testing time ranging from two hours to six months.                                                                                                                  | 62 |

| Figure 42 | <ul> <li>Sample size needed produce a single failure with 95% confidence as a function of voltage and temperature for a 11-stage ring oscillator for a testing time of (a) two hours (b) two weeks (c) two months and (d) six months.</li> </ul>                                                                                                                                                                                                                                                           | 63 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 43 | - Contour plot for sample size of four to produce at least 1 failure with 95% confidence as a function of voltage and temperature for a 11-stage ring oscillator with testing time ranging from two hours to six months.                                                                                                                                                                                                                                                                                   | 63 |

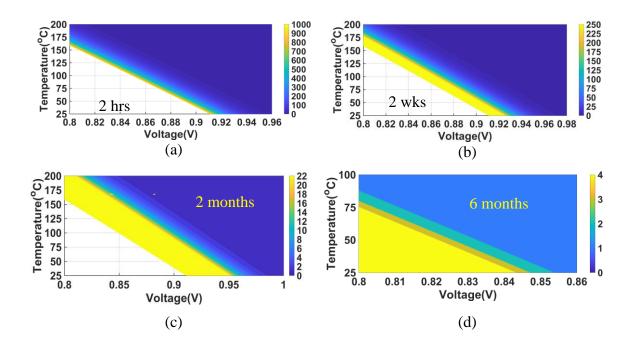

| Figure 44 | - Comparison of the contour plots for the number of stages and 63% failure probability (characteristic lifetime) as a function of voltage and temperature for (a) 2 hours (b) 2 weeks (c) 2 months and (d) 6 months.                                                                                                                                                                                                                                                                                       | 64 |

| Figure 45 | <ul> <li>Comparison of the number of stages and the test conditions needed to detect at least one failure for various sample sizes as a function of voltage and temperature for test times of (a) two hours (b) two weeks (c) two months and (d) six months.</li> </ul>                                                                                                                                                                                                                                    | 65 |

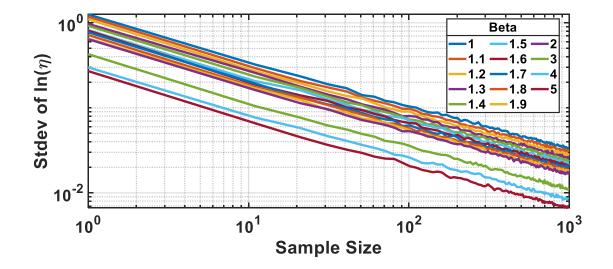

| Figure 46 | – Standard deviations of estimates of the errors in $ln(\eta)$ using Monte Carlo simulations.                                                                                                                                                                                                                                                                                                                                                                                                              | 68 |

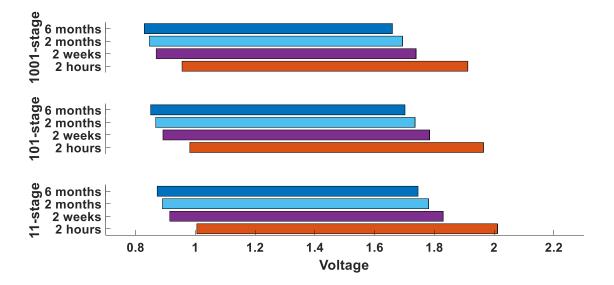

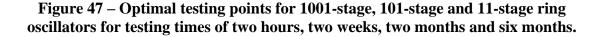

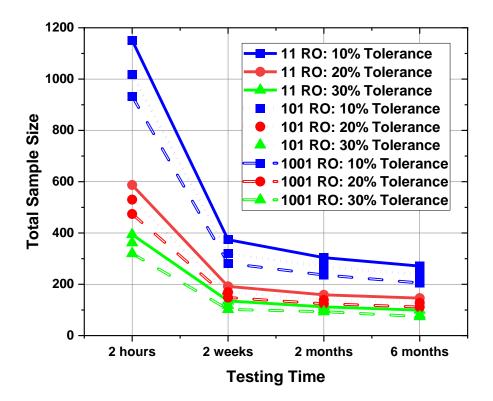

| Figure 47 | – Optimal testing points for 1001-stage, 101-stage and 11-stage ring oscillators for testing times of two hours, two weeks, two months and six months.                                                                                                                                                                                                                                                                                                                                                     | 69 |

| Figure 48 | - For a sample size of 2000, a comparison of 11-stage, 101-stage<br>and 1001-stage ring oscillators for a testing time of two hours,<br>two weeks, two months and six months in terms of (a) the lowest<br>tolerance, (b) the corresponding percentage of the sample at the<br>lower voltage point to achieve the minimum tolerance, (c) the<br>corresponding lower voltage point to achieve the minimum<br>tolerance, and (d) the corresponding higher voltage point to<br>achieve the minimum tolerance. | 72 |

| Figure 49 | - For a sample size of 2000, a comparison of 11-stage, 101-stage<br>and 1001-stage ring oscillators for a testing time of two hours,<br>two weeks, two months and six months in terms of (a) the lowest<br>tolerance, (b) the corresponding percentage of the sample at the<br>lower voltage point to achieve the minimum tolerance, (c) the<br>corresponding lower voltage point to achieve the minimum<br>tolerance, and (d) the corresponding higher voltage point to<br>achieve the minimum tolerance. | 73 |

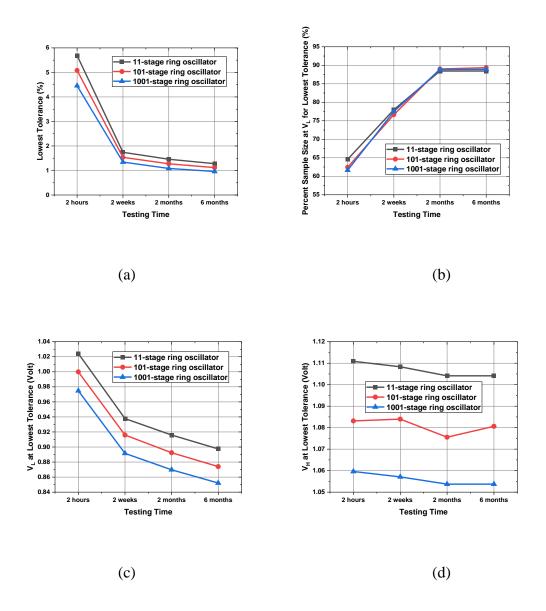

| Figure 50 | – Relationship between percent sample size at the lower voltage and the tolerance for the 11-stage, 101-stage and 1001-stage ring                                                                                                                                                                                                                                                                                                                                                                          | 74 |

х

oscillators with a testing time of two weeks. (Tolerances above 30% are not shown for clarity.)

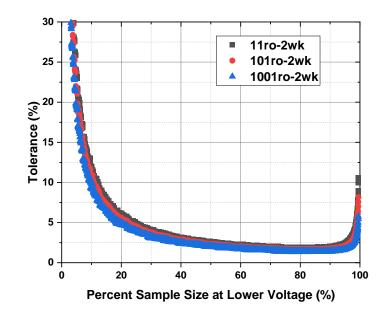

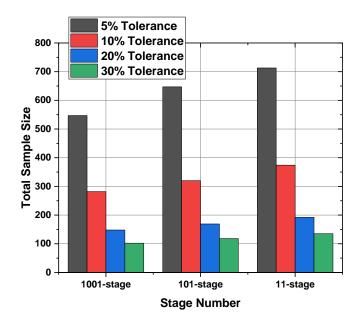

| Figure 51 | <ul> <li>Comparison between the total sample size and the testing time<br/>for 1001-stage, 101-stage and 11-stage ring oscillators to achieve<br/>a 10%, 20% and 30% tolerance.</li> </ul> | 75 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 52 | <ul> <li>Relationship between percent tolerance and number of stages<br/>for a testing time of two weeks.</li> </ul>                                                                       | 76 |

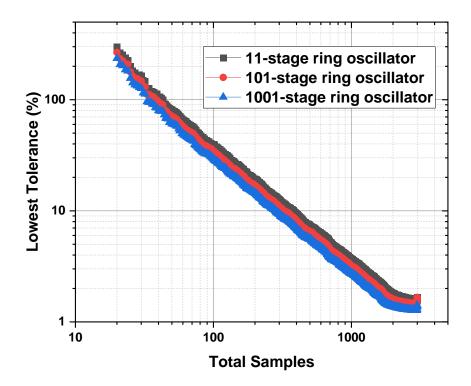

| Figure 53 | – Relationship between lowest tolerance and total sample size at a two week testing time for 11-stage ring oscillator, 101-stage ring oscillator, and 1001-stage ring oscillator.          | 77 |

# LIST OF SYMBOLS AND ABBREVIATIONS

- EM Electromigration

- FEOL TDDB Front-end-of-line time-dependent dielectric breakdown (or front-end gate oxide breakdown)

- FinFET Fin field-effect transistor

- GOBD Front-end-of-line time-dependent dielectric breakdown (or front-end gate oxide breakdown)

- GTDDB Front-end-of-line time-dependent dielectric breakdown (or front-end gate oxide breakdown)

- MLE Maximum Likelihood Estimation

- MOL TDDB Middle-of-line time-dependent dielectric breakdown

- MOSFET Metal oxide semiconductor field-effect transistor

- MTDDB Middle-of-line time-dependent dielectric breakdown

- Pdk Process design kit

## SUMMARY

The objective of this research is to develop methodologies for the failure analysis of circuits, as well as investigate the factors for accelerating testing for front-end-of-line time-dependent dielectric breakdown (FEOL TDDB). As the technology node enters into a new era where the planar MOSFET has now transitioned to FinFET structures due to device scaling, new reliability concerns arise. Therefore, it is critical to be able to understand and predict the failure for integrated circuits, especially as new emerging technologies, such as autonomous vehicles and wearable devices, are increasing the bar for reliability standards.

In this thesis, the separation of wearout mechanisms for circuits will be investigated, and the identification of failure modes for the failure samples will be analyzed. SRAMs and ring oscillators based on the 14nm FinFET GlobalFoundries/Samsung/IBM PDK will be used to study the failure modes. The systematic and random errors for online monitoring of SRAMS will also be examined.

Furthermore, the testing plans for acceleration testing will also be explored for ring oscillators. The effects of stage number and testing time will be discussed. Error reduction through sampling will also be used to find the best testing conditions for accelerated testing.

This work provides a way for engineers to better understand aging monitoring of circuits, and to design better testing to collect failure data. With these developments, engineers may make improved failure predictions for growing complex systems. In

addition, the circuit design and manufacturing processes can be enhanced with better yield and product performance.

## **INTRODUCTION**

Semiconductor devices and circuits are the core components of electronic devices. However, for these electronic devices to perform practically, reliability goals must be fulfilled [1], which has becoming even more challenging due to the increasing complexity in semiconductor manufacturing [2]. Furthermore, emerging technologies, such as autonomous vehicles and wearable sensors for health monitoring, are becoming increasingly interrelated with public safety, making the need for the assessment of highly reliable complex systems increasingly important [3-6]. Particularly for autonomous vehicles, the reliability standards are raised higher than traditional vehicles [7].

Reliability is the ability of a device to conform to its electrical, visual, and mechanical specifications over a specified period of time under specified conditions [8]. The development of technology, processes, and standards are made to ensure the reliability of semiconductor devices during application [9]. Reliability engineering is built upon a vast set of disciples, such as physics, statistics, and materials, etc., to ensure the continuous improvement of every device.

Reliability is often confused with quality, but these two have different meanings. Quality refers to the device meeting its specifications, but reliability refers to the time dependence of the device degradation [10]. Degradation is a result of the Second Law of Thermodynamics, where the entropy of isolated systems will increase over time to move to a stable state in order to lower its Gibbs Potential Free Energy, as shown in Figure 1 [11]. The degradation will affect the device parameter, as shown in Figure 2 [12]. The device parameter may increase or decrease as a result over time.

Figure 1 – Illustration of the material degradation reaction. The material will move from the initial state to the degraded state in order to lower its Gibbs Potential Free Energy [12].

Figure 2 – Materials degradation in a device can cause device parameter S to degrade with time, which can be increasing or decreasing [12].

Here, this thesis is focused on device failure under stress, and how it impacts circuit reliability. Stress is any external agent that can cause degradation to occur in the material properties to the point where the device can no longer function properly in its intended application . All material will eventually degrade over time leading to device failure, so it is critical to pinpoint when the device cannot operate properly when designing products.

### 1.1 Planar MOSFET and FinFET Device Structures

In recent years, the shrinkage of device dimensions has allowed the density of integrated circuits on a chip to increase, lower costs and increase performance [13, 14], as shown in Figure 3 [15]. With each new technology node generation developed from the result of device scaling, reliability concerns arise [16], which may be due to the device structure or fabrication changes[17]. As a result, one of the most important changes from the decrease in the gate oxide length is the device structure transition from planar metal oxide semiconductor field-effect transistor (MOSFET) device to fin field-effect transistor (FinFET) structure [18].

Figure 3 – Minimum feature size scaling trend for Intel logic technologies [15, 19].

The MOSFET device structure is the traditional device structure used in the semiconductor industry. It is composed of a gate that controls the current flowing from the source to drain, as shown in Figure 4 (a). However, with the scaling of process technology, the gate length has decreased dramatically, making it difficult for the gate to control the current [20].

The FinFET structure was developed to address the increased leakage current and short channel effects of planar MOSFETs resulting from the shrinking size of the devices [21]. It has also lowered the soft error rates in static random-access memory [22]. The FinFET structure has the channel elevated, so that the gate can surround it on all three sides, looking like a fin, as shown in Figure 4 (b).

Figure 4 – Structure of (a) Planar MOSFET and (b) FinFET device [23].

The improvement in the electrical characteristics from switching to the FinFET structure can be seen in Figure 5. However, the different structure and fabrication process for FinFETs introduces new reliability issues [24-26]. For example, the 3D structure of FinFETs gives rise to the concern of middle-of-line time-dependent dielectric breakdown, which was not previously critical in the planar MOSFET structures[27, 28]. FinFETs took around a quarter of a century to transition from the first demonstration in research to a commercialized product [29]. The first commercially-wide available FinFET chips were produced from Intel starting from their 22nm node [30], which was introduced just recently as shown in Figure 7.

Figure 5 – Comparison of planar versus FinFET transistor electrical characteristics. (a) Channel current versus gate voltage. (b) Transistor gate delay versus operating voltage [15].

Figure 6 – Normalized scaling trends in the per-bit alpha and neutron SER of SRAMs as a function of technology node [22].

Figure 7 – Intel's development of the technology node for the past five generations [15].

## 1.2 Statistical Analysis of Reliability Data

To quantify reliability, reliability can also be thought of as the probability that a semiconductor device having initial satisfactory performance can continue to perform its intended function for a given time under actual usage conditions [31]. Therefore, reliability calculations are often based on statistical data collected using failure records using failure distributions. Mathematical analysis is used to predict how long devices will function. As illustrated in Figure 8, reliability aims to move the average of the failure distribution to a higher failure time, which is different than quality, which moves to reduce the variability. It is important to be able to predict the degradation of the product when it is in the field and predict the remaining life of the product over time [32]. Usages for reliability prediction are described in Figure 9 [33].

Figure 8 – Difference between the purposes of reliability and quality.

Figure 9 – Prediction uses [33].

## 1.2.1 Weibull Distribution

The Weibull distribution is a very flexible distribution often used to analyse reliability data, especially for system failure [12]. The distribution is named after Waloddi Weibull, who originally used the probability distribution in 1951 as a model for material breaking strength, but has now widespread use in describing lifetime distributions [34]. The probability density function for a two parameter Weibull distribution can be calculated as follows:

$$f(t) = \left(\frac{\beta}{\eta}\right) \left(\frac{t}{\eta}\right)^{\beta-1} exp\left[-\left(\frac{t}{\eta}\right)^{\beta}\right] \tag{1}$$

where  $\beta$  is the shape parameter, also known as the dispersion parameter, and  $\eta$  is the characteristic lifetime, also known as the scale parameter, which is the lifetime at the 63% failure probability. The exponential distribution is a special case of the Weibull distribution where  $\beta = 1$ . Examples of the Weibull distribution are shown in Figure 10.

Figure 10 – Weibull distributions with different shape parameters,  $\beta$ , and same scale parameter,  $\eta$ .

The time-to-failure is when a device parameter degrades to the point that the device cannot function properly, and the characteristic lifetime can be used as an indicator of the time-to-failure. The time-to-failure of circuits can be investigated using compact modeling [35], where the failure modes can be described using the Weibull distribution. The failure modes will be described in more detail in Section 1.3.

### 1.2.2 Maximum Likelihood Estimation

Maximum likelihood estimation (MLE) is a statistical method that determines the parameters of a model from given observations, which would be failure times in the reliability applications discussed in this proposal, by finding the parameter values that maximizes the likelihood or highest probability of getting the observations (time-to-failure data in this proposal) given the parameters. The reasoning is that the estimate which explains the data best will be the best estimator. MLE is a powerful analysis tool that can be applied to both censored (the condition when the value of a measurement or observation

is only partially known) and uncensored failure data. MLE is used in this thesis to find the competing Weibull parameters for competing wearout mechanisms in circuits.

#### 1.2.3 Quasi-Newton Method

The quasi-Newton method is a calculation method that can find the minima or maxima of functions. It is based on Newton's method, which uses both the first and second derivative (Hessian matrix) values to find the roots of a function. Newton's method can be thought of as similar to a gradient descent method, which is a first-order method, but with the addition of using second-order information to change the step size and direction. This addition of the Hessian information helps avoid descent directions that plateau too quickly. Therefore, the quasi-Newton method is somewhere of an intermediate between Newton's method and gradient descent. The quasi-Newton method uses fewer steps to find the optimal value, taking more time to execute each step, while the gradient descent method, which is a first-order method, has the opposite properties [36].

Newton's method is generally computationally expensive and slow, because it is more difficult to calculate the second derivative. The quasi-Newton method overcomes this problem by approximating the Hessian matrix instead of computing it directly. Various algorithms are available that can be used to find the Hessian matrix.

## 1.3 Wearout Mechanisms

Reliability concerns in transistor devices must be addressed in order to ensure that a product can perform its required functions for a stated period of time, which can generally be divided into front-end and back-end wearout mechanisms [37]. One of the most

important front-end wearout mechanisms typically found in both planar MOSFET and FinFET structures is the front-end-of-line time-dependent dielectric breakdown (FEOL TDDB), also known as the front-end gate oxide breakdown (GOBD). For back-end wearout mechanisms, both planar MOSFET and FinFET devices have back-end-of-line time-dependent dielectric breakdown (BEOL TDDB or BTDDB) and electromigration (EM). However, FinFET devices have an extra wearout mechanism that is not found in planar MOSFET devices, which is the middle-of-line time-dependent dielectric breakdown (MOL TDDB or MTDDB), that occurs due to process scaling [38].

#### 1.3.1 Front-end Wearout Mechanism

Front-end-of-line time-dependent dielectric breakdown (FEOL TDDB), also known as front-end gate oxide breakdown (GOBD or GTDDB), is the main front-end wearout mechanism found in transistors, as shown in Figure 11. When transistors are turned on, the gate dielectric region is subjected to voltage and thermal stress, and traps can build-up that degrade the gate oxide material [39]. As shown in Figure 11, the traps will eventually form a conduction path, leading to the breakdown of the oxide material. For the 45-65nm, technology nodes, the gate oxide can be as thin as 1.2 nm [40], where the same defect size will have a higher impact compared to the older technology node generations with thicker oxides, because the defect size is now impacting a larger portion of the oxide thickness for the thin oxides [41].

Figure 11 – FEOL TDDB breakdown in the gate region of a FinFET transistor.

Figure 12 – Generation of traps leading to gate oxide breakdown [42].

FEOL TDDB can be modeled as [43]:

$$\eta = A_{ox} \left(\frac{1}{WL}\right)^{\frac{1}{\beta}} e^{\frac{-1}{\beta}} V^{a+bT} exp\left(\frac{c}{T} + \frac{d}{T^2}\right) s^{-1}$$

(2)

where  $\beta$  is the shape parameter, and  $\eta$  is the time-to-failure at the 63% probability point. W and L are the device width and length, s is the probability of stress, T is temperature, V is gate voltage, respectively. In addition, a, b, c, d, and A<sub>ox</sub> are fitting parameters, which depend on the type of technology process used.

#### 1.3.2 Back-end Wearout Mechanisms

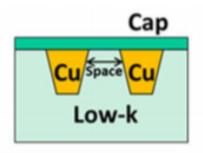

# 1.3.2.1 <u>Back-end-of-line time-dependent dielectric breakdown (BEOL TDDB or</u> <u>BTDDB)</u>

Back-end-of-line time-dependent dielectric breakdown (BEOL TDDB or BTDDB) is the dielectric breakdown between adjacent metal interconnect lines[44], as shown in Figure 13. BEOL TDDB can be modelled as [45]:

$$\eta = A_{BEOL} L_i^{\frac{-1}{\beta}} exp\left(-\gamma E^m + \frac{E_a}{kT}\right) s^{-1}$$

(3)

where  $A_{BEOL}$  is a constant that is dependent on the technology process,  $L_i$  is the vulnerable length (the distance where the metals run parallel to each other),  $E_a$  is the activation energy (~0.5 eV), T is temperature,  $\gamma$  is the field acceleration factor, s is the probability of stress, and k is the Boltzmann constant. E is the electric field, which is a function of voltage, V and the distance between the conductions,  $S_i$ , i.e.,  $E=V/S_i$ , and m is  $\frac{1}{2}$  for the  $\sqrt{E}$  model [46].

Figure 13 – BEOL TDDB breakdown occurs between the spacing of two interconnect wires [47].

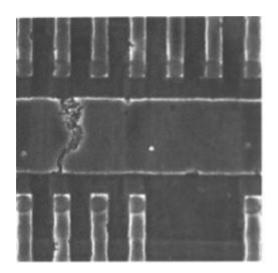

### 1.3.2.2 <u>Electromigration (EM)</u>

Electromigration (EM) is the dislocation of atoms in the lattice of interconnect metals due to the momentum transfer of electrons [48]. The movement of atoms can cause voids due to the absence of atoms at one end and hillocks due to the build-up of atoms at the other end [49], as shown in Figure 14. This phenomena results in the function failure of circuits due to the loss of connections [50], as can be seen in the image in Figure 15. It can be modelled as [51]:

$$\eta = A_{EM} J^{-n} exp\left(\frac{E_a}{kT}\right) \tag{4}$$

where  $A_{EM}$  is a constant that is dependent on the technology process, T is temperature, J is current density,  $E_a$  is the activation energy (0.85 eV), n=1 (void growth), and k is the Boltzmann constant.

Figure 14 – Formation of hillock and void resulting from electromigration.

Figure 15 – Electromigration breakdown in an interconnect wire [52].

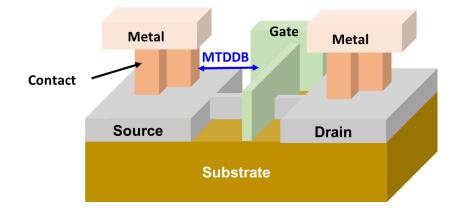

### 1.3.3 Middle-of-line Wearout Mechanism

Due to the increasing complexity of the technology nodes, the fabrication process for between the wafer fabrication and back-end assembly has now evolved into a separate process, called middle of the line (MEOL) process [53, 54]. The MEOL process can be performed after the front side treatment/bumping, or before the chip stacking assembly [55]. However, controlling the fabrication process between the polysilicon control gate and the diffusion contact may be challenging due to variations from the overlay, via size, line width, line edge roughness, defects, and image irregularities, which gives rise to dielectric breakdown in the middle-of-line [56]. Therefore, the middle-of-line time-dependent dielectric breakdown (MOL TDDB or MTDDB) is a growing concern due to the architecture change in FinFET transistors and dimension scaling [57], as shown in Figure 16, which can be found in advanced technology nodes [58]. MOL TDDB is similar to BEOL TDDB, but the dielectric breakdown occurs in the spacing between the gate and the source/drain contacts [59]. Therefore, the device-level model is similar to BEOL TDDB as follows [60]:

$$\eta = A_{MOL} L_i^{\frac{-1}{\beta}} exp\left(-\gamma E^m + \frac{E_a}{kT}\right) s^{-1}$$

(5)

where  $A_{MOL}$  is a constant the depends on the material properties of the dielectric, and m is 1 for the E model [61]. All other parameters are similar to the BEOL TDDB parameters.

Figure 16 – MTDDB breakdown occurs in the region between the contact and the gate.

### 1.4 Circuit Case Studies

#### 1.4.1 Process Design Kit (PDK)

The circuits used in this research are based on the 14nm FinFET technology node using the process design kit (PDK) jointly developed by GlobalFoundries (GF)/Samsung/IBM. A PDK is a set of files created by the foundry to model a fabrication process for the design tools that are used to design an integrated circuit. The circuits are investigated using the PDK files in Cadence Virtuoso, SPICE simulation, and Mentor Calibre for design rule checks of the layouts. The types of circuits used in this thesis are focused on ring oscillators and static random-access memories.

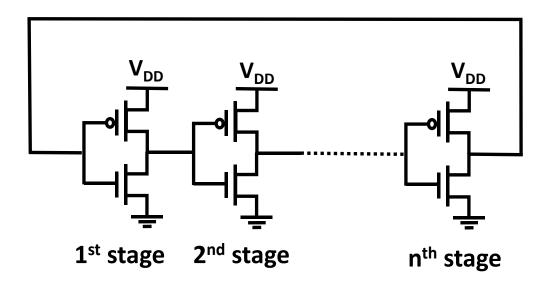

### 1.4.2 Ring Oscillators

Ring oscillators are a type of circuit that are often used in process validation [62, 63], such as in monitoring the gate delay and speed-power product of fabricated circuits due to easy implementation. The simplest type of a ring oscillator structure is composed of identical invertors and physical interconnections, as shown in Figure 17, where the output signal oscillates with a certain period depending on the gate delay. The gate delay is the length of time when the input to a logic gate becomes stable and valid to change, to the time that the output of that logic gate is stable and valid to change.

Figure 17 – Ring oscillator composed of identical invertors and physical interconnections connected together.

To oscillate, the ring oscillator requires an odd number of stages. A stage number is the number of invertors (nmos and pmos connected together in a series) in a ring oscillator. The duty cycle of a ring oscillator is the ratio of the time the circuit is on compared to the time the circuit is off, which can be used to describe the percentage of time a signal is active in the ring oscillator.

### 1.4.3 Static random-access memory (SRAM)

Static random-access memory (SRAM) is a type of circuit that retains data bits in its memory as long as power is supplied [64], occupying a major portion of the total area and power of system-on-chip ICs [65]. It is also the most common embedded-memory option for CMOS ICs [66]. The need for low power consumption and high performance for ultra-low power circuits, such as mobile and wearable devices, are the driving force for the demand for SRAMs [67].

As shown in Figure 18, an SRAM is composed of six transistors, where  $A_1$  and  $A_2$  are the access transistors, and  $L_1$ ,  $L_2$ ,  $L_3$  and  $L_4$  are the latch transistors. The data bit is stored in the latch transistors, which is the basic memory cell. The access transistors are used to control the access to the memory cell when reading and writing the data.

Figure 18 – An SRAM is composed of six transistors, where A<sub>1</sub> and A<sub>2</sub> are the access transistors, and L<sub>1</sub>, L<sub>2</sub>, L<sub>3</sub> and L<sub>4</sub> are the latch transistors.

## **1.5 Research Objectives**

This thesis aims to implement data analysis techniques to detect and identify competing wearout mechanisms in circuits. A methodology for online monitoring is also developed to detect FEOL TDDB failures. Test plans and sampling for accelerated testing are also studied to lower errors.

# 1.6 Thesis Overview

This thesis is organized as follows. Chapter 2 will discuss the failure analysis for ring oscillators and SRAMs. Chapter 3 will describe the investigation of test conditions and sampling for accelerated testing. The conclusions and future work will be explained in Chapter 4.

## FAILURE ANALYSIS OF CIRCUITS

This thesis focuses on two types of failure analysis of circuits. The first type is when the testing time is sufficient, so the entire failure data set can be collected. For these types of data sets, the failure data may be composed of more than one wearout mechanism, so the failure modes may need to be separated. The other type is for online monitoring, where the samples are monitored as they fail [68]. Generally, this type of failure data set will be incomplete, because not all samples may have failed. Through online monitoring, the goal is to prevent the user from experiencing the effects of failure and provide , notice of impending failure to allow corrective measures to be taken, which may be necessary in safety critical applications [69, 70].

## 1.7 Separation of competing wearout mechanisms in circuits

The standard method for analyzing failure samples is through examining test structures, with a typical test structure shown in Figure 19. However, actual products use circuits, which are more complex than test structures. One of the main differences between circuits and test structures is that test structures only have a single wearout mode, but circuits have confounded wearout modes. Therefore, the results from test structures may not be reflective of actual circuits.

The collection of lifetime data on large numbers of circuits is challenging, due to test setup cost and the need for large numbers of sample circuits. Ring oscillators are an intermediate between circuits and test structures. Because ring oscillators have behaviors similar to circuits, they are used instead of test structures in this thesis to test for failure modes.

Figure 19 – Illustration of a test structure [12].

In addition, invasive diagnostic methods are generally used for failure analysis, such as transmission electron microscopy (TEM), e-beam, or scanning electron microscopy (SEM), to study the failure modes, which require samples to be cut open, for example, using focused ion beam (FIB) techniques [71, 72]. For advanced technology nodes, the metrology for TEM and other failure analysis techniques can become intricate and complex, requiring significant time to prepare and analyze samples [73]. This causes a wait time to receive the failure results and high costs, which can impact product costs if done too often.

Furthermore, electron radiation from TEM and other failure analysis techniques may alter the composition or microstructure of the sample, making it difficult to interpret the results authentically [74, 75]. Also, for technology nodes for 10nm and below, when using the energy dispersive X-ray spectrometer in TEM and other failure analysis techniques for elemental identification, the peak for the composition analysis may overlap due to more and more elements used in FEOL TDDB and MOL TDDB processes[76]. Therefore, it is necessary to find a quick and non-invasive method to separate the causes of failure, so that efforts for process improvement can be prioritized.

## 1.7.1 Methodology

To analyze the confounded wearout modes in a circuit, data analysis techniques are used to separate the competing wearout mechanisms. The advantages for using data analysis include quicker, faster, scalable, and more cost-effective analysis of complex data [77, 78], and may be implemented in the monitoring of semiconductor manufacturing [79]. The wearout mechanisms are modeled as competing wearout mechanisms, which occur when failures are due to more than one degradation mode and are independent of each other.

For competing wearout mechanisms, suppose mechanism 1 (primary breakdown mode) has a probability density function,  $f_1(t)$  and cumulative distribution function,  $F_1(t)$ . The survival function is  $R_1(t) = 1 - F_1(t)$ . Similarly, mechanism 2 (secondary breakdown mode) has the probability density function,  $f_2(t)$ ; cumulative distribution function,  $F_2(t)$ ; survival function,  $R_2(t)$ . Thus, the competing failure probability density function, f(t), can be described as below [80].

$$f(t) = P\{T_1 = t, T_2 \ge t\} \cup P\{T_1 \ge t, T_2 = t\}$$

$$= P(T_1 = t, T_2 \ge t) + P(T_1 \ge t, T_2 = t)$$

$$= P(T_1 = t) P(T_2 \ge t) + P(T_1 \ge t) P(T_2 = t)$$

$$= f_1(t) * R_2(t) + f_2(t) * R_1(t)$$

(6)

The competing failure probability density function is different than the mixed Weibull probability density function, as shown below [81]:

$$f(t) = a * f_1(t) + b * f_2(t)$$

(7)

where a and b are the mixed weights. The mixed Weibull probability density function occurs when the breakdown is due to both mechanisms at the same time and should not be confused with the competing Weibull probability density function [82]. The competing Weibull probability density function describes the breakdown at a specific failure time due to only one mechanism, but the cause can be from either mechanism 1 or 2, but not both.

MLE is employed to estimate the competing Weibull parameters. The parameter values are found by maximizing the likelihood that the process described by the model has produced the data that were observed using the likelihood function. The likelihood function describes how particular values of statistical parameters are for a given set of failure observations, and for uncensored data can be simplified from [80] as:

$$\mathcal{L}(\theta) = C \prod_{i=1}^{N} f(t_i)$$

(8)

where  $\theta$  is the set of competing Weibull parameters,  $\beta_1$ ,  $\beta_2$ ,  $\eta_1$ ,  $\eta_2$ . Generally, because the goal is to obtain  $\theta$ , not the actual value of  $\mathcal{L}(\theta)$ , it is easier to work with the log likelihood function compared to the likelihood function. The log likelihood function can be written as:

$$\ln \mathcal{L}(\theta) = \sum_{i=1}^{N} \ln f(t_i) + \ln C$$

(9)

where C is a constant.

The derivatives for MLE can also be simplified from [80] as:

$$\frac{\partial \ln \mathcal{L}(\theta)}{\partial \beta_1} = \sum_{i=1}^N \left\{ \frac{dR_1(t_i)}{d\beta_1} f_2(t_i) + \frac{df_1(t_i)}{d\beta_1} R_2(t_i) \right\} / f(t_i)$$

(10)

$$\frac{\partial \ln \mathcal{L}(\theta)}{\partial \beta_2} = \sum_{i=1}^N \left\{ R_1(t_i) \frac{df_2(t_i)}{d\beta_2} + f_1(t_i) \frac{dR_2(t_i)}{d\beta_2} \right\} / f(t_i)$$

(11)

$$\frac{\partial \ln \mathcal{L}(\theta)}{\partial \eta_1} = \sum_{i=1}^N \left\{ \frac{dR_1(t_i)}{d\eta_1} f_2(t_i) + \frac{df_1(t_i)}{d\eta_1} R_2(t_i) \right\} / f(t_i)$$

(12)

$$\frac{\partial \ln \mathcal{L}(\theta)}{\partial \eta_2} = \sum_{i=1}^N \left\{ R_1(t_i) \frac{df_2(t_i)}{d\eta_2} + f_1(t_i) \frac{dR_2(t_i)}{d\eta_2} \right\} / f(t_i)$$

(13)

$$\frac{dR_k(t)}{d\beta_k} = -R_k(t) \left(\frac{t}{\eta_k}\right)^{\beta_k} \ln\left(\frac{t}{\eta_k}\right)$$

(14)

$$\frac{df_k(t)}{d\beta_k} = \left(\frac{t}{\eta_k}\right)^{\beta_k - 1} R_k(t) \left\{ \left(\frac{1}{\eta_k}\right) + \left(\frac{\beta_k}{\eta_k}\right) \ln\left(\frac{t}{\eta_k}\right) \right\} - f_k(t) \left(\frac{t}{\eta_k}\right)^{\beta_k} \ln\left(\frac{t}{\eta_k}\right)$$

(15)

$$\frac{dR_k(t)}{d\eta_k} = R_k(t) \left(\frac{\beta_k}{\eta_k}\right) \left(\frac{t}{\eta_k}\right)^{\beta_k}$$

(16)

$$\frac{df_k(t)}{d\eta_k} = \left(\frac{\beta_k}{\eta_k}\right)^2 \left(\frac{t}{\eta_k}\right)^{\beta_k - 1} R_k(t) \left\{-1 + \left(\frac{t}{\eta_k}\right)^{\beta_k}\right\}$$

(17)

where k=1 or 2.

The quasi-Newton method using the Davidon-Fletcher-Powell algorithm, also referred to as the variable metric method, is used to optimize equation (9). The algorithm was originally proposed by Davidon in 1959 and later developed by Flectcher and Power in 1963 [83]. Because the evaluation and use of the Hessian matrix is impractical, time-consuming and costly, the Davidon-Fletcher-Powell algorithm approximates the inverse Hessian matrix instead. An initial matrix  $H_0$  is chosen (usually  $H_0$ =I, where I is the identity matrix, also called unit matrix), and the inverse Hessian is updated by the sum of two symmetric rank one matrices, which allows the algorithm to run faster than a rank two calculation. The updates continue until the optimization point is reached.

The Davidon-Fletcher-Powell algorithm was chosen, because this algorithm is suitable for a data set on the order of 10 to 1000 samples. Industrial data sets for reliability failure times are generally on the order of 10 to 1000 samples. Data sets larger than 1000 samples may take too long to monitor or may be too costly. Therefore, the Davidon-Fletcher-Powell algorithm can be applied to the failure sets and can be used to analyze the data sets quickly. The implementation is shown in Figure 20 [80].

Algorithm Procedure [80]

**1. Initial condition:**  $\theta^0 = [\beta_1, \beta_2, \eta_1, \eta_2]^T$ ,  $L^0 = lnL(\theta^0)$ 2. Set optimization direction:  $d^{i} = -S_{i}g^{i}$ , where  $S_{i} = I$  (the unit matrix),  $g^{i} = -\nabla \ln L \left(\theta^{i}\right)^{T}$ , i=0 **3. Line search:**  $\theta^{i+1} = \theta^i + \alpha_i d^i$ , where  $\alpha_i$  is the optimal step length 4. Calculate parameters for Hessian matrix and new direction:  $p^{i} = \alpha_{i}d^{i}, \ g^{i+1} = -\nabla \ln L \left(\theta^{i+1}\right)^{T}, \ q_{i} = g^{i+1} - g^{i}$ 5. Estimate inverse Hessian matrix:  $S_{i+1} = S_i + \frac{p^i p^{iT}}{p^{iT} q^i} - \frac{S_i q^i q^{iT} S_i}{q^{iT} S_i q^i}$ 6. Find set of Weibull parameters: Set i=i+1. If i=4 (number of Weibull parameters) then go to Step 7; otherwise go back to step 2. 7. Iteration procedure for optimization and stop condition: If  $|\ln L(\theta^i) - L^0| < \varepsilon$ , then stop. Otherwise, set  $L^0 = \ln L (\theta^i)$ , i=0 and go back to step 2.

## Figure 20 – Implementation of the MLE algorithm.

#### 1.7.2 Investigation of Initial Conditions vs. Sample Size

The competing wearout mechanisms for 11-stage ring oscillators based on the 14nm pdk FinFET technology node jointly developed by GlobalFoundries(GF)/Samsung/ IBM were studied using the above method to extract the competing Weibull parameters from the confounded failure data. These ring oscillators have Weibull parameters of FEOL TDDB with  $\beta_1$ =1.12,  $\eta_1$ =9.87 (yrs) and MOL TDDB with  $\beta_2$ =1.9,  $\eta_2$ =15.36 (yrs).

Before using the MLE algorithm to extract the overall competing Weibull parameters, the failure distributions of the competing wearout mechanisms were modeled by first picking a point randomly from each individual distribution. Next, the smaller value is set as the lifetime, because it is the mechanism that fails first at that time point. Then, the points are plotted as ordered pairs:  $(\ln(t_1 \ln(-\ln(1-(\frac{1}{2N}))), (\ln(t_2), \ln(-\ln(1-(\frac{3}{2N}))))))$ , etc. This was done for sample sizes N of 10, 100 and 100, as shown in Figure 21.

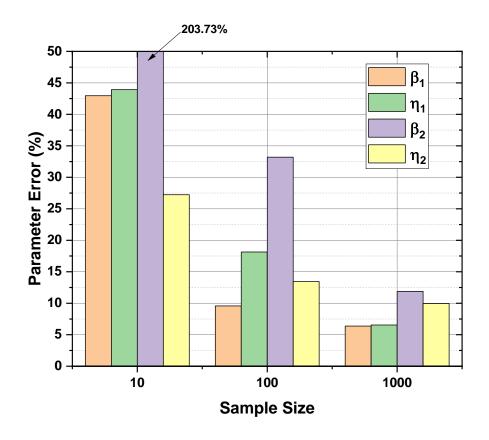

The error results of the extracted competing Weibull parameters are shown in Figure 22. The initial conditions were set at the original values to exclude the effects of randomness. As the sample size is increased, the errors for all four parameters decrease, and when the sample size is increased from an order of magnitude from 10 to 1000, the parameter errors generally decrease around 5-fold. The shape parameter of the second competing Weibull mechanism,  $\beta_2$ , has the highest error in all cases. The  $\beta_2$  value is harder to separate since it is closer to the  $\beta_1$  value, and there are fewer samples originating from the second mechanism since it fails later.

Figure 22 – Parameter errors as a function of sample size for extracted competing mechanisms, FEOL TDDB with  $\beta_1$ =1.12,  $\eta_1$ =9.87 (yrs) and MOL TDDB with  $\beta_2$ =1.9,  $\eta_2$ =15.36 (yrs).

For the cases where the initial conditions are not at the initial values, the shape and scale parameters,  $\eta$  and  $\beta$ , were both set at the same deviation from the original values at the same time. In other words, the  $\beta$  and  $\eta$  of both mechanisms were both set at 5% deviation from the initial condition, and MLE was employed to obtain the estimation results. Then, this procedure was repeated by setting both  $\beta$  and  $\eta$  of both mechanisms at 10% deviation from the initial condition, and the process was repeated again increasing the deviation by 5% each time up to the 15% deviation from the initial condition. The entire procedure was also repeated for deviation from -5% to -15% from the initial condition.

For a sample size of 10, the wearout mechanisms were able to be distinguished up to a deviation error of  $\pm 5\%$  from the actual value for the initial condition, while the sample sizes of 100 and 1000 could be separated for up to a deviation error of  $\pm 15\%$  from the actual value for the initial condition.

#### 1.7.3 Identification of Wearout Mechanism for Each Individual Sample

The previous section described a methodology to determine which competing wearout mechanisms are present in a set of failure samples. However, it is not known which samples belong to which degradation mode. Here, a methodology is developed to identify the probabilistic origin of failure for each monitored sample, determine the region of error indicating the time period where the cause of failure is unknown, and analyze the sorting accuracy. In doing so, only the necessary samples for physical failure analysis are selected instead of all failure samples, saving time and money.

As mentioned previously, the competing failure probability density function, f(t), can be described as:

$$f(t) = f_1(t) * R_2(t) + f_2(t) * R_1(t)$$

(7)

Therefore, the competing probability density function contribution from mechanism 1, called a<sub>1</sub>, is defined below:

$$a_1 = f_1(t) * R_2(t)$$

(18)

which is the probability density function portion of the overall system showing that mechanism 1 has failed but mechanism 2 is still working. Similarly, the competing probability density function contribution from mechanism 2, called a<sub>2</sub>, can be defined as:

$$a_2 = f_2(t) * R_1(t) \tag{19}$$

If the overall Weibull parameters for each set is known from the algorithm analysis in the previous section, each failure sample can be further sorted into its respective failure distribution. For each failure time point, the time-to-failure value can be inputted into each competing probability density function contribution, equation (18) and equation (19), for each distribution. Since a higher value represents the higher probability of the sample belonging to that respective distribution, one can compare the relative values, or ratio of equation (18) and equation (19), to sort the samples.

An interesting phenomenon is that for the case of competing wearout mechanisms, the relative values or the ratio of the hazard function is also the same as comparing eq. (18) to eq. (19). The hazard function for mechanism 1 is:

$$h_1(t) = \frac{f_1(t)}{R_1(t)} \tag{20}$$

and similarly, the hazard function for mechanism 2 is:

$$h_2(t) = \frac{f_2(t)}{R_2(t)} \tag{21}$$

The hazard function, also known as the instantaneous failure rate, shows the conditional probability of a failure given that the system is currently working. When multiplying both sides of eq. (20) or eq. (20) by  $R_1$  (t)\* $R_2$  (t), they can be rewritten as:

$$R_1(t) * R_2(t) * h_1(t) = f_1(t) * R_2(t)$$

(22)

and:

$$R_1(t) * R_2(t) * h_2(t) = f_2(t) * R_1(t)$$

(23)

where the right sides of eqs. (22) and (23) equal eqs. (18) and (29), respectively. Since only the relative values or ratio, not the absolute value, is needed, using the hazard function to sort the samples has the same results as using the competing probability density function contributions.

Looking back at equation (12), at any time point, the competing failure probability is always composed of two contributions,  $f_1(t) \approx R_2(t)$  and  $f_2(t) \approx R_1(t)$ . Therefore, x, which is the percentage of failures from mechanism 1 at a given time t, can be found by:

$$x = \frac{f_1(t) * R_2(t)}{f_1(t) * R_2(t) + f_2(t) * R_1(t)}$$

(24)

and y, which is the percentage of failures from mechanism 2 at a given time t, is:

$$y = \frac{f_2(t) * R_1(t)}{f_1(t) * R_2(t) + f_2(t) * R_1(t)}$$

(25)

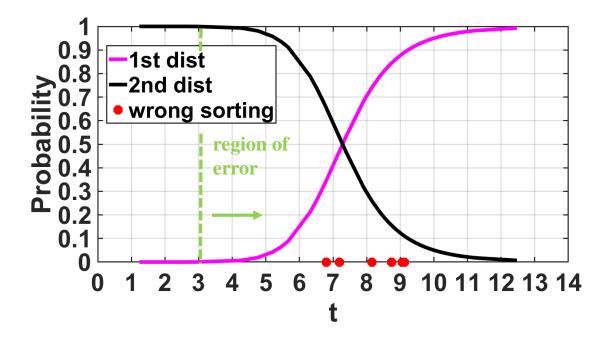

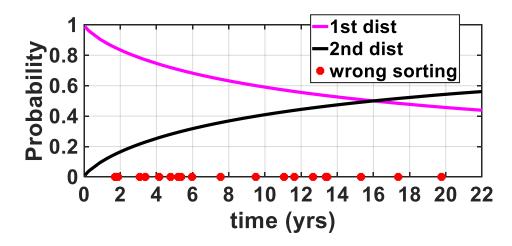

Plotting equation (24) and (21) for all failure times will show the region where error will most likely be highest, which occurs near x=y=0.5, meaning that there is a 50% probability that the sorting could be right for either distribution. This is shown as an example in Figure 23, which looks at FEOL TDDB with  $\beta_1$ =1.64,  $\eta_1$ =9.87 and EM with  $\beta_2$ =1.14,  $\eta_2$ =25.1296 for a sample size of 100 in 14nm FinFET ring oscillators. The plot will also show the region where one distribution has a 100% probability of showing up (a.k.a. the other distribution having a 0% probability of showing up), meaning that this region can have failure samples sorted to their relative distributions without any inaccuracies. When the distribution's 100% probability lowers, any future time point may be sorted incorrectly, which is called the region of error. This region identifies the time periods that are most important for physical failure analysis, where it may be necessary to perform further in-depth diagnosis.

No difference was found in the analysis of sorting errors between the original and MLE extracted parameters. The region of no error was found to increase when either the sample size or  $\beta$  ratio of the dominant wearout mechanism to secondary wearout mechanism is decreased. The sorting accuracy was also found to increase as the  $\beta$  ratio increases but varies slightly with a difference in sample size. When the percentage of each failure distribution is near 50%, there is a higher probability of the samples being sorted to the wrong distribution, due to the risk of the wrong categorization being around 50% too. This information can be used to signal that the samples near this area are the only ones that one may need to perform physical failure analysis, not the entire lot, which saves analysis costs. Therefore, the above methodology is a quick procedure to perform preliminary

Figure 23 – Sorting accuracy of 93.0% for FEOL TDDB (1<sup>st</sup> dist.) vs. EM failure (2<sup>nd</sup> dist.) in 14nm FinFET ring oscillators for a sample size of 100.

screening to identify the wearout mechanism in individual samples for confounded wearout modes.

# 1.7.3.1 Case Study

A case study using 11-stage ring oscillators based on the 14nm GlobalFoundries/IBM/Samsung FinFET technology node was used to investigate the effects of the competing wearout mechanisms. The parameters for the 14nm FinFET technology node were extracted from experimental data [84-86]. The 11-stage ring oscillators have FEOL TDDB wearout parameters of  $\beta$ =1.64,  $\eta$ =20 yrs, and MOL TDDB wearout parameters of  $\beta$ =1,  $\eta$ =10 yrs.

The selectivity of a mechanism is the probability that the failure is caused by that mechanism when there are multiple failure possibilities. If there are two wearout mechanisms, x and y with Weibull distributions,  $\eta_x$ ,  $\beta_x$  and  $\eta_y$ ,  $\beta_y$ , respectively, selectivity can be computed as follows [87]:

$$selectivity = \frac{P_{x_{fail_{first}}}}{P_{fail}}$$

(26)

where

$$P_{x_{fail_{first}}} = 1 - \exp\left(-\left(\frac{t_{stop}}{\eta_y}\right)^{\beta_y}\right) - \int_0^{\left(\frac{t_{stop}}{\eta_y}\right)^{\beta_y}} \exp\left(-u - \left(\frac{\eta_x}{\eta_y}\right)^{\beta_x} u^{\frac{\beta_x}{\beta_y}}\right) du$$

(27)

with t<sub>stop</sub>=testing time

and

$$P_{fail} = \left(1 - exp\left(-\left(\frac{t_{stop}}{\eta_x}\right)^{\beta_x}\right)\right) \left(1 - exp\left(-\left(\frac{t_{stop}}{\eta_x}\right)^{\beta_x}\right)\right)$$

(28)

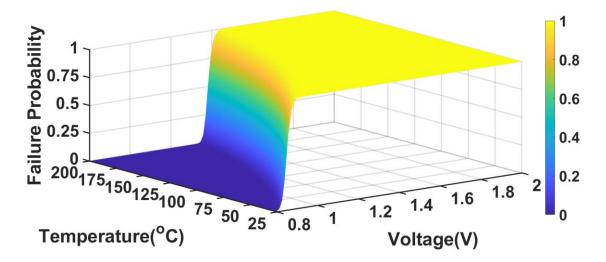

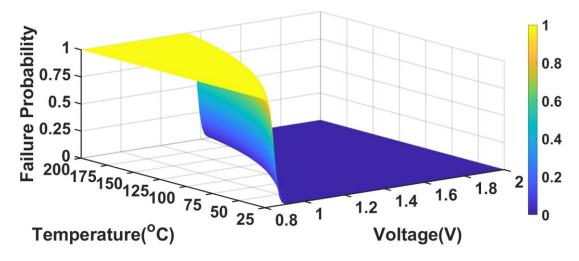

The selectivity for FEOL TDDB and MOL TDDB was found for various voltages and temperatures, as shown in Figure 24 and Figure 25. FEOL TDDB selectivity is higher at higher voltages and temperatures, while MOL TDDB is preferred at lower voltages and temperatures.

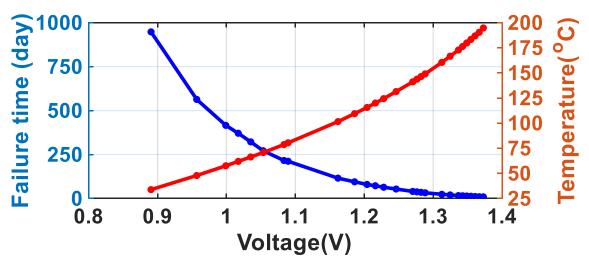

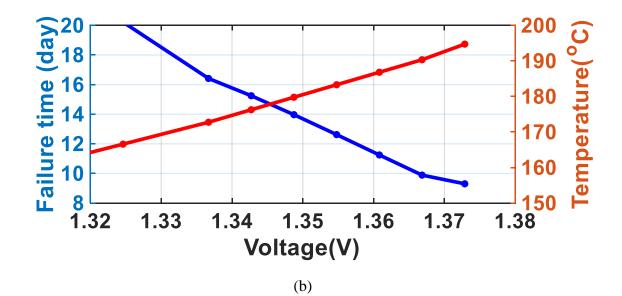

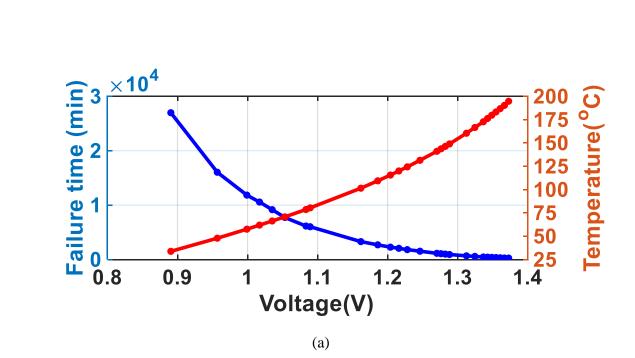

To shorten the test time, the selectivity maps were used to find a region where the FEOL TDDB and MOL TDDB had a selectivities of 0.5, and the ring oscillators were accelerated to 1.37 V, 199.72°C. The test times for the ring oscillators to reach 100 samples are shown in Figure 26, where it can be seen that there is an even mix of samples from both

wearout mechanisms. The 100th sample failure time out of 100 samples at FEOL TDDB selectivity=0.5 at various voltages and temperatures are shown in Figure 27, while the 1000th sample failure time out of 1000 samples at the same conditions are shown in Figure 28. The testing times for the 100th sample failure and 1000th sample failure can decrease by three orders depending on the accelerated testing conditions. For the same accelerated conditions of 1.37 V, 199.72°C, the 100th sample failure time out of 1000 samples is 9.3 days, while the 1000th sample failure time out of 1000 samples is 13.34 days.

The confidence interval for the extracted competing wearout mechanism are shown in Table I. Because the two competing wearout mechanisms have parameters that are close together, it is harder to separate the all the parameters, which results in a larger confidence interval level range. Also, because the selectivity is at 0.5, meaning that there is an equal probability of either sample failing at a failure point, the sorting accuracy is also lower, which is 61%, as shown in Figure 29.

Figure 24 – FEOL TDDB selectivity in 14nm FinFET ring oscillators.

Figure 25 – MOL TDDB selectivity in 14nm FinFET ring oscillators.

Figure 26 – Test times for 11-stage ring oscillators at accelerated conditions (1.37V, 194.72OC) for a sample size of 100.

Figure 27 – Failure time for 100th sample out of 100 samples at FEOL TDDB=0.5 selectivity (a) as a function of voltage and temperature (b) close-up.

Figure 28 – Failure time for 1000th sample out of 1000 samples at FEOL TDDB=0.5 selectivity (a) as a function of voltage and temperature (b) close-up.

Figure 29 – Sorting accuracy of 80% for FEOL TDDB (1st dist.) vs. MOL failure (2nd dist.) in 14nm FinFET ring oscillators for a sample size of 100.

# Table 1

# 95% Confidence Intervals for 11-stage ring oscillators at accelerated conditions (1.37V, 194.72°C)

|                      | FEOL TDDB   |             | MOL TDDB        |             |

|----------------------|-------------|-------------|-----------------|-------------|

|                      | Beta1       | Eta1        | Beta2           | Eta2        |

| Original<br>Values   | 1.64        | 2.88 (days) | 1.9             | 3.13 (days) |

| Sample Size<br>= 100 | 2.39 ± 1.39 | 3.19 ± 2.09 | $1.01 \pm 0.48$ | 2.46 ± 3.00 |

### 1.7.3.2 Application to Trojan Detection

The methodology of extracting wearout parameters with MLE can also be applied to detect Trojans and to select suspicious samples for failure analysis. Instead of extracting parameters for two confounded distributions, we assume a known distribution for mechanism 1, and use MLE to extract the parameters for mechanism 2 based on the data. Since hardware Trojans are triggered by unlikely events and accelerate a specific wearout mode depending on its design, a worst-case scenario is used as a study, where the original GTDDB parameters are  $\beta_1$ =1.64,  $\eta_1$ =10 yrs, and Trojan affected samples have altered GTDDB parameters to  $\beta_2$ =1.64,  $\eta_2$ =5 yrs in a 14nm FinFET 501-stage ring oscillator. For a sample size of 100, the sorting accuracy was found to be 80%.

#### **1.8 Failure Analysis for On-line Testing**

For online testing, product failures are observed one by one as they fail with the increase of time. Because the time to observe the failures of all products may be too long, on-line testing generally has a limited set of samples, instead of a collection of all samples. Therefore, this thesis researches a methodology to determine the wearout parameters of failure samples as the samples fail immediately, through using on-line data collected during operations.

SRAMs are major components of systems-on-chips and are also used for memory in systems that require very low power consumption and easy access to data [88]. It is static and volatile, where data retention exists as long as the device is powered without any form of a refresh. When the power is cut, data will be lost. Because it is random access, the next memory location that can be read or written does not depend on the previous access

location. The static property of SRAM is due to the feedback mechanism used to maintain the stored bit state.

To ensure that memory operation is stable during operation, the reliability of SRAMs need to be considered. Oxide layer failures cause transistor malfunctions that translate to the circuit level, such as the flipping of cell data due to voltages lower than the nominal one, making FEOL TDDB an important cause of concern [89]. In this study, we use data on failures in the SRAM to estimate the wearout model parameters of FEOL TDDB, which are based on a time-to-failure stamp. To detect failure rates, it is necessary to monitor actual failures and to link these failures to lifetime models. Because of the large number of identical cells, the SRAM can be used to detect the characteristics of wearout due to FEOL TDDB. Therefore, the SRAM data is used as a vehicle to appropriately estimate the model parameters. The parameters to be extracted are based on the two parameter Weibull distribution for FEOL TDDB, which are the characteristic lifetime,  $\eta$ , and the shape parameter,  $\beta$ . The model parameters are extracted from time-to-failure data from the cells in the SRAM.

In addition, this study also investigates the accuracy in extracting the model parameters by considering both random and systematic errors. The random errors occur due to the availability of samples (failed SRAM cells). Systematic errors occur from usage variations, such as supply voltage and operating temperature fluctuations, as well as variations due to process parameters and workload. The analysis of systematic errors is used to determine when and if sensor data is needed to supplement analytical wearout models when estimating wearout model parameters.

### 1.8.1 Methodology

The lifetime distribution of a device due to wearout by front-end gate oxide breakdown (FEOL TDDB) can be found by [87]:

$$P(t) = 1 - exp\left(-\left(\frac{t}{\eta}\right)^{\beta}\right)$$

(29)

where  $\eta$  is the characteristic lifetime and  $\beta$  is the shape parameter.

The characteristic lifetime of the SRAM,  $\eta_{SRAM}$ , is a combination of Weibull distributions for the components, and is the solution of [90]:

$$1 = \sum_{i=1}^{n} \left(\frac{\eta_{SRAM}}{\eta_i}\right)^{\beta_i} \tag{30}$$

where  $\eta_i$ , i=1, ..., n are the characteristic lifetime of all the circuit components, and  $\beta_i$  are the corresponding shape parameters. Similarly, it can be found that [91]:

$$\beta_{SRAM} = \sum_{i=1}^{n} \beta_i \left(\frac{\eta_{SRAM}}{\eta_i}\right)^{\beta_i} \tag{31}$$

When investigating the failure of the SRAM, the probability of stress for the circuit needs to be considered, because the usage scenario needs to be taken into account, where the circuit may be on and off at different times. For example, if the SRAM stores logic "1" 50% of the time and logic "0" 50% of the time, then s=0.5 in Equation (2) for all cells' four transistors in the latch. s≈0 for the access transistors because it is only turned on when the

cell is accessed. 50% is set as the baseline for comparison. If the duty cycle is changed, then the SRAM will degrade at a different rate.

The SRAM failures due to FEOL TDDB during operation are calculated using Monte Carlo simulation. The random variable is the failure probability in Equation (18). The resulting data are time stamps for the failures of SRAM cells. By using the sequence of time stamps for SRAM failures due to FEOL TDDB, the Weibull parameters are extracted using generalized maximum likelihood estimation [92].

The original SRAM cell parameters for FEOL TDDB degradation in this study are  $\eta$ =20 years and  $\beta$ =1.12. As shown in Figure 30 (a), the SRAM failure samples for a sample size of 94,000 (an SRAM with 94k cells) due to FEOL TDDB are plotted on a Weibull plot. The FEOL TDDB extracted parameters are  $\eta$ =19.966 and  $\beta$ =1.119. Figure 30 (b) shows the case where only the first 100 failed samples are available. The FEOL TDDB extracted parameters are  $\eta$ =39.66,  $\beta$ =0.99 for the first 100 samples, which are far from the actual parameters,  $\eta$ = 20 and  $\beta$ =1.12.

When data is collected during operations, information will generally be available for only part of the samples. As the sample size is increased, the FEOL TDDB extracted parameters become closer to the actual parameters. However, the monitoring time may be too long or the cost may be too great to be able to collect all the failure information from every sample.

The wearout model, Equation (2), are for single devices with s=1, where the probability of stress is considered to be the always on. The degradation for the devices will be constant with time. However, the observed data is from an SRAM cell, where the

probability of stress may be different, because the circuit may be on or off depending on the time.