# Missouri University of Science and Technology Scholars' Mine

**Electrical and Computer Engineering Faculty** Research & Creative Works

**Electrical and Computer Engineering**

02 Jul 2021

# Modeling, Analysis, and Control Design of a Single-Stage Boost Inverter

Md Rasheduzzaman

Poria Fajri

Jonathan W. Kimball Missouri University of Science and Technology, kimballjw@mst.edu

Brad Deken

Follow this and additional works at: https://scholarsmine.mst.edu/ele\_comeng\_facwork

Part of the Electrical and Computer Engineering Commons

#### Recommended Citation

M. Rasheduzzaman et al., "Modeling, Analysis, and Control Design of a Single-Stage Boost Inverter," Energies, vol. 14, no. 14, article no. 4098, MDPI, Jul 2021.

The definitive version is available at https://doi.org/10.3390/en14144098

This work is licensed under a Creative Commons Attribution 4.0 License.

This Article - Journal is brought to you for free and open access by Scholars' Mine. It has been accepted for inclusion in Electrical and Computer Engineering Faculty Research & Creative Works by an authorized administrator of Scholars' Mine. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

MDPI

Article

# Modeling, Analysis, and Control Design of a Single-Stage Boost Inverter

Md. Rasheduzzaman <sup>1,\*</sup>, Poria Fajri <sup>2</sup>, Jonathan Kimball <sup>3</sup> and Brad Deken <sup>1</sup>

- Department of Engineering and Technology, Southeast Missouri State University, Cape Girardeau, MO 63701, USA; bdeken@semo.edu

- Department of Electrical & Biomedical Engineering, University of Nevada, Reno, NV 89557, USA; pfajri@unr.edu

- Department of Electrical & Computer Engineering, Missouri University of Science and Technology, Rolla, MO 65409, USA; kimballjw@umsystem.edu

- \* Correspondence: mrasheduzzaman@semo.edu

Abstract: A single-phase, single-stage, differential boost inverter comprises two independently-controlled boost DC-DC converters, with the load connected between their outputs. The net voltage on the load is sinusoidal and has a controllable frequency and magnitude that is larger than that of the DC source. The present work first derives steady-state and small-signal models of the inverter with parasitic elements. The results obtained from the line-to-output transfer function, control-to-output transfer function, open-loop input impedance, and open-loop output impedance models are compared with that of the ones obtained from the experimental testbed. Using the new models, a voltage mode controller is designed in the synchronous reference frame. The regulator design is explored through the use of an example. The results are verified against the small-signal model, then PLECS simulations, and finally a laboratory experiment. The results indicate excellent agreement between the model and experiment during transients in voltage reference, input source voltage, and output load. A sensitivity analysis is performed based on the inverter model considering the parameter variation. Finally, loss and efficiency estimations are provided in this work.

Keywords: boost inverter; synchronous reference frame; small-signal model; voltage mode controller

Citation: Rasheduzzaman, M.; Fajri, P.; Kimball, J.; Deken, B. Modeling, Analysis, and Control Design of a Single-Stage Boost Inverter. *Energies* **2021**, *14*, 4098. https://doi.org/10.3390/en14144098

Academic Editors: Vincenzo Di Dio and Valeria Boscaino

Received: 8 June 2021 Accepted: 1 July 2021 Published: 7 July 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

# 1. Introduction

Traditional full-bridge inverters are buck type, meaning that the generated output voltage magnitude is lower than that of the DC input voltage. To generate an output voltage that is larger in magnitude than the input voltage, an additional boost stage is needed. With the two-stage configuration, the input DC signal is first stepped up using a boost converter and then passed through a buck-type full-bridge inverter. The drawbacks of the two stage configuration are discussed in [1]. Additionally, the efficiency and footprint of the two stage system are not attractive. Considering the complexity of this multistage design, a simple single-stage boost inverter was first proposed by Cáceres and Barbi [2]. The proposed system was designed for a single-phase system. Using this method only four electronic switches are engaged, in contrast to the six switches that are used in a traditional two-stage inverter. Xue et al. in [3] reported that the inverter presented by Cáceres in [2] is one of the topologies of single-phase inverters for small distributed power generators. It is reported that this particular inverter topology has the capability to operate both as a standalone and grid-connected power supply unit. The suggested applications of this type of inverter can be found in solar photovoltaic units, wind turbine systems, and fuel cell inverters [4-6].

Several single-phase, single-stage, current-source-based inverters (CSI) are discussed in [7]. In [1], a modified modulation technique and a double-tuned resonant filter has been proposed to improve the harmonic response on the DC side with relatively small

Energies **2021**, 14, 4098 2 of 29

inductance. The literature review in [7] discusses some challenges associated with the basic boost inverter structure. For improved operation, a new type of single-stage boost inverter is proposed in the same literature. However, the proposed model uses a series capacitor at the output to filter out the DC component which carries the fundamental current. In addition, the inverter fails to operate if a capacitive load is connected. The switched-capacitor differential boost inverter (SCDBI) discussed in [8,9] implemented a gain linearization strategy with the use of unipolar modulation (3L-PWM) resulting in a significant reduction of total harmonic distortion (THD) of the output voltage. However, the SCDBI inverter uses four additional switches. Although several single-stage inverter topologies exist in the literature [10–12], the one discussed in [2] has the simplest configuration.

Considering the simplicity of its operation, the inverter in [2] is discussed in this work. The inverter consists of two DC-DC synchronous boost converters. These converters are controlled independently. The inverter has four MOSFET/IGBT switches (two for each boost configuration), two inductors, and two capacitors. Identical inductors and capacitors are used for both converters. The load is connected differentially across the two output capacitors. With this configuration, the inverter was analyzed in [13] considering four different switching states. In [14], only two switching modes are considered. However, both analysis techniques excluded component parasitic from the discussion. The latter technique assumed one of the converters to be a fixed DC source which reduced the system dynamics to only one converter. The models describing the control-to-output relationship in [2,15] do not include component parasitic. The derived transfer functions contain higher-order polynomials in the denominator, which complicates controller design. In addition to that, the transfer functions for the open-loop input impedance and output impedance are not well explained in the previous work. In this work, the boost inverter operation is discussed using two operating modes. Converter dynamics from both the boost operations are considered in deriving the control-to-output transfer function. The mathematical modeling includes the component parasitic resulting in a more accurate representation of the system dynamics. Furthermore, the open-loop input and output impedance are derived and analyzed.

The primary control objective of a single-stage boost inverter is to regulate the individual converters in a way so as to generate a sinusoidal waveform with the nominal operating frequency added to a DC offset. The AC waveforms are 180° out of phase with respect to each other. The differential connection at the load terminals cancels out the DC offsets from both the converters, leaving a sinusoidal signal. The two algorithms that are commonly used in controlling boost inverters are the sliding mode controller and the current mode controller [4,16–22]. The major issues involving the sliding mode controller are variable switching frequency and complex operating theory [2,23]. The current-controlled theory presented in [18,24] overcomes these issues. However, linearization of the current-controlled model is difficult once control variables and states are considered. Both sliding mode and current-controlled mode controllers require the use of multiple voltage and current sensors.

To overcome these issues, a simple voltage-mode controller for operating the boost inverter is proposed in this work. The proposed controller requires only two voltage measurements. This results in a simpler controller algorithm that eliminates the need for an extra inner loop for current control. This in turn eliminates the need for current sensors and results in a cost-effective design. The voltage mode control of such an inverter was proposed in [25,26], in which a conventional proportional integral derivative (PID) regulator is used in both cases. However, that method suffers from a significant steady-state error in tracking the reference magnitude. Additionally, the presence of harmonic distortion and even harmonic components makes implementing such controllers impractical [27]. The other types of controller algorithm employed to control SCDBI-type inverters are a proportional resonant controller [8] and a modified proportional integral (PI) structure with an extra pole adjusted to attenuate the converter gain close to the resonance frequency [9].

In this work, a synchronous reference frame proportional integral controller (SRFPI) is proposed to control the boost inverter. The proposed controller overcomes the error

Energies **2021**, 14, 4098 3 of 29

tracking issues. The SRFPI technique has been used previously in controlling the traditional voltage source inverters [28]. A list of novel contributions in this work includes:

- A detailed derivation of the quasi-steady state equivalent model of the system;

- An accurate AC small-signal mathematical modeling of the system considering the component parasitic;

- Experimental verification of the line-to-output transfer function, control-to-output transfer function, open-loop input impedance, and open-loop output impedance;

- Design of a voltage mode controller in the synchronous reference frame and selection of controller parameters;

- Estimation of loss and efficiency of the system.

The rest of the paper is organized as follows: Section 2 discusses the basics of the boost inverter operation using the duty cycle variation. Accurate mathematical models are proposed describing the converter dynamics in Section 3. The voltage mode controller design is explained in Section 4. Finally, the results from the simulation and the experimental procedure are presented with discussions in Section 5.

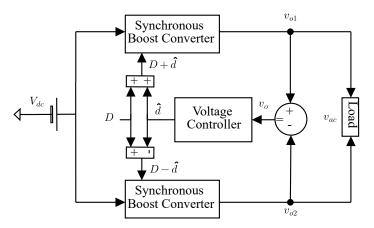

#### 2. Basics of a Boost Inverter

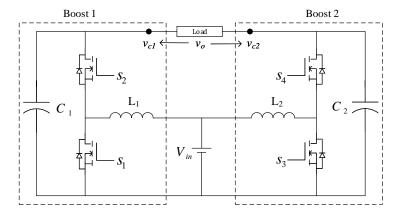

The boost inverter proposed by Cacéres [2] is provided in Figure 1. The inverter uses two synchronous boost converters, marked as "Boost 1" and "Boost 2", that enable continuous current flow with no zero states or discontinuous conduction. The original model was proposed based on the assumption that the values of the passive components are identical in both the converters. In practice, inductor values are chosen such that  $L_1 = L_2 = L$  and capacitor values are chosen as  $C_1 = C_2 = C$ . The boost sections are controlled separately to produce output voltages,  $v_{c1}$  and  $v_{c2}$ , appearing across the respective capacitors. The controllers are coordinated in a way that  $v_{c1}$  and  $v_{c2}$  are phase-shifted by  $180^{\circ}$  at all times, i.e.,

$$v_{c1} = V_{dc} + \frac{V_m}{2} \cos \omega t$$

$$v_{c2} = V_{dc} + \frac{V_m}{2} \cos(\omega t + \pi)$$

(1)

where,  $V_{dc}$  denotes the dc offset voltage,  $V_m$  is the magnitude of the ac output, and  $\omega$  is the nominal operating frequency in rad/s. If the load is connected across the capacitors, the final output voltage across the load is:

$$v_o = v_{c1} - v_{c2} = V_m \cos \omega t. \tag{2}$$

Notice the cancellation of the DC terms in (2). The cancellation occurs regardless of the power factor of the load. The output voltage has a magnitude that is twice of that of the one obtained from the individual converter's AC portion.

Figure 1. A DC-AC boost inverter.

Energies **2021**, 14, 4098 4 of 29

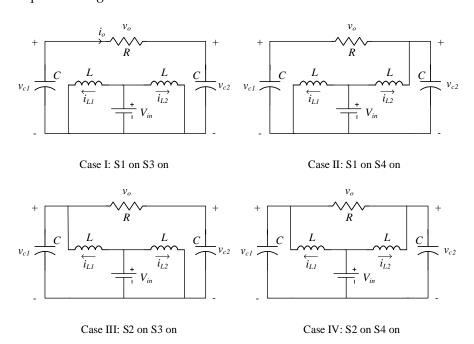

The waveform analysis in [29] explains that the boost inverter switching may not be realized using only one duty cycle variation. Assuming duty cycles for the individual boost sections to be  $D_a$  and  $D_b$  respectively, four different cases can occur. These four cases are depicted in Figure 2.

Figure 2. Four different switching cases for the boost inverter.

Only two out of these four cases can result in a sinusoidal voltage at the output. The following discussion provides a graphical representation of the duty cycles  $D_a$  and  $D_b$  and their relationship to the boost inverter output.

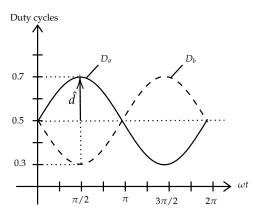

At steady-state, a conventional DC-DC boost converter produces an output voltage higher than the input voltage. The output is a fixed DC voltage with some high frequency switching ripple that is within an acceptable limit defined in the design process. In this particular configuration, the inverter consists of two boost converters, each producing a sinusoidally varying signal at a frequency much lower than the switching frequency with some DC offset. As a result, the duty cycle variations are very similar to the ones depicted in Figure 3. With the expectation that the duty cycles vary sinusoidally, both the waveforms in Figure 3 need to be centered around D = 0.5. That way the waveform symmetry is preserved as the waveforms neither clip at the floor nor saturates at the top. In that case, the AC variation has an amplitude of  $\hat{d}$ . These two duty cycle variations,  $D_a$  and  $D_b$ , maintain a 180° phase shift with respect to each other. To generalize the duty cycle variation expressions considering  $D_a = d = D + \hat{d}$ , the relationship between the duty cycles is:

$$D_b = 1 - D_a = 1 - (D + \hat{d}) = D' - \hat{d} = \hat{d}'$$

(3)

where, D = D' = 0.5.

This outcome indicates that Boost 1 inductor stores energy at the same time when Boost 2 inductor transfers energy to the load during  $0 \le \omega t < \pi$ . This process reverses during the next half cycle when  $\pi \le \omega t < 2\pi$ . The boost inverter operation is then limited to only two modes,  $Q_s$  and  $Q_s'$ . The switching signals  $S_1$  and  $S_4$  have identical switch commands  $Q_s$ , whereas switching signals  $S_2$  and  $S_3$  have commands  $Q_s'$ . This simplifies the mathematical modeling of the inverter to a great extent. The following section proposes a steady-state equivalent model and a small-signal model of the inverter system considering the component parasitic.

Energies **2021**, 14, 4098 5 of 29

Figure 3. Boost inverter waveform analysis.

# 3. Mathematical Modeling of the System

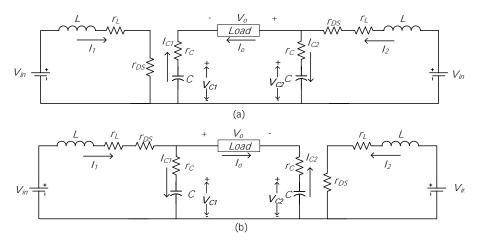

The operating modes of the boost inverter are depicted in Figure 4. For the sake of simplicity, "Load" will be replaced by a linear resistor, R, during the discussion. The parameter definitions are provided in Table 1. The average current through the left capacitor over a complete cycle is:

$$\langle I_{C1} \rangle = 0 = -D \frac{V_o}{R} + D' (I_1 - \frac{V_o}{R}).$$

From which the value of  $I_1$  is obtained as:

$$I_1 = \frac{V_o}{D'R}. (4)$$

Following the same method, the average value of the inductor voltage found from the left inductor over a complete cycle is:

$$\langle V_{L1} \rangle = 0 = D(V_{in} - (r_L + r_{DS})I_1) + D'(V_{in} - (r_L + r_{DS})I_1 - r_CI_{C1} - V_{C1}).$$

In the second time interval,  $I_{C1} = I_1 - \frac{V_0}{R}$ . From this and from (4) we obtain:

$$0 = V_{in} - \frac{V_o}{D'R} r_1 - D'(V_{C1} - \frac{V_o}{R} r_C)$$

(5)

where,  $r_1 = r_L + r_{DS} + D'r_C$ .

Similarly, the average current through the second capacitor is:

$$\langle I_{C2}\rangle = 0 = -D'\frac{V_o}{R} + D(I_2 - \frac{V_o}{R})$$

which results in the value of  $I_2$  as:

$$I_2 = \frac{V_o}{DR}. (6)$$

Finally, considering  $I_{C2} = I_2 - \frac{V_o}{R}$  in the first time interval and  $r_2 = r_L + r_{DS} + Dr_C$  the average value of the remaining inductor voltage over a complete cycle is:

$$\langle V_{L2} \rangle = 0 = D(V_{in} - (r_L + r_{DS})I_2 - r_CI_{C2} - V_{C2}) + D'(V_{in} - (r_L + r_{DS})I_2)$$

resulting in:

$$0 = V_{in} - \frac{V_o}{DR} r_2 - D' (V_{C2} - \frac{V_o}{R} r_C).$$

(7)

Energies **2021**, 14, 4098 6 of 29

**Figure 4.** Boost inverter active operating modes for (a)  $S_1 = S_4 = 1$ ,  $S_2 = S_3 = 0$  and (b)  $S_1 = S_4 = 0$ ,  $S_2 = S_3 = 1$ .

Table 1. Sample boost inverter parameters.

| Component              | Parameter  | Value          |

|------------------------|------------|----------------|

| Capacitors             | $C_1, C_2$ | 10 μF          |

| Capacitor ESR          | $r_{C}$    | $0.1\Omega$    |

| Inductors              | $L_1, L_2$ | 270 μH         |

| Inductor ESR           | $r_L$      | $0.20\Omega$   |

| MOSFET 'on' Resistance | $r_{DS}$   | $0.10\Omega$   |

| Load Resistance        | R          | $50\Omega$     |

| Supply Voltage         | $V_{in}$   | $10\mathrm{V}$ |

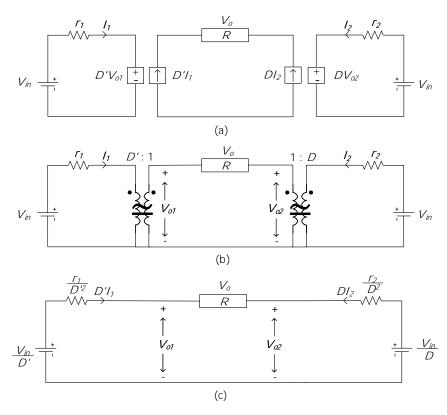

## 3.1. Quasi-Steady-State Equivalent Circuit Modeling

Taking (4) through (7) into considerations, the steady-state equivalent model of the boost inverter is formulated. The proposed steady-state equivalent model of the inverter is presented in Figure 5. From Figure 5c the individual converter outputs are:

$$V_{o1} = V_{C1} - \frac{V_o}{R} r_C = \frac{V_{in}}{D'} - \frac{r_1}{D'^2} \frac{V_o}{R}$$

(8)

$$V_{o2} = V_{C2} - \frac{V_o}{R} r_C = \frac{V_{in}}{D} + \frac{r_2}{D^2} \frac{V_o}{R}.$$

(9)

Since, the output voltage across the load resistor is  $V_0 = V_{o1} - V_{o2}$ , after subtracting (9) from (8) and then rearranging the terms gives the output-to-input ratio as:

$$G_V = \frac{V_o}{V_{in}} = \frac{2D - 1}{D(1 - D)} \times \frac{1}{1 + \frac{1}{R} \left(\frac{r_1}{D'^2} + \frac{r_2}{D^2}\right)}.$$

(10)

If the loss terms are not included, the voltage gain in (10) simply contains the gain factor M where,  $M = \frac{2D-1}{D(1-D)}$ .

After substituting the parameter values from Table 1 the steady-state characteristic plots are obtained for different values of duty cycles. They are presented in Figure 6. The plot for  $G_V$  in Figure 6a shows that at D=0.5 the output-to-input ratio becomes zero.

Energies 2021, 14, 4098 7 of 29

**Figure 5.** The steady-state equivalent model of the boost inverter. (a) Steady-state equivalent from the equations, (b) standard canonical approximation, and (c) simplified equivalent model.

**Figure 6.** The characteristic plots obtained from the steady-state equivalent model as the duty cycle is varied: (a) Voltage gain with and without parasitic losses included, (b) individual converter and inverter currents, (c) inverter power considering the conduction losses only, and (d) efficiency considering the conduction losses only for three different load values as the duty cycle is varied.

Energies **2021**, 14, 4098 8 of 29

The voltage gain lines,  $G_V$  and M, start to deviate away from linearity noticeably below D=0.2 and above D=0.8. Those are the practical limits of the inverter duty cycle. The gain curves match very closely between  $0.25 \le D \le 0.75$ . To know the current limits of individual converters, inductor currents at different duty cycles are determined. Referring to (4) and (6), the individual inductor currents are:

$$I_1 = \frac{V_{in}}{R} \times \frac{2D - 1}{D(1 - D)^2} \times \frac{1}{1 + \frac{1}{R} \left(\frac{r_1}{D'^2} + \frac{r_2}{D^2}\right)}$$

(11)

and

$$I_2 = \frac{V_{in}}{R} \times \frac{2D-1}{D^2(1-D)} \times \frac{1}{1 + \frac{1}{R} \left(\frac{r_1}{D'^2} + \frac{r_2}{D^2}\right)}$$

(12)

The two inductor currents,  $I_1$  and  $I_2$ , and the output current,  $I_0$ , are plotted for varying duty cycles in Figure 6b. A significant increase in inductor currents is noticed outside the range of  $0.3 \le D \le 0.7$ . These currents follow non-linear characteristics for a wide range of duty cycle meaning that the inductor currents are non-sinusoidal for the most part of the inverter operation. However, the output current stays linear for a range determined by the  $G_V$  curve in Figure 6a. The system conduction loss depends on  $I_1$ ,  $I_2$ , and the component parasitic. Since,  $D'I_1 = -DI_2$  the efficiency of the inverter is:

$$\eta = \frac{P_o}{P_{in}} = \frac{V_o D' I_1}{V_{in}(I_1 + I_2)} \times 100 = \frac{1}{1 + \frac{1}{R} \left(\frac{r_1}{D'^2} + \frac{r_2}{D^2}\right)} \times 100\%.$$

(13)

A comparison of active power output with and without the conduction losses is depicted in Figure 6c. As expected, the output power reduces significantly as the loss terms are included in the mathematical model. In Figure 6d, the system efficiency is presented at three different load values as the duty cycle is varied. With the increase in load resistance, fewer  $I^2R$  losses occur due to low current through the component parasitic. The efficiency calculation in (13) is significant in determining the load value that can be used in this particular boost inverter arrangement. For an accurate determination of the system efficiency, the other forms of losses such as the switching loss, dead time loss, gate charge loss, core losses in the inductor, etc. are needed to be calculated. The relationship between equivalent resistances,  $r_1$  and  $r_2$ , due to the parasitic components of the circuit elements is:

$$r_2 = r_1 + r_C(1 - 2D'). (14)$$

At D = 0.5, these two resistances become equal.

### 3.2. Small-Signal AC Modeling

The inverter small-signal AC model is obtained considering a small perturbation around the stable operating points. The quantities averaged over a cycle of the switching frequency,  $f_{sw}$ , is the summation of the DC components and the AC: components

$$v_{in} = V_{in} + \hat{v}_{in} \tag{15}$$

$$v_{L1} = V_{L1} + \hat{v}_{L1} \tag{16}$$

$$i_1 = I_1 + \hat{i}_1 \tag{17}$$

$$v_{L2} = V_{L2} + \hat{v}_{L2} \tag{18}$$

$$i_2 = I_2 + \hat{i}_2 \tag{19}$$

$$v_{C1} = V_{C1} + \hat{v}_{C1} \tag{20}$$

$$i_{C1} = I_{C1} + \hat{i}_{C1} \tag{21}$$

$$v_{C2} = V_{C2} + \hat{v}_{C2} \tag{22}$$

$$i_{C2} = I_{C2} + \hat{i}_{C2} \tag{23}$$

Energies 2021, 14, 4098 9 of 29

$$d = D + \hat{d} \tag{24}$$

$$d' = D' - \hat{d}. \tag{25}$$

Substituting (15) through (25) in (4)–(7) and then equating the AC terms and neglecting the terms given by the product of two AC terms on both sides results in:

$$0 = \hat{v}_{in} + \hat{d}(I_1 r_C + V_{C1} - \frac{V_o}{R} r_C) - \hat{i}_1 r_1 - D'(\hat{v}_{C1} - \frac{\hat{v}_o}{R} r_C)$$

(26)

$$0 = \frac{\hat{v}_o}{R} + \hat{d}I_1 - D'\hat{i}_1 \tag{27}$$

$$0 = \hat{v}_{in} - \hat{d}(I_2 r_C + V_{C2} - \frac{V_o}{R} r_C) - \hat{i}_2 r_2 - D(\hat{v}_{C2} - \frac{\hat{v}_o}{R} r_C)$$

(28)

$$0 = \frac{\hat{v}_o}{R} - \hat{d}I_2 - D\hat{i}_2. \tag{29}$$

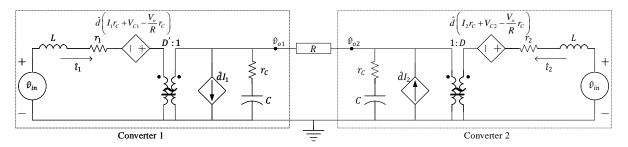

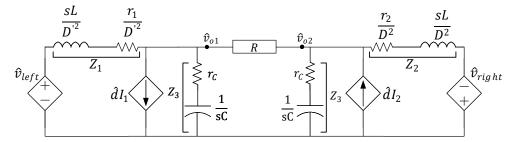

The small-signal AC model of the boost inverter is obtained based on the results in (26) through (29). The AC equivalent model is depicted in Figure 7 where,  $\hat{v}_{o1} = \hat{v}_{C1} - \frac{\hat{v}_o}{R}r_C$  and  $\hat{v}_{o2} = \hat{v}_{C2} - \frac{\hat{v}_o}{R}r_C$ .

Figure 7. The AC equivalent model of the boost inverter.

#### 3.3. Line to Output Transfer Function

To obtain the line-to-output transfer function,  $G_{vg} = \frac{\hat{v}_o}{\hat{v}_{in}}$ , the small-signal perturbation value  $\hat{d}$  is set to zero. The equivalent diagram is presented in Figure 8. After that, a Thévenin equivalent circuit with a source,  $\hat{v}_{th}$ , and an impedance,  $Z_{th}$ , is determined from the load's perspective.

Figure 8. The ac equivalent model for obtaining the line to output transfer function.

Removing the load and looking back from the load terminals the Thévenin's equivalent impedance is:

$$Z_{th} = Z_1 || Z_3 + Z_2 || Z_3. (30)$$

Energies **2021**, 14, 4098 10 of 29

where:

$$Z_1 = \frac{sL + r_1}{D'^2}; Z_2 = \frac{sL + r_2}{D^2}; Z_3 = \frac{1}{sC} + r_C.$$

(31)

The Thévenin's equivalent source is determined as:

$$\hat{v}_{th} = \hat{v}_{in} \left( \frac{1}{D'} \frac{Z_3}{Z_1 + Z_3} - \frac{1}{D} \frac{Z_3}{Z_2 + Z_3} \right). \tag{32}$$

Finally, applying the voltage divider rule, the line-to-output transfer function is:

$$G_{vg}\Big|_{\hat{d}=0} = \frac{\hat{v}_o}{\hat{v}_{in}} = \left(\frac{1}{D'}\frac{Z_3}{Z_1 + Z_3} - \frac{1}{D}\frac{Z_3}{Z_2 + Z_3}\right) \frac{1}{1 + \frac{Z_{th}}{R}}.$$

(33)

It is interesting to note that the impedances  $Z_1$  and  $Z_2$  become equal at D=0.5. The expression then becomes equal to that of the one in (10). At D=0.5, the transfer function becomes equal to zero. That means this configuration is immune to any perturbation in the input source provided D (that is, the center point of duty ratio variation) always stays at 0.5. For any other values, any variation in the input will have an effect on the output response. The Bode plots in Figure 9 obtained from the small-signal model and the experimental results match closely at D=0.7. The Bode plots overlap for a large range of frequencies.

**Figure 9.** Bode plot comparison of audio susceptibility at D = 0.7. The results obtained from the small-signal line-to-output transfer function is compared with that of the one obtained from the experimental test bed.

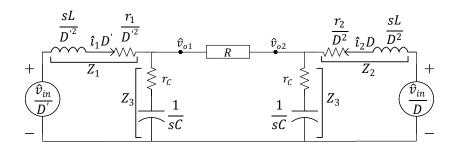

### 3.4. Control-to-Output Transfer Function

The control-to-output transfer function,  $G_{vd} = \frac{\hat{v}_0}{d}$ , is determined by setting  $\hat{v}_{in}$  to zero in the AC equivalent model. The equivalent diagram is given in Figure 10 where,  $\hat{v}_{left}$  and  $\hat{v}_{right}$  are  $\hat{d}\left(I_1r_C + V_{C1} - \frac{V_0}{R}r_C\right)/D'$  and  $\hat{d}\left(I_2r_C + V_{C2} - \frac{V_0}{R}r_C\right)/D$  respectively. After applying the source transformation technique and determining the equivalent current sources, the currents going into nodes  $\hat{v}_{01}$  and  $\hat{v}_{02}$  are:

$$\hat{i}_{left} = \hat{d} \left( \frac{1}{Z_1 D'} \left( I_1 r_C + V_{C1} - \frac{V_o}{R} r_C \right) - I_1 \right)$$

(34)

and

$$\hat{i}_{right} = \hat{d} \left( I_2 - \frac{1}{Z_2 D} \left( I_2 r_C + V_{C2} - \frac{V_o}{R} r_C \right) \right)$$

(35)

Energies **2021**, 14, 4098 11 of 29

respectively. Since, the duty cycle is varied around 0.5, the average duty cycle becomes:

$$D = D' = 0.5. (36)$$

This in turn results in:

$$Z_1 = Z_2.$$

(37)

Moreover, from Figure 5c we obtain:

$$V_o = 0$$

as a result,  $V_{C1} = V_{C2}$ , (38)

$$|I_1| = |I_2|. (39)$$

The rest of the calculations are greatly simplified as  $\hat{i}_{left}$  becomes equal to  $-\hat{i}_{right}$ .

Figure 10. The ac equivalent model for obtaining the control-to-output transfer function.

Afterwards, the superposition theorem is applied to the network to determine the node voltages considering one source at a time. With the presence of  $\hat{i}_{left}$  alone in the system, the equations relating to the node voltages are:

$$\hat{d}\left(\frac{1}{Z_1D'}(I_1r_C + V_{C1}) - I_1\right) = \hat{v}'_{o1}\left(\frac{1}{Z_1||Z_3} + \frac{1}{R}\right) + \hat{v}'_{o2}\left(\frac{-1}{R}\right) \tag{40}$$

$$0 = \hat{v}'_{o1} \left(\frac{-1}{R}\right) + \hat{v}'_{o2} \left(\frac{1}{Z_1 || Z_3} + \frac{1}{R}\right). \tag{41}$$

For simplified representation of the terms assuming:

$$\beta = \frac{1}{Z_1 D'} (I_1 r_C + V_{C1}) - I_1 \tag{42}$$

$$\gamma = \frac{1}{R} \tag{43}$$

$$\Delta = \frac{1}{Z_1 || Z_3} + \frac{1}{R}.\tag{44}$$

Solving (40) and (41):

$$\frac{\hat{v}_{o1}'}{\hat{d}} = \beta \left( \frac{\Delta}{\Delta^2 - \gamma^2} \right) \tag{45}$$

and

$$\frac{\hat{v}_{o2}'}{\hat{d}} = \beta \left( \frac{\gamma}{\Delta^2 - \gamma^2} \right). \tag{46}$$

Energies **2021**, 14, 4098 12 of 29

After that, considering the  $\hat{i}_{right}$  source alone and following a similar approach gives:

$$\frac{\hat{v}_{o1}^{"}}{\hat{d}} = \beta \left( \frac{-\gamma}{\Delta^2 - \gamma^2} \right) \tag{47}$$

and

$$\frac{\hat{v}_{o2}^{"}}{\hat{d}} = \beta \left( \frac{-\Delta}{\Delta^2 - \gamma^2} \right). \tag{48}$$

By considering (49) and by substituting in it (45) through (48) the control to output transfer function becomes:

$$\left(\frac{\hat{v}_{o1}'}{\hat{d}} + \frac{\hat{v}_{o1}''}{\hat{d}}\right) - \left(\frac{\hat{v}_{o2}'}{\hat{d}} + \frac{\hat{v}_{o2}''}{\hat{d}}\right) = \frac{\hat{v}_o}{\hat{d}} \tag{49}$$

$$G_{vd}\Big|_{\hat{v}_{in}=0} = 2\beta \left(\frac{1}{\Delta + \gamma}\right).$$

(50)

The control-to-output transfer function in (50) is much less complicated compared to the transfer functions derived in [2] or [25]. Furthermore, the proposed transfer function includes the component parasitic resulting in an accurate mathematical model of the system. The complete expression of the transfer function is given in (51):

$$G_{vd}(s) = 2V_{in} \times \frac{1 + sCr_C}{s^2 \left(LC + \frac{2LCr_C}{R}\right) + s\left(2\frac{L}{R} + 2\frac{Cr_Cr_1}{R} + D'^2Cr_C + Cr_1\right) + \left(\frac{2r_1}{R} + D'^2\right)}.$$

(51)

Ignoring the parasitic losses the transfer function becomes:

$$\frac{\hat{v}_o}{\hat{d}} = \frac{2(D'V_{C1} - I_1 sL)}{s^2 LC + 2s\frac{L}{R} + D'^2} = \frac{2V_{in}}{s^2 LC + 2s\frac{L}{R} + D'^2}.$$

(52)

This helps to quickly determine the dominant poles of the system. It is interesting to note that unlike (52), the transfer function including the loss terms in (51) contains a zero. This results from using our assumption at (36) into (10) resulting in DC average values  $V_0 = 0$  and  $I_1 = 0$  from (5). This eliminates the zero and using (8) the numerator simply becomes  $2V_{in}$ . The physical interpretation of (52) is that when the individual DC-DC converters operate at an average duty cycle of 0.5, the average DC voltage output from both the converters becomes equal. Since the load is connected differentially, the average load voltage would then become zero which results in an average inductor current from each converter being zero. As a result, the right half-plane zero vanishes leaving the input voltage in the numerator with a gain factor of two.

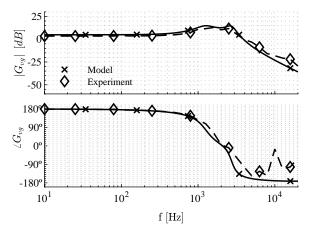

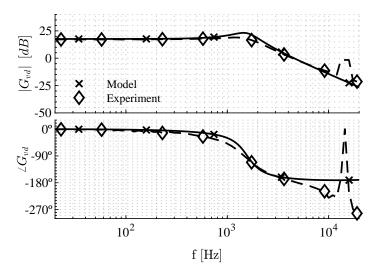

The validity of the proposed transfer function is tested using the experimental test bed. The Bode plots of the control-to-output transfer function obtained using both the mathematical model and the experimental results are provided in Figure 11. The Bode magnitude and phase responses match closely. The only discrepancy that happens around 15 kHz is mainly due to the inclusion of the switching frequency during the experiment. However, this region is beyond the range where the averaging performed in preceding sections is valid. The resonant frequency occurs at:

$$\omega_o = \sqrt{\frac{2r_1 + D'^2R}{RLC + 2LCr_C}}. (53)$$

Energies **2021**, 14, 4098 13 of 29

**Figure 11.** Bode plot comparison of control-to-output transfer function from the small-signal model and experimental test bed.

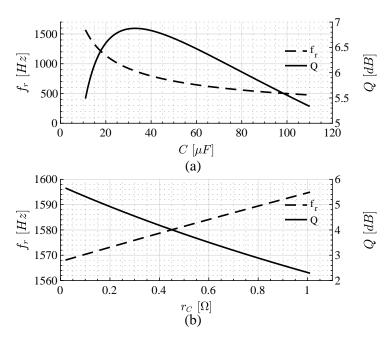

The control-to-output Bode plot has a peak value that occurs at the resonant frequency,  $f_r$ , of 1570 Hz and the measure of the dissipation in the system,  $Q = 5 \, \mathrm{dB}$  from the model whereas from the experimental results it is 1.8 dB. Both  $f_r$  and Q are impacted by the boost inverter capacitor selection. Figure 12 illustrates the impact of capacitance, C, and the capacitor ESR,  $r_C$ , on the transfer function. Capacitance primarily affects the resonant frequency with only a modest impact on Q; whereas, ESR primarily affects Q with only a modest impact on  $f_r$ . Thus a slight increase in ESR can substantially improve the transient behavior of the boost inverter by reducing Q. However, such a design selection can significantly impact converter efficiency. Therefore, ESR can be an important tradeoff to optimize.

**Figure 12.** Variation of the resonant frequency and Q as: (a) C is varied and (b)  $r_C$  is varied.

Energies **2021**, 14, 4098 14 of 29

### 3.5. Open-Loop Input Impedance

The open-loop input impedance,  $Z_i$ , is determined after setting the duty cycle perturbation  $\hat{d}$  to zero. Under this condition, the equivalent diagram becomes very similar to that of the one presented in Figure 8. The equivalent voltage sources produce  $\hat{i}_1$  and  $\hat{i}_2$  through  $Z_1$  and  $Z_2$  respectively. The expression of the input impedance then becomes:

$$Z_{i} = \frac{\hat{v}_{i}}{\hat{i}_{1} + \hat{i}_{2}} \bigg|_{\hat{d} = 0}.$$

(54)

Considering the current  $\hat{i}_0$  flowing from node  $\hat{v}_{01}$  to node  $\hat{v}_{02}$ , the three mesh equations are:

$$\begin{bmatrix} (Z_1 + Z_3)D' & 0 & -Z_3 \\ -Z_3D' & Z_3D & 2Z_3 + R \\ 0 & (Z_2 + Z_3)D & Z_3 \end{bmatrix} \begin{bmatrix} \hat{i}_1 \\ \hat{i}_2 \\ \hat{i}_o \end{bmatrix} = \begin{bmatrix} \frac{\hat{v}_{in}}{D'} \\ 0 \\ \frac{\hat{v}_{in}}{D} \end{bmatrix}.$$

(55)

This results in  $\frac{\hat{t}_1}{\hat{v}_{in}}$ ,  $\frac{\hat{t}_2}{\hat{v}_{in}}$ , and  $\frac{\hat{v}_{in}}{\hat{t}_1 + \hat{t}_2}$  as follows:

$$\frac{\hat{i}_1}{\hat{v}_{in}} = \frac{Z_3^2(2D-1) + DR(Z_2 + Z_3) + 2DZ_2Z_3}{DD'^2(Z_3^2(R+Z_1+Z_2) + R(Z_1Z_2 + Z_1Z_3 + Z_2Z_3) + 2Z_1Z_2Z_3)}$$

(56)

$$\frac{\hat{i}_2}{\hat{v}_{in}} = -\frac{RZ_1 + RZ_3 + 2Z_1Z_3 - Z_3^2(2D - 1) - DR(Z_1 + Z_3) - 2DZ_1Z_3}{D^2D'(Z_3^2(R + Z_1 + Z_2) + R(Z_1Z_2 + Z_1Z_3 + Z_2Z_3) + 2Z_1Z_2Z_3)}$$

(57)

$$Z_{i} = \frac{\hat{v}_{in}}{\hat{i}_{1} + \hat{i}_{2}}$$

$$= \frac{D^{2}D^{2}(Z_{3}^{2}(R + Z_{1} + Z_{2}) + R(Z_{1}Z_{2} + Z_{1}Z_{3} + Z_{2}Z_{3}) + 2Z_{1}Z_{2}Z_{3})}{R(Z_{1} + Z_{3})(1 + 2D) + 2D^{2}Z_{1}Z_{3} + 2D^{2}Z_{3}(R + Z_{2}) - Z_{3}^{2}(4DD^{2} - 1) + D^{2}R(Z_{1} + Z_{2})}.$$

(58)

# 3.6. Open-Loop Output Impedance

The open-loop output impedance of the boost inverter is determined considering perturbation at the load side. Considering  $\hat{d} = 0$  and  $\hat{v}_{in} = 0$  in Figure 7 the output impedance becomes:

$$Z_o = \frac{\hat{v}_o}{\hat{i}_o} \bigg|_{\hat{d}=0; \hat{v}_{in}=0} = (Z_1 || Z_3 + Z_2 || Z_3) || R.$$

(59)

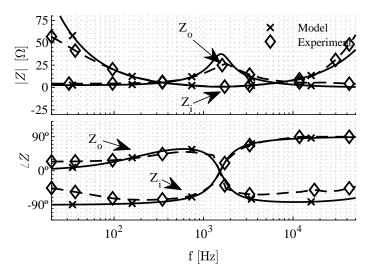

Substituting (31) in (58) and in (59) gives the input impedance and output impedance transfer functions respectively. Furthermore, using the values listed in Table 1, the transfer functions  $Z_i$  and  $Z_0$  are determined at D=D'=0.5. The corresponding Bode plots depicted in Figure 13 compares the small-signal results with the experimental results. The input impedance reaches the lowest value at a frequency that produces a resonating effect in the system. The output impedance becomes maximum at that same resonance frequency. Although, the magnitude plots match very closely, the phase plots show some deviation which can be largely attributed to the length of the cables attached to both the input and output sides of the inverter along with the possible impedance mismatch during the measurement.

Energies **2021**, 14, 4098 15 of 29

**Figure 13.** Bode plot for the open-loop input and open-loop output impedances at D = D' = 0.5.

## 4. Voltage Mode Controller Design

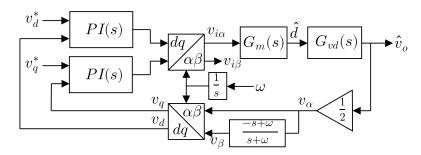

In this section, the control-to-output transfer function in (51) is used to design a voltage mode controller for the boost inverter. A conventional voltage mode controller uses a simple proportional integral (PI) controller for reference tracking. However, this approach suffers from errors in terms of magnitude mismatch and phase delay when tracking a sinusoidal signal. For a precise reference tracking, the synchronous reference frame proportional integral (SRFPI) controllers are often deployed in power electronics. An SRFPI provides control over both the direct and quadrature axis components of the reference sine wave. The top view of the overall system architecture is depicted in Figure 14. Only one voltage controller is needed to operate the system. The output of this controller produces the required duty cycle variation  $\hat{d}$ . This variation is then combined with the fixed duty cycle D to produce the final duty cycles,  $D \pm \hat{d}$ . The PWM signals for the respective boost converters are generated for controlling the individual boost sections.

Figure 14. Top view of the overall system.

The SRFPI voltage control algorithm applied to the current system is presented in Figure 15. The measured load voltage,  $\hat{v}_o$ , is reduced by a factor of two because each converter produces half the output voltage. This scaled-down voltage is termed as  $v_\alpha$ . After that, a fictitious orthogonal signal,  $v_\beta$ , is generated by applying an all-pass filter that produces a  $\frac{\pi}{2}$  delay at  $\omega$ :

$$G_{shift}(s) = \frac{-s + \omega}{s + \omega}. (60)$$

Energies 2021, 14, 4098 16 of 29

The  $v_{\alpha\beta}$  signals are then converted into direct and quadrature axis components,  $v_d$  and  $v_g$ , using the Park transformation matrix:

$$T_{\alpha\beta\to dq} = \begin{bmatrix} \cos\omega t & \sin\omega t \\ -\sin\omega t & \cos\omega t \end{bmatrix}. \tag{61}$$

The  $v_{dq}$  signals are compared against the reference values,  $v_d^*$  and  $v_q^*$ . The resulting error signals are passed through the PI controllers. The PI controller outputs are transformed back to  $v_{i\alpha}$  and  $v_{i\beta}$  using the inverse Park transformation matrix,  $T_{\alpha\beta\to dq}^{-1}$ . In the final step,  $v_{i\alpha}$  goes through the pulse-width-modulator to generate the switching signals. The transfer function of the PWM is:

$$G_m(s) = \frac{1}{v_d^*} e^{-j\omega T_d} \tag{62}$$

where,  $T_d$  is the digital control delay and  $\frac{1}{v_d^*}$  is the static gain. The overall system uses only one frequency, i.e., one time-base, as a reference.

**Figure 15.** Boost inverter voltage mode controller block diagram.

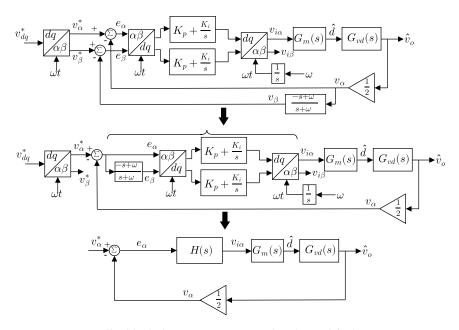

Tuning an SRFPI controller is challenging. The process is simplified by first rearranging the blocks in Figure 15 and then applying the well-known control theories. The simplified block diagram presented in Figure 16 has the reference expressed in the rotating reference frame.

Figure 16. Controller block diagram is rearranged and simplified.

Energies **2021**, 14, 4098 17 of 29

The error signal,  $e_{\beta}$ , is realized using (60) when the sinusoidal voltage is maintained at  $\omega$ . The  $e_{\beta}$  can be written in terms of  $e_{\alpha}$  as:

$$e_{\beta} = v_{\beta}^* - v_{\beta} = G_{shift}(v_{\alpha}^* - v_{\alpha}) = G_{shift} \cdot e_{\alpha}. \tag{63}$$

This results in an additional reduction in the block diagram as only  $v_{\alpha}^*$  exists in the simplified model. Setting the q axis reference,  $v_q^*$ , to 0, the reference reduces to:

$$v_{\alpha}^* = v_d^* \cos \omega t - v_q^* \sin \omega t = v_d^* \cos \omega t. \tag{64}$$

A further simplification is performed following the same technique described in [30,31]. The stationary reference frame equivalent of the voltage loop is deduced as shown inside the curly braces in Figure 16. The transfer function relating the expected output voltage,  $v_{i\alpha}$ , to the voltage error,  $e_{\alpha}$  is:

$$H(s) = K_p + \frac{K_i}{s^2 + \omega^2} \left( s - \omega \times \frac{-1 + \frac{\omega}{s}}{1 + \frac{\omega}{s}} \right). \tag{65}$$

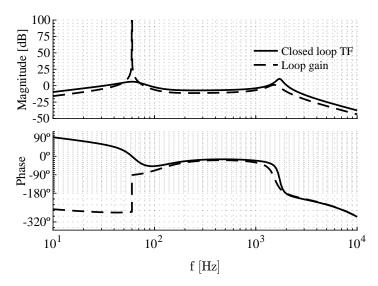

The controller design objectives are: (a) The loop-gain bandwidth ( $\omega_c$ ) is  $\frac{1}{9.21}$  of the switching frequency ( $\omega_{sw}$ ) and (b) the  $\omega_c$  is achieved at a phase margin ( $\phi_m$ ) of 45°. The loop gain of the simplified system is:

$$G_{ol}(s) = H(s) \times G_m(s) \times G_{vd}(s) \times 0.5. \tag{66}$$

For faster calculations of regulator parameters,  $K_p$  and  $K_i$ , the H(s) can be approximated to:

$$H(j\omega_{c}) = K_{p} + \frac{K_{i}}{-\omega_{c}^{2} + \omega^{2}} \left( j\omega_{c} - \omega \times \frac{-1 + \frac{\omega}{j\omega_{c}}}{1 + \frac{\omega}{j\omega_{c}}} \right)$$

$$\approx K_{p} + \frac{K_{i}}{-\omega_{c}^{2} + \omega^{2}} (j\omega_{c} + \omega)$$

$$|H(s)| \cong |K_{p}|. \tag{67}$$

This approximation is valid as long as  $\omega_c > \omega$  and  $|K_p|^2 \gg \left|\frac{K_i}{\omega_c}\right|^2$ . The condition  $\omega_c > \omega$  is usually satisfied, since  $\omega_c$  is set about  $\omega_{sw}/10$ , and  $\omega_{sw} >> \omega_c$ .

Applying the values listed in Tables 1 and 2 to (66) for an input voltage of 22 V and load reistance of 220  $\Omega$  and then setting  $|G_{ol}(j\omega_c)| = 1$ , the proportional gain becomes:

$$K_p \approx 0.077218.$$

(68)

The parameter  $K_i$  is calculated based on the phase margin requirement:

$$\angle G_{ol}(j\omega_c) = -180^\circ + \phi_m. \tag{69}$$

Evaluating the angular contributions from (51) and (62), and using the value of  $K_P$  in (65), the  $K_i$  value is found from (69). The integral gain becomes:

$$K_i \approx 33.732 \,\mathrm{rad/s}.$$

(70)

A quick check on the assumptions made earlier shows that  $\omega_c (= 10.2 \, \text{krad/s})$  is 27 times greater than  $\omega (= 377 \, \text{rad/s})$ . In addition, the value of  $|K_p|^2 (= 0.006)$  is approximately 545 times larger than the value of  $|K_i/\omega_c|^2 (= 1.1 \times 10^{-5})$ .

Energies **2021**, 14, 4098 18 of 29

| Component             | Parameter  | Value                 |

|-----------------------|------------|-----------------------|

| <b>*</b>              |            |                       |

| Nominal frequency     | $\omega$   | 377 rad/s             |

| Switching frequency   | $f_{sw}$   | 15 kHz                |

| Set point voltage     | $v_d^*$    | 25 V                  |

| Closed loop bandwidth | $\omega_c$ | $10.2\mathrm{krad/s}$ |

| Phase margin          | $\phi_m$   | 45°                   |

Table 2. Boost inverter operating conditions

The closed-loop transfer function and the loop-gain Bode plots are depicted in Figure 17. A very high loop gain of 300 dB is achieved at the nominal frequency of 60 Hz. To observe the gain plots around 0 dB more closely, a truncated magnitude plot is presented. The phase plot confirms that the desired phase margin of 45° is obtained.

Figure 17. Bode plots for the CLTF and the loop gain.

#### 5. Results and Discussions

The inverter operation is tested with the newly designed regulator gains. The results obtained from the small-signal mathematical model, the full order PLECS simulation, and the experimental test bed are compared and discussed in this section.

### 5.1. Simulation Results

Both the small-signal mathematical model and the full order model with the component parasitic are simulated in the PLECS platform. Three different perturbation cases are considered to check the system dynamics. These cases are discussed below.

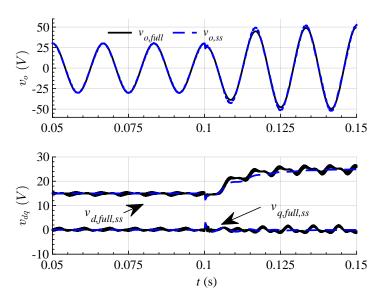

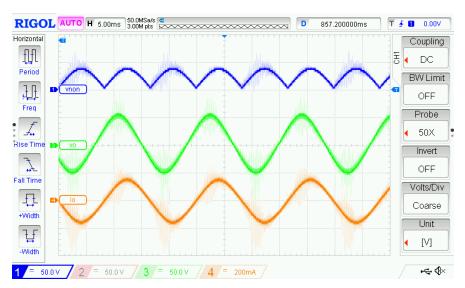

# 5.1.1. Change in Reference

A step-change in the reference voltage is made at  $t=0.1\,\mathrm{s}$ . The input voltage is kept constant at 22 V. The output voltage reference  $v_d^*$  increases from 15 V to 25 V. Figure 18 shows that, as a consequence, the peak value of the output voltage increases from 30 V to 50 V. In Figure 18, the transient responses closely agree when the full order model results are matched with that of the one obtained from the small-signal (SS) model results. The transients cease within a cycle or two. After that, a zero steady-state error is maintained. The 15 kHz switching transients are visible in the  $v_{dq}$  waveform. These switching ripples do not appear in the final output due to the natural low-pass filter characteristics of the inverter.

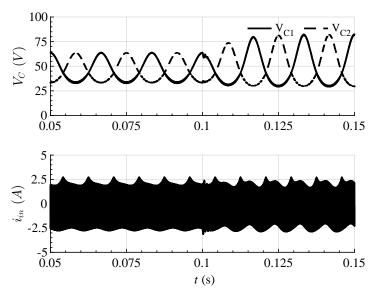

In Figure 19, the individual converter output voltages are depicted. The voltages represent an AC variation at the fundamental frequency added to a DC offset. The DC offset is equal in magnitude in both waveforms. The AC components are 180° out of phase.

Energies **2021**, 14, 4098 19 of 29

**Figure 18.** Comparison of the output voltages and the dq axis voltages from both the full order model and the small-signal model of the boost inverter. The d axis reference jumps from 15 V to 25 V and the q axis reference remains fixed at 0 V.

Figure 19. The output capacitor voltages and the supply current due to a step change in reference.

## 5.1.2. Change in Input

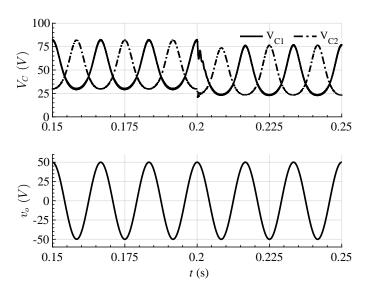

A step change in the input from 22 V to 18 V is made at t = 0.2 s. The individual capacitor voltages and the final output voltage are shown in Figure 20. An expected drop in the DC offset is observable due to the fixed part, D, in the duty cycle. The output voltage level recovers fast and shows minimal change during this event.

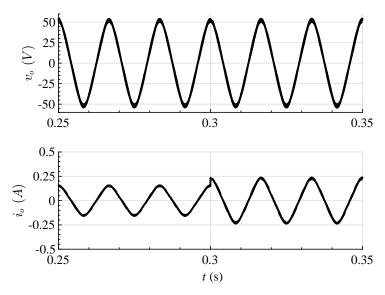

# 5.1.3. Change in Output Impedance

Initially, a  $343\,\Omega$  resistance is used as the load. At  $t=0.3\,\mathrm{s}$ , a second load consisting of  $690\,\Omega$  is added in parallel to the original one to get an equivalent of  $229\,\Omega$  load. The output voltage and output current values are recorded and presented in Figure 21. The current magnitude increases during the step change in load. The output voltage remains steady throughout the event.

Energies **2021**, 14, 4098 20 of 29

**Figure 20.** Voltages across the individual converters and the differential output due to a step change in the input supply. The input drops from 22 V to 18 V.

Figure 21. Output voltage and current due to an increase in the load.

# 5.2. Experimental Results

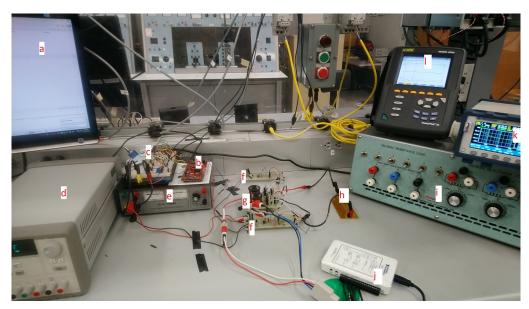

The mathematical model and the controller gains are verified using a hardware testbed. The single-phase single-stage boost inverter discussed here consists of two DC-DC boost converters. The converters are designed with identical inductor and capacitor values. The selection of inductors and capacitors is made following the formulas provided in [32]. The controller algorithm is implemented using a Texas Instrument's TMS320F28379D digital signal processor (DSP). The complete set up is depicted in Figure 22.

Energies **2021**, 14, 4098 21 of 29

**Figure 22.** Experiment testbed. (a) Code composer studio, (b) TI DSP, (c) sensor board, (d) DC power supply for the inverter, (e) sensor board power supply, (f) gate driver boards, (g) inverter, (h) 50  $\Omega$  load, (i) RLC load, (j) NI myDAQ for verification of  $G_{vg}$  and  $G_{vd}$ , (k) BK precision LCR meter for impedance verification, and (l) AEMC power quality analyzer.

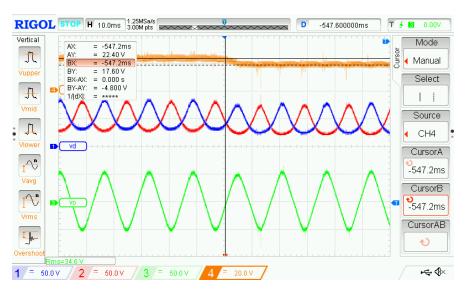

At first, the reference voltage,  $v_d$ , is changed from 15 V to 25 V. In Figure 23, the output voltage magnitude changes from 30 V to 50 V. The dq axis voltage calculations are internal to the DSP. As a result, their measurement required first passing the variables through two separate PWM channels and then measuring them across an active low-pass filter output. The cut-off frequency of the filter was selected high enough to preserve the dynamics of the signals. A volt on the oscilloscope display means an actual measurement of 10 V. The q-axis voltage swings between positive to negative values with an average of 0 V. The transient in the  $v_{dq}$  signal subsides within half-cycle. The dynamics match very closely with that of the ones presented in Figure 18.

**Figure 23.** Measurement of output voltage and *dq* axis voltages as the reference is changed.

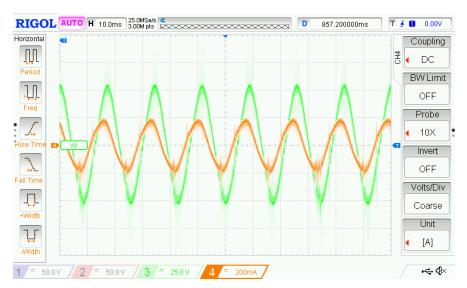

In the second experiment, the DC input is reduced from 22 V to 18 V. This step change has a minimal effect on the output voltage as seen in Figure 24. The DC offsets in  $V_{C1}$  and  $V_{C2}$  drop as expected due to the fixed part in the duty cycle. The signal dynamics match very closely with that of the ones in Figure 20. The AC variations in the capacitor voltages are  $180^{\circ}$  out of phase.

Energies **2021**, 14, 4098 22 of 29

**Figure 24.** Measurement of capacitor voltages and voltage across the load when the supply is changed.

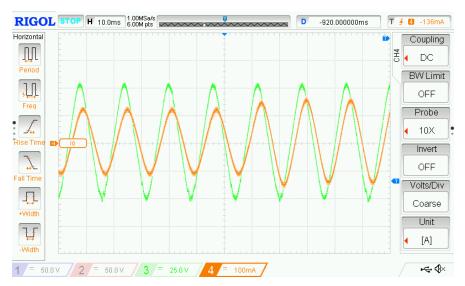

In the next experiment, a step-change in load is provided. The new load values were mentioned previously. The change in load has not resulted in any change in the magnitude or in the phase of the output voltage as seen in Figure 25. The load current has increased when the new load is added in parallel to the system. Due to the drops in the switches and in the connecting terminals, the current magnitude varies slightly when compared to that of the one in Figure 21. The transients in the experimental results are once again consistent with the simulation results.

Figure 25. Measurement of load voltage and load current due to a step change in resistive load.

The inverter system is then tested using an RC load with the resistor and the capacitor values of  $243\,\Omega$  and  $15.4\,\mu f$  respectively. The measurement of output voltage and current is presented in Figure 26. The current waveform leads the voltage waveform in this case.

Energies **2021**, 14, 4098 23 of 29

Figure 26. Measurement of output voltage and output current with an RC load.

The testbed is then subjected to an RLC load with the same resistor and capacitor values as mentioned previously. This time an inductor of 0.8 H is added to the system. The current in Figure 27 is lagging the voltage waveform, indicating that the load is more inductive. A step change in load is applied, which is noted by an increase in current magnitude.

Figure 27. Measurement of output voltage and output current with an RLC load.

A system is tested using a non-linear load. A full bridge rectifier is used to test the system. The waveforms in Figure 28 represent the inverter output voltage and output current along with the voltage measured across the diode bridge combination.

Energies **2021**, 14, 4098 24 of 29

**Figure 28.** Measurement of output voltage, output current, and the voltage across the full wave rectifier diode bridge circuit.

To demonstrate the switching ripple in the input current waveform, the measured input current in Figure 29 is zoomed at  $50\,\mathrm{us/div}$ . The inset cursor measurement shows a  $15\,\mathrm{kHz}$  ripple in the current output.

**Figure 29.** Measurement of output voltage and input current. The ripple in the current waveform demonstrates the 15 kHz switching frequency.

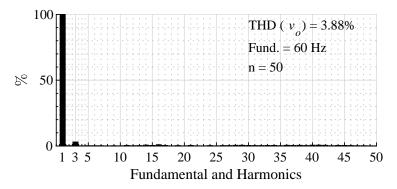

The total harmonic distortion (THD) of the output voltage is measured using an AEMC 8336 PowerPad III Power Quality Analyzer. The THD measurement is depicted in Figure 30. The measurement gives a THD value of 3.88% which is comparable to the values presented in [8,27,33]. When compared with the THD values reported in [8], the inverter discussed here has less THD level compared to the 2L-PWM and the 3L-PWM modulation techniques. However, in the same article, the L3L modulation technique shows better performance in terms of harmonics mitigation. The proportional resonant converter used to control the single-phase inverter in [33] provides a much higher THD level (11.8%) when compared to that of the one from the proposed controller. The THD values reported in [27] are slightly lower compared to the values measured in Figure 30 and below the limit mentioned in IEEE Std. 519-1992 [34]. However, the voltage control algorithm presented in this work shows a better performance in terms of tight regulation of output voltage magnitude. The peak-to-peak magnitude is maintained exactly at 100 V in this work compared to the one

Energies **2021**, 14, 4098 25 of 29

presented by Jha et al. which is 96 V. This is because there is a 300 dB gain at the operating frequency as shown in Figure 17. This high gain at the operating frequency is absent as shown in Figure 6 in [27] which results in a decreased magnitude at the operating frequency. Among the three voltage-mode controllers presented in their work, only two uses a negative feedback loop. In contrast to the method presented in this work (Figure 14), two different control loops are present and two different voltage references are required. The proposed method in this work needs only one set of references,  $v_{dq'}^*$  and compares the DC signals to generate errors that are passed through the PI controllers to produce the desired PWM signals. Whereas the control loop structure by Jha et al. uses a sinusoidal reference tracking mechanism. Using this scheme introduces steady-state amplitude and phase errors whenever a PI controller is used for tracking a sinusoidal reference signal. It is possible to reduce the error by increasing the controller gain. However, it compromises the system stability due to noise amplification.

Figure 30. Measurement of harmonics and THD.

## 5.3. Stability Margins and Sensitivity

The minimum load impedance required for the system to remain stable at all frequencies can be obtained by applying the Middlebrook's stability criterion. For that, the Thévenin equivalent output impedance of the inverter,  $Z_{0,th}$ , is determined from (59) by setting  $R=\infty$ . The peak value of the output impedance magnitude under this condition is 43.2 dB. Thus, the system is locally stable if the magnitude of the load impedance,  $Z_{load}$ , is greater than 145  $\Omega$ . If impedance magnitudes are lower, then the system will still be stable provided that the impedance ratio of the transfer function,  $\frac{Z_{0,th}}{Z_{load}}$ , satisfies the Nyquist stability test. The system stability margins for the closed-loop system in Section 4 are determined from the loop-gain Bode plot. The gain margin of the system is found to be approximately 8.43 dB at 1.62 kHz and the phase margin is found as 45° at 1.97 kHz.

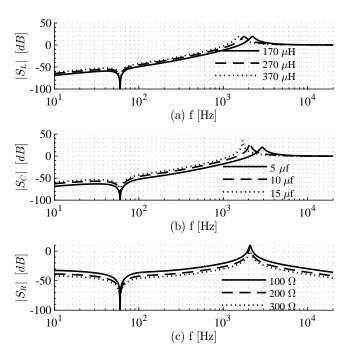

To perform a sensitivity analysis, the closed-loop transfer function,  $G_{cl}$ , is determined from (66). The sensitivity of  $G_{cl}$  with respect to parasitic components,  $r_L$ ,  $r_C$ , and  $r_{DS}$  are determined as  $S_{r_L}$ ,  $S_{r_C}$ , and  $S_{r_{DS}}$  respectively. The Bode plots respresenting the magnitude of these functions are given in Figure 31. It is observed that the system is less sensitive to changes in both  $r_L$  and  $r_{DS}$  at various frequencies. The sensitivity in both the cases becomes maximum at the resonant frequency which is expected. However, the magnitude of the sensitivity due to the different values of these two parasitic are tightly bounded in that region. The sensitivity due to the capacitor ESR, however, starts to increase as the frequency progresses. This indicates that several parallel capacitors are needed to be placed at the output side to reduce the overall  $r_C$ .

Energies **2021**, 14, 4098 26 of 29

**Figure 31.** Sensitivity due to: (a)  $r_L$ , (b)  $r_C$ , and (c)  $r_{DS}$ .

The sensitivity analysis is then carried considering variations in L, C, and load resistor, R. The Bode plots corresponding to the sensitivity functions,  $S_L$ ,  $S_C$ , and  $S_R$  are shown in Figure 32. It can be noted that the closed-loop transfer function's sensitivity is highly influenced by both the inductors and capacitors as the frequency approaches the resonant frequency and above. The sensitivity due to the load remains low at all frequencies other than the resonant peak as expected. The sensitivity in this case lowers as the load value is increased.

In all three cases, the sensitivity is lowest at 60 Hz.

**Figure 32.** Sensitivity due to: **(a)** *L*, **(b)** *C*, and **(c)** *R*.

Energies **2021**, 14, 4098 27 of 29

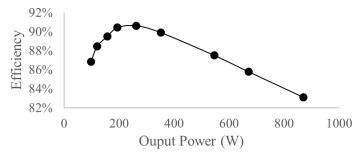

#### 5.4. Loss Estimation and Efficiency

The two main sources of losses in this system are the semiconductor device losses and the inductor  $I^2R$  losses. The low power inverter prototype in this work is constructed to verify the small-signal models and the controller algorithm. At this power level, the losses tend to dominate, resulting in poor system efficiency. To represent a practical system, the output voltage level is raised to  $110\ V_{rms}$  in the PLECS simulation platform. The system losses are then estimated using a high power MOSFET switch (C2M0025120D) for which a detailed thermal model suitable for PLECS simulation is readily available. The efficiency curve at different power levels in Figure 33 shows that the maximum efficiency occurs around 240 W. The loss breakdown for the inverter system is listed in Table 3.

Figure 33. Efficiency at different power levels.

| Loss Type   | Component     | Value            | %      |

|-------------|---------------|------------------|--------|

| Conduction  | Switch $S_1$  | 0.91 W           | 3.64 % |

| Switching   | Switch $S_1$  | 0.01 W           | 0.06%  |

| Conduction  | Switch $S_2$  | 0.55 W           | 2.18 % |

| Switching   | Switch $S_2$  | $0.02\mathrm{W}$ | 0.04%  |

| Copper loss | $r_{L}$       | 9.60 W           | 38 %   |

| ESR loss    | $r_C$         | 1.53 W           | 6.06 % |

|             | Per converter | 12.63 W          | 50 %   |

**Table 3.** Power loss distribution at the maximum output power.

Total

It is important to notice that a significant amount of loss is incurred due to the inductor parasitic. This loss can be reduced by an inductor with a lower ESR. When compared to the most recent single-phase boost inverter topologies researched in [35–37] the discussed inverter appears to be less efficient. This is mainly due to the fact that the latter topologies are inductor-less. However, the discussed topology has a much lower THD which makes it suitable for grid integration.

25.26 W

100%

#### 6. Conclusions

A single-phase single-stage boost inverter is analyzed. Both steady-state equivalent and AC small-signal mathematical models are derived that include component parasitic. The proposed models are not only accurate but also simpler compared to the existing models found in the literature review. The boost inverter open-loop input impedance and output impedance are expressed mathematically for the first time. The control-to-output transfer function including the loss terms helps to determine the appropriate controller gains in a practical inverter system. To improve the converter performance, the transfer functions for the input impedance and output impedance can be used to determine the input filter size and to calculate the load impedance for stable operation using the Middlebrook's stability criteria.

For accuracy verification purposes, the Bode plots obtained from the proposed transfer functions are compared with that of the ones found using the experimental results.

Energies **2021**, 14, 4098 28 of 29

A simple voltage mode controller developed in the synchronous reference frame is proposed for the first time to control the inverter operation. The controller gains are designed following the steps found in the classical control theory. The newly designed regulator gains are used in the full-order model as well as in the small-signal model. Finally, the control algorithm is implemented in a hardware setup. The experimental results match closely with that of the ones obtained from the simulation results. The advantages of using such inverter lies in its simple design, single-stage operation, and smaller footprint when compared to a double stage buck type inverter. Having said that, the inverter requires the use of two inductors and suffers from low device utilization as found in both the quasi-steady-state equivalent circuit model and efficiency estimation. The suggested future work for this system would be the determination of the lifetime of the capacitors that will include the measurement of fundamental and the harmonics of the voltage waveform and a detailed thermal model of the components. Additionally, the proposed models can be used to determine losses in the system more accurately.

**Author Contributions:** Conceptualization, M.R.; Formal analysis, M.R. and P.F; Funding acquisition, M.R.; Methodology, M.R. and J.K.; Resources, B.D.; Software, P.F.; Validation, M.R. and B.D.; Visualization, J.K.; Writing—original draft, M.R.; Writing—review and editing, P.F., J.K. and B.D. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported by the Grants and Research Funding Committee (GRFC) at Southeast Missouri State University awarded during the period of January 2018 through 30 June 2019.

**Conflicts of Interest:** The authors declare no conflict of interest.

#### References

- 1. Alajmi, B.N.; Ahmed, K.H.; Adam, G.P.; Williams, B.W. Single-Phase Single-Stage Transformer less Grid-Connected PV System. *IEEE Trans. Power Electron.* **2013**, 28, 2664–2676. [CrossRef]

- 2. Cáceres, R.; Barbi, I. A Boost DC-AC converter: Operation, analysis, control and experimentation. In Proceedings of the 1995 IEEE IECON 21st International Conference on Industrial Electronics, Control, and Instrumentation, Orlando, FL, USA, 6–10 November 1995; Volume 1, pp. 546–551.

- 3. Xue, Y.; Chang, L.; Kjaer, S.; Bordonau, J.; Shimizu, T. Topologies of Single-Phase Inverters for Small Distributed Power Generators: An Overview. *IEEE Trans. Power Electron.* **2004**, *19*, 1305–1314. [CrossRef]

- 4. Das, H.S.; Tan, C.W.; Yatim, A.H.M.; bin Muhamad, N.D. Analysis and control of boost inverter for fuel cell applications. In Proceedings of the IEEE International Conference on the Power and Energy (PECon), Melaka, Malaysia, 28–29 November 2016; pp. 455–460.

- 5. Khan, A.A.; Cha, H.; Khan, U.A.; Kim, H.G. Four-switch buck-boost inverter for stand-alone and grid-connected single-phase PV systems. In Proceedings of the 2017 IEEE 3rd International Future Energy Electronics Conference and ECCE Asia (IFEEC 2017—ECCE Asia), Kaohsiung, Taiwan, 3–7 June 2017; pp. 460–465.

- 6. Singh, A.; Mirafzal, B. Three-phase single-stage boost inverter for direct drive wind turbines. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–7.

- 7. Nguyen, M.K.; Tran, T.T. A Single-Phase Single-Stage Switched-Boost Inverter With Four Switches. *IEEE Trans. Power Electron.* **2018**, 33, 6769–6781. [CrossRef]

- 8. Silva, G.V.; Andrade, J.M.D.; Coelho, R.F.; Lazzarin, T.B. Switched-Capacitor Differential Boost Inverter: Design, Modeling, and Control. *IEEE Trans. Ind. Electr.* **2020**, *67*, 5421–5431. [CrossRef]

- 9. Andrade, J.M.D.; Silva, G.V.; Coelho, R.F.; Lazzarin, T.B. The switched capacitor differential boost inverter applied to grid connection. *Int. Trans. Electr. Energy Syst.* **2020**, e12752. [CrossRef]

- Chamarthi, P.; Rajeev, M.; Agarwal, V. A novel single stage zero leakage current transformer-less inverter for grid connected PV systems. In Proceedings of the 2015 IEEE 42nd Photovoltaic Specialist Conference (PVSC), New Orleans, LA, USA, 14–19 June 2015; pp. 1–5. [CrossRef]

- 11. Jain, S.; Agarwal, V. A Single-Stage Grid Connected Inverter Topology for Solar PV Systems With Maximum Power Point Tracking. *IEEE Trans. Power Electron.* **2007**, 22, 1928–1940. [CrossRef]

- 12. Patel, H.; Agarwal, V. A Single-Stage Single-Phase Transformer-Less Doubly Grounded Grid-Connected PV Interface. *IEEE Trans. Energy Convers.* **2009**, 24, 93–101. [CrossRef]

- 13. Fang, Y.; Ma, X. A Novel PV Microinverter With Coupled Inductors and Double-Boost Topology. *IEEE Trans. Power Electron.* **2010**, 25, 3139–3147. [CrossRef]

- 14. Albea, C.; Gordillo, F. Control of the boost DC-AC converter with RL load by energy shaping. In Proceedings of the 2007 46th IEEE Conference on Decision and Control, New Orleans, LA, USA, 12–14 December 2007; pp. 2417–2422. [CrossRef]

Energies **2021**, 14, 4098 29 of 29

15. Cáceres, R.; Barbi, I. A boost DC-AC converter: Analysis, design, and experimentation. *IEEE Trans. Power Electron.* 1999, 14, 134–141. [CrossRef]

- 16. Tang, Y.; Yao, W.; Blaabjerg, F. A dual mode operated boost inverter and its control strategy for ripple current reduction in single-phase uninterruptible power supplies. In Proceedings of the 2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), Seoul, South Korea, 1–5 June 2015; pp. 2227–2234. [CrossRef]

- 17. Vazquez, N.; Cortes, D.; Hernandez, C.; Alvarez, J.; Arau, J.; Alvarez, J. A new nonlinear control strategy for the boost inverter. In Proceedings of the IEEE 34th Annual Conference on Power Electronics Specialist, PESC'03, Acapulco, Mexico, 15–19 June 2003; Volume 3, pp. 1403–1407. [CrossRef]

- 18. Sanchis, P.; Ursaea, A.; Gubia, E.; Marroyo, L. Boost DC-AC inverter: A new control strategy. *IEEE Trans. Power Electron.* **2005**, 20, 343–353. [CrossRef]

- Liang, T.J.; Shyu, J.L.; Chen, J.F. A novel DC/AC boost inverter. In Proceedings of the 2002 37th Intersociety Energy Conversion Engineering Conference, IECEC'02, Washington, DC, USA, 29–31 July 2004; pp. 629–634.

- Sreekanth, T.; Lakshminarasamma, N.; Mishra, M.K. A Single-Stage Grid-Connected High Gain Buck-Boost Inverter With Maximum Power Point Tracking. IEEE Trans. Energy Convers. 2017, 32, 330–339. [CrossRef]

- 21. Cortes, D.; Vázquez, N.; Alvarez-Gallegos, J. Dynamical sliding-mode control of the boost inverter. *IEEE Trans. Ind. Electr.* **2009**, 56, 3467–3476. [CrossRef]

- 22. Cáceres, R.; Barbi, I. Sliding mode controller for the boost inverter. In Proceedings of the V IEEE International Power Electronics Congress Technical Proceedings, CIEP 96, Cuernavaca, Mexico, 14–17 October 1996; pp. 247–252.

- 23. Martínez-Salamero, L.; Valderrama-Blavi, H.; Flores-Bahamonde, F.; Bosque-Moncusi, J.M.; García, G. Using the sliding-mode control approach for analysis and design of the boost inverter. *IET Power Electr.* **2016**, *9*, 1625–1634. [CrossRef]

- 24. Zhao, W.; Lu, D.D.C.; Agelidis, V.G. Current Control of Grid-Connected Boost Inverter With Zero Steady-State Error. *IEEE Trans. Power Electron.* **2011**, *26*, 2825–2834. [CrossRef]

- 25. Khan, A.A.S.; Rahman, K.M. Voltage mode control of single phase boost inverter. In Proceedings of the 2008 International Conference on Electrical and Computer Engineering, Dhaka, Bangladesh, 20–22 December 2008; pp. 665–670.

- 26. Cáceres, R.; Rojas, R.; Camacho, O. Robust PID control of a buck-boost DC-AC converter. In Proceedings of the INTELEC. Twenty-Second International Telecommunications Energy Conference (Cat. No.00CH37131), Phoenix, AZ, USA, 10–14 September 2000; pp. 180–185. [CrossRef]

- 27. Jha, K.; Mishra, S.; Joshi, A. High-Quality Sine Wave Generation Using a Differential Boost Inverter at Higher Operating Frequency. *IEEE Trans. Ind. Appl.* **2015**, *51*, 373–384. [CrossRef]

- 28. Twining, E.; Holmes, D. Grid current regulation of a three-phase voltage source inverter with an LCL input filter. *IEEE Trans. Power Electron.* **2003**, *18*, 888–895. [CrossRef]

- 29. Tang, Y.; Bai, Y.; Kan, J.; Xu, F. Improved Dual Boost Inverter With Half Cycle Modulation. *IEEE Trans. Power Electron.* **2017**, 32, 7543–7552. [CrossRef]

- 30. Monfared, M.; Golestan, S.; Guerrero, J.M. Analysis, Design, and Experimental Verification of a Synchronous Reference Frame Voltage Control for Single-Phase Inverters. *IEEE Trans. Ind. Electron.* **2014**, *61*, 258–269. [CrossRef]

- 31. Golestan, S.; Monfared, M.; Guerrero, J.M.; Joorabian, M. A D-Q synchronous frame controller for single-phase inverters. In Proceedings of the 2011 2nd Power Electronics, Drive Systems and Technologies Conference, Tehran, Iran, 16–17 February 2011; pp. 317–323. [CrossRef]

- 32. Erickson, R.W.; Maksimovic, D. *Fundamentals of Power Electronics*, 3rd ed.; Springer International Publishing: Berlin, Germany, 2020. [CrossRef]

- 33. Baier, C.R.; Torres, M.A.; Acuna, P.; Munoz, J.A.; Melin, P.E.; Restrepo, C.; Guzman, J.I. Analysis and Design of a Control Strategy for Tracking Sinusoidal References in Single-Phase Grid-Connected Current-Source Inverters. *IEEE Trans. Power Electron.* **2018**, 33, 819–832. [CrossRef]

- 34. Blooming, T.; Carnovale, D. Application of IEEE STD 519-1992 Harmonic Limits. In Proceedings of the Conference Record of 2006 Annual Pulp and Paper Industry Technical Conference, Appleton, WI, USA, 18–23 June 2006; pp. 1–9. [CrossRef]

- 35. Iqbal, A.; Siddique, M.D.; Ali, J.S.M.; Mekhilef, S.; Lam, J. A New Eight Switch Seven Level Boost Active Neutral Point Clamped (8S-7L-BANPC) Inverter. *IEEE Access* 2020, 8, 203972–203981. [CrossRef]

- 36. Siddique, M.D.; Mekhilef, S.; Shah, N.M.; Ali, J.S.M.; Meraj, M.; Iqbal, A.; Al-Hitmi, M.A. A New Single Phase Single Switched-Capacitor Based Nine-Level Boost Inverter Topology With Reduced Switch Count and Voltage Stress. *IEEE Access* 2019, 7, 174178–174188. [CrossRef]

- 37. Siddique, M.D.; Mekhilef, S.; Shah, N.M.; Sandeep, N.; Ali, J.S.M.; Iqbal, A.; Ahmed, M.; Ghoneim, S.S.M.; Al-Harthi, M.M.; Alamri, B.; et al. A Single DC Source Nine-Level Switched-Capacitor Boost Inverter Topology With Reduced Switch Count. *IEEE Access* 2020, 8, 5840–5851. [CrossRef]