# Hamburg University of Technology Institute of Embedded Systems

Master's Thesis

# Worst-Case Execution Time Analysis for C++ Based Real-Time On-Board Software Systems

Hazem Abaza April, 2021

Degree Program: M.Sc. Mechatronics

First Examiner: Prof. Dr.-Ing. Heiko Falk TUHH Institute of Embedded Systems Second Examiner: Prof. Dr.-Ing. Frank Thielecke TUHH Institute of Aircraft System Technology Supervisor : Dr.-Ing. Zain Hammadeh German Aerospace Center (DLR)

### Abstract

Autonomous systems are today's trend in the aerospace domain. These systems require more on-board data processing capabilities. They follow data-flow programming, and have similar software architecture. Developing a framework that is applicable for these architectures reduces the development efforts and improves the re-usability. However, its design's essential requirement is to use a programming language that can offer both abstraction and static memory capabilities. As a result, C++ was chosen to develop the Tasking Framework, which is used to develop on-board data-flow-oriented applications.

Validating the timing requirements for such a framework is a long, complicated process. Estimating the worst-case execution time (WCET) is the first step within this process. Thus, in this thesis, we focus on performing WCET analysis for C++ model-based applications developed by the Tasking Framework. This work deals with two main challenges that emerged from using C++: using objects impose the need for a memory model and using virtual methods implicate indirect jumps. To this end, we developed a tool based on symbolic execution that can handle both challenges. The tool showed high precision of nearly 90 % in bounding loops of the Benchmark suit. We then integrated our advanced analysis with an open toolbox for adaptive WCET analysis. Finally, we evaluated our approach for estimating the WCET for tasks developed by the Tasking Framework.

# DECLARATION

I hereby declare on oath that the work in this thesis was composed and originated by myself and has not been submitted for another degree or diploma at any university or other institute of tertiary education. I certify that all information sources and literature used are indicated in the text and a list of references is given in the bibliography.

> Hazem Abaza Hamburg, April 08, 2021

# Contents

| 10 |

|----|

| 11 |

| 11 |

| 13 |

| 13 |

| 14 |

| 14 |

| 15 |

| 15 |

| 15 |

| 16 |

| 17 |

| 18 |

| 18 |

| 19 |

| 19 |

| 20 |

| 20 |

| 21 |

| 22 |

| 22 |

| 22 |

| 23 |

| 25 |

| 28 |

| 28 |

| 25 |

| 20 |

| 20 |

| 27 |

|    |

| 3 | Tas | king Framework 29                              |

|---|-----|------------------------------------------------|

|   | 3.1 | Motivation                                     |

|   | 3.2 | Task-Channel Application Model    30           |

|   | 3.3 | Execution model                                |

|   | 3.4 | Tasking Framework in application    33         |

|   | 3.5 | Tasking Framework as C++ developing library    |

|   | 3.6 | Tasking Framework and Static analysis          |

|   | 3.7 | Tasking Framework in This Thesis               |

|   | 3.8 | Use-Cases from Tasking Framework               |

|   |     | 3.8.1 First Use-Case                           |

|   |     | 3.8.2 Second Use-Case                          |

|   |     | 3.8.3 Third Use-Case                           |

|   |     | 3.8.4 Fourth Use-Case                          |

|   |     |                                                |

| 4 |     | CET analysis – Opportunities and Challenge 39  |

|   | 4.1 | Motivation                                     |

|   |     | 4.1.1 Motivation Example                       |

|   | 4.2 | Using State of the Art Techniques and Tools 40 |

|   |     | 4.2.1 Source Code Level                        |

|   |     | 4.2.2 Intermediate Representation Level        |

|   |     | 4.2.3 Binary Level                             |

|   | 4.3 | Summary                                        |

| 5 | Svn | nbolic Loop Bound Analysis 45                  |

|   | 5.1 | Motivation                                     |

|   | 5.2 | preliminaries                                  |

|   | 5.3 | DELOOP                                         |

|   | 0.0 | 5.3.1 Basic Idea                               |

|   | 5.4 | Implementation   52                            |

|   | 0.1 | 5.4.1 Loop Detection                           |

|   |     | 5.4.2 Data-Flow Analysis                       |

|   |     | 5.4.3 Dynamic Symbolic Execution               |

|   |     | 5.4.4 Resolving Indirect Jumps                 |

|   |     | 5.4.5 Proof of Correctness                     |

|   | 5.5 | Primary Evaluation                             |

|   | 5.6 | Conclusion                                     |

|   | 0.0 |                                                |

| 6 |     | aluation 63                                    |

|   | 6.1 | Introduction                                   |

|   | 6.2 | Experimental Setup                             |

|   | 6.3 | Loops Results                                  |

|   |     | 6.3.1 Inputs Related Loops                     |

|   |     | 6.3.2 Tasks Related Loops                      |

|   |     | 6.3.3 Events Related Loops 71                  |

|   |     | 6.3.4 Channel Related Loops                    |

|   |     | 6.3.5 Application Related Loops                |

|   |     | 6.3.6 DELOOP Bounding Results                  |

# CONTENTS

|    | 6.4   | Re-construing the Control Flow Graph    | 76 |

|----|-------|-----------------------------------------|----|

|    |       | 6.4.1 Resolving Indirect Jump Example   |    |

|    | 6.5   | WCET Estimation                         | 79 |

|    | 6.6   | Performance                             | 80 |

| 7  |       | cussion                                 | 83 |

|    | 7.1   | Conclusion                              | 83 |

|    | 7.2   | Limitations                             | 84 |

|    | 7.3   | Future Work                             | 84 |

| Re | efere | nces                                    | 84 |

| Aj | ppen  | dices                                   | 85 |

| A  | Hel   | lo World Example from Tasking Framework | 85 |

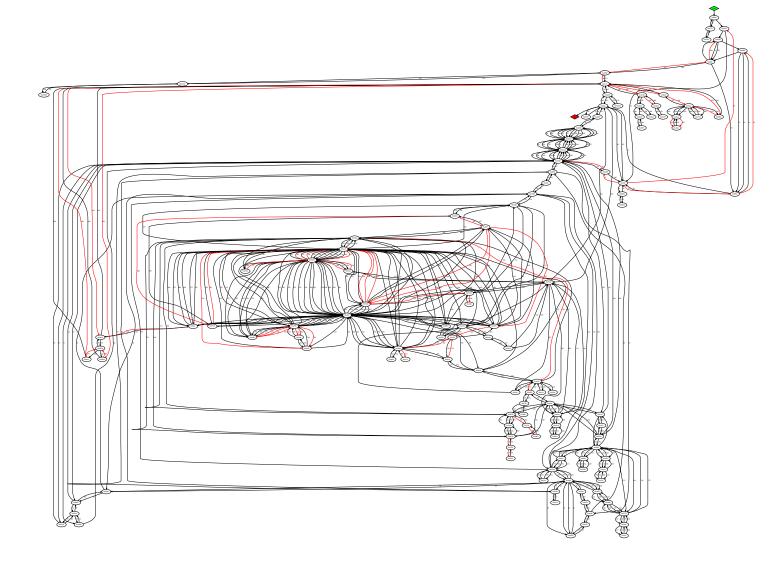

| в  | Syn   | nbolic Execution Graph                  | 88 |

6

# List of Figures

| 2.1  | Static Analysis Stages                                                         | 14 |

|------|--------------------------------------------------------------------------------|----|

| 2.2  | OTAWA Architecture                                                             | 21 |

| 2.3  | Loop Formulation with Polyhedron                                               | 24 |

|      |                                                                                |    |

| 3.1  | Tasking Framework Scheduling                                                   | 29 |

| 3.2  | Task Channel Model                                                             | 30 |

| 3.3  | BIRD - Attitude and Orbit Control System (AOCS) and Tasking Framework Elements |    |

| 3.4  | Sequence Diagram                                                               | 32 |

| 3.5  | BIRD - AOCS as realized in Tasking Framework                                   | 35 |

| 3.6  | Use-Case Number One                                                            | 37 |

| 3.7  | Use-Case Number Two                                                            | 37 |

| 3.8  | Use-Case Number Three                                                          | 38 |

| 3.9  | Use-Case Number Four                                                           | 38 |

| 4 1  |                                                                                | 40 |

| 4.1  | Analysis using SWEET                                                           | 42 |

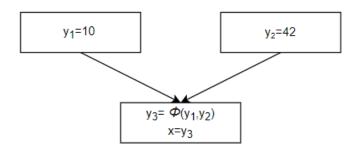

| 5.1  | $\Phi$ Function in the SSA Context                                             | 50 |

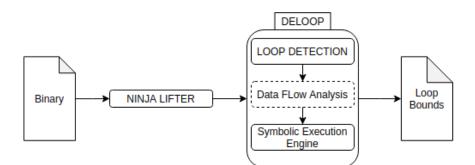

| 5.2  | DELOOP Basic Components                                                        | 52 |

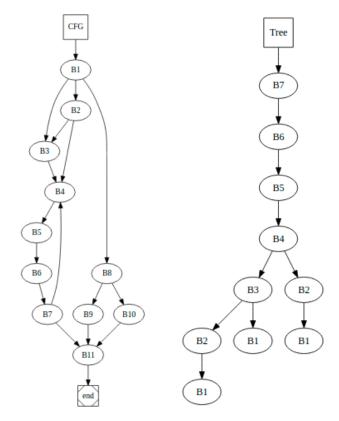

| 5.3  | Tree Generation From The CFG                                                   | 54 |

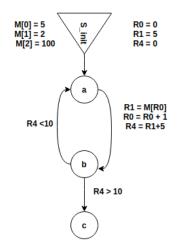

| 5.4  | Loop Execution with Z3 Engine                                                  | 57 |

|      |                                                                                |    |

| 6.1  | DELOOP with OTAWA                                                              | 65 |

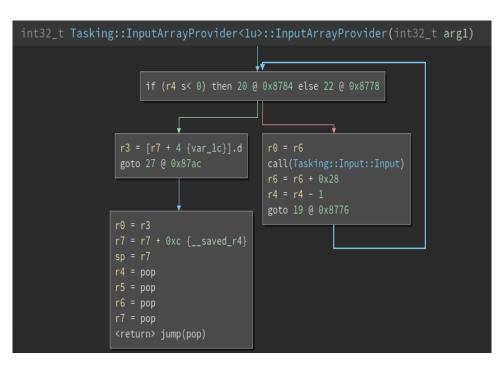

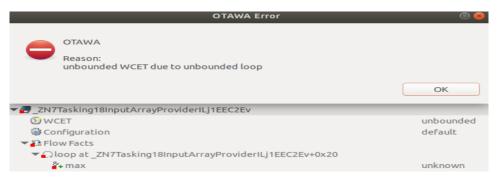

| 6.2  | Loop in Input Array Provider                                                   | 66 |

| 6.3  | Unbounded Input Array Provider Loop in OTAWA                                   | 67 |

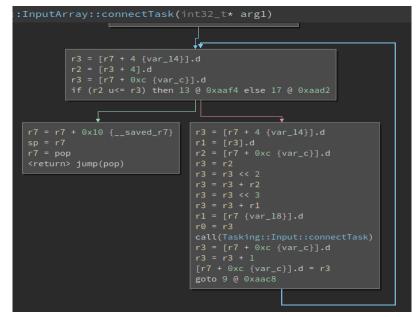

| 6.4  | reset and connectTask functions in InputArray                                  | 69 |

| 6.5  | Loop in Scheduler::restart                                                     | 71 |

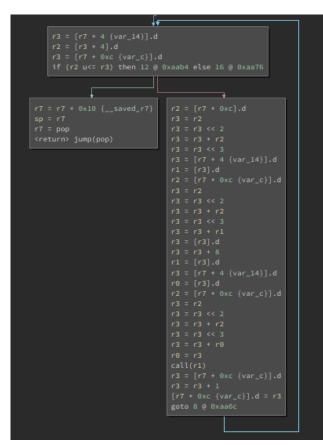

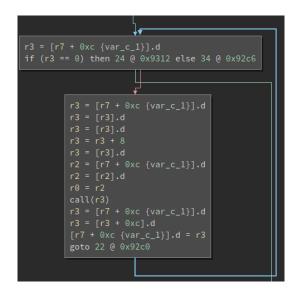

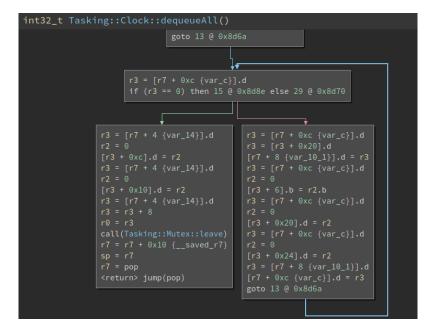

| 6.6  | Loop in Clock::dequeueAll                                                      | 72 |

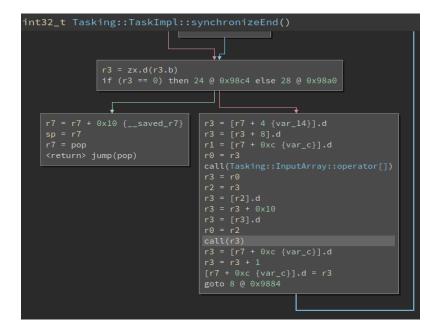

| 6.7  | Indirect Jump in TaskImpl::synchronizeEnd Function (address:0x9878)            | 76 |

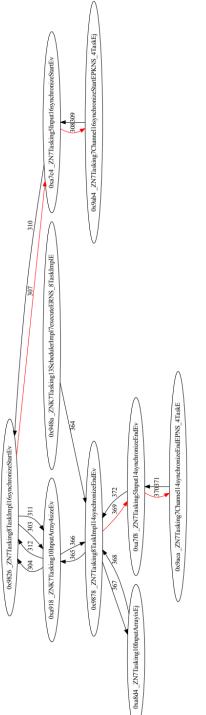

| 6.8  | Snippet from the Symbolic Execution Graph in Appendix B                        | 77 |

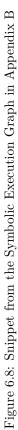

| 6.9  | Indirect Jump in Input::synchronizeEnd Function (address:0xa7f8)               | 78 |

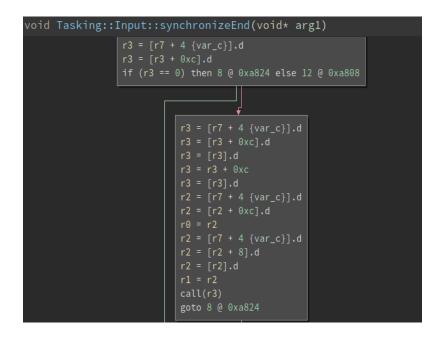

| 6.10 | WCET for Selected Functions from the Use-Cases                                 | 81 |

# List of Tables

| WCET Frameworks Comparison                                             | 21                                   |

|------------------------------------------------------------------------|--------------------------------------|

| Loop Bound Analysis Tools Comparison                                   | 26                                   |

|                                                                        |                                      |

| Benchmark Results                                                      | 61                                   |

| Comparison between DELOOP DF and DELOOP FE                             | 62                                   |

| Snippet of DELOOP Results For Input Array Provider                     | 67                                   |

| Snippet of DELOOP Results For the loops in Connect and Reset functions | 68                                   |

| DELOOP Results for the reset Loop in Scheduler::restart                | 70                                   |

| DELOOP Results For the loop in Clock::DequeueAll                       | 72                                   |

| Channel Related Loops                                                  | 73                                   |

| Complete DELOOP Results For The first Use-Case                         | 75                                   |

| WCET Results from Integrating DELOOP with OTAWA                        | 79                                   |

| Performance Results                                                    | 80                                   |

|                                                                        | Loop Bound Analysis Tools Comparison |

# List of Abbreviations

AI Abstract Interpretation

API Application Programming Interface

ASAP As Soon As Possible Scheduling

CFG Control FLow Graph

DSE Dynamic Symbolic Execution

GUI Graphical User Interface

ILP Integral Linear Programming

IR Intermediate Representation

ISA Instruction Set Architecture

LLIR Low-Level Intermediate Representation

SSA Single Static Assignment

WCET Worst Case Execution Time

# Chapter 1 Introduction

Today's software for aerospace systems is complex. This is due to the increasing number of features and the demand for high safety, quality, and reliability standards. Many design architectures have been adopted to develop these systems efficiently and reliably. The model-based approach is one of the most commonly used design patterns due to its ability to handle the systems' complexity.

The model-based approach involves designing models as elementary blocks which are then used to develop the complete software for the embedded system through automatically generated code. Following this pattern improves the productivity and ensures the software's correctness as the applications are designed in systematic and error-free methodology. MATLAB/Simulink and Stateflow are the most commonly model-based frameworks used in designing aerospace applications [30] [81] [61] [57] [45].

Due to the complexity and the dynamic orientation of the developed models, its analysis is challenging, especially when considering timing aspects. The most commonly used approaches for estimating WCET for model-based application are the integration and the measurement approaches. In the integration method, timing analyzer is inserted in the model workflow to trace the execution time of each functionality. This approach was used in various projects as [38] [76] [55] to predict the timing behavior. On the other hand, measurement analysis is a technique used to acquire timing information by measuring the execution time of the code executed dynamically on the target hardware. The analysis was used in several projects as [40] [87] [86] to estimate the worst case execution time.

The Institute for Software Technology at German Aerospace Center (DLR) has developed a model-based framework called Tasking Framework.<sup>1</sup> It is an execution platform for real-time onboard software systems. It allows the implementation of tasks as task graphs with arbitrary activation patterns. It is written in C++ following the event-driven programming paradigm. The Framework has been used for many real-world aerospace non-safety critical applications as in [78] and [44].

Certifying the Tasking Framework for safety-critical applications is a long, challenging process. As for all of its systems, the aerospace industry demands high standards of safety assurance. The most widely used standard for certifying aerospace-embedded applications as well as qualifying the implementation and verifying the tools is the ECS-Q-ST-40C standard [1]. It establishes five design assurance levels, ranging from E-Level, which is the least, to A-Level, which requires extensive

<sup>&</sup>lt;sup>1</sup>https://github.com/DLR-SC/tasking-framework

#### 1.1. CONTRIBUTION

testing and intensive verification. To qualify the Tasking Framework for C-Level certification, the standard requires ensuring the software's functional safety through proving functional correctness and hazards absence. The demonstrated proofs have to be beyond any reasonable or logical doubts.

To prove correct time behavior, it is necessary to prove that all the real-time tasks meet their deadlines, or that violating the deadlines will not harm the safety of the system. The worst-case execution times (WCET) and later the worst-case response times have to be determined to demonstrate deadline correctness. Performing WCET analysis using the previously mentioned approaches will not offer the required proof of correctness. Static worst-case execution time analysis is a good candidate for this mission. The static worst-case execution time analysis examines the program timing behavior without executing it directly on the hardware. This approach offers safe, and sound WCET and thus can be the first step in the validation process. In this thesis, we investigate the applicability of performing static WCET analysis for C++ model-based application as Tasking Framework.

# 1.1 Contribution

• Overview of the state-of-the-art static worst-case execution time analysis tools and techniques

We provide an overview of the available static analysis techniques and discuss their suitability for C++ model-based applications.

• New setup for static WCET for C++ model based applications

We introduced a new setup that can over-come the challenges of performing static WCET for C++ model based applications.

• Comprehensive Evaluation

We evaluate our setup using test-cases from Tasking Framework.

# 1.2 Structure

This thesis is organized as follows. In chapter two, we present the static analysis and its challenges. In chapter three, we demonstrate the Tasking Framework and discuss its applicability for static analysis. After that, chapter four focuses on the available tools' capabilities to perform WCET analysis for C++ model-based use-cases generated by the Tasking Framework. Chapter five presents our new symbolic execution approach for bounding loops and solving indirect jumps. Chapter six discusses the results of our approach. Finally, chapter seven presents our discussion and our future steps.

# Chapter 2

# Static Analysis

# 2.1 Introduction

Designing embedded systems for space applications is a challenging process. It requires accurate verification of its performance within its strict deadline. These systems are also called hard real-time embedded systems as they cannot miss their deadlines. Hard real-time embedded systems should respond and must react within particular time frames related to the events in their environment and the systems they control. Therefore, understanding the program execution time's characteristics is a fundamental key for building a reliable real-time system.

In hard real-time systems, the longest execution time of the program that shall occur must not exceed the specified time for the task to meet the system's timing requirements. The longest execution time is called Worst-Case Execution Time (WCET). The exact prediction of the program's WCET is a major issue. As the execution time is not always constant or consistent but instead shifts with various possibilities of events and inputs. These fluctuations happen due to variance in inputs and the software/hardware interactions.

The static analysis's main goal is to determine a given task's dynamic behavior without executing it on the target hardware. Instead, the task code is analyzed, sometimes with some annotations, to get the longest path in the task control flow graph. This control flow information is then combined with an abstract model of the target hardware to calculate an upper bound for the WCET. This is contrary to measurement-based analysis which executes every program fragment to calculate the maximum execution time. The result of the measurements are calculated by forcing the program to vary the initial conditions and inputs through certain control flow paths.

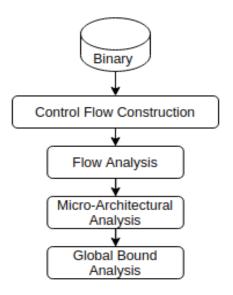

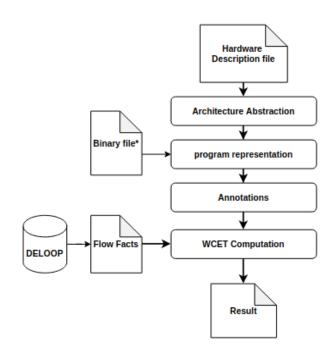

Recently, standard frameworks have been developed to perform a complete timing analysis for the code statically. Although most of them look similar from the general view, they have a lot of conceptual differences in between [56] [33] [37]. This chapter will give a general overview of the static analysis and the most commonly used techniques in each of its blocks. WCET static analysis is a safe technique to estimate a program's upper bounds for a certain architecture. A complete overview of the analysis is shown in figure 2.1. Briefly, the analysis starts by reconstructing and analyzing the program's control flow graph (CFG). Then, loop analysis and flow facts are defined through the CFG of the program to bound the execution times of each block in the program. After that, The WCET for each basic block is weighted by their execution bounds. Finally, The worst-case execution path and time of the whole function or program are then defined using integral linear programming(ILP)[48].

In the following section, we will briefly present the stages of the analysis and each stage's role in driving the WCET.

Figure 2.1: Static Analysis Stages

# 2.2 Static Analysis Stages

### 2.2.1 Control Flow Graph Reconstruction

The program's flow can be specified by the control flow graph (CFG). This graph consists of two parts: **The basic blocks graph** and **the call graph**. A basic block is defined as a group of instructions that are executed sequentially ended with a jump instruction. The basic blocks graph describes the program's flow and the relations between basic blocks. While the call graph describes only the caller-callee relations [53].

The first step of the WCET static analysis is reconstructing the CFG. Rebuilding the CFG in WCET analysis is challenging ass it starts from the binary level, not from the source code level. The process of reconstructing the CFG started by analyzing the binary and disassembling it. The control flow is recreated from the disassembled instructions and then translated to intermediate representation to be furtherly analyzed.

#### 2.2.2 Flow Analysis

The flow analysis's main goal is to constrain the program paths to narrow the solution domain. It aims to find correlations between variable values, basic block iterations, and certain program paths. In order to achieve this, further analyses are performed as:

- Value Analysis: It defines an upper-bound of the values that a register or memory location may hold. This analysis is used later for exact control-flow and data-cash analysis [27].

- Loop Bound Analysis: It recognizes loops in the program and attempts to decide upper bounds for the number of a loop iterations [15][63]. Loop bounding problem can be seen as an extension of the halting problem. As it does not only ask whether the program will stop or not, but it also asks after how many times of execution and for this reason no automatic method for loop bounds analysis can give an exact answer regarding the loop bounds. The common used methodology is to identify loop counters, and then bound their starting values through incrementing it to the highest possible value. From this information, an upper bound for the loop iterations can be estimated [34].

- Infeasible Path Analysis: It detects sets of possible paths and eliminates the infeasible ones. It uses the result of the value analysis to drive correlations that define the number of executions of a basic block. These correlations are then used to bound the WCET [27].

### 2.2.3 Micro-Architectural Analysis

. It defines upper bound for the execution of every basic block using an abstract interpretation of the program. The analysis is supported by cash and pipeline analysis to improve its result.

- Cache Analysis: It determines upper bound for the cash hit and cash miss at each program point [36].

- Pipeline Analysis: It analyzes how instructions pass through the processor pipeline [59].

# 2.2.4 Global bounds analysis

The execution time of a basic block is calculated using execution time modeling. Execution time modeling maps a sequence of instructions to its execution time. One instruction's execution time may vary from one basic block to another based on the input parameters' values, the order of the instructions, and the processor's internal state during the execution. The execution time of a basic block ( $wcet_i$ ) is combined with its loop bounds frequency  $f_i$  to determine the execution time of the block **i**. The upper-bound of execution of the program is defined by an implicit path enumeration through the CFG using ILP. The optimization function for path enumeration is modeled as:

$$WCET = max(\sum_{i=0}^{n} wcet_i \times f_i)$$

(2.1)

The target function weights the execution time of each basic block i with its frequency bound f. A solution of the ILP maximizes the sum of these weights with the path constraints and corresponds to an upper bound on the execution times [72].

# 2.3 C++ Static Analysis Challenges

Performing static analysis is for C++ is challenging whether it is done on the binary of the source code level for the below reasons [54]:

#### • Language Evolution at a Breakneck Pace

Language evolution now, unlike earlier stages of C++, is much quicker. The language committee's decision for a three-year standardization cycle leads to new standards, e.g., C++14, C++17, and now C++20 in a shorter time span [2].

#### • Language Front-end

To accommodate all language features, C++ requires a complex front-end. On the other hand, the C front-end is simpler to implement and validate. In comparison with C, there are only a few front-ends that support modern C++.

#### • Hidden Complexity

C++ offers abstraction level that facilitates the code development process and improves the production quality. The abstraction and productivity come at the price of hidden underlying complexity. This complexity affects the analyzability of the code. For example, The standard libraries depend heavily on dynamic memory allocation, increasing the risk of having unpredicted dynamic allocation scenarios. Although the standard containers has easy-to-use data structures as maps, they are highly dynamic and hard to analyze.

#### • Dynamic Memory Allocation

C++ depends heavily on dynamic memory allocations. The life-span of objects in the heap is not limited by the scope in which the initialization has occurred. Thus, the de-allocation of such objects is done outside their initialization context. Verification and validation of C++with objects in the heap is challenging as it requires information about each object's life-span, which depends on the input data to the program.

#### • Dynamic Polymorphsim

Dynamic polymorphism also called dynamic dispatch means that function calls are resolved during the run-time which implemented in C++ through virtual methods. This mean that the CFG is dependent on the flow of the data in the program. As a result, precise data-flow analysis has to be implemented to assist the control-flow analysis to resolve the dynamic dispatch [89][24].

#### • Error handling

C++ handles errors through exceptions. The success of throwing exceptions is not always granted because most C++ compilers generate code which indirectly calls malloc to allocate heap memory for the exception item. Exception handling magnificently increases control coupling which occurs by adding indirect control path from each program point to the exception handlers. Therefore, not only the analysis complexity increases but also the accuracy of the analysis deteriorates. Analyzing exceptions is even more complex at the binary code level.

#### Static Analysis Challenges for C++ Safety Critical ap-2.4plications

In this thesis, we are only interested in analyzing a subset of C++ that fits safety-critical applications. Analyzing applications that are developed following the MISRA [3] standard down-grade the complexity of the analysis and automatically expel some of the previously mentioned challenges. This thesis aims to perform the static timing analysis for application as Tasking Framework, which is developed following safety-critical standards. For example, The most common features of the MISRA standard are:

- Single Point Function Exit (MISRA Rule 6-6-5)

- No Heap Memory Allocation (MISRA Rule 18-4-1)

- No Recursion (MISRA Rule 7-5-4)

- No Exceptions (MISRA Rule 15-0 -1)

Hardware requirements for safety-critical applications also down-grade the complexity of the problem dramatically. For safety critical applications, we can safely remove the cache and the pipeline analysis from our considerations. As due to their non-deterministic behavior, caches and multi staged pipelines are not allowed to be used in on-board systems. As a result, static WCET analysis challenges for C++ safety critical applications can be narrow down into two main problems:

• Control Flow Reconstruction due to indirect jumps

In C++ code, indirect jumps result mainly from virtual methods. They ensure that the correct function is called for an object to achieve polymorphism, which is resolved during run time. Such behavior is translated on the binary level to indirect jump instructions which are branch instructions whose values are only known during the run-time, not during the compilation. These branching statements are challenging for static analysis as they cease the reconstruction of the CFG during the static analysis. For example, at the end of a basic block, branch instruction like the one in listing 2.1 will lead to the analysis's failure as the analysis will not be able to determine the branch target of the instruction statically.

Listing 2.1: Branch Instruction.

3

#### • Loop Bounding

Defining loop bounds is an essential step to get accurate WCET. This step is challenging for C++ code for the many reasons to name a few:

- Most C++ loops iterate over containers as vectors. Information about the container's size and its location in the memory is essential to bound the loop. This information is not available on the source code level and requires binary analysis to extract.

<sup>1</sup> add r1, r2

$<sup>\</sup>mathbf{2}$ mov r2, #0x80 b r3

- In C++ begin\_expr and end\_expr refer to the iterator start and end points respectively. As for C++17, the begin\_expr and the end\_expr may have different types, additionally the type of the end\_expr does not have to be an iterator. Such behaviors increase the complexity of the analysis on the source code level [2].

- C++ loops may trigger deep copy during iteration if used with non-constant iterators affecting the code's execution time dramatically. This behavior is difficult to analyze on the source code level [2].

- Some C++ loops are hidden behind the constructor. Constructing n objects from the same class sometimes is translated to loops on the binary-level. These loops are hard to detect on the source-code level.

# 2.5 State of the Art Static Analysis Tools

Many static analysis frameworks have been developed to give a precise WCET estimations. To the best of our knowledge, there are no frameworks that have been dedicated to performing WCET analysis for C++ code. This section will give a complete overview of existing relevant frameworks, their capabilities, and limitations. At the end, we will summarize their potentials to perform static WCET analysis for C++ code.

### 2.5.1 Bound-T

Bound-T performs static WCET analysis on binary code. The tool design includes target-specific modules to decode the input files beside generic modules to reconstruct the control-flow graph. To determine loop bounds, Presburger Arithmetic is used to model the loop counters arithmetically. Finally, Integral Linear programming (ILP) is used to determine the worst-case execution path (WCEP) [50].

Bound-T has some challenges in its analysis techniques, for three main reasons [4]:

• Lack of pointer analysis

The absence of pointer analysis affects the accuracy of the complete analysis. The results can only be relevant if it is guaranteed that the analyzed program has no pointers that may affect the program's control flow.

• Variably-sized memory access

The whole CFG can be wrong if the program under analysis is accessing the same variable in different ways (sometimes as a word and others as a byte).

#### • Overflow or wrap-around wrong estimations

The main tool that Bound-T uses to analyze CFG and loop bounds is based on Presburger Arithmetic. Presburger Arithmetic is a weak model for computer Arithmetic. It solves equations with integer variables assuming that these integers are bounded and can never overflow.

# 2.5.2 SWEET

The WCET research group has developed SWEET (SWEdish Execution Time tool) at the Mälardalen Real-Time Research Center. The tool was designed following the classical WCET static analysis architecture with flow analysis, low-level analysis to get the WCET estimation. The heart of the tool is the flow analysis, which is based on Abstract Execution. Abstract execution is an abstract interpretation through which loops and function calls are analyzed and executed separately in the abstract domain with abstract variables values. These values correspond to the real values that the variable may hold during execution [33]. The input to SWEET is intermediate representation in ALF format. ALF is an intermediate representation (IR) developed to facilitates the flow analysis [41].

The major functions of SWEET tool are [58]:

- **Portable analysis across different formats** In order to keep SWEET portable, all analyses are performed in ALF format. Thus, before using SWEET, any format must be translated to ALF.

- Automatically annotate all program variables

The abstract execution model supports the tool to annotate each variable within the input source code through value analysis. SWEET abstract execution model outputs annotation log for every loop and variable in the input ALF file.

Despite its capabilities, SWEET has mainly two limitations:

• There is no C++ to ALF translator

To the best of our knowledge, although it was mentioned in [41], SWEET can not take C++ programs as input. Such a translator has not been developed yet, which makes the tool only accessible by C programs or PowerPC binaries [62].

#### • Recursive functions can not be analyzed

The SWEET tool will fail to analyze recursive function calls, making it difficult to be used in sophisticated industrial applications [58].

#### 2.5.3 Chronos

The Chronos works on C code. If loop bounds are not annotated, data flow analysis is performed at the beginning to determine loop bounds. The core of the framework performs the analysis on the binary level. To this end, the binary is disassembled to reconstruct CFG. Timing of each basic block from the micro-architectural analysis is then combined with the loop-bound data to estimate WCET. One of the greatest advantages of Chronos that is it supports modeling of pipeline and branch prediction [60]. Chronos will be a good candidate for C++ code analysis If we manage to change the Chronos C-based front-end. This is possible as it is an open-source project where the source code is accessible for doing investigative experiments. However, the framework shows only one limitation which is the difficulty in analyzing recursion [77].

#### 2.5.4 OTAWA

The research group of real-time systems developed OTAWA at the University of Toulouse to integrate all kinds of open-source WCET analysis. The main goal is to develop a base framework that supports experimenting state of the art WCET algorithms. To this end, OTAWA architecture is a little bit different from the previously mentioned frameworks. As shown in figure 2.2, the base of OTAWA is an architectural abstraction. Although it supports the Instruction Set Architecture (ISA) for multi-architectures, It hides the ISA information and only reveals information relevant to the WCET analysis. This facilitates the framework re-usability for different architectures [16].

The WCET estimation performed by OTAWA starts with the binary decoding and program reconstructing to get CFG and all basic blocks of the program. The heart of the framework appears in the next phases, where two kinds of analysis are performed: program and hardware analysis. The program analysis includes value, loop, and path analysis, while the hardware analysis includes cash analysis, pipeline, buffer analysis, and every processor feature that may impact the execution time. An execution graph is then created to collect timing information from the static analysis for every basic block resulting from program and hardware features. All these data are then encoded as ILP problem constrained with loop bounds to get the WCET.

OTAWA showed good results in the comparison of the WCET tools challenge [84]. The tool was able to handle dynamic function calls and recursion. The loop bound analysis tool of OTAWA showed good performance in detecting static, arithmetic, and infinite loop bounds. However, this was only tested on C code, not C++.

#### 2.5.5 aiT

ait is the industry-standard static analyzer. The tool is used to inspect the developed applications' timing behavior and provide a tight upper bound for its WCET. It is based on Abstract Interpretation which offers a proven accurate relation to the architecture's semantics. The results of the ait analysis are deterministic for all executions (including cache and pipeline behavior). The tool depends mainly on static analysis for resolving indirect jumps and bounding loops. If the tool failed, annotations for loops and branch targets are provided in separate files by the application developer. Besides, ait covers a wide range of hardware architectures with high precision in estimating the WCET. Additionally, ait's GUI offers deep insight into the processor's functionalities, which can be used for further program optimizations [5].

One of the institute of software technology at DLR long term goal is to proof that it is safe to design safety-critical model-based aerospace applications using C++ instead o C or Ada. To present the findings to the research and the industry community a decision was made to use open source tools through this process and thus closed source analyzers as aiT are out of the scope of this thesis.

Figure 2.2: OTAWA Architecture

# 2.5.6 Summary

Many frameworks have been developed to estimate WCET. The common idea behind most of them is based on reconstructing the CFG of the executable then combining it with the micro-architecture analysis in order to estimate the WCET of each basic block [16][4][60]. Table 2.1 summarizes the tools' abilities concerning different criteria. Besides showing that some tools may have the potential to analyze C++ code, our exploration also shows that some tools do not contain loop bound analysis as a part of their structure. Thus, in the next sections, we will explore the available loop bound analysis techniques and their conveniences for C++ code.

Table 2.1: WCET Frameworks Comparison

| WCET Tool | Tool Input | Loop bound analysis | Applicable for C++ |

|-----------|------------|---------------------|--------------------|

| Bound-T   | Binary     | X                   | X                  |

| SWEET     | ALF IR     | $\checkmark$        | Maybe              |

| Chronos   | Binary     | $\checkmark$        | X                  |

| OTAWA     | Binary     | ×                   | Maybe              |

# 2.6 Loop Bound Analysis

In various static program analyses, information about how frequently a loop is iterated is important. A correct static WCET analysis is based on safe upper bounds of loops. An automated analysis must be adopted to get safe WCET estimations to skip the error resulting from manually annotating loop bounds. In this chapter, we will give an overview of the available tools for loop bound analysis. We survey the annotation languages by investigating their strengths and limitations.

### 2.6.1 Pattern-Based Technique

Pattern-Based Technique was first introduced in [46]. The analysis uses predefined patterns to trace loop variants. It provides algorithms to bound loops with multiple exits on the assembly level with and without using annotations. However, The analysis focused only on instructions within the loop basic blocks making it difficult to analyze loops with external parameters [63].

As Pattern-Based approach is not only compiler-dependent, but it also depends on the level of code optimization. The pattern-Based approach was supported in [28] with data-flow analysis to enhance its abilities to deal with more complex loops structures. Such approach fails in resolving all kinds of loops completely. User annotations must be provided to ensure safe loop bounds.

The pattern-Based approach is implemented on the binary code. Binary code is the code that is executed, and thus it carries all the relevant flow information. However, depending only on low-level information to determine the loop bounds may lead to high-level data loss. For an effective design, loop bound analysis tools working on the executable level must maintain information as CFG and annotations in the source code [42]. aiT [5], the standard static WCET analyzer, uses this approach to provide tight loop bounds. Although applying the pattern-based approach on the binary level seems to have promising results, it does not provide a generic solution to determine loop bounds.

### 2.6.2 Slicing and Abstract Interpretation

The approach is based on the fact that each new iteration updates the state of the executing program. Then, bounding the number of states will deliver an estimation for the loop upper bound. Since these states may have identical program flow, counting them will lead to the maximum number of values for loop variables [34].

This analysis is developed using standard program analysis:

#### • Program Slicing

It is introduced in [85] is a program analysis that analyzes part of the code that affects certain computation functionality. A slice of a given program regarding certain slicing criteria is a subset of the program that contains all instructions affecting this property. In loop analysis, slicing is used to define variables and statements that are relevant when estimating loop bounds.

#### • Abstract Interpretation

Abstract Interpretation is an approximation for the semantic model of the program under analysis. This sound approximation which is first formalized in [27] is mainly used in undecidable problems as static loop analysis. Loop bound analysis uses it to define the upper value of the variables affecting loop bounds at every program's execution point.

#### 2.6. LOOP BOUND ANALYSIS

Various loop analysis tools introduced this approach on the intermediate representation level (IR) [34][22]. The intermediate representation code is generated by the compiler for purposes of transformation and optimization. The IR is semantically equivalent to the program being executed with the following characteristics:

- Smaller number of instructions

- Type safe

- Portable as it is independent of the compiler and target architecture

- Accurate and efficient for static analysis as control-flow, symbolic execution and graph isomorphism

These characteristics make it a strong candidate for all kinds of flow analysis [35].

As a part of SWEET [33], The loop bound analysis tool [34] was introduced to work on the ALF IR. As mentioned before, there is no C++ to ALF translator. Some trials have been done to translate the LLVM IR into ALF IR, which opens the door for all languages using the LLVM compiler's front-end. However, this approach failed because of the unavailability of a complete, accurate translation to LLVM [82].

#### 2.6.3Polyhedrons

In addition to the Slicing and Abstract Interpretation, many loop analysis frameworks [63][66][15] supported their techniques with polyhedron models to get effective and precise computation. A polyhedron(P) is an N -dimensional figure bounded with a set of linear inequalities such that:

$$P := \{x \in Z^N | Ax = a, Bx \ge b\}$$

$$(2.2)$$

Where  $A, B \in \mathbb{Z}^{mN}$ ,  $a, b \in \mathbb{Z}^m$  and  $m \in N$  [35][63].

for (int  $j = i + 1; j \le 6; j++$ ) {

//Condition;

if(j > 4) {

}

}

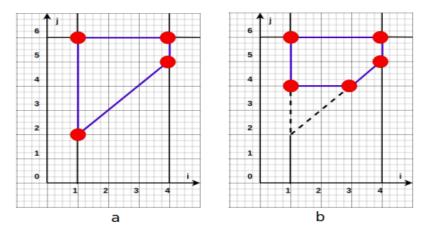

The polyhedral can precisely represent N-dimensional nested loops as N-dimensional polyhedron shape. Driving correlation between outer and inner loop is challenging and sometimes impossible, Yet, polyhedron makes it easier and less time-consuming. Consider the code in listing 2.2.

Listing 2.2: Nested loops modeled using polyhedron

for (int  $i = 1; i \le 4; i++$ ) { 1 2 3 4 567 }

To model this loop using polyhedron, the outer and the inner loop bounds has to be expressed as following:

$$\begin{bmatrix} 1 & 0 \\ -1 & 0 \end{bmatrix} \begin{bmatrix} i \\ j \end{bmatrix} \ge \begin{bmatrix} 1 \\ -4 \end{bmatrix}$$

(2.3)

$$\begin{bmatrix} -1 & 1\\ -0 & -1 \end{bmatrix} \begin{bmatrix} i\\ j \end{bmatrix} \ge \begin{bmatrix} 1\\ -6 \end{bmatrix}$$

(2.4)

The polyhedron a in figure 2.3 is modeled based on the two previous equations where each (i, j) point in the figure corresponds to a single iteration in the loop. Therefore, by determining the number of those pair points in the polyhedral area, we will restrict the loop iteration domain and obtain the number of iterations.

The polyhedron is also able to define other scenarios with branch conditions. Polyhedron b in figure 2.3 shows a new polyhedron based on the branch conditions in the code. The dotted line in polyhedron b in figure one shows the trimmed part from the polyhedron due to the code's branch condition [66].

Figure 2.3: Loop Formulation with Polyhedron

# 2.7 Loop Bound Analysis Tools

The following section will survey the available tools useful to bound loops of a C++ code. The survey will discuss the analysis used by the tool besides its strength and weakness concerning C++ loops.

# 2.7.1 r-TuBound

The pattern-based approach was introduced on the source code level in the r-TuBound loop analysis tool [56]. The tool's main goal is to build a control-flow graph for variables from extracted loops in the C/C++ source code. Applying various analyses and then translating these extracted loops into the form mentioned in listing 2.3 where a, b, c, d are symbolic integer-valued that are independent of  $i, g_1...g_m$  are boolean expressions and  $f_1...f_m$  are non-constant linear integer arithmetic functions independent of i. Based on the WCET 2011 tool challenge, the tool lacks specifying variable input ranges, it supports limited number of architectures and it also fails to analyze a C++ loop like the one in listing 2.4.

Listing 2.3: r-TuBound Transformation equation

### 2.7.2 oRange

oRange, is a very powerful loop analysis tool. It applies all kinds of analysis mentioned above to supply the user with two values, max, and min, representing the loop's upper and lower bounds. Unfortunately, oRange analyzes only C source code, making it so hard to utilize for our case. The oRange workflow starts by detecting loop indices and constructing symbolic expressions of the loops. A syntactic tree is then built based on abstract execution to combine the loop running context. Loop bounds are then formulated in the form of symbolic expressions. Finally, the resulting tree is resolved to the flow-fact numerically [18].

### 2.7.3 Polymas

The tool was built on polyhedron with an abstraction execution concept to tackle loop bounds. It analyzes the binary code running on the machine, which removes the C++ overhead and complexity. The tool proposes analysis based on polyhedrons to define a subset of registers and memory locations that may be effective to define loop bounds [15]. The tool was tested using Mälardalen WCET benchmarks in [17] however; the selected tests were simple loops with simple branching statements [43]. The tool failed to analyze simple C++ code with pointers as in listing 2.4, which makes the tool incompatible with our goal.

Listing 2.4: C++ loop over array

```

1 int main() {

2 int aNumber [] = { 16, 2, 77, 40, 12071 };

3 int counter = 0;

4 for ( int num : aNumber ) {

5 if (counter > 3) {

6 counter ++;

7 }

```

# 2.7.4 PAGAI

PAGAI is a tool to automate static analysis with input as LLVM IR [6] and an output as a list of primary constants for a certain control node in the source code. The tool provides control invariants based on user given assumptions or assertions using C/C++ standard macros. The tool checks the failure of a given assertion and indicates a warning in unsuccessful input. The execution of the tool terminates after falsifying the given assumption/assertion, and thus it can be used to check loop's variant values. The PAGAI framework is mainly based on abstract interpretation and convex polyhedrons to perform relation analysis between control-flow nodes [47].

### 2.7.5 Summary

Loop bound analysis is critical for sounding WCET analysis. In the previous sections, we explored the available loop bounds analysis tool focusing on their ability to deal with C++ loops. Table 2.2 summarizes the tools' abilities for different criteria. We found that most of the tools are based on abstract interpretation (AI) and polyhedron as main analysis techniques. In chapter four, we explore how we can use such tools to serve our goal. We integrate WCET tools with the loop-bound tools to match their input types and their analysis abilities.

Table 2.2: Loop Bound Analysis Tools Comparison

| Tool      | Analysis Input | Analysis Technique      | Applicable for C++              |

|-----------|----------------|-------------------------|---------------------------------|

| r-TuBound | C/C++          | Pattern-matching        | <b>✗</b> (limited C++ patterns) |

| oRange    | only C         | Slicing, Polyhedron, AI | ×                               |

| Polymas   | Binary         | Polyhedron, AI          | Maybe                           |

| PAGAI     | C/C++          | Polyhedron, AI          | Maybe                           |

# 2.8 Reconstructing The Control Flow Graph

Reconstructing the control flow graph from the binaries is challenging due to the presence of indirect jumps. An indirect branch has a dynamically defined target that may point towards number of locations in the program, while a direct jump has a statically specified target that points to a single location in the program [24]. Indirect jumps are commonly used to realize dynamic program behaviors by implementing common programming constructs, such as virtual function calls and calls through function pointers. Although indirect jumps are common and useful, due to their dynamic nature, it is usually difficult to resolve the target of an indirect jump through static analysis. This leads to inherent challenges in constructing the complete CFG [90]. In C++ binaries, indirect jumps are most commonly due to virtual methods where the target is calculated at run-time. Failure in resolving indirect branches leads to incomplete CFG and thus hinders the abilities of the static WCET.

Resolving indirect jumps falls into three categories:

#### • Static Analysis

During the analysis, the behavior of the target program is analyzed without concrete execution. The approach has the advantage of low cost and high coverage for the whole program. Thus, it is commonly used in industrial reverse engineering tools as IDA Pro [7]. However, this approach always leads to incomplete results due to the difficulty of resolving indirect jumps statically. The most commonly used analysis in the static approach is the data-flow analysis.

Several data-flow analysis techniques have been used to resolve indirect jumps. However, data-flow analysis requires a reliable CFG to analyze. This paradox situation is know in the literature as "chicken and egg" problem [79][73]. Program slicing is the most commonly data-flow analysis technique used to recover indirect jumps. It is a methodology for determining the set of statements of a program that potentially affects a variable's value at some point in the program. The goal of the analysis is to find all the possible influences on variables. During slicing analysis, indirect jumps are retrieved from the binary code using the classic source-destination algorithm, in which the instruction I' is said to be the lexical successor of instruction I if deleting I force the CFG to pass to I'. The technique starts with slicing the code at the indirect jump instruction, and then it performs expression substitution to high-level language. After that, it checks for pattern matching against indexed branch normal forms. Although some modifications were introduced, the proposed recovery heuristics were nearly used by most of the frameworks [25][26][32]. Despite the promising results with some tool-chains, the approach still result in incomplete CFG.

#### • Dynamic Analysis

In dynamic execution, the program is executed in order to extract the exact control flow graph. The idea is to execute programs on a set of test-cases and extract the control-flow information from the execution traces [90]. The approach can resolve a certain of indirect jumps and discover precise control flow. However, the completeness of the constructed CFG by this approach depends on the test-cases' capability to cover indirect jumps.

Traditional dynamic analysis techniques cover only a small portion of program execution paths. To improve code coverage, forced execution was introduced in [88]. In Forced execution, the code is executed semantically to explore the directions at each branch point and to compute the targets of indirect branches at run time in a scale-able way. For the same reason, The state of the art platform for resolving indirect jumps **Syder** [83] introduced symbolic dynamic execution support by program slicing to resolve indirect jump. Dynamic symbolic execution is an approach to systematically identify the program execution given an input value. The proposed approach was able to resolve indirect jumps in real world application with high accuracy and reliability.

#### • Hybrid Approach

Hybrid analysis has been used to resolve indirect jumps and to enhance the incompleteness of static analysis. In the hybrid approach, a set of seed tests are combined with statically computed jump targets to reconstruct the CFG. However, the results' completeness depends mainly on the generation of test-cases that can handle indirect jumps. Gray-box fuzzing has been introduced to generate test-case to handle indirect jumps. Gray-box fuzzing is an approach for software testing that is both salable and functional. It is commonly used in vulnerability identification and the generation of test-cases. Current gray-box fuzzing normally creates test-cases using an evolutionary algorithm based on input information from the execution. Evolutionary algorithms are randomized search heuristics that can be used to solve a variety of problems. They are governed by a number of criteria that are critical to the search's effectiveness [67]. In summary, the hybrid analysis is a promising approach to construct a more complete and precise CFG. Generating test-cases that handle more indirect jumps is the core of a successful hybrid approach. In the state-of-the-art approach to constructing CFGs [14][68][89], the test-case generation still faces the problem of unreliable test-cases that lead to incomplete coverage of the CFG.

# Chapter 3

# **Tasking Framework**

# 3.1 Motivation

Space missions are in continuous demand for computing resources to process more complex data or execute efficient algorithms. Missions like Rosetta [8] or landing of the Mars rover was designed based on lists of commands to control landing and maneuvering to reduce power consumption instead of trajectory control advance algorithms which required more power consumption.

During the development of the TET-1 satellite mission (Technology demonstrator) and Bispectral Infrared Detection (BIRD) missions, the estimator and observer control modules were computed in a fixed manner (order and time). The module's total computation time was the waiting time for the sensors' data plus the additional latency to ensure complete data arrival before computation. This model leads to a timing problem in the complete control cycle due to the latency overestimation. This has not been discovered until the launching where timing violation occurs in another bus application leading to changing the order of the computed tasks in a way that resulted in corrupted data and faulty behavior in the attitude and the complete orbit control system [65]. Hence, arises a need for a conceptual framework, which allows sharing resources based on certain configurations for all flight phases.

Figure 3.1: Tasking Framework Scheduling

The starting goal of the On-Board Computer–Next Generation project by DLR was to design qualified processing and network nodes with an operating system that ensures timing behavior for satellites. This design has also to cover the timing behavior of multi-cores and distributed systems. The core element in this design was the Tasking framework. The framework was designed mainly to improve the attitude control systems performance by dividing the computational data from the sensor into small parts, each of them called task which are then scheduled based on their availability.

Tasking Framework was designed as an application of inversion of control design pattern, which is used in designing lightweight frameworks. The framework was firstly used in the ATON (Autonomous Terrain-based Optical Navigation) project, which is a navigation system for a moon landing scenario using a couple of image processing algorithms [65]. The most important feature of the framework is changing the time behavior of the tasks being computed. Figure 3.1 shows the effect of following ASAP scheduling policy on the total response time instead of conservative scheduling in which computation is started at a predefined time in the computation cycle.

# 3.2 Task-Channel Application Model

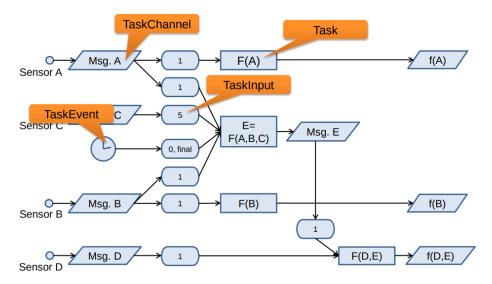

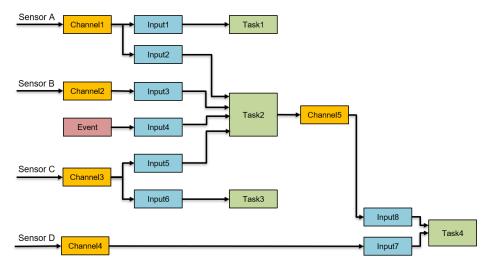

Tasking Framework was developed based on the task-channel model introduced in [39]. The concept is to have a separation between the data and functionality. In this model, A **task** is a stateless executable program, together with its memory and I/O ports while a **channel** is a message queue that connects one task's output port to another task's input port. In Tasking Framework, the channel represents a data container that can be handled through the task object. As shown in figure 3.2, it acts as an interface between tasks and interfaces with the software inputs and outputs. Using a task-channel model improves code re-usability. It is also very useful in distributed systems where some software components are needed to be migrated across computation nodes.

Tasking Framework is designed to tackle data-flow-oriented applications. In data-flow designs, the system's functionality is comprehended by examining the data flow through the system. Data-flow oriented techniques imply that the system's input data must be identified and processed to produce the required outputs. Using this approach, the program is modeled as a series of sequential operations happening in a certain order. Tasking Framework uses this design pattern to introduce structural API that does not depend on the data's availability but only on its sequence. **Except for the Execution class APIs**, All APIs introduce a high level of abstraction, making them independent of the input data's availability and the processed task. The framework can be seen as an abstraction layer similar to the operating systems that control the whole process in the abstract, generic, and deterministic way [44].

Figure 3.2: Task Channel Model

# 3.3 Execution model

In Tasking Framework an instance of a task  $\tau$  is activated when all the inputs to the task are activated. For example, in figure 3.3 Task **A** will be activated when input #1 is activated right after receiving Msg.A from the sensor A. Another way to activate a task immediately is to mark one of its inputs as final. If this input is activated, the task will run without considering the other inputs' state. For example, in figure 3.3 Task **E** will be activated when the task event (Timer) marks the input #0 as final. After that **C** will be activated instantaneously. An example on how timing parameters as task activation times and scheduler policy are specified in Tasking environment can be found in listing A.1.

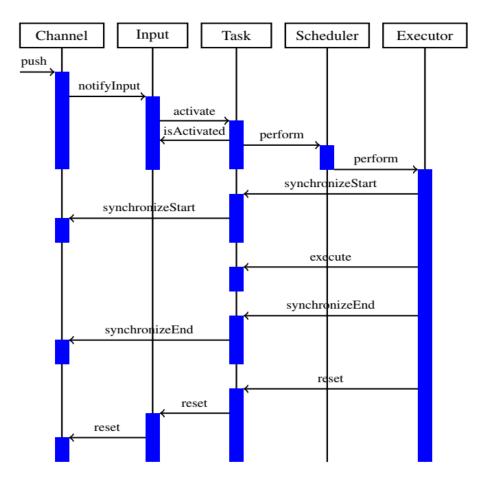

Figure 3.4 describes the sequence diagram of Tasking Framework. When a message arrives from a sensor, the main execution thread calls the **push()** method from the channel class to notify the associated inputs. If all task inputs are activated, The Tasking Framework will immediately signal a thread by calling **perform()** to execute the pending instance of this task. The task starts immediately with the scheduler of the framework. If a free resource, for example, a processor core, is available, the task will start immediately; otherwise, the task is queued [44][65].

Figure 3.3: BIRD - Attitude and Orbit Control System (AOCS) and Tasking Framework Elements

Figure 3.4: Sequence Diagram

# 3.4 Tasking Framework in application

Tasking Framework has been used in some DLR projects. The following paragraphs highlight 3 projects in which Tasking Framework has the main role. In Autonomous Terrain-based Optical Navigation (ATON) [78], Tasking Framework was used to implement the different functionalities as tasks and connect them via channels. Channels are data-containers storing the data, and component are activated periodically using events. The developers used 4 threads to execute the software on the prototype flight computer. In Euglena Combined Regenerative Organic food Production In Space project (Eu:CROPIS) [64], the Attitude and Orbit Control System (AOCS) was develoed using Tasking Framework. In Scalable On-Board Computing for Space Avionics (ScOSA) [80], a DLR project proposes and tests a new onboard computing architecture based on reconfigurable interconnected commercial off the shelf processors combined in one distributed system. Tasking Framework is used as a part of the middleware and the main API to develop the applications that run on ScOSA. An example of an application that will be developed using Tasking Framework to run on ScOSA is Onboard Data Analysis, Real-time Information System (ODARIS) [74] and Rendezvous Navigation [71]. Although Tasking Framework has been used in several applications, it has not been used for developing C-Level safety-critical tasks. Through all the previously mentioned projects, the WCET was estimated through extensive measurements in the operational environment.

# 3.5 Tasking Framework as C++ developing library

Tasking Framework is developed at the Institute for Software Technology, German Aerospace Center (DLR). It is an event-driven execution platform for real-time on-board software systems. It allows the implementation of tasks as task graphs with arbitrary activation patterns (periodic and sporadic). It is written in C++ following the event-driven programming paradigm and supports multi-threading programming [44].

Although it is not the norm for aerospace application to be developed in C++, it was used in the developing of this framework for the below reasons:

- First, The language offers modularity through the use of classes and its object-oriented functionality. Although C can also provide similar implementation to classes through struct, C++ outrages it due to constructors and deconstructors. Constructors and deconstructors guarantee that objects are always correctly initialized and are always removed after usage, preventing bugs and leakages.

- C++ allows programming abstractly and generically through templates. A template can be simplified as a macro that produces a complete full functionality for a different data type. Templates reuse algorithms for different data types efficiently and at a low resource cost.

- Type safety is another reason to use C++. Type safety means that the compiler ensures that no mix in data types occurs and that all the variables are correct. Unlike C++, C function memcpy can copy memory of double into an array of char and ending up with meaningless data.

- In large projects, using a unique descriptive naming is hard to achieve and it has always added prefixes to the names. This leads to long and unreadable names. C++ offers the simplest solution using namespaces. Namespaces allow multiple uses of the same name in different contexts, which are resolved later during compiler time. This C++ functionality ensures the multiple usages of the name in a descriptive, unique way.

- Unlike C, which uses malloc() and free() to allocate and free memory regions, C++ uses new and delete that adds constructors and destructors, ensuring that no memory leaks or bugs will occur.

- C++ introduces new concepts that do not exist in C as virtual functions, inheritance, operator overloading.

- References and smart pointers in C++ are safer than normal C pointers as they ensure that pointers can not be uninitialized or referenced to NULL.

# 3.6 Tasking Framework and Static analysis

In this section we discuss the applicability of static analysis to the Tasking Framework as a development library and to the applications developed using it. Our argumentation relays on few facts which we emphasize in the following points:

In data-flow programming the application is modelled as a directed graph, where data is processed by tasks then forwarded to subsequent tasks in a pipe-lined manner. The instructions do not have to wait for the preceding tasks to finish but can be executed as soon as the data are available, i.e. event-driven. The Tasking Framework API provides abstract classes to design the applications as directed graph of tasks and channels. The loops in the API that connect the tasks and channels are therefore bounded. In other words, the API has no dependencies on any data provided at run-time. The following loop for example in the function TaskInputArray::ConnectTask is bounded at compile time and its *length* represents the number of input a task has. In Figure 3.5 Task2 has 4 inputs, thus, *length* = 4.

for (unsigned int

$$i = 0u$$

;  $i < impl.length$ ;  $++i$ )

In Tasking Framework the channels represent data containers. The mechanism provided by Tasking Framework to exchange data between tasks and inputs is deterministic and does not rely on the data's type or value. For example, the loop in Listing 3.1 is bounded by the number of inputs associated to the considered channel.

```

Listing 3.1: Push Function

```

```

1 void Tasking::Channel::push(void)

2 {

3 for(InputImpl* i = m_inputs; i != NULL; i = i->channelNextInput)

4 {

5 i ->notifyInput();

6 }

7 }

```

#### 3.6. TASKING FRAMEWORK AND STATIC ANALYSIS

The tasks in the data-flow application are, in general, stateless bare executors of algorithms. The developer should override the virtual method *execute(void)* to implement the proper algorithm for each task. It is worth clarifying the fact that tasks are generally activated on the arrival of input data. However, it is not always the case that their CFG depends on the input data type or value. Therefore, the code in Task::execute() is in general statically analyzable as long as the developer adheres to implement stateless tasks whose CFG is independent of the input data's type or value.

Figure 3.5: BIRD - AOCS as realized in Tasking Framework

# 3.7 Tasking Framework in This Thesis

In order to use Tasking Framework in hard real-time safety-critical applications, verification and validations must be carried on to ensure its real-time capabilities. Analyzing the system's real-time capabilities and proving its abilities in meeting its deadlines can only be done using static analysis. Static analysis computes abstract over-approximations for all sets of architectural states at all points of execution. It provides a safety constrain that a certain condition will never occur at a certain execution point. This safety property allows proving a safe WCET upper bound. Providing WCET is the first step towards safety-critical applications being developed by the Framework. In this thesis, Our main goal is to define a framework that can perform automatic WCET static analysis for C++ applications as Tasking Framework [44].

Two main reasons make Tasking-Framework a good candidate test-case for our thesis.

#### • Real-time Guarantees

Tasking Framework is dedicated to develop data handling applications. It introduces a new scheduling model for satellite on-board data modeling and computation. The Framework does not follow the standard conservative scheduling where all computation processes have to wait till the arrival of one message. However, it introduces ASAP scheduling that makes better use of the available timing and improves the whole on-board system's worst-case response time. In this context, performing WCET analysis becomes essential towards computing end-to-end real-time guarantees on the proposed scheduling model for satellite on-board systems.

#### • C++ Real world Application

Tasking Framework is not a research platform that includes only subsets of C++. It is a real-world application through which we can demonstrate whether it is possible to perform WCET for model-based C++ code. The Framework includes most of the C++ structures which are used in embedded safety-critical applications. It includes classes, Abstract classes, virtual methods. This makes it a strong candidate for performing WCET analysis.

# 3.8 Use-Cases from Tasking Framework

Through this thesis, we selected four use-cases from Tasking Framework to analyze. The use-cases were carefully designed to cover all the functionalities of the Tasking Framework.

# 3.8.1 First Use-Case

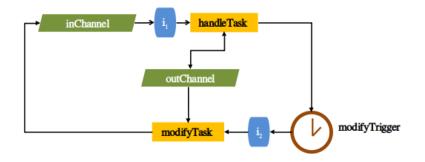

The first use-case in figure 3.6 is just a Hello World example that contains the basic components of the framework. The case is composed of *handleTask* which is activated when new data is pushed to *inChannel*. Next *handleTask* reads the values stored in *inChannel* and *outChannel*, saves the output to *outChannel* and then sets the timer, *modifyTrigger*, to 500 ms. After activation by the timer, *modifyTask* reads the value stored in *outChannel* and writes the result to *inChannel*. Then, it pushes inChannel, i.e., activating *handleTask*.

Figure 3.6: Use-Case Number One

# 3.8.2 Second Use-Case

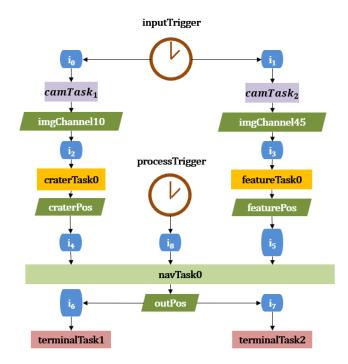

The second use-case in figure 3.7 is an actual real application of the Tasking Framework from the ATON project [78]. It is an application of a data handling model in the navigation of a sub-system. The system navigates through two cameras which are used to detect craters on the Moon's surface and then control the motor based on the craters' positions. The case consists of seven tasks, five channels and two timers. *camTask1* and *camTask2* are activated periodically every 1000 ms by *inputTrigger* while, *navTask0* is activated periodically every 100 ms.

Figure 3.7: Use-Case Number Two

### 3.8.3 Third Use-Case

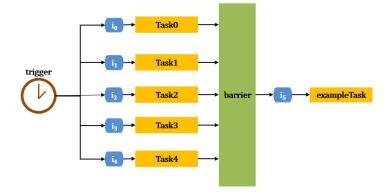

The third use-case in figure 3.8 is designed to cover the synchronization of the tasks in the Tasking Framework. The example consists of five tasks synchronized by barrier activated by the same trigger and another task starts later after the barrier. The five tasks are activated periodically every 1000 ms. When all the tasks finish execution, the barrier activates the *example task*.

Figure 3.8: Use-Case Number Three

# 3.8.4 Fourth Use-Case

The fourth example in figure 3.9 is a direct example for asynchronous execution in the Tasking Framework. The example consists of five tasks that are triggered by different timers. The tasks are even triggered with different periods ranging from 250 ms to 1500 ms.

Figure 3.9: Use-Case Number Four

38

# Chapter 4

# WCET analysis – Opportunities and Challenge

# 4.1 Motivation

This chapter will introduce the available opportunities and challenges to perform static WCET analysis on C++ code. Our main goal through this chapter is to put the literature review into action through:

- Testing the potentials of the available methodologies to get reliable results for C++

- Showing the effect of tweaking the input types

- Testing the effect of integrating tools to get a reliable static analyzer

Our target here is to answer the following questions:

- Is there an already defined methodology that is capable of analyzing C++ applications?

- If not, does integrating small changes to the current methodologies can lead to any results? For example, the modifications introduced in [82] to allow SWEET [62] to perform static WCET analysis on LLVM IR.

- If the above points are not applicable, what should be the next starting point?

# 4.1.1 Motivation Example

Defining loop bounds is an essential step to get accurate WCET. Automating this step is challenging especially for C++ code. As an example, listing 4.1 shows a loop from **Clock::dequeueAll()** function from Tasking Framework. As shown, the iteration bounds for the loop depend heavily on the size of data structures in the main memory. The loop iterates over a double-linked list in the memory and resets every list element. In order to bound such a loop, information about double-linked list sizes must be exploited. Our motivation here is to explore whether any of the previously mentioned methodologies can analyze such loop and detect the number of iterations.

Listing 4.1: dequeueAll Loop from Tasking Framework

```

1

timeQueueMutex.enter();

2

// Reset pointers of all events in queue

EventImpl* event = queueHead;

3

4

while (event != NULL)

5

ł

EventImpl* next = event->next;

6

7

event \rightarrow queued = false;

8

event \rightarrow next = NULL;

9

event \rightarrow previous = NULL;

10

event = next;

11

}

```

# 4.2 Using State of the Art Techniques and Tools

To perform a complete automated analysis, we experimented practically the capabilities of the previously mentioned tools. We divided the analysis into three categories based on the analysis input code type: source code level analysis, intermediate representation level analysis and binary-level analysis.

# 4.2.1 Source Code Level

To the best of our knowledge, no tool can perform complete static analysis for C++ code. However, there are tools like oRange [18] and PAGAI [47] that perform the loop bound analysis on the source code. During testing these tools on our Tasking Framework, we faced the following challenges:

- oRange [18] performs analysis only for C Code.

- Although PAGAI [47] performs the analysis on C and C++ code, the analysis runs only on programs structured in only one file.

To assess the usability of such tools, we compiled the code of the four Tasking Framework use-cases and lifted them back to C code using RetDec [9], which is a retargetable machine-code decompiler based on LLVM [6]. It was chosen among various decompilers because it detects and reconstructs C++ class hierarchies beside its capabilities in reconstructing function, call graphs, control-flow graphs, types and high-level constructs.

#### Results

- oRange is not able to calculate loop bounds correctly. It reports **NOCOMP** for all loops in the four use-cases from the Tasking Framework.

- PAGAI did not return useful information regarding loop bounds. For example, for lifted loop in **Tasking::Clock::dequeueAll()** shown in figure 4.2, PAGAI returned ambiguous bounding condition for all registers in the loop body. The tool result states that all register values should be larger than zero to assert that the loop path is reachable.

• Most of Tasking Framework loops depend heavily on memory accesses. Lifting the binaries back to C while maintaining a correct memory model is challenging to achieve. As in figure 4.2, the loop in **Clock::dequeueAll()** was translated to memory pointers initialized with zeros. This translation makes it hard for tools like oRange or PAGAI to bound the loops correctly.

| - LISUING 4.2. VELINGU UGUUGUGAN LOOD | Listing | 4.2: | C-Lifted | dequeueAll L | oop |

|---------------------------------------|---------|------|----------|--------------|-----|

|---------------------------------------|---------|------|----------|--------------|-----|

| 1  | while $((int32_t)(v13    v12) != 0)$ { |

|----|----------------------------------------|

| 2  | // 0xa54c                              |

| 3  | $v10 = (int32_t)v13 >> 31;$            |

| 4  | v11 = v10 + 48;                        |

| 5  | *(char *)(v10 + 10) = 0;               |

| 6  | $*(int32_t *)v11 = 0;$                 |

| 7  | $*(int32_t *)(v10 + 52) = 0;$          |

| 8  | $*(int32_t *)(v10 + 56) = 0;$          |

| 9  | $*(int32_t *)(v10 + 60) = 0;$          |

| 10 | $v12 = *(int64_t *)v11 >> 32;$         |

| 11 | v13 = v12 / 0x10000000;                |

| 12 | }                                      |

#### 4.2.2 Intermediate Representation Level

Performing the analysis on the intermediate representation was applicable using SWEET [49]. The framework performs complete automated analysis, including loop bound analysis. The recently developed LLVM IR to ALF (SWEET intermediate language) translator [82] offered a generic solution for our case. Figure 4.1 shows the required steps to perform the analysis using SWEET. Using the below bash commands in Listing 4.3, C++ code is translated to ALF IR, which is ready to be analyzed by SWEET.

Listing 4.3: SWEET to ALF

```

$ clang++ -Wall -emit-llvm -S -o - test.cpp |

opt -mem2reg -instcombine -instsimplify -instnamer |

llvm-dis -o test.ll

$ llc -march=alf -alf-standalone -o test.alf test.ll

```

#### Results

- Although SWEET performs automated loop bound analysis, it fails to bound the loops in Tasking Framework use-cases. The output flow facts file from SWEET was empty for all test-cases. In order for the analysis to proceed, flow-facts were given to SWEET.

- SWEET failed to build its abstract execution model due to the LLVM/ALF translator's failure in building correct memory model for the translated code.

- SWEET failed to find the worst-case execution path for all the use-cases.

Figure 4.1: Analysis using SWEET

## 4.2.3 Binary Level

We move forward to perform WCET analysis on binary-level using OTAWA framework [16]. The framework was used as an eclipse plugin. The use-cases were built normally for armV7m using **arm-none-eabi** toolchain with the same hardware description file given by the tool. In order to automate the analysis, we integrate POLYMAL [15] as a flow-facts generator to OTAWA.

#### Results

- OTAWA failed to reconstruct the complete CFG. Although the CFG of most functions was retrieved, the tool failed to restore the CFG of functions with indirect jump instructions.