Air Force Institute of Technology AFIT Scholar

Theses and Dissertations

Student Graduate Works

3-2021

# **Commuting Compositions for Quantum Circuit Reduction**

Brenna R. Cole

Follow this and additional works at: https://scholar.afit.edu/etd

Part of the Computer Engineering Commons, and the Electrical and Electronics Commons

#### **Recommended Citation**

Cole, Brenna R., "Commuting Compositions for Quantum Circuit Reduction" (2021). *Theses and Dissertations*. 4889. https://scholar.afit.edu/etd/4889

This Thesis is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact richard.mansfield@afit.edu.

## COMMUTING COMPOSITIONS FOR QUANTUM CIRCUIT REDUCTION

THESIS

Brenna R. Cole, Captain, USAF AFIT-ENG-MS-21-M-023

## DEPARTMENT OF THE AIR FORCE AIR UNIVERSITY

# AIR FORCE INSTITUTE OF TECHNOLOGY

Wright-Patterson Air Force Base, Ohio

DISTRIBUTION STATEMENT A APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

The views expressed in this document are those of the author and do not reflect the official policy or position of the United States Air Force, the United States Department of Defense or the United States Government. This material is declared a work of the U.S. Government and is not subject to copyright protection in the United States.

# COMMUTING COMPOSITIONS FOR QUANTUM CIRCUIT REDUCTION

### THESIS

Presented to the Faculty Department of Electrical and Computer Engineering Graduate School of Engineering and Management Air Force Institute of Technology Air University Air Education and Training Command in Partial Fulfillment of the Requirements for the Degree of Master of Science in Cyberspace Operations

> Brenna R. Cole, B.S. Captain, USAF

> > March 25, 2021

DISTRIBUTION STATEMENT A APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

# COMMUTING COMPOSITIONS FOR QUANTUM CIRCUIT REDUCTION

## THESIS

Brenna R. Cole, B.S. Captain, USAF

Committee Membership:

Laurence D. Merkle, Ph.D Chair

Scott R. Graham, Ph.D Member

Lt Col Patrick J. Sweeney, Ph.D Member

### Abstract

Quantum circuit simplification improves program execution on quantum hardware by reducing error from prolonged environmental interaction and noisy gate operations. One simplification technique is template matching, which repeatedly conducts local optimization by replacing small sequences of gates within a circuit by optimized versions. Underlying this method is the problem of identifying sequences matching templates. This is challenging because some, but not all, gates can commute within a circuit. This means there may not be a subcircuit that matches a template in the original circuit specification, but a match may exist in an equivalent rearrangement of gates. In such cases, certain reductions are possible only after the consideration of alternative gate orderings. This research focuses on the identification of commuting gate sequences in support of circuit reduction. In particular, this work generalizes the notion of commuting gates and layers to *n*-layer commuting compositions and identifies all three-layer commuting compositions composed of Toffoli, CNOT, and NOT gates for circuits with three to five qubits.

## Acknowledgements

To my parents—thank you for your love, support, and encouragement. You taught me the foundational lessons of hard work, integrity, and humility that form the bedrock of any academic endeavor.

To my advisor, Dr. Merkle—thank you for your guidance, patience and assurance. You taught me how to press forward when unsure of the destination. The Albert Einstein quote you so often shared exemplifies this: "If we knew what is was we were doing, it would not be called research, would it?"

To my committee members, Dr. Graham and Lt Col Sweeney—thank you for the classroom instruction, thesis feedback, and mentorship. Your passion for learning and teaching encourages me to continue exploring new ideas.

To my friends and fellow students—thanks for going on this journey with me. It's been fun!

Brenna R. Cole

# Table of Contents

|      |                                  | Pag                                                                                                                                                     | ;e                                                                                                      |

|------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Abst | ract                             | i                                                                                                                                                       | V                                                                                                       |

| Ackn | lowle                            | dgements                                                                                                                                                | v                                                                                                       |

| List | of Fi                            | gures                                                                                                                                                   | х                                                                                                       |

| List | of Ta                            | bles                                                                                                                                                    | ii                                                                                                      |

| I.   | Intr                             | oduction                                                                                                                                                | 1                                                                                                       |

|      | $1.2 \\ 1.3 \\ 1.4 \\ 1.5$       | MotivationProblem BackgroundQuantum Circuit Commuting CompositionsResearch ObjectivesScope1.5.1 Three Layers1.5.2 Three to Five QubitsDocument Overview | $     \begin{array}{c}       3 \\       4 \\       5 \\       6 \\       6 \\       7     \end{array} $ |

| II.  | Background and Literature Review |                                                                                                                                                         | 8                                                                                                       |

|      | 2.1                              | Quantum Computing Preliminaries2.1.1Qubits2.1.2Quantum Gates2.1.3Quantum Circuits2.1.4Circuit Representations                                           | 8<br>0<br>2                                                                                             |

|      | 2.2                              | Circuit Synthesis12.2.1Reversible Circuit Synthesis12.2.2Quantum Circuit Mapping22.2.3Hardware Constraints22.2.4Previous Work on Circuit Decomposition2 | 9<br>2<br>4                                                                                             |

|      | 2.3                              | Logical Circuit Optimization22.3.1Gate Count3.3.2Circuit Depth2.3.3Ancilla Lines33                                                                      | $0\\1$                                                                                                  |

|      | 2.4                              | Template Matching for Circuit Synthesis and<br>Optimization32.4.1Template Matching Overview32.4.2Template Matching Challenges3                          | 2<br>2                                                                                                  |

|      | 2.5                              | Qiskit Software                                                                                                                                         | 9<br>0                                                                                                  |

## Page

|      | 2.6                     | Summary                                                     | 43   |

|------|-------------------------|-------------------------------------------------------------|------|

| III. | Met                     | thodology                                                   | . 44 |

|      | 3.1                     | Overview                                                    | . 44 |

|      | 3.2                     |                                                             |      |

|      | -                       | Design Decisions                                            |      |

|      |                         | 3.3.1 NCT Gate Set                                          |      |

|      |                         | 3.3.2 Layers vs Gates                                       | . 46 |

|      |                         | 3.3.3 Qiskit Software                                       | . 46 |

|      | 3.4                     | Search For Three-Layer NCT Commuting Compositions           | 48   |

|      |                         | 3.4.1 Layer and Sequence Generation                         | 48   |

|      |                         | 3.4.2 CheckMatch Algorithm                                  | 52   |

|      | 3.5                     | 1 0                                                         |      |

|      |                         | 3.5.1 Number of Matching Sequences                          |      |

|      |                         | 3.5.2 Possibility of Circuit Reduction                      |      |

|      |                         | 3.5.3 Removing Redundant Gates                              |      |

|      |                         | 3.5.4 Existence of Single-Gate Layer Sequences              |      |

|      |                         | 3.5.5 Number and Type of Operations Per Match               |      |

|      | 3.6                     | Summary                                                     | 64   |

| IV.  | 7. Results and Analysis |                                                             | 65   |

|      | 4.1                     | Overview                                                    | 65   |

|      | 4.2                     | Search for Three-Layer NCT Commuting Compositions           |      |

|      |                         | 4.2.1 Generation of Sequences to Check                      | 65   |

|      |                         | 4.2.2 Example of Matching Three-Qubit Sequence              |      |

|      |                         | 4.2.3 Identifying Matching Sequences                        |      |

|      |                         | 4.2.4 Note on Computational Time to Find Matches            |      |

|      | 4.3                     | Sequence Analysis                                           | 99   |

|      |                         | 4.3.1 Existence of Three-Layer Commuting                    | 00   |

|      |                         | Compositions                                                | 99   |

|      |                         | 4.5.2 Elimination of Redundant Gates within<br>Sub-Circuits | 100  |

|      |                         | 4.3.3 Single Gate Layer Sequences                           |      |

|      |                         | 4.3.4 Number and Types of Gates in Sequences                |      |

|      | 4.4                     |                                                             |      |

|      |                         | v                                                           |      |

| V.   | Cor                     | nclusions1                                                  | 104  |

|      |                         | Overview                                                    |      |

|      | 5.2                     | Contributions                                               | 106  |

|      |                         | 5.2.1 Presentation of the Commuting Composition             | 100  |

|      |                         | Problem1                                                    | 106  |

## Page

|            | 522    | Investigation of Three-Layer NCT Commuting    |

|------------|--------|-----------------------------------------------|

|            | 0.2.2  | Compositions                                  |

|            | 5.2.3  | Proof of Non-Existence of Three-Gate NCT      |

|            |        | Commuting Compositions                        |

| 5.3        | Future | e Work                                        |

|            | 5.3.1  | Search for Commuting Compositions of          |

|            |        | Alternative Gate Sets or Numbers of Elements  |

|            | 5.3.2  | Develop an Efficient Method to Traverse a     |

|            |        | Quantum Circuit to Find Sub-Circuits and      |

|            |        | Replace with the Commuted Gate Ordering110    |

|            | 5.3.3  | Improve Implementation of CheckMatch          |

|            |        | Algorithm                                     |

|            | 5.3.4  | Analyze Trend between Sequence Count and      |

|            |        | Matches                                       |

|            | 5.3.5  | Apply Commuting Compositions to Reduce        |

|            |        | High-Cost Gates                               |

| 5.4        | Conch  | uding Remarks                                 |

| Appendix   | A A    | symptotic Time Complexity to Find Three-Layer |

| ripponum   |        | CT Commuting Compositions                     |

|            | 1      |                                               |

| Bibliograp | phy    |                                               |

|            |        |                                               |

# List of Figures

| Figure | Page                                              |

|--------|---------------------------------------------------|

| 1      | Bloch sphere                                      |

| 2      | CNOT gate                                         |

| 3      | Bell State circuit                                |

| 4      | OpenQASM code for Bell State circuit15            |

| 5      | Bell State circuit DAG16                          |

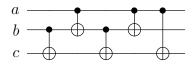

| 6      | Moving Rule                                       |

| 7      | Non-commuting gates                               |

| 8      | DAG circuit representations                       |

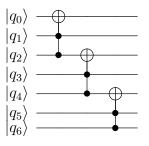

| 9      | NCT 1-bit adder circuit                           |

| 10     | MPMCT gate with four control lines                |

| 11     | MCT gate with three control lines                 |

| 12     | The NOT, CNOT, and Toffoli gates                  |

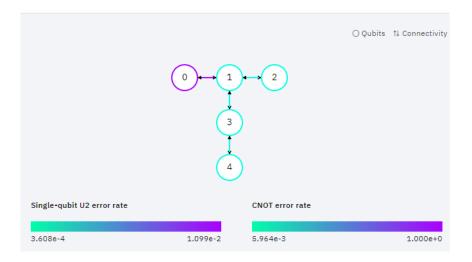

| 13     | Topology diagram for 5-qubit ibmq_5_yorktown25    |

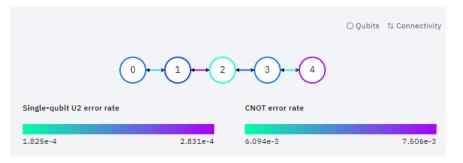

| 14     | Topology diagram for 15-qubit ibmq_16_melbourne25 |

| 15     | Barenco decomposition                             |

| 16     | Identity template                                 |

| 17     | Application of identity template                  |

| 18     | Library template                                  |

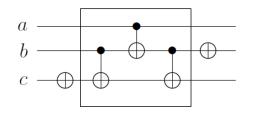

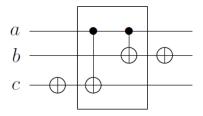

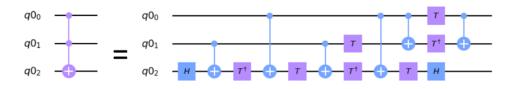

| 19     | Decomposed Toffoli gate                           |

| 20     | Toffoli gate layers                               |

| 21     | Qubit layout for ibmq_vigo59                      |

| 22     | Qubit layout for ibmq_santiago59                  |

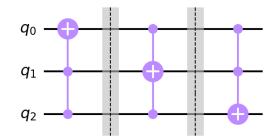

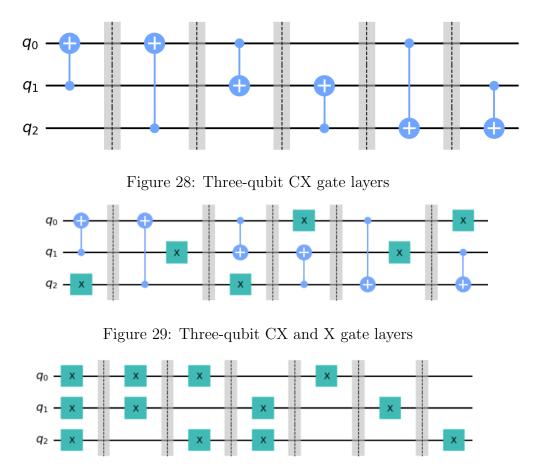

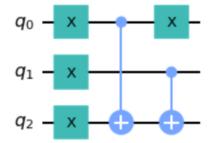

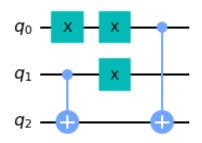

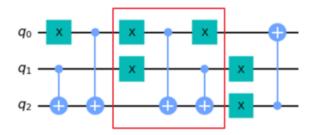

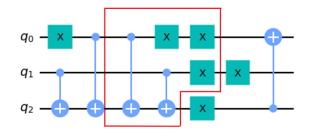

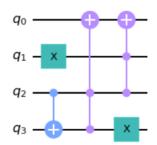

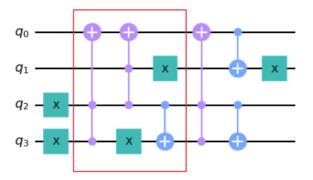

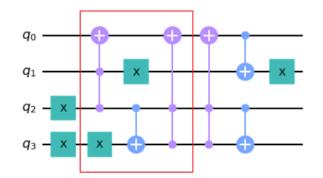

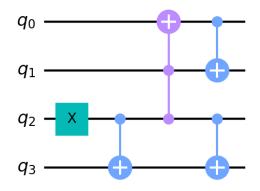

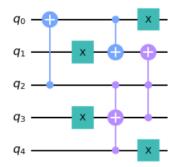

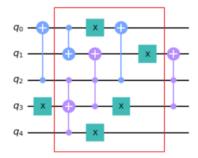

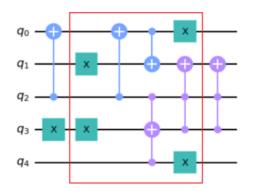

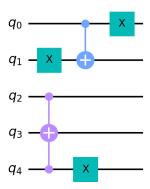

### Figure Page Matrix representations of layers 1, 2, and 3.....72 Circuit containing three-layer commuting composition Modified three-qubit circuit after elimination of

| Figure | Page                                                                          |

|--------|-------------------------------------------------------------------------------|

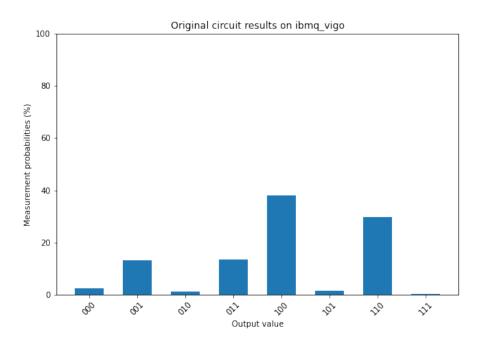

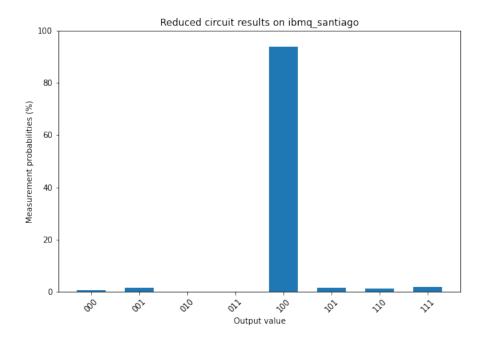

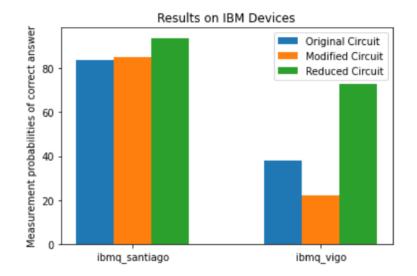

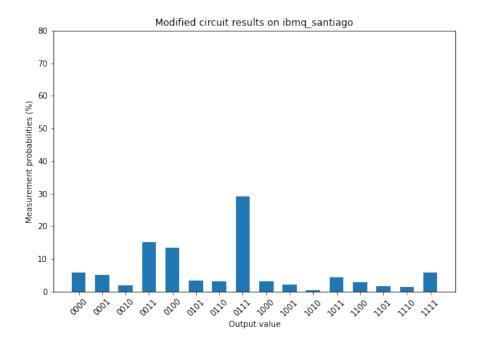

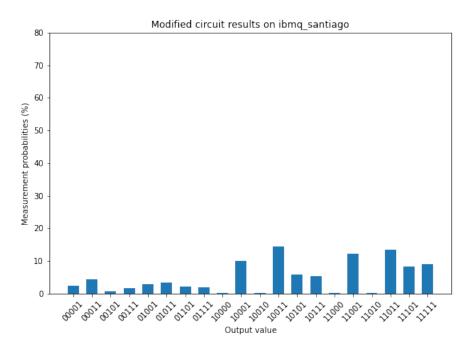

| 46     | Three-qubit original circuit results - ibmq_santaigo81                        |

| 47     | Three-qubit modified circuit results - ibmq_santaigo                          |

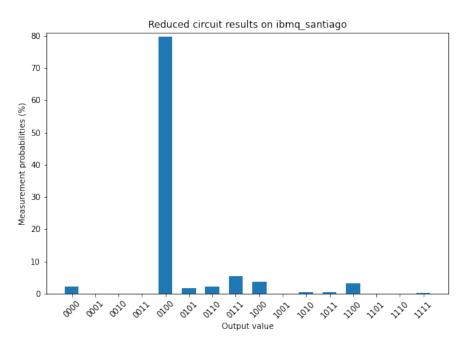

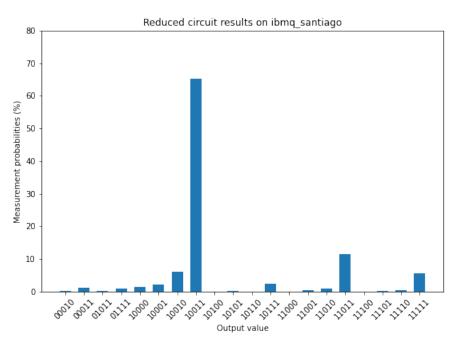

| 48     | Three-qubit reduced circuit results - ibmq_santaigo                           |

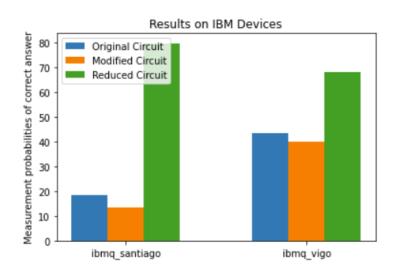

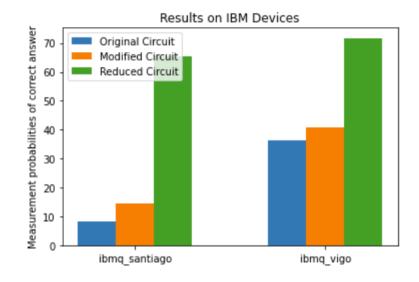

| 49     | Measurement results on ibmq_vigo and ibmq_santiago83                          |

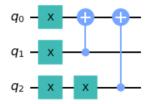

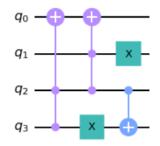

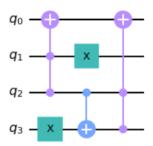

| 50     | Equivalent four-qubit circuits                                                |

| 51     | Four-qubit circuit containing three-layer commuting<br>composition subcircuit |

| 52     | Modified four-qubit circuit                                                   |

| 53     | Modified four-qubit circuit after undergoing template<br>optimization pass    |

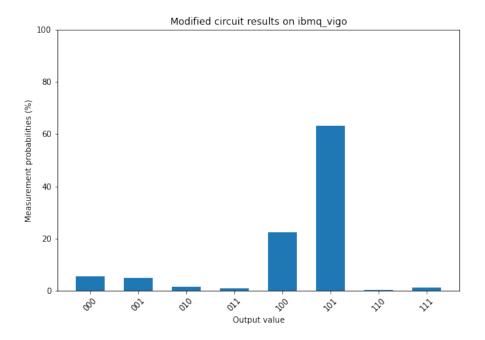

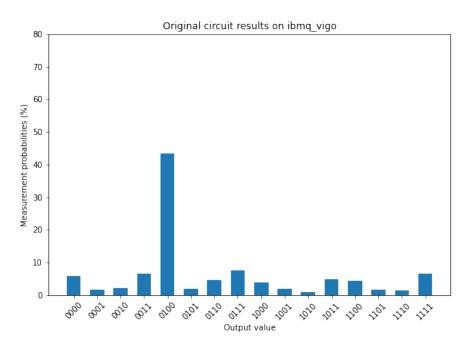

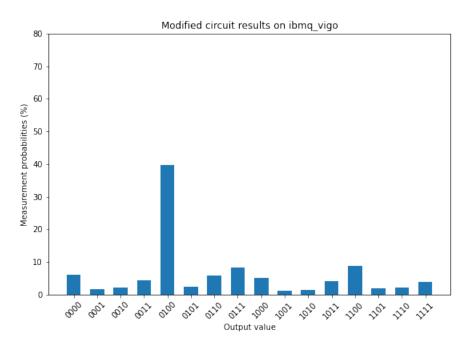

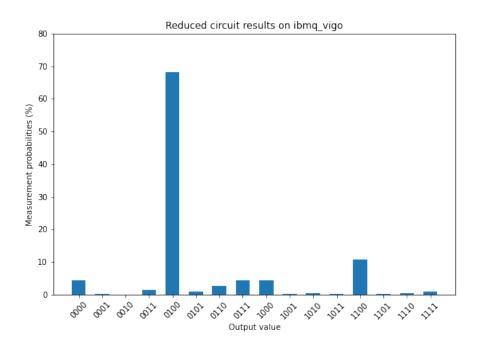

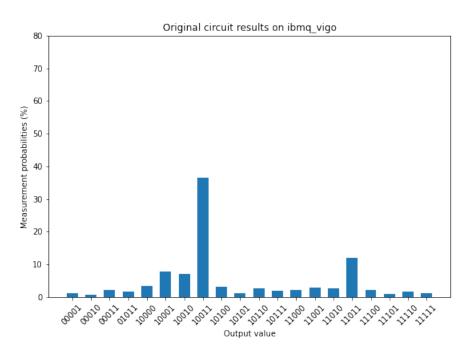

| 54     | Four-qubit original circuit results - ibmq_vigo87                             |

| 55     | Four-qubit modified circuit results - ibmq_vigo88                             |

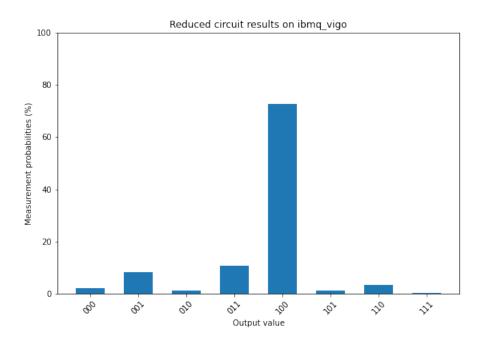

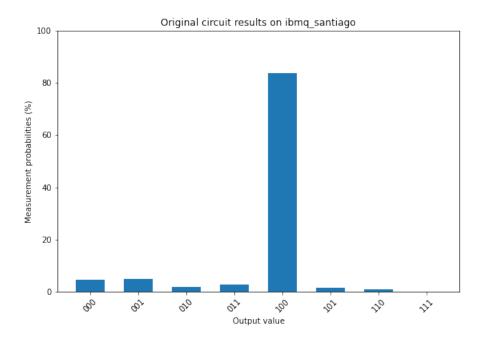

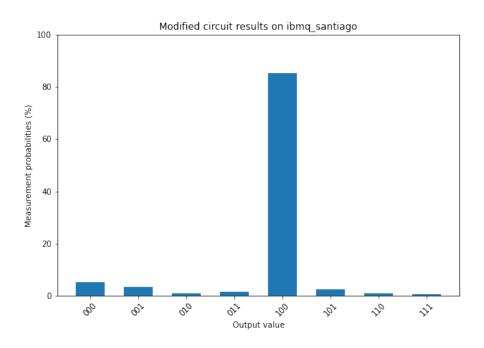

| 56     | Four-qubit reduced circuit results - ibmq_vigo88                              |

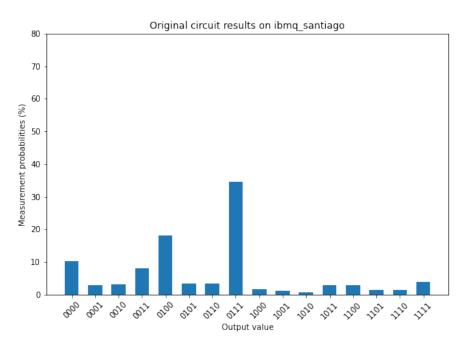

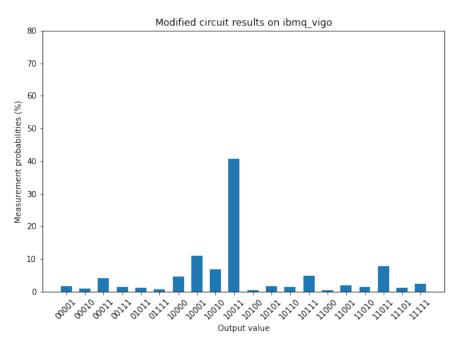

| 57     | Four-qubit original circuit results - ibmq_santaigo                           |

| 58     | Four-qubit modified circuit results - ibmq_santaigo                           |

| 59     | Four-qubit reduced circuit results - ibmq_santaigo90                          |

| 60     | Four-qubit circuit measurement results                                        |

| 61     | Equivalent five-qubit circuits                                                |

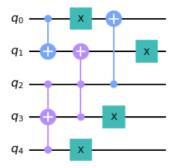

| 62     | Five qubit circuit containing three layer commuting<br>composition subcircuit |

| 63     | Modified five-qubit circuit                                                   |

| 64     | Modified five-qubit circuit after template optimization<br>pass               |

| 65     | Five-qubit original circuit results - ibmq_vigo95                             |

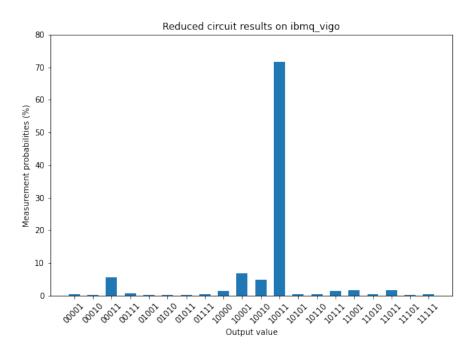

| 66     | Five-qubit modified circuit results - ibmq_vigo96                             |

| 67     | Five-qubit reduced circuit results - ibmq_vigo96                              |

| Figure | Page                                                                     |

|--------|--------------------------------------------------------------------------|

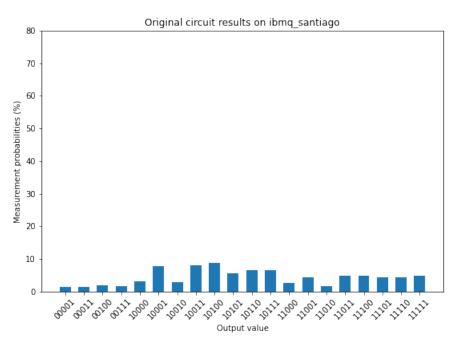

| 68     | Five-qubit original circuit results - ibmq_santaigo97                    |

| 69     | Five-qubit modified circuit results - ibmq_santaigo97                    |

| 70     | Five-qubit reduced circuit results - ibmq_santaigo                       |

| 71     | Five-qubit circuit measurement results on ibmq_vigo<br>and ibmq_santiago |

| 72     | Three-qubit three-layer NCT commuting compositions<br>in reduced form    |

| 73     | X, Y, and Z gate matrices109                                             |

| 74     | X and Y gates do not commute                                             |

| 75     | Y and Z gates do not commute109                                          |

| 76     | XYZ three-layer commuting composition                                    |

# List of Tables

| Table | Ι                                                       | Page  |

|-------|---------------------------------------------------------|-------|

| 1     | Original three-qubit circuit costs post-transpilation   | . 77  |

| 2     | Modified three-qubit circuit costs post-transpilation   | . 77  |

| 3     | Original four-qubit circuit costs post-transpilation    | . 85  |

| 4     | Modified four-qubit circuit costs post-transpilation    | . 85  |

| 5     | Original five-qubit circuit costs post-transpilation    | . 93  |

| 6     | Modified five-qubit circuit costs post-transpilation    | . 93  |

| 7     | Level three optimization results for five-qubit circuit | . 94  |

| 8     | Non-reducible three-layer NCT commuting compositions    | 101   |

| 9     | Number and types of gates in three-qubit circuits       | 103   |

| 10    | Number and types of gates in four-qubit circuits        | 103   |

| 11    | Number and types of gates in five-qubit circuits        | . 103 |

## COMMUTING COMPOSITIONS FOR QUANTUM CIRCUIT REDUCTION

## I. Introduction

### 1.1 Motivation

The United States is in a great power competition with near-peer adversaries [38]. Establishing a strategic edge in this competition is crucial to national defense. A key component to reaching that state is technological superiority. As quoted in the U.S. Air Force's Science and Technology Strategy, former Secretary of the Air Force Heather Wilson said, "The advantage will go to those who create the best technologies and who integrate and field them in creative operational ways that provide military advantage" [63]. Leading the race to develop and utilize game-changing technologies is vital to securing a military and economic advantage over adversarial nations.

Quantum computing is one of the developing technologies that will contribute to this competitive edge. The United States has recognized it as so with the enactment of the National Quantum Initiative (NQI) Act in December 2018 [54]. This Act creates a coordinated federal approach to quantum development in order to ensure U.S. leadership in quantum sciences for the nation's security and economic prosperity [47].

In addition to the United States, China and Russia have recognized quantum sciences as a technology leading to a strategic edge. China is building a national quantum science research center, leads the world in number of quantum communication and cryptography patents, and is investing generous funding towards quantum development [21]. Russia, while lagging behind in the early years of quantum research, has joined the race by investing \$790 million for quantum research and development [20, 57]. The active pursuit by near-peer adversaries of quantum development increases the urgency for the United States to develop a quantum computer capable of solving real-world problems and using it to strengthen military capabilities.

The foreseen advantage of quantum computers is due to the novel method in which they processes data. Rather than simply speeding up classical computation techniques, it fundamentally alters the manner in which information is processed by harnessing properties of quantum mechanics [45]. As a result, some problems that are classically infeasible to compute have known quantum solutions. This promises huge implications to fields such as data security and materials engineering.

One of the first contributions heralding the power of quantum computing is the algorithm created by Peter Shor in 1999 that efficiently solves the problem of factoring large prime numbers, which is believed to be classically intractable [59]. The difficulty of factoring such numbers is the foundation of the widely-used RSA encryption algorithm. This algorithm is used for securing data in many applications, ranging from bank transactions to military communications. Once a quantum computer exists that is capable of running non-trivial instances of Shor's algorithm, this prominent encryption algorithm will no longer be secure.

Another example of quantum computing potential is its foreseen capability to simulate atomic-level molecular chemistry [19]. Classical computers struggle to precisely simulate molecular behavior of anything larger than a few atoms due to computational constraints [45]. The ability to simulate the structure of complex molecules will enable a more robust understanding of chemical interactions [54]. This could be applied to a range of defense-oriented material engineering problems to create stronger equipment or weapon systems, for example.

While known quantum algorithms such as Shor's exist, hardware capable of run-

ning such algorithms is still being developed. The current state of quantum computers is termed the Noisy Intermediate Scale Quantum Computing (NISQ) era. This refers to quantum computers that have low qubit counts, short coherence times, and high error rates [6]. This is a promising step towards developing useful quantum computers, but it is not enough to achieve the anticipated uses of quantum computing technologies. In order to do so, the physical quantum devices must be improved. While this hardware is being developed, however, there is still much software-oriented research that can be done to improve the state of existing technology and accelerate the advent of quantum computers useful for solving real problems. The research presented in this work contributes to that endeavor by presenting a new way to decrease circuit cost, thus making programs execute more efficiently and yield better results in the current noisy environment.

#### 1.2 Problem Background

The initiative to improve the state of quantum computing spans a wide berth of scientific fields and research areas. Among others, physicists, mathematicians, and computer scientists are working to investigate physical qubit technologies, develop quantum algorithms, and improve computations via quantum error correction codes. The focus of this research—reversible and quantum circuit optimization—is another such field dedicated to the advancement of quantum computing.

The goal of circuit optimization is to minimize the costs associated with circuit execution. This is an objective of both classical and quantum computing—the more efficiently a circuit runs the better. However, the low coherence times and high noise present in current quantum computers add to the importance of streamlining the execution process. Coherence time relates to the length of time a qubit can be expected to remain in an excited state, which is key to harnessing the potential of quantum computers [24]. The longer a circuit takes to execute, the more likely a qubit is to decohere, rendering the computation useless. Coherence times are low in current devices due to noise, or disruption from interaction with the environment, that disturbs the fragile qubit state. Every gate operation in a circuit induces additional noise; therefore, fewer gates will lead to not only faster execution time, but also less error.

One of the methods designed to reduce the cost of a circuit is template matching. This technique searches a circuit for a subcircuit matching a template of gates, then replaces the subcircuit with an optimized version. An underlying challenge in this approach is pattern matching, or finding a sequence of gates that matches a given template. A significant difficulty of this problem lies in the fact that some, but not all, gates can commute in a quantum circuit. This means that there may exist alternate orderings of gates that realize the same function, and a template may be found in the rearranged order of gates but not the original.

This leads to the main premise of this research: to identify equivalent alternative orderings of gates so that pattern matching algorithms may discover more template matches and corresponding simplifications, leading to greater reductions in circuit costs.

#### **1.3 Quantum Circuit Commuting Compositions**

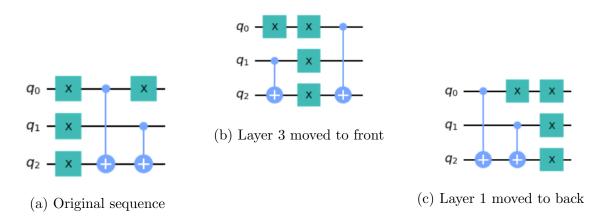

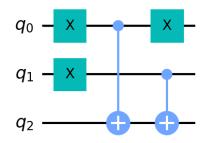

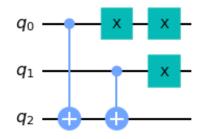

Commutations of quantum gates within a circuit can result in multiple gate sequences realizing the same function. Alternative orderings could yield gate sequences that match templates with known reductions. Previous researchers of quantum circuit simplification, such as Rahman, et al. and Iten, et al., account for pairwise commutation of gates in their algorithms [53, 28]. The latter of these works presents the idea of considering commutations of more than two gates. It states that "in general, it could happen that in a circuit  $C = (C_1, C_2, C_3)$ , no gates commute pairwise, but the unitary corresponding to  $(C_1, C_2)$  could commute with the unitary corresponding to  $C_3$ . Hence, one could bring the circuit C into the form  $(C_3, C_1, C_2)$ , which could help matching in principle" [28].

The present work generalizes and formalizes that postulate with the proposal of the commuting composition property.

A commuting composition is defined as a sequence of  $n \ge 2$  elements such that the product (i.e. composition) of the first k elements (0 < k < n) commutes with the product (i.e. composition) of the remaining (n - k) elements.

An **n-layer commuting composition** is a commuting composition of n elements where no subsequences of (n-1) or fewer elements create a commuting composition. In other words, n is the minimal number of elements in this sequence required for a commutation to exist.

In regards to quantum circuits, the elements can be gates or layers (where a layer can contain multiple concurrent gates). The composition of elements corresponds to the product of the unitary matrices corresponding to each element. The identity gate is included as an element: if k = 1 or (n - k) = 1, the single layer can be viewed as a composition in the sense that it is equivalent to itself composed with the identity. More detailed explanations of these concepts are given in Sections 2.1.2 and 2.1.3.

### 1.4 Research Objectives

This goal of this research is to answer the following research question and test the associated hypotheses:

#### **Research Question:**

How can commuting compositions of layers within a quantum circuit be used to make circuit transpilation more effective?

#### Hypotheses:

- 1. Three-element commuting compositions for circuits composed of NOT, CNOT and Toffoli gates exist.

- 2. Rearrangements of quantum gates in a circuit can yield reductions not otherwise captured by state of the art optimization tools.

- 3. Consideration of commuting layers will yield more three-element commuting compositions than accounting for gates alone.

The idea the research question addresses is whether alternative orderings of quantum gates realizing the same function as the original circuit could result in improved program execution after undergoing transpilation techniques. It has already been shown that accounting for pairwise commutation of gates within template matching algorithms can yield better results than searching the original gate specification alone [53, 28]. Pairwise commutation, however, is a small subset of the greater problem that the research question poses. This work further investigates the topic by expanding the search from two to three elements and examining commutations of groupings of gates rather than commutations of single gates. The hypotheses are the propositions tested in support of this investigation. They are designed to prove whether such commuting circuits exist, whether they can improve current reduction techniques, and whether it is beneficial to consider commutations of layers of gates.

### 1.5 Scope

#### 1.5.1 Three Layers

This work searches for and analyzes commuting compositions of three layers. This extends previous research in two respects. First, previous work considered only single gates per layer, not the more general layers considered here. Second, it considered only sequences of two gates, not three.

#### 1.5.2 Three to Five Qubits

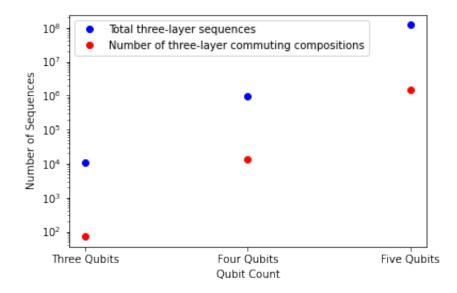

This work analyzes circuits composed of three to five qubits. It begins with circuits of three qubits because that is the minimum required to allow all gates from the NOT, CNOT, and Toffoli gate set to be in the circuit. It ends with five qubits because this number allows for an initial exploration of three-layer commuting compositions that will help inform whether it is worthwhile to search for commuting compositions in circuits containing more than five qubits. The O(n!) complexity of the problem (See Appendix A) makes it computationally expensive to search for high-qubit count circuits. This five-qubit analysis lays the groundwork to determine whether to expend the resources to consider greater numbers.

#### **1.6 Document Overview**

The remainder of this document is structured as follows. Chapter II discusses background information and previous work related to quantum circuit reduction and template optimization techniques. Chapter III describes the methodology employed to identify and analyze three layer NCT commuting compositions. Chapter IV presents the results of the investigation of the commuting sequences. Finally, Chapter V concludes the document by summarizing the contributions of this research and proposes future work.

### II. Background and Literature Review

This chapter presents an overview of concepts related to quantum circuit optimization via template matching. It lays the groundwork for understanding the commuting composition problem and its role in quantum circuit reduction. Section 2.1 reviews fundamental concepts of quantum computing; Section 2.2 discusses the process of realizing a given function as a quantum circuit; Section 2.3 describes cost metrics used to analyze the efficiency of a circuit; Section 2.4 presents the template matching optimization technique; and 2.5 describes Qiskit, which is the primary toolset used in this research.

### 2.1 Quantum Computing Preliminaries

Quantum computing is a computational paradigm using quantum mechanics to process information. This section describes key elements of quantum computation and how they differ from classical computation. It begins with explaining the quantum bit (qubit) in Section 2.1.1, proceeds with how qubits are manipulated via gates in Section 2.1.2, and explains how gates are combined to make a circuit in Section 2.1.3. Finally, this section ends by describing ways in which circuits are specified in Section 2.1.4.

#### 2.1.1 Qubits

The basic unit of information for quantum computing is the qubit. Unlike a classical bit which can exist in only the 0 or 1 state, a qubit can exist in a linear combination of 0 and 1. The state of a qubit is represented as  $|\psi\rangle = \alpha |0\rangle + \beta |1\rangle$ , with  $\alpha, \beta \in \mathbb{C}$  and  $|\alpha|^2 + |\beta|^2 = 1$ . This state can also be represented as a vector,  $\binom{\alpha}{\beta}$ . When a qubit is in a linear combination in which both  $\alpha$  and  $\beta$  are nonzero,

it is in a state of *superposition*. When a qubit is observed, or measured, it collapses from the superposition to either 0 or 1 [45]. The state corresponding to 0 is written as  $|0\rangle = 1 |0\rangle + 0 |1\rangle = \begin{pmatrix} 1 \\ 0 \end{pmatrix}$  and the state corresponding to 1 is written as  $|1\rangle = 0 |0\rangle + 1 |1\rangle = \begin{pmatrix} 0 \\ 1 \end{pmatrix}$ .

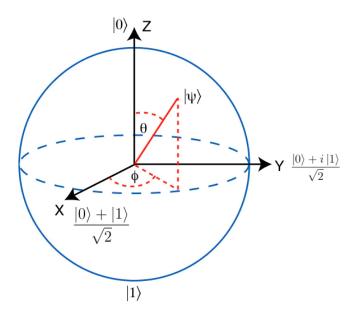

The state space of a quantum system is a Hilbert space over the complex numbers [17]. Specifically, a quantum system's state is described by a unit vector within this complex space [45]. For a single qubit,  $|\psi\rangle = \alpha |0\rangle + \beta |1\rangle$ , the amplitudes  $\alpha$  and  $\beta$  span a 2-dimensional Hilbert space that comprises every state in which the single qubit quantum system can exist. This 2-dimensional state space is often represented by the Bloch sphere, as shown in Figure 1.

Figure 1: Bloch sphere. Adapted from QuTech [48].

For a system with *n* qubits, the state space corresponds to a 2<sup>*n*</sup>-dimensional Hilbert space, given by the tensor product of the individual qubit state vectors [27]. For example, a quantum system with two qubits  $|\psi_1\rangle = \alpha_1 |0\rangle + \beta_1 |1\rangle$  and  $|\psi_2\rangle = \alpha_2 |0\rangle + \beta_2 |1\rangle$  spans a 4-dimensional Hilbert space, given by

$$|\psi\rangle = |\psi_1\rangle \otimes |\psi_2\rangle = \begin{pmatrix} \alpha_1 \\ \beta_1 \end{pmatrix} \otimes \begin{pmatrix} \alpha_2 \\ \beta_2 \end{pmatrix} = \begin{pmatrix} \alpha_1\alpha_2 \\ \alpha_1\beta_2 \\ \beta_1\alpha_2 \\ \beta_1\beta_2 \end{pmatrix}$$

(1)

Qubits are currently realized by a variety of physical technologies, to include ion traps, superconductors, linear optic tools, diamonds, and quantum dots [55]. It is an ongoing area of research to determine which existing or new technologies will emerge as the primary materials used, as each have advantages and disadvantages. For example, ion trap-based systems have seen higher coherence times, lower error rates, and more connectivity between qubits, but have lower qubit counts due to the difficulty of controlling them and their high susceptibility to noise [33, 43]. Superconducting quantum computers, which use the transmon qubit, have higher qubit counts and are easier to control, but have lower coherence times, experience higher error, and have fewer adjacent qubits [33, 34, 43]. The concept of adjacent qubits is described in Section 2.2.3.

#### 2.1.2 Quantum Gates

To perform a computation on a qubit, a quantum gate is applied to it. This is a physical operation, such as a microwave pulse, that is performed on a qubit to alter its state. All quantum gates can be represented as unitary matrices [9]. A unitary matrix is a matrix U such that  $UU^{\dagger} = I$ , where  $U^{\dagger}$  is the adjoint of U (complex conjugate of U transposed) [45]. Since  $UU^{\dagger} = I$ , the inverse of U ( $U^{\dagger}$ ) exists and thus every quantum gate is reversible. A gate operation on a single qubit can be visualized by a rotation about the origin on the bloch sphere. For example, Equation 2 shows the matrix corresponding to the Pauli X gate, also known as the NOT gate [25]. The X gate functions similarly to the classical NOT gate: as the classical NOT gate inverts a bit, the quantum NOT gate inverts a qubit. Visualized on the Bloch sphere, this gate rotates the state vector by 180° around the x-axis.

$$X = \left(\begin{array}{cc} 0 & 1\\ 1 & 0 \end{array}\right) \tag{2}$$

Thus, the X gate inverts a qubit  $|\psi\rangle = \alpha |0\rangle + \beta |1\rangle$  by switching the positions of  $\alpha$  and  $\beta$  to give  $|\psi\rangle = \beta |0\rangle + \alpha |1\rangle$ . This can be verified by calculating the product of the the X gate and the qubit state, as shown in Equation 3.

$$\left(\begin{array}{cc}

0 & 1\\

1 & 0

\end{array}\right)

\left(\begin{array}{c}

\alpha\\

\beta

\end{array}\right) =

\left(\begin{array}{c}

\beta\\

\alpha

\end{array}\right)$$

(3)

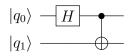

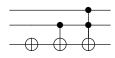

Most quantum computing devices support gates that operate on one or two qubits [6]. In the two-qubit case, one of the qubits is specified as the control qubit and the other is specified as the target qubit. When the control qubit is in the  $|1\rangle$ state, the operation is applied to the target qubit. For example, Figure 2 shows the two-qubit CNOT gate, which applies the X gate to the target qubit  $(|q_1\rangle)$  when the control qubit  $(|q_0\rangle)$  is  $|1\rangle$ . The matrix representation of this gate is in Equation 4.

Figure 2: CNOT gate

$$CNOT = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \end{pmatrix}$$

(4)

#### 2.1.3 Quantum Circuits

A quantum circuit is a sequence of operators applied to qubits in a quantum system. The circuit corresponds to a unitary matrix that is the product of the operator for each layer in the circuit multiplied in reverse order [27]. As an example, consider the circuit generating a Bell State as shown in Figure 3. This circuit entangles two qubits, which means that their states cannot be isolated from one another—the state of the quantum system cannot be written as the product of two individual qubit states [45]. To compute the final circuit unitary, the matrices corresponding to the individual layers must first be computed. This is done by calculating the tensor product of the matrices corresponding to the gates operating on the individual qubits in the system for each layer.

Figure 3: Bell State circuit

In the Bell State example, let  $L_1$  refer to the layer in which the Hadamard gate is applied to  $|q_0\rangle$ . In this layer, no state-changing operations are applied to  $|q_1\rangle$ , so the identity matrix can be used to represent the gate for that qubit. The unitary matrix corresponding to the operator for the entire layer is therefore computed as shown in Equation 5.

$$L_{1} = H \otimes I = \frac{1}{\sqrt{2}} \begin{pmatrix} 1 & 1 \\ 1 & -1 \end{pmatrix} \otimes \begin{pmatrix} 1 & 0 \\ 0 & 1 \end{pmatrix} = \frac{1}{\sqrt{2}} \begin{pmatrix} 1 & 0 & 1 & 0 \\ 0 & 1 & 0 & 1 \\ 1 & 0 & -1 & 0 \\ 0 & 1 & 0 & -1 \end{pmatrix}$$

(5)

The matrix representation of the second layer of operations, which in this case will be denoted  $L_2$ , is the matrix for the CNOT operation, as shown in Equation 6.

$$L_{2} = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \end{pmatrix}$$

(6)

The unitary corresponding to the entire circuit can then be calculated by taking the product of  $L_2$  and  $L_1$ . As previously mentioned, to calculate the circuit unitary, the order of operands is multiplied in reverse order relative to how it appears in the circuit diagram. A state analysis of the quantum system after the operand is applied for each layer shows the reason for this. The original state is  $|\psi_0\rangle$ . The state of the system after application of the first layer operand is  $|\psi_1\rangle = L_1 |\psi_0\rangle$ . The final state of the system after application of the second layer operand is  $|\psi_2\rangle = L_2 |\psi_1\rangle = L_2 L_1 |\psi_0\rangle$ . Therefore, to calculate the state of the final system, the operator for the entire circuit can be applied to the original state. In this case, that operator is  $L_2 \cdot L_1$ . The matrix analysis for this is shown in Equation 7.

$$L_{2}L_{1} = \frac{1}{\sqrt{2}} \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \end{pmatrix} \begin{pmatrix} 1 & 0 & 1 & 0 \\ 0 & 1 & 0 & 1 \\ 1 & 0 & -1 & 0 \\ 0 & 1 & 0 & -1 \end{pmatrix} = \frac{1}{\sqrt{2}} \begin{pmatrix} 1 & 0 & 1 & 0 \\ 0 & 1 & 0 & 1 \\ 0 & 1 & 0 & -1 \\ 1 & 0 & -1 & 0 \end{pmatrix}$$

(7)

Using the operator for the circuit, the resulting state of the quantum system can be computed by multiplying the circuit operator and the quantum system's state vector (by which it is meant to left-multiply the state vector by the matrix of the circuit operator). For example, Equation 8 shows the result of a quantum system in the state  $|00\rangle = \begin{pmatrix} 1\\0\\0\\0 \end{pmatrix}$  with the Bell State circuit applied to it is  $\frac{1}{\sqrt{2}} \begin{pmatrix} 1\\0\\0\\1 \end{pmatrix} = \frac{1}{\sqrt{2}} \left[ \begin{pmatrix} 1\\0\\0\\0 \end{pmatrix} + \begin{pmatrix} 0\\0\\1\\0 \end{pmatrix} \right] = \frac{1}{\sqrt{2}} \left( |00\rangle + |11\rangle \right).$

$$U|00\rangle = L_2 L_1 |00\rangle = \frac{1}{\sqrt{2}} \begin{pmatrix} 1 & 0 & 1 & 0 \\ 0 & 1 & 0 & 1 \\ 0 & 1 & 0 & -1 \\ 1 & 0 & -1 & 0 \end{pmatrix} \begin{pmatrix} 1 \\ 0 \\ 0 \\ 0 \\ 0 \end{pmatrix} = \frac{1}{\sqrt{2}} \begin{pmatrix} 1 \\ 0 \\ 0 \\ 1 \end{pmatrix}$$

(8)

This means that, when measured, the system will collapse to either  $|00\rangle$  or  $|11\rangle$  with a 50% probability for each possibility.

#### 2.1.4 Circuit Representations

Quantum circuits can be specified in multiple ways. Three of the most common methods are circuit diagrams, instruction lists, and directed acyclic graphs (DAGs).

A quantum circuit diagram is a figure showing "wires" that represent the logical

qubits in the quantum system. Each gate that is applied to a single qubit is represented with a symbol, commonly a boxed letter or a crossed circle. Gates that operate on more than one qubit are shown with a dot on the control qubit(s) connected to a gate symbol on the target qubit. The representation of the Bell State circuit in Figure 3 is an example of defining a circuit via a diagram.

In addition to diagrams, circuits can be described in text by defining a list of instructions operating on qubits, called a netlist [44]. This is similar to writing a classical program using assembly language. Netlists can be created in multiple formats. Example languages are OpenQASM, Qiskit, and REAL [14, 25, 60]. Circuits represented in these languages are text files that describe the gates in the circuit and the qubit registers on which the gates act. Figure 4 shows an OpenQASM instruction list format specifying a Bell State circuit. OpenQASM is defined in more detail in Section 2.5.2.

```

1

OPENQASM 2.0;

2

include "gelib1.inc";

3

4

qreg q[2];

5

creg c[2];

6

7

h q[0];

8

cx q[0],q[1];

9

measure q[0] \rightarrow c[0];

measure q[1] \rightarrow c[1];

10

```

Figure 4: OpenQASM code for Bell State circuit

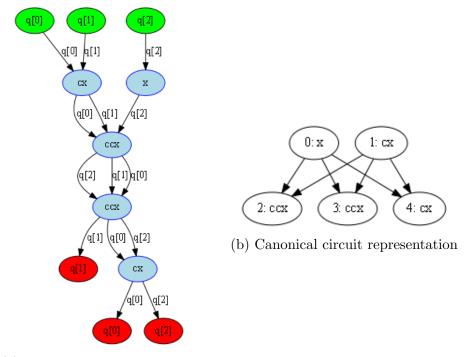

In addition to diagrams and netlists, quantum circuits can be represented as directed acyclic graphs (DAG)s. In this representation, the nodes of the graph correspond to gates, quantum registers, and classical registers, and the edges correspond to logical qubits or classical bits that are the input or output for each of the nodes [25, 44]. As an example, a DAG representation of the Bell State circuit is shown in Figure 5.

Figure 5: Bell State circuit DAG

Circuit diagrams, netlists, and most DAGs show a specific sequence of gates in the circuit, but that sequence is not necessarily the only one that will compute to the same overall matrix operator. For any two gates A and B, if AB = BA, the gates commute and can switch execution order in the circuit without altering the function. In other words, the output after the execution of both gates does not change depending on which executes first.

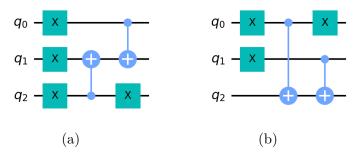

One example of this is the moving rule, formally defined as the property that "two adjacent gates  $g_1$  and  $g_2$  with controls  $c_1$  and  $c_2$ , and targets  $t_1$  and  $t_2$  can be interchanged if  $c_1 \cap t_2 = \emptyset$  and  $c_2 \cap t_1 = \emptyset$ " [53]. The two gates depicted in Figure 6a show an example. In this case, each gate's control lines are disjoint from the other gate's target line. This means the gates can be interchanged, yielding the equivalent circuit in Figure 6b.

In contrast to this example is the circuit given in Figure 7, in which the two gates

Figure 6: Gate commutation via moving rule

share a common line between the target of the first gate and the control of the second gate. In this case, the gates cannot commute and must be executed in the order shown in order to realize the desired function.

Figure 7: Non-commuting gates

The moving rule shows one instance of when two gates can commute within a circuit. It is not sufficient, however, to account for all gate commutations. In particular, it does not generalize to more than two gates or to gates that are not directly adjacent. The research conducted in this work considers problems that are not captured by the moving rule.

Rahman et al. presented a type of DAG that incorporates the moving rule, known as the *canonical form* or *DependencyDAG* [25, 28, 53]. Unlike the DAG shown in Figure 5, a DependencyDAG only has an edge between gate nodes if one of those nodes depends on the other.

The difference between the previously-mentioned DAG and the DependencyDAG is shown in Figure 8. Both graphs represent the same circuit, but unlike Figure 8a, Figure 8b shows the existence of a dependency between gates by an unlabelled edge

(a) DAG circuit representation

Figure 8: DAG circuit representations

between nodes. Where there is not an edge, no dependency exists. In contrast, the edges in Figure 8a correspond to the logical qubits upon which the gates are operating. Those edges give no indication of whether the gates can commute. For example, the two CCX gates in this circuit can commute. Figure 8a has a directed edge between the first and second of these gates, corresponding to the gate order in which the circuit was originally specified. It does not indicate whether this order is required for the circuit to realize the desired function. Figure 8b does not have an edge between these gates (nodes 2 and 3). This indicates that they are independent of one another and that the order in which they execute will not impact the functionality of the circuit.

While the canonical form shows pairwise commutations that allow for some gate reorderings (two gates can commute if they are not dependent on one another), it does not depict all possible gate sequences that can realize the original function. It considers dependency between neighboring gates, but there could exist a case in which pairs of gates could move together in the circuit without compromising the dependency between them or changing the circuit's function. This would yield an alternative gate sequence not captured by the canonical form.

#### 2.2 Circuit Synthesis

The process of realizing an algorithm or function on a physical quantum computer can be decomposed into three steps: synthesizing the function into a reversible circuit (Section 2.2.1), mapping gates from the reversible to quantum level (Section 2.2.2), and modifying the quantum-level circuit to account for physical constraints (Section 2.2.3). Understanding these abstraction levels is important for circuit optimization as simplification can be conducted during any of the steps in this process. Depending on the method used, it may be more effective to run the technique at a higher or lower abstraction level. Furthermore, understanding the decomposition of a high-level reversible gate into quantum gates lends insight into which gates to target for reduction in order to achieve the best performance when the circuit is run on quantum hardware.

#### 2.2.1 Reversible Circuit Synthesis

The first step in implementing a function on a quantum computer is synthesis into a reversible circuit. A reversible circuit is a bijective mapping of inputs to outputs, composed of cascades of reversible gates, and has no fanout or feedback [15]. Unlike a classical gate, a reversible gate must have an equal number of inputs and outputs and a one-to-one mapping between them [56].

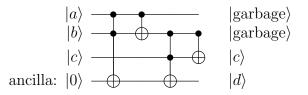

Any function, reversible or irreversible, can be implemented as a reversible circuit [2]. If the function is irreversible, ancilla inputs and garbage outputs are used to embed the function into a reversible circuit. Ancilla lines are added to the original inputs to enable the function, and garbage outputs are lines for which the final output values are not considered in the result [56]. For example, Figure 9 shows a reversible embedding of a one-bit full adder function (a one-bit full adder includes both a carry-in input and a carry-out output) [61]. The one-bit full adder function is

Figure 9: NCT 1-bit adder circuit. Bits a, b, c are added and the result is dc

not inherently reversible, but the addition of the ancilla line and the exclusion of the two garbage lines from the result allows for the reversible embedding.

Although all quantum gates are reversible, not all reversible circuits are composed of quantum gates. Often, abstract reversible gates, which can operate on arbitrarily many inputs, are used. While these gates work well to embed a function into a reversible circuit, they cannot be run directly on a quantum computer, as most quantum devices are only able to implement gates that operate on one or two inputs. There are several universal gate libraries used for reversible circuit synthesis: among the most common are the Mixed-Polarity Multiple-Control Toffoli (MPMCT) gates, Multiple-Control Toffoli (MCT) gates, and NCT gates [2, 5]. These gate sets are listed below from higher to lower levels of abstraction.

• The **MPMCT gate library** is the set containing MPMCT gates. A MPMCT gate is defined as a gate g(C, t) where C is the set of controls lines and t is the target. Each control element is either a positive or negative control. The X operation is performed on the target line if and only if the state of the control line is asserted in accordance with its specification of a positive or negative or neg

Figure 10: MPMCT gate with four control lines

control [1]. An example of a MPMCT gate is shown in Figure 10. In this example, an X operation is performed on the target if control lines  $c_1$  and  $c_3$  are in the  $|0\rangle$  state and control lines  $c_2$  and  $c_4$  are in the  $|1\rangle$  state.

• The MCT gate library is a subset of the MPMCT gate library for which all controls are positive. This means that the control lines are asserted, and the X is performed on the target, if and only if the control lines are in positive states [2]. An example of a MCT gate is shown in Figure 11. In this example,

Figure 11: MCT gate with three control lines

an X operation is performed on the target if  $c_1, c_2$ , and  $c_3$  are in the  $|1\rangle$  state.

• The **NCT gate library** is a subset of the MCT library in which the number of control lines is two or fewer. In other words, it is exactly the set containing the NOT, CNOT, and Toffoli gates [2]. The NOT, CNOT and Toffoli gates are also referred to as the X, CX and CCX gates, respectively. The NCT gates are shown in Figure 12. The matrices corresponding to these gates are shown in Equations 9–11.

Figure 12: The NOT, CNOT, and Toffoli gates

$$X = \begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix}$$

(9)

$$CX = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \end{pmatrix}$$

(10)

$$CCX = \begin{pmatrix} 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 1 & 0 \end{pmatrix}$$

(11)

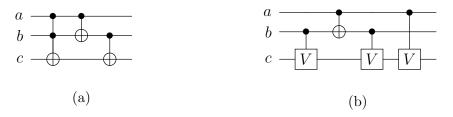

# 2.2.2 Quantum Circuit Mapping

Once a function has been synthesised into a cascade of reversible gates, those gates are decomposed into sequences of quantum gates. The quantum gate decomposition is based on a chosen gate library. Two of the common universal quantum gate libraries are the NCV library and the Clifford+T library [2]. The NCV gate library is composed of the Pauli-X gate, the CNOT gate, the Controlled-V (CV) gate, and the Controlled- $V^{\dagger}$  gate [30]. The V gate is also known as the square-root-of-not gate. The matrix representations for the X and CX gates are shown in Equations 9 and 10 in Section 2.2.1; the remaining gate matrices are shown in Equations 12 and 13.

$$CV = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & \frac{1+i}{2} & \frac{1-i}{2} \\ 0 & 0 & \frac{1-i}{2} & \frac{1+i}{2} \end{pmatrix}$$

(12)

$$CV^{\dagger} = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & \frac{1-i}{2} & \frac{1+i}{2} \\ 0 & 0 & \frac{1+i}{2} & \frac{1-i}{2} \end{pmatrix}$$

(13)

The NCV gate library was used frequently in early work on quantum circuit mapping.

Recently, the Clifford+T gate library has been used more often than the NCV gate library due to its role in fault tolerant computing [46]. In particular, the set of Clifford gates has seen promising results in research on quantum error correction using stabilizer codes [12]. The T gate is added to the Clifford set in order to achieve universality. The Clifford+T gate library is composed of the Clifford gates (X, CNOT, H, S, and S<sup>†</sup>), along with the T and T<sup>†</sup> gates [41]. The matrix representations of these gates (other than the X and CNOT gates shown previously in Equations 9 and 10,

respectively) are shown in Equations 14–18.

$$H = \frac{1}{\sqrt{2}} \begin{pmatrix} 1 & 1\\ 1 & -1 \end{pmatrix} \tag{14}$$

$$S = \begin{pmatrix} 1 & 0 \\ 0 & i \end{pmatrix}$$

(15)

$$S^{\dagger} = \left(\begin{array}{cc} 1 & 0\\ 0 & -\mathbf{i} \end{array}\right) \tag{16}$$

$$T = \begin{pmatrix} 1 & 0\\ 0 & e^{\frac{i\pi}{4}} \end{pmatrix}$$

(17)

$$T^{\dagger} = \begin{pmatrix} 1 & 0 \\ 0 & e^{\frac{-i\pi}{4}} \end{pmatrix} \tag{18}$$

Regardless of the gate set used for mapping, this step produces a logical circuit composed of quantum gates that is at the low-level instruction set required to run on an ideal quantum computer. However, there is one final step before it can be run on an actual device—the logical circuit must be converted into a physically realizable circuit by accommodating for any hardware-imposed constraints.

# 2.2.3 Hardware Constraints

Once an algorithm has been mapped to a logical quantum circuit, the final step is to modify that circuit to account for architecture-specific physical constraints. These are restrictions due to the the construction of the quantum computer rather than the abstract laws of quantum physics.

NISQ-era quantum computers have limited connectivity between qubits. The

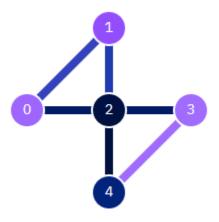

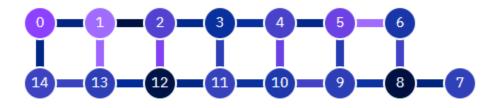

physical connectivity of the qubits on a quantum device is referred to as its topology. A topology diagram shows what connections exist between physical qubits. Qubits corresponds to the nodes and an edge indicates they qubits connected [25]. Two qubits are *adjacent* if they are physically connected, which means two-qubit operations are allowed between them. Examples of topologies for two IBM quantum computers are shown in Figures 13 - 14.

Figure 13: Topology diagram for 5-qubit ibmq\_5\_yorktown

Figure 14: Topology diagram for 15-qubit ibmq\_16\_melbourne

The linear nearest neighbor (LNN) constraint states that a two qubit gate can only be applied to physically adjacent qubits [31]. For example, physical qubits 0 and 2 in Figure 13 can be used in a two-qubit operation, but physical qubits 0 and 3 cannot. In order to achieve adjacency when a pair of physical qubits involved in a two-qubit operation are not in positions allowing it to occur, SWAP operations are applied to interchange the positions of logical qubits on the physical topology. SWAP operations are costly and noisy, so an open field of research is how to minimize the number of SWAP operations required to implement a quantum circuit.

One example of such work is presented by Bataille and Luque, in which they analyze the mathematical properties of the set of circuits generated by SWAP and CNOT gates to find minimization techniques [9]. These are incorporated into an algorithm that optimizes gate selection for the circuit, which works so long as the qubit topology is a complete graph. Another example is by Rahman et al., which presents a method to account for the nearest neighbor constraint during the reversible circuit synthesis step as opposed to a post-processing step [52].

A problem related to minimizing the number of SWAP operations is mapping logical qubits to physical qubits. If the logical qubits are mapped to physical qubits such that the two physical qubits involved in a two qubit operation are already adjacent or able to be made adjacent with a relatively small number of SWAPs, the circuit execution will be more efficient and output better results.

An example of this type of work can be seen in the research presented by Murali et al., which inputs an optimization problem formulated from hardware constraints and circuit characteristics to the Z3 satisfiability modulo theory (SMT) solver to output a logical to physical qubit mapping that minimizes execution time by reducing number of inserted SWAPs [42]. Another example of work on qubit mapping is presented by De Almeida et al., which focuses specifically on CNOT restrictions present in IBM quantum hardware. In this research, the authors find optimal qubit permutations adhering to IBM CNOT gate restrictions by formulating it as an integer linear programming problem that accounts for different mapping costs [16].

## 2.2.4 Previous Work on Circuit Decomposition

This Section describes previous research that has been done on reversible circuit synthesis. It focuses on converting high-level reversible circuits into quantum circuits. Section 2.2.4.1 describes decomposing MCT gates into NCT gates, and Section 2.2.4.2 describes methods for mapping reversible circuits into equivalent quantum-level realizations.

## 2.2.4.1 Reversible Level

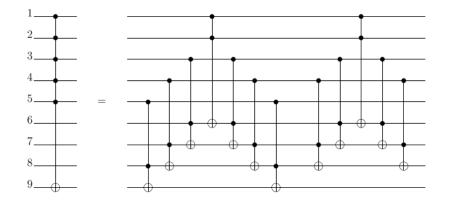

One of the major works used for decomposition of a reversible circuit into a quantum circuit is *Elementary gates for quantum computation*, in which Barenco et al. propose techniques for decomposing MCT gates with large numbers of control lines into NCT gates (MCT gates with two or fewer control lines) [8]. This is commonly referred to as Barenco decomposition or basic Toffoli gate decomposition [58]. An example of this decomposition is shown in Figure 15. This decomposition algorithm is

Figure 15: Barenco decomposition example. Reproduced from Barenco et al. [8].

often used as a starting point for researchers mapping reversible circuits to quantum circuits. Barenco decomposition is used to convert high-level reversible circuits to circuits containing only NCT gates. From there, the NCT gates are decomposed into a quantum-level gate set. It is also important to note that while Barenco decomposition provides an effective method for breaking large MCT gates into smaller ones, it is not the only or necessarily the most efficient way. An ongoing area of research is finding other methods for large MCT gate decomposition.

#### 2.2.4.2 Reversible to Quantum Circuit Mapping

Many methods are employed for synthesis and optimization of reversible circuits into cascades of quantum gates. This present research focuses on template matching, which is described in greater detail in Section 2.4. This section presents alternative approaches so that the reader has a broader understanding of the field and how template matching compares to other solutions.

Much research towards mapping a reversible circuit to a Clifford+T based quantum circuit first maps the reversible circuit to an NCV circuit before transforming the NCV circuit to a Clifford+T circuit. One example is by Miller et al., in which the authors map NCV circuits to Clifford+T circuits by replacing all V and V<sup>†</sup> gates with Clifford+T equivalents, then rearranging the placement of the T gates to enable possible gate cancellations, and finally optimizing the subcircuits between the T gates by looking for possible CNOT reductions [41]. For each step of this process the authors provide the algorithm for how they accomplished it.

Another example is by Abdessaied et al., which presents an approach to map MPMCT Toffoli gates (as opposed to starting with only MCT or NCT gates) into Clifford+T based circuits [1]. The method presented defines four cases to which a gate can belong. It then considers a reversible circuit gate by gate, and for each gate maps it to a Clifford+T gate cascade based on which of the four cases it matches.

An example of a template-based mapping approach is shown in the work by Biswal et al. [11]. In this paper, the authors use a tool called Colorado University Decision Diagram (CUDD) to transform a function into a binary decision diagram (BDD). The resulting BDD graph is traversed node by node, and each node is replaced with the quantum subcircuit from a template library that corresponds to the specific node structure. The node is mapped to a reversible circuit, which is then mapped to a circuit comprised of elementary gates from the NCV library, and finally all gates that are not in the Clifford+T library are exchanged for equivalent sequences of fault tolerant gates. After this, the new circuit is traversed for redundant gates that can be eliminated and for patterns in which T gates can be restructured to cancel each other (reducing the T-count) or be executed in parallel (reducing the T-depth).

Another technique used to map reversible circuits to quantum circuits is exclusive sum of products (ESOP). An example of this method for the design of Clifford+T based circuits is by Meuli et al. [39]. This paper first uses a k-input lookup table (k-LUT) mapping technique to map a single large gate into sequences of smaller gates. It then uses ESOP decomposition to map the smaller gates to a Clifford+T network. Following this, they use a post-synthesis optimization method based on graph matching to further reduce the T-count and T-depth.

# 2.3 Logical Circuit Optimization

Circuit optimization is a major area of research within the quantum computing field. This is particularly important in the current NISQ-era because of the low resource availability and high error rates. Circuit simplification is not only a matter of making a program run more efficiently, but of making it capable of executing correctly at all. Current per-qubit and per-gate error rates are high, meaning that more efficient execution translates to lower overall error rates. Furthermore, the circuit optimization problem is complicated by the fact that current and anticipated quantum computers only implement gates between selected pairs of qubits (See Section 2.2.3). Three primary cost metrics considered in evaluating quantum circuits are gate count, circuit depth, and ancilla line count [7]. These are discussed in Sections 2.3.1, 2.3.2, and 2.3.3, respectively.

#### 2.3.1 Gate Count

The number of gates in a circuit is a key component in the overall circuit efficiency. In addition to requiring more processing time, the application of a quantum gate to one or more qubits will result in some error, which contributes to decoherence and can affect the outcome of the computation [18]. Therefore, the lower the gate count, the faster the circuit will run and the higher the likelihood it will produce usable results.

The total number of quantum gates that are in the circuit is known as as the *quantum cost*. Often, variations of total quantum cost are considered based on the difficultly of implementing a certain type of gate or the gate type that is preferred for a specific architecture.

For example, most optimization techniques for circuits composed of gates from the Clifford+T set (discussed in Section 2.2.2) aim to reduce the *T*-count, or number of T and T<sup>†</sup> gates, as the cost of a fault-tolerant implementation of a T gate is significantly higher then the rest of the gates in the set [1, 11, 46]. This has been the emphasis of most Clifford+T based optimization research in the past, although more recently the number of CNOT gates in a Clifford+T circuit is being considered as well.

Reduction of CNOT gates is important because two-qubit gates have higher error rates than single-qubit gates [23]. Additionally, they can be more costly to implement due to the LNN constraint, which requires the physical qubits involved in a two-qubit operation to be adjacent [10]. In order to achieve that requirement, SWAP operations, which exchange the location of two qubits and are composed of three CNOT gates, are repeatedly used to move the control and target qubits until they are adjacent so that the logical operation can be executed [6]. This means that in order to execute one logical CNOT operation, many physical CNOTs may be required.

## 2.3.2 Circuit Depth

*Circuit depth* refers to the number of distinct layers that exist in the circuit. A layer is a set of quantum gates that can be executed concurrently. The more gates that can be executed concurrently, the smaller the total execution time of the circuit [2].

As with gate count, circuit depth has variations that depend on the gate set used for circuit construction. For example, a Clifford+T adaptation of circuit depth is the *T-depth*, or number of layers containing one or more T or T<sup>†</sup> gates [46]. Again, the strong focus on reducing T-depth is due to the high cost of the T-gate implementations. If the T or T<sup>†</sup> gates are in the same layer, processing time is used more efficiently. This is because the slot of time used for the layer will be the length required to execute the T gate. If the other gates that need to be executed in this layer are also T gates, their execution times overlap. If the other gates take less time to execute, the processor is doing nothing on the non-T gate lines while waiting for the T operation to finish. The goal, therefore, is to group the T gates into as few layers as possible to minimize the number of layers with long execution times.

#### 2.3.3 Ancilla Lines

Ancilla lines are extra control or data lines added to a circuit [2]. They are required to embed a non-reversible function into a reversible circuit [56]. Additional ancilla lines may also be necessary in the decomposition process from a reversible circuit to a quantum circuit [62].

There is often a trade off between the number of ancilla lines in a circuit vs the other costs, particularly gate count and circuit depth. An example is the approach taken by Biswal et al., which achieves very low T-depth at the cost of using many ancilla qubits [11]. In this work, the number of ancilla qubits can outnumber the number of non-ancilla of qubits in the computation. This is infeasible with current devices, as existing hardware technologies have low qubit counts.

## 2.4 Template Matching for Circuit Synthesis and Optimization

This section describes the circuit optimization method of template matching. Section 2.4.1 defines template matching and explains the difference between identity and library templates. Section 2.4.2 explains the main challenges inherent to template matching.

## 2.4.1 Template Matching Overview

Template matching is an optimization method that reduces circuit cost by repeatedly conducting local optimization of subcircuits [35]. This technique traverses a circuit searching for subcircuits matching known templates, then replaces each identified subcircuit with the corresponding lower-cost but functionally equivalent gate sequence [37].

Research into template matching for reversible circuit simplification started in 2003 with the work done by Miller et al. [40]. This work presents the idea of reducing circuit cost by replacing a sequence of gates with an equivalent but smaller sequence for circuits composed of gates from the NCT set. Building upon this, Maslov et al. published an article in 2005 on template matching specifically for quantum circuits [35]. It extends the earlier work by creating NCV gate templates and presenting the idea of a stand-alone template called an identity template, discussed in Section 2.4.1.1. Since then, there have been many implementations of template matching to improve cost metrics of quantum circuits. Variations include abstraction level, gate

set, number of qubits, and type of template used. There are two primary types of templates for circuit reduction: identity templates and library templates.

#### 2.4.1.1 Identity Templates

As defined by Abdessaied et al., identity templates are circuits realizing the identity operator that are composed of "m gates such that each subcircuit of size less than m/2 cannot be replaced by another template" [3]. Since the matrix corresponding to the template is equal to the identity, if the complete sequence of gates in the template is found, the entire sequence can be removed from the circuit. An example of an identity template is shown in Figure 16.

Figure 16: Identity template example. Reproduced from Maslov et al. [35]

Identity templates have the useful property that was presented as Lemma 2 in *Toffoli network synthesis using templates*: "If a network  $G_0G_1...G_m$  realizes the identity function, then for any k-shift,  $G_kG_{(k+1) \mod m} \cdots G_{(k-1) \mod m}$  realizes the identity" [36]. This property is useful in that the template can be thought of as a cycle it can start with any of the gates present in the template and the sequence of gates going around the ring from the starting gate to the ending gate (directly preceding the starting gate) is an equivalent identity template. Therefore, a sequence matching the template does not necessarily have to start at the first gate specified, but rather can start at any gate so long as the subsequent gate order remains the same.

Furthermore, identity templates have the advantage that the entire gate sequence does not need to be present in order to yield a reduction by template application. The only criterion to result in a reduction is that more than half of the gates in the template match, with a greater number matching meaning a greater reduction. Formally, this is the following: "a series of gates in a network that matches the sequence of gates  $G_iG_{(i+1) \mod m} \cdots G_{(i+k-1) \mod m}$  of the template  $G_0G_1 \cdots G_{m-1}$  exactly, is replaced with the sequence  $G_{(i-1) \mod m}G_{(i-2) \mod m} \cdots G_{(i+k) \mod m}$  without changing the network's output, where  $k \in \mathbb{N}, k \geq \frac{m}{2}$ " [36].

For example, given the m = 5 gate template  $G_0G_1G_2G_3G_4$  shown in Figure 16, at least  $\frac{5}{2}$  gates need to match for a reduction. Therefore, if three gates are matched, say  $G_0G_1G_2$ , they can be replaced with  $G_4G_3$ , thereby reducing the gate count by one. This can be seen in Figure 17. The boxed subcircuit in Figure 17a can be replaced with the boxed subcircuit in Figure 17b.

(a) Circuit prior to template application(b) Circuit after template applicationFigure 17: Application of identity template

A disadvantage of approaches based on identity templates is that they cannot be used to convert between gate sets: the template and its application must be done at the same level of abstraction. One use of template application techniques is to combine the decomposition of a high-level reversible circuit to a quantum-level circuit with the optimization step. Identity templates do not allow this—the decomposition and optimization steps must be done independently.

The previously discussed work by Maslov et al. is an example of template matching using identity templates [35]. This work presents NCV gate templates and applies them to quantum-level realizations of MCT gates with up to 11 lines. The results are compared to the best-known quantum realizations at the time of the writing to evaluate differences in gate count. The results ranged from 76.56% to 93.75% fewer gates in the circuits simplified by the NCV templates.

## 2.4.1.2 Library Templates

Library templates are a type of template composed of two sequences of gates of differing lengths but equivalent operator matrices. These are referred to as library templates in this work to distinguish them from identity templates. In literature, only the term "template" is used; the specific type is determined by context.

Cost savings via library templates can therefore be realized by replacing occurrences of one element of each pair by occurrences of the corresponding element. These templates do not necessarily compute to the identity; the only requirement is that the correlated templates realize the same operator. An example of a library template is shown in Figure 18.

Figure 18: Library template. Subfigure (b) shows the optimal NCV version of the circuit in subfigure (a). This template is designed to combine the optimization and decomposition steps so that decomposing the NCT circuit into the NCV circuit will produce better results. Reproduced from Arpita et al. [7]

Two advantages of library templates are that they can realize any operator and that the paired sequences can be composed of different gate sets. Lifting the restriction that the gate sequence must compute the identity offers more flexibility in the construction of templates; any sequence with an optimized corresponding version can be used. This significantly increases the number of templates available. The fact that the template and its pair can be composed of different gate sets is advantageous in that these templates can be used to combine the optimization and mapping procedures into one step. Rather than decomposing the circuit to a lower level gate set, then applying an optimization scheme, the optimization can occur at the same time as decomposition by mapping small sequences of a higher level gate set to a known optimized sequence of lower level gates.

A disadvantage of library templates is that, for the majority of cases, the entire sequence of gates in the template must be matched. This makes it more difficult to find template matches within the larger circuit, and leads to the templates more often being composed of a smaller number of gates than that of the identity templates.

An example of research using this method was conducted by Scott and Dueck, in which the researchers considered pairs of MCT gates operating on three or fewer qubits on up to four lines and identified the optimal NCV gate realization of each pair [58]. Therefore, the templates in this case were composed of two NCT gates and their equivalent NCV realization. The authors report on the results of computational experiments comparing the effectiveness of decomposing a large circuit gate by gate, as had previously been done, to doing so two-gates at a time. Their experiments use their template matching technique on all 3-bit reversible functions and a set of benchmarks from Revlib [60]. They discovered that of the 40,310 circuits tested for the 3-bit reversible case, 91.45% of them were improved, with an average improvement of 19.565% reduction in gate count. Of the 16 benchmark functions, all were improved. The improvements ranged from a 11.6% to 63.2% reduction in gate count.

Following on to this work is that done by Arpita et al., in which the researchers create the same type of templates as Scott and Dueck, but increase the number of gates in the template to three [7]. Using benchmarks from RevLib, they apply Barenco decomposition to decompose the large MCT gates into NCT gates, then decompose the NCT circuit into a NCV circuit using their triple-gate templates. They compared the gate count of the resulting circuits to that of Scott and Dueck for eight common benchmarks to find that five circuits had better results using triple gate templates and three circuits had better results using template pairs.

## 2.4.2 Template Matching Challenges

Although template matching techniques have been shown to improve circuit costs, the challenges of generating templates and identifying template-matching sequences currently limit the impact these techniques can have.

## 2.4.2.1 Template Search