#### University of Tennessee, Knoxville

## TRACE: Tennessee Research and Creative **Exchange**

**Doctoral Dissertations**

Graduate School

8-2020

# Modeling and Optimization Algorithm for SiC-based Three-phase **Motor Drive System**

Ren Ren

University of Tennessee, Knoxville, rren3@vols.utk.edu

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

Part of the Electrical and Electronics Commons, and the Power and Energy Commons

#### **Recommended Citation**

Ren, Ren, "Modeling and Optimization Algorithm for SiC-based Three-phase Motor Drive System." PhD diss., University of Tennessee, 2020.

https://trace.tennessee.edu/utk\_graddiss/6892

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Ren Ren entitled "Modeling and Optimization Algorithm for SiC-based Three-phase Motor Drive System." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Fred Wang, Major Professor

We have read this dissertation and recommend its acceptance:

Leon Tolbert, Daniel Costinett, Zheyu Zhang

Accepted for the Council:

Dixie L. Thompson

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# Modeling and Optimization Algorithm for SiC-based Three-phase Motor Drive System

A Dissertation Presented for the

**Doctor of Philosophy**

**Degree**

The University of Tennessee, Knoxville

Ren Ren

August 2020

#### Acknowledgment

First of all, I would like to express my deepest gratitude to my advisor, Dr. Fred Wang, for his support and guidance during my Ph.D. study. With deep insights into power electronics, he enables me to look at power electronics with a new horizon from physics instead of only focusing on circuits level. He taught me how to do solid research in a systematic way and with critical thinking. I was also always surprised by his high energy and concentration, and Dr. Wang devotes most of his time to students and can remember most details in our discussions and weekly meetings although he needs to follow up on several projects in the meantime. More importantly, Dr. Wang taught me how to be a mature person on communication, teamwork, project management, and life plan, benefiting my career as well as my personal life.

I am deeply grateful to Dr. Leon. M. Tolbert, for his suggestions on my research and encouragement. He is always willing to help me review my papers and dissertations, providing valuable comments and corrections. Also, he is very patient and kind to answer my questions on the different things that I am not familiar with, like honor society, school policy and research career development.

I would like to thank Dr. Daniel Costinett, for kindly spending time to discuss with me and to inspire me for the new idea. His class on the high frequency converter analysis inspires me to use different mathematical methods to solve the problems.

I would like to thank Dr. Zheyu Zhang, for kindly accepting my invitation as my Ph.D. committee member. I admire that he can always catch key points for the research and gave me very constructive suggestions.

I would like to thank Boeing, NASA, and Safran for the financial support of my Ph.D. study. Special thanks are for Eugene V. Solodovnik in Boeing and Cyrille Gautier in Safran, for being my industry sponsor and their help and patience in guiding my project. I also appreciate Dr. Min Kao for providing EECS Min Kao Fellowship during my last year Ph.D. study.

I would like to thank all the colleagues whom I work with in different projects: Dr. Bo Liu, Dr. Edward Jones, Dr. Ruirui Chen, Dr. Handong Gui, Mr. Zhou Dong, Mr. Jiahao Niu, Mr. Haiguo Li, Dr. Zheyu Zhang, Dr. Ben Guo, Dr. Xiaonan Lu. It was a great experience to work with all of you. I also cherish the help and friendship from all other students, alumni, and visiting scholars in the power electronics lab. They are Dr. Yiwei Ma, Dr. Chongwen Zhao, Dr. Ling Jiang, Dr. Fei Yang, Dr. Jingxin Wang, Dr. Zhiqiang Wang, Dr. Weimin Zhang, Dr. Yutian Cui, Mr. Bradford Trento, Dr. Wenchao Cao, Dr. Jing Wang, Dr. Saeed Anwar, Dr. Chun Gan, Dr. Shiqi Ji, Dr. Li Zhang, Dr. Yu Ren, Mr. Zhe Yang, Mr. Wen Zhang, Mr. Jie Li, Mr. Xingxuan Huang, Mr. Zimin Wang, Mr. Zihan Gao, Dr. Mitchell Smith, Ms. Jingjing Sun, Ms. Shuyao Wang, Ms. Le Kong, Ms. Maeve Lawniczak, Mr. Jacob Dyer, Mr. Craig Timms, Mr. Geoff Laughon, Mr. Chi Xu, Mr. Gabriel Gabian, Mr. Mark Nakmali, Mr. Spencer Cochran, Ms. Paige Williford, Mr. Dingrui Li, Mr. Xiaoyang Wang, Mr. Jordan Sangid, Mr. Doug Bouler, Mr. Daniel Merced Cirino, Mr. Kamal Sabi, Mr. Nattapat Praisuwanna, Mr. Andrew Foote, Mr. Jared Baxter, Mr. Zhouyang Li, Mr. Yifan Zhang, Ms. Min Lin, Mr. Liyan Zhu, Mr. Yang Huang, Mr. Ruiyang Qin, Mr. Yu Yan. Specially, I would like to thank Dr. Bo Liu, Dr. Edward Jones, Dr. Zheyu Zhang, Dr. Ruirui Chen, Mr. Zhou Dong, Mr. Jiahao Niu, Mr. Zhe Yang, Mr. Xingxuan Huang and Mr. Wen Zhang for numerous brainstorming discussions we had together.

I would like to thank the staff members of the University of Tennessee. They are Mr. Robert B. Martin, Ms. Wendy Smith, Ms. Judy Evans, Ms. Dana Bryson, Mr. Ryan Smiley and Mr. Adam Hardebeck.

Finally, but most importantly I would like to express my heartiest thanks to my parents and my wife Jiamei Huang for their unconditional love. Special thanks to my wife Jiamei, she always gave me a warm hug whenever I met difficulties and felt frustrated. Without her support and encouragement, this work is never possible.

This dissertation made use of Engineering Research Center Shared Facilities supported by the Engineering Research Center Program of the National Science Foundation and the Department of Energy under NSF Award Number EEC-1041877 and the CURENT Industry Partnership Program.

#### **Abstract**

More electric aircraft (MEA) and electrified aircraft propulsion (EAP) becomes the important topics in the area of transportation electrifications, expecting remarkable environmental and economic benefits. However, they bring the urgent challenges for the power electronics design since the new power architecture in the electrified aircraft requires many benchmark designs and comparisons. Also, a large number of power electronics converter designs with different specifications and system-level configurations need to be conducted in MEA and EAP, which demands huge design efforts and costs. Moreover, the long debugging and testing process increases the time to market because of gaps between the paper design and implementation.

To address these issues, this dissertation covers the modeling and optimization algorithms for SiC-based three-phase motor drive systems in aviation applications. The improved models can help reduce the gaps between the paper design and implementation, and the implemented optimization algorithms can reduce the required execution time of the design program.

The models related to magnetic core based inductors, geometry layouts, switching behaviors, device loss, and cooling design have been explored and improved, and several modeling techniques like analytical, numerical, and curve-fitting methods are applied. With the developed models, more physics characteristics of power electronics components are incorporated, and the design accuracy can be improved.

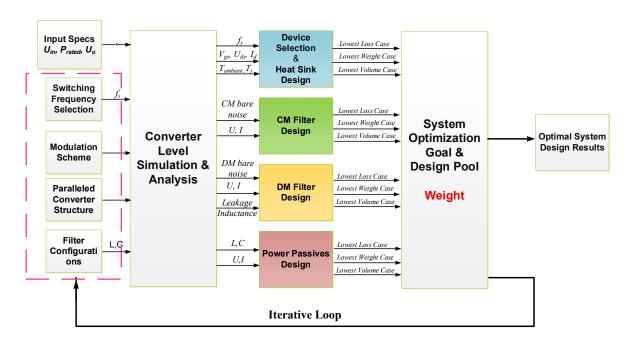

To improve the design efficiency and to reduce the design time, optimization schemes for the filter design, device selection combined with cooling design, and system-level optimization are studied and implemented. For filter design, two optimization schemes including  $A_p$  based weight prediction and particle swarm optimization are adopted to reduce searching efforts. For device

selection and related cooling design, a design iteration considering practical layouts and switching speed is proposed. For system-level optimization, the design algorithm enables the evaluation of different topologies, modulation schemes, switching frequencies, filter configurations, cooling methods, and paralleled converter structure. To reduce the execution time of system-level optimization, a switching function based simulation and waveform synthesis method are adopted.

Furthermore, combined with the concept of design automation, software integrated with the developed models, optimization algorithms, and simulations is developed to enable visualization of the design configurations, database management, and design results.

## **Table of Contents**

| Chapter | One Intr | oduction                                                          | 1  |

|---------|----------|-------------------------------------------------------------------|----|

| 1.1     | Applica  | ation Background                                                  | 1  |

| 1.2     | Researc  | ch Motivations and Challenges                                     | 4  |

|         | 1.2.1    | Modeling                                                          | 8  |

|         | 1.2.2    | Design Approach and Optimization                                  | 9  |

|         | 1.2.3    | Design Automation                                                 | 13 |

| 1.3     | Propos   | ed Model-Data-Optimization Framework for Power Electronics Design | 13 |

| 1.4     | Dissert  | ation Layout                                                      | 15 |

| Chapter | Two Lit  | erature Review                                                    | 18 |

| 2.1     | Power    | Semiconductors Modeling                                           | 18 |

|         | 2.1.1    | Switching Behavior Model                                          | 19 |

|         | 2.1.2    | Device Loss Model                                                 | 22 |

|         | 2.1.3    | Thermal Model for Power Devices                                   | 25 |

| 2.2     | Passive  | e Components Modeling in Power Electronics                        | 27 |

|         | 2.2.1    | Magnetics Core Inductor                                           | 28 |

|         | 2.2.2    | Capacitor                                                         | 37 |

|         | 2.2.3    | Heatsink and Fan                                                  | 40 |

|         | 2.2.4    | Busbar and PCB Layout                                             | 41 |

| 2.3     | Design   | Optimization in Power Electronics Design                          | 43 |

|         | 2.3.1    | Optimization Algorithm Review                                     | 44 |

|         | 2.3.2    | Local Optimization for a Specific Trade-off Design Problem        | 49 |

|         | 2.3.3    | Global Optimization of Whole Power Stage Design                   | 51 |

| 2.4     | Summa    | ary                                                               | 59 |

| Chapter  |            | lter Design Optimization Considering Non-linear Physics Characteristics    |

|----------|------------|----------------------------------------------------------------------------|

|          |            |                                                                            |

| 3.1      | Impacts    | s of Current-bias Dependent Permeability on EMI filter Design              |

|          | 3.1.1      | Investigation of Current-bias Dependent Permeability of DM Cores 63        |

|          | 3.1.2      | Variable Inductor Model with Considering Current-bias Dependent            |

| Pe       | ermeabilit | ty66                                                                       |

|          | 3.1.3      | Study of Induced Unbalanced DM Impedance and Mixed-mode Noise 68           |

|          | 3.1.4      | Design Algorithm with Consideration of Current-bias Dependent              |

| Pe       | ermeabilit | ty71                                                                       |

|          | 3.1.5      | Experimental Verification                                                  |

| 3.2      | Impeda     | ince-based CM Inductor Design Approach Considering Frequency-dependent     |

| and Imag | inary Per  | meability                                                                  |

|          | 3.2.1      | Characteristics of Frequency-dependent Permeability for CM Cores 79        |

|          | 3.2.2      | Modeling of Frequency-Dependent Permeability and Derivation of Required    |

| In       | npedance   | of CM Inductor                                                             |

|          | 3.2.3      | Impedance-based CM Inductor Design Approach                                |

|          | 3.2.4      | Experimental Results                                                       |

| 3.3      | Maxim      | um Magnetic Flux Density Model for CM Inductors                            |

|          | 3.3.1      | Limitation of Conventional Model                                           |

|          | 3.3.2      | Proposed Common Mode Flux Density Model                                    |

|          | 3.3.3      | Verification and Comparison96                                              |

| 3.4      | Leakag     | e Model of Toroidal CM Inductor with Analogy of Reluctance and Capacitance |

|          | C          | 99                                                                         |

|          | 3.4.1      | Rod Core Inductance Derivation with Analogy of Reluctance and              |

| Ca       | apacitanc  |                                                                            |

|          | 3.4.2      | Leakage Inductance of CM Choke Derivation                                  |

|    |                 | 3.4.3                                        | Verification of Proposed Leakage Model                                                                                                                                                                                             | 109                         |

|----|-----------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

|    | 3.5             | Film C                                       | apacitor Model                                                                                                                                                                                                                     | 112                         |

|    |                 | 3.5.1                                        | Frequency-Dependent Ac Voltage Rating Model                                                                                                                                                                                        | 113                         |

|    |                 | 3.5.2                                        | ESL and ESR Model                                                                                                                                                                                                                  | 114                         |

|    | 3.6             | Ac Dv/                                       | dt Filter Design Routine and Optimization with $A_P$ prediction                                                                                                                                                                    | 116                         |

|    |                 | 3.6.1                                        | Determination of Corner Frequency of <i>Dv/dt</i> Filter                                                                                                                                                                           | 116                         |

|    |                 | 3.6.2                                        | Distribution of L and C with a Targeted Corner Frequency                                                                                                                                                                           | 118                         |

|    | 3.7             | PSO-ba                                       | ased EMI Filter Routine and Optimization                                                                                                                                                                                           | 122                         |

|    |                 | 3.7.1                                        | Determination of Corner Frequency of EMI Filter                                                                                                                                                                                    | 122                         |

|    |                 | 3.7.2                                        | Design Iteration of EMI Filters                                                                                                                                                                                                    | 124                         |

|    |                 | 3.7.3                                        | Design Optimization Algorithm Selection and Improvement                                                                                                                                                                            | 125                         |

|    | 3.8             | Summa                                        | ary                                                                                                                                                                                                                                | 128                         |

| Cł | antor           | Farm Dar                                     | vice Selection Optimization Considering Switching Speed Limitat                                                                                                                                                                    | tion and                    |

| CI | iaptei          | rour De                                      | vice selection Optimization Considering Switching Speed Limital                                                                                                                                                                    | uon anu                     |

| CI | _               |                                              | Layout                                                                                                                                                                                                                             |                             |

|    | _               | er-loop L                                    |                                                                                                                                                                                                                                    | 131                         |

|    | Pow             | er-loop L                                    | Layout                                                                                                                                                                                                                             | 131<br>132                  |

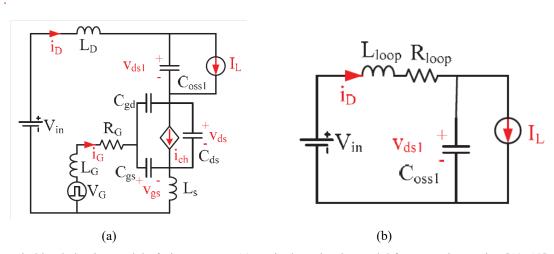

|    | Pow             | er-loop L<br>SiC MO                          | OSFETs Switching Behavior Model                                                                                                                                                                                                    | 131<br>132<br>132           |

|    | Pow             | SiC MG<br>4.1.1<br>4.1.2                     | DSFETs Switching Behavior Model                                                                                                                                                                                                    | 131<br>132<br>132<br>136    |

|    | <b>Pow</b> (4.1 | SiC MG<br>4.1.1<br>4.1.2                     | DSFETs Switching Behavior Model  Discrete-time Modeling of Switching Behavior  Switching Speed Prediction and Verification                                                                                                         | 131 132 132 136 139         |

|    | <b>Pow</b> (4.1 | SiC MO 4.1.1 4.1.2 Busbar                    | Discrete-time Modeling of Switching Behavior  Switching Speed Prediction and Verification  Model                                                                                                                                   | 131 132 132 136 139         |

|    | <b>Pow</b> (4.1 | SiC MO 4.1.1 4.1.2 Busbar 4.2.1 4.2.2        | Discrete-time Modeling of Switching Behavior  Switching Speed Prediction and Verification  Model  Thermal Model.                                                                                                                   | 131 132 132 136 139 139     |

|    | Power 4.1 4.2   | SiC MO 4.1.1 4.1.2 Busbar 4.2.1 4.2.2        | Discrete-time Modeling of Switching Behavior  Switching Speed Prediction and Verification  Model  Thermal Model.  Thickness Determination                                                                                          | 131 132 132 136 139 141 142 |

|    | Power 4.1 4.2   | SiC MG 4.1.1 4.1.2 Busbar 4.2.1 4.2.2 Numeri | DSFETs Switching Behavior Model.  Discrete-time Modeling of Switching Behavior.  Switching Speed Prediction and Verification.  Model.  Thermal Model.  Thickness Determination.  ical Modeling of Power-loop Inductance with PEEC. | 131 132 136 139 139 141 142 |

| 4.4     | Gate Resistance Selection with Switching Speed Optimization |                                                                 | 155 |

|---------|-------------------------------------------------------------|-----------------------------------------------------------------|-----|

|         | 4.4.1                                                       | Gate Resistance General Selection Constraints                   | 156 |

|         | 4.4.2                                                       | Turn-off Gate Resistance Selection with di/dt constraint        | 157 |

|         | 4.4.3                                                       | Turn-on Gate Resistance Selection with $dv/dt$ constraint       | 158 |

|         | 4.4.4                                                       | Complete Design Example for Gate Resistance Selection           | 160 |

| 4.5     | Summa                                                       | ary                                                             | 164 |

| Chapter | Five Co                                                     | oling Design Optimization with Multi-variable Device Loss Scali | ng  |

|         | •••••                                                       |                                                                 | 166 |

| 5.1     | Cooling                                                     | g System Model                                                  | 166 |

|         | 5.1.1                                                       | Correction of Thermal Resistance of Extruded Heatsink           | 166 |

|         | 5.1.2                                                       | Pressure Drop Model of Heatsinks and Fans                       | 168 |

| 5.2     | Switch                                                      | ing Loss Scaling Method Considering Practical Parameters        | 170 |

|         | 5.2.1                                                       | Proposed Scaling Method                                         | 170 |

|         | 5.2.2                                                       | Verification of Proposed Scaling Method                         | 174 |

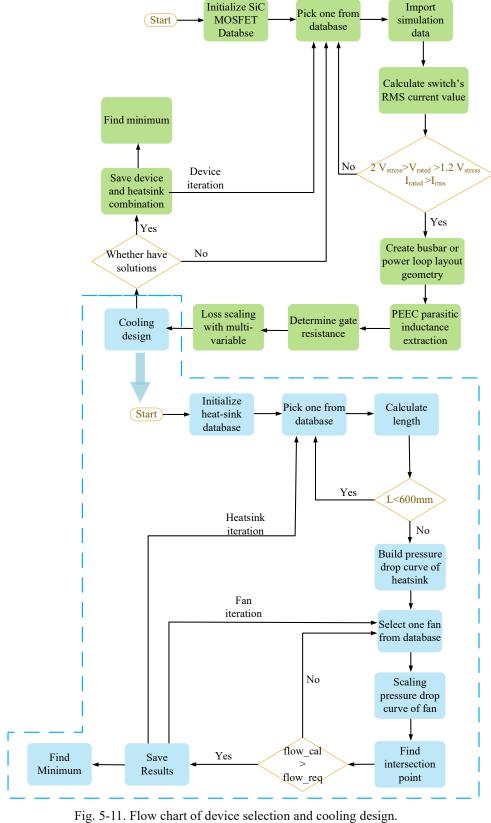

| 5.3     | Design                                                      | Iteration Combined with Device Selection and Cooling Design     | 178 |

| 5.4     | Summa                                                       | nry                                                             | 180 |

| Chapter | Six Syst                                                    | em-level Iteration and Optimization                             | 182 |

| 6.1     | Switch                                                      | ing Function based Fast Simulation Scheme                       | 182 |

| 6.2     | Curren                                                      | t Waveforms Synthesis for Components Design                     | 189 |

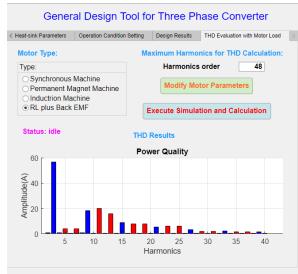

| 6.3     | THD E                                                       | valuation with Motor Model                                      | 191 |

| 6.4     | System                                                      | l-level Optimization with Frequency and Modulation Selection    | 196 |

|         | 6.4.1                                                       | System Iteration Scheme                                         | 196 |

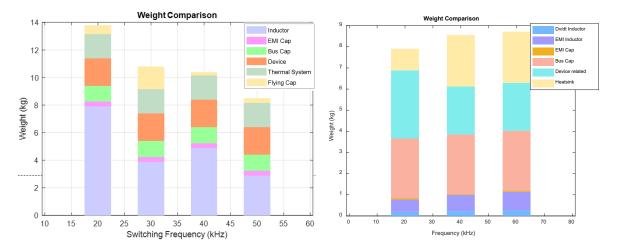

|         | 6.4.2                                                       | Case Study                                                      | 198 |

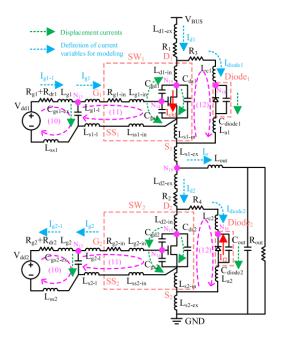

| 6.5     | Design                                                      | Routine for Paralleled Converters                               | 207 |

| Vita      |          |                                                                 | 243 |

|-----------|----------|-----------------------------------------------------------------|-----|

| Reference | •••••    |                                                                 | 231 |

| 8.2       | Future   | Work                                                            | 228 |

| 8.1       | Conclu   | sion                                                            | 225 |

| Chapter E | Eight Co | onclusion and Future Work                                       | 225 |

| 7.5       | Summa    | ry                                                              | 224 |

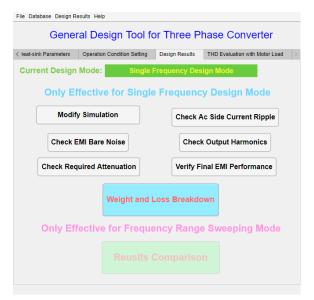

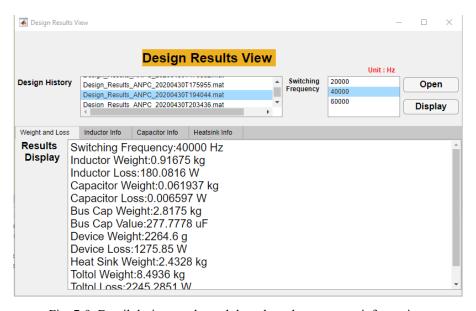

| 7.4       | Design   | Results Visualization                                           | 221 |

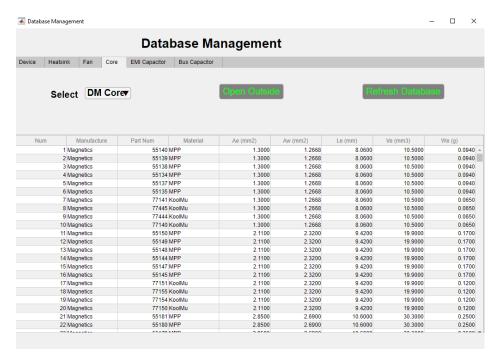

| 7.3       | Databas  | se Construction and Management                                  | 220 |

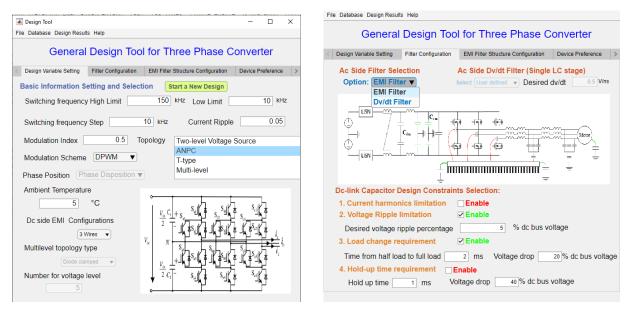

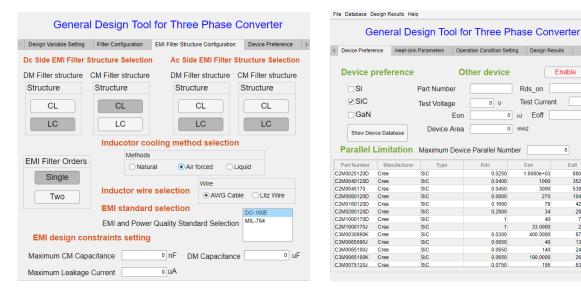

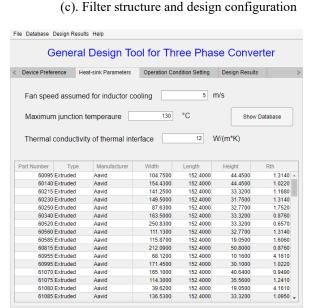

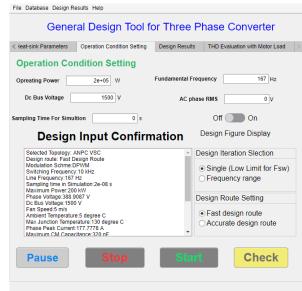

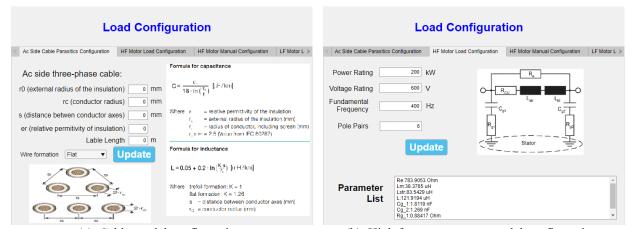

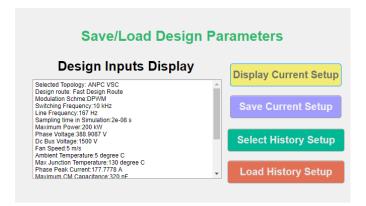

| 7.2       | Design   | Configuration                                                   | 216 |

| 7.1       | Model-   | view-controller (MVC) Architecture based UI framework           | 215 |

| Chapter S | even D   | evelopment for Software                                         | 215 |

| 6.6       | Summa    | ry                                                              | 213 |

|           | 6.5.2    | Case Study                                                      | 210 |

|           | 6.5.1    | Design Strategies for Interleaving Angle and Coupled inductance | 207 |

## **List of Tables**

| Table 3-1. Comparisons for different DM core materials                                    | 65  |

|-------------------------------------------------------------------------------------------|-----|

| Table 3-2. Testing Condition and Specs of ANPC                                            | 74  |

| Table 3-3. Specs of Two DM Inductors                                                      | 75  |

| Table 3-4. Specs of ANPC for EMI filter design                                            | 89  |

| Table 3-5. Design results with two design approaches                                      | 90  |

| Table 3-6. Comparison Results for Two Magnetic Flux Density Models                        | 98  |

| Table 4-1. Key parameter comparison between the predicted results and the testing results | 139 |

| Table 4-2. Main futures of four numerical methods for field problems.                     | 146 |

| Table 4-3. Parameters of design example with C3M0065090J.                                 | 161 |

| Table 4-4. Gate resistance selection constraints summary.                                 | 162 |

| Table 5-1. Summary of Switching Loss Separation.                                          | 173 |

| Table 5-2. Specs for switching loss comparison.                                           | 177 |

| Table 5-3. Switching loss calculation comparison with two scaling methods                 | 178 |

| Table 6-1. Motor Drive Controller Specification                                           | 198 |

# **List of Figures**

| Fig. 1-1. Power consumption distribution for non-propulsive applications in conventional aircraft.    |

|-------------------------------------------------------------------------------------------------------|

|                                                                                                       |

| Fig. 1-2. Power consumption distribution for non-propulsive applications in the MEA                   |

| Fig. 1-3. The performance factors of power electronics converters in the MEA applications 5           |

| Fig. 1-4. A general view of design problem in power electronics in [11]                               |

| Fig. 1-5. MOD framework for the development of the design tool for three-phase ac motor drive         |

| applications. 14                                                                                      |

| Fig. 2-1. Switching behavior model of Si MOSFET: (a) equivalent circuits model for saturation         |

| region [12, 13], (b) equivalent circuits model for ohmic region [13]                                  |

| Fig. 2-2. Switching behavior model of one phase-leg in [18]                                           |

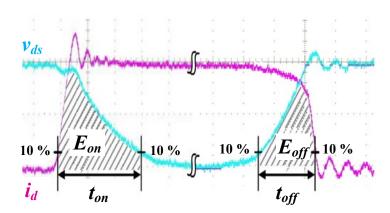

| Fig. 2-3. Calculation of switching times and energies by double pulse testing [25]                    |

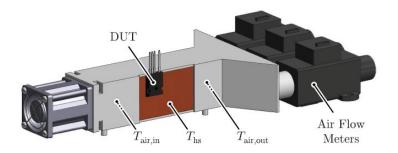

| Fig. 2-4. Illustration of setup for calorimetric switching loss measurement in [29]                   |

| Fig. 2-5. Steady-state thermal modeling for TO-type packages in [33]                                  |

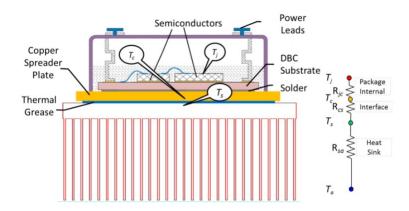

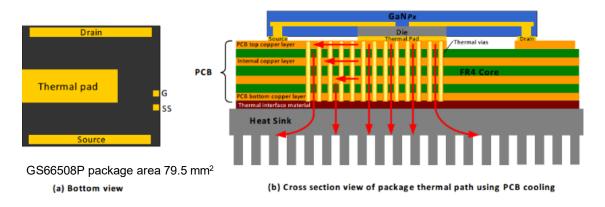

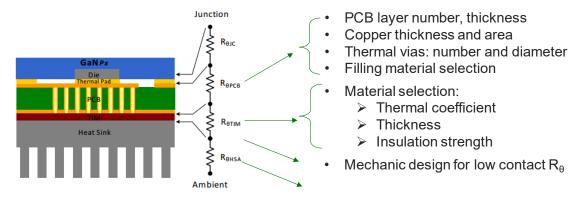

| Fig. 2-6. Thermal flow of surface mount power devices through PCB in [34]                             |

| Fig. 2-7. Steady-state thermal modeling for surface mount packages in [35]                            |

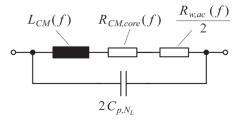

| Fig. 2-8. Lumped circuits model of inductors in [10]                                                  |

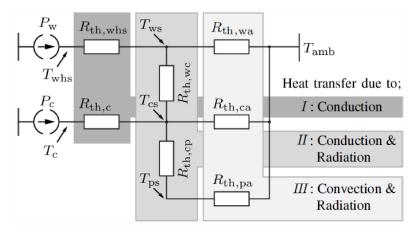

| Fig. 2-9. Illustration of thermal resistance network modeling for level 3 thermal design of inductors |

| in [62]                                                                                               |

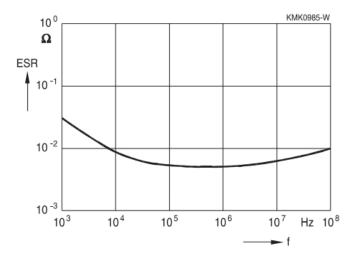

| Fig. 2-10. Typical ESR curve with frequency in [65]                                                   |

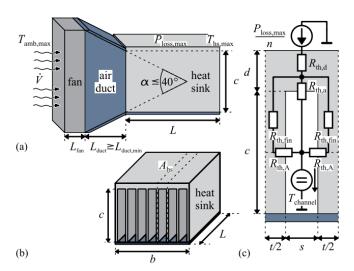

| Fig. 2-11. Illustration of a cooling system with extruded heatsink and fan [69]                       |

| Fig. 2-12. Illustration of dynamic fluid models on cooling design [69]                                |

| Fig. 2-13. A general review of design problem in power electronics in [89]                            |

| Fig. 2-14. Classification of optimization algorithms in two categories                                |

| Fig. 2-15. Local optimization summary in power electronics design                                     |

| Fig. 2-16. The configuration of an industrial motor drive in [11].                                                 | 52        |

|--------------------------------------------------------------------------------------------------------------------|-----------|

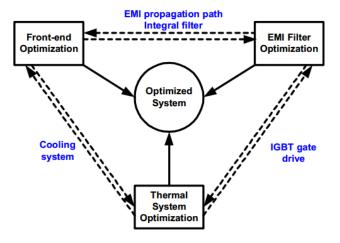

| Fig. 2-17. Approach for system optimization for a motor drive in [11].                                             | 53        |

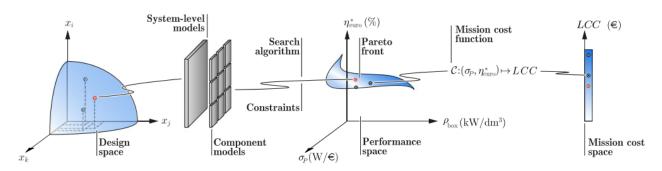

| Fig. 2-18. General concept for multi-objective optimization with Pareto-front curve in [101] 5                     | 53        |

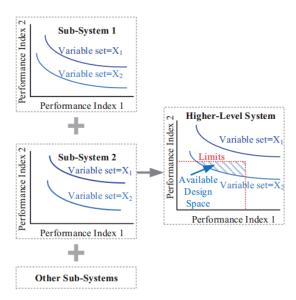

| Fig. 2-19. Higher-level system Pareto front could be identified by synthesizing sub-system Pare fronts in [126].   |           |

| Fig. 2-20. Three layers of optimization structure in [126] for EV charger application                              | 55        |

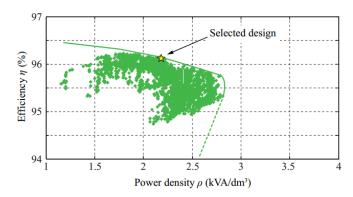

| Fig. 2-21. Pareto curve of the η-ρ performance space and the selected design point in [62]                         | 57        |

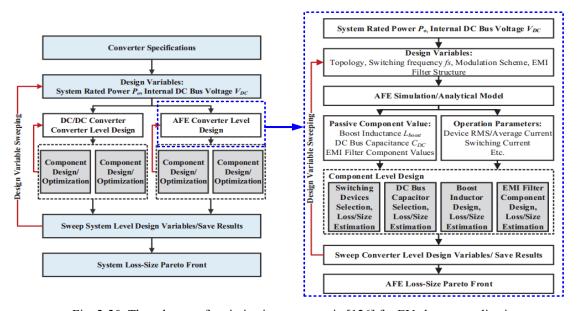

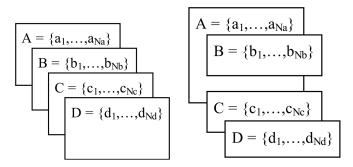

| Fig. 2-22. Design variables arrangement comparison: centralized optimizer vs. distribute optimizers.               |           |

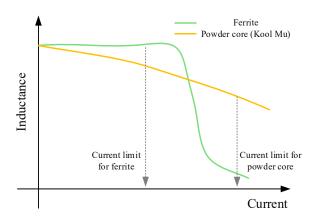

| Fig. 3-1. Inductance curve with current-bias for ferrite and powder core [127]                                     | 64        |

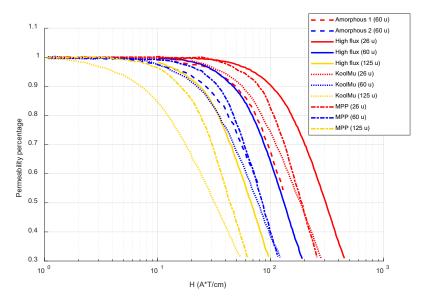

| Fig. 3-2. Permeability percentage curves with current-bias for amorphous and powder core                           | 65        |

| Fig. 3-3. Permeability percentage curve with current-bias for amorphous and powder core 6                          | 67        |

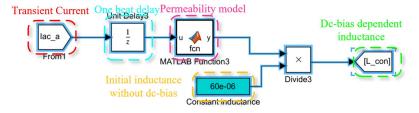

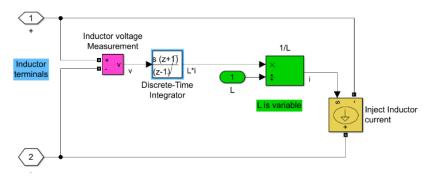

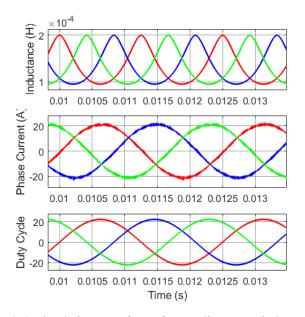

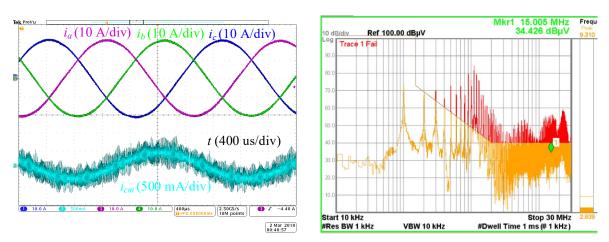

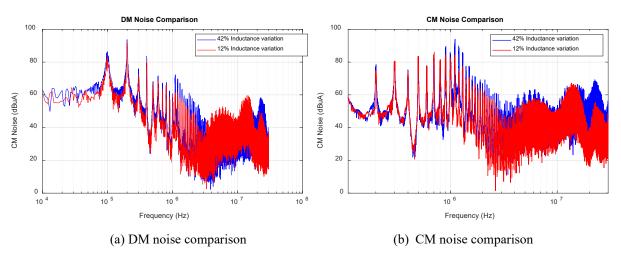

| Fig. 3-4. Simulation waveforms for non-linear DM inductance                                                        | 69        |

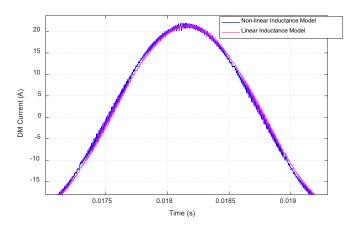

| Fig. 3-5. DM currents comparison with or without non-linear DM inductor model                                      | 70        |

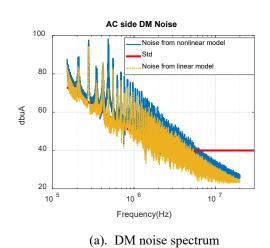

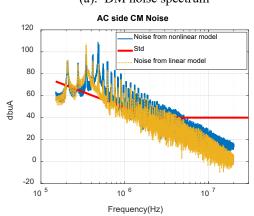

| Fig. 3-6. Noise spectrum comparisons from simulation results.                                                      | 70        |

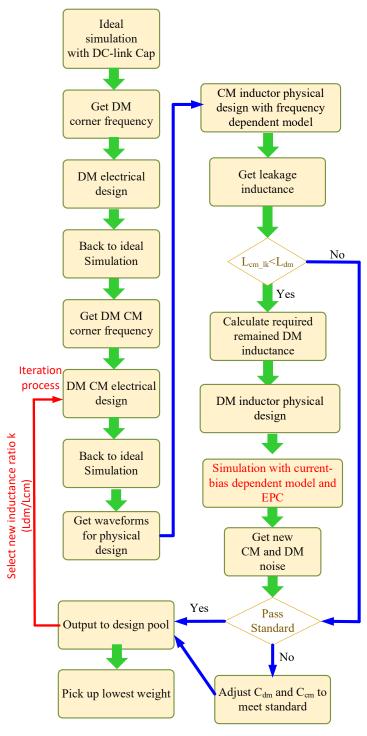

| Fig. 3-7. Flow chart of the design algorithm of EMI filter with consideration of current-bidependent permeability. |           |

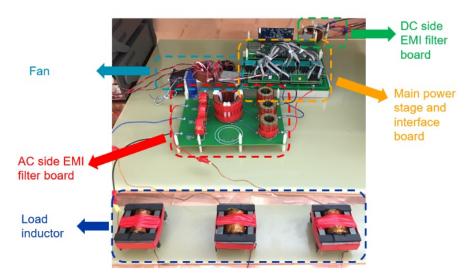

| Fig. 3-8. The prototype of ANPC for EMI testing setup.                                                             | 74        |

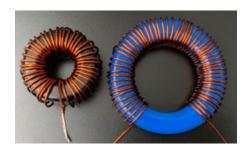

| Fig. 3-9. The prototype of two DM inductors                                                                        | 76        |

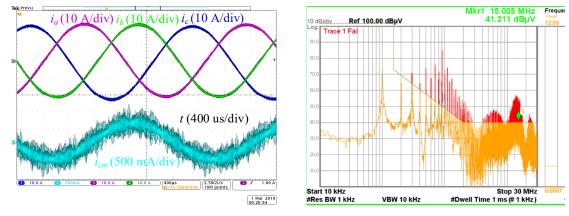

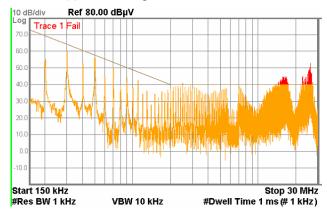

| Fig. 3-10. Experimental waveforms and noise measurement for two inductors                                          | 77        |

| Fig. 3-11. EMI bare noise comparisons only with DM inductors.                                                      | 77        |

| Fig. 3-12. Corner frequency design of CM filter.                                                                   | 78        |

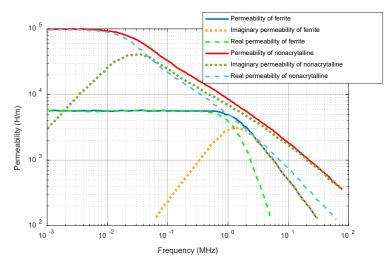

| Fig. 3-13. Permeability curve for ferrite and nanocrystalline cores.                                               | 79        |

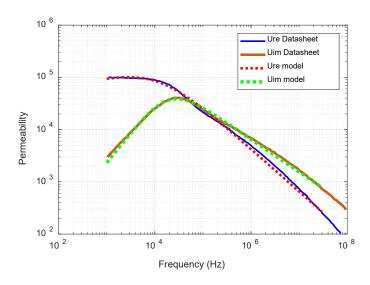

| Fig. 3-14. Curve fitting results of the real and imaginary permeability of nanocrystalline materi                  | ial<br>81 |

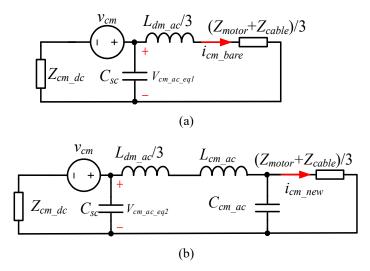

| Fig. 3-15. Equivalent common-mode circuits of a three-phase converter (a) without CM filter, (b)                    |

|---------------------------------------------------------------------------------------------------------------------|

| the CM filter83                                                                                                     |

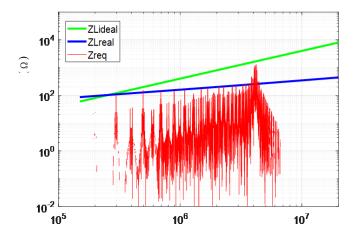

| Fig. 3-16. Real impedance curve of the traditional design approach                                                  |

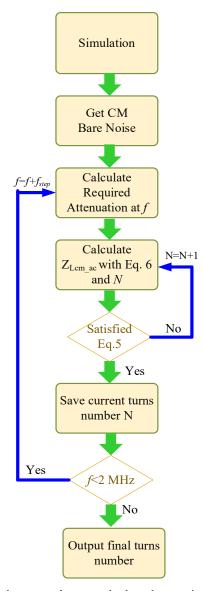

| Fig. 3-17. Design procedure to calculate the required turns number                                                  |

| Fig. 3-18. Physical design procedure and iteration for CM inductors                                                 |

| Fig. 3-19. The prototype of two CM inductors.                                                                       |

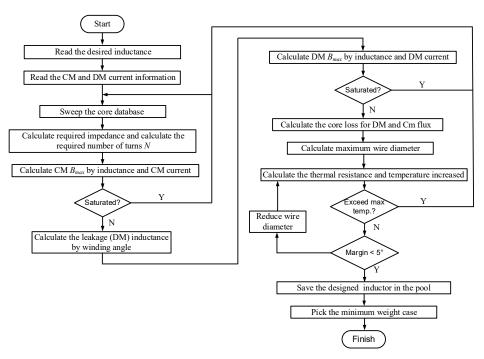

| Fig. 3-20. Comparisons between measured results and design results                                                  |

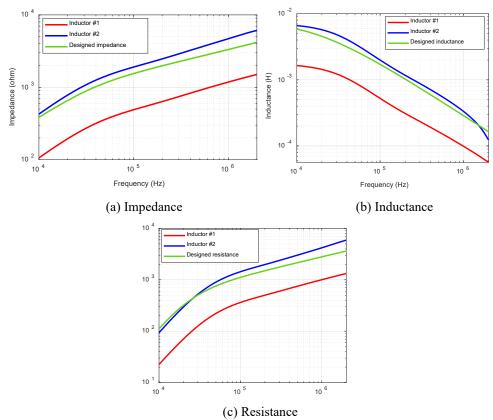

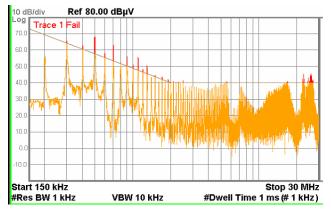

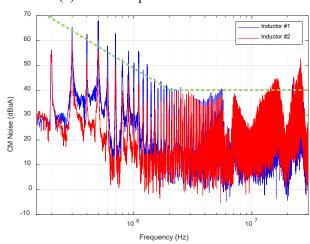

| Fig. 3-21. Noise spectrums comparison with two design inductors                                                     |

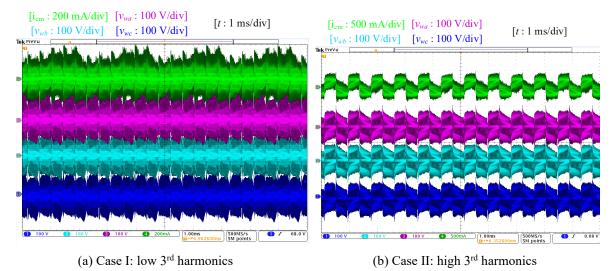

| Fig. 3-22. CM inductor voltage and current waveforms                                                                |

| Fig. 3-23. Derived magnetic flux density waveforms comparison for case II                                           |

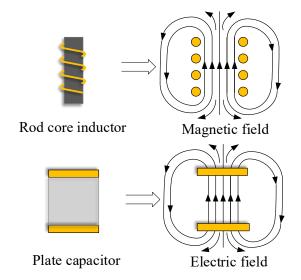

| Fig. 3-24. The analogy between the electric field of plate capacitors and the magnetic field of rod core inductors. |

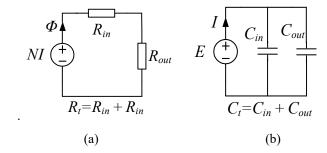

| Fig. 3-25. The duality between: (a). magnetic circuits, (b). electrical circuits                                    |

| Fig. 3-26. Leakage modeling comparison with two rod core inductance models                                          |

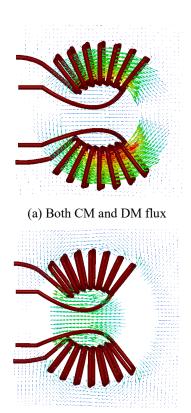

| Fig. 3-27. Magnetic fields of two-phase CM choke (hiding toroidal core)                                             |

| Fig. 3-28. The analogy of magnetic fields and electric fields for a CM choke with a large turns number.             |

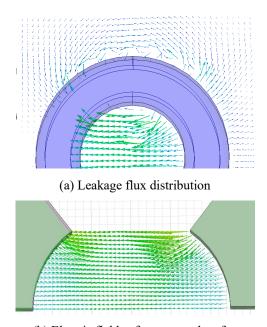

| Fig. 3-29. Geometry equivalent transformation from curved faces to folded planes                                    |

| Fig. 3-30. Electric filed for non-parallel planes in polar coordinates                                              |

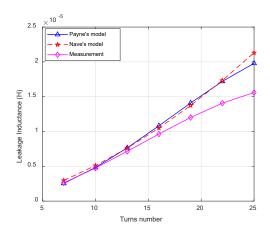

| Fig. 3-31. Comparison of leakage inductance models with FEM simulation results for magnetic core ZW43610TC.         |

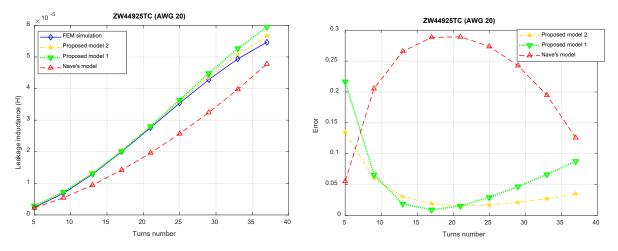

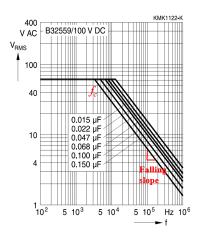

| Fig. 3-32. Comparison of leakage inductance models with FEM simulation results for magnetic core ZW44925TC.         |

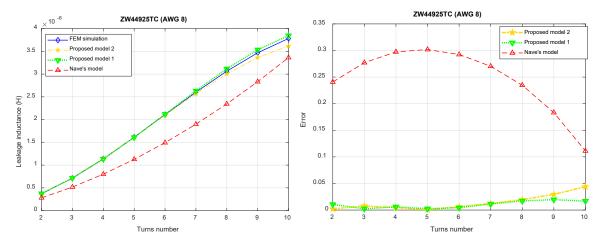

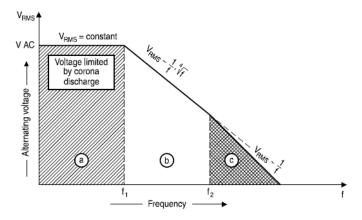

| Fig. 3-33. Limits for maximum ac RMS voltage with the operating frequency [139] 113                                 |

| Fig. 3-34. The typical ac voltage rating curves as a function of the frequency                                      |

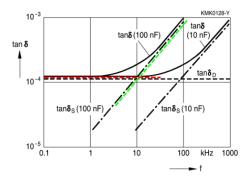

| Fig. 3-35. The measured dissipation factor as a function of the frequency in [139] 11                                                                                                                                                            | 5  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 3-36. The illustration of three cores bundled wires in [140]                                                                                                                                                                                | .7 |

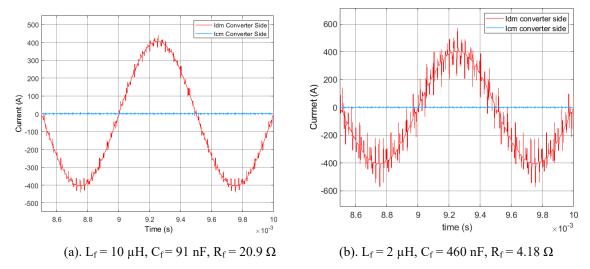

| Fig. 3-37. Converter ac side output current with different LC combinations when the corner frequency of $dv/dt$ filter is 166.7 kHz.                                                                                                             |    |

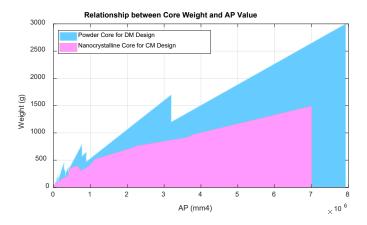

| Fig. 3-38. Relationship between core weight and AP value.                                                                                                                                                                                        | 20 |

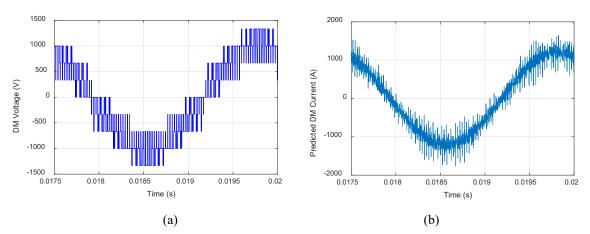

| Fig. 3-39. Output current prediction with phase PWM voltage: (a) PWM voltage of bridge output terminal, (b) predicted output current.                                                                                                            |    |

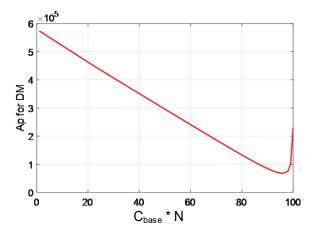

| Fig. 3-40. One optimization example for dv/dt inductor                                                                                                                                                                                           | 21 |

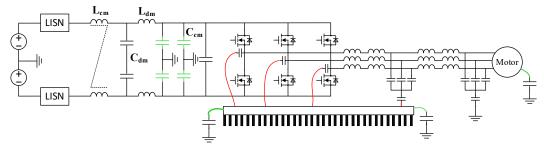

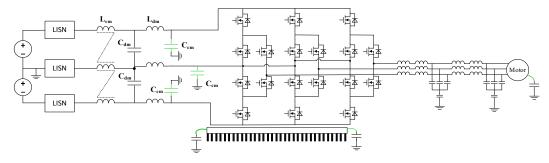

| Fig. 3-41. Two EMI configurations in this project.                                                                                                                                                                                               | 23 |

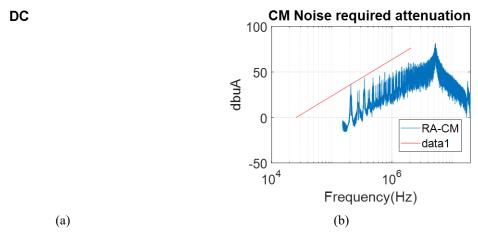

| Fig. 3-42. Corner frequency calculation based on bare noise, (a) dc side CM bare noise, (b) corner frequency determination based on required attenuation.                                                                                        |    |

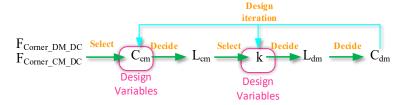

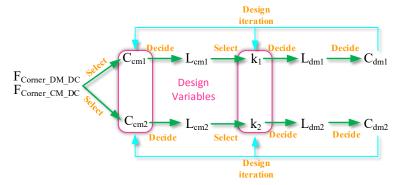

| Fig. 3-43. Design iteration of dc side EMI filter design                                                                                                                                                                                         | 25 |

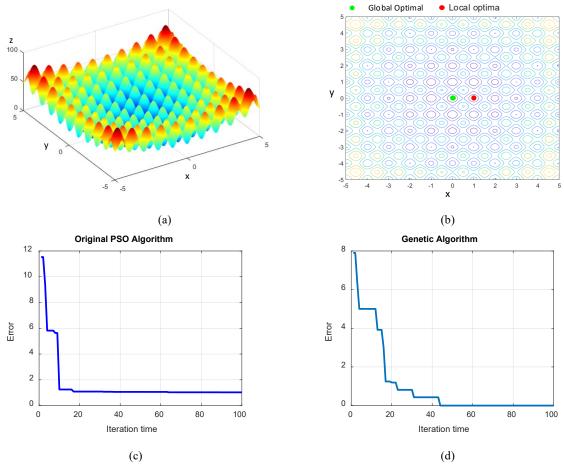

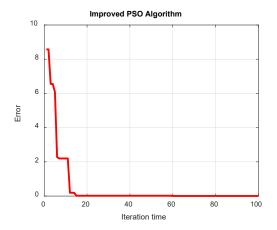

| Fig. 3-44. Verification of PSO and GA algorithm with a strong non-linear function: (a) plot of the non-linear function with two variables, (b) contour plot of x-y plane, (c) iteration convergence with PSO, (d) iteration convergence with GA. | th |

| Fig. 3-45. Verification of the improved PSO algorithm.                                                                                                                                                                                           | 27 |

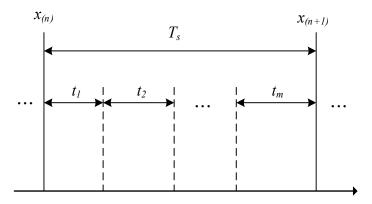

| Fig. 4-1. The illustration of <i>M</i> modes in one switching cycle for discrete-time modeling 13                                                                                                                                                | 3  |

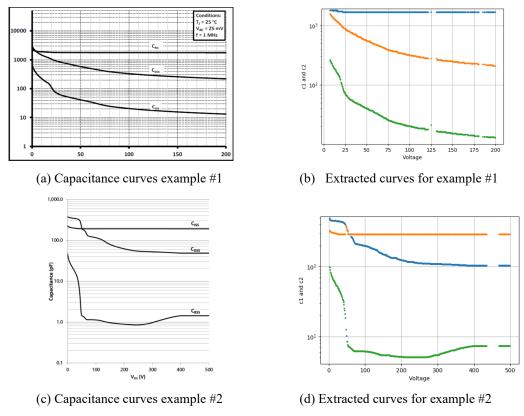

| Fig. 4-2. Automatic extraction of capacitance curves                                                                                                                                                                                             | ;4 |

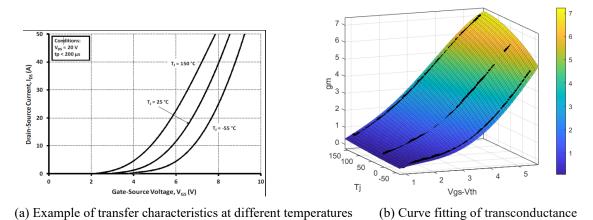

| Fig. 4-3. Curve fitting results of transconductance as a function of junction temperature 13                                                                                                                                                     | 34 |

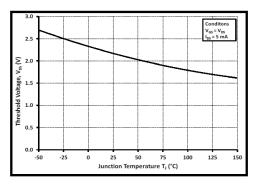

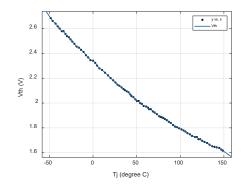

| Fig. 4-4. Curve fitting results of threshold voltage as a function of junction temperature 13                                                                                                                                                    | 5  |

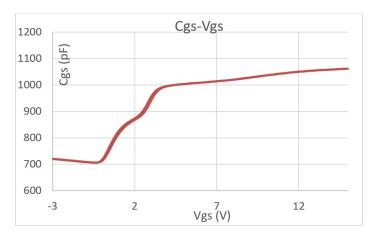

| Fig. 4-5. The characterization results of $C_{gs}$ as a function of $v_{gs}$ .                                                                                                                                                                   | 5  |

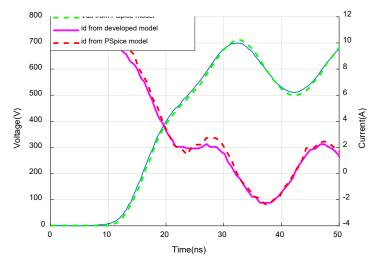

| Fig. 4-6. Waveform comparison between the developed model and PSpice model                                                                                                                                                                       | 6  |

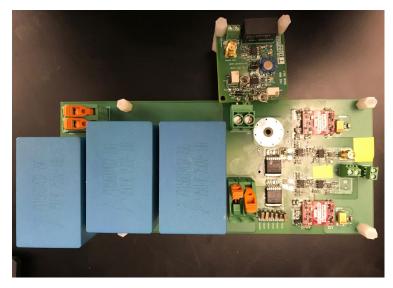

| Fig. 4-7. Prototype of DPT platform for SiC MOSFET C3M0065090J                                                                                                                                                                                   | ;7 |

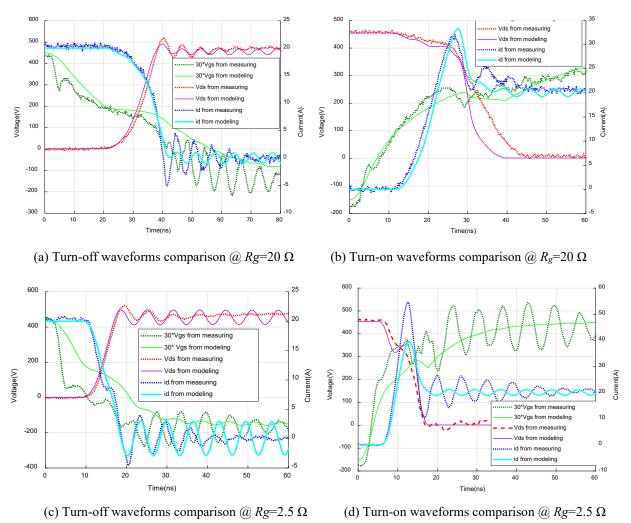

| Fig. 4-8. Waveform comparison at the testing condition of 450 V and 20 A with different gar resistances.                                                                                                                                         |    |

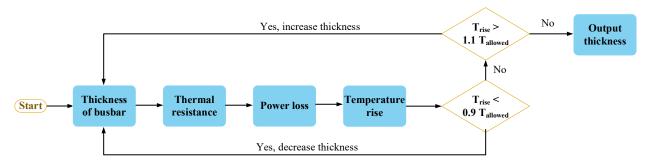

| Fig. 4-9. Design iteration for busbar thickness selection.                                                                                                                                                                                       | 1  |

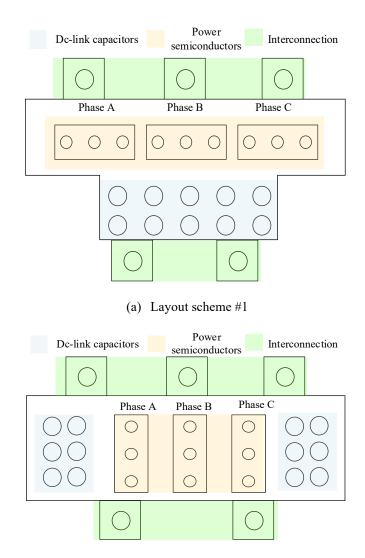

| Fig. 4-10. One example of predefined two-level voltage source inverter layouts                        |

|-------------------------------------------------------------------------------------------------------|

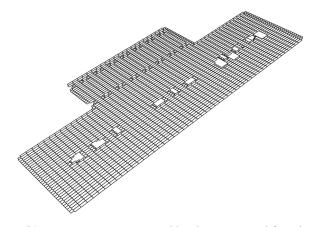

| Fig. 4-11. Example of automatically created geometry with geometry description script language        |

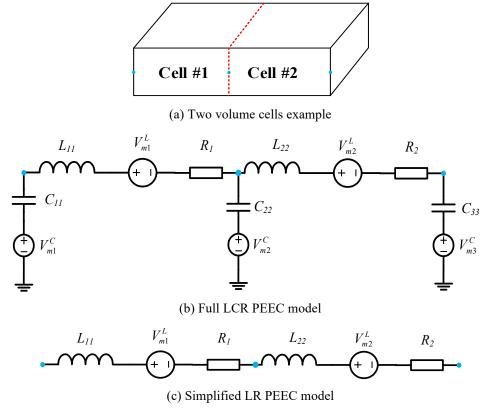

| Fig. 4-12. Example of PEEC model for two volume cells                                                 |

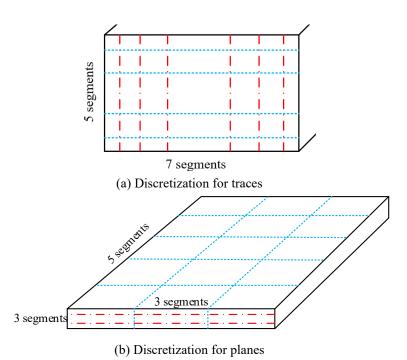

| Fig. 4-13. Discretization schemes for different geometries.                                           |

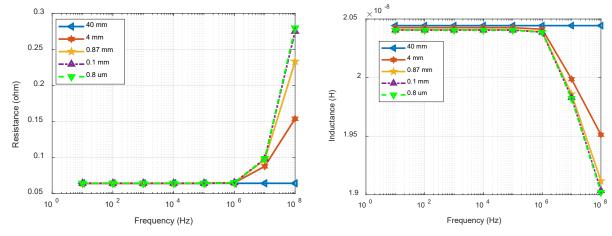

| Fig. 4-14. Impedance matrix as a function of frequency with different discretization resolutions  152 |

| Fig. 4-15. Relative error as a function of frequency compared to 0.8 um discretization results. 152   |

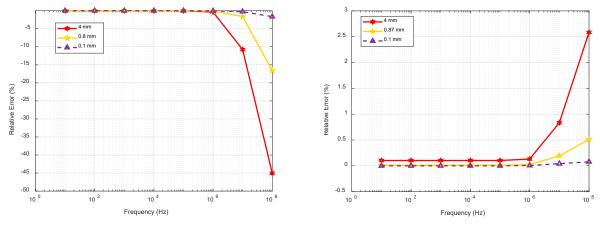

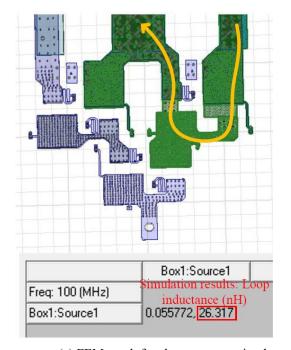

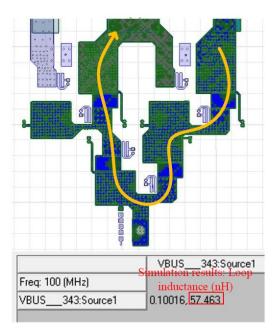

| Fig. 4-16. Extracted inductance value comparison of ANPC layout between FEM and PEEC. 154             |

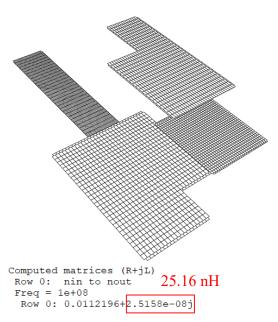

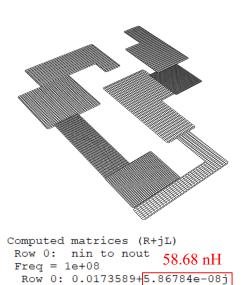

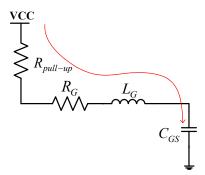

| Fig. 4-17. Extracted inductance value comparison of the laminated busbar between FEM and PEEC         |

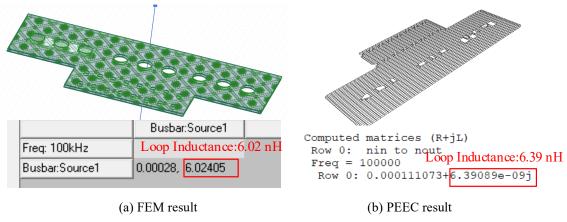

| Fig. 4-18. Equivalent circuits for gate drive during turn-on transient                                |

| Fig. 4-19. Diagram of the determination of turn-off gate resistance considering <i>di/dt</i>          |

| Fig. 4-20. Malfunction of gate drive due to high $dv/dt$ event.                                       |

| Fig. 4-21. Diagram of the determination of turn-on gate resistance considering <i>dv/dt</i>           |

| Fig. 4-22. Automatically created power loop layout for design example with C3M0065090J 163            |

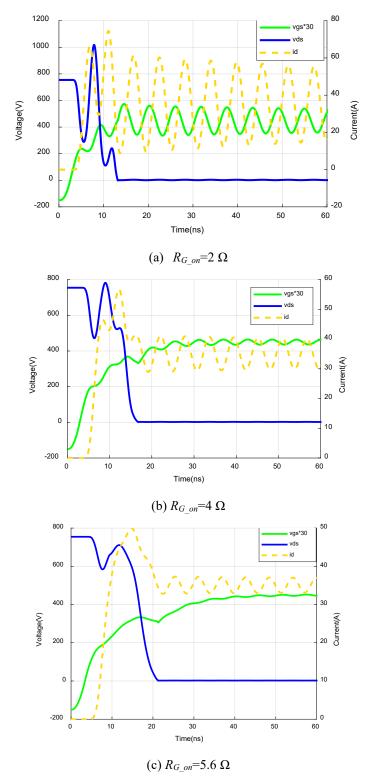

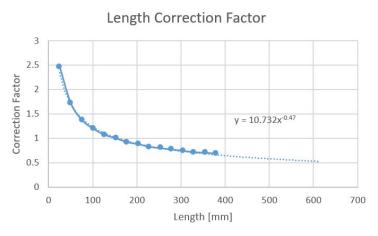

| Fig. 4-23. Switching waveforms and $v_{gs}$ comparison with different gate resistances                |

| Fig. 4-24. Switching waveforms and $v_{ds}$ comparison with different gate resistances                |

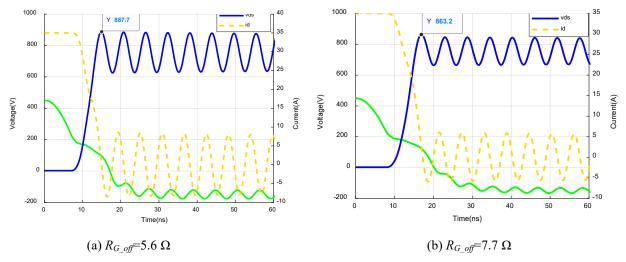

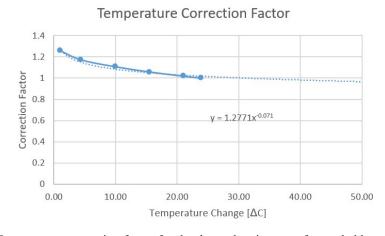

| Fig. 5-1. Length correction factor for the thermal resistance of extruded heatsinks                   |

| Fig. 5-2. Temperature correction factor for the thermal resistance of extruded heatsinks 167          |

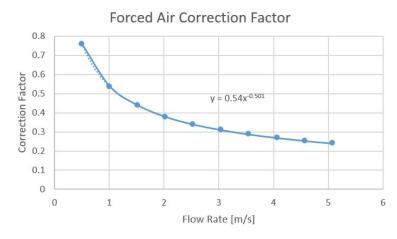

| Fig. 5-3. Forced air correction factor for the thermal resistance of extruded heatsinks               |

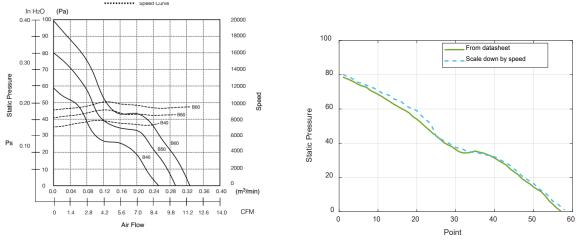

| Fig. 5-4. Pressure drop curves scaling with the law of fans                                           |

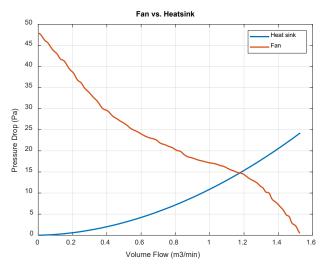

| Fig. 5-5. Operating condition determination with pressure drop curves of selected heatsink and fan    |

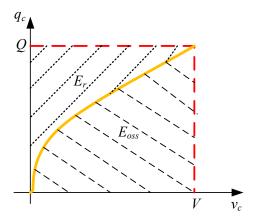

| Fig. 5-6. Loss related to the non-linear canacitance during charging and discharging.                 |

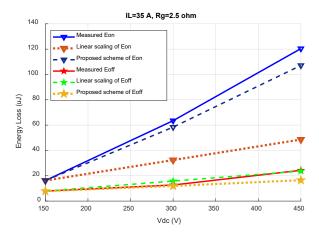

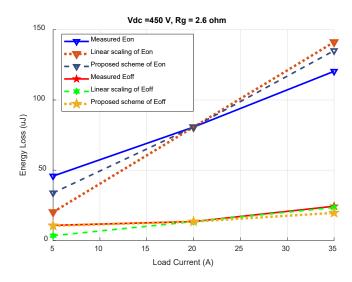

| Fig. 5-7. Switching loss scaling at different testing voltages.                                                                                                | 174    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

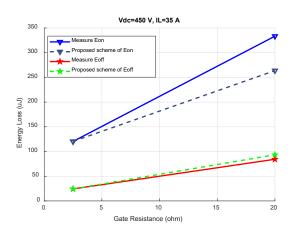

| Fig. 5-8. Switching loss scaling at different testing currents.                                                                                                | 175    |

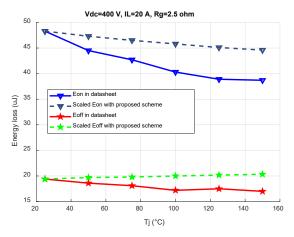

| Fig. 5-9. Switching loss scaling at different gate resistances.                                                                                                | 176    |

| Fig. 5-10. Switching loss scaling at different junction temperatures.                                                                                          | 176    |

| Fig. 5-11. Flow chart of device selection and cooling design.                                                                                                  | 179    |

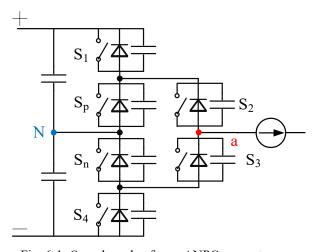

| Fig. 6-1. One phase-leg for an ANPC converter.                                                                                                                 | 183    |

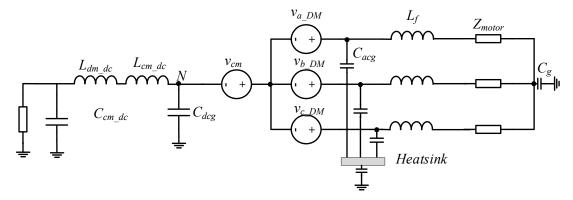

| Fig. 6-2. General equivalent circuits for ac outputs of three-phase converter systems                                                                          | 184    |

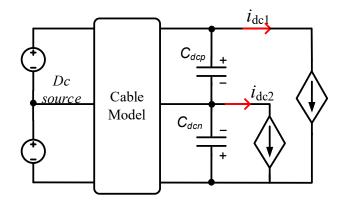

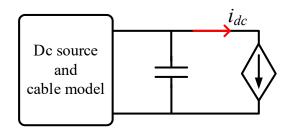

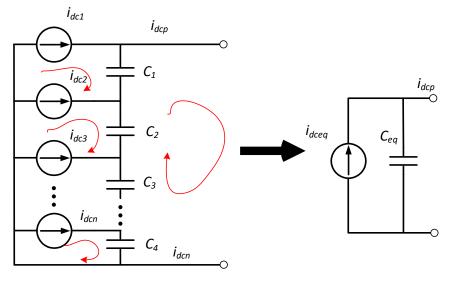

| Fig. 6-3. Dc input side equivalent circuits for ANPC converter.                                                                                                | 185    |

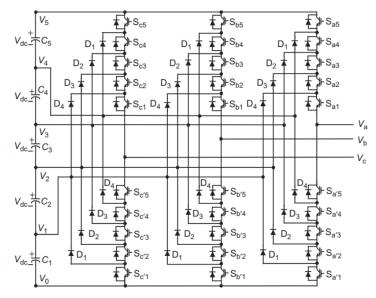

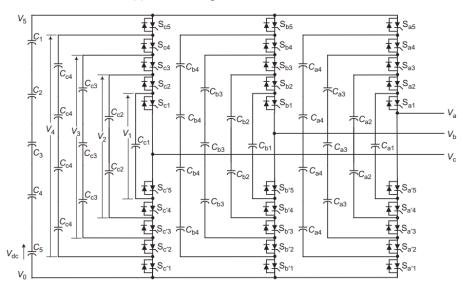

| Fig. 6-4. Two multi-level topologies for a three-phase converter system in [153]                                                                               | 186    |

| Fig. 6-5. General dc side equivalent circuits for multi-level converters.                                                                                      | 187    |

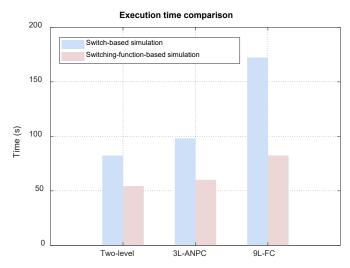

| Fig. 6-6. Simulation time comparison for three topologies.                                                                                                     | 189    |

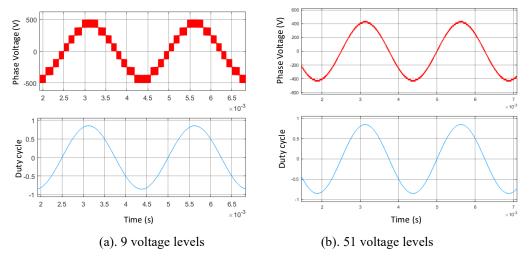

| Fig. 6-7. Phase voltage synthesis for multi-level converters.                                                                                                  | 190    |

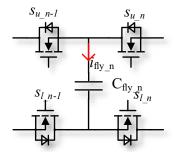

| Fig. 6-8. Switching cell in flying capacitor clamped topology                                                                                                  | 191    |

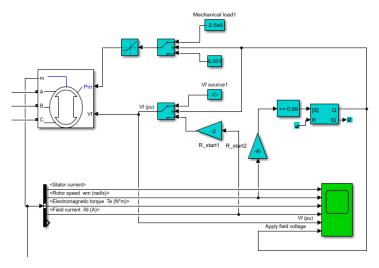

| Fig. 6-9. Open-loop scheme for starting a synchronous machine                                                                                                  | 193    |

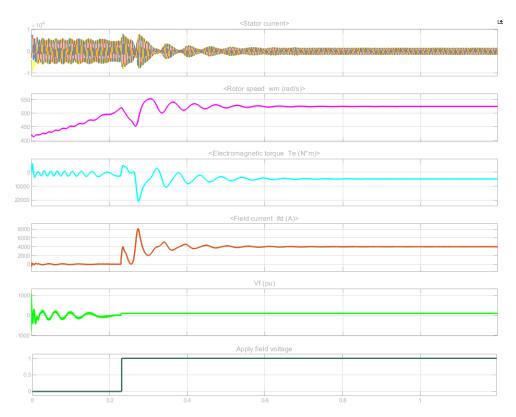

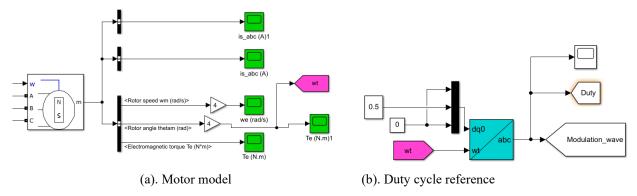

| Fig. 6-10. Synchronous machine open-loop simulation waveforms                                                                                                  | 193    |

| Fig. 6-11. THD evaluation with steady-state operating waveforms in the open-loop simulation with steady-state operating waveforms in the open-loop simulation. | ation. |

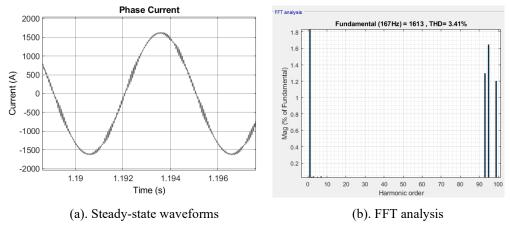

|                                                                                                                                                                | 194    |

| Fig. 6-12. Open-loop scheme for starting a permanent magnet synchronous machine                                                                                | 195    |

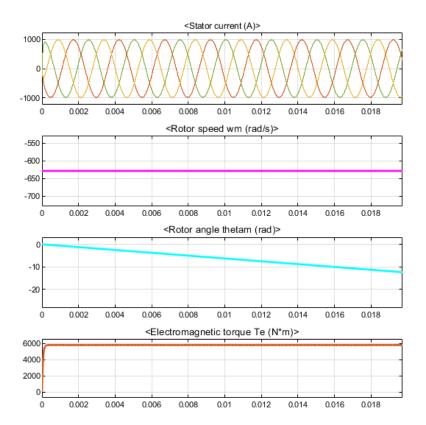

| Fig. 6-13. PMSM open-loop simulation waveforms.                                                                                                                | 195    |

| Fig. 6-14. Design diagram for the whole converter.                                                                                                             | 197    |

| Fig. 6-15. System-level iteration diagram.                                                                                                                     | 197    |

| Fig. 6-16. Power architecture of the motor drive controller.                                                                                                   | 198    |

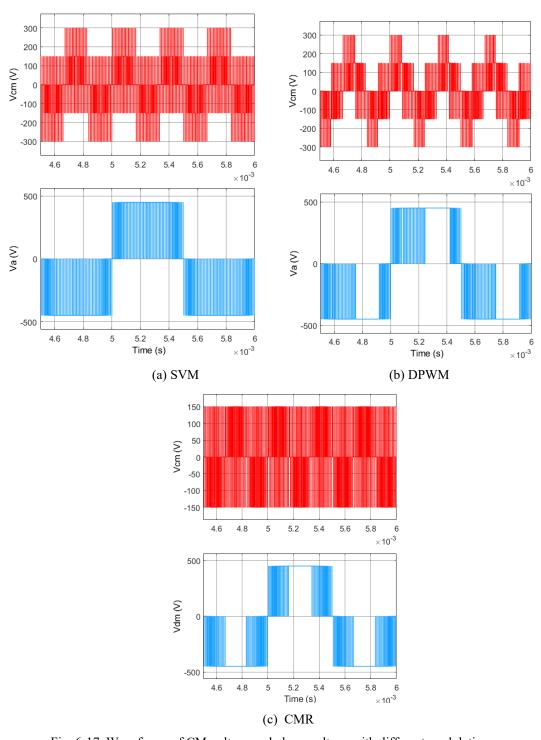

| Fig. 6-17. Waveforms of CM voltage and phase voltage with different modulations                                                                                | 200    |

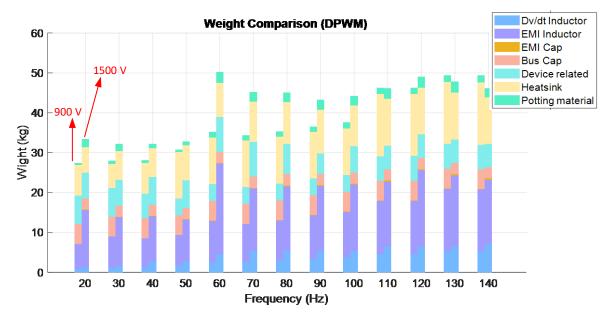

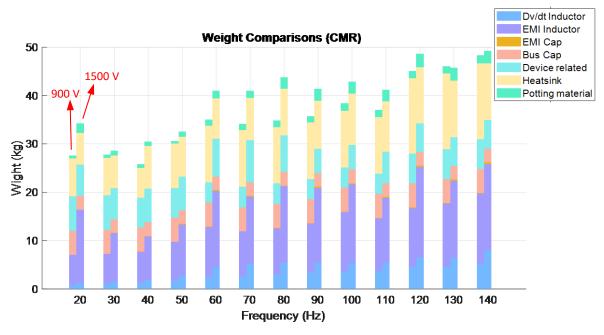

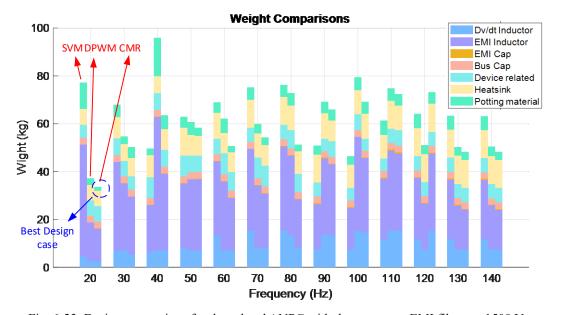

| Fig. 6-18. Design results for three-level ANPC with SVM and single-stage EMI filter                                                                            | 201    |

| Fig. 6-19. Design results for three-level ANPC with DPWM and single-stage EMI filter           | . 202 |

|------------------------------------------------------------------------------------------------|-------|

| Fig. 6-20. Design results for three-level ANPC with CMR and single-stage EMI filter            | . 202 |

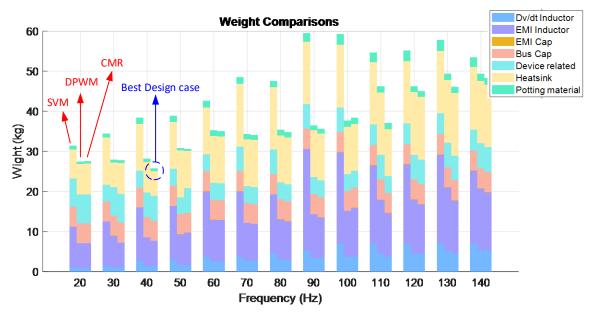

| Fig. 6-21. Design comparison for three-level ANPC with the single-stage EMI filter at 90       | 00 V. |

|                                                                                                | . 203 |

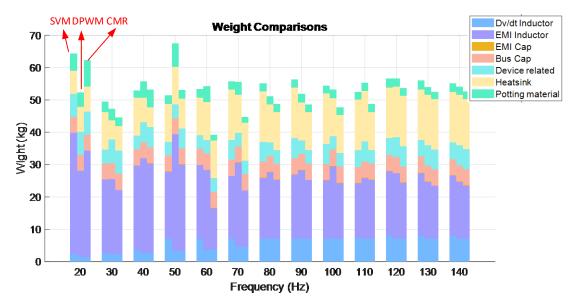

| Fig. 6-22. Design comparison for three-level ANPC with the two-stage EMI filters at 900 V.     | 204   |

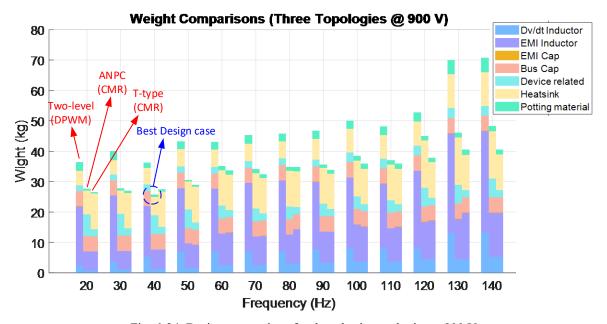

| Fig. 6-23. Design comparison for three-level ANPC with the two-stage EMI filters at 150        | 00 V. |

|                                                                                                | . 204 |

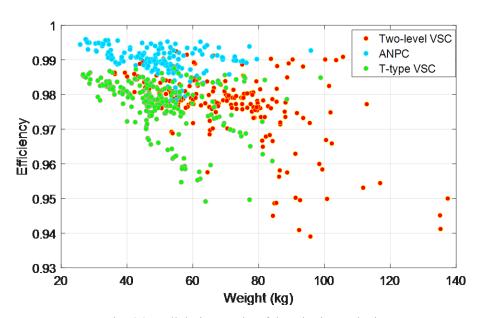

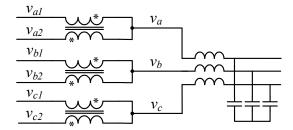

| Fig. 6-24. Design comparison for three basic topologies at 900 V                               | . 206 |

| Fig. 6-25. All design results of three basic topologies.                                       | . 206 |

| Fig. 6-26. The configuration of coupled inductors in two paralleled converters                 | . 208 |

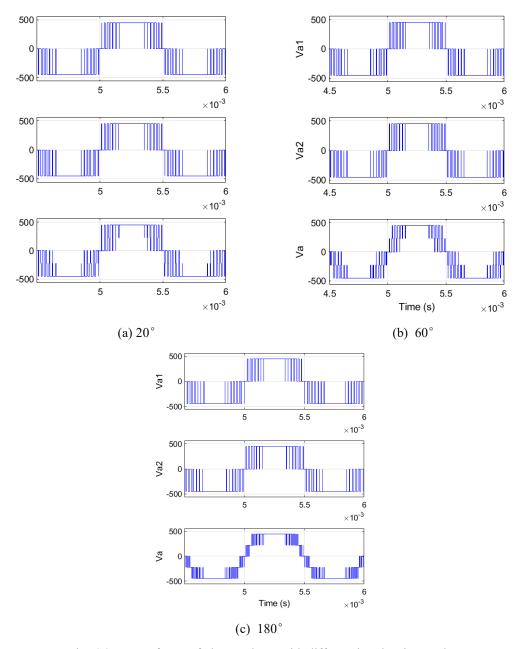

| Fig. 6-27. Waveforms of phase voltage with different interleaving angles                       | . 209 |

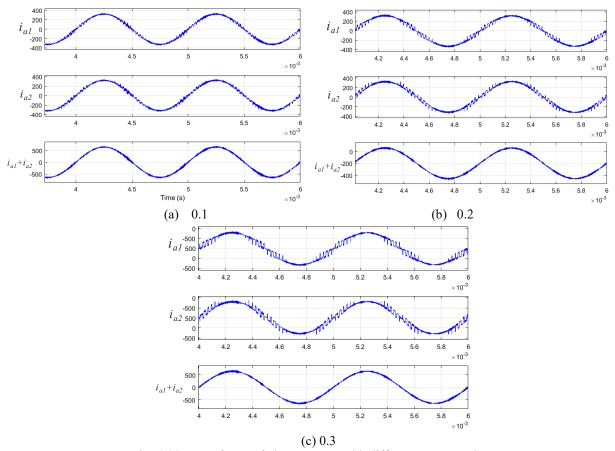

| Fig. 6-28. Waveforms of phase current with different current ratios.                           | . 210 |

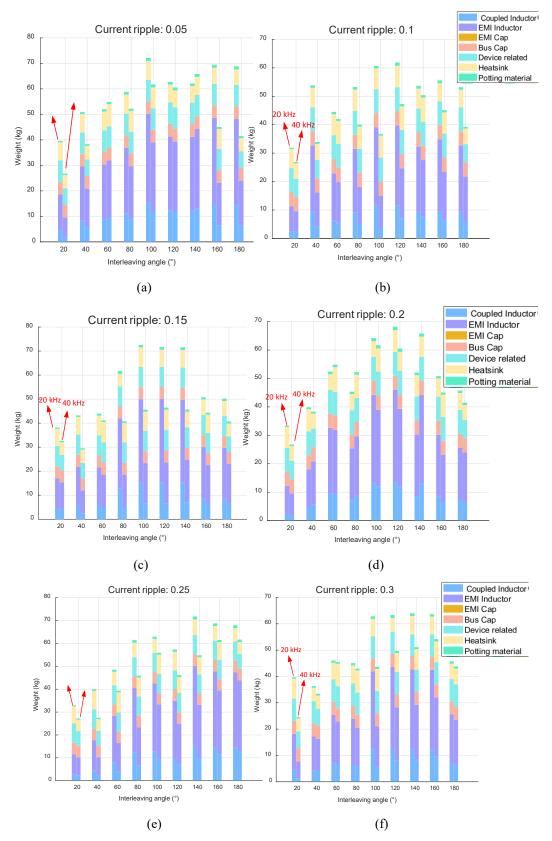

| Fig. 6-29. Design results of two paralleled ANPC converters with different interleaving angles | s and |

| circulating current ratios.                                                                    | . 212 |

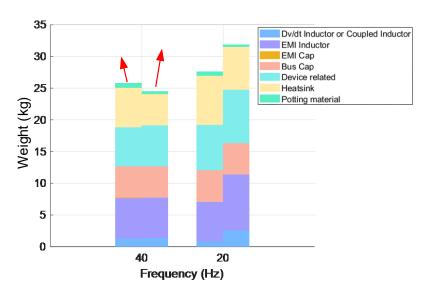

| Fig. 6-30. Design Comparison between the single converter and two paralleled converters        | . 213 |

| Fig. 7-1. MVC architecture based software framework.                                           | . 215 |

| Fig. 7-2. Design configurations provided by the developed software.                            | . 217 |

| Fig. 7-3. Load configurations in the developed software.                                       | . 219 |

| Fig. 7-4. Design parameters save and load function in the developed software                   | . 219 |

| Fig. 7-5. Database management in the developed software                                        | . 220 |

| Fig. 7-6. Design visualization functions for the developed software.                           | . 222 |

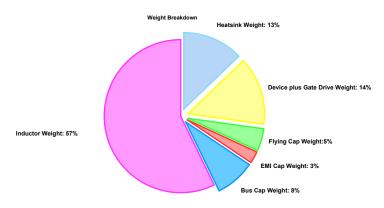

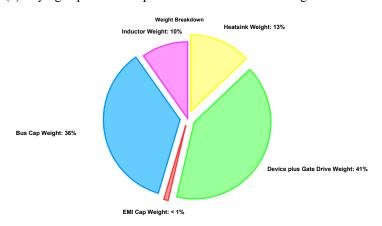

| Fig. 7-7. Weight breakdown for a single converter design result                                | . 222 |

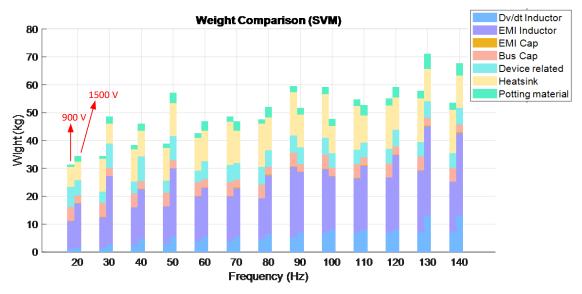

| Fig. 7-8. Weight comparison at different switching frequencies                                 | . 223 |

| Fig. 7-9. Detail design results and the selected component information.                        | . 223 |

#### **Chapter One**

#### Introduction

Transportation electrification becomes an irreversible trend to cope with the petroleum-based energy crisis and environmental pollution issues. Based on U.S. Energy Information Administration, transportation consumed energy is the second largest part, which is only lower than electric power consumption, and 93% of the consumed energy in transportation is from petroleum [1]. Hence, there is a huge and long-term opportunity while the transportation electrification revolution is underway, and there will be remarkable environmental and economic benefits for industry as well as new challenges and research topics for academia. In this context, the power electronics converter system, as an interface between the electrical power and power take-off unit (motor drives in most cases), will make major contributions to overcome the most urgent challenges in the process of transportation electrification.

In this chapter, the more electric aircraft (MEA), as the target application, is investigated to show requirements for the design of the power electronics converter system. The main target for the converter system in MEA is to achieve the lightest weight considering fuel economy. Furthermore, it is discussed what are the challenges and motivations for the design of power electronics converters at MEA applications. Eventually, a Model-Data-Optimization (MDO) framework is proposed to help develop such a design software to reduce the gap between the paper design and implementations and to improve the design efficiency.

#### 1.1 Application Background

More electric aircraft (MEA) employ an increasing amount of electric power in the place of hydraulic, pneumatic, and mechanical power. The purpose of proposing the concept of MEA is to

further improve the efficiency, to reduce the fuel-cost and CO<sub>2</sub> emissions [2], and to reduce the weight by replacing heavy hydraulic, pneumatic, and mechanical driven equipment. According to the report from military aircraft studies [3], MEA technologies will help realize a 5.4% increase in average flying time between failures and a 6.5% decrease in the total aircraft weight.

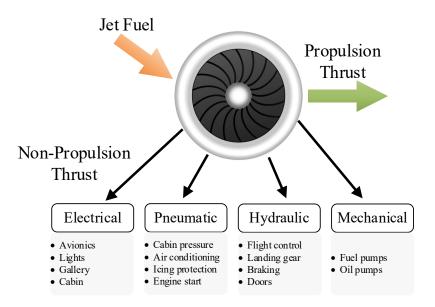

As shown in Fig. 1-1, the power created by turbines in conventional aircraft (e.g., A330) can be divided into a propulsive part and a non-propulsive part [4]. Electrical power only takes a very small portion of non-propulsive power for non-critical equipment and loads such as lights, cabin, and avionics. Most important functions like flight control and fuel pumping are realized by hydraulic and mechanical power from the main turbines. However, the hydraulic and mechanical drive equipment is typically heavy, inflexible, and requires regular maintenance [5]. Also, due to the requirement of the high reliability for aircraft, back-up hydraulic equipment for the flight control is installed in conventional aircraft. Hence, one main intention of the MEA concept is to replace the hydraulic actuators with motors [6].

Fig. 1-1. Power consumption distribution for non-propulsive applications in conventional aircraft.

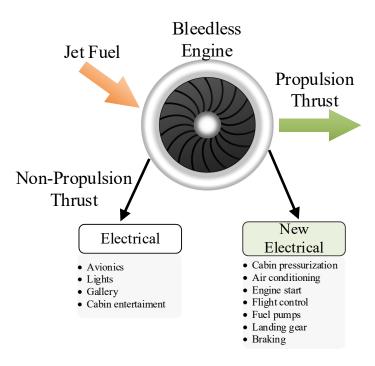

Fig. 1-2. Power consumption distribution for non-propulsive applications in the MEA

To fully take advantage of the MEA concept, Fig. 1-2 shows a new mapping of non-propulsive power, and the most critical equipment is electrically powered. Moreover, to further improve the engine efficiency, a bleedless engine is applied instead of a bleed air engine [7]. Without bleed air, however, the aircraft requires a new environmental control system (ECS) for cabin pressurization, air conditioning, and icing protection. All these changes have led to significantly increased use of power converters and electric drives for this application, and power electronics converters design begins to play a key role in the design stage of MEA, and the high power density (weight based) of the converter system is the most desirable objective for fuel economy.

Moreover, power system architecture in MEA is still under development, and different schemes with different dc-link voltages and ac grid frequencies are proposed. The mechanical gearbox between turbines and generators are eliminated for high power generating efficiency. This, however, results in a varied line frequency (360 Hz – 800 Hz) compared with the constant main

frequency of 400 Hz [8]. Also, many voltage levels exist in different aviation power architectures. For dc grid, 28 V, 270 V, 540 V, 900 V, 1000 V, 1500 V, 2400 V, and 7500 V are all considered as candidates while, for the ac grid, 115 V and 230 V from 360 Hz to 800 Hz are mainly considered [9]. As a result, to have a better understanding of how these parameters impact the system weight and performance, several benchmark design works need to be conducted for detailed comparisons.

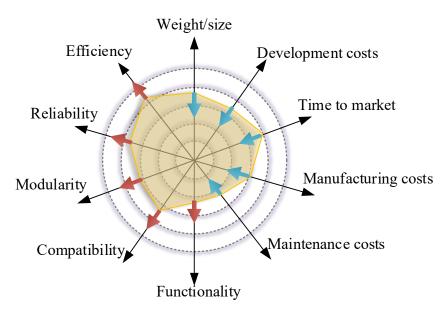

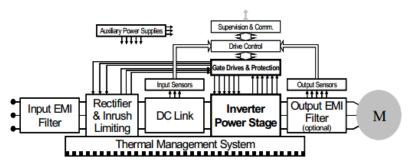

On the other hand, since the power capacity in MEA is going to much higher (Airbus A330, 300 kVA; A380, 600 kVA; Boeing 787, 1 MVA), more and more power electronics converters will be applied, and the performance of power electronics converters becomes critical to the whole system. As shown in Fig. 1-3, weight, development costs, time to market and other performance factors must be considered and optimized carefully in the design stage.

However, owing to the high complexity of power electronics design which requires knowledge from multi-physics domains, no commercial power electronics design tool is available for an accurate converter performance evaluation. Generally, a comprehensive converter design incorporates several engineers from electric, thermal, and mechanical areas, and it can take 6 months to one year to evaluate and compare different topologies, modulations, and other technologies for only one specific application. Moreover, even though a complete design result has been finished in the paper design, it could still take a long time to debug converters due to the gaps between the paper design and the implementations.

#### 1.2 Research Motivations and Challenges

Several factors contribute to the gaps between the paper design and implementations. First, the real performance of components diverges from the predicted performance due to inaccurate models. For example, the state-of-art core loss model IGSE is a curve-fitting model rather than an

Fig. 1-3. The performance factors of power electronics converters in the MEA applications.

analytical model, and it cannot have a good estimation of core losses when a dc bias exists. Also, the current leakage inductance model for common-mode inductors in the literature still has 30% errors in some cases compared with testing results [10].

Second, the conventional design approach has not considered the non-linear physics characteristics of power electronics components. The EMI noise prediction highly depends on the impedance of magnetic core inductors. However, the impedance of magnetic core inductors can be varied with the operating frequency and current bias.

Third, the conventional design approach has experience-based assumption and margin selection rather than the scientific or optimized ones. For example, the current ripple is usually assumed as 10-20% of the peak current. However, the current ripple has impacts on the inductance value, inductor loss, device loss, cooling design and EMI noise spectrum. Such an experience-

based rule to select inductance value is not scientific to get an overall optimal point for the whole converter system.

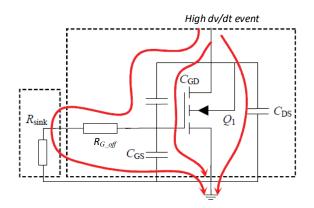

At last, the conventional design approach also is not capable of considering the interactions between the device switching behavior and the geometry of circuits, and a trial-and-error procedure is always required in the debugging stage. One example is how to select gate resistance which determines the switching speed. The switching speed affects both switching losses and switching frequency capabilities, and the faster switching speed is, the lower switching loss and higher switching frequency can be achieved. Moreover, the cooling design is also closely related to gate resistance selection due to its influence on the switches' loss. However, the gate resistance selection is generally decided by the allowed voltage spike during turn-off and is highly associated with the layout or geometry of PCB or busbar. As a result, it causes gaps between the paper design and testing results since the gate resistance selection is generally neglected in the paper design stage, and the impacts of these factors on the system-level converter performance are not included during the design. Hence, a trial-and-error procedure in the implementation step is carried out for debugging the converter. It is common to adjust gate resistance and redo the busbar or PCB layout in the debugging stage of the designed converter.

Furthermore, the power electronics converter design comprises numerous design variables and knowledge from several different fields such as electrical, thermal, mechanical, and magnetics, and it generally relies on the experience of engineers by fixing some design variables (like switching frequency, current ripple) and introducing some assumptions (e.g., constant inductance value and operating junction temperature). This traditional design procedure simplifies the design problem and provides a reasonable design point, but to verify, evaluate, and improve the converter performance with designed parameters, time-domain simulations need to be carried out for several

design iterations. As a result, this experience and simulation-based design procedure will lead to a good but not the optimal design. The optimal design is closely related to the objective function, and it can be selected as the minimum loss, lowest cost, smallest size, or lightest weight based on the application requirement in power electronics design. Also, the multi-objective function can be applied to determine the optimal design to achieve the balance between two or several design objectives, e.g., efficiency and cost, power density and efficiency.

The purpose of the dissertation is to develop a comprehensive, scientific and automated design approach for SiC-based power electronics converters for three-phase ac motor drive in MEA applications that shrinks the gaps between the paper design and real performance of implemented converters, and also enables the weight optimization to determine the lightest converter system scheme. By utilizing advanced analytical modeling, numerical modeling and data-driven based modeling methods, the developed approach will fully consider non-linear physics characteristics of power electronics components neglected by the traditional design approach. Also, an optimization algorithm will be applied to reduce trial-and-error efforts in the switching frequency selection, LC filter value determination and other experience-based selection of design variables, providing a near-optimal design margin or design rule for components. Another feature of the proposed design approach is to cover the design coupling between the parasitics and layout geometries in real circuits, impacting the allowed switching speed and gate resistance selection. The partial element equivalent circuit (PEEC) method combined with advanced device models will be used to establish a link between the switching speed and layout geometries, affording a switching speed optimization considering busbar layout and EMI performance. It is also expected that the design approach will realize the capability of automated design without the integration of the expensive and computationally intensive FEM simulation software.

In the following, the challenges of this work have been separated into three aspects: modeling, design approach and optimization, design automation.

#### 1.2.1 Modeling

The accurate models for power electronics components can effectively shrink the gaps between the paper design results and the implementation results. Also, with the advanced modeling, more non-linear physics characteristics and parasitics are considered in the paper design stage, further reducing the design gaps. The main challenges of modeling in power electronics design are:

- 1) Further to improve the accuracy of the modeling. Most models in power electronics have assumptions, and they can be applied only in some limited cases and ranges for acceptable errors, e.g., the leakage inductance model for toroidal common chokes and device loss model at different operating conditions.

- 2) Need to consider more non-linear physics characteristics of power electronics components. The inductance, capacitance and thermal resistance of heatsink are generally treated as constant values in power electronics design, but actually, they are not. For example, since the inductance highly depends on the current bias (magnetic field strength) and operating frequency, a time-varying inductor model should be developed considering the non-linear permeability model.

- 3) To solve the most difficult modeling problems by employing data-driven based modeling methods. The state-of-art core loss calculation method IGSE is still not accurate enough when the inductor has a dc-bias current. If a large amount of core loss data can be collected by measurements and simulations accurately, a data-driven based

method can be applied to train a multi-layer artificial neural network (ANN) based model.

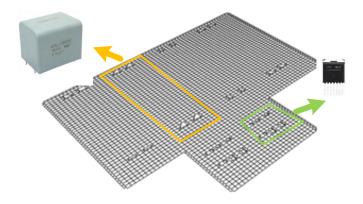

4) To effectively and efficiently model the geometry-related parasitics. Nowadays FEM software is widely applied for the extraction of parasitics for the busbar and PCB layout. However, it requires users to draw or import the 3-D geometry manually and the parasitics only can be estimated at the end of the layout work. A lightweight tool or algorithm needs to be developed for parasitic extraction in the paper design stage before the implementation stage, and the tool can help create near-optimal layout automatically with the selected power switches and dc-link capacitors. Thus, the parasitics of the created layout can be quickly evaluated, then the switching speed can be further determined for the switching loss calculation and cooling design.

#### 1.2.2 Design Approach and Optimization

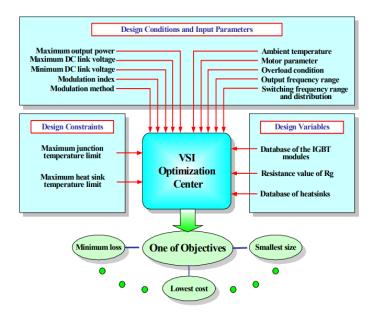

Optimization methodology compels engineers to design in a structured way. Based on Fig. 1-4, the optimization problem in power electronics can be formulated in the following way:

Minimize or maximize:

F(x) Objective function

Subject to:

g(x) < 0 inequality constraints

h(x)=m equality constraints

$1 \le x_i \le N$  integer constraints

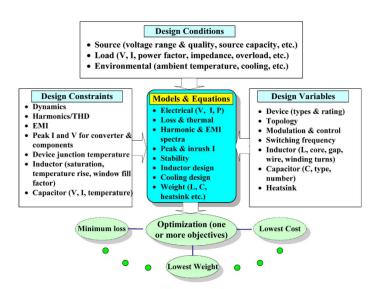

Fig. 1-4. A general view of design problem in power electronics in [11].

where

$$\mathbf{x} = \begin{cases} x_1 \\ x_2 \\ \cdot \\ \cdot \\ x_n \end{cases}$$

design variables

Objective function: This function describes what the goal of optimization is, and what the designer's requirement is. For power electronics, under global optimization, the objective function can be the lowest cost, lowest weight or highest efficiency. But under a partial optimization case, for a specific trade-off design, the objective function can also be the lowest harmonics, lowest CM voltage and so on.

One feature for objective function is that it can only have one target. If there is more than one objective, it is essential to assign a weight for each objective and sum up to one objective function by using weighting coefficients.

Constraints: The calculation of the objective function should be conducted under some given constraints. Usually, it includes three parts: inequality constraints, equality constraints and integer constraints. Inequality constraints and equality constraints are used to describe some design requirements. For example, one inequality constraint in power electronics design is that converter noise should be lower than the EMI standard while one equality constraint in power electronics design is that the working junction temperature of power devices is 150 °C. Integer constraints is a physical limitation for some components, like turns number, and it must be an integer during the optimization procedure.

Design variable: This is the most straightforward part of one optimization procedure. In power electronics, if selecting the design variables from the bottom level, it will be hundreds of variables like turns number, core material, core shape, core dimensions, device type, capacitor type, etc. Another important remark is some design variables in power electronics are discrete variables rather than continuous variables, such as turns number or device type. Therefore, the optimization algorithms should be selected carefully to adapt to discrete variables.

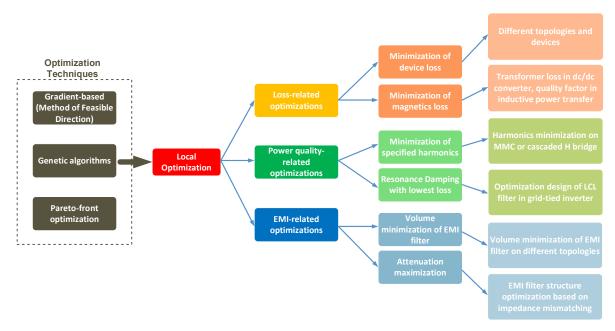

However, most design approaches only focus on one function block of power electronics converters, such as the minimum harmonics, the minimum EMI filter volume, the minimum power switches' loss, the lightest heatsink design and so on, rather than the whole system-level performance. In this work, the objective of the design is to achieve the lightest weight design for the whole power electronics system including all function blocks in the motor drive applications. The efficiency of the converter system is also important, but it will not be added to the objective function. Instead, a minimum efficiency requirement will be applied in the design contains to exclude low-efficiency design cases. The main challenges of the design approach and optimization in this work are:

- 1) Try to avoid experience-oriented design rules and margin selections which helps to get a reasonable design but not an optimal design. For example, for a given corner frequency of one single-stage LC filter in EMI design, how to distribute L and C is a design trade-off. Usually, designers try to use the largest capacitance value and the smallest inductance value to achieve the minimum volume or weight. Nonetheless, the smallest inductance does not equal the minimum weight since the high current ripple can lead to a high core loss, which may increase the core size and weight. There should be a design optimization to solve design trade-offs more scientifically.

- 2) Consider additional impact factors on the realistic converter performance that previously have been neglected. In the conventional approach, to simplify the design, some assumptions are made for quick evaluation, but it indeed leads to a non-optimized design. For example, the pressure drops of heatsink and fan should be considered for the cooling design. The impact of the gate resistance selection on switching loss and voltage spike should also be considered.

- 3) How to accelerate the simulation speed for the design? Power electronics design requires many raw data of operating waveforms for the design of components. An investigation of the simplified and fast simulation scheme is necessary to improve the efficiency of the design tool.

- 4) How to formulate the power electronics design problems and to apply the optimization algorithms in the power electronics design? Brute force may not be efficient enough for the power electronics design.

#### 1.2.3 Design Automation

Design automation is one of the most desirable features for a design tool, and it requires the incorporation of multiple software from different physics domains. To reduce manual interventions, the interfaces among multiple software need to be developed and tested. The main challenges of design automation in this work are:

- 1) Build databases for all power electronics components. The program can easily read and write the data in each database with a simple and friendly interface.

- 2) Establish the communication link among multiple software for the multi-physics design. However, another way is to apply self-developed lightweight algorithms or functions to replace large scale software that only part of functions is used for the design.

- 3) Develop a friendly user interface to do the configuration of design parameters, the management of design results and database.

- 4) Develop the visualization function to better display the design results.

#### 1.3 Proposed Model-Data-Optimization Framework for Power Electronics Design

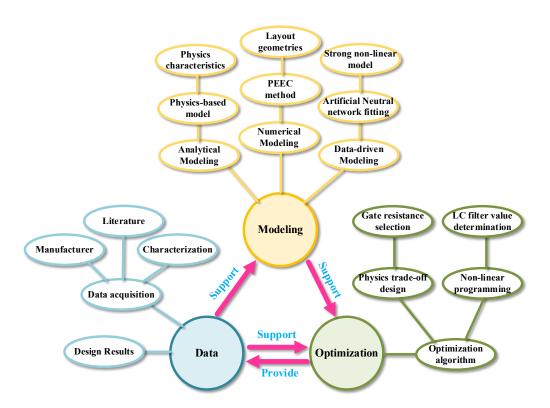

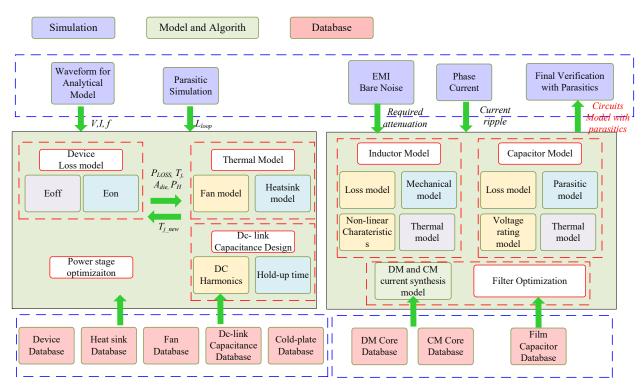

MDO based strategy is proposed to develop the design tool. As shown in Fig. 1-5, MDO stands for modeling, data, and optimization. MDO separates the design approach into three aspects: establishing models, acquiring data, applying optimization algorithm. All three aspects are combined to reduce the experience-based design procedure and unscientific design margins selection and to include unconsidered physics characteristics in the current design method.

Three modeling techniques are adopted for the modeling part. Analytical modeling and curve fitting modeling are applied for most models for fast calculation with acceptable error. Data-driven

based modeling is used for the strong non-linear models like the core loss model and the leakage inductance model. Numerical modeling is adopted for the estimation of parasitics of the geometry-related structure of the busbar or the layout of the power loop. In this work, numerical modeling does not rely on the commercial FEM software like Ansys since it is so heavy and bulky with integrating too many functions, and only a few functions are really valuable for power electronics users. Instead, a lightweight partial element equivalent circuits (PEEC) based numerical modeling method is implemented to calculate the self and mutual inductance of different mechanical structures.

Data acquisition provides three functions in the design tool. First, through the data collection from datasheet provided by manufacturers, databases with all required parameters for power

Fig. 1-5. MOD framework for the development of the design tool for three-phase ac motor drive applications.

electronics components are established as the design inputs of the physical design of each component. Second, collecting the data from the characterization, measurements, simulations can be used for training ANN-based models to solve the most difficult and strong non-linear models in the power electronics area. Third, the design results can also be collected to create and train an expert system to predict the system performance without going through the detailed design procedure. Also, the created expert system could give design recommendations in terms of topologies, modulations, switching frequencies, and EMI filter structures only based on the specifications of converters.

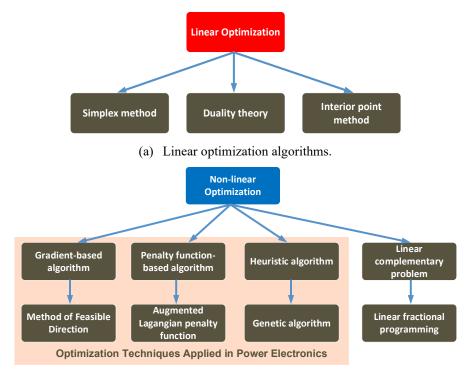

Non-linear optimization algorithms and design strategies are applied for different kinds of trade-off problems in the power electronics design. Population-based searching algorithms like particle swarm optimization (PSO) and genetic algorithm (GA) are appropriate to discrete type design variables, non-linear and non-convex design problems in power electronics design.

#### 1.4 Dissertation Layout

This dissertation is organized as follows:

The state-of-art research on the modeling and design optimizations of power electronics are reviewed in Chapter 2, and the research gaps are summarized.

Chapter 3 presents two filter design optimization schemes for different filters. For ac side dv/dt filters, a weight optimization with Ap prediction is applied. For EMI filters, a design optimization scheme combined with the modeling of non-linear characteristics of magnetic core inductors and the improved PSO algorithm is proposed. The frequency-dependent permeability of nanocrystalline cores and the current-bias-dependent permeability of powder cores are covered in the design, and their impacts on the filter performance are studied. Furthermore, a new perspective

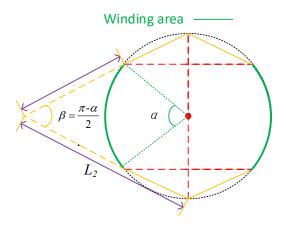

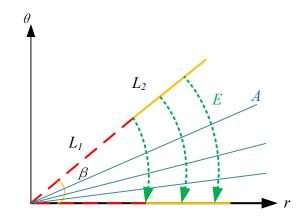

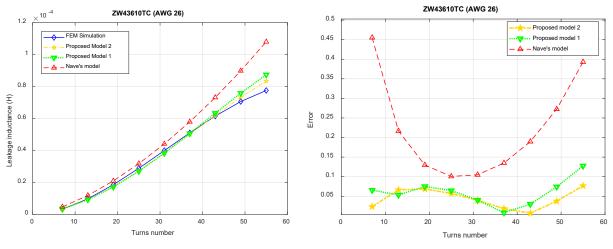

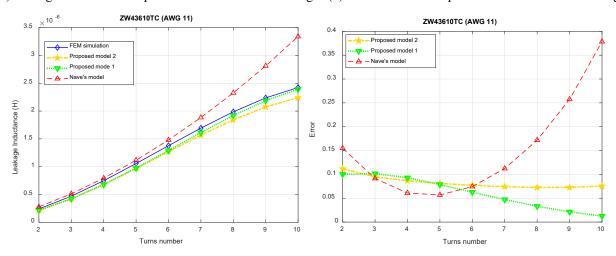

of the leakage inductor modeling through the analogy between reluctance and capacitance is applied to improve the accuracy of the leakage inductance modeling of toroidal cores.

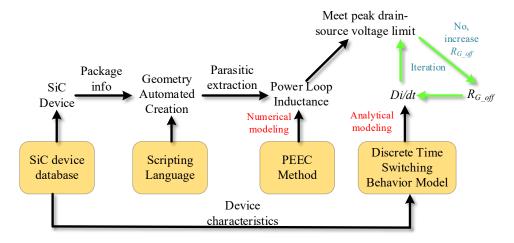

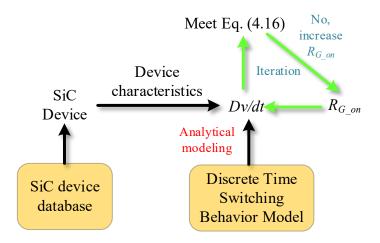

Chapter 4 proposes a device selection scheme considering the practical layout and switching speed. A discrete-time switching behavior model is developed to predict the switching speed at different operating conditions and gate resistances, and an automatic geometry creation program is implemented with PEEC numerical modeling method to estimate the practical parasitic inductance of the busbar or PCB layout with the selected power devices. With the estimated parasitics, the gate resistance can be determined by the proper switching speed to avoid overvoltage and crosstalk issues.

Chapter 5 develops a cooling optimization scheme with more practical constraints. First, the pressure drops of heatsink and fans are modeled and considered to decide the airflow speed of the selected fan and the corresponding thermal resistance of the selected heatsink. Second, to obtain more accurate switching loss data, a multi-variable switching loss scaling method is proposed to incorporate more practical parameters including the gate resistance, the operating junction temperature. At last, a complete design iteration covering device selection optimization and cooling design is given.

Chapter 6 studies system-level iteration and optimization in terms of the selection of the switching frequency, modulation scheme, and topology. To accelerate the design iterations, a switching function based simulation scheme is presented for the three-phase inverter system, and current synthesis with switching functions is also given as inputs for the design of power electronics components. Moreover, the design algorithm for the paralleled converters is presented. Two extra design variables including the coupling inductance and interleaving angle are included to search the lowest system weight of two paralleled converters.

Chapter 7 presents the development of software that integrates all the design models and algorithms proposed in the dissertation. The developed software provides multiple functionalities covering the design configuration, database management, and design results visualization.

Chapter 8 summarizes the research work and contributions presented in this dissertation and discusses future work.

# **Chapter Two**