### University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

**Graduate School**

8-2021

# Toward Reliable and Efficient Message Passing Software for HPC Systems: Fault Tolerance and Vector Extension

Dong Zhong dzhong@vols.utk.edu

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

Part of the Computer and Systems Architecture Commons, Digital Communications and Networking Commons, and the Hardware Systems Commons

#### **Recommended Citation**

Zhong, Dong, "Toward Reliable and Efficient Message Passing Software for HPC Systems: Fault Tolerance and Vector Extension. " PhD diss., University of Tennessee, 2021. https://trace.tennessee.edu/utk\_graddiss/6500

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Dong Zhong entitled "Toward Reliable and Efficient Message Passing Software for HPC Systems: Fault Tolerance and Vector Extension." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Computer Science.

Jack Dongarra, Major Professor

We have read this dissertation and recommend its acceptance:

Jack Dongarra, George Bosilca, Michael Jantz, Yingkui Li

Accepted for the Council:

Dixie L. Thompson

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

#### Toward Reliable and Efficient Message Passing Software for HPC Systems:

Fault Tolerance and Vector Extension

A Dissertation Presented for the

Doctor of Philosophy

Degree

The University of Tennessee, Knoxville

Dong Zhong

August 2021

© by Dong Zhong, 2021 All Rights Reserved. To my parents Zhong Yuan and Yanxiong Tuo, my brothers Geng Zhong and Lei Zhong for their love, trust, and support.

## Acknowledgments

I would like to thank my advisor, Dr. Jack Dongarra, for giving me the opportunity to join Innovative Computing Laboratory (ICL) as a graduate research assistant. I appreciate the unconditional support and professional guidance. It is a great privilege to work with him, and his experience and wisdom will always be the guidance for my future work and life.

I would also like to thank my co-advisor and group leader Dr. George Bosilca for his guidance, motivation, and support during my graduate study. His comprehensive and thorough approach to thinking through a research problem inspired me to think more before taking action. His kindness, patience, and encouragement made my study and research a pleasant experience, and I feel lucky to be in this great group. He introduced me to the high-performance computing field and has been guiding me through my whole Ph.D. study. I could not have finished this dissertation without his help.

I would like to thank my committee members Dr. Michael Jantz and Dr. Yingkui Li for serving on my dissertation committee. I appreciate the invaluable guidance and insightful comments they gave to me on my research and studies. I would like to thank all professors and staff at UT and ICL for their inspiring and amazing assistance.

I would like to express my appreciation to my current and former colleagues at ICL, including Dr. Thomas Herault, Dr. Aurelien Bouteiller, Dr. Wei Wu, Dr. Chongxiao Cao, Dr. Reazul Hoque, Dr. Thananon Patinyasakdikul, Dr. David Eberius, Dr. Xi Luo, Yu Pei, Qinglei Cao for their help and company. I also thank my friend Dr. Yunhe Feng for the friendship and happiness. I wish them all the best.

Last but not least, I would like to express my deepest gratitude to my family. I would not be able to achieve anything without their love and support.

### Abstract

As the scale of High-performance Computing (HPC) systems continues to grow, researchers are devoted to achieving the best performance of running long computing jobs on these systems. My research focuses on reliability and efficiency for HPC software.

First, as systems become larger, mean-time-to-failure (MTTF) of these HPC systems is negatively impacted and tends to decrease; thus, handling system failures becomes a primary challenge. My research aims to present a general design for the implementation of an efficient runtime-level failure detection and propagation strategy that is able to detect both node and process failures, targeting large-scale, dynamic systems. The strategy employs multiple overlapping topologies to optimize detection and propagation, minimizing the incurred overheads and guaranteeing the scalability of the entire framework. My design and implementation are evaluating using results from different machines using benchmarks to compare to related works. The results show that my design and implementation outperform non-HPC solutions significantly and are competitive with specialized HPC solutions that can manage only MPI applications.

Second, I endeavor to employ instruction-level parallelization to achieve optimal performance. Novel processors support long vector extensions, which enables researchers to exploit the potential peak performance of target architectures. Intel introduced Advanced Vector Extension (AVX512 and AVX2) instructions for x86 Instruction Set Architecture (ISA). Arm introduced Scalable Vector Extension (SVE) with a new set of A64 instructions. Both enable greater parallelisms. My research utilizes long vector reduction instructions to improve the performance of MPI reduction operations. Also, I use the gather and scatter feature to speed up the packing and unpacking operation in MPI. The evaluation of the resulting software stack under different scenarios demonstrates that the approach is not only efficient but also generalizable to many vector architectures.

## **Table of Contents**

| 1 | Intr | roduction                                                  | 1  |

|---|------|------------------------------------------------------------|----|

|   | 1.1  | Motivation                                                 | 2  |

|   |      | 1.1.1 Resiliency                                           | 2  |

|   |      | 1.1.2 Long Vector Extension                                | 4  |

|   | 1.2  | Contributions                                              | 7  |

|   |      | 1.2.1 Failure Detection and Propagation in Runtime Systems | 7  |

|   |      | 1.2.2 Computation Optimization in MPI                      | 7  |

|   |      | 1.2.3 Communication Optimization in MPI                    | 8  |

| 2 | Bac  | kground and Literature Review of Related Work              | 9  |

|   | 2.1  | Overview                                                   | 9  |

|   | 2.2  | MPI                                                        | 9  |

|   |      | 2.2.1 The Open MPI Library                                 | 10 |

|   |      | 2.2.2 PMIx and PRRTE                                       | 10 |

|   | 2.3  | Fault Tolerance                                            | 11 |

|   |      | 2.3.1 Failure Detection                                    | 11 |

|   |      | 2.3.2 Reliable Broadcast                                   | 12 |

|   | 2.4  | Long Vector Extension                                      | 13 |

| 3 | Fail | lure detection and propagation in HPC systems              | 15 |

|   | 3.1  | A Generic HPC Failure Detection Service                    | 15 |

|   |      | 3.1.1 Machine Model                                        | 16 |

|   |      | 3.1.2 Failure Model                                        | 16 |

|   |                                   | 3.1.3                                                                          | Notations                                                                           | 17                                                                                                                     |

|---|-----------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|   |                                   | 3.1.4                                                                          | Detection of Process Failures                                                       | 17                                                                                                                     |

|   |                                   | 3.1.5                                                                          | Detection of Node/Daemon Failures                                                   | 17                                                                                                                     |

|   |                                   | 3.1.6                                                                          | Broadcasting Fault Information                                                      | 19                                                                                                                     |

|   |                                   | 3.1.7                                                                          | PMIx Interface                                                                      | 23                                                                                                                     |

|   |                                   | 3.1.8                                                                          | RDAEMON <sup>#</sup> in the PRRTE Architecture $\ldots \ldots \ldots \ldots \ldots$ | 23                                                                                                                     |

|   | 3.2                               | Exper                                                                          | imental Evaluation                                                                  | 25                                                                                                                     |

|   |                                   | 3.2.1                                                                          | Experimental Setup                                                                  | 25                                                                                                                     |

|   |                                   | 3.2.2                                                                          | Accuracy                                                                            | 26                                                                                                                     |

|   |                                   | 3.2.3                                                                          | Noise                                                                               | 26                                                                                                                     |

|   |                                   | 3.2.4                                                                          | Comparison with SWIM                                                                | 28                                                                                                                     |

|   |                                   | 3.2.5                                                                          | Comparison with ULFM for Process Failures                                           | 29                                                                                                                     |

|   |                                   | 3.2.6                                                                          | Node Failures Detection                                                             | 33                                                                                                                     |

|   | 3.3                               | Comm                                                                           | nunication Models Coverage and Application Evaluation                               | 35                                                                                                                     |

|   |                                   | 3.3.1                                                                          | Two-sided Application                                                               | 39                                                                                                                     |

|   |                                   | 3.3.2                                                                          | One-sided Application                                                               | 41                                                                                                                     |

|   |                                   |                                                                                |                                                                                     |                                                                                                                        |

| 4 | Red                               | luctior                                                                        | Operation Using Long Vector Extension                                               | 44                                                                                                                     |

| 4 | <b>Red</b><br>4.1                 |                                                                                | Operation Using Long Vector Extension                                               | <b>44</b><br>44                                                                                                        |

| 4 |                                   | Overv                                                                          | iew                                                                                 |                                                                                                                        |

| 4 | 4.1                               | Overv                                                                          |                                                                                     | 44                                                                                                                     |

| 4 | 4.1                               | Overv<br>Design                                                                | iew                                                                                 | 44<br>45                                                                                                               |

| 4 | 4.1                               | Overv<br>Design<br>4.2.1                                                       | iew                                                                                 | 44<br>45<br>45                                                                                                         |

| 4 | 4.1                               | Overv<br>Design<br>4.2.1<br>4.2.2                                              | iew                                                                                 | 44<br>45<br>45<br>47                                                                                                   |

| 4 | 4.1                               | Overv<br>Design<br>4.2.1<br>4.2.2<br>4.2.3                                     | iew                                                                                 | <ol> <li>44</li> <li>45</li> <li>45</li> <li>47</li> <li>47</li> </ol>                                                 |

| 4 | 4.1                               | Overv<br>Design<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                            | iew                                                                                 | <ol> <li>44</li> <li>45</li> <li>45</li> <li>47</li> <li>47</li> <li>49</li> </ol>                                     |

| 4 | 4.1                               | Overv<br>Design<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6          | iew                                                                                 | 44<br>45<br>45<br>47<br>47<br>49<br>53                                                                                 |

| 4 | <ul><li>4.1</li><li>4.2</li></ul> | Overv<br>Design<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6          | iew                                                                                 | <ol> <li>44</li> <li>45</li> <li>45</li> <li>47</li> <li>47</li> <li>49</li> <li>53</li> <li>58</li> </ol>             |

| 4 | <ul><li>4.1</li><li>4.2</li></ul> | Overv<br>Design<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>MPI I | iew                                                                                 | <ul> <li>44</li> <li>45</li> <li>45</li> <li>47</li> <li>47</li> <li>49</li> <li>53</li> <li>58</li> <li>58</li> </ul> |

|    | 4.4      | Perfor | mance Tool Evaluation                         | 64 |  |

|----|----------|--------|-----------------------------------------------|----|--|

|    | 4.5      | Applie | eation Evaluation                             | 66 |  |

|    |          | 4.5.1  | LAMMPS Application Evaluation                 | 66 |  |

|    |          | 4.5.2  | Deep Learning Application Evaluation          | 68 |  |

| 5  | Pac      | k and  | Unpack Using Long Vector Gather and Scatter   | 71 |  |

|    | 5.1      | Overv  | iew                                           | 71 |  |

|    | 5.2      | Desigr | n and Implementation in OPEN MPI              | 72 |  |

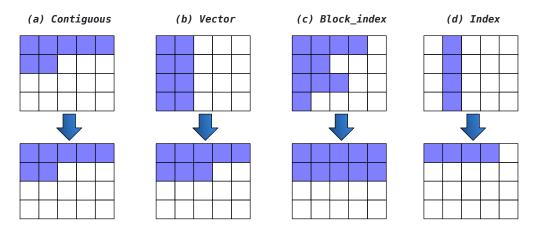

|    |          | 5.2.1  | Memory Access Pattern                         | 72 |  |

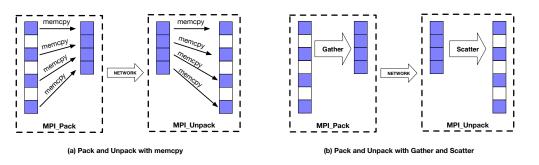

|    |          | 5.2.2  | Pack and Unpack with Gather and Scatter       | 74 |  |

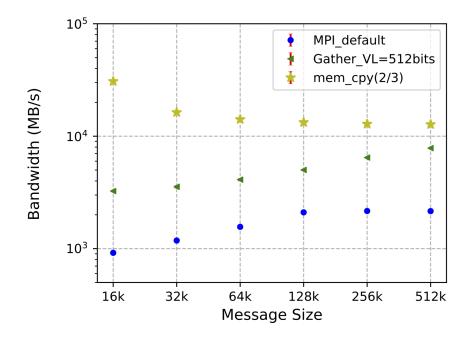

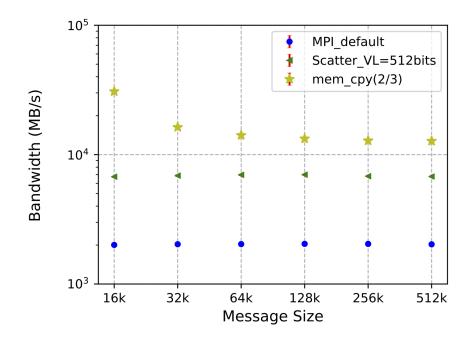

|    |          | 5.2.3  | Benchmark Evaluation                          | 78 |  |

|    | 5.3      | Applic | cation Evaluation with AVX-512 Implementation | 84 |  |

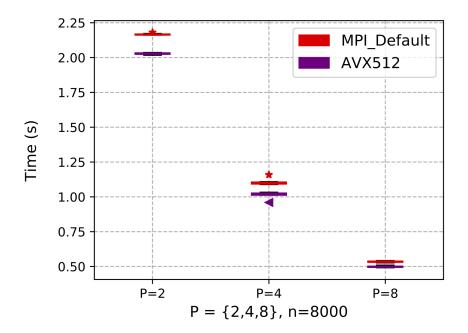

|    |          | 5.3.1  | Domain-decomposed 2D Stencil                  | 84 |  |

|    |          | 5.3.2  | 2D Fast Fourier Transform                     | 86 |  |

| 6  | Cor      | clusio | ns and Future Work                            | 90 |  |

|    | 6.1      | Conclu | usions                                        | 90 |  |

|    | 6.2      | Future | e Work                                        | 92 |  |

| Bi | bliog    | graphy |                                               | 93 |  |

| Vi | Vita 104 |        |                                               |    |  |

## List of Tables

| 3.1 | Parameters and notations                           | .8 |

|-----|----------------------------------------------------|----|

| 4.1 | Supported types and operations                     | 57 |

| 4.2 | Supported CPU flags                                | 57 |

| 5.1 | East-west vector data represent                    | 35 |

| 5.2 | MPI stencil configuration and execution on 2D grid | 37 |

## List of Figures

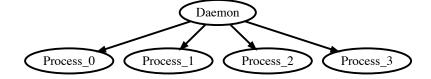

| 3.1  | Hierarchical notification of hosted processes through PMIx notification                   |    |

|------|-------------------------------------------------------------------------------------------|----|

|      | routines. The PRRTE daemon is in charge of observing and forwarding                       |    |

|      | notifications to the node-local managed application processes. The detection              |    |

|      | and reliable broadcast topology operates at the node level between daemons.               | 18 |

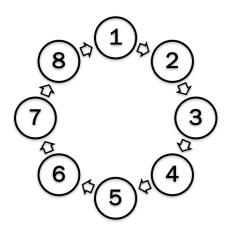

| 3.2  | Daemons monitor one another along a ring topology to detect node failures.                | 18 |

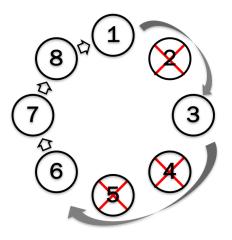

| 3.3  | The algorithm mends the detection ring topology when a node failure occurs                |    |

|      | by requesting heartbeats from the closest live ancestor in the ring                       | 18 |

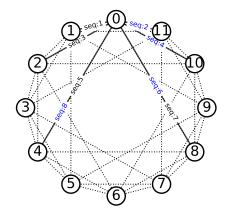

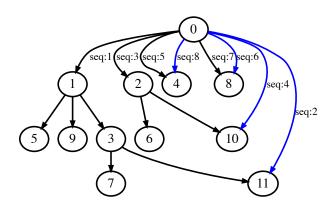

| 3.4  | Binomial graph with 12 nodes with messages sent from 0 highlighted                        | 22 |

| 3.5  | Binomial spanning tree in broadcast from node 0, redundant messages from                  |    |

|      | 0 are colored in blue                                                                     | 22 |

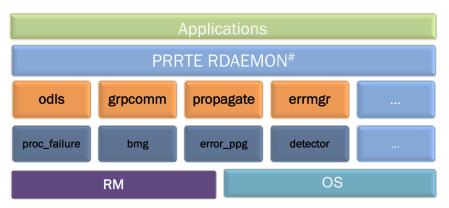

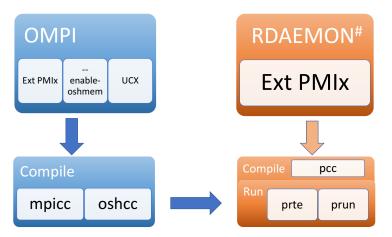

| 3.6  | Resilient PRRTE architecture. The orange boxes represent components with                  |    |

|      | added resilience features. The dark blue colored boxes are new modules                    | 24 |

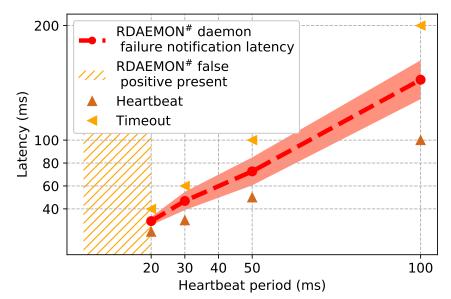

| 3.7  | Accuracy with short detection heartbeat and timeout                                       | 27 |

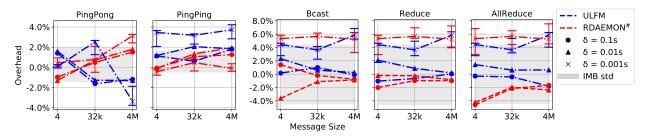

| 3.8  | PRRTE with fault tolerance overhead over PRRTE and ULFM using IMB.                        | 27 |

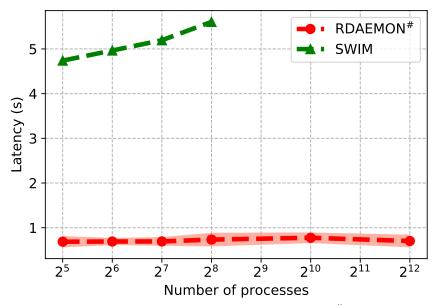

| 3.9  | Detection latency comparison between $\operatorname{RDAEMON}^{\#}$ and SWIM with increas- |    |

|      | ing number of processes ( $\delta = 0.5s$ )                                               | 30 |

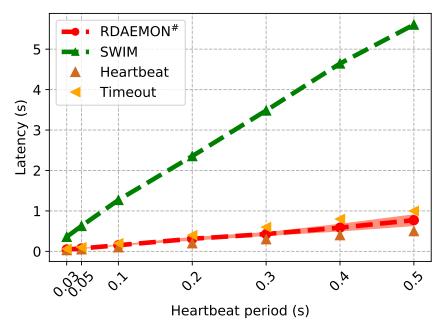

| 3.10 | Detection and Propagation delay comparison between $\operatorname{RDAEMON}^{\#}$ and      |    |

|      | SWIM with varying heartbeat period                                                        | 30 |

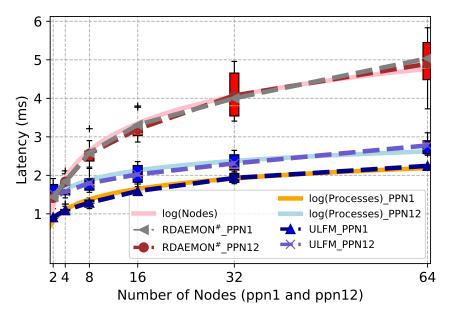

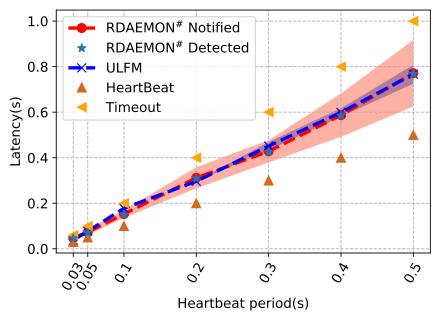

| 3.11 | Process failure detection and propagation delay compared to ULFM                          | 32 |

| 3.12 | Process failure detection and propagation delay on Cori                                   | 34 |

| 3.13 | Single Daemon Failure detection and propagation delay compared to ULFM                    |    |

|      | with different heartbeat period.                                                          | 34 |

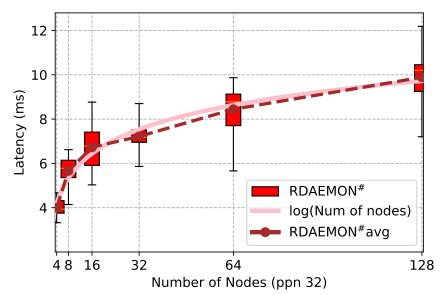

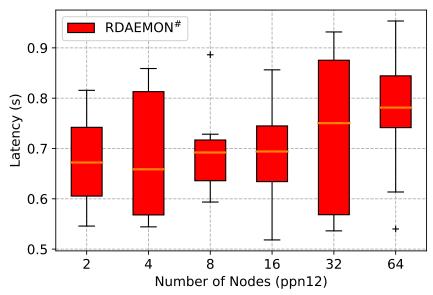

| 3.14 | Single Daemon Failure Detection and Propagation delay with different number          |   |

|------|--------------------------------------------------------------------------------------|---|

|      | of nodes $(\delta = 0.5s)$                                                           | 3 |

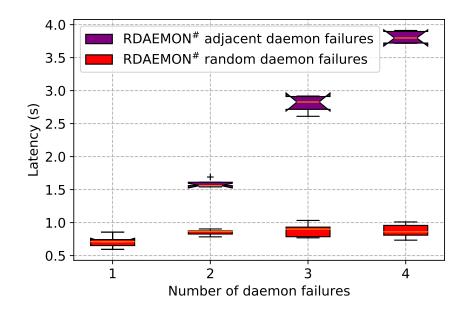

| 3.15 | Multiple daemon failures at the same time ( $\delta = 0.5s, 64$ Nodes)               | 3 |

| 3.16 | Hybrid programming model support of MPI and OPENSHMEM                                | 3 |

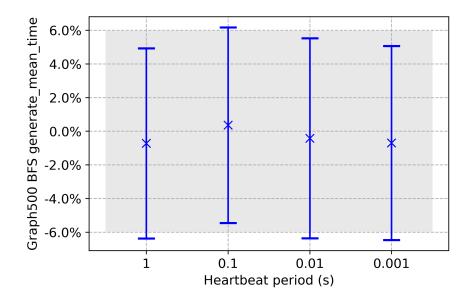

| 3.17 | Overhead for generating BFS running mpi_test_simple when using PRRTE                 |   |

|      | with fault tolerance over PRRTE (32K MPI ranks; the gray area represents             |   |

|      | the normal variability of the benchmark)                                             | 4 |

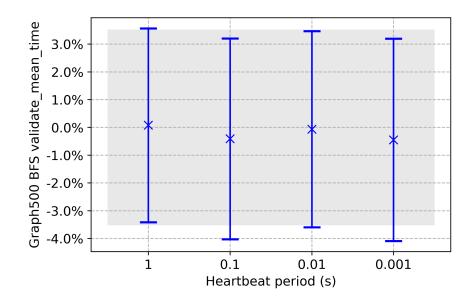

| 3.18 | Overhead for validating BFS in mpi_test_simple when using PRRTE with                 |   |

|      | fault tolerance over PRRTE (32K MPI ranks; the gray area represents the              |   |

|      | normal variability of the benchmark)                                                 | 4 |

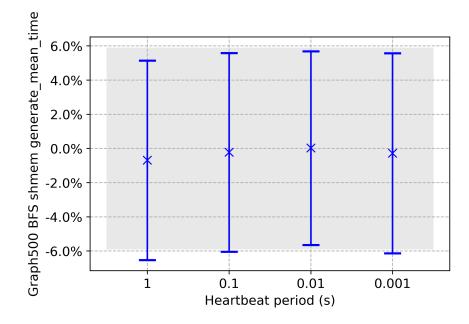

| 3.19 | Overhead for generating BFS running graph500_shmem_one_sided upon PRRTE              |   |

|      | with fault tolerance over PRRTE (32K OPENSHMEM PEs; the gray area                    |   |

|      | represents the normal variability of the benchmark)                                  | 4 |

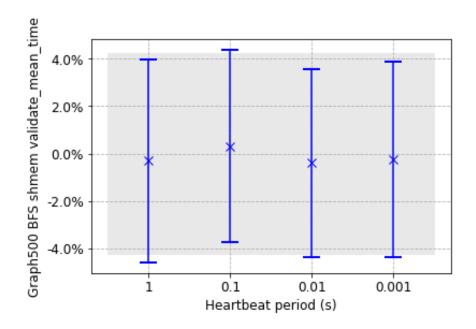

| 3.20 | Overhead for validating BFS running graph500_shmem_one_sided upon PRRTE              |   |

|      | with fault tolerance over PRRTE (32K OPENSHMEM PEs; the gray area                    |   |

|      | represents the normal variability of the benchmark)                                  | 4 |

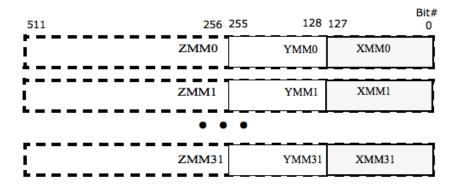

| 4.1  | AVX512-Bit Wide Vectors and SIMD Register Set                                        | 4 |

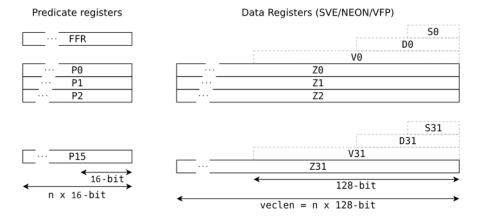

| 4.2  | Arm SVE Registers                                                                    | 4 |

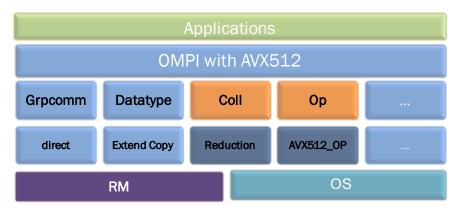

| 4.3  | OPEN MPI architecture. The orange boxes represent components with added              |   |

|      | AVX-512 reduction features. The dark blue colored boxes are new modules              | 5 |

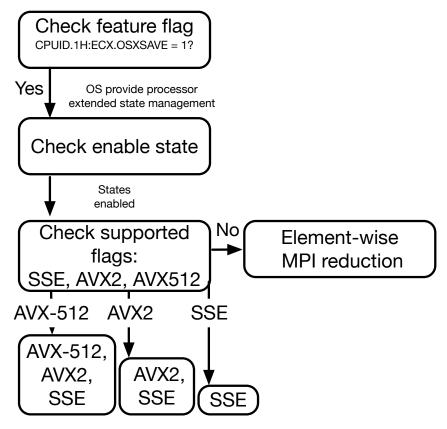

| 4.4  | Integrate and automatically activate the AVX component into the OPEN MPI             |   |

|      | build system                                                                         | 5 |

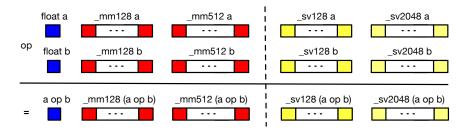

| 4.5  | Example of single precision floating-point values using : $(\_)$ scalar standard     |   |

|      | C code, ( $\_$ ) AVXs 128 bits ~ 512 bits SIMD vector of 4,8,16 values; ( $\_$ ) SVE |   |

|      | 128 bits $\sim$ 2048 bits SIMD vector of different values                            | 5 |

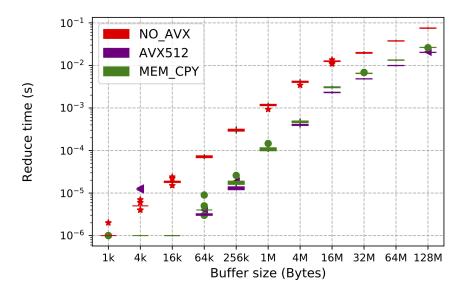

| 4.6  | Comparison of MPL_SUM with AVX-512 reduction enable and disable for                  |   |

|      | MPI_UINT8_T together with memcpy                                                     | 6 |

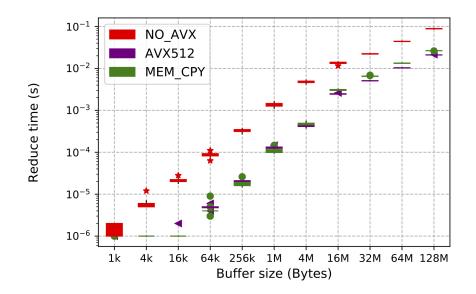

| 4.7  | Comparison of MPI_BAND with AVX-512 reduction enable and disable for                 |   |

|      | MPI_UINT8_T together with memcpy                                                     | 6 |

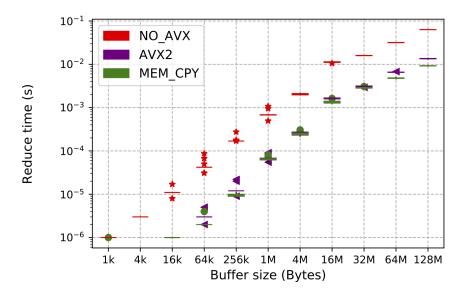

| 4.8  | AMD EPYC 7302 16-Core Processor: comparison of MPI_BAND for MPI_UINTERMINED and the transmission of MPI_BAND for MPI_UINTERMISSION and the transmission of MPI_BAND for MPI_UINTERMINED and the transmission of MPI_BAND for MPI_UINTERMINED and the transmission of MPI_BAND for MPI_UINTERMISSION and the transmission and transmission | 8_T |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | with and without AVX2, with the memcpy operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 63  |

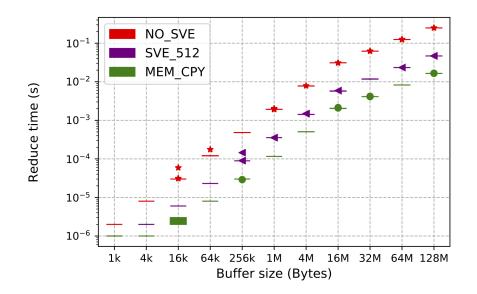

| 4.9  | Arm A64FX: comparison of MPLSUM with SVE (Vector Length = $512$ bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|      | reduction enable and disable for MPI_UINT8_T together with memcpy $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63  |

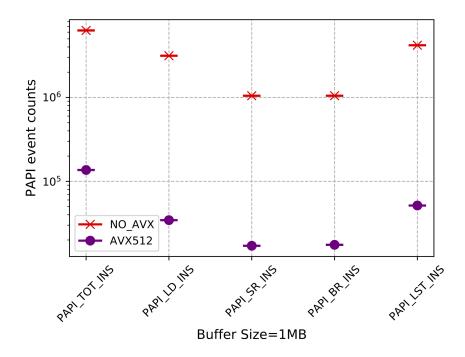

| 4.10 | Comparison between AVX-512 optimized OPEN MPI and default OPEN MPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|      | for MPLSUM reduction with PAPI instruction events overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 65  |

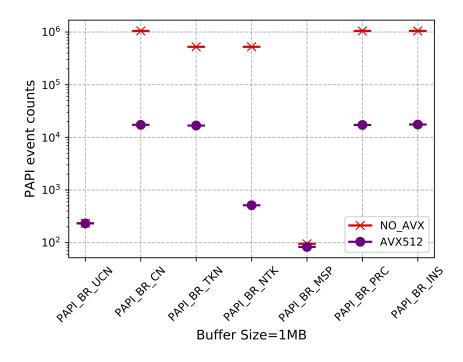

| 4.11 | Comparison between AVX-512 optimized OPEN MPI and default OPEN MPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|      | for MPLSUM reduction with PAPI branch counters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 65  |

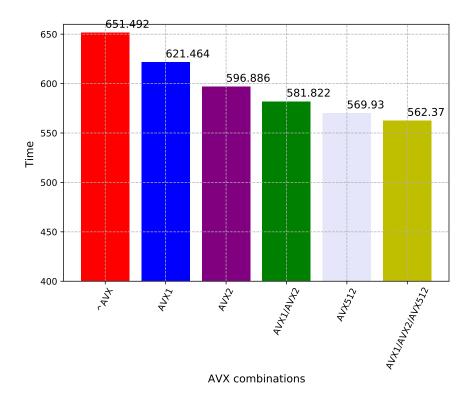

| 4.12 | LAMMPS chute: loop time on 24 procs for 100 steps with 259200000 atoms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|      | with different AVX capabilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 67  |

| 4.13 | tf_cnn_benchmarks results using Horovod (model: alexnet) on stampede2 with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|      | AVX-512 optimized OPEN MPI and default OPEN MPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 70  |

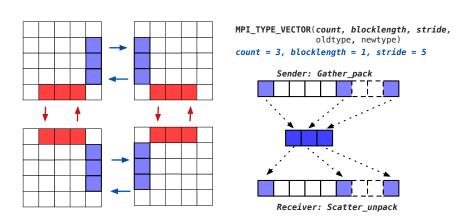

| 5.1  | Memory layout of datatype (contiguous and non-contiguous) in MPI $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 73  |

| 5.2  | Comparison between general memory copy and AVX/SVE gather/scatter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|      | implementation for packing and unpacking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 75  |

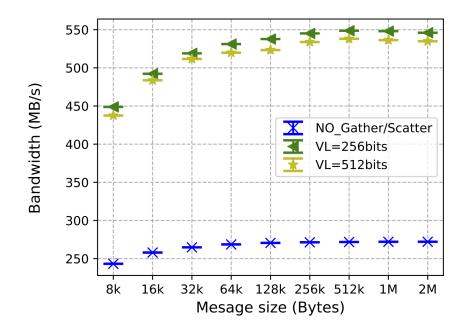

| 5.3  | Comparison of MPI_Pack with AVX-512 gather enable and disable together                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|      | with memcpy for vector datatype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 81  |

| 5.4  | Comparison of MPI_Unpack with AVX-512 scatter enable and disable together $% \mathcal{A}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|      | with memcpy for vector datatype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 81  |

| 5.5  | $Comparison \ of \ MPLPack/Unpack \ with \ SVE \ gather/scatter \ enable \ and \ disable$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|      | together with memcpy for vector datatype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 83  |

| 5.6  | Domain-decomposed 2D stencil. Data exchanged in east-west direction must                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|      | be packed and unpacked in communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 85  |

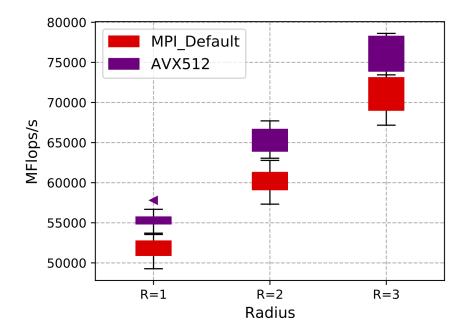

| 5.7  | 2-d Stencil results with and without AVX-512 gather pack and scatter unpack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|      | for different radius                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 87  |