# The Impact of Single Event Effect Reliability of Convolution Neural Network Architectures and Hardening Approaches Implemented on SRAM FPGA

A Thesis Submitted to the

College of Graduate and Postdoctoral Studies

In Partial Fulfillment of the Requirements

For the Degree of Master of Science

In the Department of Electrical and Computer Engineering

University of Saskatchewan

Saskatoon

By

Yixiu Wang

© Copyright Yixiu Wang, June 2021. All rights reserved

Unless otherwise noted, copyright of the material in this thesis belongs to the author

#### **PERMISSION TO USE**

In presenting this thesis/dissertation in partial fulfillment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis/dissertation in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis/dissertation work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis/dissertation or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis/dissertation.

Requests for permission to copy or to make other uses of materials in this thesis/dissertation in whole or part should be addressed to:

Head of the Department of Electrical and Computer Engineering 57 Campus Drive University of Saskatchewan Saskatoon, Saskatchewan S7N5A9 Canada

OR

Dean

College of Graduate and Postdoctoral Studies University of Saskatchewan 116 Thorvaldson Building, 110 Science Place Saskatoon, Saskatchewan S7N5C9 Canada

## **ABSTRACT**

Convolution neural networks (CNNs) have powerful data processing and learning capabilities, which have been widely applied to image processing related applications, especially in autonomous driving, medical image classification, space exploration and military applications. Due to the low power consumption, high flexibility, and parallel characteristics of modern field-programmable gate arrays (FPGAs), they are frequently used in CNN implementation as a hardware acceleration platform. Two architectures are mainly used to implement CNNs on FPGAs: the streaming architecture and single computation engines (SCEs) architecture. In the streaming architecture of a CNN, each layer is implemented with one distinct hardware block and each block can be optimized separately. On the other hand, the single computation engine architecture uses a systolic array of processing elements or a matrix multiplication unit as a computation engine to execute the CNN layers sequentially. The control of the hardware and the scheduling of operations is performed by a control unit and associated software. The advantage of this design paradigm is that it consists of a fixed architectural template that can be scaled based on the input of CNNs and the available FPGA resources. Therefore, it is suitable to implement modern complex CNNs that may not fit into the streaming architecture.

SRAM-based FPGAs are sensitive to radiation effects, which can generate single event effects (SEEs) in the system. Designs are required to reduce the radiation effects in FPGA-based CNNs for many applications. Previous radiation effects studies mainly focused on streaming architecture and explored triple-modular redundancy (TMR) or selective hardening techniques. As far as the authors know, there are very few radiation effects studies on the CNNs implemented with SCEs architecture on FPGAs and no radiation effects evaluation between the two architectures with proton irradiation.

In this thesis, we implement a Modified National Institute of Standards and Technology (MNIST) CNN with two mainstream architectures, both streaming architecture and SCEs architecture, on a Xilinx Zynq UltraScale+ multiprocessor system on a chip (MPSoC) ZCU-102 evaluation kit. Then we evaluate their error, hang, and total failure rate with proton irradiation test at Tri-University Meson Facility (TRIUMF). The cross-section results for different architectures showed that the SCEs design has higher error cross-sections and total failure cross-sections than that of the streaming architecture, even though SCEs architecture uses much fewer hardware

resources in FPGA. In addition, two resilience techniques for SCEs architecture named spatial TMR and temporal TMR are designed and adopted for the SCEs architecture with the same hardware structure and utilization by reusing process elements (PEs) or using multiple PEs to carry out each calculation. As a result, the cross-sections of the spatial TMR and temporal TMR SCEs architecture designs are reduced by 34.9% and 59.2%, with an execution time overhead of 14.2% and 21.4% compared with non-harden one, respectively. Thus, the study shows that SCEs architecture for FPGA acceleration has excellent potential for applications in a radiation environment with minimal overhead due to its scalability and flexibility, and spatial TMR and temporal TMR could effectively reduce the error rate and total failure rate with no extra hardware resources. This suggests that spatial TMR and temporal TMR propose in my project seems to be generic for SCEs architecture, and it could be a better redundancy choice for complex CNNs implement with not enough hardware resources.

#### **ACKNOWLEDGEMENTS**

This thesis can't be finished without some other people's help. I appreciate them and would like to say thank you so much!

Firstly, I would like to say thank you to my father and mother. Even if I am not by your side, once I encounter a problem that I can't solve, you will still try your best to help me. At the same time, give me the right to choose my own life, trust me and encourage me. Thanks for all those loves, I know I can afford it, but I will try my best to make a better life by myself. I will love you forever.

Secondly, I would like to thank you for Dr Chen, who is the most patient teacher I have ever seen. Dr. Chen not only teach my knowledge, but also teach me how to think and solve problems in my research. In addition, he also teaches me to find the inner motivation for my own life. Thank you, professor; without the help, I can publish the papers and finish my studies.

Thirdly, I do want to say thank you to Jin. He is a good and trustworthy person, as my best friend, he helps me a lot in daily life, as my teacher, he teaches me a lot of software knowledge and programming idea, as working partners, we have completed one after another project together, without his help, I can't complete my research.

Also, I want to say thank you to Dr Teng and Dr Ko. I took their class during the graduate time. I learned a lot about verification and computer architecture knowledge, which let me understand my project.

Furthermore, I want to say thank you to Shuting and Zhiwu, and you guys carried on all those proton tests. Without that help, I could not get experimental so successfully.

Finally, I want to say thanks to all the people in Dr Chen's group and my roommate; you guys give me a lot of help in lab and everyday life. Without that help, I could not devote all of myself to the project.

Thank you for all you help, patient, trust and encourage.

## TABLE OF CONTENTS

| PERMISSION TO USE                             | i   |

|-----------------------------------------------|-----|

| ABSTRACT                                      | ii  |

| ACKNOWLEDGEMENTS                              | iv  |

| TABLE OF CONTENTS                             | v   |

| LIST OF FIGURES                               | vii |

| LIST OF ABBREVIATIONS                         | X   |

| 1. Introduction                               | 1   |

| 1.1 Introduction:                             | 1   |

| 1.2 Motivation:                               | 3   |

| 1.3 Objectives                                | 4   |

| 1.4 Thesis Organization                       | 5   |

| 1.5 References                                | 7   |

| 2. BACKGROUND                                 | 10  |

| 2.1 Convolution Neural Network                |     |

| 2.1.1 Introduction                            |     |

| 2.1.2 Construction                            | 11  |

| 2.1.3 MNIST                                   | 12  |

| 2.2 PFGA                                      |     |

| 2.2.1 Component                               |     |

| 2.2.2 Construction                            |     |

| 2.3 Neural Network Accelerator                |     |

| 2.3.1 Streaming Architectures                 |     |

| 2.3.2 Single Computation Engines Architecture |     |

| 2.4 SEU and Redundancy                        | 21  |

| 2.4.1 Single Event Upset                      | 21  |

| 2.4.2 TMR                                     | 24  |

| 2.5 References                                | 26  |

| 3. ARCHITECTURE DESIGN AND HARDENING APPROACH | 29  |

| 3.1 Streaming and SCEs Architectures on FPGA  | 29  |

|                                     | 3.  | .1.1              | MNIST Architecture                   | 29 |  |  |  |  |

|-------------------------------------|-----|-------------------|--------------------------------------|----|--|--|--|--|

|                                     | 3.  | .1.2              | Streaming Architecture               | 31 |  |  |  |  |

|                                     | 3.  | .1.3              | SCEs Architecture.                   | 36 |  |  |  |  |

|                                     | 3.2 | Haro              | dening Approach for SCEs             | 40 |  |  |  |  |

|                                     | 3.  | .2.1              | Temporal TMR                         | 41 |  |  |  |  |

|                                     | 3.  | .2.2              | Spatial TMR                          | 43 |  |  |  |  |

|                                     | 3.3 | Refe              | erence                               | 46 |  |  |  |  |

|                                     | 3.4 | App               | endix                                | 47 |  |  |  |  |

| 4                                   | . E | XPER              | IMENTAL AND RESULT                   | 52 |  |  |  |  |

|                                     | 4.1 | Expe              | erimental Setup                      | 52 |  |  |  |  |

|                                     | 4.2 | Expe              | erimental Result                     | 54 |  |  |  |  |

|                                     | 4.  | .2.1              | Result Case.                         | 54 |  |  |  |  |

|                                     | 4.  | .2.2              | Result for Different Architecture    | 55 |  |  |  |  |

|                                     | 4.  | .2.3              | Result for Different Harden Approach | 56 |  |  |  |  |

| 5. ANALYSIS                         |     |                   |                                      |    |  |  |  |  |

| 5.1 Streaming and SCEs Architecture |     |                   |                                      |    |  |  |  |  |

|                                     | 5.  | .1.1              | Architecture (PS and PL)             | 57 |  |  |  |  |

|                                     | 5.  | .1.2              | Utilization                          | 58 |  |  |  |  |

| 5.2 Harden Approach                 |     |                   |                                      |    |  |  |  |  |

|                                     | 5.  | .2.1              | Reuse                                | 60 |  |  |  |  |

|                                     | 5.  | .2.2              | Refresh Rate                         | 61 |  |  |  |  |

| 6                                   | . C | CONCI             | LUSIONS AND FUTURE WORK              | 62 |  |  |  |  |

|                                     | 6.1 | Sum               | ımary                                | 62 |  |  |  |  |

|                                     | 6.2 | 2 Conclusions     |                                      |    |  |  |  |  |

|                                     | 6.3 | 5.3 Contributions |                                      |    |  |  |  |  |

|                                     | 61  | E4                | wo Work                              | 62 |  |  |  |  |

# LIST OF FIGURES

| Figure 1.1 Example of AI in life                                             | 2  |

|------------------------------------------------------------------------------|----|

| Figure 1.2 Single Event Upset and Single Event Transient                     | 3  |

| Figure 1.3 Image Identification based on FPGA                                | 3  |

| Figure 2.1 Convolution Neural Network Architecture Copyright                 | 10 |

| Figure 2.2 Convolution Neural Network construction example [6]               | 12 |

| Figure 2.3 MNIST Construction Example Copyright                              | 12 |

| Figure 2.4 FPGA Constructions Copyright @ Xilinx                             | 13 |

| Figure 2.5 Zynq UltraScale+ MPSoC Architecture Copyright @ Xilinx            | 15 |

| Figure 2.6 AXI Hand-shake protocol Copyright @ Xilinx                        | 17 |

| Figure 2.7 Example of a streaming accelerator architecture [24]              | 19 |

| Figure 2.8 Example of a single computer engine accelerator architecture [24] | 20 |

| Figure 2.9 Transistor-level schematic of D-flip-flop                         | 22 |

| Figure 2.10 Single Event Upset copyright Copyright @ NASA                    | 24 |

| Figure 2.11 Triple modular redundancy                                        | 25 |

| Figure 3.1 MNIST CNN topology                                                | 29 |

| Figure 3.2 Streaming architecture design diagram                             | 31 |

| Figure 3.3 The structure of CNN_PLATFROM                                     | 32 |

| Figure 3.4 CONV1 Scanning process for Streaming architecture                 | 33 |

| Figure 3.5 Output buffer structure                                           | 35 |

| Figure 3.6 SCEs architecture design diagram                                  | 36 |

| Figure 3.7 CONV1 scanning process in SCEs architecture                       | 37 |

| Figure 3.8 PE module structure                                               | 38 |

| Figure 3.9 Output buffer module structure                                    | 39 |

| Figure 3.10 Temporal TMR design diagram                                      | 42 |

| Figure 3.11 Spatial TMR design diagram                                       | 44 |

| Figure 4.1 The schematic of the testing system for proton exposures test     | 52 |

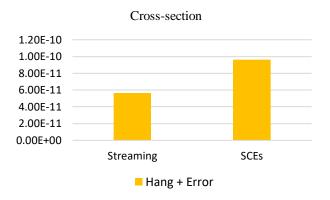

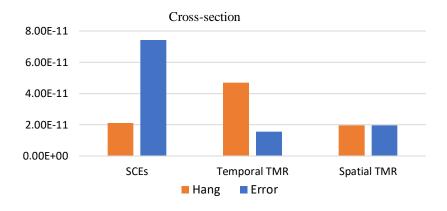

| Figure 5.1 Cross-sections of hang and errors for each design                 | 57 |

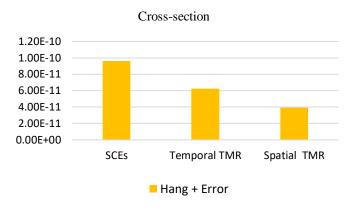

| Figure 5.2 Cross-sections of total failures for each design                  | 58 |

| Figure 5.3 Cross-sections of hang and errors for each SECs design            | 59 |

| Figure | 5 4 Cross  | sections (  | of total fail | ires for eac | ch SCFs d | ecion   | <br>60 |

|--------|------------|-------------|---------------|--------------|-----------|---------|--------|

| riguic | 3.4 CIUSS. | -8000110113 | oi ioiai iaii | iies ioi eai | ui sets u | .csigii | <br>00 |

# LIST OF TABLES

| Table 3.1 UltraScale + MPSoC Resource utilization and processing time           | 41 |

|---------------------------------------------------------------------------------|----|

| Table 4.1 Description of each situation                                         | 54 |

| Table 4.2 Description of finally hang and error situation                       | 55 |

| Table 4.3 Test result for Streaming architecture and SCEs architecture          | 56 |

| <b>Table 4.4</b> Test results for SCEs architecture and related harden approach | 56 |

## LIST OF ABBREVIATIONS

ASIC Application Specific Integrated Circuits

ARM Advanced RISC Machine

AMBA ARM Advanced Microcontroller Bus Architecture

AXI The Advanced eXtensible Interface

APU Application Processing Unit in ARM

BRAM Block Memory

BNN Binary Neural Network

BUFGMUX Buffer Global Clock Mux

CNN Convolutional Neural Network

CPU Central Processing Unit

CLA Carry-lookahead Adder

CLB Configurable Logic Block

CONV Convolutional Layer

CAN Controller Area Network

DCM Digital Clock Manager

DFF D-flip-flop

FPGA Field Programmable Gate Arrays

FC Fully-connect Layer

FIT Failure in Time

GPIO General-purpose Input/Output

GPU Graphics Processing Unit

IOB Input/Output Block

LCU Logic Control Unit

LSB Least Significant Bit

MOU Memory Optimization Unit

MCU Memory Control Unit

MACs Multiply Accumulate

MNIST Modified National Institute of Standards and Technology

MPSoC Multiprocessor System on a Chip

NSREC Nuclear & Space Radiation Effects Conference

MSB Most Significant Bit

PCIe Peripheral Component Interconnect Express

PS Processing System

PL Programmable Logic

ReLU Rectified Linear Unit

RPU Real-time Processing Unit in ARM

SAs Streaming Architectures

SRAM Static Random-access Memory

SATA Abbreviated from Serial AT Attachment

SCEs Single Computer Engines

SEE Single Event Effect

SET Single Event Transient

SEU Single Event Upset

TRIUMF Tri-University Meson Facility

TMR Triple Module Redundancy

UART Universal Asynchronous Receiver/Transmitter

## 1. Introduction

#### 1.1 Introduction:

As a new and disruptive science and technology, artificial intelligence is leading the transformation of science and technology and industrial applications [1]. With the development and application of artificial intelligence, human lifestyle and thinking structure are gradually being affected [2,3]. Artificial intelligence is different from the automation of conventional computers enables machines to learn [4], organize, adapt, and act. It can be said that artificial intelligence gives machines life and wisdom.

Since 1950s, Alan Turing, the father of artificial intelligence, who asked question about machine thinking, and published the thesis "Can Machines Think?" [6]. Then in 1970s, the first anthropomorphic robot born at Waseda University [5,7]. Later, Geoffrey Everest Hinton introduced backpropagation algorithm to multi-layers neural network training in 1980s. Until now in the 21st century, artificial intelligence has ushered in vigorous development. With the continuous improvement of artificial intelligence technology, this technology has also been put into more and more application fields, like the computer program 'AlphaGo' [8], speech recognition 'Siri' [9], facial and fingerprints recognition in mobile phone unlocking area [10-12], Tesla's autonomous driving [13], and automated production in machine manufacturing [14]. Even beyond earth, artificial intelligence in space, like exploration robot with build-in artificial intelligence [29]. Simultaneously, with the development of artificial intelligence, algorithm research, data training, artificial intelligence chips, and other scientific fields are also gradually advancing [15].

With the large-scale application of artificial intelligence in various human life scenarios showing in Figure 1.1, human life has brought many conveniences. At the same time, it has dramatically improved the quality of human life. While bringing these benefits to convenience, the relative has also produced Safety hazards [16,17], such as the burst of acceleration accident of Tesla's artificially driven car, even though the agency said it cause by pedal misapplication, but there are still doubt and worry about its reliability [27]. The aircraft accident for Ethiopia Airlines flight ET302, which may be due to the maneuvering characteristics augmentation system which is a flight law computer software algorithm [28]. These accidents caused by artificial intelligence have also led people to start research on the safety and reliability of the artificial intelligence field.

Figure 1.1 Example of AI in life

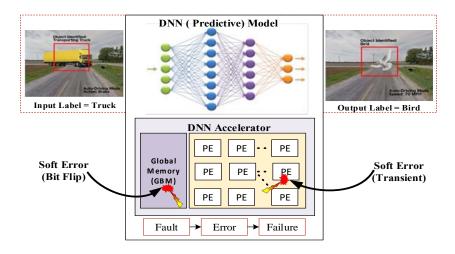

At the same time, as the development of artificial intelligence, the amount of computing and data processing has gradually increased. The types of equipment used have also increased. Simultaneously, as the amount of data processing has increased, the error rate will increase correspondingly. A significant application direction is the hardware field, such as Field Programmable Gate Arrays (FPGA), Application Specific Integrated Circuits (ASIC), Graphics Processing Unit (GPU), etc. This hardware all contains the part composed of Static Random-access Memory (SRAM) [26], which are sensitive to SEE. When a microelectronic device, such as a microprocessor, semiconductor memory, or power transistors [18-20] exposed to external radiation, such as (ions, electrons, photons...), the storage particles will be reversed or come with a current transient, it may cause configuration memory flip or output wave change. The CNN function will be destroyed, as is shown in Figure 1.2. Single event upset (SEU) happens on global memory, and single event transient (SET) occurs on PE unit. Therefore, research the reliability of SRAM-based hardware devices is beneficial for understanding and safe application of artificial intelligence.

Figure 1.2 Single Event Upset and Single Event Transient

#### 1.2 Motivation:

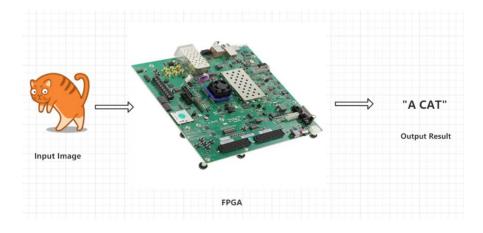

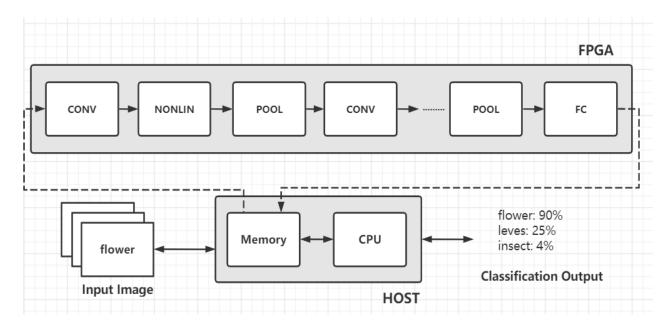

Since FPGA is called a field programmable logic Array, it has vital flexibility and wide reusability. Convolutional Neural Network (CNN) is widely used on SRAM-based FPGA. For example, in data image processing, autonomous driving, military industry and aerospace. Figure 1.4 shows the FPGA-based image recognition system. These scenarios cover a large part of the application of FPGA scenes in our lives [21,22]. But due to the characteristics of SRAM storage particles, when it exposed to an irradiation environment, SEE may happen on SRAM-based FPGAs. Then, the output result will be influenced. Therefore, studying the reliability of CNN, which implement on SRAM-based FPGA, will help us to better understand and apply CNN on FPGA-based FPGA, also bring convenience to our lives.

Figure 1.3 Image Identification based on FPGA

Nowadays, most CNNs used on FPGAs are composed of two architectures, Single compute engines (SCEs) architecture and streaming architectures [23]. Studying and comparing the reliability of the two architectures under irradiation will allow us to select the better architectures for application in different scenarios.

Recently, there have been many harden designs of CNNs on SRAM-based FPGA. Most of the design is based on the traditional Triple Module Redundancy (TMR). The reliability has been increased by adding additional redundant circuits for a voting handshake or reduce the calculation data, such as selective harden or Binary Neural Network based (BNN) methods. However, all these reinforcement methods mention before are all aimed at streaming architecture. There are relatively few reinforcement methods and research for the SECs architecture [24-25]. Therefore, studying SCEs and designing relative reinforcement methods can better understand and apply the SCEs architecture.

As artificial intelligence is widely used on SRAM-based FPGAs for data processing and accelerated calculations, at the same time, with the increase in data volume and the complexity of calculations, system reliability has gradually become a concern after processing frequency and power consumption.

Therefore, studying the reliability performance of different architectures of artificial intelligence on SRAM-based FPGAs and designing corresponding reinforcement methods will allow us to better understand how to select different architectures and corresponding reinforcement methods according to different situations, also make CNNs run and work more stable.

## 1.3 Objectives

According to the researching content in this work, the overall goal of the thesis is to study the impact of SEE reliability of CNN architectures and hardening approaches implemented on SRAM-based FPGA. The study will follow the steps.

#### 1) Train the MNIST Neural Network.

Select a basic and representative MNIST model, then use Keras to train a MNIST CNN that can recognize handwritten 0-9 numbers with an accuracy of 91%.

- 2) Implement MNIST by Single Computation Engines (SCEs) and Streaming architecture on FPGA.

- Design the trained MNIST CNN according to SCEs architecture and the Streaming architecture, then implement them on the FPGA, respectively.

- 3) Test and compare the reliability of the two architectures, analyze and draw a conclusion. Proton tests are performed on the MNIST network of two different architectures. Calculate the cross-section based on the test results. Analyze based on the combination of its architecture and utilization.

- 4) Design two harden methods for SCEs architecture.

- According to the characteristics of SCEs structure, design two harden methods called temporal and spatial TMR by multiplexing PEs. Without adding additional circuits.

- 5) Test and compare in general, analyze and draw conclusion.

- Test these two harden methods for SCEs architecture, compare with traditional SCEs, analyze and draw a conclusion.

## 1.4 Thesis Organization

The main content and structure of the thesis is organized as follows:

The first chapter focuses on the motivation and objectives of this study. It provides the risks of SEEs for SRAM-based FPGAs with the development and application of convolutional neural networks (CNNs). It then presents the objective of the research and reports the research status. Finally, it discusses the project's goals, specific plans, and corresponding steps.

The second chapter explains the prior knowledge and literature research involved in the thesis First, it explains the CNN and the primary CNN model based on the modified national institute of standards and technology (MNIST) database used in the project. Subsequently, the FPGA and its elemental composition are introduced, and the characteristics of the modern processing subsystem and programmable logic (PS+PL) heterogeneous FPGA are introduced. Then, the two primary structures, Streaming architecture and SCEs architecture, used in the project are described. Finally, the SEE and TMR are briefly explained.

The third chapter explains the design proposed in this thesis. Two basic CNN acceleration models were applied to FPGAs, namely to SCEs architecture and Streaming architecture. The related design and implementation were introduced according to the use of the MNIST network and the applied FPGA, followed by detailed design and data processing steps. The second part introduces the two hardened designs based on the SCEs architecture. The two hardening approaches are called temporal and spatial TMR. Its design features and how it is implemented on an FPGA are described. Then, its calculation steps as well as how redundancy is achieved are explained. Finally, the appendix related code and references is included.

The fourth chapter mainly describes the proton experiment. The details related to the experiment are first described. Then, the situations and classifications of the experiment and the experimental results are discussed.

In the fifth chapter, according to the relevant experimental data and the situation in the experiment, the different architectures are analyzed. The experimental phenomenon from the perspective of resource use and computing design is considered, and then the experimental results of different reinforcement methods are combined with their design. The calculation method (reuse rate and refresh rate) is analyzed, and the advantages and disadvantages of the reinforcement method are detailed.

The last chapter summarizes the implementation and progress of the project and the results obtained at this stage. First, it outlines the advantages and disadvantages of the two different architectures under irradiation environment and how to choose applications. Subsequently, two other reinforcement methods for the structure of SCEs are summarized, future work and related conjectures based on the current results are explained.

#### 1.5 REFERENCES

- [1] H. Barrow, "Keynote Speaker-3: History of Computing and AI, a Personal Viewpoint," 2015 17th UKSim-AMSS International Conference on Modelling and Simulation (UKSim), 2015, pp. 5-5, doi: 10.1109/UKSim.2015.109.

- [2] Tu Xuyan, "Life, Artificial Life and Generalized Artificial Life," 2005 International Conference on Neural Networks and Brain, 2005, pp. 1425-1428, doi: 10.1109/ICNNB.2005.1614898.

- [3] M. A. Titu and A. Stanciu, "Human and Aritificial Intelligence: the partnership that imparts hope," 2019 11th International Conference on Electronics, Computers and Artificial Intelligence (ECAI), 2019, pp. 1-6, doi: 10.1109/ECAI46879.2019.9041998.

- [4] T. Shibata, K. Ohkawa and K. Tanie, "Spontaneous behavior of robots for cooperation. Emotionally intelligent robot system," *Proceedings of IEEE International Conference on Robotics and Automation*, 1996, pp. 2426-2431 vol.3, doi: 10.1109/ROBOT.1996.506527.

- [5] Takanishi A. (2019) Historical Perspective of Humanoid Robot Research in Asia. In: Goswami A., Vadakkepat P. (eds) Humanoid Robotics: A Reference. Springer, Dordrecht.doi.org/10.1007/978-94-007-6046-2\_145.

- [6] P. T. Saunders, "Alan Turing and biology," in *IEEE Annals of the History of Computing*, vol. 15, no. 3, pp. 33-36, 1993, doi: 10.1109/85.222839.

- [7] I. Kato et al., *Development of Bipedal Walking Robot (WABOT-1)*. Biomechanism, vol. 2 (edited and published by SOBIM printed by University of Tokyo Press, 1973), pp. 173—214

- [8] Silver, D., Schrittwieser, J., Simonyan, K. *et al.* Mastering the game of Go without human knowledge. *Nature* **550**, 354–359 (2017).

- [9] Siri Team, "Hey Siri: An On-device DNN-powered Voice Trigger for Apple's Personal Assistant" 2017.10. [Online]. Available: <a href="https://machinelearning.apple.com/research/hey-siri">https://machinelearning.apple.com/research/hey-siri</a>

- [10] S. Subhash, P. N. Srivatsa, S. Siddesh, A. Ullas and B. Santhosh, "Artificial Intelligence-based Voice Assistant," 2020 Fourth World Conference on Smart Trends in Systems, Security and Sustainability (WorldS4), 2020, pp. 593-596, doi: 10.1109/WorldS450073.2020.9210344.

- [11] E. Jiang, "A review of the comparative studies on traditional and intelligent face recognition methods," 2020 International Conference on Computer Vision, Image and Deep Learning (CVIDL), 2020, pp. 11-15, doi: 10.1109/CVIDL51233.2020.00010.

- [12] Xiao Sun and Zhuming Ai, "Automatic feature extraction and recognition of fingerprint images," *Proceedings of Third International Conference on Signal Processing (ICSP'96)*, 1996, pp. 1086-1089 vol.2, doi: 10.1109/ICSIGP.1996.566282.

- [13] M. A. A. Babiker, M. A. O. Elawad and A. H. M. Ahmed, "Convolutional Neural Network for a Self-Driving Car in a Virtual Environment," 2019 International Conference on Computer, Control, Electrical, and Electronics Engineering (ICCCEEE), 2019, pp. 1-6, doi: 10.1109/ICCCEEE46830.2019.9070826.

- [14] J. -J. Aucouturier *et al.*, "Cheek to Chip: Dancing Robots and AI's Future," in *IEEE Intelligent Systems*, vol. 23, no. 2, pp. 74-84, March-April 2008, doi: 10.1109/MIS.2008.22.

- [15] Y. Chen *et al.*, "DaDianNao: A Machine-Learning Supercomputer," *2014 47th Annual IEEE/ACM International Symposium on Microarchitecture*, 2014, pp. 609-622, doi: 10.1109/MICRO.2014.58

- [16] Scherer, Matthew U. "Regulating artificial intelligence systems: Risks, challenges, competencies, and strategies." *Harv. JL & Tech.* 29 (2015): 353.

- [17] OA Oso ba, and WI Welser. "The Risks of Artificial Intelligence to Security and the Future of Work." (2017). [Online]. Available: <a href="https://www.rand.org/pubs/perspectives/PE237.html">https://www.rand.org/pubs/perspectives/PE237.html</a>

- [18]E. Normand, "Single-event effects in avionics," in *IEEE Transactions on Nuclear Science*, vol. 43, no. 2, pp. 461-474, April 1996.

- [19]S. Duzellier et al., "Low energy proton induced SEE in memories," in *IEEE Transactions on Nuclear Science*, vol. 44, no. 6, pp. 2306-2310, Dec. 1997.

- [20]R. A. Reed et al., "Heavy ion and proton-induced single event multiple upset," in *IEEE Transactions on Nuclear Science*, vol. 44, no. 6, pp. 2224-2229, Dec. 1997.

- [21] G. Wei, Y. Hou, Z. Zhao, Q. Cui, G. Deng and X. Tao, "Demo: FPGA-Cloud Architecture For CNN," 2018 24th Asia-Pacific Conference on Communications (APCC), 2018, pp. 7-8, doi: 10.1109/APCC.2018.8633447.

- [22] T. Geng et al., "FPDeep: Acceleration and Load Balancing of CNN Training on FPGA Clusters," 2018 IEEE 26th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), 2018, pp. 81-84, doi: 10.1109/FCCM.2018.00021.

- [23] [2] Venieris, S. I., Kouris, A., & Bouganis, C. (2018). Toolflows for Mapping Convolutional Neural Networks on FPGAs. ACM Computing Surveys, 51(3).

- [24] F. Libano *et al.*, "Selective Hardening for Neural Networks in FPGAs," in *IEEE Transactions on Nuclear Science*, vol. 66, no. 1, pp. 216-222, Jan. 2019.

- [25] F. Libano, *et al.*, "Understanding the Impact of Quantization, Accuracy, and Radiation on the Reliability of Convolutional Neural Networks on FPGAs," in *IEEE Transactions on Nuclear Science*, vol. 67, no. 7, pp. 1478-1484, July 2020.

- [26] W. S. Yu, R. Huang, S. Q. Xu, S. Wang, E. Kan and G. E. Suh, "SRAM-DRAM hybrid memory with applications to efficient register files in fine-grained multi-threading," 2011 38th Annual International Symposium on Computer Architecture (ISCA), 2011, pp. 247-258.

- [27] Ian Duncan, "Bursts of acceleration in Tesla vehicles caused by drivers mistaking accelerators for breaks, feds conclude," [Online]. Available: https://www.washingtonpost.com/transportation/2021/01/08/tesla-brakes/

- [28] Aircraft Accident Investigation Bureau Interim report. [Online]. Available: <a href="https://reports.aviation-safety.net/2019/20190310-0">https://reports.aviation-safety.net/2019/20190310-0</a> B38M ET-AVJ Interim.pdf

- [29] Artificial intelligence in space. [Online]. Available: <a href="https://www.esa.int/Enabling\_Support/Preparing\_for\_the\_Future/Discovery\_and\_Preparation/Artificial\_intelligence\_in\_space">https://www.esa.int/Enabling\_Support/Preparing\_for\_the\_Future/Discovery\_and\_Preparation/Artificial\_intelligence\_in\_space</a>

## 2. BACKGROUND

This chapter will explain the knowledge involved in this project, first, the basic knowledge about CNN and MNIST database. Then comes FPGA knowledge, including the architecture of the basic FPGA, the architecture of modern heterogeneous FPGAs, and the AXI protocol. After that, introducing two CNN hardware acceleration architectures based on FPGA named Streaming and SCEs architecture. Finally, the knowledge of SEU and Redundancy.

#### 2.1 Convolution Neural Network

#### 2.1.1 Introduction

CNNs are a deep learning model or multilayer perceptron similar to Artificial Neural Networks (ANNs), which is often used to analyze visual images [1]. The emergence of CNNs is inspired by biological processing [2] because the connection pattern between neurons is similar to the tissue of the visual cortex of animals [3]. Individual cortical neurons only respond to stimuli in a restricted field of vision, called the receptive field. The receptive fields of different neurons partially overlap so that they can cover the entire field of view.

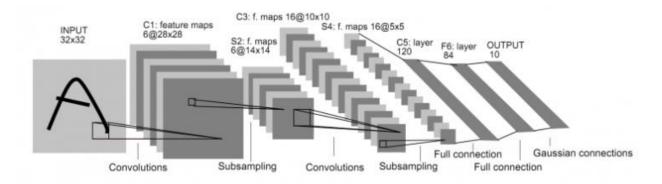

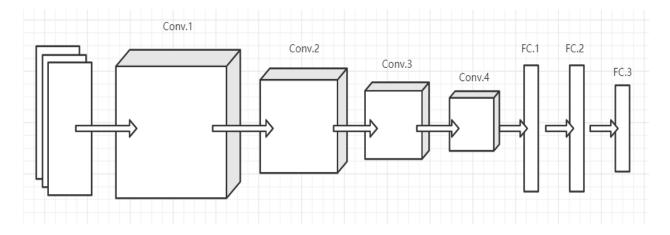

CNN architecture, as shown in Figure 2.1, is very similar to the ANN architecture [4,5], especially the last layer of the network, which is fully-connected (FC) layer. An additional convolutional layer, activation layer, and pooling layer are used for feature extraction to simulate human brain processing.

Figure 2.1 Convolution Neural Network Architecture Copyright

Figure 2.2 shows an example of the basic components of CNNs, which is a typical car plate recognition CNN [6]. It makes specific judgments based on the input image. It first extracts the

features through the convolutional layer, and then performs linear conversion through the activation layer, after which the features are filtered through the pooling layer. Finally, the features extracted to obtain the final result by using a fully connected layer.

#### 2.1.2 Construction

## 1) Convolutional Layer

In a CNN, each convolutional layer is composed of several convolution kernels, and the parameters of each convolution kernel are optimized using the backpropagation algorithm. The purpose of the convolution operation is to extract different input features [7]. The first layer of the convolutional layer may only extract some low-level features, such as edges, lines, and corners. More layers of the network can iteratively extract more complex features from the lower-level features.

## 2) Rectified Linear Units (ReLU) Layer

The activation function of this layer of nerves uses linear rectification [8]. The convolution layer performs multiple convolutions on the original image to generate a set of linear activation responses, whereas the nonlinear activation layer performs a nonlinear activation on the previous results from latest layers.

#### 3) Pooling Layer

Typically, after the convolutional layer, a feature with a large dimension is obtained [9]. The feature is cut into several regions, and the maximum or average value is taken to obtain a new feature with a smaller dimension.

## 4) Fully-Connected Layer

The acquired local features obtained were fully connected and partially characterized by the weight matrix generated and were assembled into a complete picture [10].

Figure 2.2 Convolution Neural Network construction example [6]

## **2.1.3 MNIST**

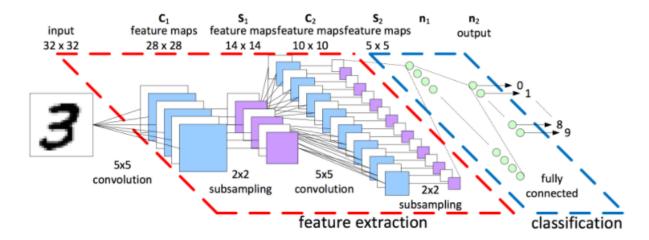

The MNIST database is an extensive database of handwritten digits that is commonly used to train various image processing systems [11,12]. The MNIST database uses  $28 \times 28$  pixels handwritten array as the dataset. The test and training sets are separated.

The main task of the MNIST handwritten digit recognition model is to input an image of handwritten digits and then recognize which digit is handwritten in the image [13], as shown in Figure 2.3. For this project, we trained and designed a MNIST-based network with an accuracy of 90% for subsequent hardware design.

Figure 2.3 MNIST Construction Example Copyright

#### 2.2 PFGA

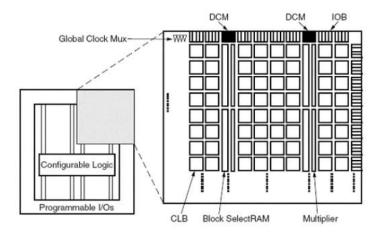

FPGAs, also known as field programmable logic gate arrays, are an integrated circuit with programmable characteristics that are pre-designed and implemented on silicon [14,15]. It can be configured as a specified circuit structure according to the needs of designers, so that customers do not have to rely on chip manufacturers. It is widely used in prototype verification, communications, automotive electronics, industrial control, aerospace, data centers, and other fields.

## 2.2.1 Component

The internal structure of the FPGA (mainly for XILINX FPGAs) includes a programmable input/output unit (I/O bank), configuration logic block (CLB), digital clock management module (DCM), embedded block RAM (BRAM), global clock network (global clock mux) wiring resources and embedded underlying functional units [16]. The components of the standard FPGA are shown in Figure 2.4.

Figure 2.4 FPGA Constructions Copyright @ Xilinx

#### (1) Input/output Blocks

At present, most FPGA I/O units are designed as programmable modes, which can be flexibly configured through software and constraints to adapt to different electrical standards and corresponding I/O physical characteristics [17]. The user can adjust the supply voltage, adjust the input drive current, and match the corresponding impedance and resistance.

## (2) Configurable Logic Blocks

The basic configuration logic blocks of the FPGA are composed of look-up tables (LUTs) and registers. The function of the LUT is to complete a pure combinational logic function [18]. In this way, synchronous or asynchronous reset and clock enable can be determined, and it can also be configured as a latch. The sequential design is completed through the register in the FPGA, and the relatively complex design is completed through the register and the LUT together. Classic configurable logic blocks are composed of LUTs and registers. The internal structure of the registers and LUTs of different manufacturers are different. The number and combination modes are also different. For example, in the Xilinx 7 Series FPGA, each CLB can be configured as either a 6-input LUT with one output or as two 5-input LUTs with two separate outputs.

## (3) Global Clock Mux

Most of the device modules in the FPGA are synchronized. Therefore, it is necessary to use a standard clock to make synchronizers when developing an FPGA project. In FPGA timing analysis, due to the uncertainty of the system frequency and combinational logic delay, the time for the signal to reach each synchronous device inside the FPGA is different, which affects the reliability and functionality of the system operation.

The role of the global clock mux is to solve the clock synchronization problem [19]. The clock signal is connected to the root of the tree as the origin point. Different synchronization devices are connected to the leaves as the endpoints, and through the buffer global clock mux (BUFGMUX) the same clock signal reach different synchronization devices with the same delay.

#### (4) Digital Clock Manager

DCM is an important device for processing the clock inside an FPGA [20]. There are three main components: clock de-skew, frequency synthesis, and phase shifting.

#### 2.2.2 Construction

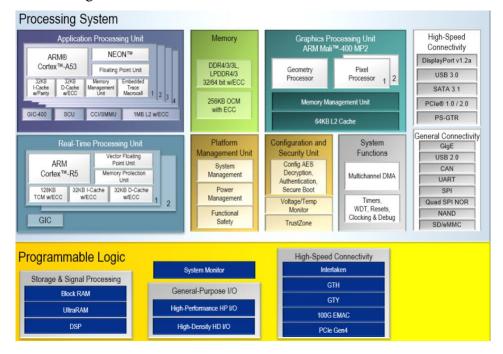

### (1) UltraScale+ Multiprocessor System on Chip (MPSoC)

The ZCU-102 FPGA used was the Zynq UltraScale+ MPSoC series, which is the second-generation Zynq platform of Xilinx. It contains a complete ARM processing subsystem (PS) in its FPGA, including a quad-core Cortex-A53 processor or a dual-core Cortex-A53 plus a dual-core Cortex-R5 processor [21]. The entire processor was built around the processor. Moreover, the processor subsystem integrates a memory controller and a large number of peripherals such that the processor core is completely independent of the programmable logic unit in Zynq. That is, if the programmable logic unit (PL) is not used temporarily, the subsystem of the processor can also work independently, which is essentially different from the previous FPGA. The UltraScale+ MPSoC is shown in Figure 2.5.

Figure 2.5 Zynq UltraScale+ MPSoC Architecture Copyright @ Xilinx

The Zynq platform has two major functional blocks: the PS and PL parts. More directly, they are the SoC part of the ARM and the FPGA part. Among them, the PS integrates the APU ARM Cortex<sup>TM</sup>-A53 processor, RPU Cortex-R5 processor, advanced microcontroller bus architecture (AMBA)® interconnection, internal memory, external memory interface (DDR controller), and

peripherals. These peripherals include a USB bus interface, Ethernet interface, SD/eMMC interface, I2C bus interface, CAN bus interface, UART interface, GPIO [22], and high-speed interfaces, such as PCIe, SATA, and Display Port.

#### (2) Advanced eXtensible Interface (AXI)

AXI is an interface protocol introduced by Xilinx from the six series of FPGAs. It mainly describes the data transmission method between the master and slave devices. AXI continues to be used in Zynq, where the version is AXI4, so we often see AXI4.0 the Zynq internal equipment has an AXI interface. In fact, AXI is a part of the AMBA proposed by ARM [23]. It is a high-performance, high-bandwidth, and low-latency on-chip bus, which is also used to replace the previous AHB and APB buses. The first version of AXI (AXI3) was included in AMBA3.0, released in 2003, and the second version of AXI (AXI4) was included in AMBA 4.0, which was released in 2010.

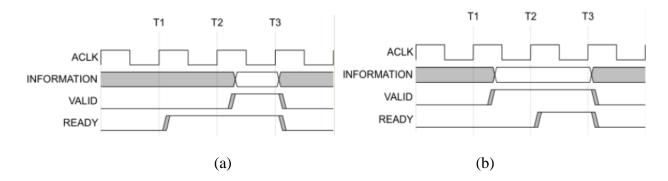

The AXI protocol mainly describes the data transmission mode between the master and slave devices. The master device and slave device establish a connection through a handshake signal. There are three types of AXI handshake methods. First, READY waits for VALID (as shown in Figure 2.6 (a)). The READY signal from the slave asserts after T1, which means that the slave is ready to receive data. Until the VALID signal becomes logic 1, the data in the information line will meet the handshake between the slave and master device. Then, the data are sent to the slave device.

Figure 2.6 AXI Hand-shake protocol Copyright @ Xilinx

The second type is the ready VALID first, as shown in Figure 2.6 (b). For the master device, the data plan to send is ready for transfer; therefore, in the information line, the data is waiting for the handshake between the slave and master to be done after T1. Then, until T2, the ready signal from the slave asserts and the data held in the information line are sent to the slave part. The third type is READY and VALID asserted simultaneously (as shown in Figure 2.6 (c)), where the VALID from the master and the READY single from the slave become logic 1 at the same time. Then, the information with the VALID signal will be sent to the slave part.

In any of these three handshake scenarios, the slave part sends out the READY signal when the slave device is ready to receive data. When the data of the master device is ready to be sent, it sends out and maintains the VALID signal with the data used in the transfer, indicating that the data is valid and stable. Data starts to transfer between the slave and master parts only when the VALID and READY signals are both valid at the same clock cycle, which is also a means of handshake. When these two signals continue to be valid, the master device continues to transmit the next data, which also means a burst in the AXI protocol. In each READY VALID period, all data in the information line can be sent from the master to the slave part. In this burst process, the master device can cancel the VALID signal at time, or the slave device can cancel the READY signal to terminate the transmission [23]. However, once the handshake agreement is not met, data transfer between the slave and master stops.

#### 2.3 Neural Network Accelerator

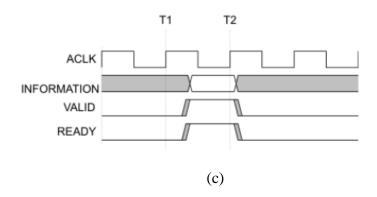

## 2.3.1 Streaming Architectures

In the CNN network in the streaming architecture, various layers are placed in the FPGA, and each module corresponds to each CNN level [25]. The module was specially optimized and processed. Different hardware modules are arranged according to the CNN's structural order and placed in the FPGA species, as shown in Figure 2.7. All the CNN structural modules, the convolutional layer, the pooling layer, the activation layer, and the fully connected layers, are connected in turn. They are calculated and run in the FPGA in a pipelined manner [24].

Data will be passed from the PC to the FPGA and transmitted in each module component in sequence according to the streaming fluid structure through different parts of the neural network. Because this method uses the parallel characteristics between the various levels through the pipeline, the CNN running on FPGA has the characteristic of running scans in parallel, which greatly increases the speed of calculation. Simultaneously, due to the method of fluid mapping, the streaming architecture consumes a lot of logic resources, resulting in an inflexible design and demanding equipment requirements. At the same time, because of the fluid mapping method, the streaming architecture consumes a lot of logic resources. The design needs to change frequently and requires considerable time for compilation.

At this stage, the basic design of the fluid architecture network is to separate the CNN used and then to split each layer in order; each stage is mapped to the FPGA according to the module, and the pair can be parallelized. The pipeline design was carried out during the processing stage. Subsequently, the performance resources and space allocation are adjusted from each module to meet the needs of each layer and the overall design [25,26]. Different hardware systems in the streaming architecture are responsible for executing different CNN parts. Therefore, when there is a CNN architecture that needs to be implemented, the FPGA must be completely reconfigured. However, this design is less flexible and has low reusability. However, due to the pertinence and uniqueness of its design, the streaming architecture for different CNN models are very effective.

**Figure 2.7** Example of a streaming accelerator architecture [24]

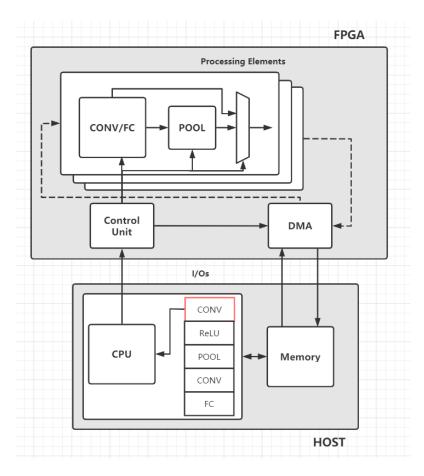

#### 2.3.2 Single Computation Engines Architecture

This design method is more flexible than a partially customized streaming structure and saves resources. The SCEs architecture is composed of arithmetic units that become the processing engine, which usually executes the data received from the buffer to process the systolic array or matrix calculations [24]. The calculation process and calculation method of the hardware in the SCEs architecture is scheduled and determined by the software, as shown in Figure 2.8. This design is a fixed template. The hardware end is composed of many processing elements with a control unit [27]. To mobilize and allocate the computing unit, we read the corresponding computing data. In terms of software, the CPU will need to execute the corresponding CNN level and transmit the corresponding instructions to the control unit to read and manipulate the data. The use of a template can be scaled correspondingly, according to the number of resources the FPGA board uses and the CNN being applied.

Through this scheme, when different CNN networks are executed, different instruction sequences can be communicated through the CPU, so that the hardware side can allocate and call processing elements according to the new instructions to perform arithmetic processing. This method highlights the flexibility of the design, which does not need to target the CNN network

and can configure and expand the modification system based only on the resources of the FPGA to be used. Therefore, after a compilation and design, the same hardware design bitstream can carry multiple CNN networks without additional time overhead due to redesign and configuration. Although the SCEs architecture has greatly improved the flexibility, the processing efficiency is reduced due to the processor-like control mechanism. A template was used at the same time. Adapting to multiple CNNs will lead to large performance differences between different CNNs and different workloads.

In the network using SCEs at this stage, different instruction sequences are first designed for the CPU and mapped to the FPGA hardware. Then, the hardware is designed according to the characteristics of the hardware and the amounts of resources. Then, it was passed according to different CNNs. The CPU sends different instruction sequences to the hardware to execute the CNN.

Figure 2.8 Example of a single computer engine accelerator architecture [24]

## 2.4 SEU and Redundancy

SEEs refer to a radiation effect that causes abnormal changes in the state of the device when a single high-energy particle passes through the sensitive area of a microelectronic device, including single-event flipping, single-event latch, and single-event upset [28]. SEEs cause these two main errors. The first type of error is a "soft error." When a soft error happens, a temporary also non-destructive error will occur in the system. It will not lead a permanent failure and can recover by itself. The second type of error is a "hard error" which causes permanent failure for the entire system.

## 2.4.1 Single Event Upset

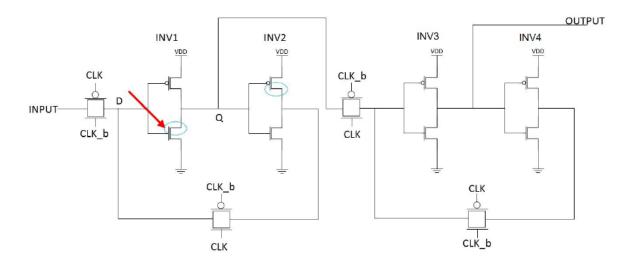

Sequential logic circuits and combinational logic circuits are the two main categories of digital circuits. Both the current input and current can determine the output for the sequential logic circuit. This means that a memory block or element should be set in a sequential logic circuit to store the previous data. In Figure 2.8, it is the basic transistor-level schematic of a D-flip-flop (DFF) and the most basic register element in integrated circuit (IC) design. There are two D-latches, each containing a latch and transmission gate. Two latch inverters between 0 and 1 to store the 1-bit data. The transmission in INV1 and INV4 is open when the clock is 0. The data are latched in the first latch; that is,, the data is stored in the first latch and cannot pass to the second latch because of the close for gate in INV2. In this period, the second latch holds the previous data until the clock signal asserts. As the clock rising edge arrives, gate1 and gate4 will close, and the gates in INV2 and INV3 will be switched on. At the same time, data will be passed to latch2 and stored in latch1, and stable data can be grabbed in this moment.

Figure 2.9 Transistor-level schematic of D-flip-flop

The first paragraph describes the basic DFF process. The DFF will work properly (store 0 or 1) when it matches the set-up and hold-up time. However, when a single high-energy particle passes through the sensitive area, such as the PMOS in DFF, it may cause the store bit in the latch to flip, and the output data from the DFF will be incorrect. In this bit flip situation, the minimum total charge to upset the data stored in the latch is called the critical charge ( $Q_C$ ), which is the most important parameter to judge whether the data stored in latch will reverse. Equation 2.1 shows that the critical charge can be considered as the product of the total capacitance of the transistor node ( $C_n$ ) and the voltage of the power supply ( $V_{dd}$ ).

$$Q_C = C_n \times V_{dd} \tag{2.1}$$

$$\sigma = n/N \tag{2.2}$$

$$FIT = \sigma \times \phi \times 10^9 \tag{2.3}$$

When an SEU occurs in a microelectronic device, which means that in a radiation environment, the sensitive node has collected enough charge (greater than the critical charge), data in latch 1 is 0 (Q=1, D=0) when the clock signal asserts. The NMOS in INV2 and the PMOS in INV1 are

closed in this situation. The PMOS in INV2 and NMOS in INV1 are turned on at the same time, which indicates that both PMOS in INV1 and NMOS in INV2 are drained. This is shown in Figure 2.8. If a single high-energy particle hits the NMOS drain area in INV1. The black arrow indicates this case. During the charge collection period, a current pulse occurs in the sensitive area. If the pulse is larger than the critical charger, the logic values of the Q output will reverse from 0 to 1. The data store in latch is flipped totally (Q=0, D=1), and the wrong data will be held until the next clocking rising edge. This phenomenon is called SEU, and the possibility that SEU may occur in storage memory is represented by the "cross-section," as shown in Equation 2.2, where the cross-section ( $\sigma$ ) is equal to the total errors (n) in one device divided by the particle total fluence (N).

A single event flip is a single high-energy particle acting on a semiconductor device, causing an abnormal change in the logic state of the device. A single event upset is the most common and typical of multiple SEEs caused by space radiation, and it mainly occurs in data storage or instruction-related devices. The device error caused by a single event flip is a "soft error," that is, it can be restored to the normal state by system reset, re-power on, or re-write.

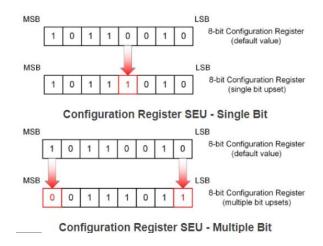

These soft errors can be divided into single-bit upsets and multiple-bit upsets As shown in Figure 2.10, in the 8-bit configuration register, the default value changes from 10110010 to 10111010, as the rad arrow pointer the third bit changes from 0 to 1. This causes the configuration data to be wrong; 10110010 implies a write operation in the device instruction, but it changes to 10111010, which means read operation in device instruction, which causes the device operation to be wrong, but it can be recovered by a system reset. The second part is a multiple-bit upset, and the configuration bit in Figure 2.10 changes from 10110010 to 00111011. The last significant bit (LSB) and the most significant bit (MSB) together with the third bit reverse from the original logic value. As in one 4-LUTs, it has 4-bit input and 1-bit output. The configuration generated in the bitstream is 10110010, but when this device received irradiation and when multiple-bit upset occurred, the configuration changed to 00111011, and the function this LUTs represent is wrong. Finally, this may cause the device to run in error.

Figure 2.10 Single Event Upset copyright Copyright @ NASA

Another common unit to measure the Soft Error Rate (SER) is Failure in Time (FIT), it also considered as the possibility for an SEU happened in electronic device. A one-time failure in one billion device hours is one FIT. Here is the example, the FIT value for a single chip electronic system is 10000, that means between per 114 years the whole system will get one failure. FIT can be considered as the cross-section ( $\sigma$ ) multiply the fluence of a particle in the environment ( $\phi$ ) with  $10^9$ . This equation is shown in equation 2.3.

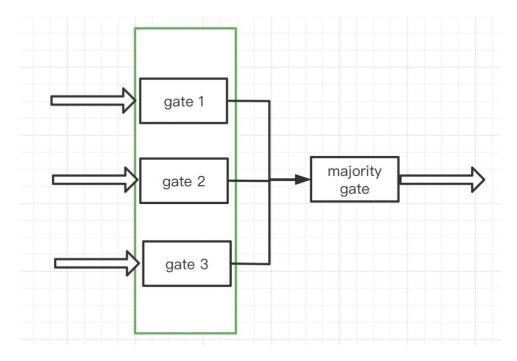

#### 2.4.2 TMR

TMR implies that the system deliberately configures duplicate parts and skills to improve its reliability. In computer science, TMR is sometimes referred to as triple-mode redundancy. As shown in Figure 2.7, there are three gates in the green rectangle; these three gates are same but constructed with different circuits. Each of these gates can perform the same function in this system. All the results of the gates will flow direction to the majority gate module, which works for voting to obtain the final results. In a normal situation, these three gates will generate the same output result and send it to the majority gate; then, the majority gate chooses any one to be the output, because all the three outputs from the three gates are correct. However, when this system is in an irradiation environment, and an SEE occurs in the system with only one gate, the wrong result will come from the device. However, if TMR is implemented here, such as the design in the green rectangle, if one of those three gates occurs in SEE, the other two will work normally with a high

probability, because the probability that both sets of gates occur with SEE is very small, so the majority can vote to the right result by voting those sets of right results from those two normal gates.

Figure 2.11 Triple modular redundancy

The TMR is a fault-tolerant form of N-modular redundancy. Three identical systems were used to perform the same function, and then through a majority-voting system, the output of the majority was taken as the final output. If only one of the three systems was damaged and the other two remained normally, the majority voting system used the two pairs of outputs and the result for those The TMR is a fault-tolerant form of N-modular redundancy. Three identical systems were used to perform the same function, and then through a majority-voting system, the output of the majority was taken as the final output. If only one of the three systems was damaged and the other two remained normally, the majority voting system used the two pairs of outputs and this vote result was considered to be the final output.

#### 2.5 REFERENCES

- [1] S. U. Amin, K. Agarwal, and R. Beg, "Genetic neural network based data mining in prediction of heart disease using risk factors," in Proc. IEEE Conf. Inf. Commun. Technol., Apr. 2013, pp. 1227–1231.

- [2] Pedraza, A., Gallego, J., Lopez, S., Gonzalez, L., Laurinavicius, A., & Bueno, G. (2017, July). Glomerulus classification with convolutional neural networks. In *Annual conference on medical image understanding and analysis* (pp. 839-849). Springer, Cham.

- [3] Bernal, J., Kushibar, K., Asfaw, D. S., Valverde, S., Oliver, A., Martí, R., & Lladó, X. (2019). Deep convolutional neural networks for brain image analysis on magnetic resonance imaging: a review. *Artificial intelligence in medicine*, 95, 64-81.

- [4] Islam, Kh Tohidul, Ram Gopal Raj, and Abdullah Al-Murad. "Performance of SVM, CNN, and ANN with BoW, HOG, and image pixels in face recognition." 2017 2nd International Conference on Electrical & Electronic Engineering (ICEEE). IEEE, 2017.

- [5] Petersson, Henrik, David Gustafsson, and David Bergstrom. "Hyperspectral image analysis using deep learning—A review." 2016 sixth international conference on image processing theory, tools and applications (IPTA). IEEE, 2016.

- [6] S. Lee, K. Son, H. Kim and J. Park, "Car plate recognition based on CNN using embedded system with GPU," 2017 10th International Conference on Human System Interactions (HSI), 2017, pp. 239-241, doi: 10.1109/HSI.2017.8005037.

- [7] Uchida K, Tanaka M, Okutomi M. Coupled convolution layer for convolutional neural network. Neural Netw. 2018 Sep; 105:197-205. doi: 10.1016/j.neunet.2018.05.002. Epub 2018 May 16. PMID: 29870927.

- [8] Agarap A F. Deep learning using rectified linear units (relu)[J]. arXiv preprint arXiv:1803.08375, 2018.

- [9] Yu, Dingjun, et al. "Mixed pooling for convolutional neural networks." *International conference on rough sets and knowledge technology*. Springer, Cham, 2014.

- [10] Wohlhart P, Lepetit V. Learning descriptors for object recognition and 3d pose estimation[C] *IEEE conference on computer vision and pattern recognition*. 2015: 3109-3118.

- [11] Deng L. The mnist database of handwritten digit images for machine learning research [best of the web][J]. *IEEE Signal Processing Magazine*, 2012, 29(6): 141-142.

- [12] G. Cohen, S. Afshar, J. Tapson and A. van Schaik, "EMNIST: Extending MNIST to handwritten letters," 2017 International Joint Conference on Neural Networks (IJCNN), 2017, pp. 2921-2926, doi: 10.1109/IJCNN.2017.7966217

- [13] Wu M, Zhang Z. Handwritten digit classification using the mnist data set[J]. Course project CSE802: Pattern Classification & Analysis, 2010.

- [14] Robert Keim," What Is an FPGA? An Introduction to Programmable Logic," [Online]. Available: <a href="https://www.allaboutcircuits.com/technical-articles/what-is-an-fpga-introduction-to-programmable-logic-fpga-vs-microcontroller/">https://www.allaboutcircuits.com/technical-articles/what-is-an-fpga-introduction-to-programmable-logic-fpga-vs-microcontroller/</a>

- [15] Serrano, J "Introduction to FPGA design." (2008). [Online]. Available: <a href="http://www.jps-pcb.com/upfile/2017/02/20170204171513\_891.pdf">http://www.jps-pcb.com/upfile/2017/02/20170204171513\_891.pdf</a>

- [16] S. Trimberger, "FPGA Technology: Past, Present and Future," ESSCIRC '95: Twenty-first European Solid-State Circuits Conference, 1995, pp. 12-15.

- [17] Linde, Arne & Nordström, Tomas & Taveniku, Mikael. (1992). Using FPLs to Implement a Reconfigurable Highly Parallel Computer. Selected Papers from: Second International Workshop on Field Programmable Logic and Applications. 705. 199-210. 10.1007/3-540-57091-8\_45.

- [18] I. P. Dugganapally, W. K. Al-Assadi, V. Pillai and S. Smith, "Design and Implementation of FPGA Configuration Logic Block Using Asynchronous Semi-Static NCL Circuits," *2008 IEEE Region 5 Conference*, 2008, pp. 1-6, doi: 10.1109/TPSD.2008.4562768.

- [19] Christian, Schuck & Bastian, Haetzer & Becker, Juergen. (2009). An Interface for a Decentralized 2D Reconfiguration on Xilinx Virtex-FPGAs for Organic Computing. International Journal of Reconfigurable Computing. 2009. 10.1155/2009/273791.

- [20] N. Fujieda, M. Takeda and S. Ichikawa, "An Analysis of DCM-Based True Random Number Generator," in *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 67, no. 6, pp. 1109-1113, June 2020, doi: 10.1109/TCSII.2019.2926555.

- [21] ZCU102 Evaluation Board User Guide, UG1182(v1.6) June 12,2019. Xilinx. [Online]. Available: <a href="https://www.xilinx.com/support/documentation/boards">https://www.xilinx.com/support/documentation/boards</a> and <a href="https://www.xilinx.com/support/documentation/boards">https://www.xilinx.com/support/documentation/boards</a> a

- [22] Zynq UltraScale+ MPSoC Data Sheet: Overview, DS891(v1.8) October 2,2019. Xilinx. [Online]. Available: <a href="https://www.xilinx.com/support/documentation/data\_sheets/ds891-zynq-ultrascale-plus-overview.pdf">https://www.xilinx.com/support/documentation/data\_sheets/ds891-zynq-ultrascale-plus-overview.pdf</a>

- [23] AXI Reference Guide, UG1037 (v4.0) July 15, 2017. [Online]. Available: <a href="https://www.xilinx.com/support/documentation/data\_sheets/ds891-zynq-ultrascale-plus-overview.pdf">https://www.xilinx.com/support/documentation/data\_sheets/ds891-zynq-ultrascale-plus-overview.pdf</a>

- [24] Venieris, Stylianos I., Alexandros Kouris, and Christos-Savvas Bouganis. "Toolflows for mapping convolutional neural networks on FPGAs: A survey and future directions." arXiv preprint arXiv:1803.05900 (2018).

- [25] Szegedy, Christian, et al. "Inception-v4, inception-resnet and the impact of residual connections on learning." *Proceedings of the AAAI Conference on Artificial Intelligence*. Vol. 31. No. 1. 2017.

- [26] Rehan Hameed, Wajahat Qadeer, Megan Wachs, Omid Azizi, Alex Solomatnikov, Benjamin C. Lee, Stephen Richardson, Christos Kozyrakis, and Mark Horowitz. 2010. Understanding Sources of Inefficiency in General-purpose Chips. In Proceedings of the 37th Annual International Symposium on Computer Architecture (ISCA '10). ACM, 37–47.

- [27] Kenneth A. LaBel, Single Event Effects (SEEs) Specification Approach. [Online]. Available: <a href="https://radhome.gsfc.nasa.gov/radhome/papers/SEEspec.pdf">https://radhome.gsfc.nasa.gov/radhome/papers/SEEspec.pdf</a>

## 3. ARCHITECTURE DESIGN AND HARDENING APPROACH

This chapter introduces the MNIST architecture used in the project and how to implement it on the ZCU-102 board with SCEs and Streaming architectures in detail. Then, two harden TMR designs based on SCEs architecture are introduced with design ideas, detailed implementation steps, and related code.

## 3.1 Streaming and SCEs Architectures on FPGA

The MNIST CNNs are implemented on the 16-nm Fin-FET Zynq UltraScale+ MPSoC (Xilinx XCZU9EG-2FFVB1156 on the evaluation board ZCU102). It is composed of a processing system (PS) which uses a quad-core ARM A53 with programmable logic (PL). FPGA-based CNN accelerators can be classified into two types: streaming architecture and single computation engines (SCEs) architecture [1]. This study implemented both streaming and SCEs architectures and evaluated the architectural vulnerability of each by using a higher level of granularity which is accomplished by dividing the architecture into two parts, the PL and the PS in the FPGA instead of looking at each layer.

### 3.1.1 MNIST Architecture

The CNN in this project uses the standard MNIST data set. The standard MNIST is a data set of  $28 \times 28$  pixels images of handwritten decimal digital from 0 to 9. For the beginning we write a python code to train a CNN by Keras with standard MNIST data set. The accuracy for this MNIST CNN is 90%, which means for each of the ten handwritten decimal numbers our network can correctly recognize nine decimal numbers from zero to nine.

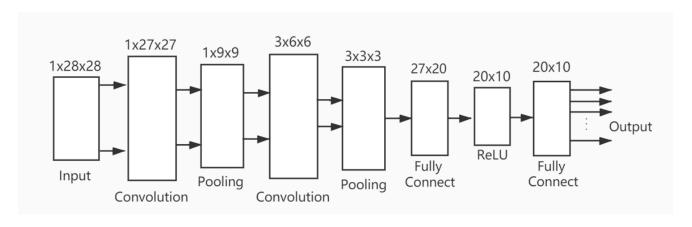

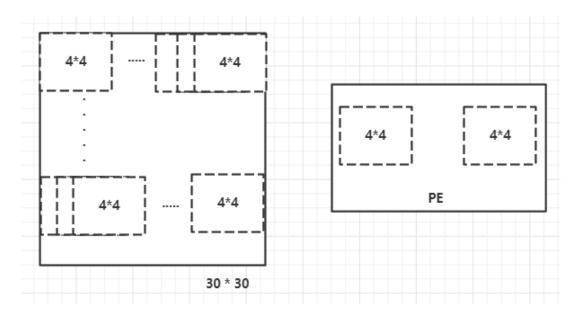

Figure 3.1 MNIST CNN topology

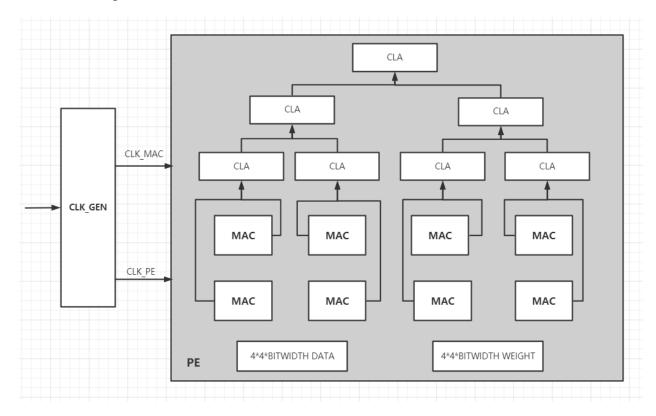

As shown in Figire 3.1, the MNIST CNN receives a data set of 28 × 28 pixels images of handwritten decimal numbers as a total of 784 pixels of input data. Then a round padding will add to the  $28 \times 28$  matrix. In other words, a circle of 0's will be added to the periphery of the matrix which makes the size of this input matrix  $30 \times 30$ . After this it will pass through the first convolution layer, CONV1, which is a  $1 \times 4 \times 4$  matrix. Then a  $27 \times 27$  size new matrix will be generated as the new input matrix for pooling layers 1. The size of the first pooling is  $3 \times 3$ , and the function for those two layers is to find the max number value in each  $3 \times 3$  matrix. After first max pooling layer the feature for the input is extracted to generate a  $9 \times 9$  size matrix. Convolution layer2 CONV2 will scan this  $9 \times 9$  matrix with 3 sets of  $4 \times 4$  size matrices. The output for CONV2 are then 3 sets of  $3 \times 3$  matrices. By using a flatten layer, those three matrixes will become 27 individual outputs, all of which will pass the  $27 \times 20$  size fully connected layer multiply and adding bias. The result from fully connected layer1 will be the input for the ReLU activation layer, generating a set of linear activation responses. Those 20 individual responses will act as the last input for the fully connected layer2. At the end, 10 individual numbers will be the final output, with each one representing the possibility for the decimal number between 0 to 9. The highest value in those ten outputs will be used as the MNIST CNN identified result. Table 3.1 shows the MNIST CNN construction. Tt can be combined with the Figure 3.1, the topology for MNIST CNN, to better understand the data process.

**Table 3.1** MNIST CNN construction

| Input          | 784 pixels                                      |  |  |

|----------------|-------------------------------------------------|--|--|

| Conv layer1    | $1 \times 4 \times 4$ filter                    |  |  |

| Max pooling1   | $3 \times 3$ filter                             |  |  |

| Conv layer2    | $3 \times 4 \times 4$ filter                    |  |  |

| Max pooling2   | $2 \times 2$ filter                             |  |  |

| Flatten layer  | $3 \times 3 \times 3$ matrix inputs, 27 outputs |  |  |

| Fully connect1 | 27 inputs, 20 outputs                           |  |  |

| ReLU1          | 20 inputs, 20 outputs                           |  |  |

| Fully connect2 | 20 inputs, 10 outputs                                                   |  |

|----------------|-------------------------------------------------------------------------|--|

| Output         | The image classification - the result can be any integer between 0 to 9 |  |

## 3.1.2 Streaming Architecture

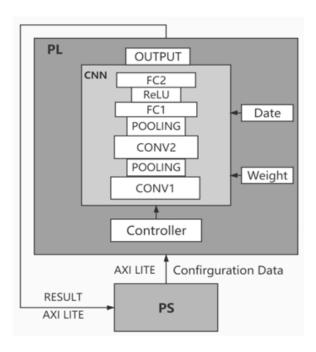

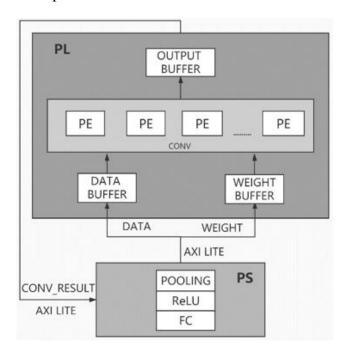

The MNIST are implemented on a ZCU-102 FPGA with Streaming architecture, which consists of three parts. The first part is the PS which communicates with the host PC by UART. It can also send the final result to the host PC and the instructions to the controller in PL. The second part is the controller in the PL. It works as a decoder, for the instructions from PS. The last part is the CNN calculation part, which performs whole CNN calculation.

In the streaming architecture the entire CNN layers are placed into the PL part of the FPGA, including its convolutional layer, pooling layer, flatten layer, and fully connected layer. Each layer is implemented into different blocks of the FPGA and form the pipeline for the calculations. The block diagram of the streaming architecture CNN is shown in Fig 3.2. Please note that the PS is also included in the diagram. It reads the calculation results from the PL and sends it to terminal by a UART port.

Figure 3.2 Streaming architecture design diagram

After receiving the instruction from the host PC, the PS side transmits it to the PL through AXI-lite, where the CNN and the controller are packaged together to form an IP package. This new AXI IP supports the AXI1-lite protocol (connected through AXI-interconnect and share the same clock). The PL part receives the 32 bits of control information, then the controller module unpacks and decoder it into the corresponding number of operations rounds (indicated by 8-1 bits). In the 32 bits operation code the operation interval (indicated by 10-9 bits) generates the corresponding start signal (0 bits).

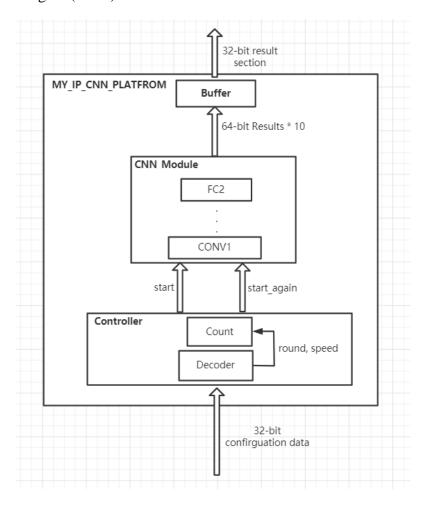

Figure 3.3 The structure of CNN\_PLATFROM

Figure 3.3 shows the detailed structure for the CNN-PLATFROM module in the PL part. When the 32-bit configuration data is received and decoded by the controller module, as explained in the previous paragraph, the corresponding number of operations round and the operation interval

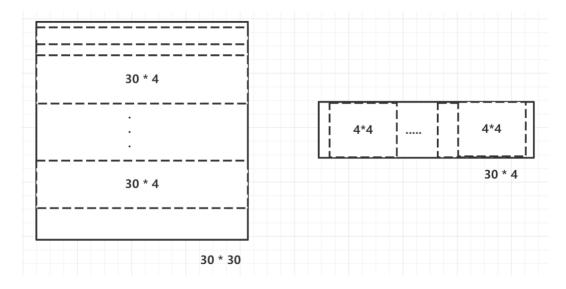

will be controlled by the count block. The related code will be showed in chapter 3.3. The corresponding round and speed that was decoded will then be generated to homologous start and start\_again signals, which are outputs from the controller module. Those two signals will then become two inputs for the CNN module. They will be used to start, refresh, and restart the process in calculation. The CONV1 module starts to extract the  $28 \times 28$  data stored in the ROM (stored in 8 bits form) and the  $4 \times 4$  weight (8 bits form) is also stored in ROM. These corresponding data and weights are required by the first convolutional layer. After obtaining the data it will first add a layer of padding according to the settings of the MNIST model. To elaborate, a circle of 0's will be added to the periphery of  $28 \times 28$  matrix and the size will become  $30 \times 30$ . Then, the scanning will start according to the corresponding MNIST matrix parameters and it will generate the corresponding matrix and perform the convolution operation on the obtained matrix.

Figure 3.4 CONV1 Scanning process for Streaming architecture

In this design, the first round of data is divided into 27 groups. The Figure 3.4. shows the scanning process in CONV1. This  $30 \times 30$  matrix will be scanned by a  $30 \times 4$  matrix and it will be scanned 27 times in total - each time a  $30 \times 4$  size of matrix is generated. The 27 groups of matrixes are operated in sequence, and each  $30 \times 4$  matrix will be scanned by its weight matrix, the  $4 \times 4$  matrix, as shown in Figure 3.4. In each  $4 \times 4$  matrix all the data will first perform the multiplication operation. After, 16 individual products will be generated then those products will be added together. Each time the multiplication and adding is finished the CONV1 module will

double the bit-width for each result from 32-bit to 64-bit in order to ensure the accuracy of the result. Each convolution result will then be scanned and stored in corresponding RAM.

The CONV1 module will wait for all the data scanning operations to be completed, then final results for CONV1 will be stored in temporal RAM. Then CONV1 results will be sent to a  $3 \times 3$  max pooling, and the scan procedure is similar to the process in CONV1 - A  $27 \times 27$  size matrix will be scanned by a  $3 \times 3$  matrix. In each pooling matrix the biggest number in those 9 digital numbers will be chosen to be the result. The corresponding pooling matrix is generated in turn to get a new  $9 \times 9$  matrix. Then, CONV2 is executed, and the process is the same as the process for CONV1. The related code will be showed in chapter 3.3.

Since the CONV2 layers have three sets of weight, the input data for CONV2 will be copied three times and will generate three sets of  $9 \times 9$  matrices. Each  $9 \times 9$  matrix will be scanned by the  $4 \times 9$  scan matrix, then it will be divided into 6 parts. After that each  $4 \times 9$  matrix will be scanned by the weight  $4 \times 4$  array, and the same procedure in CONV1 will be processed in CONV2. Each output after this process will be re-arranged and stored in temporal RAMs. Three sets of  $6 \times 6$  matrices will be generated as the output from the CONV2 layer.

Then, pooling layer2 of a  $2 \times 2$  matrix size will follow. The process in pooling layer2 is same as pooling layer1. After pooling layer2 the system will generate three sets of  $3 \times 3$  matrices as the input of the flatten layer. In the flatten layer, the matrix will be serial data, where 27 individual 64-bit data will produce a 1728-bit output. Fully connected layer1 (FC1) will use those 27 individual pieces of data to multiply with a  $27 \times 20$  weight array. After that, 20 results will be generated, and all those results will add with corresponding bias. The results obtained from FC1 will enter the ReLU activation layer. The function for this layer is to find the result which is bigger than logic 0. If the result is bigger than logic 0, the output will be itself. If not, the result for the input logic number will be logic 0 (here, the ReLU activation function is simulated by hardware).

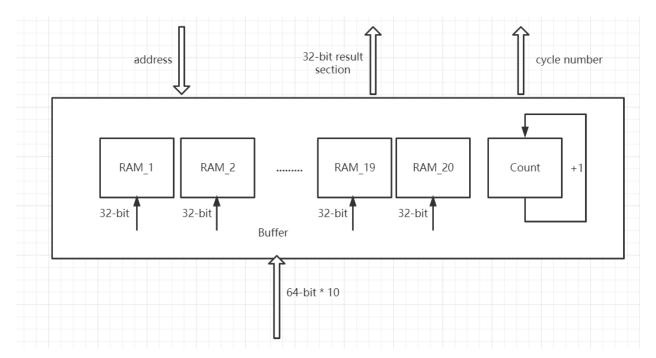

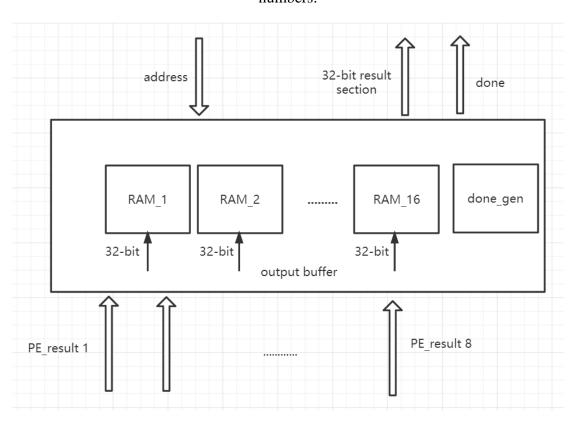

After the activation layer matrix, data will pass the final FC2 layer to get the result. It will then multiply with the FC2 array, which is size  $20 \times 10$ , the process in FC2 is same with FC1. In the end, the FC layers will get ten 64-bit binary number representing the probability of each decimal number from 0 to 9. The product will be divided into two 32bits and transmitted back to the PS through AXI lite, as shown in Figure 3.5. Each time the PS part will send the 32-bit address signal to the output buffer by AXI protocol, each address points to a corresponding RAM in output

buffer. PS part will send the data in sequence to traverse each RAMs with count block in the output buffer, then all the results will be sent back to the ARM core in PS, each time with a 32-bit result section.

At the same time, the final data will be accompanied by a number of rounds of this operation. As shown in the output buffer structure, the count block will add logic 1 after each entire calculate done, and the cycle number will also be transmitted to the PS part. Then, the PS terminal will be transmitted through UART and displayed on the host PC. The host PC will also generate a file for recording, including the test result and the test information.

Figure 3.5 Output buffer structure

The PS side here does not participate in calculations, it only performs UART data transmission and send configuration data to PL part. According to the comparison with the MNIST on the PC side, the accuracy for this Streaming architecture version implemented on a FPGA is after 4 decimal places.

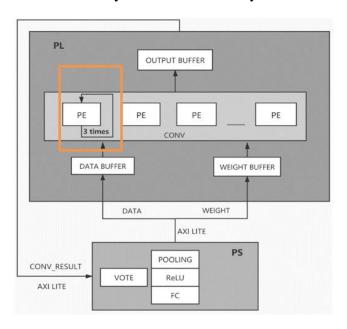

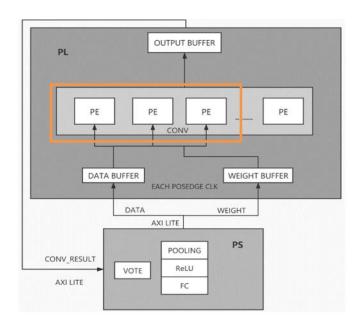

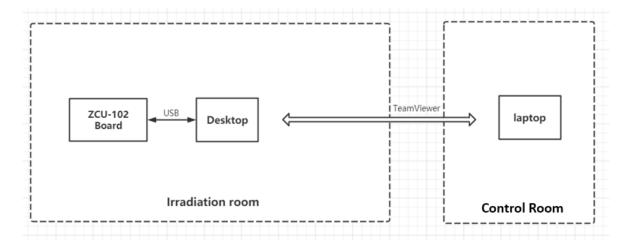

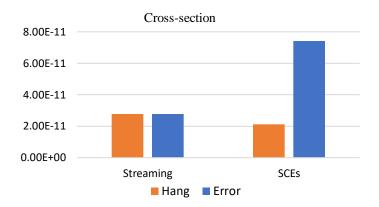

#### 3.1.3 SCEs Architecture