### A Thesis Submitted for the Degree of PhD at the University of Warwick

Permanent WRAP URL:

http://wrap.warwick.ac.uk/158274

### Copyright and reuse:

This thesis is made available online and is protected by original copyright. Please scroll down to view the document itself. Please refer to the repository record for this item for information to help you to cite it. Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

### Towards the Use of Mini-Applications in Performance Prediction and Optimisation of Production Codes

by

Andrew Martin Buchanan Owenson

Thesis

Submitted to the University of Warwick

in partial fulfilment of the requirements

for admission to the degree of

Doctor of Philosophy

**Department of Computer Science**

March 2020

## Contents

| List of | Table          | S                                               | $\mathbf{iv}$ |

|---------|----------------|-------------------------------------------------|---------------|

| List of | Figur          | es                                              | $\mathbf{v}$  |

| Ackno   | wledgr         | nents                                           | viii          |

| Declar  | ations         |                                                 | ix            |

| Abstra  | nct            |                                                 | x             |

| Acrony  | $\mathbf{yms}$ |                                                 | xiii          |

| Chapte  | er 1 I         | introduction                                    | 1             |

| 1.1     | Motiv          | ation                                           | 3             |

| 1.2     | Contr          | ibutions                                        | 4             |

| 1.3     | Thesis         | s overview                                      | 4             |

| Chapte  | er 2 F         | Parallel computing and profiling                | 6             |

| 2.1     | Parall         | el computing                                    | 6             |

|         | 2.1.1          | Vector processing                               | 6             |

|         | 2.1.2          | Instruction-level parallelism                   | 8             |

|         | 2.1.3          | Multi-core processing                           | 10            |

| 2.2     | Perfor         | mance profiling                                 | 11            |

|         | 2.2.1          | Runtime metrics                                 | 12            |

|         | 2.2.2          | Performance counters                            | 14            |

| 2.3     | Mini a         | applications                                    | 15            |

|         | 2.3.1          | Characterising similarity                       | 16            |

| 2.4     | Perfor         | mance modelling                                 | 17            |

|         | 2.4.1          | Performance projection                          | 17            |

|         | 2.4.2          | Mechanistic modelling of superscalar processors | 18            |

| 2.5                         | Summary                                                                                                                                                                                                              | 20                                                                                                                     |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Chapte                      | er 3 Computational Fluid Dynamics, Software and Hardware                                                                                                                                                             | <b>21</b>                                                                                                              |

| 3.1                         | HYDRA                                                                                                                                                                                                                | 21                                                                                                                     |

|                             | 3.1.1 Unstructured grid                                                                                                                                                                                              | 21                                                                                                                     |

|                             | 3.1.2 Multigrid                                                                                                                                                                                                      | 24                                                                                                                     |

|                             | 3.1.3 OPlus                                                                                                                                                                                                          | 25                                                                                                                     |

| 3.2                         | HYDRA performance engineering                                                                                                                                                                                        | 25                                                                                                                     |

|                             | 3.2.1 HYDRA performance model                                                                                                                                                                                        | 25                                                                                                                     |

|                             | 3.2.2 MG-CFD proxy-application                                                                                                                                                                                       | 27                                                                                                                     |

| 3.3                         | Summary                                                                                                                                                                                                              | 30                                                                                                                     |

| Chapte                      | er 4 Assessing and improving the proxy-application MG-CFD                                                                                                                                                            | 33                                                                                                                     |

| 4.1                         | Reviewing representativeness of MG-CFD                                                                                                                                                                               | 33                                                                                                                     |

|                             | 4.1.1 Arithmetic intensity                                                                                                                                                                                           | 33                                                                                                                     |

|                             | 4.1.2 Data-safe parallel computation                                                                                                                                                                                 | 36                                                                                                                     |

|                             | 4.1.3 Validation of restored MG-CFD                                                                                                                                                                                  | 36                                                                                                                     |

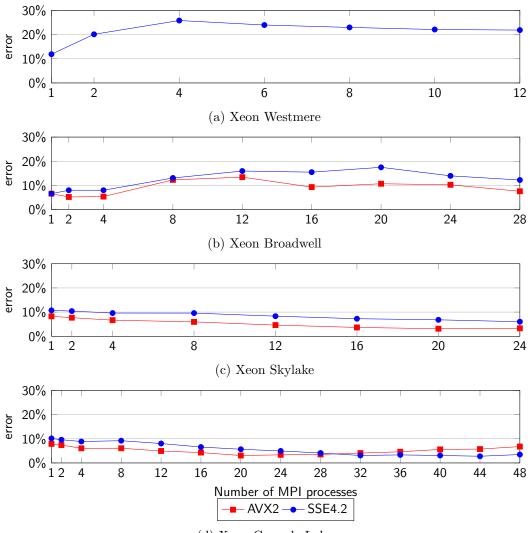

| 4.2                         | MPI strong scaling                                                                                                                                                                                                   | 38                                                                                                                     |

| 4.3                         | Summary                                                                                                                                                                                                              | 41                                                                                                                     |

|                             |                                                                                                                                                                                                                      | 42                                                                                                                     |

| -                           | er 5 Performance model of MG-CFD                                                                                                                                                                                     | <b>42</b><br>43                                                                                                        |

| 5.1                         | MG-CFD IPC investigation                                                                                                                                                                                             | 43<br>44                                                                                                               |

| 5.2                         | Performance model development                                                                                                                                                                                        |                                                                                                                        |

| гo                          | 5.2.1 Difference model                                                                                                                                                                                               | 45                                                                                                                     |

| 5.3                         |                                                                                                                                                                                                                      | 45                                                                                                                     |

| ۲.4                         | CPI estimation                                                                                                                                                                                                       | 50                                                                                                                     |

| 5.4                         | CPI estimation                                                                                                                                                                                                       | 50<br>52                                                                                                               |

| $5.4 \\ 5.5$                | CPI estimation                                                                                                                                                                                                       | $50 \\ 52 \\ 54$                                                                                                       |

|                             | CPI estimation                                                                                                                                                                                                       | 50<br>52<br>54<br>54                                                                                                   |

| 5.5                         | CPI estimationModel validationPredicting strong scaling5.5.1Memory benchmarking5.5.2Predicting performance of HYDRA                                                                                                  | 50<br>52<br>54<br>54<br>59                                                                                             |

|                             | CPI estimation                                                                                                                                                                                                       | 50<br>52<br>54<br>54<br>59<br>62                                                                                       |

| 5.5                         | CPI estimationModel validationPredicting strong scaling5.5.1Memory benchmarking5.5.2Predicting performance of HYDRAVectorising unstructured grid compute5.6.1Conflict avoidance                                      | 50<br>52<br>54<br>54<br>59<br>62<br>62                                                                                 |

| 5.5                         | CPI estimationModel validationPredicting strong scaling5.5.1Memory benchmarking5.5.2Predicting performance of HYDRAVectorising unstructured grid compute5.6.1Conflict avoidance5.6.2Vectorisation performance        | 50<br>52<br>54<br>54<br>59<br>62<br>62<br>63                                                                           |

| 5.5                         | CPI estimationModel validationPredicting strong scaling5.5.1Memory benchmarking5.5.2Predicting performance of HYDRAVectorising unstructured grid compute5.6.1Conflict avoidance                                      | 50<br>52<br>54<br>54<br>59<br>62<br>62                                                                                 |

| 5.5<br>5.6<br>5.7           | CPI estimationModel validationPredicting strong scaling5.5.1Memory benchmarking5.5.2Predicting performance of HYDRAVectorising unstructured grid compute5.6.1Conflict avoidance5.6.2Vectorisation performance        | $50 \\ 52 \\ 54 \\ 54 \\ 59 \\ 62 \\ 62 \\ 63 \\ 63$                                                                   |

| 5.5<br>5.6<br>5.7           | CPI estimationModel validationPredicting strong scaling5.5.1Memory benchmarking5.5.2Predicting performance of HYDRAVectorising unstructured grid compute5.6.1Conflict avoidance5.6.2Vectorisation performanceSummary | 50<br>52<br>54<br>54<br>59<br>62<br>62<br>63<br>66                                                                     |

| 5.5<br>5.6<br>5.7<br>Chapte | CPI estimation                                                                                                                                                                                                       | <ul> <li>50</li> <li>52</li> <li>54</li> <li>59</li> <li>62</li> <li>62</li> <li>63</li> <li>66</li> <li>67</li> </ul> |

| 6.2.2 | MG-CFD strong scaling optimisation | 71 |

|-------|------------------------------------|----|

|       |                                    |    |

# List of Tables

| 3.1 | Significant constituents of HYDRA runtime, measured on a single    |    |

|-----|--------------------------------------------------------------------|----|

|     | node of Xeon Broadwell with 28 MPI processes                       | 22 |

| 3.2 | Hardware/software configurations                                   | 32 |

|     |                                                                    |    |

| 5.1 | Relative cost of double-precision FP DIV and SQRT instructions     |    |

|     | relative to MUL, in clock cycles                                   | 43 |

| 5.2 | Single-thread compact-HYDRA runtime prediction errors of the three |    |

|     | described models                                                   | 52 |

| 5.3 | Model error statistics of predicted vflux compute strong scaling   | 61 |

# List of Figures

| 2.1 | 5-stage pipeline of instruction fetch (IF), decode (ID), execute (EX),  |    |

|-----|-------------------------------------------------------------------------|----|

|     | memory read (MEM), write result (WB). Column of highlighted stages      |    |

|     | are performed simultaneously                                            | 8  |

| 2.2 | Instruction dispatch and issue stages of Xeon Skylake pipeline [28] .   | 9  |

| 2.3 | Comparison of single-core (left) and multi-core (right) design. Single- |    |

|     | core designs have one integrated memory controller (IMC) and two        |    |

|     | levels of cache. Multi-core typically has a third level of cache shared |    |

|     | by all cores, and server-grade designs have multiple IMCs for more      |    |

|     | bandwidth.                                                              | 11 |

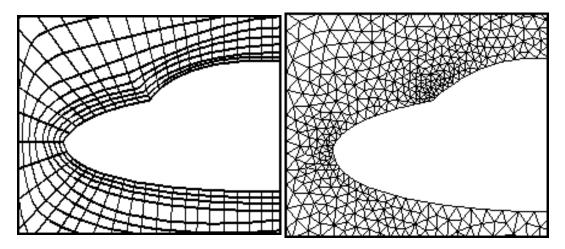

| 3.1 | Comparison of structured and unstructured grid [62]                     | 22 |

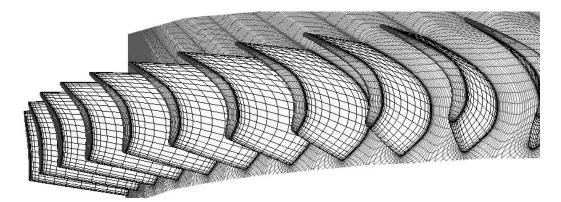

| 3.2 | Visualisation of a rotor section from NASA's SSME 2-stage fuel          |    |

|     | turbine, similar to the meshes used in this work.                       | 24 |

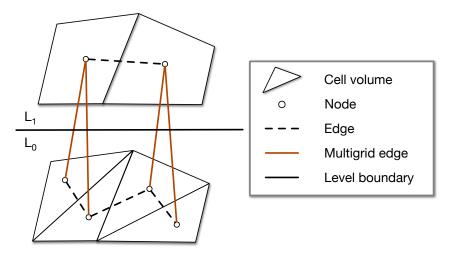

| 3.3 | Representation of a finite-volume decomposition mapped to an un-        |    |

|     | structured grid over two multigrid levels                               | 25 |

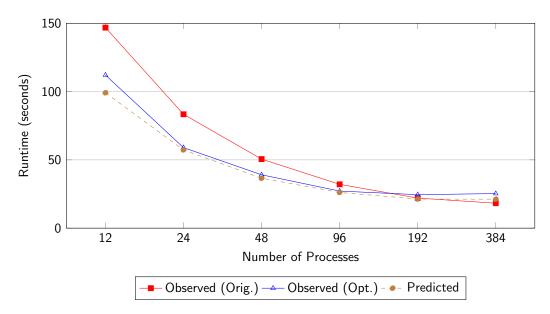

| 3.4 | HYDRA observed performance, before and after optimisation, and the      |    |

|     | performance model predictions. Model highlighted sub-optimal per-       |    |

|     | formance, caused by nonblocking asynchronous MPI communication          |    |

|     | not overlapping with compute. Switching to nonblocking synchronous      |    |

|     | MPI improved overlapping, matching model.                               | 27 |

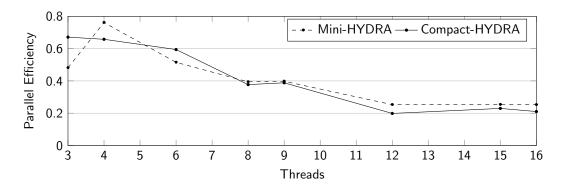

| 3.5 | Parallel efficiency of mini-HYDRA and compact-HYDRA on Xeon             |    |

|     | Haswell                                                                 | 29 |

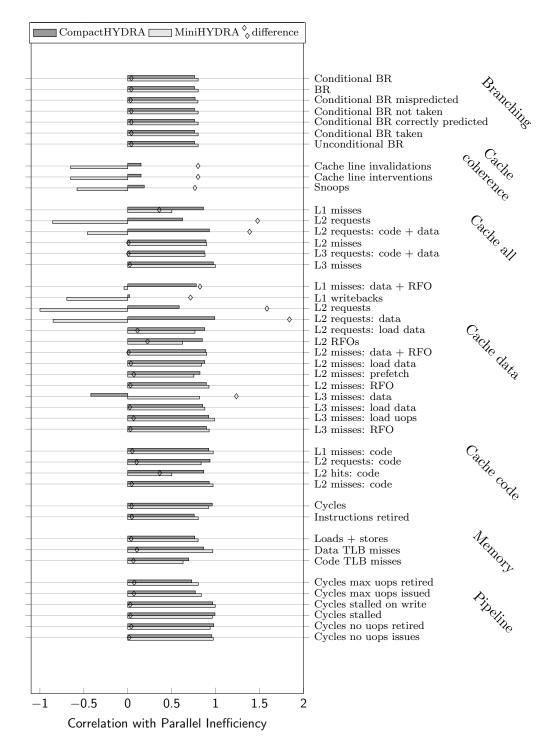

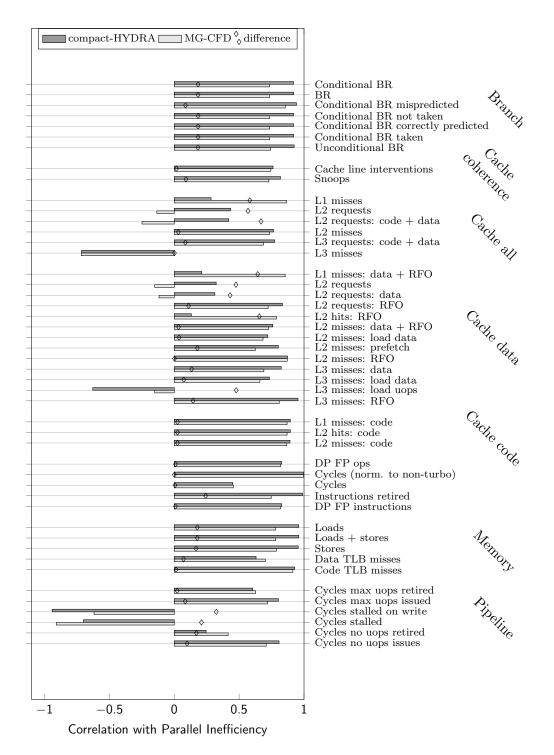

| 3.6 | Plot of correlation between parallel efficiency loss and various PAPI performance counters for MG-CFD and compact-HYDRA on Xeon Haswell. The difference in correlation between MG-CFD and compact-HYDRA is also plotted, which can exceed 1.0 for serious divergence (worst case is $\pm 2$ ). Major divergence occurs with events relating to L1-L2 data traffic. Negligible divergence (i.e. high similarity) in events relating to L2-L3 traffic and pipeline utilisation. | 31       |

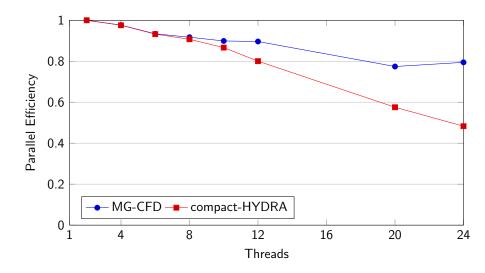

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

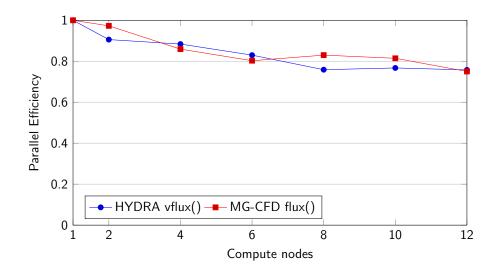

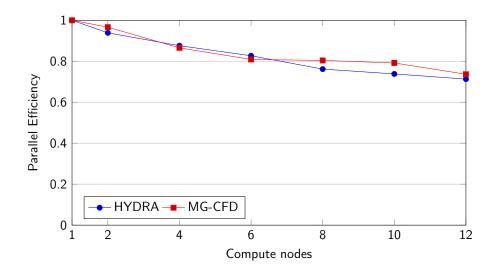

| 4.1 | Parallel efficiency of compact-HYDRA and numerically-corrected MG-CFD, on Xeon Skylake with AVX-512 auto-vectorisation. Similar scaling exhibited until compact-HYDRA hits its memory-bound near                                                                                                                                                                                                                                                                              |          |

| 4.2 | 12 threads                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 34       |

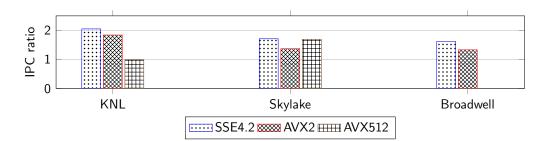

| 4.3 | KNL (and Skylake)                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35       |

| 4.4 | Xeon Skylake                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37       |

| 4.5 | expensive HYDRA routine vflux and OP2-MG-CFD flux() routine .<br>MPI strong scaling parallel efficiency on Westmere cluster, of total<br>walltime of HYDRA and OP2-MG-CFD                                                                                                                                                                                                                                                                                                     | 39<br>40 |

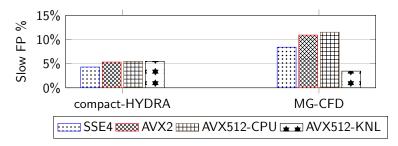

| 5.1 | Proportion of floating-point (FP) instructions in flux loop that are                                                                                                                                                                                                                                                                                                                                                                                                          |          |

|     | relatively 'slow', meaning low throughput                                                                                                                                                                                                                                                                                                                                                                                                                                     | 44       |

| 5.2 | Instruction dispatch and issue stages of Xeon Skylake pipeline $\left[28\right]$ .                                                                                                                                                                                                                                                                                                                                                                                            | 47       |

| 5.3 | Ideal scheduling model of instructions to execution ports within Sky-                                                                                                                                                                                                                                                                                                                                                                                                         |          |

|     | lake. Instructions with fewest compatible ports are scheduled first. $% \left( {{{\bf{n}}_{{\rm{s}}}}} \right)$ .                                                                                                                                                                                                                                                                                                                                                             | 48       |

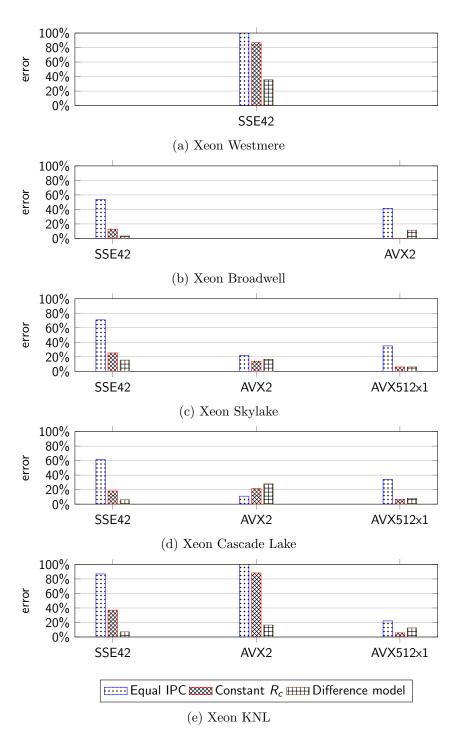

| 5.4 | Model prediction errors of single-threaded compact-HYDRA cycle                                                                                                                                                                                                                                                                                                                                                                                                                |          |

|     | consumption.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53       |

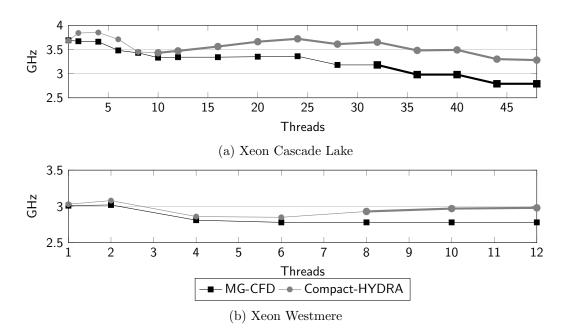

| 5.5 | Relationship between multicore load and observed turbo GHz. Bold<br>line indicates when code is memory-bound, thin line when compute-<br>bound. When both codes are compute-bound they operate at similar<br>clock speed, important for model accuracy.                                                                                                                                                                                                                       | 56       |

|     | r                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55       |

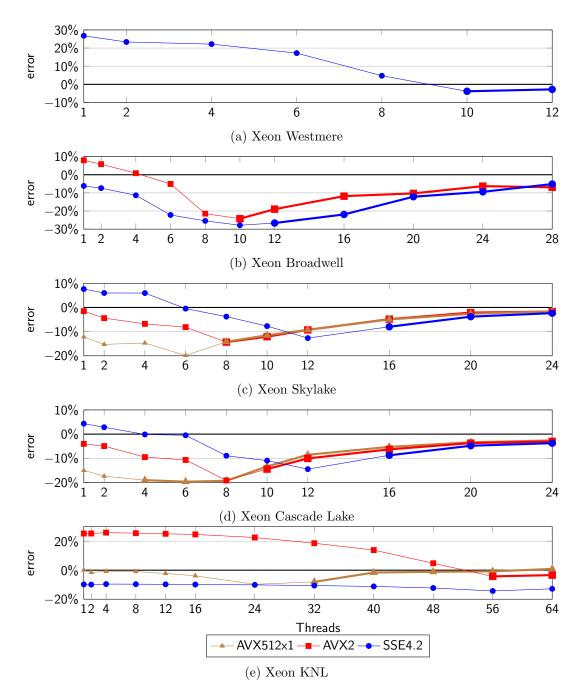

| 5.6  | Model prediction errors of compact-HYDRA strong scaling. A negative    |    |

|------|------------------------------------------------------------------------|----|

|      | error represents an under-prediction of actual performance. Bold line  |    |

|      | indicates when predicted performance is memory-bound, thin line        |    |

|      | when compute-bound. Cascade Lake sequence clipped at 24 threads        |    |

|      | for brevity                                                            | 57 |

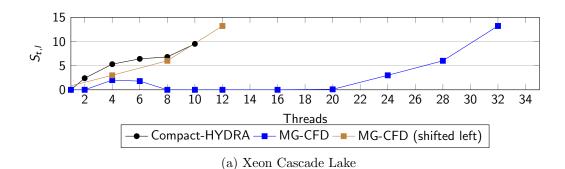

| 5.7  | Relationship between thread count and stalled cycles for compact-      |    |

|      | HYDRA and MG-CFD, at compute-bound thread counts. Each kernel          |    |

|      | encounters increasing penalty of similar size when approaching $t_b$ , |    |

|      | made clear by shifting MG-CFD datapoints                               | 58 |

| 5.8  | Model error of predicted HYDRA vflux() compute strong scaling          | 60 |

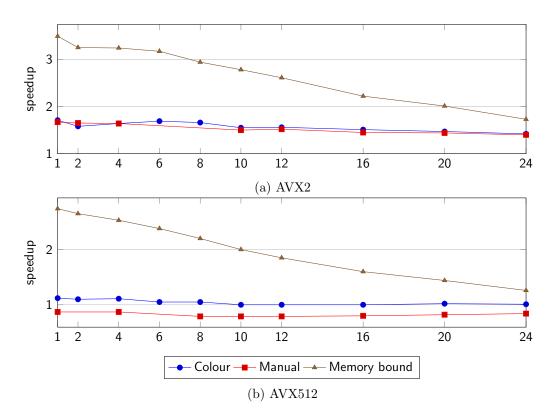

| 5.9  | Vectorisation speedups with two conflict-avoidance schemes on Xeon     |    |

|      | Skylake. Also shown is maximum speedup permitted by achievable         |    |

|      | memory performance.                                                    | 64 |

| 5.10 | MG-CFD GHz with and without vectorisation. Only with $\mathrm{AVX512}$ |    |

|      | does vectorisation reduce $\operatorname{GHz}$                         | 65 |

| 5.11 | Changes to floating-point quantity and throughput in vectorised MG-    |    |

|      | CFD. Increased quantity or lower throughput reduces achievable speedup | 65 |

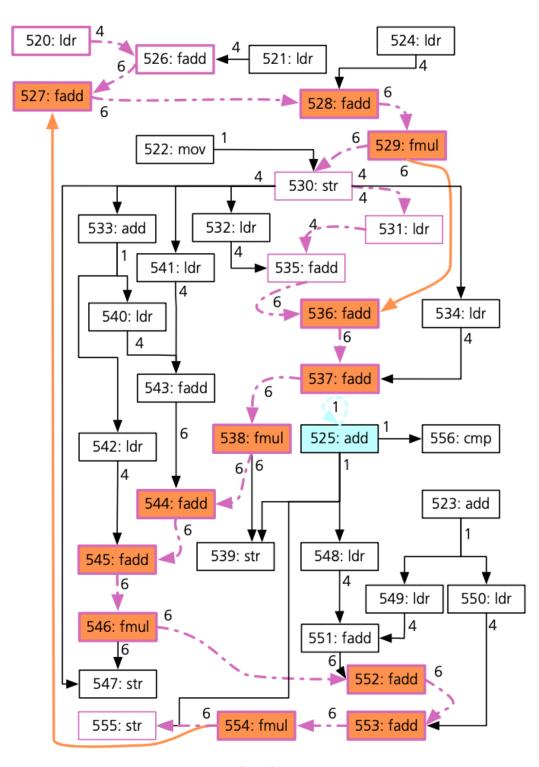

| 6.1  | Critical path detection (pink) by OSACA tool, of Gause-Seidel loop on  |    |

|      | TX2 architecture [34]. Path numbers are instruction latency (cycles-   |    |

|      | per-instruction (CPI)), in-box numbers are disassembly line numbers.   |    |

|      | Performance predicted to be bound mostly by floating-point execution.  | 70 |

### Acknowledgments

First and foremost, I must thank my supervisor, Prof. Stephen Jarvis, for the opportunity to undertake this Ph.D., and for his confidence in me, his enthusiasm, and his guidance and support throughout.

I also must thank past and present members of the High Performance and Scientific Computing group, with special thanks to: Dr. Steven Wright, Dr. Richard Bunt, Dr. James Davis, Prof. Gihan Mudalige, and Dean Chester. Thanks for the mentoring, the discussions, and the prompt support.

This work would not be possible without outside collaboration and sponsorship. I thank the opportunity to collaborate with Rolls-Royce, with special thanks to Dr. Yoon Ho and Matthew Street for their critical support. I also wish to thank Intel for initiating the collaboration, and their technical support throughout.

Lastly, I thank my family for support and encouragement throughout.

### Declarations

This thesis is submitted to the University of Warwick in support of my application for the degree of Doctor of Philosophy. It has been composed by myself and has not been submitted in any previous application for any degree. The work presented (including data generated and data analysis) was carried out by the author except in the cases outlined below:

• The initial development and validation of MG-CFD as a representative miniapplication of HYDRA, described in Chapter 3, was performed by Dr. Richard Bunt. Where this thesis also develops MG-CFD, it is to address deficiencies and improve representativeness.

Parts of this thesis have been previously published by the author in the following:

- [44] A. Owenson, S. Wright, R. Bunt, S. Jarvis, Y. Ho, and M. Street. Developing and using a geometric multigrid, unstructured grid mini-application to assess many-core architectures. In <u>2018 26th Euromicro International Conference on</u> Parallel, Distributed and Network-based Processing (PDP), pages 68–76, 2018

- [45] A. Owenson, S. Wright, R. Bunt, Y. Ho, M. Street, and S. Jarvis. An unstructured cfd mini-application for the performance prediction of a production cfd code. Concurrency and Computation: Practice and Experience, 2019

### Abstract

Maintaining the performance of large scientific codes is a difficult task. To aid in this task a number of mini-applications have been developed that are more tractable to analyse than large-scale production codes, while retaining the performance characteristics of them. These "mini-apps" also enable faster hardware evaluation, and for sensitive commercial codes allow evaluation of code and system changes outside of access approval processes.

Techniques for validating the representativeness of a mini-application to a target code are ultimately qualitative, requiring the researcher to decide whether the similarity is strong enough for the mini-application to be trusted to provide accurate predictions of the target performance. Little consideration is given to the sensitivity of those predictions to the few differences between the mini-application and its target, how those potentially-minor static differences may lead to each code responding very differently to a change in the computing environment.

An existing mini-application, 'Mini-HYDRA', of a production CFD simulation code is reviewed. Arithmetic differences lead to divergence in intra-node performance scaling, so the developers had removed some arithmetic from Mini-HYDRA, but this breaks the simulation so limits numerical research. This work restores the arithmetic, repeating validation for similar performance scaling, achieving similar intra-node scaling performance whilst neither are memory-bound. MPI strong scaling functionality is also added, achieving very similar multi-node scaling performance.

The arithmetic restoration inevitably leads to different memory-bounds, and also different and varied responses to changes in processor architecture or instruction set. A performance model is developed that predicts this difference in response, in terms of the arithmetic differences. It is supplemented by a new benchmark that measures the memory-bound of CFD loops. Together, they predict the strong scaling performance of a production 'target' code, with a mean error of 8.8% (s = 5.2%). Finally, the model is used to investigate limited speedup from vectorisation despite not being memory-bound. It identifies that instruction throughput is significantly reduced relative to serial counterparts, independent of data ordering in memory, indicating a bottleneck within the processor core.

### **Sponsorships and Grants**

This research is supported by

- 1. Rolls-Royce plc.

- 2. EU Horizon 2020 Clean Sky Project

- 3. UK Engineering and Physical Sciences Research Council (EPSRC)

- 4. Intel Corporation

Funding sources are: EP/S005072/1 - Strategic Partnership in Computational Science for Advanced Simulation and Modelling of Engineering Systems (ASiMoV); EPSRC Industrial CASE award 15220082

### Acronyms

- **ASiMoV** Advanced Simulation and Modelling of Engineering Systems.

- **AVX** advanced vector extensions.

- **BSP** bulk synchronous parallel.

- **CFD** computational fluid dynamics.

- **CISC** complex instruction set computing.

- **CPI** cycles-per-instruction.

- DAG directed acyclic graph.

- **DNN** deep neural network.

- **DSL** domain-specific abstraction library.

- **DT** data throughput.

- FLOPs floating-point operations per second.

- FMA fused multiply-accumulate.

- FP floating-point.

- FPGA field-programmable gate array.

- ${\bf FU}$  functional unit.

- GPGPU general purpose graphic processing unit.

- GPU graphic processing unit.

- HBM high-bandwidth memory.

- **HPC** high-performance computing.

HT high-throughput.

**IDQ** instruction decode queue.

**ILP** instruction-level parallelism.

**IMC** integrated memory controller.

**IP** intellectual property.

**IPC** instructions-per-cycle.

**ISA** instruction set architecture.

**KNL** Knights Landing.

LT low-throughput.

MG multigrid.

MIMD multiple instruction, multiple data.

$\mathbf{MSR}$  model-specific register.

**OSACA** Open-Source Architecture Code Analyzer.

**PAPI** performance application programming interface.

PGAS partitioned global address space.

**QAP** quadratic assignment problem.

**RFO** read-for-ownership.

**RISC** reduced instruction set computing.

**RK** Runge-Kutta.

${\bf SIMD}\,$  single instruction, multiple data.

**SIMT** single instruction, multiple thread.

**SSE** streaming SIMD extensions.

### Chapter 1

### Introduction

Computational simulation of physical phenomena have become an important component of scientific discovery and engineering design. It can be cheaper and faster than physical experiments, informing and directing early-stage research and design. Simulation can also be necessary when real-world testing is highly challenging, such as assessing aerodynamic performance of a full-scale airframe that is far too large for a wind tunnel [23], or simply illegal. Achieving accurate simulations require the use of a supercomputer, a computing system specialising in numerical computation with performance several magnitudes greater than a typical household or office computer.

One industry quick to adopt computational simulation is aerospace engineering. Initially adopted by national organisations for the design of space and military aircraft, computational fluid dynamics (CFD) soon spread throughout the aerospace industry. CFD has become an essential tool for the historic improvement of airframes and engine turbomachinery, driving improvements to fuel economy and noise pollution [30] [40]. These improvements must continue into the future to further reduce emissions, increasingly demanded by people and Governments, requiring further improvements to the scope and performance of CFD simulations [22].

Early supercomputers consisted of a small number of complex processors specalised at performing floating-point arithmetic, eagerly adopted by national research and defense laboratories such as CERN in Europe and Los Alamos National Laboratory in the United States [12]. This early system design culminated in achieving approximately 1 billion floating-point operations per second (GFLOP/s), but limits of the design and demand for more performance drove a transition to more parallel systems, consisting of a large number of simpler processors executing in parallel (often called a *cluster*). Economics drove a later transition to general-purpose commodity processors. Processor performance steadily improved as transistors shrunk, increasing operating frequency and density, but this Dennard scaling ended around 2006 as heat and power leakage imposed physical limits - this accelerated the transition into parallelism with multicore CPUs. The one PetaFLOP/s (1 million GFLOPS/s) milestone was passed in 2008, sparking the discussion around how to achieve the next 1000x increase in performance to one ExaFLOP/s. Incorporating projections of expected technology progress, an exascale system would consume 100 MW, an unacceptable amount of power in terms of operating cost and pressure on the local power grid [5]. The exascale challenge emerged with the primary goal of achieving 1 ExaFLOP/s within a 20 MW power cap. This has led to a greater variety of computing architectures, and greater heterogeneity in cluster configurations, in the search for energy efficiency. Particularly, greater adoption of general purpose graphic processing units (GPGPUs) and reduced instruction set computing (RISC) CPU architectures - no supercomputer can meet the exascale challenge without being primarily composed of one of these. More exotic architectures are available offering even greater energy efficiency such as field-programmable gate arrays (FPGAs), but these are difficult to program so remain experimental and areas of research.

The current high-performance computing (HPC) landscape of varied hardware and heterogeneous clusters presents challenges to both cluster operators and users. For operators purchasing an upgrade or new system, they face the complex question of what hardware to select, and in which configuration. They must also factor in the needs of their users, that the change in architecture does not cause unacceptable frustration and prevent important research and simulations. Users must be increasingly prepared to 'port' their software to new architectures and parallelism technologies, meaning to tailor their code execution and data movement to conform well to the architecture design; alternatively, they can select and integrate an appropriate parallel programming abstraction or framework that performs this tailoring behind-the-scenes (such as OpenCL/SYCL, Kokkos, or OP2).

For a simulation application to exploit the performance offered by a modern supercomputer it must be highly parallel, and increasingly incorporate new optimisations and technologies. This is challenging for large legacy codes, as any performance improvement is unknown until after significant time has been invested in software development. Some of these codes face the additional challenge of being proprietary or even classified, impeding the evaluation of potential computing system upgrades – hardware evaluation prior to purchase is integral to system procurement, as application performance depends on more than just the advertised FLOP/s rate. These challenges have spurred the development of 'mini-applications', small codes that capture the key performance characteristics of a target application, either by containing critical portions of that application or consisting of measurably-similar unrestricted code. This target code can also be referred to as the 'parent' of the mini-application. Where the mini-application shares no code with its parent, but through evaluation is verifed to still capture key characteristics, then it is useful to refer to this instead as a *proxy*-application. The uses of a mini-application derive from the code being much smaller than its parent code, so it is quicker to modify and debug, and easier to compile on new systems. Common use cases are (i) implementing a potential optimisation in code, such as rearranging how data is stored in memory, (ii) evaluating a parallel programming abstraction, such as contrasting partitioned global address space (PGAS) with MPI regarding usability and performance, and (iii) porting to a new processor architecture. The goal of each is to improve the performance of the parent code on current hardware, or to improve the transition of the parent code to new hardware.

### 1.1 Motivation

Upon the outset of research, the goal was to use an existing proxy-application of a production CFD code, named mini-HYDRA and HYDRA respectively, to address two specific challenges faced by HYDRA. One is to use mini-HYDRA to collect performance data to calibrate an existing performance model of HYDRA, then used to generate performance predictions - this can inform supercomputer scheduling decisions, and accelerate benchmarking of novel hardware. The second challenge is to identify optimisation opportunities with mini-HYDRA that will transfer to HYDRA. allowing it to better utilise the increasing complexity in processor architectures. Mini-HYDRA had been validated using to a published technique that was previously used to validate another unrelated proxy-application, where those original authors then used their validated proxy-application to make predictive assessments of the performance of its target code [59]. However it became clear that while mini-HYDRA had been validated correctly, this technique is ultimately qualitative, as relatively minor static differences between it and the production code can lead to predictive assessments being significantly incorrect, e.g. of predicting no change in performance from a change of instruction set when in fact the target code experiences a significant slowdown.

Given that the proxy-application is more similar than it is different, this poses the question of whether modelling can *transform* proxy-application performance data to the target, allowing the proxy-application to provide accurate quantitative performance prediction.

### **1.2** Contributions

This thesis makes the following contributions:

- Review mini-HYDRA, an existing proxy-application of the production CFD code HYDRA. Restore arithmetic to correct its CFD, and repeat validation inevitably some similarity is lost due to different memory-bounds and arithmetic constituents. Add MPI strong scaling, validation shows high similarity in multi-node scaling.

- Presents a new performance projection model for HYDRA, accounting for differences between it and its proxy-application (now called MG-CFD), with which it is possible to project from MG-CFD to HYDRA performance on a range of existing and emerging HPC architectures. This is highly significant for Rolls-Royce plc. as they increase their use of virtual certification and simulation-based engine design;

- Demonstrates that it is possible to use a proxy-application and performance modelling to predict the performance of a production 'target' code, predicting runtime of most expensive loop under strong scaling with a mean error of 8.8% (s = 5.2%);

- Combine MG-CFD and the performance model to assess efficacy of autovectorising unstructured grid compute. Identifies that vectorised floating-point throughput is approximately half that of serial execution, independent of mesh ordering, indicating a bottleneck within the processor core. Allows expectations of achievable speedup of target application to be determined, not relying on the theoretical maximum of e.g.  $4\times$ .

### 1.3 Thesis overview

- Chapter 2 covers technical concepts regarding parallel computation and performance analysis. It describes techniques that processor manufacturers have designed to provide parallel computation; modelling techniques for predicting performance of a code; and tools for collecting relevant performance data.

- Chapter 3 introduces Rolls-Royce 'HYDRA', a CFD simulation code, detailing aspects of its design that makes HPC challenging. An overview of how HYDRA currently achieves parallel execution is also provided. Finally, an existing proxy-application of HYDRA is summarised, then named mini-HYDRA.

- **Chapter 4** reviews MG-CFD in detail (formerly named mini-HYDRA), discussing particular challenges faced when designing a proxy-application. Prior modifications made to the CFD to improve a particular aspect of performance similarity are reversed, as they undermine capture of the key computational property influencing performance. This modified code is re-validated, and an alternative solution to challenge is proposed. MG-CFD is further improved with MPI strong scaling, for multi-node performance assessment

- Chapter 5 delves deeper into the differences between HYDRA and its proxyapplication, and why these lead to difficulty relating performance from the proxy-application to HYDRA loops. A performance model is developed, that seeks to predict the performance difference between the proxy-application and a HYDRA loop, from the known differences in code. Model prediction accuracy is evaluated across several architectures and ISAs. Finally, the model is used to explore the efficacy of vectorising this class of code, identifying that speedup is limited by lower throughput of vectorised FP instructions.

- Chapter 6 concludes this thesis with a summary of the work performed, revisiting key arguments and outcomes. Limitations of the work in its current form are discussed, and future work that can address these are detailed.

### Chapter 2

### Parallel computing and profiling

### 2.1 Parallel computing

With the end of Dennard scaling, further improvements in computation throughput have been realised through increasing parallelisation. There are several ways by which this can be achieved. Common approachs are instruction-level parallelism (ILP), vector processing, and multi-core processors.

#### 2.1.1 Vector processing

Vector processing, or single instruction, multiple data (SIMD) execution, is the application of the same single operation on multiple data elements. The early vector processors that appeared in supercomputers during the 1970s were essentially data processors, designed to provide a steady stream of data into a scalar but pipelined arithmetic functional unit. The 1974 CDC STAR-100 vector processor streamed data direct from memory to the ALUs, so very wide vectors were needed to mask the latencies and setup costs [18]. The 1976 CRAY-1 introduced vector registers, 64 words wide. A loop of several instructions over 64 words or less can achieve good performance by chaining together a sequence of instructions, storing intermediate results in the registers [51].

The 1990s transition to commodity hardware and massively parallel processor clusters led to vector processing losing their importance, but slowly re-emerged several years later in commodity processors. These were initially 1 word wide in the MMX ISA and limited to integer operations, widening and supporting more data types with successive ISAs: SSE introduced 128-bit FP SIMD, SSE2 added double-precision FP, AVX extended to 256-bit, and AVX-512 extended further to 512-bit. These new SIMD operations differ to the early vector processors in one fundamental way, they execute one instruction on multiple data elements in lockstep, so as these vectors become wider the demand on memory performance increases proportionally. The data streaming function that was explicitly performed by older vector processors is now performed implicitly by hardware prefetchers that scan for patterns in the memory accesses, and by explicit prefetch instructions inserted into code.

#### SIMD instruction set architectures

An ISA is the interface between software and functional units within a processor. Being an interface and not an implementation, different processor architectures are free to implement the operations with different circuit designs, which can result in different throughputs of the same instruction. One example of deviation could be the decision of whether to add pipelining to the expensive FP division operation. An ISA is constituted of three parts: the instruction set itself, defining the available operations and their operands; the data types; the registers available for storing state. A SIMD ISA is typically an extension of a base ISA such as x86-64, providing additional operations and registers for vector computation. Recent major SIMD ISAs are SSE4, AVX2, and AVX-512.

- 1. **SSE4** provides 128-bit double-precision floating-point vector compute, supported by  $16 \times 128$ -bit vector registers.

- 2. **AVX2** provides 256-bit versions of SSE4 instructions and registers, and also switches from a two-operand to three-operand format which allows source code to be compiled to fewer instructions.

- 3. **AVX-512F** extends further to 512-bit, and adds an additional 16 registers for a total of 32.

Unlike previous SIMD ISAs, AVX-512 is composed of several subsets. AVX-512F (foundation) and AVX-512CD (conflict detection) are universal sets, implemented in all architectures that advertise any AVX-512 support. Then there are several extensions that are specific to certain architectures:

- 1. Intel Xeon Phi Knights Landing (KNL) implements AVX-512 PF and ER, providing new prefetch instructions and improved approximations of transcendental functions.

- 2. Intel Xeon processors (Skylake and later) implements AVX-512 DQ, BW and VL, support additional non-floating-point types and execution of AVX-512 instructions on sub-512-bit operands.

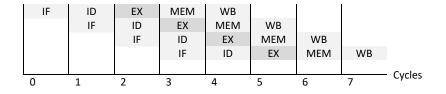

Figure 2.1: 5-stage pipeline of instruction fetch (IF), decode (ID), execute (EX), memory read (MEM), write result (WB). Column of highlighted stages are performed simultaneously.

Thus with AVX-512, a code that is auto-vectorised for different architectures that implement AVX-512F but with different subsets is likely to generate different machine code with differing performance.

#### 2.1.2 Instruction-level parallelism

Fundamentally, all software is compiled to a linear sequence of instructions, generally falling into the categories of data movement, branching, and arithmetic. In the typical fetch-decode-execute instruction cycle, each individual instruction is fetched, decoded, then executed. From early post-war computing efforts several ILP techniques were developed. One is pipelining, which splits the instruction cycle into distinct stages that are processed in a staggered fashion across several clock cycles. Although one individual instruction requires more clock cycles to complete, the processor can process different stages of different instructions simultaneously, increasing overall throughput. This is illustrated in Figure 2.1, which presents the 5-stage pipeline of fetch, decode, execute, memory read, write result, with 5 instructions being processed at different stages simultaneously.

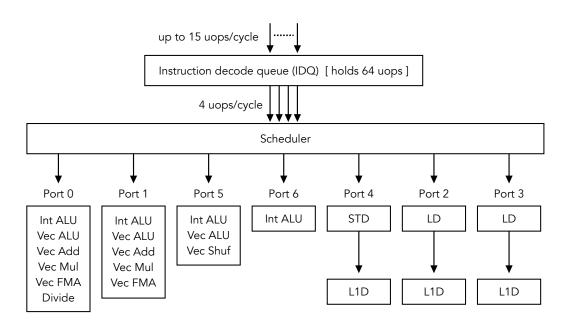

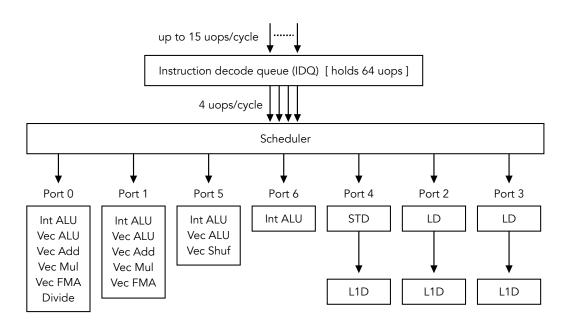

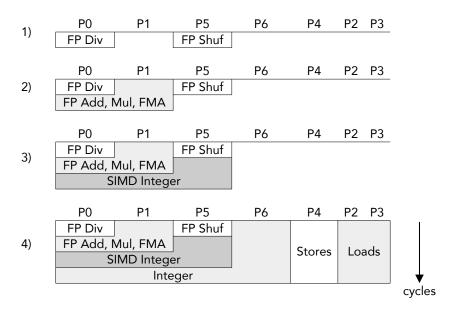

Another ILP technique exists in superscalar processors, which extends pipelining by supporting several parallel instances of each stage. The number of stage instances is a decision of processor architecture design, constrained by the available transistor budget and the need to balance throughput with the other stages. An example is shown in Figure 2.2, which shows for the Xeon Skylake architecture the pipeline portion regarding instruction dispatch to functional units, and memory R/W [28]. The instruction decode queue (IDQ) receives up to 15 decoded  $\mu$ -ops/cycle from three distinct instruction decoders.  $\mu$ -ops are a feature of complex instruction set computing (CISC), where assembly-level instructions can be mapped to several transistor-level micro-operations, for example to a memory load  $\mu$ -op and an arithmetic  $\mu$ -op. The IDQ then dispatches up to 4  $\mu$ -ops/cycle to the scheduler, in turn

Figure 2.2: Instruction dispatch and issue stages of Xeon Skylake pipeline [28]

dispatching to the appropriate functional units as they become free. The number and distribution of functional units is another architecture design decision, also constrained by the transistor budget and need to provide good performance to many different codes. In this example two FP functional units (FUs) reside across ports 0 and 1, and four integer FUs reside across ports 0, 1, 5 and 6. Thus a code consisting mostly of FP arithmetic and with a high arithmetic intensity will be bottlenecked by these two ports to a maximum of 2 FP operations/cycle, despite the plethora of other functional units and higher throughput of instruction decoding. Memory load and store FUs typically reside on separate ports, in this example on ports 2, 3 and 4. Understanding how a particular code flows through a particular processor pipeline can provide insight into how well it is utilising that architecture, and what architectural changes would improve its throughput.

The first superscalar processor was the Cray CDC 6660 in 1964, and this also introduced a third ILP technique - out-of-order execution. Complementing superscalar execution, this is an instruction scheduling strategy that opportunistically executes a sequence of instructions in a non-linear order to increase utilisation of superscalar resources, reducing overall runtime. The first scheduling algorithm was Thornton's 'scoreboard', that tracks availability of functional units and registers [57]. Data dependencies between instructions are implicitly handled by tracking the occupancy of registers. As resources become available, the scoreboard can dispatch queued instructions for execution. The Tomasulo algorithm was proposed and implemented several years later, improving the design with reservation stations distributed across the functional units, replacing the single centralised scoreboard [58]. These abstract away registers - an instruction now operates on logical registers, and the station selects whichever physical registers are available. Modern out-of-order execution logic has not changed significantly from this, using larger buffers as increasing transistor budgets permit, able to track approximately 50 instructions. The logical complexity consumes significant transistor resources, so is generally not present in low-cost or low-power processor designs.

#### 2.1.3 Multi-core processing

Dennard scaling was the primary driver of improvements in performance of MOSFET processors. This law states that as transistor size reduced, their power density was unchanged, so that voltage and current consumption each reduced proportionally to length [17]. This enabled chips to contain more transistors and operate at higher clock frequencies without increasing total chip power consumption, which is typically a hard limit. This law began to noticably break down as transistor lengths approached 65nm in 2005, as current leakage became a significant problem through wasting 50% of total power. Thus the useful power needed to be utilised more efficiently, and as power was proportional to the square of frequency then frequency increases had to end. New transistor designs and fabrication techniques were able to reduce current leakage, but the increased headroom was used for more transistors. Post-2005 processors continue to increase transistor counts, but have seen their operating frequencies stagnate; to continue improving performance they transitioned from single-core to multi-core designs.

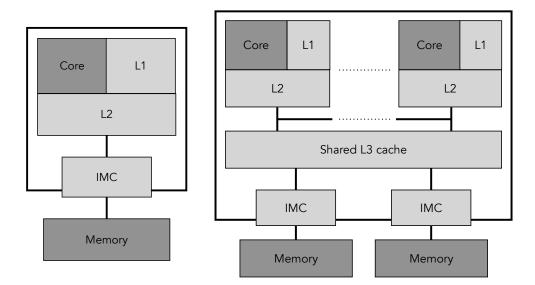

Where a "single core" processor contains a single core (the instruction pipeline) and one or two levels of cache memory, a multi-core processor contains multiples of these within a single silicon package (an example of multiple instruction, multiple data (MIMD)). A cache coherence protocol such as MESI is implemented to allow multiple cores to safely read/write on the same data (cached in their respective local caches) [46], and a typical multi-core processor has an additional level of cache shared between the cores. Figure 2.3 illustrates a typical server-grade multi-core processor, with many cores communicating over an interconnect bus, an additional level of shared cache, and an additional IMC to increase memory bandwidth.

For a computational workload to utilise multiple cores to increase its throughput, it must instantiate multiple and parallel strands of execution then distribute its workload among them. The former can be achieved using lightweight threads, each

Figure 2.3: Comparison of single-core (left) and multi-core (right) design. Single-core designs have one IMC and two levels of cache. Multi-core typically has a third level of cache shared by all cores, and server-grade designs have multiple IMCs for more bandwidth.

executing on a separate core; threads share the same address space, which provides an opportunity for greater data reuse; but this also limits them to reside within the same operating system session, in practice meaning the same computing node. An alternative to threads are processes, each of which has a separate and independent address space; typically these are used when threading is not possible, such as in a distributed memory system. Workload distribution requires that the input data arrays be partitioned, and that each thread or process be allocated one partition. Additionally, if the computation kernel is stencil-based, then data communication must be performed between cores of adjacent partitions.

### 2.2 Performance profiling

Performance profiling is the targeted collection of fine-grained performance data during code execution. Typically this is measurement of time duration using system timers, known as walltime, but can also include hardware performance counters that count events such as CPU cache hits and misses. There are two common methods for collecting this data, with different tradeoffs – sampling profilers, or source code instrumentation. A sampling profiler is particularly useful when source code is not modifiable, or when a quick analysis is required. At frequent intervals the profiler interrupts execution of the target code to record the executing function and its call stack, and may also record performance counter values. With sufficient sampling, the total runtime can be partitioned to the observed executing functions. Data accuracy is dependent on the frequency of sampling, and commerical profilers such as Cray CrayPat and Intel VTune use a default sampling interval of 10ms.

If fine accuracy or granularity is required but without the overhead issues of very frequent sampling, then the alternative to the sampling profiler is source code instrumentation. This is the insertion of data-collecting instrumentation directly into the source code of a target application, typically consisting of additional function calls to an external data aggregator that records provided data and finally writes to file. The direct insertion allows (i) the collected performance data to be directly associated with specific code blocks, (ii) for overhead costs to be controlled, and (iii) for non-performance data to be collected such as array sizes and variable values. Thus this provides the most accurate data, but for a comprehensive understanding then significant code modification is required; for a large application, comprehensive collection is only feasible with a tool that automatically inserts the instrumentation. Consideration must be given to the overhead of the instrumentation, and so is typically inserted around significant loops and pre-existing function calls rather than within.

Whichever method is used, the collected data is at the fine granularity of individual functions or loops, and for a parallel code the data is further broken down to individual processes or threads. This enables an understanding of which portions of the code are consuming the most time, and whether a parallel workload is being evenly distributed across processes. Further, it enables the calculation of performance metrics that concisely represent application performance, and enable comparison with other codes.

#### 2.2.1 Runtime metrics

When analysing runtime, or using it to inform a decision, it is typically compared against a second runtime after a change in execution environment. This could be a change in hardware such as a processor upgrade, or a change in the software such as a data layout optimization or different parallel programming abstraction. The most common metric here is runtime speedup, which for example is  $2\times$  if the runtime reduced by 50%:

$$speedup = \frac{runtime_{before}}{runtime_{after}}$$

(2.1)

This can also be applied to a change in parallel hardware resources assigned to execution of a parallel code. Specifically, the speedup provided by N parallel threads over one serial thread can be defined as:

$$S(N) = \frac{runtime_1}{runtime_N} \tag{2.2}$$

This can be generalised to measure the speedup of N parallel *resources* over one; this resource can be one thread as describe above, or it can be one entire compute node. A better metric for parallel performance incorporates the expectation (or hope) that speedup will equal N. If the achieved speedup is less than N, then the additional hardware resources are not being fully utilised. This metric is parallel efficiency, and is calculated by dividing the speedup by N, giving a value between 0 and 1 (full efficiency):

$$efficiency(N) = \frac{S(N)}{N}$$

(2.3)

There are two common reasons why parallel efficiency can be below 1.0, otherwise known as parallel efficiency loss – resource contention and imperfect workload decomposition. Most multicore systems have two shared hardware resources - main memory, and the network interface. The total electricity consumption and heat dissipation within a processor package can also be considered a shared resource. This manifests as a problem in multicore processors with dynamic clock frequency - as more cores are utilised then heat and power draw increases, and the clock frequency is reduced to manage these. This is also known as thermal throttling, and is particularly noticable with vectorised codes. For many HPC codes and systems, contention for these shared resources is a significant problem and constrains parallel performance.

The second reason for parallel efficiency loss relates to how a parallel workload is distributed and synchronised among threads or processes. The goal with parallelising a workload is that each parallel thread of execution receives an equal portion of work, such that they complete at the same time - a perfectly balanced load. Any inequality in the distribution results in some threads idling as they wait for other threads to finish - load imbalance. Minimising load imbalance is particularly difficult for some codes, and an important area of research. Most HPC codes that distribute work among processes (rather than purely threads) will require frequent inter-process communication to synchronise data. For example with iterative stencil loops where an array value update requires neighbouring values, some of those neighbours will reside on other processes requiring inter-process communication to transfer their values. This synchronisation introduces additional work that can become significant at high process counts.

#### 2.2.2 Performance counters

Within processors there are hundreds of specific and varied hardware events. Some common examples are a clock cycle, the retiring of an instruction, and a L1 cache miss. There are more specific events, such as a clock cycle on which no instructions were scheduled for execution, or a memory store instruction being retired. These allow for a uniquely deep insight into performance of a code. To count occurrences of these events a modern processor provides a much smaller number of specialised registers. These counters are directly integrated into the architecture, so they count events with zero overhead; only the configuration and later retrieval from user space has overhead, albiet low at approximately 10,000 cycles, which for a benchmark code like STREAM is 5% or less [50].

Configuring of and access to most counters is performed via model-specific registers (MSRs), which are only accessible from kernel space; the exception are uncore (off-core) events that are configured via the PCI address space, but in Linux this is also only accessible by the kernel. The **perf** interface in Linux provides user access to this functionality, as both a command-line utility and through an API of system calls. On top of this are built several libraries, the most popular being the performance application programming interface (PAPI) library [7]. It provides access to 'preset' events, which are a commonly-used subset of all available CPU core events with architecture-agnostic and vendor-agnostic aliases; this set includes the example hardware events listed earlier. It also provides access to all 'native' events, necessary when measuring uncore events such as those monitoring main memory traffic. Listing 2.1 shows the ease with which PAPI allows several performance counters to be monitored during execution of a code block, in this case cycle consumption and number of instructions of a computation loop.

```

Listing 2.1: PAPI code to record cycles and instructions of 'compute_loop()'

```

```

int event_set_id;

PAPI_create_eventset(&event_set_id);

PAPI_add_named_event(event_set_id, "PAPI_TOT_CYC");

PAPI_add_named_event(event_set_id, "PAPI_TOT_INS");

PAPI_start(event_set_id);

compute_loop();

long counts[2];

PAPI_stop(event_set_id, counts);

```

There are many events within a modern processor that can be monitored, many of which have configurable options. A summary of the most useful events are covered here, many of which relate to the cache hierarchy. The L1 cache typically has a small number of events, for when a cache line is replaced. A line replacement indicates that a load instruction requested data not in cache, or that the hardware prefetcher pre-emptively loaded a new cache line. The remaining levels of cache have more events, with fine granularity to provide a rich understanding of how the cache hierarchy is being utilised. They differentiate between requests for code or data, whether a request is to load data or read-for-ownership (RFO) (for writing), whether a load/store instruction or prefetcher created the request, and whether the requested data was present or missing. The core pipeline has various events being monitored, in particular: cycle consumption, stalled cycles, and instruction counts.

### 2.3 Mini applications

There are numerous benchmarks and mini-applications representing the performance of different classes of HPC applications, some of which have been released as component parts of projects such as the Mantevo Project [25], the ECP Proxy Apps Suite [1], and the UK Mini-App Consortium [14]. Mini-applications from these repositories have been used in a variety of contexts.

One such example is miniMD, which has been used to explore the performance of molecular dynamics codes on the Intel Xeon Phi Knights Corner architecture [47]. Using a combination of AVX intrinsics and algorithmic optimisations, e.g. overlapping PCIe transfers with computation, the authors demonstrate a  $5\times$  speed-up for the gather-scatter bottleneck typically present in MD codes.

Mallinson et al. compare the performance of two PGAS programming models (OpenSHMEM and Co-Array Fortran) against MPI using CloverLeaf, an Lagrangian-Eulerian hydrodynamics mini-application [36]. The authors demonstrate that Open-SHMEM is able to outperform an equivalent MPI implementation by 7.78 iterations/sec, at 4096 sockets, when using proprietary nonblocking operations from Cray and 4 MB memory pages.

LULESH, a hydrodynamics mini-application representative of ALE3D, is used to assess the suitability of emerging parallel programming models (e.g. Liszt and Loci) along with more established models such as OpenMP [31], in terms of programmer productivity, runtime performance and ease of optimisation. The reduced size of LULESH when compared with ALE3D allowed the authors to examine eight parallel programming models. Their conclusion highlights that while the emerging models such as Chapel and Loci enable a high level of productivity, they cannot match the performance of more established models such as MPI and OpenMP.

Similarly, Giles et al. examine the performance of OP2, a domain-specific abstraction library (DSL) for unstructured grid codes using the AIRFOIL CFD miniapplication [48]. The authors demonstrate that they are able to achieve performance within 6% of a hand-coded implementation.

The CFD code included in the Rodinia benchmark suite has been used to examine the performance of a Graphic processing unit (GPU) when running unstructured grid applications [15]. From the results, Corrigan et al. conclude that GPUs show promise for this class of code given an increase in double precision performance in the future.

#### 2.3.1 Characterising similarity

A typical mini-application is designed around one or several key loops extracted from a target application, i.e. it contains code from the application with minimal 'boilerplate' for execution (hence "mini"). Thus it can be assumed that the key performance characteristics are captured, with some simple performance comparison to verify this. But it is not always possible or desirable to share code with an application, for example if that application is subject to intellectual property (IP) restrictions that greatly limit portability – one important feature of a mini-application is portability. For these scenarios, the mini-application will have to differ in code, but still capture the key performance characteristics – this sub-class of mini-application is referred to as a proxy-application. Then verification of similarity becomes more important.

Research on verifying similarity is a relatively young field, with the earliest known work in 2014. Most of this research has a common theme – quantify the degree to which a proxy-application and its target application stress the same parts of hardware, and design a metric to embody the similarities. Barrett et al. proposed that if a proxy-application is similar to its target, then it should be predictive of performance [4]. A direct interpretation of predictive is used, meaning the performance metric (e.g. runtime) should simply match without transformation. Tramm et al. first proposed using correlations between hardware performance counters and parallel efficiency loss, where a strong correlation indicates a particular hardware event is harming performance [59]. Where strong correlations are exhibited (> 0.85), if both codes exhibit similar correlations for the same hardware events, then the proxy-application can be considered to be similar to the target. A limitation of this work is that the data processing is manual. Is 0.85 the right threshold for a

strong correlation? What size difference between the two correlations with an event is needed to mean dissimilarity?

Islam et al. improved upon this approach with machine learning techniques, automating feature selection and data analysis [29]. This enables two robust metrics: (i) the significance of a particular hardware resource (e.g. L2 cache) to the selected performance attribute (e.g. parallel efficiency loss); (ii) the similarity of this significance between proxy-application and target code. Aaziz et al. added MPI metrics to the analysis – times, message sizes and counts, grouped by MPI primitive type (send, recv, collective, wait) – and applied hierarchical clustering directly to the metrics rather than correlate with runtime or scaling [2]. A standard cluster similarity metric quantified similarity of a proxy-application, effectively for in-core metrics, but struggled on their MPI metrics where the proxy-application used different MPI primitives to its target. They later abstracted away from primitives with a metric based on pair-wise communication, assisted by CrayPat profiler [3].

### 2.4 Performance modelling

The previous section summarised research on verifying proxy-applications. These are important and useful contributions, adding robustness to the verification. But they do not directly address whether or how a proxy-application can predict performance of its target application. If a proxy-application is highly similar to its target application, then it should be possible to use it to generate accurate performance predictions of the target. Two relevant areas of research are reviewed here – performance projection, and mechanistic modelling of processors.

#### 2.4.1 Performance projection

Performance projection concerns the application of purely statistical or machine learning techniques, to predict performance of one code from a variety of others. Sharkawi et al. propose a technique of identifying surrogate codes that are quantifiably similar to the target code according to 25 performance metrics [53]. These surrogates are executed, and a genetic algorithm calculates a weighting based on how similarly performance is affected by the hardware resources. Their weighted average is used as a prediction of compute performance (excluding MPI), achieving a mean error of 7.2% on a IBM Power6 and 10.5% on a Intel Core. In follow-up work they add a performance model for MPI communications [54]. Hoste et al. apply a similar technique but to microarchitecture-independent metrics, predicting the ranking of machine performance with 0.89 mean rank correlation [27]. Shweta et al. seek to achieve both goals, predict performance (not just ranking) but without systemspecific hardware metrics [52]. Similarity is calculated as in prior work, as Pearson correlation of a performance metric across systems, but they use collaborative filtering from social networks to identify similar benchmarks. Rather than predict runtime, they predict instructions-per-second (IPS). They report RMSE values, calculated across predictions – mostly these fall between 1 to 3, but the IPS values range 0.05 to 22.99, so for those applications near the low end of range this RMSE is very high. No per-application errors are given. Wang et al. apply a deep neural network (DNN) model to hardware features readily provided by manufacturers (cores, cache size, etc), to predict performance on new Intel architectures and SKUs [64]. Evaluated with two benchmark suites, SPEC and Geekbench, model error is 5% and 11% respectively.

#### 2.4.2 Mechanistic modelling of superscalar processors

A mechanistic core model is an analytical performance model with structure derived from the processor core architecture. In the context of modern superscalar processors, this model typically focuses on throughput of instructions through, and bottlenecks of, the various pipeline stages. These are intended to execute several magnitudes faster than a cycle-accurate simulator.

Michaud et. al present the first mechanistic model relevant to a superscalar processor, constructing a simple model of the interaction between branch misprediction rate and instruction fetch rate, exploring how this affects the achievable ILP within the processor design space [38]. Despite its simplicity it provided useful insight into processor design, indicating that to double ILP it is necessary to both double the instruction fetch rate and reduce the branch misprediction rate by  $4\times$ . Taha et. al extend this much further to cover more stages of the superscalar pipeline [56]. They also introduce the concept of the *interval* model, although they term this *macroblocks*, where instructions are approximated as executing in blocks separated by misprediction-induced stalls. They implement three specific extensions to capture additional bottlenecks within a superscalar processor:

- limited throughput of functional units of each instruction class

- reorder buffer with limited size, which limits the scope for out-of-order execution

- limited instruction retirement bandwidth