# Identifying and Harnessing Concurrency for Parallel and Distributed Network Simulation

Philipp Josef Andelfinger

Identifying and Harnessing Concurrency for Parallel and Distributed Network Simulation

# Identifying and Harnessing Concurrency for Parallel and Distributed Network Simulation

by Philipp Josef Andelfinger

Dissertation, Karlsruher Institut für Technologie (KIT) Fakultät für Informatik, 2016

Tag der mündlichen Prüfung: 10. Februar 2016

Referenten: Prof. Dr. rer. nat. Hannes Hartenstein, Dr. Kalyan Perumalla

#### Impressum

Karlsruher Institut für Technologie (KIT) KIT Scientific Publishing Straße am Forum 2 D-76131 Karlsruhe

KIT Scientific Publishing is a registered trademark of Karlsruhe Institute of Technology. Reprint using the book cover is not allowed.

www.ksp.kit.edu

This document – excluding the cover, pictures and graphs – is licensed under the Creative Commons Attribution-Share Alike 3.0 DE License (CC BY-SA 3.0 DE): http://creativecommons.org/licenses/by-sa/3.0/de/

The cover page is licensed under the Creative Commons

Attribution-No Derivatives 3.0.55 \*\* Attribution-No Derivatives 3.0 DE License (CC BY-ND 3.0 DE): http://creativecommons.org/licenses/by-nd/3.0/de/

Print on Demand 2016

ISBN 978-3-7315-0511-2 DOI 10.5445/KSP/1000054019

## Zusammenfassung

Da Netzwerke von Computern inhärent parallele Systeme darstellen, können Simulationen von Computernetzen häufig durch parallele und verteilte Ausführung auf mehreren Prozessoren substantiell beschleunigt werden. Simulationsmodelle von Computernetzen können sich jedoch grundlegend in ihrer Eignung für eine Parallelisierung unterscheiden. Obwohl sich bereits eine Vielzahl von vorausgehenden Arbeiten mit der effizienten parallelen Ausführung von Netzwerkmodellen befasst hat, besteht ein Mangel an Verfahren, die Entscheidungen bezüglich der Parallelisierung von Netzwerkmodellen und die Wahl geeigneter Hardware-Plattformen, Simulatorarchitekturen und Synchronisationsansätze unterstützen. Zusätzlich hat die breite Verfügbarkeit kostengünstiger Manycore-Hardware das Spektrum möglicher Realisierungen von Simulatoren über die Möglichkeiten traditioneller CPU-basierter Ansätze hinaus erweitert.

Diese Dissertation betrachtet die effiziente Ausführung von Netzwerksimulationen aus zwei Perspektiven: zunächst werden Evaluationsmethoden vorgeschlagen, die eine Abschätzung des Parallelisierungspotentials von Netzwerkmodellen erlauben. Im Anschluss werden Ansätze vorgestellt, die das identifizierte Parallelisierungspotential mittels moderner Manycore-Hardware effizient ausnutzen.

Identifizierung von Nebenläufigkeit: wir stellen einen analytischen Ansatz vor, der die durchschnittliche Anzahl an Recheneinheiten abschätzt, die von einem idealisierten parallelen oder verteilten Simulationslauf eines gegebenen Netzwerkmodells ausgelastet werden können. Die Abschätzung erfolgt auf Basis von Modellwissen und einfachen Netzwerkstatistiken, die in sequentiellen Simulationsläufen gewonnen werden. Da das vorgestellte Verfahren nicht auf automatisierten Methoden wie der "Critical Path Analysis" beruht, erlauben die Schätzungen ein Verständnis von Zusammenhängen zwischen den Kommunikationsmustern im simulierten Netzwerk und der resultierenden Nebenläufigkeit des Netzwerkmodells. Ein Verständnis dieser Zusammenhänge kann Modelloptimierungen und die Auswahl geeigneter Simulatorarchitekturen unterstützen. Das Verfahren basiert auf einer näherungsweisen Bestimmung des Simulationsfortschritts unter dem Synchronisationsalgorithmus YAWNS. Wir legen den Zusammenhang zwischen Critical Path Analysis und YAWNS dar und beweisen die Gültigkeit unseres Ansatzes sowie existierender Arbeiten, die unsere Annahmen teilen. Eine Evaluation der Akkuratheit konkreter Schätzungen wird anhand einer Anwendung des Schätzverfahrens auf Implementierungen dreier Netzwerkmodelle in bekannten Netzwerksimulatoren durchgeführt.

Um zusätzlich zu den Eigenschaften des untersuchten Netzwerkmodells auch die zur Durchführung verwendete Hardware und den Synchronisationsansatz zu berücksichtigen, stellen wir ein Werkzeug vor, dass die Laufzeit paralleler und verteilter Simulationen auf Basis sequentieller Simulationen und Hardware-Messungen prädiziert. Das Werkzeug führt eine Simulation einer

geplanten parallelen oder verteilten Simulation durch ("Simulation zweiter Ordnung"). Wir zeigen, dass im Falle von Netzwerkmodellen mit nicht-trivialen Berechnungen pro simulierter Nachricht eine angemessen akkurate Prädiktion erreicht wird.

Nutzung von Nebenläufigkeit: traditionelle Ansätze der parallelen und verteilten Simulation greifen zur Ausführung des Netzwerkmodells auf einen Verbund von CPUs zurück. In einigen existierenden Arbeiten ergaben sich für Modelle von Peer-to-Peer-Netzwerken durch Parallelisierung der Simulation nur geringe Laufzeitverbesserungen. Wir analysieren und vergleichen zwei Partitionierungsstrategien für Modelle von Netzwerken, die auf dem Protokoll Kademlia basieren. Ein Beispiel für ein solches Netzwerk ist die BitTorrent DHT, eines der größten öffentlichen Peer-to-Peer-Netzwerke. Mittels einer Partitionierung der Simulation basierend auf der logischen Topologie des Netzwerkes erreichen wir eine Beschleunigung der Simulation um einen Faktor von 6,0 im Vergleich mit einer sequentiellen Ausführung sowie eine nahezu lineare Reduktion des Speicherbedarfs pro Rechenknoten.

Da die mittels einer CPU-basierten parallelen und verteilten Ausführung erreichte Beschleunigung einer Simulation die hierzu erforderlichen Hardware-Ressourcen nicht in jedem Falle rechtfertigen kann, untersuchen wir die Ausführung von Netzwerksimulationen auf Grafikprozessoren (Graphics Processing Units, GPUs). Heutige GPUs sind in der Lage, allgemeine Berechnungen auf hunderten oder tausenden paralleler Recheneinheiten durchzuführen. Eine im Arbeitsplatzrechner eines Forschers vorhandene kostengünstige GPU kann dazu dienen, die Wartezeit zwischen Änderungen an einem Netzwerkmodell und dem Erhalten von Simulationsergebnissen zu verringern.

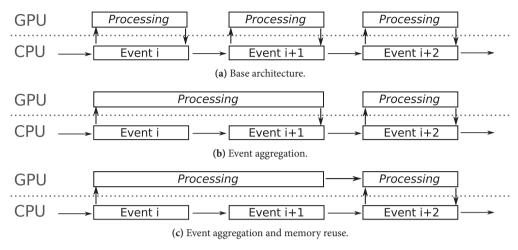

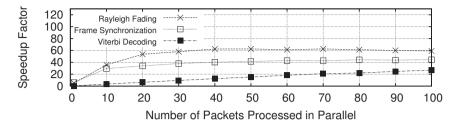

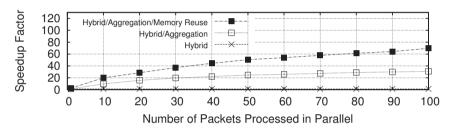

Zuächst vergleichen und evaluieren wir Architekturen zur GPU-Beschleunigung rechenaufwändiger Schritte einer CPU-basierten detaillierten Simulation drahtloser Netzwerke. Obwohl eine einzelne simulierte Nachrichtenübertragung bereits Möglichkeiten zur parallelen Verarbeitung bietet, zeigen unsere Messungen, dass eine signifikante Beschleunigung der Simulation es erforderlich macht, mehrere Nachrichtenübertragungen aggregiert zu betrachten. Um die Korrektheit der Simulation zu gewährleisten, muss hierbei die Möglichkeit von Interaktionen zwischen mehreren Sendevorgängen berücksichtigt werden. Unsere Ergebnisse demonstrieren daher, dass bereits im betrachteten Fall einer GPU-Beschleunigung einzelner Schritte einer durch eine CPU verwalteten Simulation Synchronisationsmechanismen aus dem Feld der parallelen und verteilten Simulationen erforderlich sind.

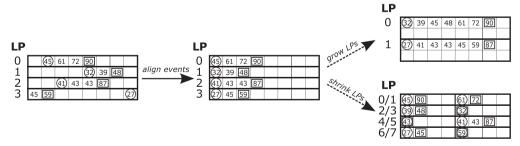

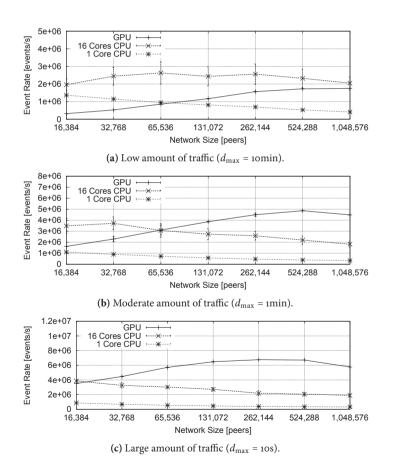

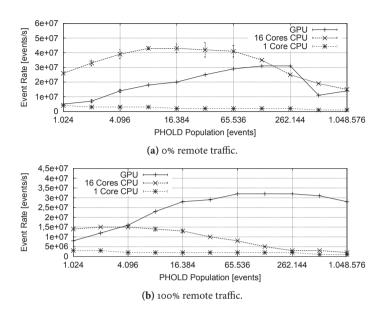

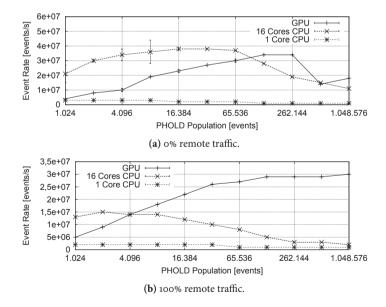

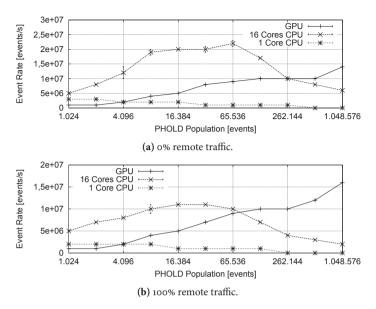

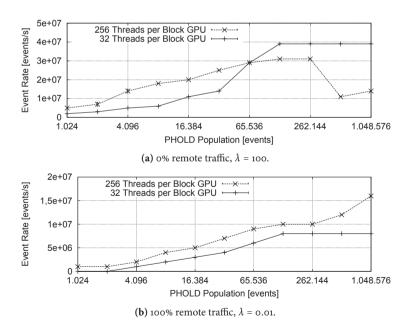

Schließlich stellen wir einen rein GPU-basierten Simulationsansatz vor, in welchem neben dem Netzwerkmodell auch die gesamte Simulationslogik auf einer GPU ausgeführt wird. Da auf eine Interaktion zwischen einer CPU des Host-Systems und der GPU weitestgehend verzichtet wird, eignet sich der rein GPU-basierte Ansatz auch im Falle von Netzwerkmodellen, deren Simulationsereignisse jeweils nur geringfügige Berechnungen erfordern. Im Gegensatz zu existierenden Arbeiten werden in unserem Ansatz die simulierten Knoten zu Gruppen zusammengefasst, welche jeweils gemeinsam betrachtet werden. Diese Aggregation erlaubt es, die Auslastung der Rechneneinheiten der GPU gegenüber dem Verwaltungsaufwand der Simulation abzuwägen, indem der Grad an Aggregation basierend auf Messungen der Simulationsleistung dynamisch zur Laufzeit angepasst wird. Eine Leistungsbewertung unserer Implementierung des Ansatzes anhand eines Modells Kademlia-basierter Netzwerke und des Benchmark-Modells PHOLD zeigt eine Beschleunigung der Simulationen um einen Faktor von bis zu 19,5 bzw. 27,5 im Vergleich mit einer sequentiellen CPU-basierten Ausführung, sowie eine Ereignisrate von bis zu 6,8\*106 bzw. 39,3\*106 Ereignissen pro Sekunde auf einer einzelnen GPU.

### **Abstract**

Since computer networks are inherently parallel systems, simulations of computer networks can in many cases be accelerated substantially through parallel and distributed execution on a set of interconnected processors. Still, simulation models of computer networks vary significantly in their parallelization potentials. Although an enormous number of works consider the efficient parallel execution of specific network models, there is still a lack of guidelines that help in decisions on parallelization and in the selection of hardware platforms, simulator architectures and synchronization approaches that enable an efficient execution. Further, the advent of commodity many-core devices has broadened the range of possible simulator realizations beyond the possibilities of traditional CPU-based approaches.

This dissertation addresses the efficient execution of simulation models of computer networks from two perspectives: we propose evaluation methods to determine a model's parallelization potential and provide simulator realizations that efficiently exploit the identified potentials using modern many-core hardware.

Identifying Concurrency: we propose an analytical approach to estimate the concurrency of network models, i.e., the number of processors that can be occupied in an idealized parallel and distributed simulation run based only on model knowledge and simple network statistics from sequential simulation runs. By not relying on an automated "black-box" method such as critical path analysis, our estimation approach exposes the relationships between the communication patterns in a simulated network and the resulting concurrency of the simulation. Insights into these relationships may guide model optimizations and the selection of suitable simulator architectures. Our estimations approximate the progress of simulations performed using the well-known synchronization algorithm YAWNS. After clarifying the relationship between critical path analysis and YAWNS, we provide a proof that shows the validity of the general approach and that substantiates the results of previous works that share our assumptions. Empirical results on the example of three network models implemented in popular simulators demonstrate that the estimations are sufficiently accurate to evaluate the models' parallelization potential, while avoiding an automated "black-box" analysis of sequential simulation runs.

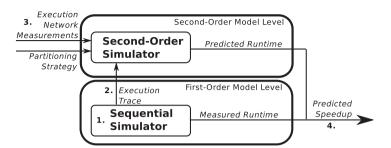

In order to take into account both the properties of the considered network model as well as the execution hardware and synchronization approach, we present a tool that predicts the runtime of parallel and distributed simulations on the basis of sequential simulation runs and hardware measurements. The tool performs a simulation of an envisioned parallel and distributed simulation ("second-order simulation"). We show that reasonably accurate runtime predictions are achieved for distributed simulation runs in the case of network models where simulated messages require non-trivial amounts of computation.

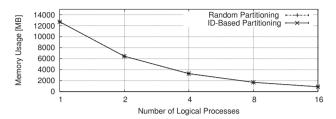

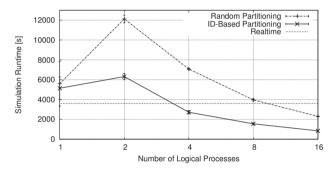

Harnessing Concurrency: traditionally, parallel and distributed simulations rely on interconnected CPUs for execution of the simulation model. In some previous works, models of peer-to-peer networks have been reported to benefit only to a small degree from parallelization in CPU-based execution environments. We analyze and compare two partitioning strategies for models of Kademlia-based networks such as the BitTorrent DHT, one of the largest public peer-to-peer networks. When applying a partitioning strategy based on the logical topology of the network, we achieve a simulation speedup of 6.0 compared to a sequential execution and a near-linear reduction of the memory requirements per execution node.

Since high-performance CPU-based parallel and distributed simulations can consume enormous amounts of hardware resources that may not be justified by the achieved runtime reductions, we consider the acceleration of network simulations using graphics processing units (GPUs). GPUs have evolved to support general-purpose computations on hundreds or thousands of parallel processing elements. An inexpensive GPU in a researcher's workstation can be used to shorten the feedback loop between changes to the network model and the retrieval of the corresponding simulation results.

We compare and evaluate architectures for a GPU-based coprocessing of detailed wireless network simulations. Although each simulated transmission already provides opportunities for parallel processing, we show that significant runtime reductions require an aggregated consideration of multiple transmissions in parallel. Since, in order to maintain correctness, the potential for interactions between multiple transmissions must be considered, the results show that even a simple GPU-based coprocessing requires synchronization mechanisms from the field of parallel and distributed simulation.

Subsequently, we propose a fully GPU-based simulation approach that executes all simulation logic as well as the network model on a GPU. Due to avoiding most interaction between a host CPU and the GPU, the fully GPU-based approach is applicable to network models where individual events require only small amounts of computation. Contrary to existing works, our approach aggregates sets of simulated nodes that are considered jointly. The aggregation enables the exploitation of a tradeoff between the utilization of the GPU's processing elements and simulation overheads by dynamically adapting the degree of aggregation according to performance measurements at simulation runtime. We conduct a performance evaluation of our implementation on the example of a model of Kademlia-based networks and the well-known PHOLD benchmark model. Using a single commodity GPU, we achieve a speedup of up to 19.5 and event rates up to  $6.8 \times 10^6$  for the model of Kademlia-based networks. A speedup of up to 27.5 and event rates of up to  $39.3 \times 10^6$  events per second of wall-clock time are achieved in the case of the PHOLD model.

# Contents

|   | Zusa | ammenfassung                             |            |

|---|------|------------------------------------------|------------|

|   | Abs  | tracti                                   | iii        |

|   | List | of Figures                               | ij         |

|   | List | of Tables                                | X          |

| 1 | 1.1  | Contributions                            | 2          |

|   | 1.2  | Thesis Outline                           | 5          |

| Ι | Fu   | ndamentals                               | 7          |

| 2 | Para | ıllel and Distributed Network Simulation | ç          |

|   | 2.1  | Synchronization of Simulated Time        | 1          |

|   |      | 2.1.1 Conservative Algorithms            | 1          |

|   |      |                                          | 12         |

|   | 2.2  | Performance Evaluation                   | 13         |

|   |      | 2.2.1 Taxonomy                           | 13         |

|   |      | 2.2.2 Strategies                         | 16         |

|   | 2.3  | Simulator Adaptation                     | 18         |

|   |      | 2.3.1 Lookahead                          | 18         |

|   |      | 2.3.2 Partitioning                       | 19         |

|   |      | 2.3.3 Synchronization                    | 20         |

| 3 | Con  |                                          | <b>2</b> 3 |

|   | 3.1  | •                                        | 2.4        |

|   | 3.2  | 1 67                                     | 26         |

|   | 3.3  |                                          | 26         |

|   | 3.4  |                                          | 28         |

|   | 3.5  | Comparison                               | 28         |

| II | Ide         | entifying Concurrency                                      | 31 |

|----|-------------|------------------------------------------------------------|----|

| 4  | Iden        | tifying Concurrency - Introduction                         | 33 |

| 5  | Ana         | lytical Concurrency Estimation Approach                    | 35 |

|    | 5.1         | Fundamental Algorithms                                     | 37 |

|    | 5.2         | Methodology                                                | 39 |

|    | J. <u>_</u> | 5.2.1 Consideration of Fixed Lookahead                     | 39 |

|    |             | 5.2.2 Relationship between Critical Path Analysis and      | 3) |

|    |             | Synchronization Algorithms                                 | 41 |

|    |             | 5.2.3 Analytical Concurrency Estimation Model              | 42 |

|    |             | 5.2.4 Limited Deviation between ACPA- and                  | •  |

|    |             | YAWNS-Based Concurrency                                    | 43 |

|    | 5.3         | Network Model Analysis                                     | 48 |

|    | , ,         | 5.3.1 Peer-to-Peer Overlay Network                         | 48 |

|    |             | 5.3.2 TCP/IP in a Fixed Topology                           | 50 |

|    |             | 5.3.3 Wireless Ad-Hoc Communication                        | 54 |

|    | 5.4         | Evaluation                                                 | 56 |

|    |             | 5.4.1 Sensitivity Analysis                                 | 56 |

|    |             | 5.4.2 Validation of Estimations                            | 58 |

|    | 5.5         | Towards a Consideration of Variable Event Processing Times | 62 |

|    |             | 5.5.1 Refined Concurrency Estimation Model                 | 62 |

|    |             | 5.5.2 Impact of Variable Event Processing Times            | 63 |

|    | 5.6         | Discussion                                                 | 64 |

|    | 5.7         | Conclusions                                                | 65 |

| 6  | Seco        | ond-Order Network Simulation                               | 67 |

|    | 6.1         | Methodology                                                | 68 |

|    |             | 6.1.1 Modeling Levels                                      | 68 |

|    |             | 6.1.2 Prediction Workflow                                  | 69 |

|    |             | 6.1.3 Model Components                                     | 69 |

|    |             | 6.1.4 Hardware Measurements                                | 70 |

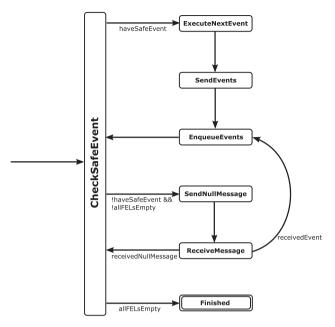

|    |             | 6.1.5 Second-Order Simulator Operation                     | 70 |

|    | 6.2         | Performance Predictions                                    | 72 |

|    |             | 6.2.1 Experiments                                          | 73 |

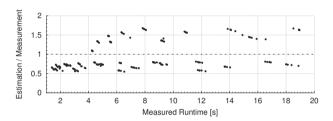

|    |             | 6.2.2 Evaluation                                           | 74 |

|    | 6.3         | Discussion                                                 | 76 |

| 7  | Iden        | tifying Concurrency – Conclusions                          | 77 |

| II | H     | arnessing Concurrency                                    | <b>79</b> |

|----|-------|----------------------------------------------------------|-----------|

| 8  | Harr  | nessing Concurrency – Introduction                       | 81        |

| 9  | CPU   | -Based Distributed Simulation of Kademlia-Based Networks | 83        |

|    | 9.1   | Related Work                                             | 84        |

|    | 9.2   | Partitioning Schemes                                     | 84        |

|    |       | 9.2.1 ID-Based Partitioning                              | 85        |

|    |       | 9.2.2 Location-Based Partitioning                        | 87        |

|    | 9.3   | Simulator Evaluation                                     | 88        |

|    |       | 9.3.1 Performance                                        | 89        |

|    |       | 9.3.2 Synchronization Efficiency                         | 91        |

|    | 9.4   | Conclusions                                              | 95        |

| 10 | GPU   | -Based Parallel Simulation                               | 97        |

|    | 10.1  | General-Purpose Computation on Graphics Processing Units | 98        |

|    |       | 10.1.1 The Graphics Pipeline                             | 99        |

|    |       | 10.1.2 NVIDIA CUDA                                       | 100       |

|    | 10.2  | Related Work                                             | 101       |

|    |       |                                                          | 101       |

|    |       | 10.2.2 Fully GPU-Based Simulation                        | 102       |

|    | 10.3  |                                                          | 106       |

|    |       |                                                          | 106       |

|    |       |                                                          | 107       |

|    |       | 3.9                                                      | 108       |

|    | 10.4  | ,                                                        | 109       |

|    |       | ' 1                                                      | 110       |

|    |       | •                                                        | 114       |

|    |       | 10.4.3 Discussion                                        | 125       |

|    | 10.5  | Conclusions                                              | 126       |

| 11 | Harr  | nessing Concurrency - Conclusions                        | 129       |

| 12 | Cone  | clusions and Outlook                                     | 131       |

|    | Bibli | ography                                                  | 137       |

# List of Figures

| 2.1        | A simulation round using TAW No                                                     | 12 |

|------------|-------------------------------------------------------------------------------------|----|

| 2.2        | Taxonomy of the main factors critical to PADS performance                           | 15 |

| 2.3        | Example of an event precedence graph                                                | 15 |

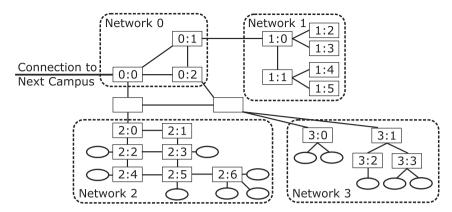

| 3.1        | A single campus network of the NMS topology                                         | 27 |

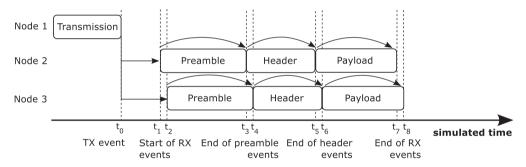

| 3.2        | Sequence of events during a transmission in the wireless network model              | 27 |

| 5.1        | Critical path analysis of a precedence graph with fixed event processing times      | 37 |

| 5.2        | Synchronization using YAWNS                                                         | 39 |

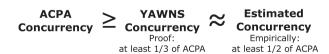

| 5.3        | Relationships between results of ACPA, YAWNS and our estimation approach            | 41 |

| 5.4        | Full precedence graph.                                                              | 41 |

|            | Reduced precedence graph.                                                           |    |

| 5.5<br>5.6 | Event visibility and node assignment using ACPA on a reduced precedence graph       | 45 |

| -          | , , , , , , , , , , , , , , , , , , , ,                                             | 47 |

| 5.7        | Processing of a reduced precedence graph using ACPA                                 | 47 |

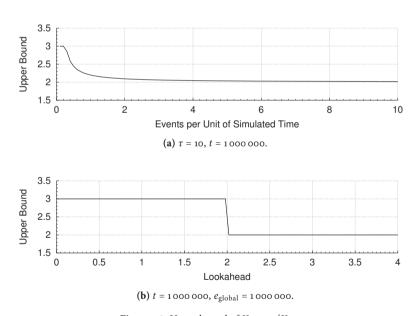

| 5.8        | Upper bound of $X_{\text{YAWNS}}/X_{\text{ACPA}}$                                   | 47 |

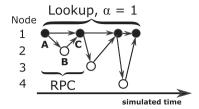

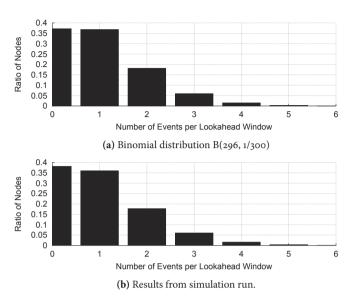

| 5.9        | Event patterns in Kademlia <sub>A</sub>                                             | 49 |

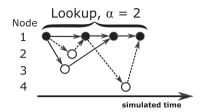

| 5.10       | A campus network in the NMS network model.                                          | 51 |

| 5.11       | Event patterns in the <b>NMS</b> model                                              | 52 |

| 5.12       | Concurrency of a single transmission in Wireless <sub>A</sub>                       | 55 |

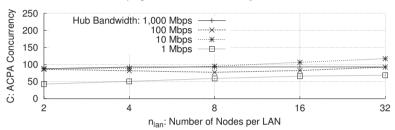

| 5.13       | Sensitivity analysis of Kademlia <sub>A</sub>                                       | 57 |

| 5.14       | Sensitivity analysis of the NMS model                                               | 58 |

| 5.15       | Sensitivity analysis of Wireless <sub>A</sub>                                       | 58 |

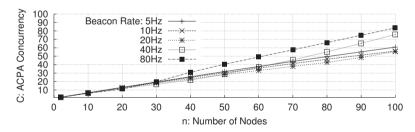

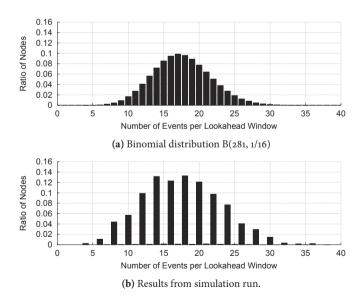

| 5.16       | Comparison of YAWNS (Y) with ACPA concurrency ( <i>C</i> )                          | 60 |

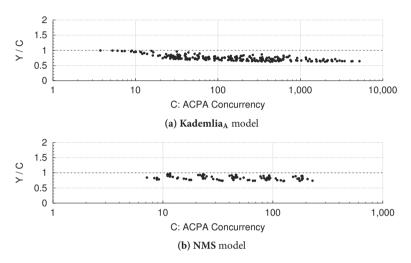

| 5.17       | Comparison of analytical estimate ( $C_{est}$ ) with ACPA concurrency ( $C$ )       | 60 |

| 5.18       | Expected and observed distribution of events per node in the <i>active</i> category | 61 |

| 5.19       | Expected and observed distribution of events per node of the <i>hub</i> category    | 61 |

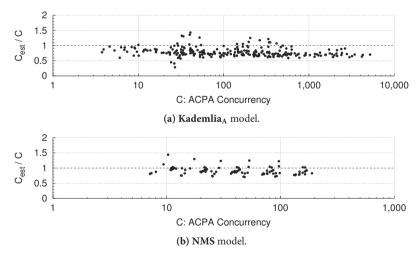

| 5.20       | Comparison of our analytical estimate ( $C_{est}$ ) with ACPA concurrency ( $C$ )   | 62 |

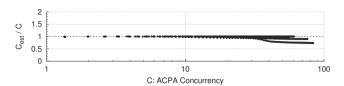

| 5.21       | Distribution of per-event processing time                                           | 65 |

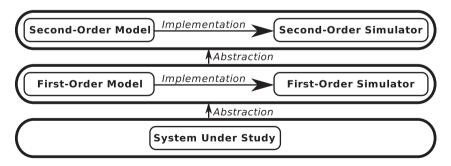

| 6.1        | Levels of abstraction in modeling of simulations                                    | 68 |

| 6.2        | Data flow during performance prediction                                             | 69 |

| 6.3        | Finite state machine description of the LP behavior in SONSim                       | 73 |

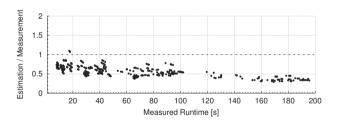

| 6.4        | Accuracy of runtime estimations of the <b>Kademlia</b> <sub>B</sub> model           | 75 |

| 6.5        | Accuracy of runtime estimations of the <b>PHOLD</b> model                           | 75 |

| 6.6        | Accuracy of <b>PHOLD</b> runtime estimations with artificial processing time        | 75 |

#### LIST OF FIGURES

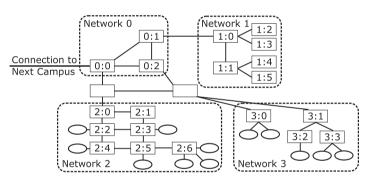

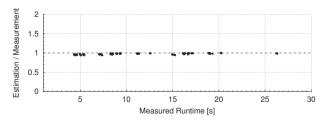

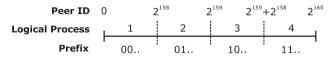

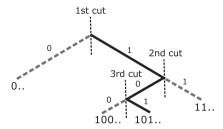

| 9.1   | Example of ID-based partitioning.                                                            | 86  |

|-------|----------------------------------------------------------------------------------------------|-----|

| 9.2   | Binary tree structure of a Kademlia routing table                                            | 86  |

| 9.3   | Location-based partitioning scheme                                                           | 87  |

| 9.4   | Memory usage per LP                                                                          | 89  |

| 9.5   | Simulation runtime                                                                           | 89  |

| 9.6   | EOT calculation                                                                              | 92  |

| 9.7   | Example of waiting times due to synchronization                                              | 93  |

| 10.1  | Hybrid CPU-GPU-based simulation architectures                                                | 107 |

| 10.2  | Speedup by GPU-based parallelization of signal processing algorithms                         | 109 |

| 10.3  | Speedup of hybrid CPU-GPU-based architectures                                                | 109 |

| 10.4  | Fully GPU-based simulation                                                                   | 110 |

| 10.5  | Event insertion                                                                              | 112 |

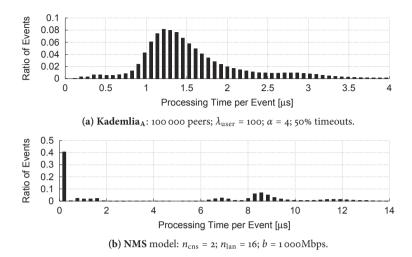

| 10.6  | Adaptation of LP size                                                                        | 113 |

| 10.7  | Event rate for <b>Kademlia</b> <sub>C</sub> varying the memory access synchronization method | 118 |

| 10.8  | Event rate for <b>Kademlia</b> <sub>C</sub> varying the simulator variant                    | 119 |

| 10.9  | Event rate of GPU-based simulation of the <b>PHOLD</b> model with $\lambda$ = 100            | 121 |

| 10.10 | Event rate of GPU-based simulation of the <b>PHOLD</b> model with $\lambda = 1$              | 121 |

|       | Event rate of GPU-based simulation of the <b>PHOLD</b> model with $\lambda$ = 0.01           | 122 |

| 10.12 | Varying the number of GPU threads per block                                                  | 123 |

# List of Tables

| 3.1               | Comparison of the considered network models                                                                          | 29             |

|-------------------|----------------------------------------------------------------------------------------------------------------------|----------------|

| 5.1<br>5.2<br>5.3 | Symbols used in algorithms                                                                                           | 40<br>65<br>65 |

| 9.1               | Average distance between remote peers using location-based partitioning                                              | 88             |

| 9.2               | Percentage of messages to local peers depending on the partitioning scheme                                           | 90             |

| 9.3               | Percentage of time spent in the different execution states                                                           | 90             |

| 9.4               | EOT and EIT quality when varying the number of LPs                                                                   | 94             |

| 10.1              | Time complexity of the GPU-based simulation tasks                                                                    | 117            |

| 10.2              | Symbols used in the time complexity analysis                                                                         | 117            |

| 10.3              | Percentage of runtime spent on simulation steps for <b>Kademlia</b> <sub>C</sub> with $d_{\text{max}} = 10\text{s.}$ | 124            |

| 10.4              | Event rates using fixed-sized and adaptive LPs to execute <b>Kademlia</b> <sub>C</sub>                               | 124            |

| 10.5              | Event rates and maximum speedup when varying the LP size for <b>PHOLD</b>                                            | 125            |

# 1 Introduction

The recent decades have seen a vast increase in the scale and complexity of networked systems. The emergence of smart grids, the expected advent of smart cities and the Internet of Things will further accelerate the deployment of networked systems spanning cities or entire regions. The design of these large-scale systems is not possible without relying on simulations to evaluate different approaches, topologies and protocols. Frequently, networked systems are evaluated using discreteevent simulations, where changes in system state are represented by events occurring at discrete points in simulated time. However, the runtimes of discrete-event simulations can be prohibitively large: accurate simulation of highly dynamic systems at realistic scale entails processing vast numbers of events representing the complex interactions between, e.g., vehicles, mobile devices or systems in a smart grid. Parallel and distributed simulation is an approach to reduce simulation runtime by distributing the computational workload of an individual simulation run to a number of processors communicating using shared memory or a network. While parallel and distributed simulation is commonly applied when investigating systems whose state is subject to continuous changes, efficient parallel and distributed simulation of systems that are adequately described by discreteevent models is still regarded as a challenging problem, even after multiple decades of research. The main challenge in parallel and distributed discrete-event simulation is the synchronization between processors: to gain meaningful results, a synchronization mechanism must enforce an ordering of the simulation events so that the results of the parallel or distributed simulation are identical to those of a corresponding sequential run. In addition, an efficient parallelization depends on a sufficient amount of independence in the behavior of the components of the modeled system, i.e., sufficient numbers of events that can be processed independently, and on methods for efficient parallel execution of events during simulation runtime. We refer to the largest possible number of events that can be executed in parallel according to a network model's properties, averaged over a simulation run, as the *concurrency* of the simulation.

Due to the diminishing performance improvements of individual processor cores and the increasing prevalence of many-core devices with hundreds of cores, parallel and distributed simulation is becoming a key method to enable the evaluation of large-scale networked systems. However, since the runtime interactions between a network model and a simulator realization are difficult to predict, there is still a lack of guidance for decisions on whether a given model will benefit sufficiently from parallelization to justify the required development effort. The research question motivating this dissertation can therefore be stated as follows:

How can the parallelization potential of discrete-event models of computer networks be estimated and explained?

Since most existing approaches evaluate the parallelization potential of network models without a consideration of the causes for the respective results, novel evaluation approaches are needed to gain insights into the factors influencing a model's parallelization potential. Such insights may form guidelines for researchers to decide whether the parallelization of a model is worthwhile, and what simulator realization should be chosen.

While some network models exhibit enormous degrees of concurrency, achieving large performance gains through traditional parallel and distributed approaches can require significant hardware resources. Even if high simulation performance is achieved, the fine-grained computational tasks and the frequent need for communication between processors associated with the execution of many network models can render parallel and distributed simulations a comparatively inefficient use of large-scale computing resources.

In the past years, the massively parallel computing resources of graphics cards are increasingly applied to general computations in various scientific domains, enabling the high-performance execution of fine-grained parallel tasks. Since today, such many-core devices are readily available in commodity workstations, graphics cards can be utilized to accelerate network simulations without the need to allocate traditional high-performance computing resources. However, the heritage of graphics card architecture in computing three-dimensional graphics requires a reconsideration of simulator architecture in order to efficiently map the highly irregular tasks of discrete-event simulations to a graphics card's computing resources. Hence, our second research question can be stated as follows:

How can computationally intensive network simulations be executed efficiently on commodity graphics cards?

Whereas large-scale cluster resources in shared use can substantially reduce the overall time required for large parameter studies, an acceleration using commodity graphics cards is particularly applicable in exploratory phases of simulation studies, where a short feedback loop is the prime concern.

### 1.1 Contributions

The dissertation addresses the challenges of achieving high performance in parallel and distributed network simulation from two perspectives: we first consider the *identification of concurrency* in network simulation models by analytical and simulation-based methods. Subsequently, we focus on *harnessing concurrency* in network models by proposing high-performance simulator architectures and implementations running on CPU-based distributed systems as well as on GPU-based many-core devices.

#### Identifying Concurrency

After clarifying the key factors determining parallel simulation performance and the scope of existing evaluation approaches based on a categorization of the performance-critical factors such as synchronization costs and partitioning strategies, we expand the set of available performance evaluation approaches.

Analytical concurrency estimation approach: The most fundamental requirement for an efficient parallel execution of a network model is a sufficient degree of concurrency in the interactions between simulated nodes. However, the relationships between a simulated network's topology and communication patterns, and the resulting concurrency, are still not well understood. We present an analytical model to estimate the concurrency of network models that enables insights into the sources of concurrency based on an analysis of the communication patterns in the considered network model. Such insights are not easily obtained through an automated analysis of simulation traces in a "black-box" fashion, e.g., using critical path analysis. Our analytical estimations approximate the concurrency results obtainable using the well-known YAWNS synchronization algorithm that has been used for concurrency estimation of simulations in existing works. We provide a proof of the fundamental result that under common assumptions, the results of a concurrency analysis using the YAWNS algorithm shows only limited deviation from critical path analysis. Although a broader range of network models should still be considered in future work, we consider our results to be strong evidence towards the following statement:

The concurrency of network simulations can be estimated at reasonable accuracy without relying on an automated analysis of event traces.

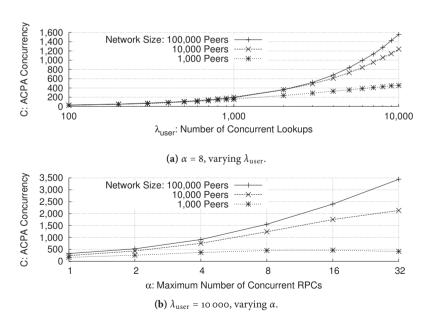

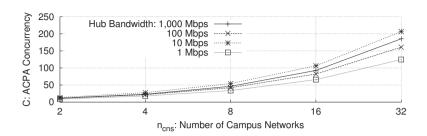

We study models of three fundamentally different classes of networks: a peer-to-peer network, IP-based routing in a fixed topology, and a wireless network. The analysis exposes the relationships between the communication patterns among the simulated nodes of the considered network models, and the resulting concurrency.

**Simulation-based performance estimation tool**: To take into account both the properties of the network model as well as the simulator realization and execution environment, we present a tool that predicts the runtime of simulation runs. The prediction is performed by a simulation of the execution of an envisioned distributed network simulator ("second-order simulation") based on measurements of the costs of individual simulation events and of the communication between processors. The tool allows researchers to vary the configuration of the envisioned simulation system, e.g., the properties of the network model or the simulation scale, to evaluate performance potentials and limitations prior to parallelization.

### Harnessing Concurrency

Subsequently, we propose and evaluate architectures and mechanisms for parallel and distributed network simulations for execution on different classes of network simulation studies and hardware environments.

Analysis of partitioning strategies for distributed simulations of Kademlia-based peer-topeer networks: We consider the performance gains by distributed simulation of a model of the BitTorrent DHT, a widely deployed public peer-to-peer network based on the Kademlia protocol currently comprised of about 10 million nodes. Some previous works have reported models of peer-to-peer networks to benefit little from parallel and distributed simulation due to fine computational granularity and a need for frequent communication between processors. However, we show that for the considered network model, overheads can be reduced substantially using a partitioning approach that follows the logical topology of the network, whereas a spatial partitioning can moderately decrease the overheads required for inter-processor synchronization. Performance measurements in a high-performance cluster environment show a simulation speedup factor of up to 6.0 compared to a sequential run.

**Evaluation of hybrid CPU-GPU-based simulator architectures**: We evaluate the performance of different GPU-accelerated simulator architectures for acceleration of wireless network simulation. We show that GPUs can be applied to exploit the data parallelism in models where the low-level details of wireless transmissions are reflected by computationally expensive signal processing tasks. Since only the signal processing steps are executed on the GPU, whereas the remaining simulation tasks are handled by the CPU, substantial performance gains require a aggregated consideration of multiple packet receptions. Since the aggregation approach must maintain the correctness of the simulation, even a simple GPU-based coprocessing requires mechanisms from parallel and distributed simulation.

Adaptive fully GPU-based simulation: We propose a GPU-based simulation approach that performs all steps of discrete-event network simulations on a GPU and efficiently executes models that lack explicit data parallelism. Fully GPU-based network simulation entails a tradeoff between the utilization of the GPU's cores and the incurred simulation overheads. Contrary to previous works, we take this tradeoff into account by proposing an aggregated consideration of multiple simulated nodes. The proposed mechanism enables a runtime adaptation of the degree of aggregation to balance GPU utilization and simulation overhead according to the parametrization of the network model and the activity in the simulated network. Our results support the following statement:

A dynamically adaptable aggregation of simulated nodes substantially reduces the runtime of fully GPU-based network simulations.

In simulations of Kademlia-based peer-to-peer networks, a speedup factor of up to 19.5 in comparison with a sequential execution is achieved on a commodity graphics card. In simulations of the PHOLD benchmark model, we observed a speedup factor of up to 27.5. The simulator achieves event rates of up to 39.3  $\times$  10 $^6$  events per second of wall-clock time. In contrast to traditional distributed simulations in CPU-based supercomputing environments in shared use, the proposed simulation approach can be deployed on consumer GPUs in researchers' workstations and hence enables low turnaround times with respect to simulation results.

Parts of the contributions presented in this dissertation have been published in the following previous works:

- Philipp Andelfinger and Hannes Hartenstein. Model-Based Concurrency Analysis of Network Simulations. In Proceedings of the ACM SIGSIM Conference on Principles of Advanced Discrete Simulation, pages 223–234. ACM, 2015.

- Philipp Andelfinger and Hannes Hartenstein. Exploiting the Parallelism of Large-Scale Application-Layer Networks by Adaptive GPU-based Simulation. In *Proceedings of the Winter Simulation Conference*, pages 3471–3482. IEEE, 2014.

- Philipp Andelfinger, Konrad Jünemann, and Hannes Hartenstein. Parallelism Potentials in Distributed Simulations of Kademlia-based Peer-to-Peer Networks. In *Proceedings of the* Conference on Simulation Tools and Techniques, pages 41–50. ICST, 2014.

- Philipp Andelfinger and Hannes Hartenstein. Towards Performance Evaluation of Conservative Distributed Discrete-Event Network Simulations Using Second-Order Simulation. In Proceedings of the ACM SIGSIM Conference on Principles of Advanced Discrete Simulation, pages 221–230. ACM, 2013.

- Philipp Andelfinger, Jens Mittag, and Hannes Hartenstein. GPU-Based Architectures and Their Benefit for Accurate and Efficient Wireless Network Simulations. In Proceedings of the International Symposium on Modeling, Analysis and Simulation of Computer and Telecommunication Systems, pages 421–424. IEEE, 2011.

### 1.2 Thesis Outline

The dissertation is structured as follows: in Part I, we first give a brief overview of parallel and distributed discrete-event simulation. We propose a simple taxonomy for performance evaluation approaches in the context of parallel and distributed simulation and discuss related work. Since high simulation performance can require an adaptation of properties of the simulator to the considered network model, we discuss existing work on simulator adaptation. Part I concludes with a characterization and comparison of the specific network models that will serve as examples in the remainder of the dissertation.

In Part II, we propose methods to evaluate the parallelization potential of network models. We present an estimation approach that determines the number of processors that can be occupied by a parallel or distributed simulation of a given network model based only on model knowledge and basic network statistics obtained from sequential simulation runs. We provide a proof that shows the validity of the estimation approach. The estimation accuracy is evaluated empirically on the example of three network models. We detail the steps towards a refinement of the estimation approach and discuss the effects on the estimation results. Subsequently, we present a simulation-based tool that predicts the runtime of parallel or distributed simulations based on a simulation trace generated in a sequential simulation run and on measurements of the execution environment. The prediction accuracy is evaluated by a comparison with measurement results of simulations on physical hardware.

In Part III, we propose methods for efficient parallel and distributed execution of network simulations. First, we analyze and evaluate two partitioning strategies for distributed simulation of one of the largest existing peer-to-peer networks and show that the simulation runtime can be reduced substantially using a partitioning strategy that follows the logical topology of the peer-to-peer network. Subsequently, we study two approaches to accelerate network simulations using modern graphics processing units (GPUs): first, we propose architectures for accelerating a traditional sequential simulator using GPU-based execution of computationally expensive simulation tasks. Finally, we propose an approach for fully GPU-based execution of network simulations without the need for a CPU-based management of simulation tasks. The approach is evaluated using a comparison of its time complexity with existing works and measurements of simulation performance.

Chapter 12 provides conclusions from our results and sketches directions for future work.

# Part I Fundamentals

2

## Parallel and Distributed Network Simulation

A frequent goal of researchers and engineers is to gain an understanding of properties of a real-world or envisioned system. If the system in question is a computer network, the relevant properties may for instance be the maximum throughput in a given network topology, the time required to route a packet between two nodes, or the scalability of a novel network protocol. To determine the desired properties, a number of evaluation methods present themselves [Law14]: if the network under study already exists or can be constructed with tolerable effort, it is possible to perform experiments on it directly by triggering the relevant behavior and conducting measurements of the desired properties. If the topology of the network under study and the behavior leading to the desired property are sufficiently simple, it can be possible to construct an analytical model that enables a mathematical derivation of the desired properties. In many cases, however, the network under study does not yet exist, is expensive to construct and, due to its complexity, defies analytical modeling. Such networks under study are typically evaluated using simulation. Averill Law defines the term simulation as follows: "In a simulation we use a computer to evaluate a model numerically, and data are gathered in order to estimate the desired true characteristic of the model." [Law14] The behavior of computer networks is usually described adequately by simulation models that involve a notion of time, that contain probabilistic components, and that change their state at discrete points in simulated time. These properties characterize the class of discrete-event models. An event is an "instantaneous occurrence that may change the state of the system" [Law14].

An event is represented by two elements: a timestamp specifying the event's point of occurrence in simulated time, and a code segment referred to as an *event handler* that performs the required changes in system state. For instance, an event may increment a counter representing the number of messages received by a node in a simulated network. In addition, an event may schedule new events to be executed at a later point in simulated time.

A discrete-event *simulator* performs the task of executing the events in a simulation in chronological order of their occurrence. In the simulator, the events to be executed are held in a data structure called the *future event list* (FEL). The task of executing events in timestamp order is performed by iteratively removing the earliest event from the FEL and executing the event by calling its event handler.

A discrete-event simulation model of a computer network (*network model*) typically includes the following elements:

- A description of a static or dynamic **network topology**, i.e., of the links between the nodes in the network. Depending on the modeling detail, the maximum throughput of each link is specified, while the latency of each link or each message passing over a link is given as a constant value or drawn from a probability distribution.

- An implementation of one or more **network protocols** that govern the behavior of the nodes.

The protocols are implemented in the form of event handlers that are scheduled to be called on the arrival of a message at a node or after a certain period of simulated time has passed.

For reasons of development cost or simulation performance, the protocol implementations may abstract from details of the protocol specification or of a reference implementation.

- An implementation of the behavior of one or more **applications**. The applications rely on the functionality specified in the implemented protocols.

An initial set of events is inserted into the FEL during initialization of the simulation. All further behavior of the network model is induced by the initial events and new events scheduled during simulation.

The complexity and scale of a realistic network model translates to immense computational demands and huge memory requirements to execute the simulation, rendering some simulation studies prohibitively expensive due to the large simulation runtimes, and others infeasible due to memory constraints.

Frequently, to study the sensitivity of a network model's behavior to a range of parameters, simulation studies involve multiple executions of the simulation model under various parameter combinations. Since most simulations include probabilistic components, additional repetitions are required to achieve an acceptable degree of confidence in the results. Hence, a simple way to reduce the overall time required for a simulation study is to distribute the required executions of the model to a number of processors ("Multiple Replications in Parallel", MRIP [EMP97]). Since the separate executions can be processed independently, an interaction between processors is required solely to aggregate the results of all executions. However, MRIP does not reduce the runtime and memory requirements of individual model executions.

*Individual* discrete-event model executions can offer substantial potential for parallelization as well. In fact, Le Boudec considers concurrency to be an inherent property of simulations: "A first task of a simulation program is to simulate parallelism: several parallel actions can take place in the real system, and in the program, they are serialized." [LB10].

Parallel and distributed simulation (PADS) describes mechanisms to distribute the computational workload of individual model executions to a set of processors interconnected using shared memory or a network [Fujo1]. Hence, PADS can be seen to reverse the serialization of the parallel actions of the modeled system. PADS can reduce both the runtime and memory consumption of individual

model executions. Similarly to parallel and distributed computing in other domains, one of the challenges of PADS is to maximize the computational throughput by finding a partitioning of the network model that balances the computational workload evenly between the available processors. Contrary to the use of the term in mathematics, in the PADS literature, the term *partition* refers to only one individual segment of a partitioned network model. We additionally use the term *logical process* (LP) to refer to a partition of a network model together with the simulator instance managing its execution. The interactions between nodes simulated in separate LPs are reflected by the exchange of events in the form of messages between LPs transferred via shared memory or a network. We subsume these two communication mechanisms under the term *interconnect*.

In PADS, determining a suitable partitioning can be particularly difficult due to the potentially highly dynamic behavior of the simulated entities, which may require dynamic adaptations of the partitioning strategy. An additional challenge is given by the requirement for maintaining a consistent behavior of the simulated entities with respect to simulated time. In other words, it must be ensured that the results of a parallel or distributed simulation correspond to those of a sequential execution on a single processor. For instance, the observed behavior of a simulated node may differ substantially depending on the ordering of incoming messages. The need for a correspondence between the results of a sequential simulation run and a parallel or distributed run is equivalent with the requirement for an execution of all events pertaining to an individual simulated node *in non-decreasing timestamp order*. In the literature, this requirement is referred to as the *local causality constraint* [Fujo1].

### 2.1 Synchronization of Simulated Time

There are two fundamental classes of synchronization algorithms that ensure the correctness of PADS results. *Conservative* algorithms guarantee a non-decreasing timestamp order previous to each event execution, whereas *optimistic* algorithms detect violations of timestamp order and subsequently perform rollbacks to a previous correct simulation state.

A survey of the literature on synchronization algorithms, on which the following overview is based, is given by Fujimoto [Fujo1].

### 2.1.1 Conservative Algorithms

Conservative synchronization algorithms adhere to the local causality constraint by ensuring *a priori*, i.e., prior to the execution of each event, that the execution of the event does not create the possibility of a violation of timestamp order. Events for which violations can be ruled out are called *safe* events. Identifying safe events efficiently is the main challenge in the design of conservative synchronization algorithms.

The earliest well-known first synchronization algorithm was described in publications by Bryant [Bry77], and Chandy and Misra [CM79] and is commonly referred to as the *Chandy-Misra-Bryant* (CMB) algorithm. In CMB, each LP owns queues that each hold the events that arrive from one of the remote LPs in "first-in first-out" (FIFO) order. Events both created locally and to be executed locally are also inserted into a FIFO queue. Since events are assumed to be sent in timestamp order and since this order is assumed to be maintained by the interconnect, the

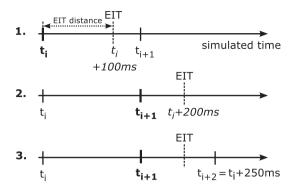

events in all FIFO queues are in non-decreasing timestamp order. Hence, the timestamp of the last received event in each FIFO queue serves as a lower bound for the timestamps of any event received from the LP associated with the queue. Now, each LP can calculate the minimum of the last received timestamps in all of its FIFO queues to determine a lower bound on the timestamp of any further event received by another LP (earliest input time, EIT [BToo]). All events in the local queues with timestamps lower than the EIT are safe and can therefore be processed in timestamp order without the risk of a violation of the local causality constraint. If the EIT does not render any events safe, the LP blocks until more events are received. Without further mechanisms, CMB will frequently create deadlocks: if there is a cycle of empty FIFOs and the timestamps of the last received events in the FIFOs are too small to allow any LP to execute further events, the simulation cannot proceed. Deadlocks can be avoided by exchanging *null messages* containing the earliest possible timestamp of an event created by one LP to be executed in another LP. The timestamp in a null message is the sum of the earliest possible timestamp of an event received by an LP and the minimum timestamp delta between an event and its creation. This minimum timestamp delta is called the *lookahead*  $\tau$  and must be determined based on knowledge of the network model. CMB with the addition of null messages is frequently called the Null Message Algorithm (NMA). Both CMB and NMA are asynchronous algorithms in the sense that the LPs independently alternate between waiting for events to become safe and the processing of events.

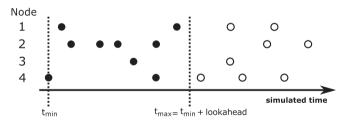

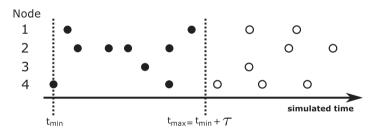

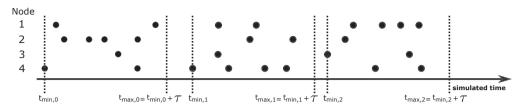

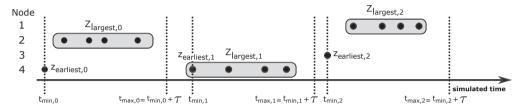

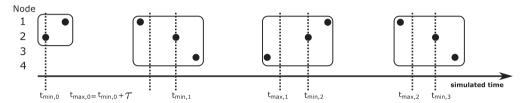

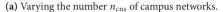

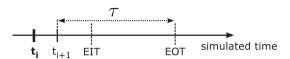

Under *synchronous* algorithms, the LPs alternate in lockstep between EIT calculation and the processing of events. A well-known synchronous algorithm is YAWNS [NMI89, Nic93] (cf. Figure 2.1): before events are processed, the global minimum timestamp  $t_{\min}$  of all events in the simulation is determined. The sum  $t_{\max} = t_{\min} + \tau$  of the global minimum and the lookahead is the earliest possible timestamp of a new event created by any event in the simulation. Hence, all events in the *lookahead window*  $\{t_{\min}, t_{\min} + 1, \dots, t_{\max}\}$  are safe to be processed. Now, each LP executes all events in the lookahead window in timestamp order before the next lookahead window is calculated.

**Figure 2.1:** A simulation round using YAWNS: events in  $\{t_{\min}, t_{\min} + 1, \dots, t_{\max}\}$  create no events with timestamps below  $t_{\max}$  and are thus safe to be executed in parallel.

### 2.1.2 Optimistic Algorithms

Since the remainder of the thesis focuses on conservative synchronization, we give only a brief sketch of optimistic synchronization algorithms. The main idea of optimistic synchronization is to allow for violations of the local causality constraint, but to perform rollbacks of the simulation to restore correctness after a violation. A well-known optimistic algorithm is Time Warp [Jef85]:

each LP creates periodic checkpoints of the simulation state. If an LP receives an event with a lower timestamp than a non-empty set of previously executed events, the LP restores its state to a point before the execution of the set of erroneously executed events. Since the erroneously executed events may have created new events for remove LPs, so-called anti-messages are sent to these LPs to delete the erroneously created events. To limit the amount of memory required for checkpoints, the lower bound of the timestamp of a rollback is calculated periodically. All checkpoints created earlier than this lower bound can be discarded.

Optimistic synchronization can perform better than conservative synchronization in cases where violations of the causality constraint can be ruled out for only small ranges in simulated time, but where actual violations occur only infrequently. In these cases, small lookahead values lead to slow progress using conservative synchronization. On the other hand, optimistic synchronization requires the simulator engine to store sufficient data so that a previous model state can be recovered. Hence, optimistic synchronization can incur substantial memory requirements. Substantial reductions in the memory requirements of optimistic synchronization and further performance increases are possible using reversible computing [CPF99, Per13].

### 2.2 Performance Evaluation

The benefits of PADS vary immensely depending on the network model and the simulator realization. Due to the complex interactions between the behavior of the network model during simulation runtime and the mechanisms used for communication and synchronization between the processors executing the simulation, estimating the performance of parallel and distributed simulations is a difficult task that has been the focus of a substantial body of research.

A particular challenge is given by the fact that simulation is typically applied in cases where the behavior of a system cannot be easily predicted analytically. Hence, since the runtime behavior of the model can strongly affect the simulation performance, predicting the simulation performance becomes difficult as well.

### 2.2.1 Taxonomy

A multitude of performance estimation and evaluation approaches have been proposed, each focusing on a subset of the factors determining the observed performance of a real-world execution of a simulation model. In the following, we will give an introduction to the key performance-critical factors, categorizing previous works in the field of performance evaluation according to the considered subset of factors.

We motivate our focus on sets of performance-critical factors with the observation that real-world networked systems are highly parallel and work in real-time. Hence, in theory it should be possible to simulate these systems in real-time by imitating the parallelism that is inherent in the real-world systems. However, the reported benefits of PADS vary immensely. In some cases, a large speedup compared to a sequential execution was achieved [PFP04], while in other cases there were only modest performance gains or runtime even increased after parallelization [QRT12]. These results raise the question: *if the modeled system itself contains high amounts of parallelism, why is the parallelism not exploited by PADS?*

To approach this question, we first distinguish between three key metrics that describe different aspects of PADS performance and which we will return to repeatedly throughout the remainder of the thesis:

- Speedup is the ratio between the execution time of a sequential simulation run and a parallel

or distributed simulation run. It is influenced by the network model, the synchronization

algorithm, the simulator implementation, and the execution hardware.

- Parallelism is the measured average number of events executed in parallel in a parallel or distributed simulation run.

- Concurrency is the average number of events in a simulation run that can be executed in

parallel, assuming an unlimited number of processors and no costs for synchronization

and communication between logical processes. The concurrency is a property of the network model and scenario configuration and forms an upper bound for the parallelism in a

simulation run.

The distinction between parallelism and concurrency is made in analogy to the use of the terms in the literature on software engineering. For instance, Briot et al. describe concurrency as "referring to the non-sequential semantics of a program", and parallelism as "referring to the actual implementation of a concurrent system" [BGL98]. Note that in contrast to the software engineering domain, where the terms are used in a more qualitative sense to refer to aspects of software systems and their execution, we define both concurrency and parallelism as specific measurable quantities.

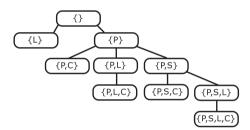

To enable a more fine-grained categorization of performance evaluation approaches, we propose a taxonomy of the main factors that determine PADS performance (cf. Figure 2.2), tracing the properties of the network model itself (the root node of the tree) to the measured or estimated performance of a full simulation run (the leaf node on the deepest level of the tree).

The literature has focused on the performance-critical factors depicted in Figure 2.2:

- 1. Lookahead: Under a conservative synchronization algorithm, in order to adhere to the local causality constraint, only safe events are executed. Depending on properties of the network model, it may be sufficient to determine a global and constant minimum timestamp delta between an event and its creation and choose this value as a fixed lookahead. In other cases, the lookahead must be determined dynamically for efficient simulation. Limited lookahead can restrict the portion of the concurrency of a network model that can be exploited in a simulation run.

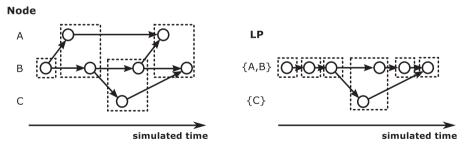

- 2. Partitioning: Given a limited number of processors to perform the simulation on, sets of nodes in the network must be assigned to logical processes (LPs), each handling a segment of the simulated network. Partitioning the network to n LPs introduces two limitations with respect to the network model's concurrency. First, since only a maximum of n LPs can execute events in parallel, the maximum number of parallel events is n. Second, as events in each LP are executed in timestamp-order, previously independent events are given a sequential order to be followed in the simulation. We can model the changes in the number of parallel events by additional edges in an event precedence graph (cf. Figure 2.3) that describes the order between events that must be maintained during execution to guarantee the correctness of the simulation. The impact of the partitioning on the precedence graph and the resulting

number of parallel events can be influenced by the number of LPs chosen and the strategy by which nodes are assigned to LPs. Event precedence graphs are considered in more detail in Chapter 5.

- 3. **Communication:** Simulated messages crossing LP boundaries require physical communication between LPs. In parallel simulations using shared memory, physical communication takes the form of synchronized accesses to memory. The amount of inter-LP communication is dependent on the chosen partitioning strategy. Hence, all vertices containing the factor C in Figure 2.2 also contain the factor P.

- 4. **Synchronization:** Synchronization is required to maintain the causal relationships between nodes simulated in different LPs. There is a dependence of the costs of the synchronization algorithm on the partitioning strategy and on the number of LPs.

The remainder of this section provides an overview of existing work on performance evaluation of PADS, categorizing the approaches by the considered performance-critical factors.

Figure 2.2: Taxonomy of the main factors critical to PADS performance (L: Lookahead, P: Partitioning, C: Communication, S: Synchronization).

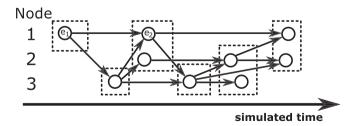

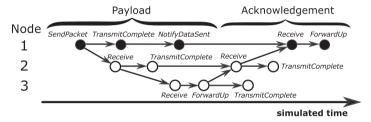

**Figure 2.3:** Example of an event precedence graph for a simulation of a network of three nodes. An edge  $e_1 \rightarrow e_2$  signifies the precedence relation "event  $e_1$  must be executed before event  $e_2$ ". Dashed rectangles signify groups of events that can be executed in parallel. The left-hand graph shows the precedence structure on the node level, corresponding to the full concurrency in the network simulation itself. In the right-hand graph, nodes A and B are assigned to the same logical process, which is reflected by a reduction in the number of events that can be executed in parallel.

### 2.2.2 Strategies

#### Measurements

A wide variety of works study the performance of PADS by benchmarking simulation runs on physical hardware. Measuring the runtime of a simulation run considers the effects of the model partitioning, the costs of communication and synchronization, as well as the available lookahead ( $\{P, L, C, S\}$ ). Many works in this category focus on the impact of the choice of synchronization algorithm (e.g., [RJD89, KY91, BRA95]). While benchmarking results can accurately represent the simulation performance on a given hardware platform, the measured runtime is affected by all of the performance-critical factors. Hence, it can be difficult to generalize measurement results.

To isolate the impacts of the costs for synchronization, the Ideal Simulation Protocol (ISP) [JB96, BToo enables performance measurements while excluding synchronization costs. ISP requires two simulation runs: in the first run, a trace is generated that contains the timestamp ordering of all events. In the second run, the information of the trace can be used to execute all events in non-decreasing timestamp order without resorting to a traditional conservative or optimistic synchronization algorithm. Blocking of LPs is required only when the earliest next event is yet to be created or is still being transferred over the interconnect. Hence, the second simulation run is performed with only minimal costs for synchronization. When comparing the simulation performance under a traditional synchronization algorithm with ISP, the costs for synchronization can be studied in isolation. Simulation studies using ISP compare simulation runs under the performance-critical factors  $\{P, L, C\}$  with runs under the factors  $\{P, L, C, S\}$ . De Munck et al. [DMVB13] applied ISP to study the costs of conservative synchronization algorithms in the context of modern hardware environments. By studying two different simulation models and various traditional and novel variants of the null message algorithm, their results show the large dependence of PADS performance on the interaction between the simulation model and the synchronization algorithm, in particular with respect to the null message sending strategy.

#### Analytical Modeling

While a detailed analytical description of the performance of a full simulation run on physical hardware is usually unattainable, analytical modeling can still provide insights into the impact of isolated performance-critical factors or give coarse indications of the expected performance.

Critical Path Analysis is a method that processes an event precedence graph to determine the path containing the events that must be executed in order, i.e., that cannot be executed concurrently. If no weights are assigned to the vertices of the graph representing events, the sum weight of the vertices represents the minimal number of event execution iterations that must be performed to complete the simulation. If this number is divided by the total number of events in the simulation, we arrive at the concurrency of the network model in isolation, i.e., {} in Figure 2.2. Traditional critical path analysis assumes can be considered to assume sufficient lookahead to enable optimal synchronization between logical processes. In Chapter 5 we give an algorithmic description of critical path analysis and propose a variant that assumes a configurable fixed lookahead value.

Liu et al. [LNPP99] performed micro-benchmarks on physical hardware and performed back-ofthe-envelope calculations of the expected performance of parallel simulations under synchronous conservative synchronization. Their estimations consider the performance-critical aspects  $\{P, S, L, C\}$  and in an experiment are able to approximate the runtime of a parallel simulator implementation with an error below 10%. In Chapter 5, we present an analytical estimation method that predicts the raw concurrency of a network model. While Liu et al. assume an even distribution of events to LPs, our approach focuses on the imbalances in event counts between the simulated nodes, enabling concurrency estimations for models of comparatively large complexity.

Park et al. [PFP04] constructed an analytical estimation model for the number of null messages generated in large-scale network simulations. Hence, they consider an aspect of the synchronization costs ( $\{S\}$ ) in a simulation. Their estimations enable predictions of the synchronization overhead in PADS using the null message algorithm.

Pienta et al. [PF13] modeled the concurrency in simulations of networks with node degrees following a power law (scale-free networks). Under an assumed communication pattern between nodes, a recursive term is derived for the number of events executed in each iteration of a simulation under synchronous conservative simulation. Again, calculated concurrency values reflect the concurrency of the network model itself, without considering further performance-critical factors, i.e., {}. The analytical approach presented in Chapter 5 provides more direct insights into a network model's concurrency by not requiring an iterative model. Like Pienta et al., we base our estimations on the YAWNS algorithm (cf. Section 2.1.1). We provide a proof of the soundness of this approach by determining an upper bound for the deviation between the results obtained using YAWNS and critical path analysis under commonly applied assumptions. Additionally, our experiments focus on concrete network models implemented in popular network simulators.

#### Second-Order Simulation

PADS is frequently applied for the evaluation of networked systems. However, the PADS system comprised of a set of interconnected processors, a synchronization algorithm, and a network model can be considered a networked system in itself and can consequently be evaluated using simulations. Based on this observation, a number of previous works have created simulation models of PADS systems similar to simulation models for performance evaluation of general sequential, parallel, and distributed applications [BM02, ZKK04, BKR07, HMS+09, RHB+11, BRM12]. We refer to the simulation of a simulation as *second-order simulation*.

Using second-order simulation approaches, it is possible to consider all performance-critical aspects ( $\{P, S, L, C\}$ ), while individual aspects can still be suppressed to determine their impact on performance in isolation.

Swope et al. [SF87] simulate the execution of distributed simulations using assumed costs for execution of the first-order model code, and for system calls and communication between processors in the first-order simulator. Similarly to the Ideal Simulation Protocol (cf. Section 2.2.2), knowledge of the sequence of future events enables optimal synchronization. Hence, their approach enables an evaluation of the expected simulation performance under the performance-critical factors  $\{P, L, C\}$ .

The following works consider the full set of performance-critical factors  $\{P, S, L, C\}$ .

Wong et al. [WHL95] simulate a conservatively synchronized parallel execution of a simulation during a sequential run of an instrumented simulator implementation.

Juhasz et al. [JTKG01] propose a second-order simulation tool to estimate the expected benefit of parallelization of a simulation model. A trace of the events executed in a sequential run of the first-order simulator is used to guide the execution of the second-order simulation under a number of synchronization algorithms.

Perumalla et al. [PFT<sup>+</sup>05] propose a trace-based second-order simulation approach with a focus on selecting a suitable synchronization algorithm for a given type of first-order model.

Ewald et al. [EHU+06] present a second-order simulation approach implemented in the simulation system JAMES II. Their approach extends the execution of an unmodified first-order simulation model by a second-order simulation model predicting the time required for the interactions between LPs.

Gianni et al. [GID10] combine network model knowledge with benchmarking results on physical hardware to generate a queuing network model of distributed simulations. The PADS runtime is determined by simulating the queuing network in the simulation framework OMNet++.

A key challenge in performance prediction of PADS is the estimation accuracy given events associated with low computational costs. In such cases, two issues pose difficulties: first, it is difficult to accurately measure and predict the costs of fine-grained computations. Second, low per-event computation times tend to increase the impact of network overheads on the resulting simulation performance. However, without a detailed model of the interconnect between LPs, the costs of individual communication operations between LPs will be limited.

Previous works have not focused on estimation accuracy with respect to models with fine-grained computations. In Chapter 6, we present a second-order simulation tool that we use to predict the estimated runtime of simulation of multiple network models with fine-grained computations. We evaluate the prediction accuracy by comparing the predictions to the runtime of PADS runs on physical hardware.

### 2.3 Simulator Adaptation

A variety of previous works has studied the adaptation of the simulator configuration to the given network model. Although some simulations may perform well under a suitable *static* configuration determined prior to the simulation run, network models with highly dynamic or unpredictable behavior may require adaptations of the simulator configuration *at runtime* to achieve high simulation performance. In this section, we give an overview of existing approaches to static and runtime adaptation of the simulator configuration. The overview is structured according to the considered performance-critical factors. Since the impact of the performance-critical factor *communication* is largely determined by the interconnect and the chosen network model *partitioning*, approaches to reduce communication in PADS are discussed as part of the works on partitioning.

#### 2.3.1 Lookahead

The lookahead is central to the performance of PADS under conservative synchronization, since the lookahead determines the length of periods in simulated time that LPs can process without blocking to wait for events or null messages from other LPs. The maximum lookahead that is possible in a simulation is a property of the network model. Typically, the maximum lookahead

in a network model is not fully exploited, since in general, the answer to the associated question "What is the earliest possible timestamp of an event that the current LP will create for another LP" is not trivially answered. A common approach in the field of network simulations is the use of a fixed lookahead value according to a lower bound on the delta in simulated time between an activity in an LP and a resulting activity in a remote LP [Nic96], e.g., the smallest possible link latency between network nodes simulated in separate LPs. To extract further lookahead, it is possible to supply model-specific knowledge to the simulator [MB98, LNo2, CKo6, PVMo9, WDYR13]. A more general solution is given by modeling the state and control flow of the model and analyzing the resulting graph statically or dynamically to determine the shortest possible timestamp of an event created in the current LP for another LP [CS89, MB99, ZPo1].