# MODELING, DESIGN, AND CHARACTERIZATION OF THROUGH VIAS IN SILICON AND GLASS INTERPOSERS

A Dissertation Presented to The Academic Faculty

by

Tapobrata Bandyopadhyay

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology December 2011

COPYRIGHT © 2011 BY TAPOBRATA BANDYOPADHYAY

# MODELING, DESIGN, AND CHARACTERIZATION OF THROUGH VIAS IN SILICON AND GLASS INTERPOSERS

## Approved by:

Dr. Rao R. Tummala, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Saibal Mukhopadhyay School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Venky Sundaram School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Madhavan Swaminathan, Co-Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Sung Kyu Lim School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Suresh Sitaraman School of Mechanical Engineering Georgia Institute of Technology

Date Approved: 22<sup>nd</sup> August, 2011.

#### **ACKNOWLEDGEMENTS**

I would like to express my gratitude to all who have inspired and helped me to complete this dissertation.

I am thankful to my advisor, Dr. Rao R. Tummala, for giving me the opportunity to pursue graduate research in the 3D Systems Packaging Research Center (PRC) at Georgia Institute of Technology. His vision, guidance, and support enabled me to give shape to this thesis. I would like to thank my co-advisor, Dr. Madhavan Swaminathan, for his constant encouragement and active guidance throughout my graduate research. I would like to express my gratitude to Dr. Sung Kyu Lim, Dr. Saibal Mukhopadhyay, Dr. Suresh Sitaraman, and Dr. Venky Sundaram, for their important advice and comments as committee members for my dissertation.

I feel lucky to have had the opportunity to work with very bright and helpful research faculty members in PRC and EPSILON group. I sincerely thank Dr. Mahadevan K. Iyer who actively mentored me during the first couple of years of my research at PRC. I also sincerely acknowledge Dr. Ritwik Chatterjee who mentored me regularly during the next part of my research, specifically for the research work on Si interposers. I'm thankful to Dr. Venky Sundaram for guiding my research for the Silicon and Glass Interposer (SiGI) consortium at PRC. I sincerely appreciate the help and support of Dr. Daehyun Chung, Dr. P.M. Raj, Dr. Sunghwan (Max) Min, and Mr. Nitesh Kumbhat.

My friends and colleagues in PRC and EPSILON group made the journey towards this thesis a pleasant and memorable one. I would like to mention and appreciate all the present student members of PRC and EPSILON - Biancun Xie, Dibyajat Mishra, Gokul Kumar, Jae Young Choi, James Compagnoni, Jianyong Xie, Koushik Ramachandran, Kyuhwan Han, Myunghyun Ha, Partha Chakraborti, Qiao Chen, Sadia Khan, Satyan Telikepalli, Saumya Gandhi, Srikrishna Sitaraman, Suzanne Huh, Vijay Sukumaran, Xian Qin, and Yushu Wang. I also thank past members of PRC and EPSILON - Abdemanaf Tambawala, Abhilash Goyal, Abhishek Choudhury, Ankur Aggarwal, Aswani Kurra, Dhanya Athreya, Gaurav Mehrotra, Gopal Jha, Eddy Hwang, Janani Chandrasekhar, Kanika Sethi, Ki Jin Han, Krishna Bharath, Krishna Srinivasan, Narayanan T.V., Nevin Atltunyurt, Nithya Sankaran, Ranjeeth Doppalapudi, Vishal Laddha, and Vivek Sridharan.

Special thanks to all my wonderful friends who made my stay in Atlanta a memorable one – Ananda Barua, Arindam Basu, Aritra Banerjee, Arun Rambhatla, Arunkumar Subramanian, Arup and Rita, Atri Dutta, Ayan and Payel, Bevin Perumana, Debrup Das, Kousik and Priya, Mrinmoy Ghosh, Nand Kishore and Neha, Padmanava Sen, Prabir Saha, Ramanan Subramanian, Saikat and Payel, Shantanu Dey, Shreyas Sen, Soumendu and Ananya, Subho Chatterjee, and many more.

Finally, no person can be successful without the love and support of his family. My deepest gratitude is reserved for my grandparents – late Mr. Siddhananda Chatterjee, late Mr. Jyotilal Banerjee, Mrs. Sangita Chatterjee, and late Mrs. Roma Banerjee. I humbly and respectfully acknowledge the love, blessings, and sacrifices of my parents – Dr. Urmibrata Bandyopadhyay and Mrs. Susmita Bandyopadhyay. I also thank my sister, Tilottama, for always cheerfully encouraging me.

# TABLE OF CONTENTS

|                                                                    | Page |

|--------------------------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                                   | iv   |

| LIST OF TABLES                                                     | X    |

| LIST OF FIGURES                                                    | xi   |

| SUMMARY                                                            | xvii |

| CHAPTER 1: INTRODUCTION                                            | 1    |

| 1.1 Previous Research on Through Package Vias in Si Interposers    | 6    |

| 1.2 Previous Research on Through Package Vias in Glass Interposers | 7    |

| 1.3 Previous Research on Nano-Copper Interconnections              | 9    |

| 1.4 Outline of Dissertation                                        | 10   |

| CHAPTER 2: TPV IN SILICON INTERPOSERS                              | 11   |

| 2.1 MOS Capacitance in Si TPVs                                     | 11   |

| 2.2 Electrical Modeling                                            | 14   |

| 2.2.1 Full Depletion Approximation Analysis                        | 15   |

| 2.2.1.1 Outer Surface                                              | 15   |

| 2.2.1.2 Inner Surface                                              | 19   |

| 2.2.2 Exact Analysis                                               | 22   |

| 2.2.3 Electrical Model                                             | 29   |

| 2.3 Parametric Study                                               | 35   |

| 2.3.1. Si TPV Diameter                                             | 35   |

| 2.3.2. Liner Thickness                                             | 37   |

| 2.3.3. Liner Material                                              | 38   |

| 2.3.4. Resistivity of Silicon                                      | 39   |

| 2.3.5.     | Si TPV Metal                              | 40 |

|------------|-------------------------------------------|----|

| 2.4 Desi   | ign Guidelines                            | 42 |

| 2.4.1      | Si TPVs in Signal Delivery Network (SDN)  | 42 |

| 2.4.2      | Si TPVs in Power Delivery Network (PDN)   | 43 |

| 2.4.3      | Si TPVs as Variable Capacitors            | 43 |

| 2.5 Elec   | etromagnetic Simulation                   | 44 |

| 2.5.1      | Depletion Region Modeling                 | 44 |

| 2.5.2      | TPVs in Wafer-Si and Panel-Si Interposers | 48 |

| 2.5.3      | Effect of TPV Liner Thickness             | 51 |

| 2.5.4      | Effect of TPV Diameter                    | 53 |

| 2.5.5      | Microstrip Line to Si TPV Transition      | 54 |

| 2.6 Con    | clusion                                   | 57 |

| CHAPTER 3: | : TPV IN GLASS INTERPOSERS                | 58 |

| 3.1 Elec   | etromagnetic Modeling and Simulation      | 58 |

| 3.1.1      | TPVs in Glass and Silicon Interposers     | 59 |

| 3.1.2      | Effect of TPV Diameter                    | 62 |

| 3.1.3      | Effect of Glass and Polymer Choice        | 63 |

| 3.1.4      | CPW Line to Glass TPV Transition          | 64 |

| 3.1.5      | Microstrip Line to Glass TPV Transition   | 67 |

| 3.2 Para   | asitic Extraction of Glass TPVs           | 69 |

| 3.3 Curi   | rent Density Simulation                   | 72 |

| 3.4 Con    | clusion                                   | 78 |

| CHAPT | ER 4: POWER DELIVERY NETWORK DESIGN                                                                      | 80  |

|-------|----------------------------------------------------------------------------------------------------------|-----|

| 4.1   | Power Delivery Network in Si Interposers                                                                 | 80  |

| 4.2   | Power Delivery Network in Glass Interposers                                                              | 87  |

| 4.3   | Conclusion                                                                                               | 93  |

| СНАРТ | ER 5: ELECTRICAL CHARACTERIZATION                                                                        | 95  |

| 5.1   | Si TPV MOS Capacitance                                                                                   | 95  |

| 5.2   | Interconnection Wiring                                                                                   | 96  |

| 5.3   | Through Package Via                                                                                      | 103 |

| 5.4   | Power and Ground Planes                                                                                  | 111 |

| 5.5   | Conclusion                                                                                               | 112 |

| СНАРТ | ER 6: NANO-COPPER INTERCONNECTIONS                                                                       | 113 |

| 6.1   | Modeling and Simulations                                                                                 | 114 |

| (     | 5.1.1 Electromagnetic Modeling                                                                           | 114 |

| (     | 5.1.2 Comparison with Flip-chip Bumps                                                                    | 115 |

| 6.2   | Parametric Study                                                                                         | 116 |

| (     | 5.2.1 Interconnection Shape                                                                              | 117 |

| (     | 5.2.2 Interconnection Dimension                                                                          | 117 |

| (     | 5.2.3 Number of Ground Connections                                                                       | 119 |

| 6.3   | Test Vehicle Design and Measurement                                                                      | 120 |

| 6.4   | Conclusion                                                                                               | 123 |

| СНАРТ | ER 7: CONCLUSIONS                                                                                        | 124 |

| 7.1   | Contributions                                                                                            | 128 |

| 7     | 7.1.1 Accurate Equivalent Circuit-Model of Si TPVs                                                       | 128 |

| 7     | 7.1.2 Power Delivery Network Design in Silicon and Glass Interposers.                                    | 129 |

| •     | 7.1.3 Modeling, Design, Characterization and, Signal Integrity Analysis of Glass and Silicon Interposers |     |

| 7.1.4     | Interconnections          | 131 |

|-----------|---------------------------|-----|

| 7.2 Futu  | re Work                   | 132 |

| 7.3 Publ  | ications                  | 133 |

| 7.3.1     | Book Chapters             | 133 |

| 7.3.2     | Refereed Journal Articles | 133 |

| 7.3.3     | Conference Publications   | 134 |

| 7.3.4     | Awards                    | 137 |

| REFERENCE | ES                        | 138 |

# LIST OF TABLES

|                                                                     | Page |

|---------------------------------------------------------------------|------|

| Table 1: Comparison between organic and silicon interposers in 2010 | 4    |

| Table 2: Work function of metals.                                   | 41   |

| Table 3: Current density in CPW lines.                              | 73   |

| Table 4: Current density in TPVs.                                   | 74   |

| Table 5: Current density in Pd-lined TPVs                           | 75   |

| Table 6: Current density in filled and conformal TPVs               | 77   |

| Table 7: Physical dimensions of co-axial TPVs in glass interposer   | 90   |

| Table 8: Eye diagram parameters of CPW lines.                       | 102  |

# LIST OF FIGURES

|            | F                                                                                                                                                                                     | age |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 1.  | Schematic view of a 3D system                                                                                                                                                         | 2   |

| Figure 2.  | Structure of a through package via in Si interposer (Si TPV)                                                                                                                          | 12  |

| Figure 3.  | Capacitance-Voltage plot for a planar-MOS capacitor in p-type Si                                                                                                                      | 12  |

| Figure 4.  | Schematic cross-section diagram of Si TPV (with SiO <sub>2</sub> liner) biased in the depletion region of operation. (a) Cylindrical Si TPV. (b) Annular Si TPV. (c) Co-axial Si TPV. | 15  |

| Figure 5.  | Energy diagram of a metal-oxide-semiconductor (MOS) junction at flat band condition.                                                                                                  | 16  |

| Figure 6.  | (a) Potential and, (b) Electric field distribution in Si as a function of the distance from the Si-SiO <sub>2</sub> interface when $V_{TPV} = 0.6V$                                   | 23  |

| Figure 7.  | Charge distribution in Si as a function of the distance from the Si-SiO $_2$ interface when $V_{TPV}=0.6V_{\cdots}$                                                                   | 24  |

| Figure 8.  | Per unit length Si TPV capacitance-voltage plots for low frequency operation in (a) p-type doped silicon, and (b) n-type doped silicon                                                | 26  |

| Figure 9.  | Per unit length Si TPV capacitance-voltage plots for high frequency operation in (a) p-type doped silicon, and (b) n-type doped silicon                                               | 27  |

| Figure 10. | Per unit length Si TPV capacitance-voltage plots for deep depletion operation in (a) p-type doped silicon, and (b) n-type doped silicon                                               | 28  |

| Figure 11. | (a) Schematic view, and (b) Equivalent circuit-model of a pair of Si TPVs.                                                                                                            | 30  |

| Figure 12. | Parasitic elements of a pair of Si TPVs. (a) Resistance, (b) Self and mutual inductance, (c) Equivalent conductance, (d) Equivalent capacitance.                                      | 32  |

| Figure 13. | S-parameter comparison of Si TPV model with and without MOS capacitance. (a) Insertion Loss, (b) Return Loss.                                                                         | 34  |

| Figure 14. | Per unit length Si TPV capacitance-voltage plots for different Si TPV diameters.                                                                                                      | 36  |

| Figure 15. | Per unit length Si TPV capacitance-voltage plots for different Si TPV liner thicknesses.                                                                                              | 37  |

| Figure 16. | Per unit length Si TPV capacitance-voltage plots for different Si TPV liner materials                                      | 38 |

|------------|----------------------------------------------------------------------------------------------------------------------------|----|

| Figure 17. | Per unit length Si TPV capacitance-voltage plots for different Si substrate resistivity                                    | 39 |

| Figure 18. | Per unit length Si TPV capacitance-voltage plots for different Si TPV filling metals.                                      | 41 |

| Figure 19. | Two-port Si TPV model in CST Microwave Studio (CST MWS)                                                                    | 44 |

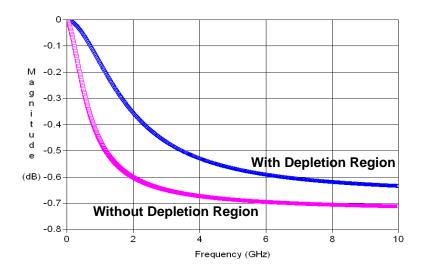

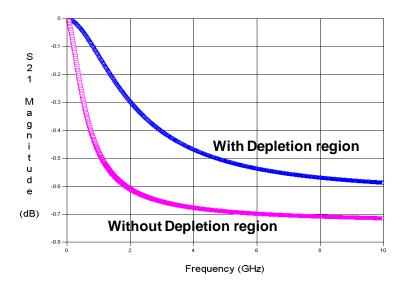

| Figure 20. | Simulation results (Insertion loss) obtained from CST MWS for Si TPVs with and without depletion region.                   | 45 |

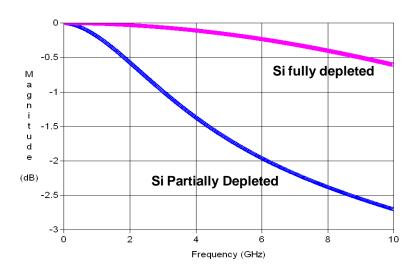

| Figure 21. | Insertion loss comparison of annular Si TPVs.                                                                              | 46 |

| Figure 22. | Insertion loss comparison of co-axial Si TPVs.                                                                             | 46 |

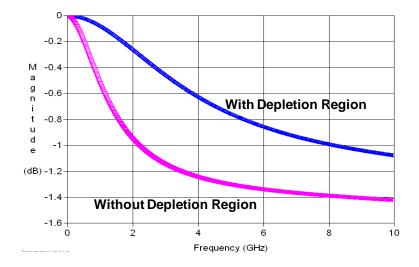

| Figure 23. | Insertion loss comparison of co-axial Si TPVs with the Si (between core and shell) either completely or partially depleted | 48 |

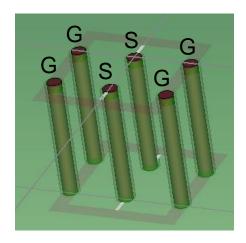

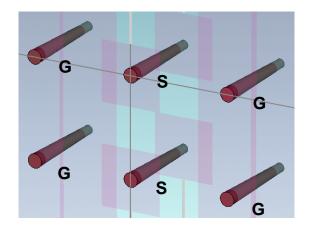

| Figure 24. | Si TPV model in CST Microwave Studio for loss and crosstalk studies                                                        | 49 |

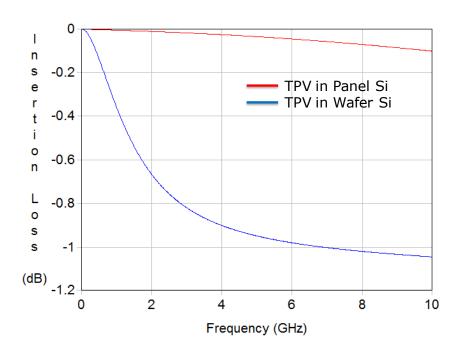

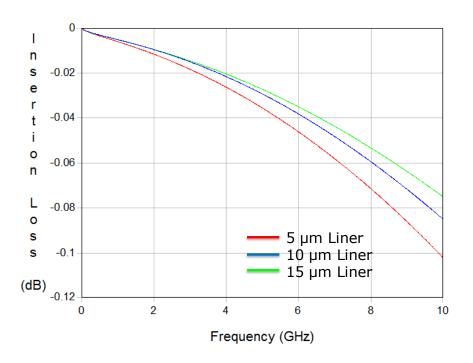

| Figure 25. | Insertion loss comparison between TPVs in panel-Si and wafer-Si interposers.                                               | 50 |

| Figure 26. | Far-end crosstalk comparison between TPVs in panel-Si and wafer-Si interposers.                                            | 50 |

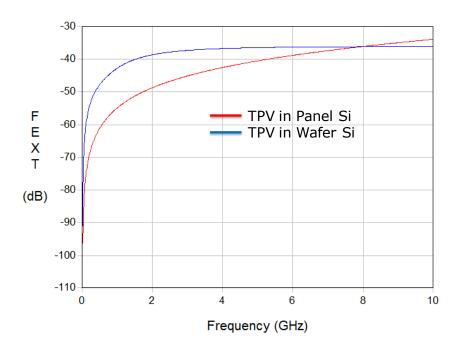

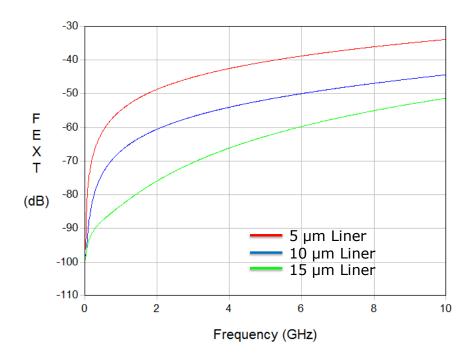

| Figure 27. | Insertion loss plots for TPVs with different liner thicknesses in panel-Si interposer.                                     | 52 |

| Figure 28. | Far-end crosstalk plots for TPVs with different liner thicknesses in panel-Si interposer.                                  | 52 |

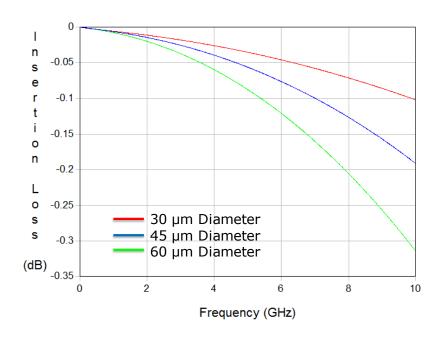

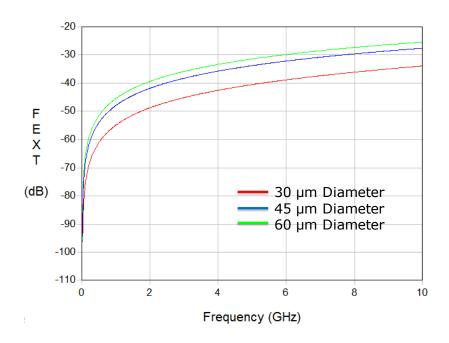

| Figure 29. | Insertion loss plots for TPVs with different diameters in panel-Si interposer.                                             | 53 |

| Figure 30. | Far-end crosstalk plots for TPVs with different diameters in panel-Si interposer.                                          | 54 |

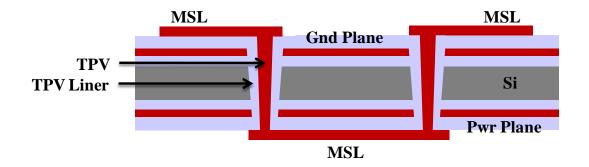

| Figure 31. | Schematic diagram of microstrip line (MSL) to TPV transitions in a four-metal-layer silicon interposer.                    | 55 |

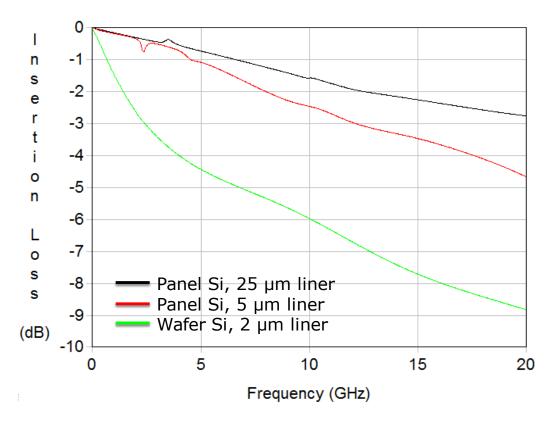

| Figure 32. | Insertion loss plots of MSL-TPV transitions in different silicon interposers.                                              | 56 |

| Figure 33. | Glass TPV model in CST Microwave Studio for loss and crosstalk studies.                                                    | 59 |

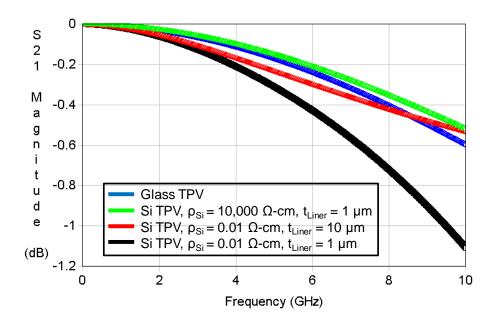

| Figure 34. | Insertion loss comparison between TPVs in glass and silicon interposers.                                                                            | 60 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

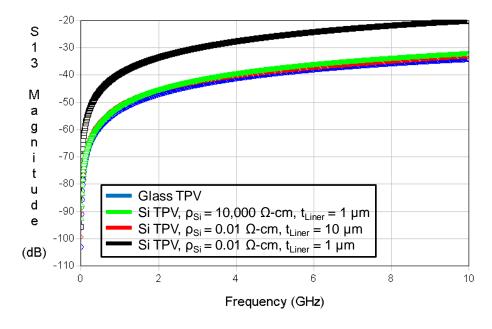

| Figure 35. | Near-end crosstalk comparison between TPVs in glass and silicon interposers.                                                                        | 60 |

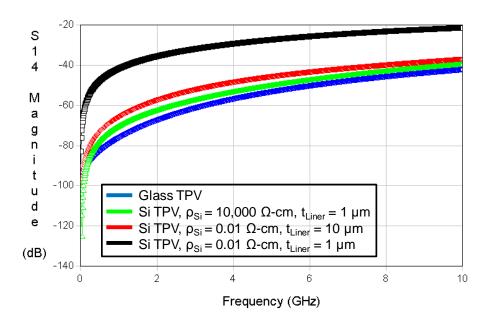

| Figure 36. | Far-end crosstalk comparison between TPVs in glass and silicon interposers.                                                                         | 61 |

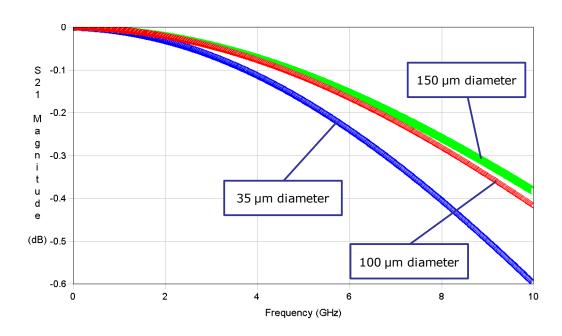

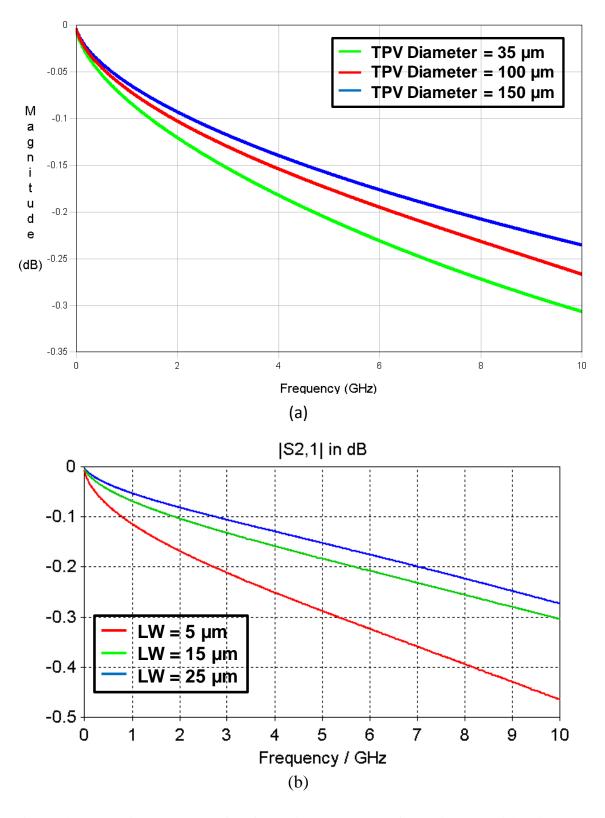

| Figure 37. | Insertion loss plots for glass TPVs of different diameters.                                                                                         | 62 |

| Figure 38. | Far-end crosstalk plots for glass TPVs of different diameters.                                                                                      | 63 |

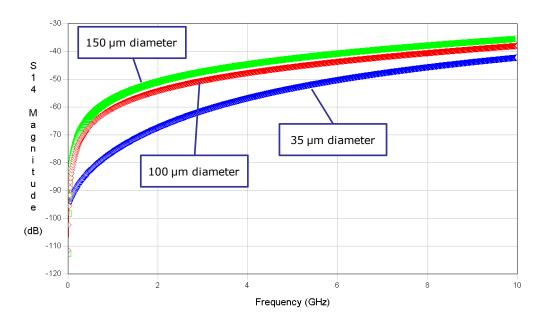

| Figure 39. | Insertion loss plots of TPVs in different glass interposers.                                                                                        | 64 |

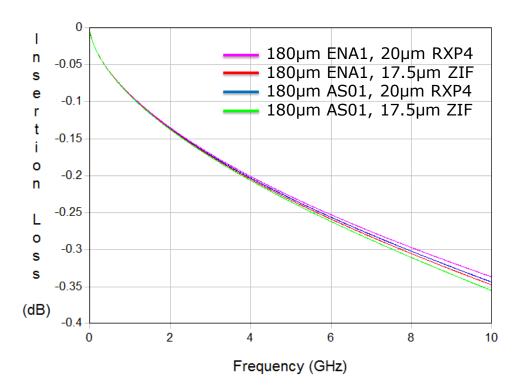

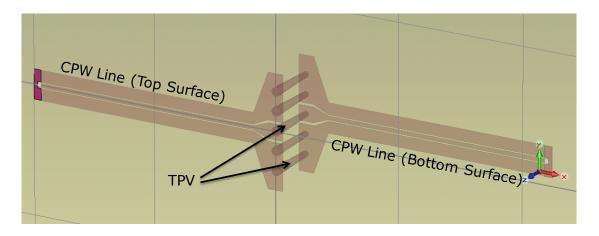

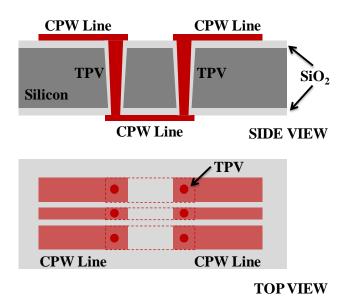

| Figure 40. | Model of co-planar waveguide (CPW) line to TPV to CPW line transition in CST Microwave Studio.                                                      | 65 |

| Figure 41. | Insertion loss plots for CPW line to TPV to CPW line transition in glass interposers. (a) Effect of TPV diameter, (b) Effect of CPW line width (LW) | 66 |

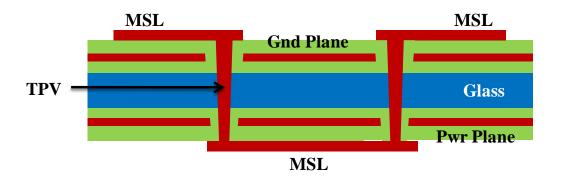

| Figure 42. | Schematic diagram of microstrip line (MSL) to TPV transitions in a four-metal-layer glass interposer.                                               | 67 |

| Figure 43. | Insertion loss plots of MSL-TPV transitions in different glass interposers.                                                                         | 68 |

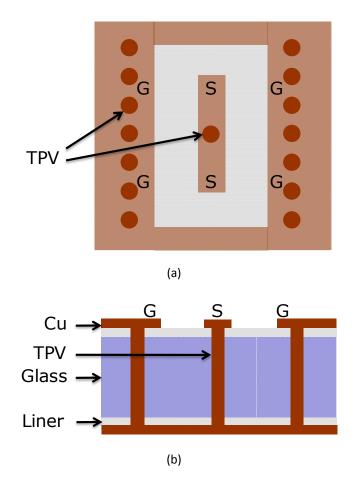

| Figure 44. | Structure for extracting resistance and inductance of TPV. (a) Top View, (b) Side view.                                                             | 70 |

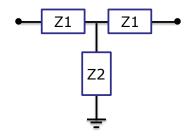

| Figure 45. | Equivalent T-model of the structure shown in Figure 44                                                                                              | 71 |

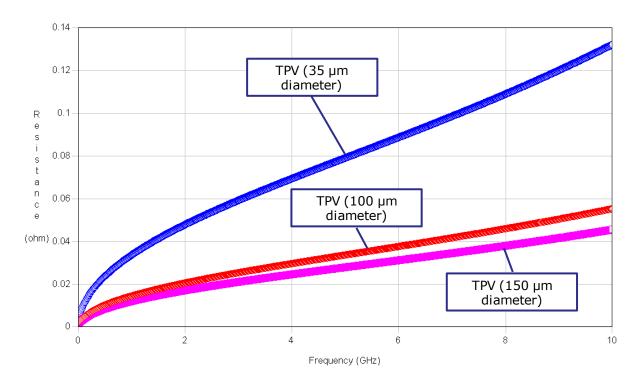

| Figure 46. | Resistance plots for glass TPVs with different diameters.                                                                                           | 71 |

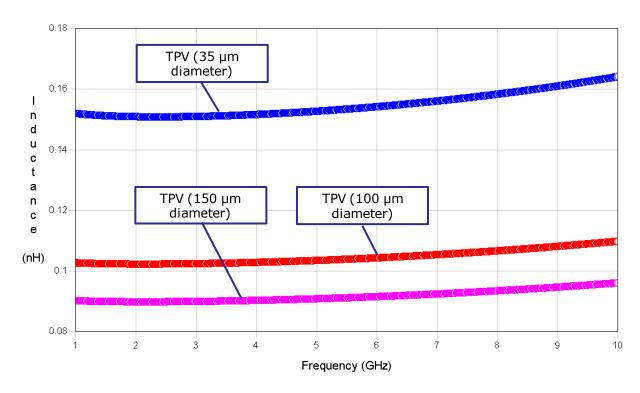

| Figure 47. | Inductance plots for glass TPVs with different diameters                                                                                            | 72 |

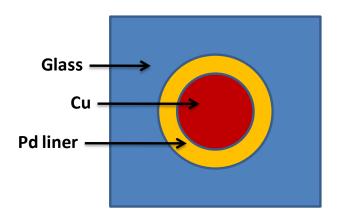

| Figure 48. | Cross-sectional schematic of a Pd-lined TPV in glass interposer                                                                                     | 74 |

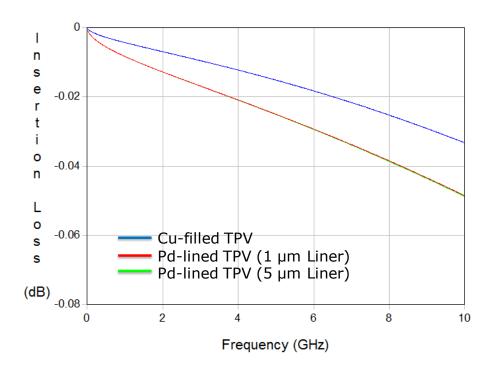

| Figure 49. | Effect of Pd-lining on the insertion loss of TPVs                                                                                                   | 76 |

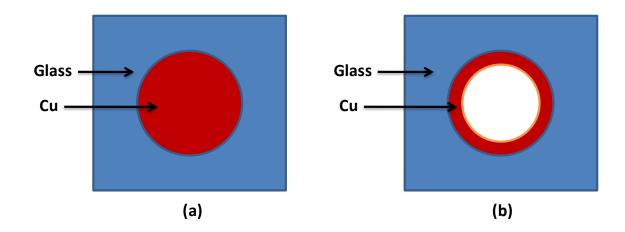

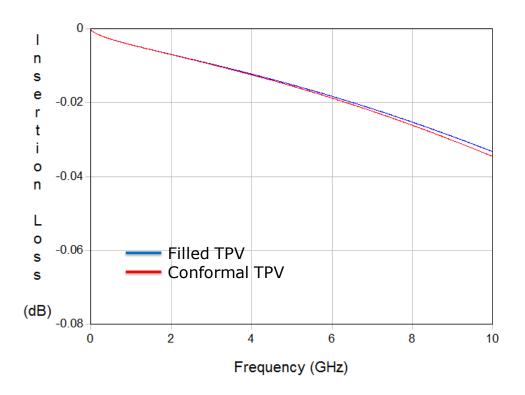

| Figure 50. | Cross-sectional schematic of TPV in glass interposer. (a) Filled TPV, (b) Conformal TPV.                                                            | 77 |

| Figure 51. | Effect of conformal via filling on its insertion loss                                                                                               | 78 |

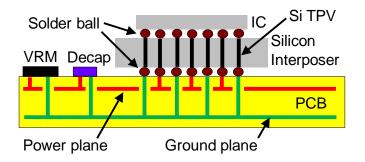

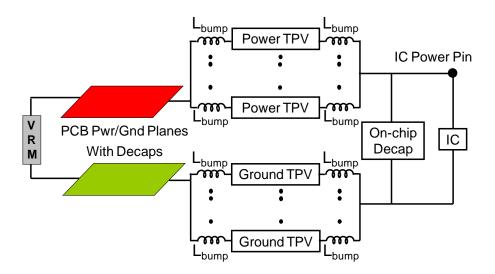

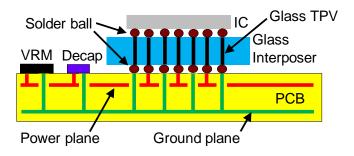

| Figure 52. | Schematic view of the power-delivery network of a 3D system with Si interposer.                                                                     | 81 |

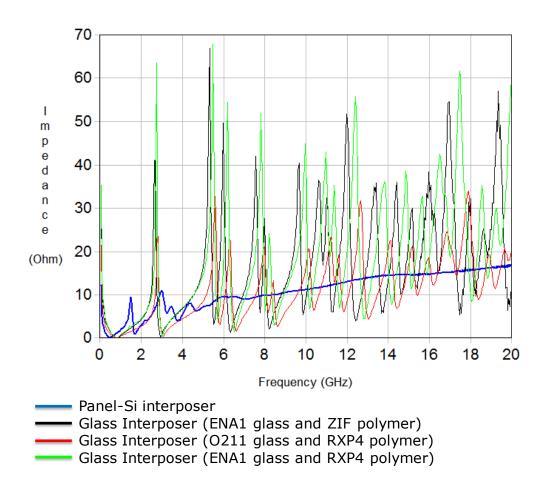

| Figure 53. | Conceptual model of power-delivery network of a 3D system                                                                                                                                                                 | 82   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

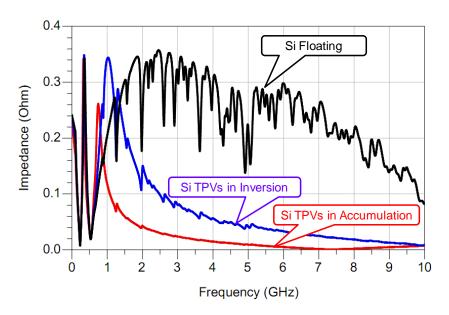

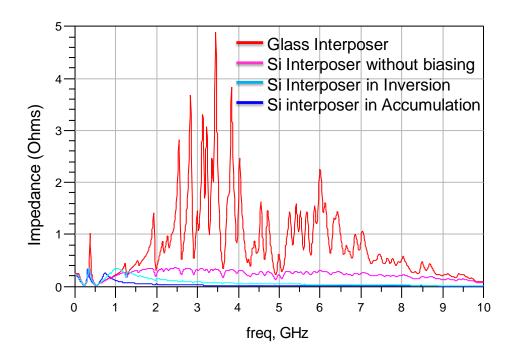

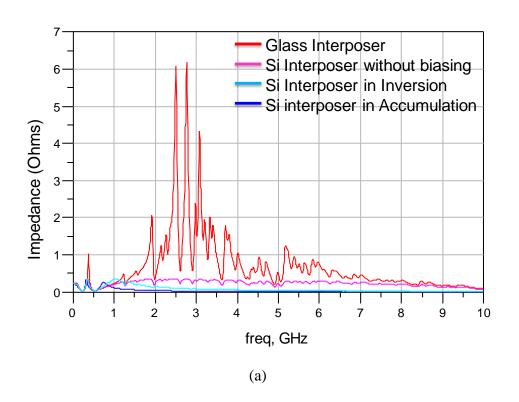

| Figure 54. | Simulated impedance plots at the IC power pin of a 3D system                                                                                                                                                              | 83   |

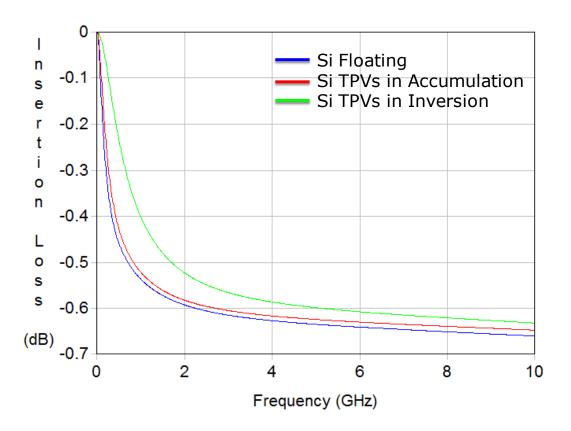

| Figure 55. | Insertion Loss of Si TPVs under different biasing conditions                                                                                                                                                              | 85   |

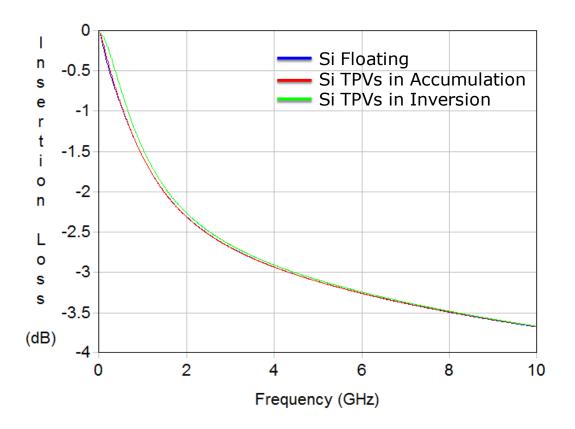

| Figure 56. | Insertion loss of CPW-TPV-CPW signal path in Si interposer under different biasing conditions                                                                                                                             | 86   |

| Figure 57. | Schematic view of the power-delivery network of a 3D system with glass interposer                                                                                                                                         | 87   |

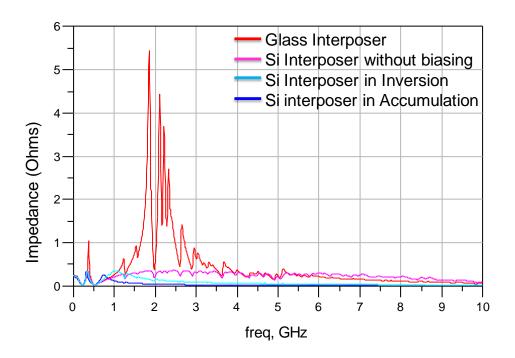

| Figure 58. | Simulated impedance plots at the IC power pin of a 3D system. The glass interposer PDN consists of 1 pF on-chip decoupling capacitor                                                                                      | 88   |

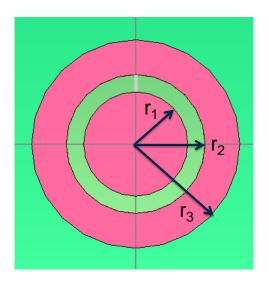

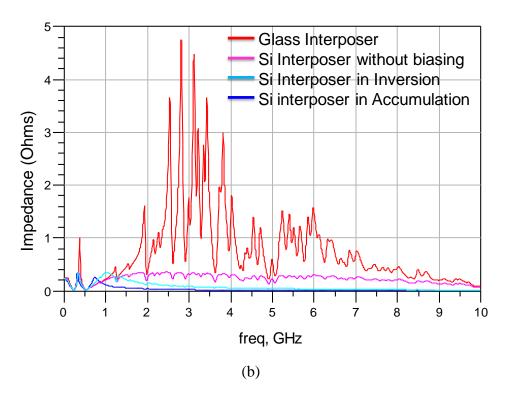

| Figure 59. | Schematic of a co-axial TPV.                                                                                                                                                                                              | 89   |

| Figure 60. | Simulated impedance plots at the IC power pin of a 3D system. The glass interposer PDN consists of co-axial TPVs and 1 pF on-chip decoupling capacitor. (a) Glass interposer with TPV A, (b) Glass interposer with TPV B. | 91   |

| Figure 61. | Simulated impedance plots at the IC power pin of a 3D system. The glass interposer PDN consists of 100 pF on-chip decoupling capacitor                                                                                    | 92   |

| Figure 62. | Simulated impedance plots at the IC power pin of a 3D system. The glass interposer PDN consists of 2 nF on-chip decoupling capacitor                                                                                      | 93   |

| Figure 63. | Model-to-Measurement correlation of the Si TPV capacitance based on measured data from [58].                                                                                                                              | 96   |

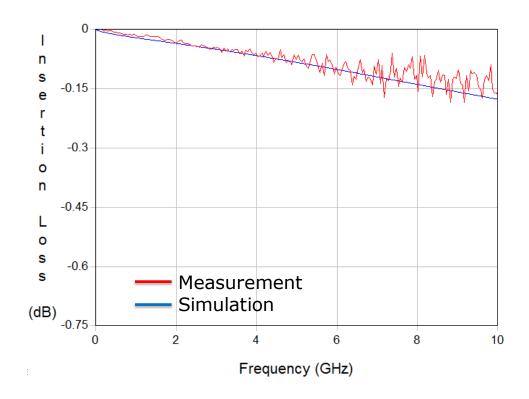

| Figure 64. | Insertion loss plot of a co-planar waveguide (CPW) line in SiO <sub>2</sub> -coated, Si interposer (Wafer-Si interposer)                                                                                                  | 97   |

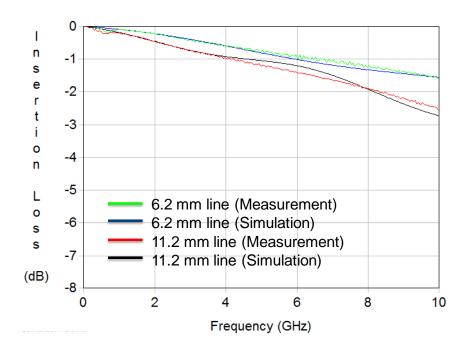

| Figure 65. | Insertion loss plots of CPW lines in polymer-laminated, polycrystalline Si interposer (Panel-Si interposer).                                                                                                              | 98   |

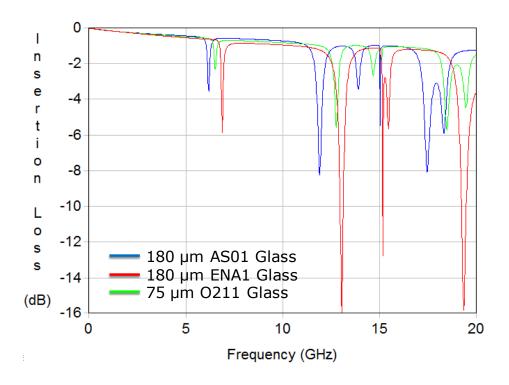

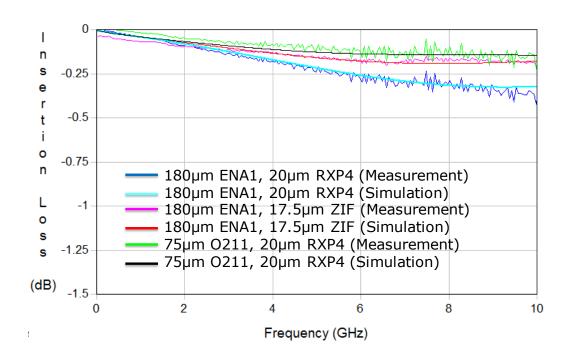

| Figure 66. | Insertion loss plots of 6.2 mm long CPW lines in glass interposers                                                                                                                                                        | 99   |

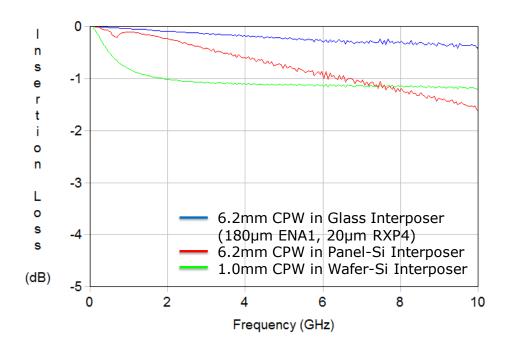

| Figure 67. | Comparison of measured insertion loss of CPW lines in glass, panel-Si, and wafer-Si interposers.                                                                                                                          | .100 |

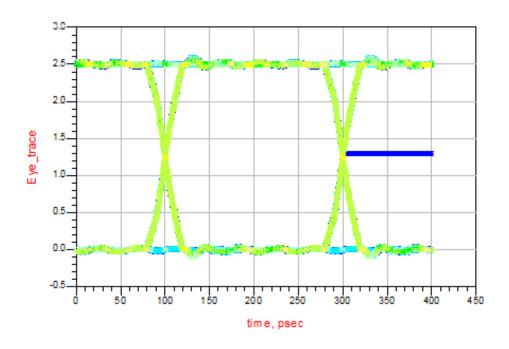

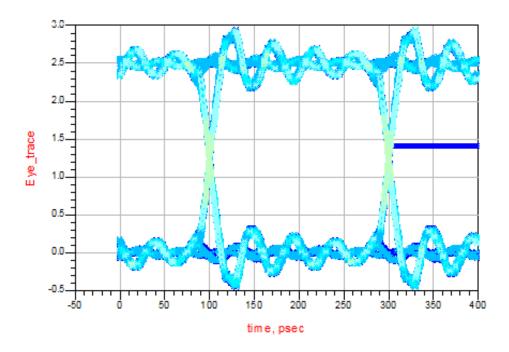

| Figure 68. | Eye diagram of CPW line (1 mm long) in wafer-Si interposer when excited by a 5 Gbps pseudo-random bit stream (PRBS)                                                                                                       | .101 |

| Figure 69. | Eye diagram of CPW line (1 mm long) in panel-Si interposer when excited by 5 Gbps pseudo-random bit stream (PRBS).                                                                                                        | .101 |

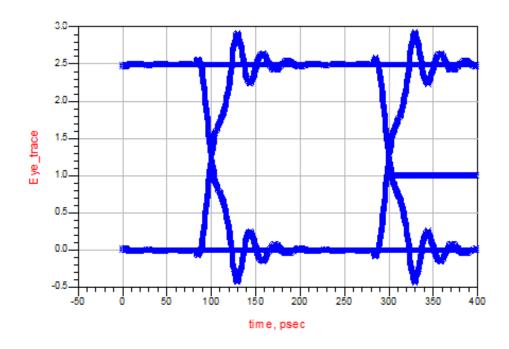

| Figure 70. | Eye diagram of CPW line (1 mm long) in ENA1 glass interposer when excited by 5 Gbps pseudo-random bit stream (PRBS).                             | 102 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 71. | Schematic of a CPW-TPV test structure in Si interposer                                                                                           | 104 |

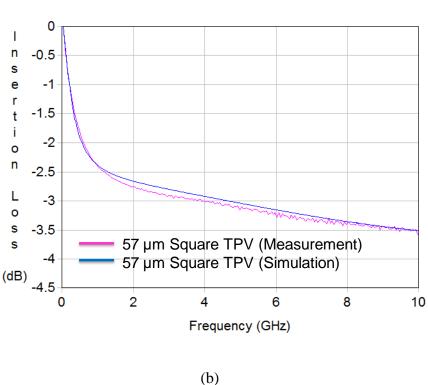

| Figure 72. | Insertion loss plots for CPW-TPV test structures in wafer-Si interposer.  (a) TPV with circular cross-section. (b) TPV with square cross-section | 105 |

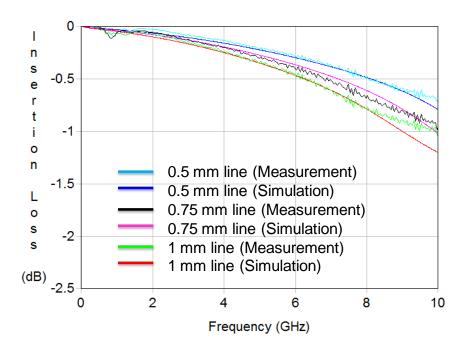

| Figure 73. | Insertion loss plots for CPW-TPV test structures in panel-Si interposer                                                                          | 107 |

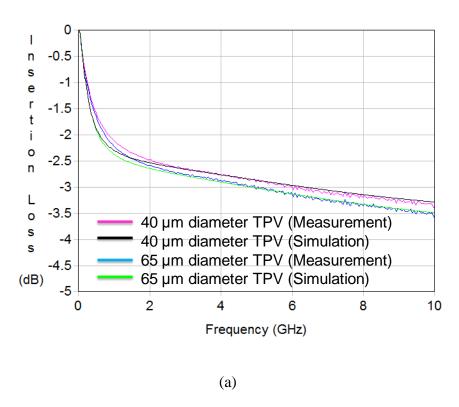

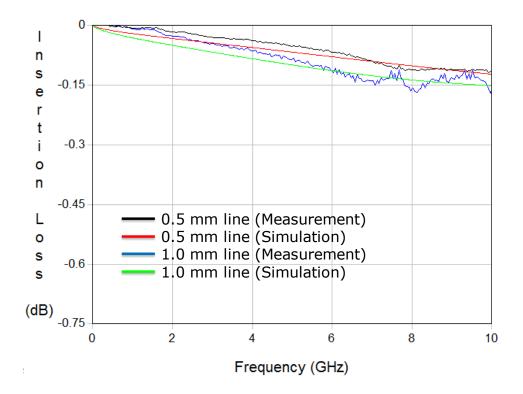

| Figure 74. | Insertion loss plots of CPW-TPV structures in ENA1 glass interposer with RXP4 polymer coating on surface.                                        | 108 |

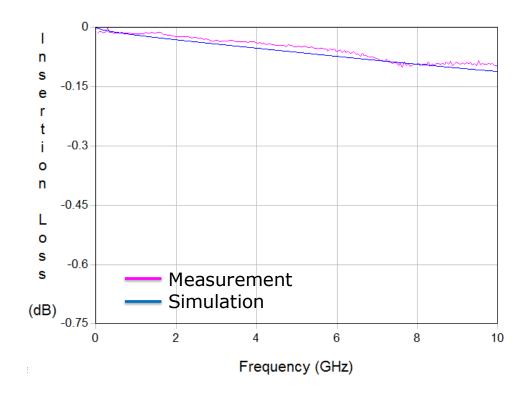

| Figure 75. | Insertion loss plot of CPW-TPV structure in ENA1 glass interposer with ZIF polymer coating on surface.                                           | 109 |

| Figure 76. | Insertion loss plot of CPW-TPV structure in O211 glass interposer with RXP4 polymer coating on surface.                                          | 110 |

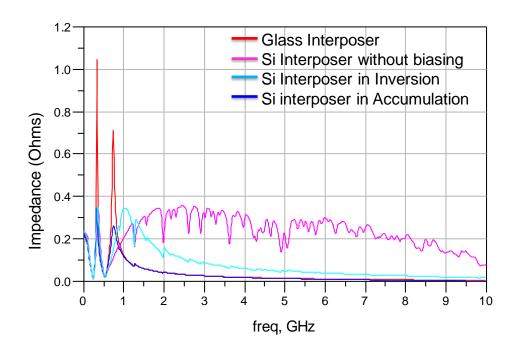

| Figure 77. | Measured impedance plots of glass interposers and panel-Si interposers                                                                           | 111 |

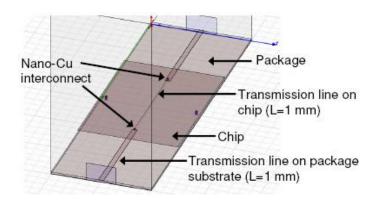

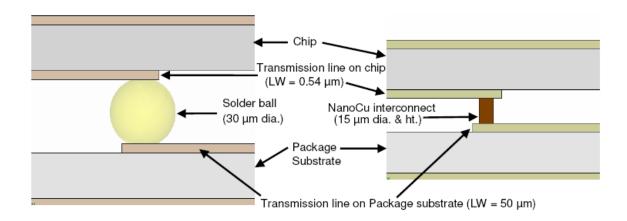

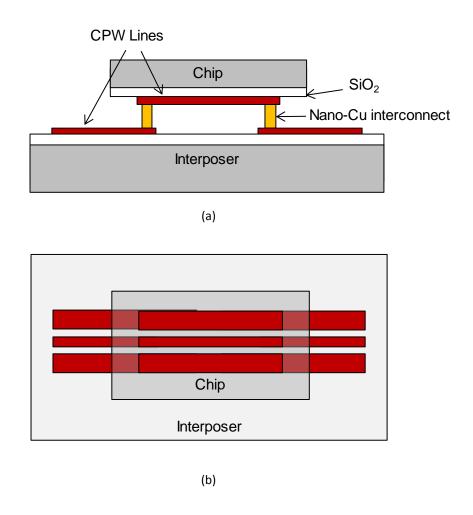

| Figure 78. | Cross-section view of a chip-on-interposer configuration with nano-copper interconnections.                                                      | 113 |

| Figure 79. | Cross-section view of a chip-on-chip configuration with nano-copper interconnections.                                                            | 114 |

| Figure 80. | HFSS model for a chip-on-interposer configuration with nano-copper interconnection.                                                              | 115 |

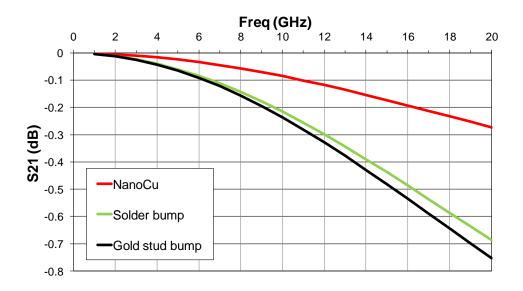

| Figure 81. | A comparison between traditional solder ball flip-chip and nano-copper interconnection.                                                          | 116 |

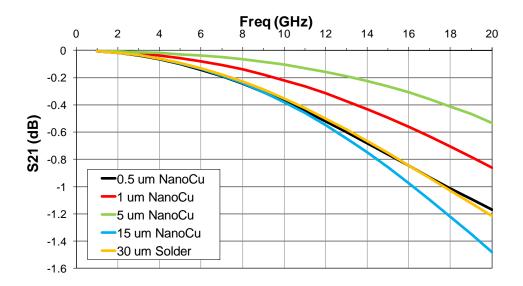

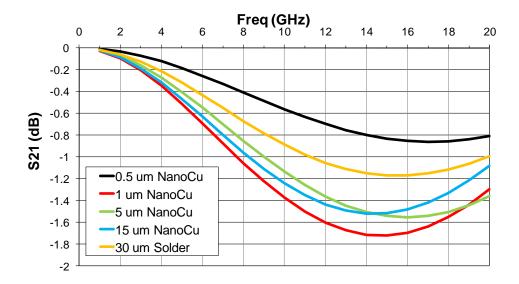

| Figure 82. | The effect of interconnection material on signal transmission                                                                                    | 116 |

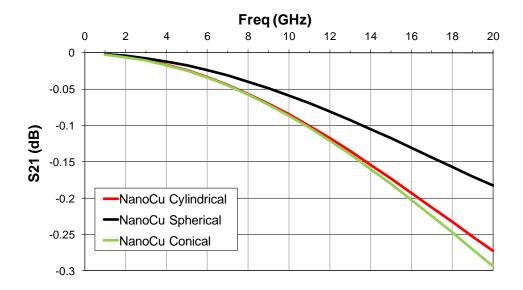

| Figure 83. | The effect of shape of nano-copper interconnections on system response in a chip-on-interposer configuration                                     | 117 |

| Figure 84. | A parametric study on the dimensions (diameter and height) of the nano-copper interconnections in a chip-on-interposer configuration             | 118 |

| Figure 85. | A parametric study on the dimensions (diameter and height) of the nano-copper interconnections in a chip-on-chip configuration.                  | 119 |

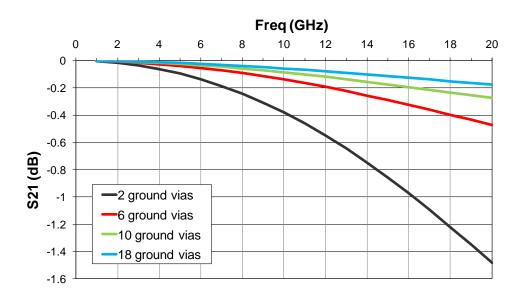

| Figure 86. | System response variations due difference in the number of ground bumps/vias connections in a chip-on-interposer configuration.                  | 120 |

| Figure 87. | Schematic view of Test Vehicle. (a) Side view, (b) Top view                                                                                      | 121 |

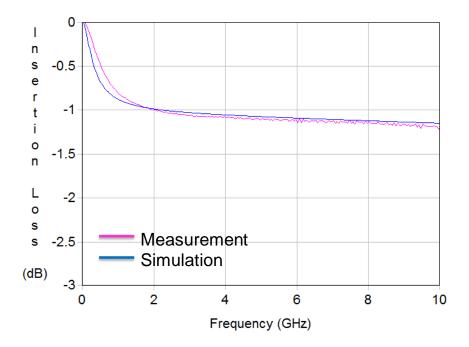

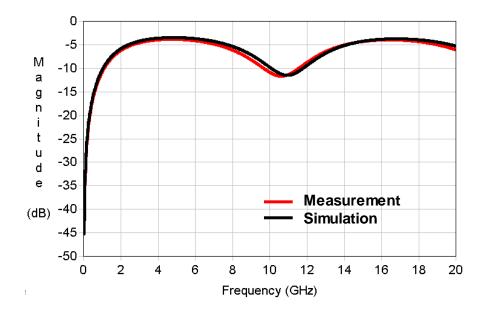

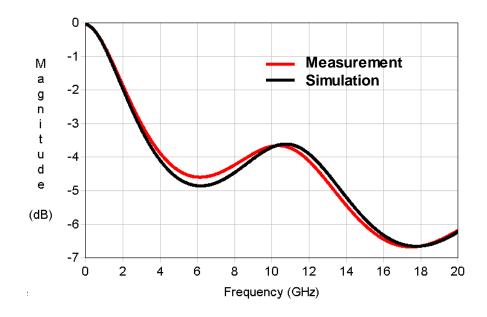

| Figure 88. Return loss comparison between measurement and simulation results     | 122 |

|----------------------------------------------------------------------------------|-----|

| Figure 89. Insertion loss comparison between measurement and simulation results. | 122 |

### **SUMMARY**

During the last decade, the trend in consumer electronics has been to develop products with better performance, smaller size, lower cost, and enhanced functionality. Convergent systems need technologies that can integrate digital, RF, analog, and sensor functions with minimal interference. Multi-function integration can be achieved by chip stacking, using 3D IC technology. The 3D IC technology requires very high-density chip-to-interposer interconnections. Organic interposers fail to achieve these targets because of poor dimensional stability, poor thermal performance, high co-efficient of thermal expansion (CTE) mismatch with silicon die, and high cost. Silicon and glass-based 3D interposers are potential candidates for fulfilling the requirements of next-generation ICs and 3D ICs.

The objective of this dissertation is to electrically model through vias in 3D interposers considering silicon biasing effects and, to address power and high-speed signal-integrity issues in 3D interposers.

Accurate electrical modeling of the through package via (TPV) in a 3D interposer is very important. An equivalent circuit-model representation of the TPV enables interposer design and analysis using circuit solvers which is much faster than full-wave 3D electromagnetic simulations. To generate an accurate circuit-model of the TPVs in Si interposers (Si TPVs), it is essential to model the MOS capacitance effect. This dissertation proposes, for the first time, an equivalent circuit-model of the Si TPV considering the bias-voltage-dependent metal-oxide-semiconductor (MOS) capacitance

effect. Important design guidelines and optimizations for the Si TPVs used in the signal-delivery network (SDN), power-delivery network (PDN), and as variable-capacitor elements are proposed.

Glass has excellent insulating properties (just like SiO<sub>2</sub>) as compared with the semiconducting nature of silicon. This dissertation studies and compares the advantages and disadvantages of glass and silicon as electronic package substrate materials for 3D interposers. The TPVs in glass interposers (Glass TPVs) are modeled, designed, and simulated by using electromagnetic field solvers. Signal and power integrity analyses are performed for Si TPVs as well as for glass TPVs.

Power integrity plays an important role in driving system performance. Therefore, it is essential to acquire an in-depth understanding of the issues that impact the power integrity of 3D interposers. To provide clean power, decoupling capacitors need to be placed close to the chips. This dissertation presents PDN design in silicon interposers by using the MOS capacitance of Si TPVs for decoupling. In this way, the Si TPV is used not only as an interconnection and wiring element, but also as an important passive component in Si interposers.

High-speed signal-integrity is vital in any electrical system design. In 3D interposers, the issue of crosstalk between high-density TPVs is a concern. Silicon interposers suffer from high substrate loss and enhanced coupling between Si TPVs because of the finite conductivity of Si. This dissertation presents the comparative analysis of the signal-delivery network in 3D interposers for high-speed signal transmissions.

The electrical parasitics of traditional solder-based flip-chip interconnections (for chip-to-chip and chip-to-interposer applications) need to be reduced by at least an order of magnitude considering the clock frequency, supply voltage, and signal-to-noise ratio of future RF and analog mixed-signal systems. In addition, the losses associated with the chip-to-interposer interconnection transitions need to be minimized. To address these challenges, this dissertation presents the electrical modeling, simulation, and characterization of a novel ultra-fine pitch, nano-structured copper-based interconnection technique. Nano-structured electroplated copper is chosen as the interconnection material because of its excellent toughness, fracture strength, good electrical conductivity, and resistance to electromigration. The electrical performance of these interconnections are studied, and compared with traditional Pb-free solder interconnections for chip-to-chip and chip-to-interposer applications.

The major contributions of this dissertation are as follows:

- Accurate equivalent circuit-model of Si TPVs considering MOS capacitance effects.

Design guidelines for Si TPVs in (i) signal-delivery network, (ii) power-delivery network, and (iii) variable-capacitor applications.

- 2. Power-delivery network design in silicon interposers (using Si TPVs as decoupling capacitors) and glass interposers.

- Modeling, design, characterization, and signal-integrity analysis of interconnections in glass and silicon interposers.

- 4. Modeling, design, and characterization of nano-structured copper-based (Nano-Cu) chip-to-interposer interconnections.

#### CHAPTER 1

#### INTRODUCTION

Advancements in very large scale integration (VLSI) technology, following Moore's Law, have led to unprecedented transistor and interconnection scaling. As a result, interconnection delay in long global wires is an increasing problem in ICs relative to delays in transistor switching [1, 2]. In the latest microelectronics technology nodes, interconnection delay has become the limiting factor in determining the speed of digital systems [3]. Further, miniaturization by traditional IC scaling in future planar-CMOS technology faces significant challenges [4]. Stacking of ICs using three-dimensional (3D) integration technology helps in significantly reducing wiring lengths, interconnection latency, and power dissipation while reducing the size of the chip and enhancing performance [3, 5-9].

Through silicon vias (TSVs), which are through vias in the IC, are a key enabling technology for 3D IC integration which helps in realizing highly miniaturized, complex, next-generation systems [4]. The 3D integration with TSVs [10-13] has several advantages over wirebonding such as shorter interconnection length, lower electrical parasitics and latency, and higher bandwidth. The TSVs can be formed as area arrays in contrast to peripheral wirebonding leading to greater vertical-interconnection density and reduced form factor [14]. The TSVs also enable heterogeneous integration by stacking ICs with different technologies (e.g., digital IC, analog IC, power IC, MEMS, sensor chips, etc.).

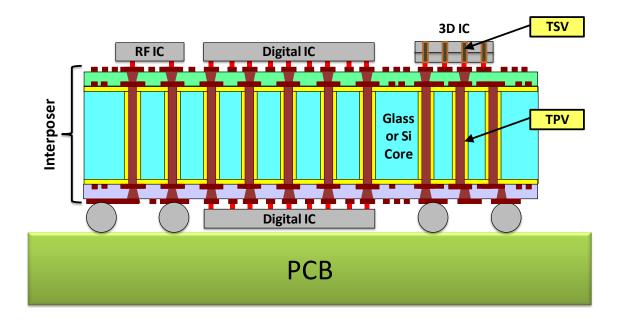

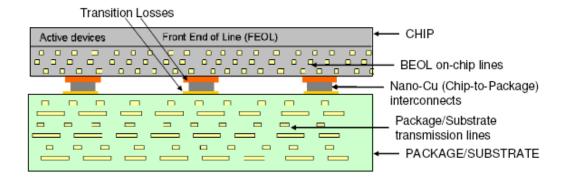

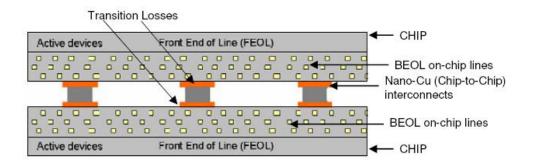

The 3D ICs require large number of I/O connections from the chip stack to the interposer (also known as the package). There is a need to develop low-cost interposer technology which can support this huge I/O need for next-generation 3D ICs. This requires fine-pitch lines, blind vias, and through vias in the interposer. The through vias in the interposer are known as through package vias (TPVs) [15]. The TSVs in stacked ICs as well as TPVs in glass or silicon interposers are important components of a 3D system. Figure 1 shows the schematic view of a 3D system consisting of several ICs and 3D ICs assembled on a high-density interposer which, in turn, is connected to the Printed Circuit Board (PCB).

Figure 1. Schematic view of a 3D system (Source: 3D Systems Packaging Research Center).

Interposer technology from the 1960s to the early 1990s was based on ceramic substrates. In the early 1990s, the high performance IC packaging industry transitioned from thick-film-based ceramic substrates to thin-film-based organic interposers, primarily

for cost and performance reasons. Since then, much progress has been made in increasing the wiring density and high I/O capabilities, and reducing the cost of this technology [16, 17]. The organic interposer is now the standard and more than a billion units have been manufactured to package ICs.

Three major barriers are foreseen with organic interposers – (i) limitation in supporting high I/O requirements, (ii) thermal performance, and (iii) cost. All of these barriers limit the use of organic interposers to above 10  $\mu$ m lithography technologies at about 50  $\mu$ m pitch. In addition, as the number of layers are increased the organic interposer suffers from warpage [15, 18]. The 3D ICs require I/O pitch down to 10-30  $\mu$ m with lithography ground rules around 1  $\mu$ m. Therefore, the challenges for organic interposers are two-fold, as follows:

- (i) Poor dimensional stability: Organic interposers suffer from poor dimensional stability which makes alignment of vias in one layer with vias in the next layer impossible without big capture pads. This prevents from achieving the necessary I/O densities.

- (ii) High co-efficient of thermal expansion (CTE) mismatch: Organic interposers suffer from high CTE of 18 ppm/°C as compared to silicon of 3 ppm/°C. This large CTE mismatch leads to ultra-low k (ULK) reliability challenges within ICs and 3D ICs. Further, it creates a reliability concern for the interconnection between the interposer and the IC or 3D IC.

Silicon interposers overcome the above problems with organic interposers. They can achieve very high I/O densities because of their excellent dimensional stability and smooth surface finish [19, 20]. Other advantages of silicon interposers are the wide availability of fabrication equipment for wafer processing, and perfect match between the CTEs of the IC and the interposer. Table 1 compares the properties of organic and silicon interposers.

Table 1: Comparison between organic and silicon interposers in 2010.

| Property                               | Organic Interposer       | Silicon Interposer      |

|----------------------------------------|--------------------------|-------------------------|

| IC-to-Interposer Interconnection Pitch | 60-100 μm                | 40 μm                   |

| Interposer line width                  | 20 μm                    | 0.8 µm                  |

| IC-to-Interposer CTE match             | 3 ppm/°C to<br>17 ppm/°C | 3 ppm/°C to<br>3 ppm/°C |

| Dimensional Stability                  | Poor                     | Good                    |

Silicon interposers face a different set of challenges. They suffer from high electrical loss because of the semiconducting nature of the substrate. Silicon interposer is a costly technology because of expensive wafer-level back end of line (BEOL) facilities, tools, materials, and processes. These interposers are limited to 300 mm wafer sizes.

Glass interposer is a potential alternative to overcome the above-mentioned shortcomings of silicon interposer. Glass, like  $SiO_2$ , has very high electrical resistivity ( $10^{12}$ - $10^{16}$   $\Omega$ -cm) and is dimensionally stable up to at least 500°C. The CTE of glass is close to the CTE of silicon die. Additionally, glass is available in ultra thin (less than 100  $\mu$ m thickness) and ultra-large (more than 10 sq. meters) panels by a new process called

"Fusion Process" invented by Corning Glass [21]. Large glass panels used for high-definition liquid crystal displays (LCD) can be easily used for processing glass interposers to achieve low cost and high throughput. Availability of thin glass panels eliminates the cost of thinning down the interposer which is required for silicon interposer technology.

However, silicon has some advantages over glass such as superior thermal conductivity. The semiconducting nature of the silicon substrate can also be used for important and novel designs. For example, the voltage-dependent MOS capacitance associated with TPVs in silicon interposers (Si TPVs) can be utilized for power supply decoupling as well as for tunable capacitors and filters.

As mentioned earlier, 3D ICs require ultra-fine pitch interconnections between the IC and the interposer. Reducing I/O pitch and interconnection losses are the two key technological barriers identified by the ITRS [4] for micro/nano electronic modules. The state-of-the-art chip-to-interposer flip-chip interconnections have 30-50  $\mu$ m diameters (60-80  $\mu$ m pitch) whereas the substrate interconnections have 50-100  $\mu$ m line width. Solder based flip-chip interconnections have parasitics (R, L, C) of 27-41 m- $\Omega$  [22], 0.1 nH (approximately), and 0.1-0.5 pF [22]. The solder alternatives (ACA/ACF) suffer from high cross-talk between the particles beyond 20 GHz [23].

The above parasitics should be reduced by at least an order of magnitude considering the clock frequency, supply voltage, and signal-to-noise ratio of future RF and analog mixed-signal systems. In addition, the losses associated with the chip-to-interposer interconnection transitions should be minimized. To address these challenges,

this dissertation proposes a novel, ultra-fine pitch chip-to-interposer interconnection technique based on nano-structured copper. Nano-structured electroplated copper is chosen as the interconnection material because of its excellent toughness, fracture strength [24], good electrical conductivity, and resistance to electromigration.

#### 1.1 Previous Research on Through Package Vias in Si Interposers

Electrical modeling of Si TPVs is very important for 3D system design and analysis, and consequently there have been several publications focusing on Si TPV modeling and simulations. In [25-27], two-port vector network analyzer (VNA) measurements were performed on Si TPVs. An equivalent circuit-model of the Si TPVs was proposed and its parameters were fitted to match the measured data. In [28], 2-port VNA measurements were performed on a two Si TPV chain. The S-parameters of the Si TPVs were obtained by de-embedding the interconnection lines. An equivalent circuit-model was proposed and its parameters were fitted to the de-embedded measurement data. However, in these studies, the Si substrate was left floating without any bias on it. In [29], a simplified R-L model of a Si TPV was extracted from VNA measurement without biasing the Si substrate, as well.

In [30], Si TPVs were analyzed as parallel round wires. An equivalent circuit-model for Si TPVs was proposed based on this analysis and the results were compared with full-wave electromagnetic (EM) simulation results. The circuit-model correlated well with the simulation results only beyond 30 GHz. The Si substrate was not biased in either the analysis or the EM simulation. In [31], an equivalent circuit-model of four Si TPVs (in GSSG configuration) was proposed and its values were obtained by curve

fitting to simulation results. An analytical modeling of propagation delay in Si TPVs was presented in [32]. In [33], equivalent circuit-models of isolated and coupled Si TPVs were presented. The model parameters were expressed by empirical equations and extracted using a quasi-static electromagnetic field solver.

All the aforementioned papers related to Si TPV modeling have considered the Si substrate as a lossy dielectric material and ignored its semiconducting properties. These models neglect the voltage-dependent MOS capacitance associated with Si TPVs. Ignoring the semiconductor properties of the substrate and the resulting MOS capacitance introduces significant inaccuracies in the modeling of the capacitance in these structures.

This dissertation presents in-depth study of the semiconducting and biasing effects in silicon interposers. It presents a more accurate electrical model of a Si TPV by considering the MOS capacitance effects. The results are correlated with measurement data to validate the model. Design guidelines are proposed for designing Si TPVs in the signal and power-delivery networks as well as for Si TPVs in variable-capacitor applications. Power-delivery network in silicon interposers is designed using Si TPVs as decoupling capacitors.

#### 1.2 Previous Research on Through Package Vias in Glass Interposers

Glass as an electronic packaging substrate has been investigated in the recent past. The research has mostly focused on the formation and metallization of interconnections in glass interposers. Fraunhofer IZM has reported on through via formation using different lasers and surface metallization in glass. Formation of optical waveguides on glass using ion exchange methods have been studied for photonic

applications [34-37]. The use of excimer laser machining for forming pads, traces, and microvias in glass substrates have also been explored [38].

Laminated glass substrates have been examined by Loughborough University for interconnecting ICs and photonic devices [39]. The key challenges addressed were via formation in glass using lasers, direct metallization in glass using self-assembled monolayers (SAM), and glass-to-glass bonding to from a multi-layer interposer. The NEC Schott company has demonstrated the use of glass wafers with metalized tungsten vias providing electrical connection and hermetic sealing [40]. This approach is based on flowing glass over tungsten plugs resulting in through vias (approximately 100 µm in diameter) in glass substrate.

This dissertation focuses on the modeling, design, signal-integrity analysis, and characterization of TPVs in glass interposers. Electromagnetic modeling and simulations are performed for glass TPVs with different dimensions to study the signal loss and crosstalk. The electrical performance of glass TPVs is compared with Si TPVs. Redistribution layer (RDL) line to TPV transition structures are designed and simulated to estimate the loss and crosstalk. The effect of varying different material and physical parameters of the interconnections in the glass interposer on the signal-integrity is studied.

#### 1.3 Previous Research on Nano-Copper Interconnections

Nano-structured metal-based interconnections have been developed and studied [24, 41-43]. Most of the research in this area has focused on the fabrication and reliability of these interconnections. Nano-structured nickel-based chip-to-interposer interconnections have been developed at 200 µm pitch [41]. Resistance and inductance of the Nano-nickel interconnections were extracted from measured data and compared with solder based interconnection.

It has been reported that nano-structured copper interconnections have enhanced fracture toughness and fatigue resistance as compared with bulk copper [24]. Nano-structured metals usually have higher resistivity than bulk metals [44, 45]. However, it was shown that nano-structured copper with a high density of nanoscale growth twins have enhanced tensile strength but similar electrical resistivity as compared to pure copper [46]. The electrical parasitics of the Nano-Cu interconnections have been extracted from EM simulations [42, 43]. The simulated response was curve fitted to an equivalent circuit-model to extract the electrical parasitics.

This dissertation studies the high-frequency performance of nano-copper-based chip-to-interposer interconnections (with dimensions in the order of 15 to 0.5  $\mu$ m) for chip-on-interposer and chip-on-chip configurations. Physical and material parametric studies are performed on this interconnection by means of full-wave EM simulations. Important interconnection and package design guidelines (obtained from the parametric analysis) are also presented for this nano-copper-based chip-to-interposer interconnection.

#### **1.4** Outline of Dissertation

The dissertation is broadly organized as follows. Chapter 2 describes the modeling and design of TPVs in silicon interposers. Chapter 3 describes the modeling and design of TPVs in glass interposers. Chapter 4 presents the design and comparative analysis of power-delivery networks in Si and glass interposers. The characterization of interconnections in Si and glass interposers is presented in Chapter 5. Chapter 6 presents the modeling and design of ultra-fine pitch Nano-Cu chip-to-interposer interconnections. Chapter 7 concludes this dissertation and proposes future work.

### **CHAPTER 2**

#### TPV IN SILICON INTERPOSERS

Three-dimensional (3D) integration of microelectronic systems reduces the interconnection length, wiring delay, and system size while enhancing functionality by heterogeneous integration. Through silicon vias (TSVs) are the vertical interconnections in 3D ICs. Through package via in silicon interposers (Si TPV) is a key building block for high performance 3D systems. Si TPVs are sometimes referred as TSVs in published literature. This chapter presents accurate electrical modeling of Si TPVs considering metal-oxide-semiconductor (MOS) capacitance effects. Parametric analysis of Si TPV capacitance is performed on several physical and material parameters. Design guidelines are proposed for Si TPVs used in signal and power-delivery networks as well as for Si TPVs as variable capacitors.

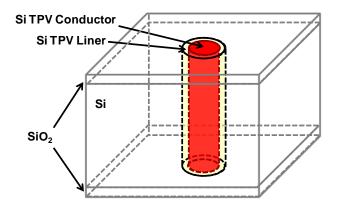

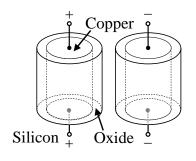

#### 2.1 MOS Capacitance in Si TPVs

Through package vias in Si interposers (Si TPVs) have a cylindrical metal-oxide-semiconductor (MOS) structure as shown in Figure 2. The Si substrate has a layer of SiO<sub>2</sub> liner on its top and bottom surfaces. The through hole is lined with a dielectric material (usually SiO<sub>2</sub>), and filled with a conductive material (typically a metal). The Si substrate is doped either n-type or p-type and is biased (usually to ground potential).

Figure 2. Structure of a through package via in Si interposer (Si TPV).

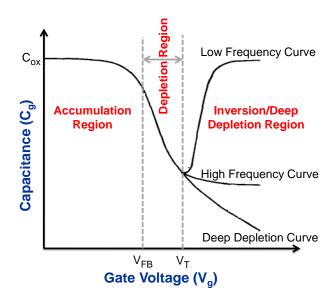

The inner conductor of the Si TPV acts as a metal electrode separated from the biased Si substrate by the dielectric liner - similar to the metal electrode in a MOS capacitor or the gate in a MOSFET. Figure 3 shows a typical capacitance ( $C_g$ ) plot with change in the gate voltage ( $V_g$ ) for a planar MOS structure in a p-type doped Si substrate. The C-V plot for the MOS capacitance effect in Si TPV also exhibits a similar trend [47].

Figure 3. Capacitance-Voltage plot for a planar-MOS capacitor in p-type Si. ( $V_{FB}$ : Flat band voltage,  $V_{T}$ : Threshold voltage,  $C_{ox}$ : Oxide capacitance)

As shown in Figure 3, at high gate voltages the MOS capacitance has three possibilities - deep depletion, high frequency, and low frequency.

When the DC component of the gate voltage changes very fast (typically, > 5 V/s) the generation of minority carriers cannot keep up with the rate of change of the gate voltage [48]. Hence, no inversion region is formed. Any increase in the gate voltage is matched by an increase in the width of the depletion region resulting in the deep depletion mode of operation. Si TPVs in the signal-delivery network of digital systems carry high-frequency signals with sharp rise and fall time, and therefore follow the deep depletion C-V curve.

When the DC component of the gate voltage changes slowly, an inversion region is formed for high gate voltage. The MOS capacitor behavior is determined by the frequency of the small signal AC component of the gate voltage. The minority carrier generation rate cannot keep up with high-frequency (typically, > 1 MHz) small signal AC component of the gate voltage [48]. In this high frequency mode of operation, the depletion width changes with any AC change in the gate voltage. Si TPVs in the power-delivery network of digital systems carry DC power along with high-frequency noise (such as simultaneous switching noise). These Si TPVs follow the high frequency C-V curve.

When the gate voltage has a low frequency small signal AC component, the minority carrier generation rate matches any change in the gate voltage. The width of the inversion region changes with the gate voltage in this low frequency mode of operation. Si TPVs in an ideal power-delivery network (i.e., without any high-frequency noise) follow the low frequency C-V curve.

#### 2.2 Electrical Modeling

The MOS capacitance of a Si TPV is analytically modeled in this section. The electric field, potential, and charge distribution around the Si TPV is obtained by solving Poisson's equation in cylindrical co-ordinates. The charges, if present, in the SiO<sub>2</sub> liner and the Si-SiO<sub>2</sub> interface are neglected. The Si substrate is modeled to be biased at ground potential. The analysis is performed for a p-type Si substrate but a similar analysis can also be performed for an n-type Si substrate as well.

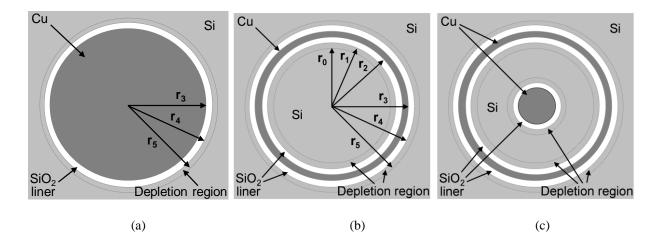

Three types of Si TPV shapes are considered as shown in Figure 4. The MOS capacitance analysis is performed at (i) the inner surface and, (ii) the outer surface of the Si TPV. The cylindrical Si TPVs require only the second analysis while the annular and co-axial Si TPVs require both the analyses. The case of the cylindrical Si TPV (i.e., the analysis at the outer surface) is presented first.

Figure 4. Schematic cross-section diagram of Si TPV (with  $SiO_2$  liner) biased in the depletion region of operation. (a) Cylindrical Si TPV. (b) Annular Si TPV. (c) Coaxial Si TPV.

## 2.2.1 Full Depletion Approximation Analysis

The analysis is first performed with the full depletion approximation (FDA). The FDA simplifies the analysis by assuming that the depletion region (formed in the semiconductor) is fully depleted (i.e., there are no mobile charge carriers in the depletion region). The more detailed analysis is presented in Section 2.2.2.

## 2.2.1.1 Outer Surface

The voltage on the Si TPV, V<sub>TPV</sub>, can be expressed by the following equation:

$$V_{TPV} = \frac{Q_{TPV}}{C_{ox,out}} + V_{FB} + \varphi_S \tag{1}$$

where,

$Q_{TPV}$  = Charge on the Si TPV

$C_{ox,out}$  = SiO<sub>2</sub> liner capacitance

$V_{FB}$  = Flat band voltage

$\varphi_S$  = Surface potential at the Si-SiO<sub>2</sub> interface.

For a Si TPV (as shown in Figure 4) with length L, the oxide layer capacitance at the outer surface ( $C_{ox,out}$ ) can be expressed by the cylindrical capacitor formula as follows:

$$C_{ox,out} = \frac{2\pi\varepsilon_{ox}L}{\ln\frac{r_4}{r_3}}$$

(2)

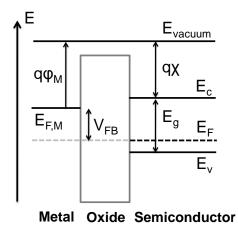

Figure 5. Energy diagram of a metal-oxide-semiconductor (MOS) junction at flat band condition. The semiconductor is doped p-type.

The flat band voltage ( $V_{FB}$ ) is the voltage that needs to be applied on the Si TPV to obtain a flat band energy diagram as shown in Figure 5. In a flat band condition, there are no charges in the semiconductor.  $V_{FB}$  is the difference between the work function of the Si TPV metal ( $\varphi_M$ ) and the silicon ( $\varphi_{Si}$ ). It can be expressed by the following equation:

$$V_{FB} = \varphi_M - \varphi_{Si} = \varphi_M - X - \frac{E_g}{2g} - \varphi_t ln \frac{N_a}{n_i}$$

(3)

where,

X = Electron affinity of Si (4.05 V)

$E_g$  = Band gap energy of Si (1.12 eV at room temperature)

$q = Electronic charge (1.6022 \times 10^{-19} coulombs)$

$$\varphi_t = \frac{KT}{q} = 0.026 \text{ V (at 300 °K)}$$

$K = Boltzmann's constant = 1.3807 \times 10^{-23} \text{ m}^2 \text{ kg s}^{-2} \text{ K}^{-1}$

T = Absolute temperature

$N_a$  = Doping concentration of the acceptor ions

$n_i = \text{Intrinsic carrier concentration of Si} \ (1.18 \ x \ 10^{10} \ \text{cm}^{\text{--}3} \ \text{at } 300 \ \text{°K}).$

To calculate the surface potential ( $\varphi_S$ ), the charge distribution around the Si TPV can be represented by Poisson's equation in cylindrical co-ordinates as follows:

$$\frac{d^2\varphi}{dr^2} + \frac{1}{r}\frac{d\varphi}{dr} = -\frac{\rho}{\varepsilon_{\rm S}} \tag{4}$$

$\varphi$  and  $\rho$  are the potential and charge density at a radius r, respectively, and  $\varepsilon_S$  is the permittivity of Si. Due to geometry, the charge distribution is modeled to be axisymmetric and not varying along the length of the Si TPV.

Poisson's equation in cylindrical co-ordinates (Equation 4) can be solved with the full depletion approximation (FDA) to simplify the analysis. In the FDA, the depletion layer charge is approximated to be entirely because of the ionized acceptor atoms. Equation 4 can be re-written as following:

$$\frac{1}{r}\frac{d}{dr}\left(r\frac{d\varphi}{dr}\right) = \frac{qN_a}{\varepsilon_s} \tag{5}$$

The potential and the electric field at the edge of the outer depletion region ( $r = r_5$  in Figure 4) is zero. Integrating Equation 5 from r (where  $r_4 < r < r_5$ ) to  $r_5$ ,

$$-r\frac{d\varphi}{dr} = \frac{qN_a}{2\varepsilon_s}(r_5^2 - r^2) \tag{6}$$

Integrating from  $r_4$  to  $r_5$ ,

$$\varphi_S = \frac{qN_a}{2\varepsilon_S} \left( r_5^2 \ln \frac{r_5}{r_4} - \frac{r_5^2 - r_4^2}{2} \right) \tag{7}$$

where  $\varphi_S$  = Surface potential at the Si-SiO<sub>2</sub> interface.

The charge on the metal, Q<sub>TPV</sub> is equal to the charge in the depletion region.

$$Q_{TPV} = qN_a\pi(r_5^2 - r_4^2)$$

(8)

Equation 1 can be re-written using Equations 2, 3, 7, and 8 as the following:

$$V_{G} = \varphi_{M} - \chi - \frac{E_{g}}{2q} - \varphi_{t} ln \frac{N_{a}}{n_{i}} + \frac{qN_{a}}{2\varepsilon_{S}} \left(r_{5}^{2} ln \frac{r_{5}}{r_{4}} - \frac{r_{5}^{2} - r_{4}^{2}}{2}\right) + \frac{qN_{a}(r_{5}^{2} - r_{4}^{2})}{2\varepsilon_{ox}} ln \frac{r_{4}}{r_{3}}$$

(9)

The radius of the edge of the depletion region,  $r_5$ , is calculated from Equation 9. It is used to calculate the depletion capacitance.

$$C_{d,out} = \frac{2\pi\varepsilon_s L}{\ln\frac{r_5}{r_4}}$$

(10)

The total Si TPV capacitance ( $C_{TPV}$ ) is a series combination of the oxide and depletion capacitance.

$$\frac{1}{C_{TPV}} = \frac{1}{C_{ox,out}} + \frac{1}{C_{d,out}}$$

(11)

At threshold condition, the Si-SiO<sub>2</sub> surface potential is twice the bulk potential  $(\varphi_B)$ .

$$\varphi_S = 2\varphi_B = 2\varphi_t ln \frac{N_a}{n_i}$$

(12)

The radius of the outer depletion region edge at threshold  $(r_{5,T})$  is calculated by equating Equation 7 to  $2\varphi_B$ .

$$\frac{qN_a}{2\varepsilon_S} \left( r_{5,T}^2 ln \frac{r_{5,T}}{r_4} - \frac{r_{5,T}^2 - r_4^2}{2} \right) = 2\varphi_B$$

(13)

Using Equations 9 and 13, the threshold voltage can be calculated by the following equation:

$$V_{T,out} = \varphi_M - \chi - \frac{E_g}{2q} + \varphi_t ln \frac{N_a}{n_i} + \frac{qN_a(r_{5,T}^2 - r_4^2)}{2\varepsilon_{ox}} ln \frac{r_4}{r_3}$$

(14)

## 2.2.1.2 Inner Surface

The inner surface analysis is applicable for annular and co-axial Si TPVs. The voltage on the Si TPV,  $V_{TPV}$ , can be expressed by the following equation:

$$V_{TPV} = \frac{Q_{TPV}}{C_{ox,out}} + V_{FB} + \varphi_S \tag{15}$$

where,

$Q_{TPV}$  = Charge on the Si TPV

$C_{ox,in}$  = SiO<sub>2</sub> liner capacitance

$V_{FB}$  = Flat band voltage

$\varphi_S$  = Surface potential at the Si-SiO<sub>2</sub> interface.

For a Si TPV (as shown in Figure 4) with length L, the oxide layer capacitance at the inner layer  $(C_{ox,in})$  can be expressed by the cylindrical capacitor formula.

$$C_{ox,in} = \frac{2\pi\varepsilon_{ox}L}{\ln\frac{r_2}{r_1}} \tag{16}$$

To calculate the surface potential  $(\varphi_S)$ , the charge distribution around the Si TPV can be represented by Poisson's equation in cylindrical co-ordinates which can be simplified with the FDA to obatin Equation 5. The potential and the electric field at the edge of the inner depletion region  $(r = r_0 \text{ in Figure 4})$  is zero. Integrating Equation 5 from  $r_0$  to r (where  $r_0 < r < r_1$ ),

$$r\frac{d\varphi}{dr} = \frac{qN_a}{2\varepsilon_c}(r^2 - r_0^2) \tag{17}$$

Integrating from  $r_0$  to  $r_1$

$$\varphi_S = \frac{qN_a}{2\varepsilon_S} \left( \frac{r_1^2 - r_0^2}{2} - r_0^2 ln \frac{r_1}{r_0} \right)$$

(18)

where  $\varphi_S$  = Surface potential at the Si-SiO<sub>2</sub> interface.

The charge on the metal, Q<sub>TPV</sub> is equal to the charge in the depletion region.

$$Q_{TPV} = qN_a\pi(r_1^2 - r_0^2)$$

(19)

Equation 15 can be re-written using Equations 3, 16, 18, and 19 in the following way:

$$V_{G} = \varphi_{M} - \chi - \frac{E_{g}}{2q} - \varphi_{t} ln \frac{N_{a}}{n_{i}} + \frac{qN_{a}}{2\varepsilon_{S}} \left( \frac{r_{1}^{2} - r_{0}^{2}}{2} - r_{0}^{2} ln \frac{r_{1}}{r_{0}} \right) + \frac{qN_{a}(r_{1}^{2} - r_{0}^{2})}{2\varepsilon_{ox}} ln \frac{r_{2}}{r_{1}}$$

(20)

The radius of the edge of the depletion region,  $r_0$ , is calculated from Equation 20. It is used to calculate the depletion capacitance.

$$C_{d,in} = \frac{2\pi\varepsilon_{s}L}{\ln\frac{r_{1}}{r_{0}}}$$

(21)

The capacitance of an annular Si TPV is a combination of the inner and outer surface capacitances.

$$C_{TPV} = \left(\frac{1}{C_{ox,in}} + \frac{1}{C_{d,in}}\right)^{-1} + \left(\frac{1}{C_{ox,out}} + \frac{1}{C_{d,out}}\right)^{-1} \tag{22}$$

At threshold condition, the Si-SiO<sub>2</sub> surface potential is twice the bulk potential( $\varphi_B$ ), as expressed in Equation 12. The radius of the inner depletion region edge at threshold ( $r_{0,T}$ ) is calculated by equating Equation 18 to  $2\varphi_B$ .

$$\frac{qN_a}{2\varepsilon_S} \left( \frac{r_1^2 - r_0^2}{2} - r_0^2 \ln \frac{r_1}{r_0} \right) = 2\varphi_B$$

(23)

Using Equations 20 and 23, the threshold voltage is given as follows:

$$V_{T,in} = \varphi_M - \chi - \frac{E_g}{2q} + \varphi_t ln \frac{N_a}{n_i} + \frac{qN_a(r_1^2 - r_{0,T}^2)}{2\varepsilon_{ox}} ln \frac{r_2}{r_1}$$

(24)

### 2.2.2 Exact Analysis

The full depletion approximation (FDA) enables a simple analysis but it does not provide the most accurate result. Poisson's equation in cylindrical co-ordinates (Equation 4) can be analyzed rigorously without using the FDA to obtain a more accurate result.

The charge distribution in the silicon is composed of fixed doping ions  $(N_a)$ , holes (p), and electrons (n) in the semiconductor. The charge density can therefore be expressed by the following equations:

$$\rho = q(-N_a + p - n) \qquad (25)$$

$$\rho = qN_a \left(-1 + e^{-\frac{\varphi}{\varphi_t}} - e^{\frac{\varphi - 2\varphi_B}{\varphi_t}}\right) \qquad (26)$$

$$\varphi_B = \varphi_t \ln \frac{N_a}{n_t} \qquad (27)$$

Equation 4 can be re-written using Equation 26 as following:

$$\frac{d^2\varphi}{dr^2} + \frac{1}{r}\frac{d\varphi}{dr} = \frac{qN_a}{\varepsilon_S} \left( 1 - e^{-\frac{\varphi}{\varphi_t}} + e^{\frac{\varphi - 2\varphi_B}{\varphi_t}} \right) \tag{28}$$

There are no analytical solutions to Equation 28. Hence, this equation is solved numerically using the classical 4<sup>th</sup> order Runge-Kutta method [49] in MATLAB.

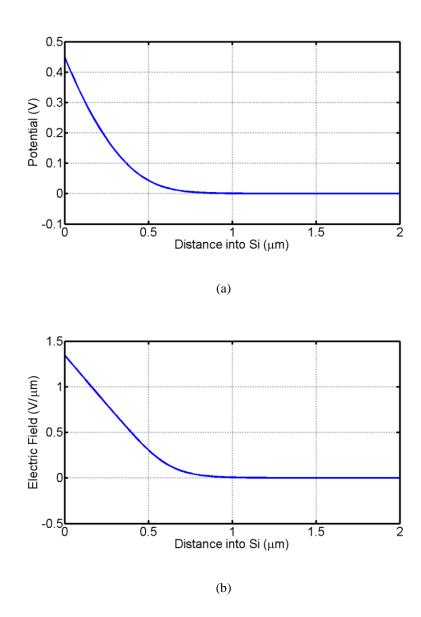

The initial conditions are the surface potential  $(\varphi)$  and electric field  $(-d\varphi/dr)$  at the Si-SiO<sub>2</sub> interface  $(r = r_4)$ . For a given surface potential, the electric field at the Si-SiO<sub>2</sub> interface is obtained iteratively such that the potential and electric field distributions converge as shown in Figure 6 (a) and (b).

Figure 6. (a) Potential and, (b) Electric field distribution in Si as a function of the distance from the Si-SiO<sub>2</sub> interface when  $V_{TPV}=0.6V$ . Oxide liner thickness = 0.1  $\mu m$ .

The distance at which the potential and electric fields become zero represents the edge of the depletion region. Equation 26 along with the potential distribution can be used to plot the charge distribution in Si as shown in Figure 7.

Figure 7. Charge distribution in Si as a function of the distance from the Si-SiO $_2$  interface when  $V_{TPV}=0.6V$ .

The charge on the Si TPV  $(Q_{TPV})$  is equal to the total charge in the Si.

$$Q_{TPV} = \varepsilon_S \oint_{S} E \, dS = -2\pi r_4 L \varepsilon_S \frac{d\varphi}{dr} \Big|_{r=r_4} \tag{29}$$

In Equation 29, the value of the electric field at the  $Si\text{-}SiO_2$  interface  $(r=r_4)$  is obtained from the numerical solution of Equation 28. Using Equations 1, 2, 3, and 29, the voltage on the Si TPV for a given surface potential can be calculated. The Si TPV capacitance for a given Si TPV voltage is also calculated from the potential and electric field distributions in Si.

$$C_{TPV} = \frac{dQ}{d\varphi}\Big|_{r=r_{\Delta}} \tag{30}$$

$$\Rightarrow C_{TPV} = 2\pi r_4 \, \varepsilon_S \frac{d}{d\varphi} \left( -\frac{d\varphi}{dr} \right) \bigg|_{r=r_4} \tag{31}$$

The threshold point is reached when  $\varphi_S = 2\varphi_B$ . At this point, the Si TPV voltage is called the threshold voltage (V<sub>T</sub>).

In low frequency operation, the Si TPV capacitance is obtained from Equation 31. In high-frequency operation, beyond the threshold voltage, the Si TPV capacitance remains constant at the capacitance value reached at threshold point. In the deep depletion mode of operation, the inversion region (composed of minority charges) does not form due to the fast change in the DC component of the voltage carried by the Si TPV. The capacitance in this mode, beyond the threshold voltage, is obtained by neglecting the minority carrier density (n in a p-type doped Si substrate) in Equation 25.

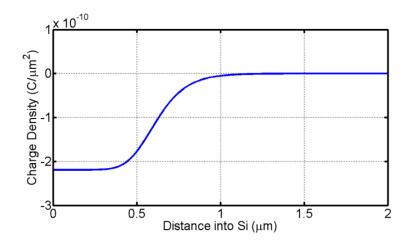

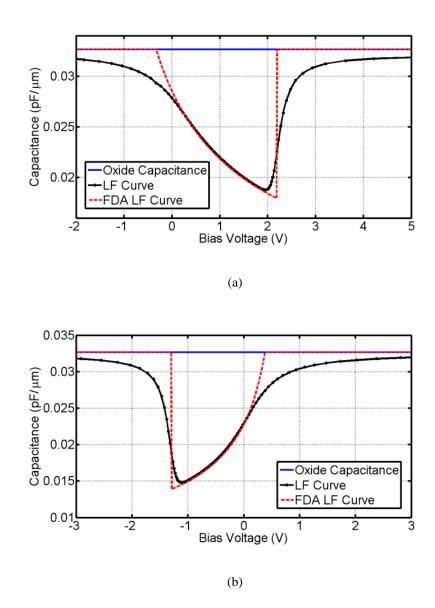

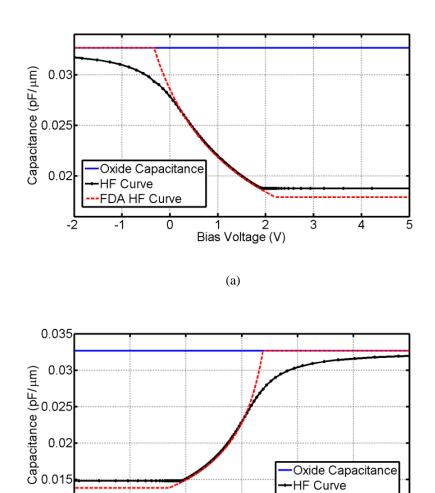

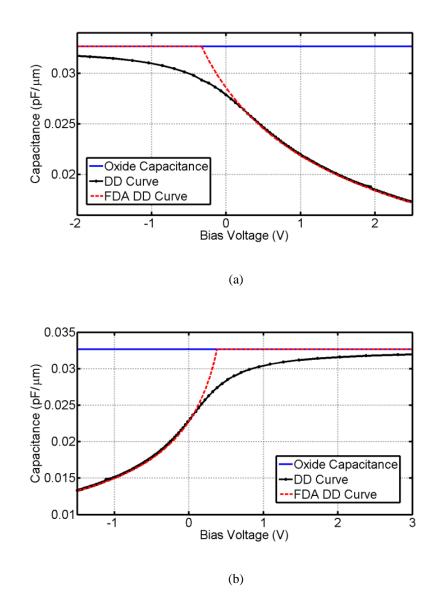

The low frequency, high frequency, and deep depletion Si TPV capacitance-voltage (C-V) curves are shown in Figure 8, Figure 9, and Figure 10 respectively. These figures compare the Si TPV C-V plots obtained by this analysis with those obtained by using the FDA. The Si TPV is modeled to be filled with copper. It is 30  $\mu$ m in diameter with 0.1  $\mu$ m thick SiO<sub>2</sub> liner. The resistivity of the Si substrate is 1  $\Omega$ -cm resistivity. In Figure 8, Figure 9, and Figure 10, the term 'Bias Voltage' refers to the voltage difference between the Si TPV and the Si substrate.

If the MOS capacitance effect is neglected then the Si TPV capacitance is equal to just the oxide capacitance. The solid blue curves in Figure 8, Figure 9, and Figure 10 represents this C-V plot. It is observed from these figures that neglecting the MOS effect in Si TPV can lead to significant inaccuracies in calculating its capacitance. Using only the oxide capacitance (by neglecting the MOS effect) results in over estimation of the

TSV capacitance. This can lead to errors while designing interconnections in 3D ICs and Si interposers.

Figure 8. Per unit length Si TPV capacitance-voltage plots for low frequency operation in (a) p-type doped silicon, and (b) n-type doped silicon. Black solid curve with dots: Exact C-V plot. Red dotted curve: C-V plot assuming full depletion approximation. Blue solid curve: Oxide capacitance (C-V plot neglecting MOS effect).

Figure 9. Per unit length Si TPV capacitance-voltage plots for high frequency operation in (a) p-type doped silicon, and (b) n-type doped silicon. Black solid curve with dots: Exact C-V plot. Red dotted curve: C-V plot assuming full depletion approximation. Blue solid curve: Oxide capacitance (C-V plot neglecting MOS effect).

0 Bias Voltage (V)

(b)

0.01<u>L</u>

-2

Oxide Capacitance

HF Curve FDA HF Curve

Figure 10. Per unit length Si TPV capacitance-voltage plots for deep depletion operation in (a) p-type doped silicon, and (b) n-type doped silicon. Black solid curve with dots: Exact C-V plot. Red dotted curve: C-V plot assuming full depletion approximation. Blue solid curve: Oxide capacitance (C-V plot neglecting MOS effect).

From Figure 8, Figure 9, and Figure 10 it is observed that the FDA solution results in considerable error near the flat band and threshold regions. The FDA assumes that there are no mobile charge carriers (holes or electrons) in the depletion region. In the low frequency operation FDA approximates the Si TPV capacitance to be equal to the liner capacitance in the accumulation and inversion regions.

In reality, there are significant contributions from the mobile charge carriers near the flat band and threshold points. This is the cause for the inaccuracies suffered by the full depletion approximation. The numerical analysis of Poisson's equation considering the fixed and mobile charges in Si, as described in this section, captures the actual Si TPV C-V relationship. This analysis considers uniform doping in the Si substrate. The analysis for a non-uniformly doped Si substrate can be performed as a continuation of this research work in the future. The effect of generation-recombination can also be studied in detail as part of a future work.

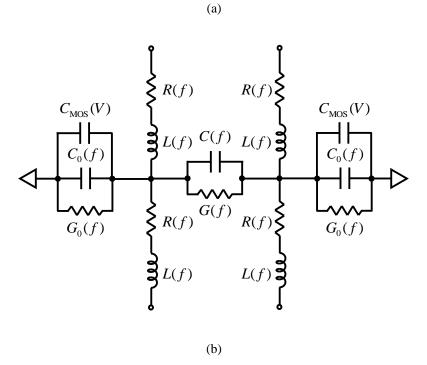

#### 2.2.3 Electrical Model

Modeling the MOS capacitance of the Si TPV is important in developing an accurate electrical circuit-model. Figure 11 shows the equivalent circuit-model of a pair of Si TPVs.

Figure 11. (a) Schematic view, and (b) Equivalent circuit-model of a pair of Si TPVs.

The frequency dependent parameters R(f), L(f), C(f), G(f),  $C_0(f)$ , and  $G_0(f)$  are derived in [50]. R(f) and L(f) represents the resistance and inductance of the Si TPV. C(f) is the coupling capacitance between the Si TPVs while G(f) is the silicon substrate conductance between the Si TPVs.  $C_0(f)$  and  $G_0(f)$  are the capacitance and substrate conductance to ground respectively.  $C_{MOS}(V)$  represents the voltage-dependent MOS capacitance of the Si TPV.

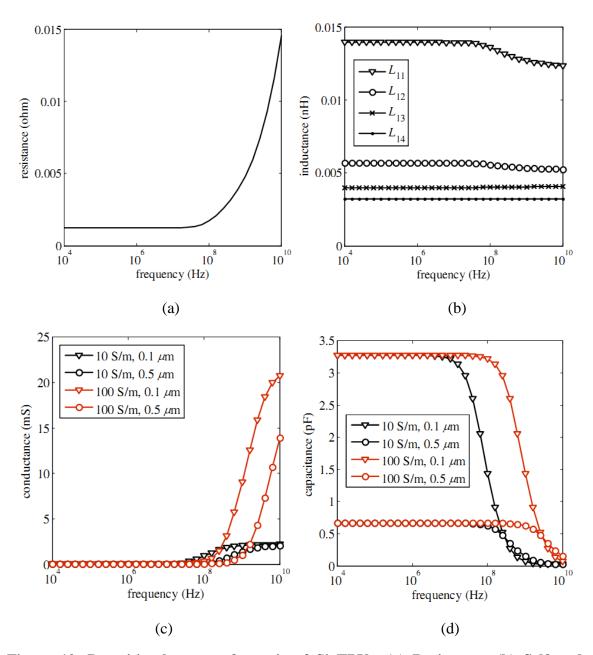

Figure 12 shows the electrical parasitics of a pair of Si TPVs. The via diameter was 30  $\mu$ m, via pitch was 60  $\mu$ m, and via length was 100  $\mu$ m. Four models were modeled – (i) 0.1  $\mu$ m thick SiO<sub>2</sub> liner and 10 S/m Si conductivity, (ii) 0.5  $\mu$ m thick SiO<sub>2</sub> liner and 10 S/m Si conductivity, and (iv) 0.5  $\mu$ m thick SiO<sub>2</sub> liner and 100 S/m Si conductivity, and 100 S/m Si conductivity corresponds to 10  $\Omega$ -cm and 1  $\Omega$ -cm resistivity, respectively.

The resistance and inductance varies with frequency, as shown in Figure 12 (a) and Figure 12 (b), because of proximity and skin effects. In Figure 12 (b),  $L_{11}$  represents the self inductance of the Si TPV. Mutual inductance between the Si TPVs is represented by the terms  $L_{12}$ ,  $L_{13}$ , and  $L_{14}$ . The resistance and inductance plots are independent of the SiO<sub>2</sub> liner thickness and the Si resistivity because these terms are dependent only on the via (conductor) geometry.

Figure 12 (c) plots the equivalent conductance ( $G_0(f) + 2G(f)$ ) of the Si TPV. The capacitance and conductance of the vias are influenced by the SiO<sub>2</sub> liner thickness and Si conductivity. The conductance at high frequencies depends strongly on the Si conductivity. The via conductance increases with increase in Si conductivity. Decreasing the liner thickness increases the equivalent conductance of the via because of more Si material between the vias.

Figure 12. Parasitic elements of a pair of Si TPVs. (a) Resistance, (b) Self and mutual inductance, (c) Equivalent conductance, (d) Equivalent capacitance.

Figure 12 (d) plots the equivalent capacitance  $(C_0(f) + 2C(f))$  of the Si TPV. The capacitance depends strongly on the liner thickness at low frequency and on the Si conductivity at high frequency. At low frequency, the capacitance increases with decrease in the liner thickness. At high frequency, the capacitance decreases with decrease in Si conductivity.

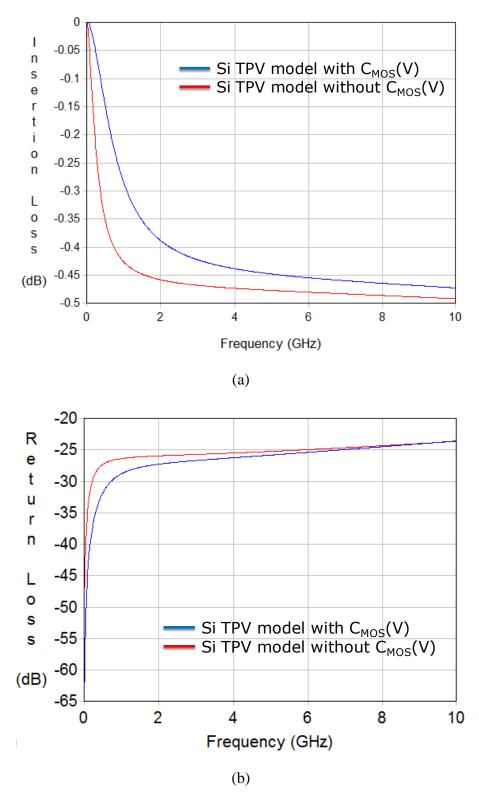

Figure 13 compares the s-parameters obtained from the circuit model of a pair of Si TPVs with and without the MOS capacitance element. The via diameter was 30  $\mu$ m, via pitch was 60  $\mu$ m, and via length was 100  $\mu$ m. The Si TPV was modeled with 0.1  $\mu$ m thick SiO<sub>2</sub> liner and 10  $\Omega$ -cm Si resistivity. It is observed that when the MOS capacitance is neglected it leads to higher insertion and return loss estimation of the Si TPVs because of overestimating the via capacitance.

Figure 13. S-parameter comparison of Si TPV model with and without MOS capacitance. (a) Insertion Loss, (b) Return Loss.

### 2.3 Parametric Study

The effect of different Si TPV physical parameters on its capacitance was studied based on the MOS capacitance analysis described in the previous section. This section discusses the results of these parametric studies on cylindrical Si TPVs. Similar trends were observed for annular [51] and co-axial Si TPVs as well. The different Si TPV parameters that were studied are (i) Si TPV diameter, (ii) Si TPV liner thickness, (iii) Si TPV liner material, (iv) Si resistivity, and (v) Si TPV metal. The Si TPV capacitance-voltage curves for high frequency operation are plotted for these comparisons. In this section, 'Bias Voltage' refers to the difference in voltage between the Si TPV and the silicon substrate.

#### 2.3.1. Si TPV Diameter

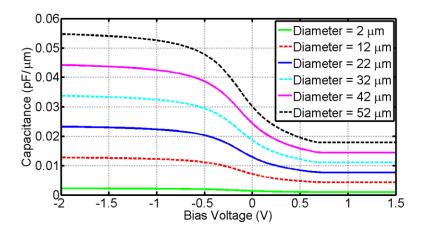

The effect of varying the Si TPV diameter on its capacitance was studied. The Cu filled Si TPVs were modeled with 0.1  $\mu$ m thick SiO<sub>2</sub> liner. The Si was modeled as a p-type substrate with 10  $\Omega$ -cm resistivity and biased to ground potential. Figure 14 shows the per unit length Si TPV capacitance plotted as a function of the (Si TPV to Si) bias voltage difference for different Si TPV diameters.

Figure 14. Per unit length Si TPV capacitance-voltage plots for different Si TPV diameters.

It is observed from Figure 14 that the Si TPV capacitance decreases with decrease in the Si TPV diameter. Further, the difference between the Si TPV capacitance in the accumulation and inversion regions decrease with decrease in the Si TPV diameter.

The Si TPV capacitance is a series combination of the liner capacitance and the depletion capacitance. In the accumulation region, the Si TPV capacitance is very close to the oxide capacitance value. The Si TPV capacitance in the depletion and inversion region is influenced by the depletion capacitance. As compared to the depletion capacitance, the liner capacitance reduces faster with reduction in the Si TPV diameter because the liner thickness was considered to be constant. This results in smaller difference in Si TPV capacitance between accumulation and inversion regions with decrease in Si TPV diameter.

In other words, a Si TPV with a smaller liner thickness to Si TPV diameter ratio leads to a larger difference between the Si TPV capacitance in the accumulation and inversion regions.

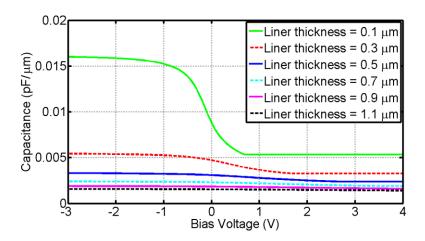

#### 2.3.2. Liner Thickness

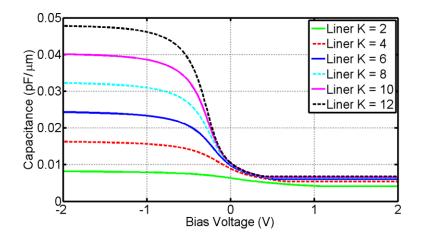

The effect of varying the Si TPV liner thickness on its capacitance was studied. The Cu-filled Si TPVs were modeled with a diameter of 15  $\mu$ m and SiO<sub>2</sub> liner. The Si was modeled as a p-type substrate with 10  $\Omega$ -cm resistivity and biased to ground potential. Figure 15 shows the per unit length Si TPV capacitance plotted as a function of the (Si TPV to Si) bias voltage difference for different Si TPV liner thicknesses.

Figure 15. Per unit length Si TPV capacitance-voltage plots for different Si TPV liner thicknesses.

It is observed from Figure 15 that the Si TPV capacitance decreases with increase in the Si TPV liner thickness. Further, the difference between the Si TPV capacitance in the accumulation and inversion regions decrease rapidly with increase in the Si TPV liner thickness.

A thicker Si TPV liner reduces the liner capacitance. A thicker Si TPV liner also leads to a smaller electric field at the Si-liner interface. This creates a smaller depletion region which leads to a higher depletion capacitance. Due to these effects, the difference

between the Si TPV capacitance in the accumulation and inversion regions rapidly decrease with increase in the liner thickness. For Si TPVs with thick (> 1  $\mu$ m) liner the MOS capacitance effect is negligible.

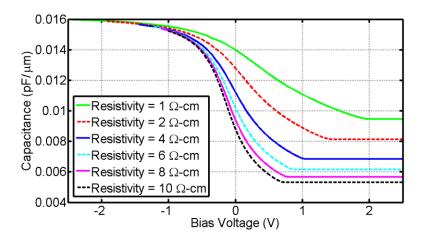

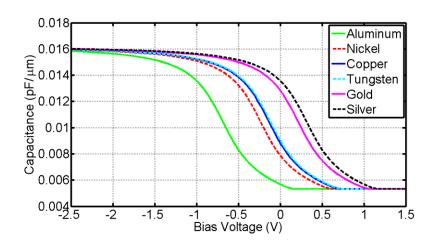

#### 2.3.3. Liner Material

The effect of using different Si TPV liner materials on its capacitance was studied. The Cu-filled Si TPVs were modeled with a diameter of 15  $\mu$ m and 0.1  $\mu$ m thick liner. The Si is modeled as a p-type substrate with 10  $\Omega$ -cm resistivity and biased to ground potential. Figure 16 shows the per unit length Si TPV capacitance plotted as a function of the (Si TPV to Si) bias voltage difference for different Si TPV liner materials.

Figure 16. Per unit length Si TPV capacitance-voltage plots for different Si TPV liner materials.

It is observed from Figure 16 that the Si TPV capacitance decreases with decrease in the dielectric constant of the Si TPV liner material. Further, the difference between the Si TPV capacitance in the accumulation and inversion regions decrease with decrease in the Si TPV liner's dielectric constant.